## MASTER

FPGA platform for emulation of composable and predictable MPSoC power management

She, D.

Award date: 2009

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# EINDHOVEN UNIVERSITY OF TECHNOLOGY

MSC THESIS

# FPGA Platform for Emulation of Composable and Predictable MPSoC Power Management

Dongrui She

Advisors: MSc. Aleksandar Milutinovic Prof.dr. Kees Goossens Prof.dr. Henk Corporaal

September 2, 2009

# Abstract

As the IC technology is advancing quickly, Multi-processor System-on-Chip (MP-SoC) becomes the trend of embedded System-on-Chip (SoC) design. A typical modern MPSoC for embedded systems usually runs multiple applications, some of which have real-time requirements. To meet the real-time requirements, predictable system is needed. The interference between applications in the MPSoC usually result in exponential increase in design and verification complexity. To avoid such situations, we need composable system, on which the temporal behavior of different applications does not depend on each other. In modern IC design, especially for embedded systems, power consumption is becoming a major constraint, which means power management is essential for MPSoC. Hence we need composable and predictable MPSoC with power management capability.

In this thesis, the design and implementation of an FPGA-based composable and predictable platform for emulating the power management of MPSoC are presented. The platform consists of multiple MicroBlaze processor cores and Æthereal Network on Chip (NoC) is used as the interconnection. The platform enables the sharing of different resources, including the processer, among different applications in a composable way. The support for data-flow application in the platform hardware and software enables the predictable execution of streaming applications. And with the power management hardware and software infrastructure, composable and predictable power management for each application is possible. The support for power management in data-flow application is implemented and demonstrated in the experiments, which saves up to 50% energy compared to the trivial power management policy.

# Acknowledgements

The nine months time in the SoC Architectures and Infrastructure research group of the NXP Semiconductors has given me a great opportunity to learn and experiment the research in computer architecture. First, I would like to thank my supervisors at NXP Semiconductors, Kees Gossens and Aleksandar Milutinovic, for their great support and interest in my work. I would also like to thank Henk Corporaal, my supervisor at the university, for providing me with valuable feedback and support. Finally, I would like to thank the other members in the group, especially the students, for the support and the good time I had during my project.

# Contents

| $\mathbf{Li}$ | st of | Figures                                      | iii          |

|---------------|-------|----------------------------------------------|--------------|

| $\mathbf{Li}$ | st of | Tables                                       | $\mathbf{v}$ |

| 1             | Inti  | roduction                                    | 1            |

|               | 1.1   | Challenges in MPSoC Design                   | 1            |

|               | 1.2   | Problem Description                          | 2            |

|               | 1.3   | Requirements                                 | 3            |

|               | 1.4   | Contributions                                | 3            |

|               | 1.5   | Thesis Outline                               | 4            |

| <b>2</b>      | Bas   | ic Concepts and Methodology                  | <b>5</b>     |

|               | 2.1   | Composability                                | 5            |

|               | 2.2   | Real-time Applications and Predictability    | 6            |

|               | 2.3   | Power Management                             | 7            |

|               | 2.4   | Network on Chip                              | 10           |

|               | 2.5   | Data-flow Graph Programming Model            | 11           |

|               | 2.6   | FPGA-based Hardware Emulation and Simulation | 12           |

|               | 2.7   | Proposed System Architecture and Design Flow | 12           |

|               | 2.8   | Summary                                      | 14           |

| 3             | Haı   | dware Platform Design                        | 15           |

|               | 3.1   | NoC Based Interconnection                    | 16           |

|               | 3.2   | Processing Tile Design                       | 17           |

|               | 3.3   | Monitor Tile Design                          | 29           |

|               | 3.4   | System Configuration                         | 30           |

|               | 3.5   | Integration                                  | 30           |

|               | 3.6   | Summary                                      | 31           |

| 4             | Sof   | tware Platform Design                        | 33           |

|               | 4.1   | Scheduling on the Processing Tile            | 34           |

|               | 4.2   | Inter-task Communication                     | 40           |

|               | 4.3   | Power Management                             | 46           |

|               | 4.4   | Monitor Support                              | 50           |

|               | 4.5   | Integration                                  | 51           |

|               | 4.6   | Summary                                      | 53           |

| <b>5</b>     | Exp       | periments and Results                     | 55 |

|--------------|-----------|-------------------------------------------|----|

|              | $5.1^{-}$ | Experimental System Setup                 | 55 |

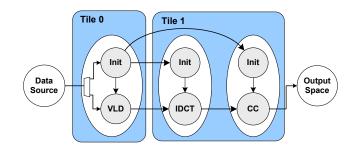

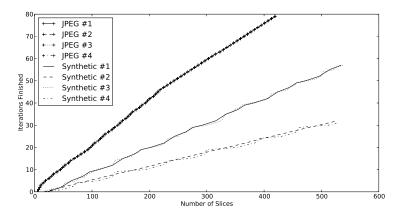

|              | 5.2       | Test Applications                         | 56 |

|              | 5.3       | Experiments and Results                   | 58 |

|              | 5.4       | Summary                                   | 74 |

| 6            | Rel       | ated Work                                 | 75 |

|              | 6.1       | Composable and Predictable MPSoC Platform | 75 |

|              | 6.2       | Power Management in MPSoC                 | 76 |

|              | 6.3       | FPGA-based Hardware Emulation             | 76 |

| 7            | Cor       | clusions and Future Work                  | 79 |

|              | 7.1       | Conclusions                               | 79 |

|              | 7.2       | Future Work                               | 80 |

| Bi           | bliog     | graphy                                    | 81 |

| $\mathbf{A}$ | No        | C Specification XML Files                 | 87 |

|              | A.1       | Architecture Specification                | 87 |

|              |           | Communication Specification               |    |

# **List of Figures**

| 1.1  | A typical architecture of an MPSoC                                  | 1  |

|------|---------------------------------------------------------------------|----|

| 2.1  | Composable system                                                   | 6  |

| 2.2  | Power-delay curve                                                   | 8  |

| 2.3  | An examples of DVFS                                                 | 9  |

| 2.4  | Examples of interconnection based on shared bus and network-on-chip | 10 |

| 2.5  | Data-flow graph                                                     | 11 |

| 2.6  | Proposed architecture                                               | 13 |

| 2.7  | Design Flow of the System                                           | 14 |

| 3.1  | Hardware platform architecture                                      | 15 |

| 3.2  | Æthereal Network Interface                                          | 16 |

| 3.3  | Interconnection based on Æthereal NoC                               | 17 |

| 3.4  | Architecture of the processing tile                                 | 18 |

| 3.5  | MicroBlaze core architecture                                        | 18 |

| 3.6  | Power Management Unit                                               | 20 |

| 3.7  | Example of $\frac{3}{8}$ Output Frequency                           | 22 |

| 3.8  | Architecture of the frequency generator                             | 22 |

| 3.9  | Frequency switch in the frequency generator                         | 23 |

| 3.10 | Gate and un-gate of the clock                                       | 23 |

| 3.11 | Frequency switching with gate and un-gate                           | 24 |

| 3.12 | Connection DMA controller                                           | 26 |

| 3.13 | Tile Communication Infrastructure for Multi-connection              | 28 |

| 3.14 | Communication unit examples                                         | 28 |

| 3.15 | Overlap of DMA transaction and task execution                       | 29 |

| 3.16 | Tile Architecture and Clock Domains                                 | 29 |

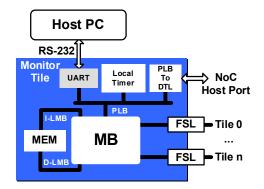

| 3.17 | Monitor Tile Architecture                                           | 30 |

| 3.18 | Hardware Platform Architecture                                      | 31 |

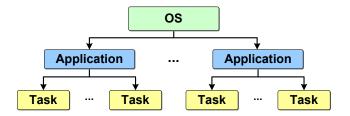

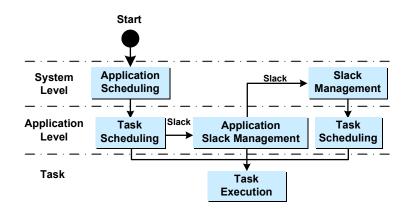

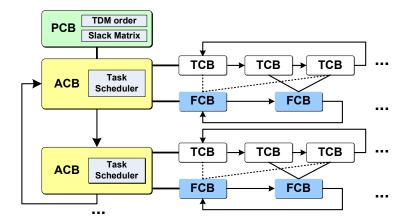

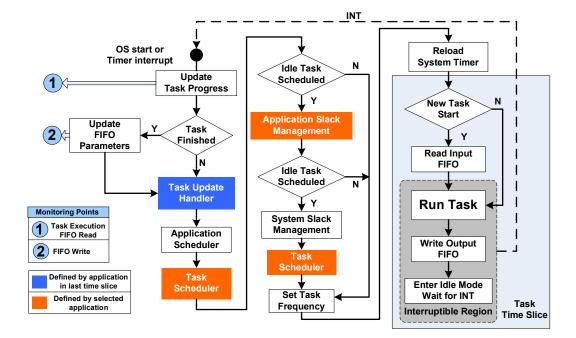

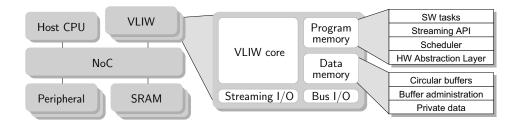

| 4.1  | Hierarchy in the operating system on a processor                    | 33 |

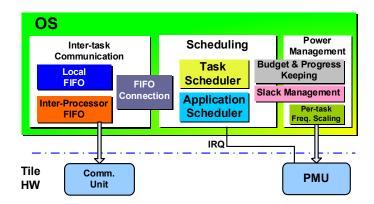

| 4.2  | Operating system structure on processing tile                       | 34 |

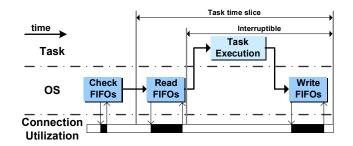

| 4.3  | Time slices in the operating system                                 | 34 |

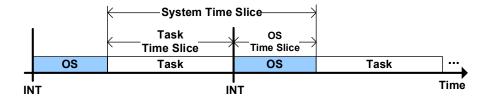

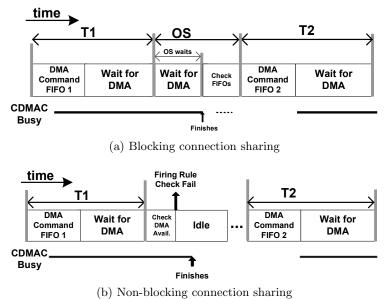

| 4.4  | Use OS time slice to hide the variation                             | 36 |

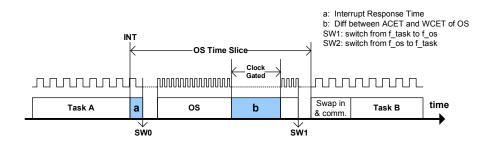

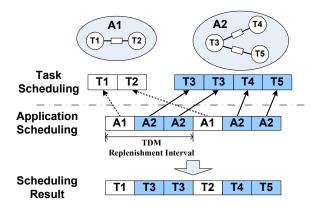

| 4.5  | An Example of Two-level Scheduling                                  | 37 |

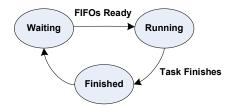

| 4.6  | Different task states in data-flow application                      | 38 |

| 4.7  | Two-level Scheduling with Slack Management                          | 39 |

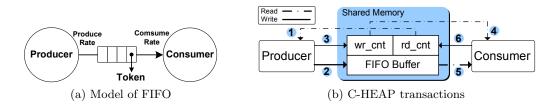

| 4.8  | Model of FIFO and communication protocol                            | 41 |

| 4.9  | Communication Flow for Data-flow Model                                                                                                                                        |

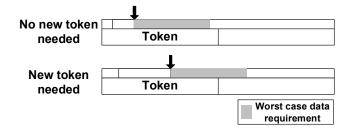

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.10 | Example of Variable Buffer 43                                                                                                                                                 |

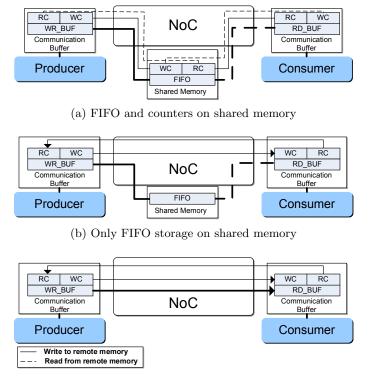

|      | Three different memory mappings of a FIFO 44                                                                                                                                  |

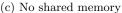

| 4.12 | Connection sharing example                                                                                                                                                    |

|      | Number of time slices changes                                                                                                                                                 |

| 4.14 | Monitoring packet                                                                                                                                                             |

| 4.15 | Data structure of the system                                                                                                                                                  |

|      | Kernel loop of the OS                                                                                                                                                         |

| 5.1  | Dual tile system with VGA output                                                                                                                                              |

| 5.2  | FPGA tool flow                                                                                                                                                                |

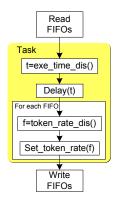

| 5.3  | Flowchart of the synthetic task                                                                                                                                               |

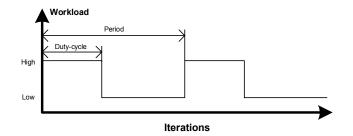

| 5.4  | PWM workload distribution                                                                                                                                                     |

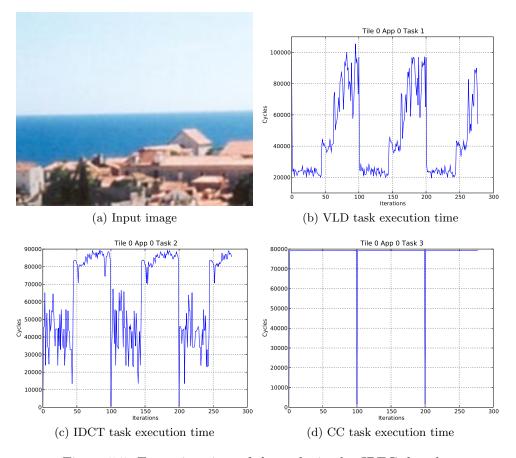

| 5.5  | Execution time of the tasks in the JPEG decoder                                                                                                                               |

| 5.6  | Mapping of the JPEG decoder                                                                                                                                                   |

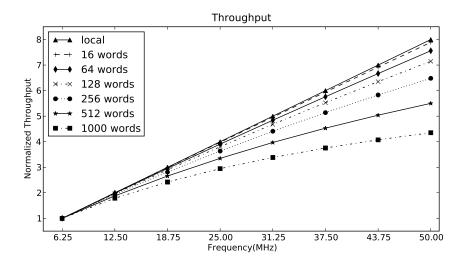

| 5.7  | Throughput at different frequencies                                                                                                                                           |

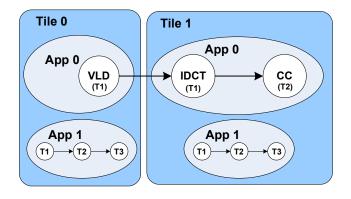

| 5.8  | Slack Management Test Application                                                                                                                                             |

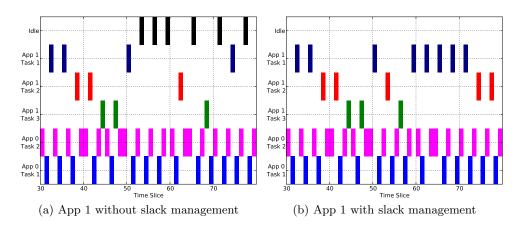

| 5.9  | Scheduling without slack management                                                                                                                                           |

| 5.10 | Scheduling with slack management                                                                                                                                              |

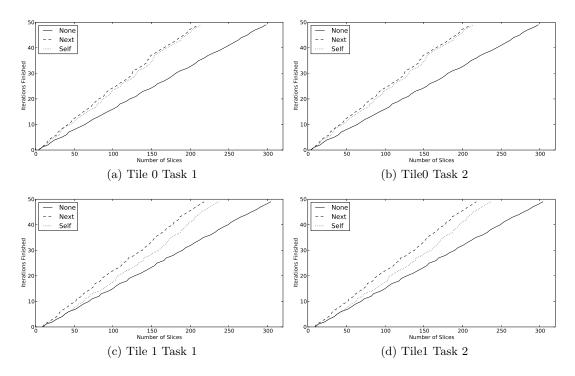

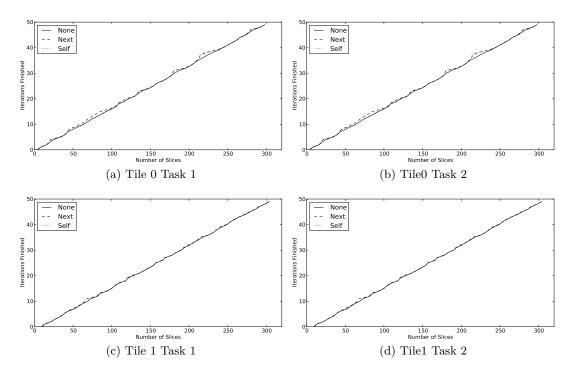

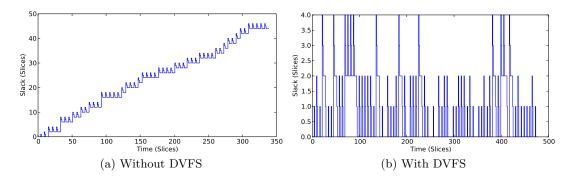

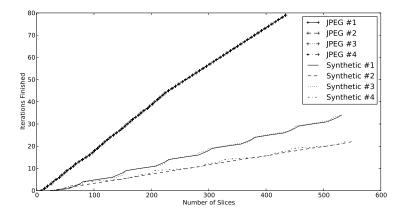

| 5.11 | Throughput without DVFS                                                                                                                                                       |

| 5.12 | Throughput with DVFS                                                                                                                                                          |

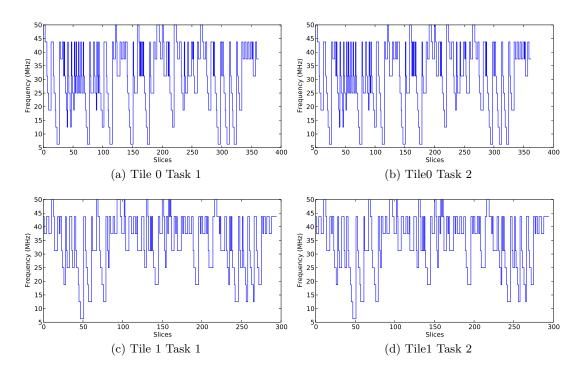

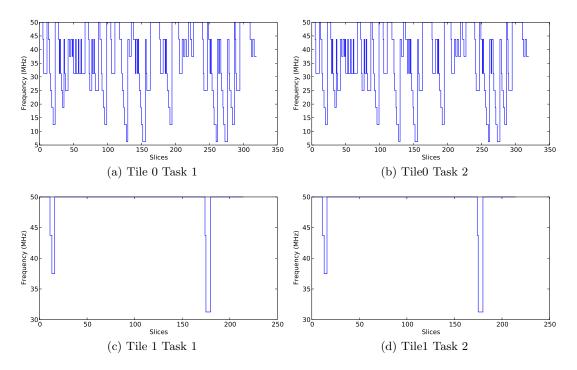

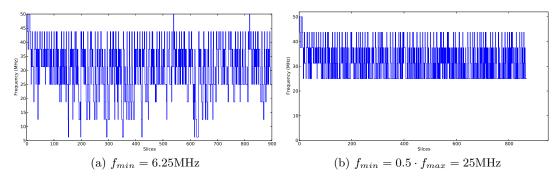

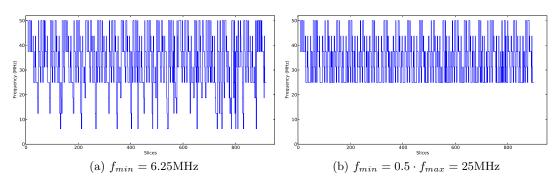

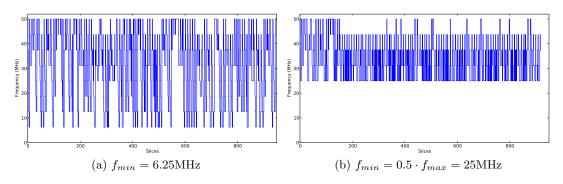

|      | Frequency of each task with next-eligible policy (subsampled) 65                                                                                                              |

|      | Frequency of each task with self policy (subsampled)                                                                                                                          |

|      | Accumulated slack for Tile 0 T2 with next-eligible policy 66                                                                                                                  |

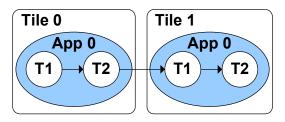

|      | Composability test applications                                                                                                                                               |

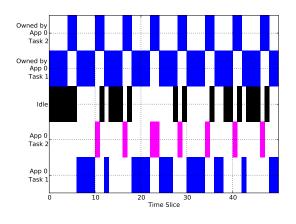

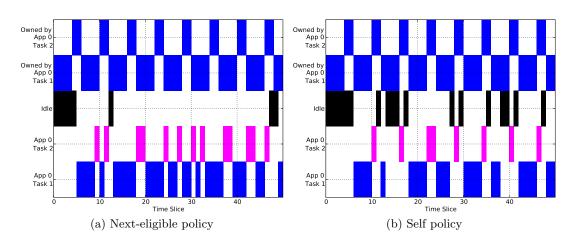

|      | Scheduling of tile 1                                                                                                                                                          |

|      | Throughput in different test cases on tile $0 \ldots $ |

|      | Throughput of different test cases on tile 1                                                                                                                                  |

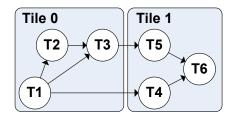

|      | Task graph of the synthetic application                                                                                                                                       |

| 5.21 | Frequency of Tile 0 with random workload                                                                                                                                      |

|      | Frequency of Tile 1 with random workload                                                                                                                                      |

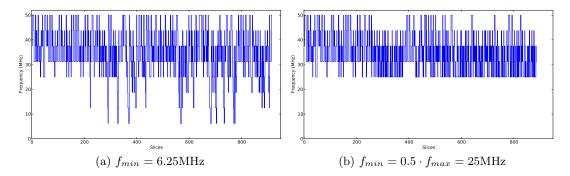

| 5.23 | Frequency of Tile 0 with PWM workload                                                                                                                                         |

| 5.24 | Frequency of Tile 1 with PWM workload                                                                                                                                         |

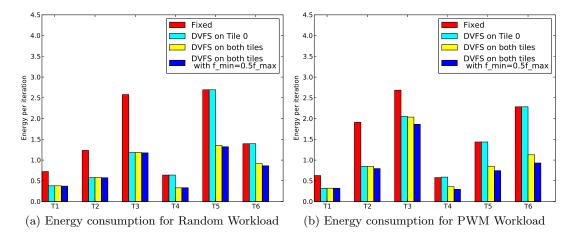

|      | Energy consumption of the test application                                                                                                                                    |

| 6.1  | CoMPSoC architecture template, from [23]                                                                                                                                      |

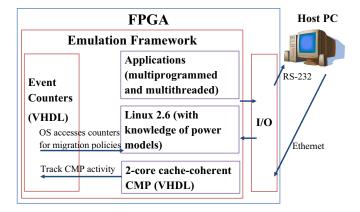

| 6.2  | FPGA based Power Evaluation Platform, from [9] 77                                                                                                                             |

# **List of Tables**

| 4.1  | SDF graph task states                    | 38 |

|------|------------------------------------------|----|

| 4.2  | Different memory mapping of FIFOs        | 43 |

| 4.3  | Monitoring packet types                  | 51 |

| 5.1  | Dual tile system configuration           | 55 |

| 5.2  | Parameters for a synthetic task          | 57 |

| 5.3  | Different workload of the task           | 60 |

| 5.4  | Execution times at different frequencies | 61 |

| 5.5  | Configurations of the synthetic tasks    | 62 |

| 5.6  | Processor utilization                    | 63 |

| 5.7  | Composability test case                  | 67 |

| 5.8  | Task workloads in composability test     | 68 |

| 5.9  | FIFO size in the synthetic application   | 70 |

| 5.10 | Workload of the synthetic tasks          | 70 |

| 5.11 | Energy consumption for random workload   | 72 |

|      |                                          | 74 |

|      |                                          |    |

# Chapter 1 Introduction

A typical chip for an embedded system, i.e. a system-on-chip (SoC) usually integrates different intellectual property (IP) components.

As technology advances rapidly, more complex IPs are integrated to a single chip. Embedded systems, especially the ones in consumer electronics business usually have strict requirements on cost efficiency, power efficiency, and time to market. To fulfill these requirements, modern SoCs tend to integrate multiple programable processing cores such as general purpose processors and DSPs which run software, along with other resources like a external memory controller, resulting in multiprocessor system-on-chip (MPSoC).

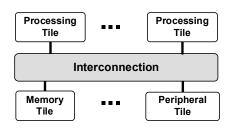

Figure 1.1: A typical architecture of an MPSoC

Fig. 1.1 shows a typical architecture of an MPSoC. The processing tile (PT) consists of a programable processing core, typically a processor or DSP, and local resources that are tightly coupled with the core. An MPSoC has multiple PTs, and other resources such as memories, and these elements communicates with each other via an interconnection infrastructure. To fully utilize the computation power of such a system and achieve cost and power efficiency, multiple applications, some of which have real-time requirements, are mapped on the system. Applications mapped on the system can be independent, and yet they still share some resources.

# 1.1 Challenges in MPSoC Design

The technology development introduces a lot of challenges in the MPSoC design. In this section we will discuss the key challenges in MPSoC design.

#### 1.1.1 Verification Complexity and Composability

With the increasing integration level in MPSoC, the complexity of verification is growing for both software and hardware. Interference between different components of the system, which may come from different vendors, increases the complexity of design and verification. If this interference is not handled properly, the complexity grows exponentially as more IPs and software are integrated in the system.

To keep verification complexity linear, we want to avoid the unintended interference between components in the system. To be specific, the applications in the system should not influence each other unless we want it. A system with such property is called a *composable* system. In such a system, hardware and software components can be designed and verified independently, therefore the complexity of verification is linear in the number of applications and components.

#### 1.1.2 Predictability

In embedded systems, a lot of applications have real-time requirements, e.g. video player should be able to deliver result at a certain frame rate. To meet such requirements, the behavior of the system should be bounded in temporal domain, i.e. it should be *predictable*.

#### 1.1.3 Power Efficiency

Power consumption has become the major concern in the modern IC design. For embedded systems, power efficiency is even more important as many systems are powered very limited power supply, e.g. batteries, solar panels. ICs in embedded systems need to have power management capability in order to achieve power efficiency.

#### 1.1.4 Simulation-based Verification

The design of an IC has to be verified before it enters the fabrication process. Typical verification methods include formal verification and simulation-based verification.

Current IC verification practices depend heavily on simulation. For the verification of MPSoC, it usually requires hardware-software co-simulation. Softwarebased simulators have limited simulation speed, and the situation gets worse as the number of processor cores keeps increasing. This results in a situation where the verification process is becoming a dominant part of development in terms of both time and money.

By using Field Programable Gate Array (FPGA) for emulation of the SoC, we can achieve a speed that is very close to real system, and yet the platform has the flexibility similar to software simulation.

## **1.2** Problem Description

Hansson et al. [23] introduce CoMPSoC, a predictable and composable MPSoC template, which removes all interference between applications through resource reservations. In [19], the design of CompOSe, an RTOS that enables composable sharing of processor between applications is presented. These works give a good template for designing a composable and predictable MPSoC. However, the power management is not addressed in these works.

The goal in this thesis is to design an MPSoC platform that extends CoMP-SoC and CompOSe with power management capability, and define an FPGA-based emulation platform based on it. The follows have to be done:

- Define a hardware and software infrastructure for power management in a composable and predictable MPSoC platform, which is targeting streaming applications.

- Design and implement an FPGA-based platform for the emulation of composable and predictable power management on the MPSoC platform.

## **1.3** Requirements

What we want to achieve in this thesis is to design and implement a platform with the following properties:

- The MPSoC platform is a scalable platform targeting streaming applications.

- Multiple applications, which may have real-time requirements, run on the same processor in a composable way.

- The emulation platform has the hardware infrastructure to support the emulation of power management, and together with the software system, it is possible to perform composable and predictable power management.

- The speed of the emulation is sufficient to run actual applications.

- The observability of the emulation platform is sufficient for verification and experiments for the applications.

## **1.4** Contributions

In the work of this thesis, we achieve the follows:

- Hardware and software infrastructure for power management in a composable and predictable MPSoC platform based on the CoMPSoC template.

- Composable two-level scheduling on each processor with task budgeting interface and slack management.

- Composable and predictable power management for data-flow applications.

- Improve inter-processor communication by DMA controller on processing tile.

- Monitor for gathering trace data of the FPGA emulation.

# 1.5 Thesis Outline

The remainder of this thesis is organized as follows. In Chapter 2, the concepts of different aspects of the platform are introduced, as well as the the proposed architecture and methodology. Then we start to describe the details in the design of the platform, the hardware system design is in Chapter 3, followed by the software system design in Chapter 4. Next the experiments we have done are shown in Chapter 5. Related work is presented in Chapter 6 and the thesis ends with conclusions and future work in Chapter 7.

# <u>Chapter 2</u> Basic Concepts and Methodology

The design of a power efficient, composable and predictable MPSoC involves satisfaction of trade-offs in a lot of different aspects. This chapter gives the description of the important concepts. Section 2.1 gives the definition of composability and explains its necessity in modern MPSoC design. Another orthogonal aspect, the real-time requirement of a system and the predictability are discussed in Section 2.2. Thereafter, in Section 2.3, the power model of CMOS circuit and the basic concepts of power management are introduced. Next in Section 2.4, the interconnection of MPSoC is discussed and the network-on-chip is proposed as the solution. The programming model for streaming application in this platform, the data-flow graph model, is introduced in Section 2.5. Then we discuss the importance of FPGA emulation in modern MPSoC verification in Section 2.6. Finally, the architecture of a platform is proposed in Section 2.7, as well as the design flow.

# 2.1 Composability

An application is a set of communicating tasks, which provides a certain function for the system.

With the advance in technology, it is common to have a number of independent applications running on one system instead of physically independent systems, e.g. a smart-phone normally has the functionalities which used to be provided separately by a cell-phone, a digital camera and a PDA.

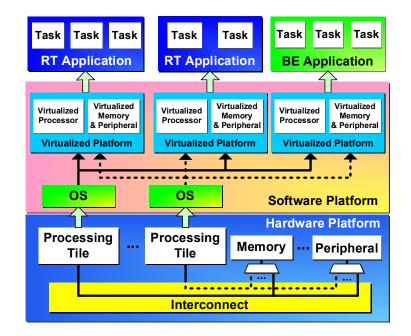

The integration of different applications in one system means that the level of resource sharing is increased. A system is composable if there is no interference between applications, which means the behavior of an application is not influenced by the presence or absence of other applications. In such systems, resources allocated to an application can be seen as a virtualized platform that only runs this application. Thus the application can be designed and verified separately. Fig. 2.1 gives an example of such a system, three applications run at the same platform, and each of them has a virtual platform that only runs the application. To achieve composability, both hardware and software resources have to be shared in a composable way. In this work we focus on the composability in the temporal domain, similar to [29].

Traditionally, composability is achieved by avoiding sharing resources, e.g. in the automotive industry, each function is offered by a separate processor and dedicated resources, such systems are common in both automotive and aerospace industry. Apparently, this solution is too expensive, and not energy efficient for most embedded systems, especially for the ones in consumer electronic business. For such systems, resource sharing is necessary, and it brings up the problem of composable scheduling for hardware and software resources.

Figure 2.1: Composable system

# 2.2 Real-time Applications and Predictability

An application is said to be real-time if the correctness of its operation depends not only upon its functional correctness, but also upon the time in which it is performed.

The real-time requirement of an application is usually defined by deadline. Applications can have different kinds of real-time requirements, namely, hard real-time (HRT), firm real-time (FRT) and soft real-time (SRT) [13].

The main difference of different real-time requirements is the effect of deadline misses. For hard real-time applications, the misses of deadline can lead to critical failure and therefore are unacceptable, e.g. the flight control system of an airplane. Firm real-time applications have similar real-time requirements as hard real-time applications, except that deadline misses make the result useless but do not cause critical failure, e.g. an audio playback device. Soft real-time on the other hand, allows deadline misses as long as they are not too often. Most multimedia applications have soft real-time requirements, which are often specified in probability terms.

In this work we call an application a real-time (RT) application if it has such requirement, otherwise we call it a best-effort (BE) application. The real-time requirement is defined in terms of throughput and latency requirements.

#### 2.2.1 Predictability

A system is predictable if its behavior is bounded in the temporal domain, i.e. it provides guaranteed *useful* lower bounds on performance [8]. It is essential for a system running real-time application to be predictable in order to meet the real-time requirements. To achieve predictability, both the hardware and the software should be able to provide predictable service to the applications.

## 2.3 Power Management

In this section, the power model of CMOS circuit is introduced, and the techniques for power management for such circuits are discussed.

#### 2.3.1 Power Consumption Model of CMOS digital circuit

In a CMOS digital circuit, the power dissipation can be calculated by (2.1), which consists of two parts, dynamic power dissipation and static power dissipation.

$$P = P_{dynamic} + P_{static} = \alpha C V_{DD}^2 f + I_{leak} V_{DD} + I_{SC} V_{DD}$$

(2.1)

#### **Dynamic Power Consumption**

The dynamic power consumption of CMOS circuit can be modeled by the charging and discharging of capacitance, and it is determined by (2.2),

$$P_{dynamic} = \alpha C V_{DD}^2 f \tag{2.2}$$

where  $\alpha$  is the activity rate of the circuit, i.e. the probability that a power consuming transition happens in the system in every clock cycle. C is the capacitance of the circuit,  $V_{DD}$  is the supply voltage and f is the frequency of the circuit.

#### Static Power Consumption

The static power consumption is determined by leakage current, the short circuit current and the supply voltage, as (2.3).

$$P_{static} = I_{leak} V_{DD} + I_{SC} V_{DD} \tag{2.3}$$

In traditional IC design, static power consumption is considered insignificant. However as IC process technology continues advancing towards smaller feature size, static power is becoming increasingly important. It is believed that static power may become the dominant factor in IC power consumption, especially for the deep sub-micron technologies below 65nm.

This work focuses on the power management of processors in active mode, in which the dynamic power consumption is the dominant factor.

For static power consumption, a lot of technologies in circuit design and IC process provide choices to reduce the static power, but they are beyond the scope of this work, so we do not go into the details of them.

#### 2.3.2 Power Management Techniques

According to (2.2), to reduce the dynamic power consumption, we should reduce the follows: C,  $\alpha$ , f and  $V_{DD}$ .

C and  $\alpha$  are mostly determined by the circuit design and the type of the application. Obviously, the best way to reduce the dynamic power consumption is to lower the supply voltage  $V_{DD}$  as it can result in quadratic power reduction. However, reducing the supply voltage increases the circuit delay, which can be estimated by (2.4), where  $\tau$  is the propagation delay of a CMOS transistor,  $V_T$  is the threshold voltage and  $V_G$  is the input gate voltage [14].

$$\tau \propto \frac{V_{DD}}{(V_G - V_T)^2} \tag{2.4}$$

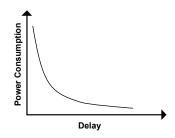

From (2.2) and (2.4), we can see there is a trade-off between power consumption and the delay. The curve in Fig. 2.2 is the typical power-delay curve, the exact shape and value depend on the process and circuit design. The delay of a circuit determines the maximum frequency it can run at. For a digital computing system such as a processor, this is a trade-off between power consumption and computational performance.

Figure 2.2: Power-delay curve

Another technology for saving dynamic power in digital system is clock gating, which disables the clock when the circuit is idle but the idle time is not long enough to shut down the circuit. It changes the f in (2.2) to 0 and saves the dynamic power.

For static power consumption, most of the techniques of reducing static power consumption are at circuit level. One of the techniques is adaptive body biasing (ABB) [44], which can reduce the leakage current. Another technology that is also popular is power gating, which completely shuts down part of the circuit and is able to save a lot of energy, but the overhead is high and it is useful only when the power-off time is long enough.

#### 2.3.3 Architectural Level Power Management

As discussed in Section 2.3.2, the most effective way to save dynamic power is to lower the supply voltage. The trade-off between power consumption and performance becomes the most important problem. Deciding the frequency and supply voltage statically at design time clearly limits the possibility of power saving for a processor based system because the workload of a processor varies according to the software it runs. For real-time applications, the static frequency-voltage point is determined by the worst case workload which usually results in significant overestimation in the actual execution. At this point, one can see that dynamic adjust of the frequency and supply voltage based on runtime information would be a good solution to this problem for microprocessor, i.e. the dynamic voltage and frequency scaling (DVFS) technique [26, 41].

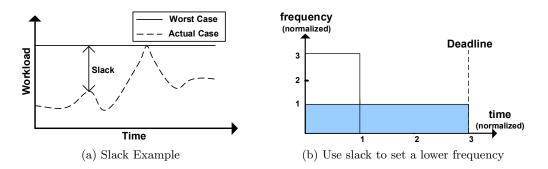

Figure 2.3: An examples of DVFS

The basic idea of DVFS is to dynamically adjust the processor's frequency so it runs at a lower supply voltage. For hard or firm real-time applications the problem here is to make sure the task still finishes in time. Assuming that the workload of a task is defined by the number of cycles it needed to finish, and there is is a deadline for this task, a number of cycles are allocated to this job according to the worst case workload and the deadline. In reality the actual workload often varies, the difference between the worst-case and actual-case workload is called slack, as Fig. 2.3a shows. If the processor is able to detect slack generated at runtime, it can use it to lower the frequency. The task produces the correct result at the right time as long as the task gets the required number of cycles before the deadline. Fig. 2.3b gives an example of DVFS using slack, the job is given 3 time units to finish its work but at the maximal frequency 3 it only needs 1 time unit, so it can lower the frequency to 1 which allows a lower supply voltage, and can fully utilize the time assigned to it. It has been proven that the just-in-time policy minimizes dynamic power in DVFS [26], i.e. the processor finishes the task just before the deadline. In DVFS for best-effort or soft real-time applications, similar technique can be used, and there are more possibilities since the timing constraints for these applications is not so strict as hard/firm real-time applications. Per-core DVFS is an attractive option for MPSoC power management, but it requires careful consideration of the trade-off between the overhead and the energy saving [28].

For static power consumption, power gating is a practical choice at architectural level. Some studies also suggest use ABB at the architectural level in order to reduce static power consumption [35]. At application level, most of these techniques do not show significant effect at runtime, and some of them can be simulated by the same infrastructure as the DVFS simulation, e.g. the power gating.

In this work we assume the techniques described above are used, and we focus on per-core dynamic power management at the architectural level using DVFS on an MPSoC.

## 2.4 Network on Chip

When multiple applications are integrated on the same system, resource sharing between applications is inevitable as different elements in the system need to communicate and resources need to be reused.

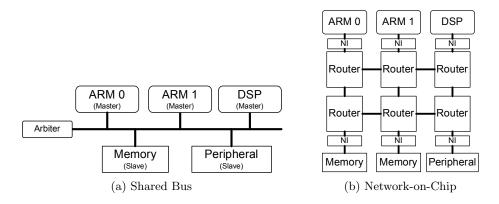

Figure 2.4: Examples of interconnection based on shared bus and network-on-chip

In traditional SoC architecture, shared buses such as AHB [4] and PLB [24] are widely used for solving this problem. In such an architecture, IPs that need to access resources are masters on the bus, and the resources are slaves on the bus, as shown in Fig. 2.4a. For shared buses, at any given moment, only one master has the control of the bus and is able to access one of the slaves. Concurrent requests are scheduled by the bus arbiter.

The shared bus is simple and cheap, but it is not scalable at either architectural or physical level. At the architectural level, a shared bus is not scalable as it is shared by all masters, which becomes a central bottleneck, causing severe performance losses when number of masters increases. At physical level, the structure of shared bus results in long global wires, which causes large delay and easily becomes the critical path in the system implementation.

Networks on chip (NoC) [18] are the solution for this problem. A typical NoC consists of a number of routers and links between them, see Fig. 2.4b. IPs are connected to the network through a network interface (NI). Data is routed through routers in the network. The data transfer in a NoC uses only local wires between routers, which provides scalability at physical level. Additionally, NoC makes it easier for IPs to run at their own clock domain compared to shared bus. It enables globally asynchronous locally synchronous (GALS) system design [32], which eases the design and provide more possibility for reducing power consumption. At the architectural level, NoC handles concurrent transactions and can be easily pipelined, therefore it does not become the central bottleneck. A NoC can provide high bandwidth for multiple IPs in the system by properly allocating resources.

NoCs achieve a better trade-off than traditional interconnection architectures [3, 11]. Crossbar and multi-layered or hierarchical bus structure have been used to improve the scalability of shared buses, but due to the nature of bus, these inter-

connection cannot completely solve the problem, and a NoC would be the most reasonable choice of interconnection for large scale MPSoC [3].

As stated earlier in this chapter, to build a composable and predictable system, composable and predictable services should be provided by each component in the system. For NoC this is not trivial as its structure is more complex. The Æthereal [20] architecture addresses this issue by supporting time-division multiple access (TDMA) of the network components across different connections, i.e. virtual wires. With the TDMA time slots allocated to match the application requirements, Quality of Service (QoS) guarantees is achieved, and the guaranteed service connections are composable [21, 22]. The Ætheral is chosen to be the interconnection of the platform in this work. More details are given later in Chapter 3.

## 2.5 Data-flow Graph Programming Model

Data-flow graphs are often used for modeling DSP applications and designing streaming multimedia applications [34]. The platform in this work supports different types of data-flow graph model, and we focus on the synchronous data-flow graph [33].

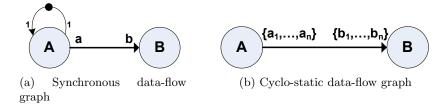

A synchronous data-flow (SDF) graph models tasks as nodes in the graph, called *actors*. The communication channels between tasks are represented by *directed* edges in the graph. The actor execution in SDF graph is called *firing*, incoming edges to an actor represent the input data needed by the actor in one firing, while outgoing edges represent the output data produced by the actor in one firing. Fig. 2.5a is an example of SDF graph with two actors and one communication channel.

It is clear that the edges in the SDF graph represent the data dependence between actors. The communications in the SDF graph is done in first-in-firstout (FIFO) channels, the amount of data transferred is measured in *tokens*. The number of tokens an actor produces or consumes in one firing is called *rate*, as *a* and *b* in Fig. 2.5a, for actor *A* and actor *B*, respectively.

In SDF graph, whether an actor is allowed to fire or not, depends only on the status of the FIFOs connected to it. If all incoming FIFOs have enough data and all outgoing FIFOs have enough free space, the actor is allowed to fire once, and the tokens are consumed according to the rate of the FIFOs. A self-edge in SDF graph is used to model *auto-concurrency*, i.e. then maximum number of simultaneous executions the actor, e.g. actor A in Fig. 2.5a cannot start a new execution until the last one finishes. The SDF graph is monotonic, i.e. starting early does not increase the completion time of the successors of an actor, which is important in scheduling and power management.

Figure 2.5: Data-flow graph

There are different kinds of data-flow graphs besides SDF graph. The Cyclostatic data-flow (CSDF) graph model [10] is a similar computation model as SDF graph. The major difference is that instead of having constant value in SDF, the rate of a FIFO in the graph varies according to a pre-defined sequence, see Fig. 2.5b. This modification makes it easier to model applications. CSDF graph can be converted to SDF graph [39], so the analysis techniques for SDF graph still apply. Kahn process network (KPN) proposed by Kahn in [27] is even more expressive, as it allows data-dependency on the rate and actor behavior, on the other hand it makes the analysis more difficult.

In this work we choose the data-flow graph as the programming model for streaming applications. Note that the platform in this work has built-in support for the scheduling and communication of the data-flow graph model, but it does not mean only applications using this model can run on the platform.

## 2.6 FPGA-based Hardware Emulation and Simulation

As mention in Chapter 1, IC verification practice usually depends heavily on simulation. Software-based simulation has limited simulation speed. The situation gets worse as the number of processor cores in the design keeps increasing. The requirement for hardware-software co-simulation puts even more pressure on the simulator. A typical trade-off in software simulator is to trade speed for abstraction-level. However, even for simple simulators, the speed is quite limited [6, 12].

To correctly capture the behavior of an MPSoC, the simulation has to be detailed, which leads to slow simulation. This results in a situation where the verification process is becoming a dominant part of development, in both time and money.

FPGA-based emulation and simulation platforms are able to perform fast simulation way at low cost. Comparing to a software simulator, an FPGA platform provides a much higher speed, usually more than 1/10 of the real system speed, sometimes even at full speed. Moreover, the FPGA platform is very close to the real IC environment, one can test the design without really producing the chip. With state-of-the-art FPGA technology, the observability of such platforms is comparable to software simulators. The Berkeley Emulation Engine (BEE) [15], and the Research Accelerator for Multiple Processors (RAMP) based on BEE [46] are interesting examples of such FPGA platforms.

The speed of FPGA emulation is a motivation of this work.

# 2.7 Proposed System Architecture and Design Flow

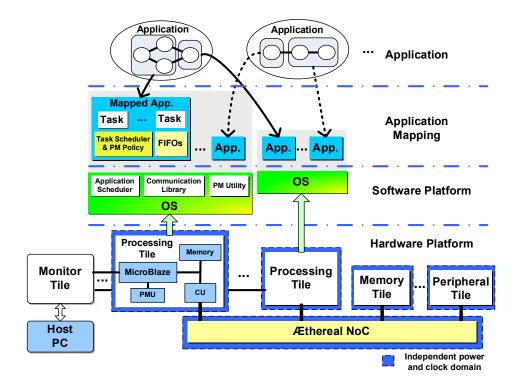

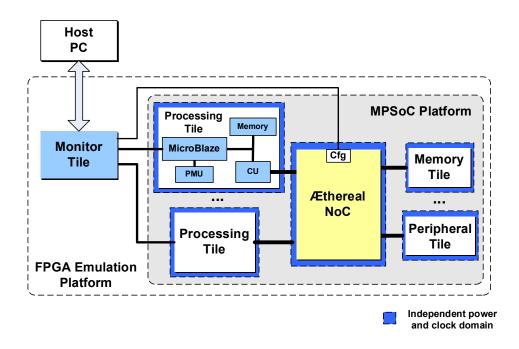

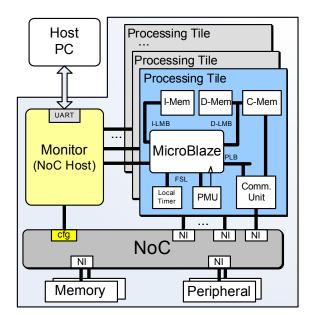

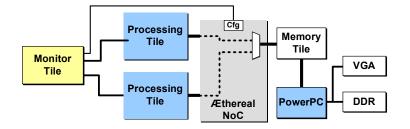

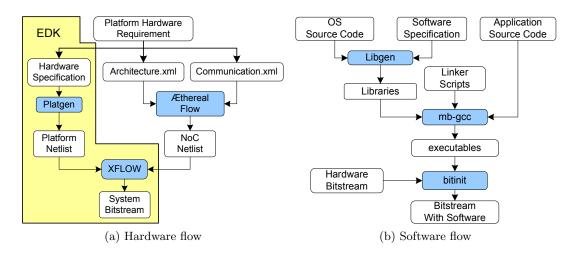

In this work, we extend the CoMPSoC template in [23], and propose a tiled MPSoC architecture. They system consists of a number of tiles, as Fig. 2.6 shows. There are different types of tiles in the system, e.g. processing tile and memory tile. These tiles are connected by the Æthereal NoC which allows predictable and composable communication between different tiles.

Figure 2.6: Proposed architecture

We focus on the hardware and software design of the processing tile, on which the software applications are running. A processing tile has a MicroBlaze processor with some local memories, a power management unit and a communication unit. On the processor, an operating system (OS), which is an extension of the work in [19], manages the processing tile resources and schedules application in a composable manner. We assume the streaming applications are mapped on the platform using data-flow graph model, which is directly supported by the OS. An application can be mapped to one or multiple processing tiles.

As the system is designed in the globally asynchronous locally synchronous (GALS) style, each processing tile performs the power management independently. This enables the per-tile power management. In this work we design and implement a power management unit (PMU) on each processing tile, which allows the processor to perform DVFS on the tile.

Apart from the processing tiles and resource tiles, a monitor tile is introduced to guarantee the observability of the system. The monitor tile collects data at runtime from each processing tile, and sends the data to the host PC for analysis.

For power management, we assume the PMU on each processing tile is able to generate different frequencies for the tile independently. Although it is difficult or even impossible to implement complete DVFS on an FPGA due to the missing of on-chip voltage scaling infrastructure, we do manage to create a power management unit that enables the processing tile to emulate the behavior of DVFS.

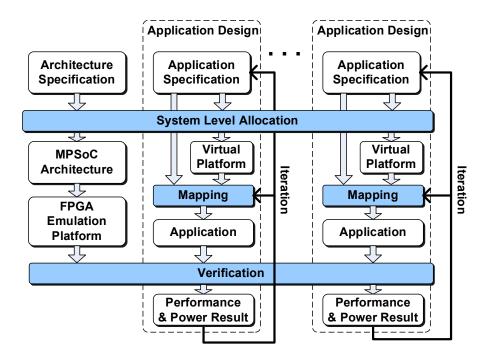

On such a platform, the design flow is simple and effective, see Fig. 2.7. As the components in the system provide composable services, it is possible to design the applications separately. Each application has its own task set, scheduling algorithm

and power management policy. The application is mapped on the virtual platform and verified independently, as the composability of the system guarantees that integration of applications does not affect the behavior of an individual application. However, in the current implementation, the composable design flow is still not complete yet, the mapping of different applications are still performed together.

Figure 2.7: Design Flow of the System

## 2.8 Summary

The basic concepts of the platform are introduced in this chapter. The composability and predictability are two important properties in MPSoC design for embedded system. The power consumption is becoming the major problem in modern IC design, which is also the most important motivation of this work. We discuss the power model and different power management techniques in this chapter. Then the necessity of developing FPGA-based emulation platform is presented. Finally, we show the proposed system architecture, as well as the design flow for such platform. In the remainder of this thesis, the design of this platform is explained in detail.

# Chapter 3 Hardware Platform Design

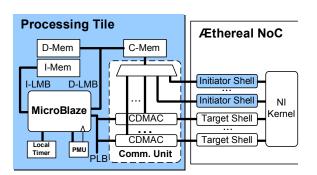

In this chapter, the design and implementation of the hardware modules in the platform are presented. The hardware platform architecture is shown in Fig. 3.1. The system consists of different kinds of tiles and a NoC that connects them.

Figure 3.1: Hardware platform architecture

Interconnection of the platform is a key element in a tiled architecture, so we first introduce the Æthereal NoC in Section 3.1. Next, the most important tile in the system, the processing tile is described in Section 3.2, including the power management and communication infrastructure. Then the hardware part of the monitor, which plays an important role in the emulation system, is discussed in Section 3.3, and the system configuration, which is implemented on the monitor tile, is introduced in Section 3.4. Finally, we put everything together to a complete hardware platform in Section 3.5.

# 3.1 NoC Based Interconnection

The Æthereal NoC is used as the interconnection between different tiles in the system. In this section, we briefly introduce the architecture of the Æthereal NoC, as well as the communication in Æthereal.

#### 3.1.1 Æthereal NoC

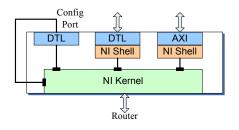

The Æthereal NoC consist of two kinds of components, the routers that transfer data among each other and network interface (NI) that are responsible for connecting the IPs to the router network [20, 22].

The NI consists of two parts, the NI *kernel* and the NI *shell*, as shown in Fig. 3.2. The NI shell is used as the bridge between the IP and the NI kernel, which allows the IP to use different protocols to access the NoC, e.g. DTL [40]. The core functions of NI, e.g. the packetization and depacketization, are provided by the NI kernel. In this work, the DTL shell is used to connecting different tiles.

Figure 3.2: Æthereal Network Interface

#### 3.1.2 Connection-based Communication

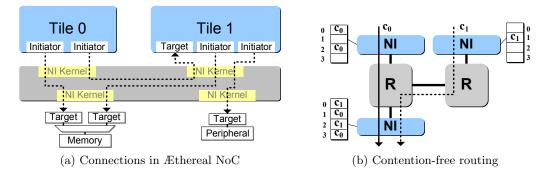

In the Æthereal NoC, communication between nodes of the network is based on connections, which are established by resource reservation as Fig. 3.3a illustrates.

The links between components are resources that are shared with different IPs. Contention on the links has to be resolved properly so the interconnection is composable and predictable. Æthereal solves this problem by time division multiplexing (TDM) scheduling of the links, which results in a contention-free routing [22].

Connections have requirements for the quality of service(QoS), which are characterized by the bandwidth and latency requirements. There is a slot table on each NI. Some slots in the slot table are reserved for a connection base on its QoS requirements. An IP is only allowed to send data to the NoC when the current time slot is reserved for the connection it is using. The slot tables in different NIs are synchronized, so it is possible to allocate the slots such that no contention on the links even happens. A simple example is given in Fig. 3.3b. Two connections  $c_0$ and  $c_1$  need to reach the NI at the bottom and each cycle a datum is transferred through a link.  $c_0$  is allowed to send data at time slot 0 and 2, and  $c_1$  is allowed data at time slot 1, so there is no contention at the left router and the destination NI.

Figure 3.3: Interconnection based on Æthereal NoC

In Æthereal, connections without QoS requirements, i.e. the best-effort connections use the time slots that are not allocated, or allocated but not used.

With this contention-free routing scheme, the interference between any two connections with guaranteed service is eliminated, so the interconnection is composable. And since the routing is based on TDM, the temporal behavior could be easily bounded, i.e. the NoC is also predictable.

In this work, different applications use the composable connections provided by Æthereal to access the remote resources.

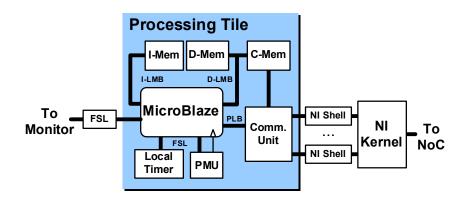

# 3.2 Processing Tile Design

The processing tile is the central element in the system. Apart from running task code, a processing tile also needs to provide the following things:

- Hardware infrastructure that allows software on the processor to perform power management.

- Hardware infrastructure that connects the tile to the NoC, allows software to access remote resource

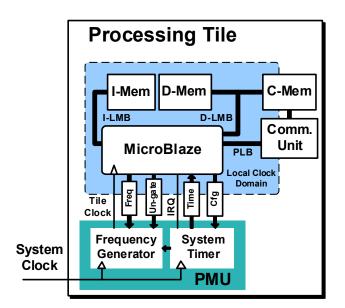

The architecture of a processing tile is in Fig. 3.4. There are three main components in a processing tile: a MicroBlaze processor core, a power management unit and a communication unit.

The PMU is connected to the processor via FIFO interface which provides clock domain crossing. The communication unit is connected to the local data bus, which could be accessed by the processor using load/store instructions.

To ease the analysis of predictability, we decide not to use the cache in MicroBlaze. Moreover, all communication with off-tile resources is performed by the communication unit. As the platform is targeting streaming applications, such design is efficient. Other configurations of the core are determined according to the application requirement.

Besides the main components, an instruction memory and data memory are also essential parts of the tile, they are connected to the processor via local memory bus (LMB), and the communication unit accesses the data memory using DTL

Figure 3.4: Architecture of the processing tile

protocol [40]. The local timer, a counter that counts the local clock, i.e. the output clock of the PMU is also provided, which can be useful for the software. In addition a processing tile may have some local peripherals, depending on the requirements of the applications, e.g. a computation accelerator.

The remainder of this section presents the design and integration of the components in detail.

#### 3.2.1 The MicroBlaze Processor Core

MicroBlaze is a 32-bit processor soft-core provided by Xilinx [49]. The instruction set architecture (ISA) of MicroBlaze is a typical reduced instruction set computer (RISC) ISA.

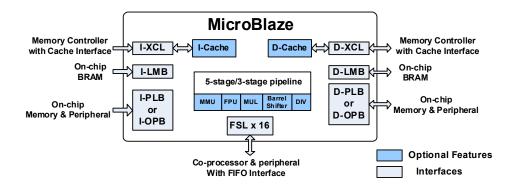

Figure 3.5: MicroBlaze core architecture

The MicroBlaze core is highly configurable, which enables users to keep only needed things in the system. The following parts of MicroBlaze core are configurable,

- Pipeline: 5 stages by default, 3 if optimized for area;

- Arithmetic unit: optional barrel shifter, hardware multiplier, divider, floating point unit (FPU), etc;

• Memory system: configurable memory management unit (MMU), cache and cache-links;

In addition, the MicroBlaze core has different interfaces for communicating with others IPs, including other processors [49]:

- Processor Local Bus (PLB) or On-chip Peripheral Bus (OPB): shared bus for on-chip IPs, available on both data and instruction side. It is part of the CoreConnect of IBM [24].

- Local Memory Bus (LMB): a single-master bus for accessing Block RAM(BRAM) on the FPGA. It is simple and provides zero-wait-state access to local memory. Available on both data and instruction side.

- Fast Simplex Link (FSL) [48]: a simple FIFO protocol. The interface is directly connected to the register file of MicroBlaze and a set of instructions is used to control it. Typically, it is used for co-processor and high speed peripheral.

- Xilinx Cache Link (XCL): a dedicated FIFO interface based on the protocol of FSL. It provides low latency access for the cache controller and reduces the traffic on the bus. Available on both data and instruction side.

In comparison to other synthesizable processor cores, e.g. the LEON and Open-RISC, MicroBlaze achieves a good trade-off between performance and resource utilization on FPGA [36]. By using different configurations, MicroBlaze can be used in a very wide range of cases, from doing simple finite state machine (FSM) duty, to running operating systems that require a full featured processor, e.g. Linux. In the area-optimized configuration, a MicroBlaze core utilizes only about 600 slices in a Virtex2-Pro FPGA [1].

The simplicity of this core makes it easy to analyze. Without complex features such as multiple issue, dynamic branch prediction, and out-of-order execution, it is easy to predict the behavior of a MicroBlaze core, provided the peripherals are also predictable, and this is very important for our system.

Although a simple single-issue in-order core seems to be quite limited in performance, the flexible interfaces of MicroBlaze allow users to extend the processor in different ways, e.g. connecting a computation engine via the FSL interface can achieve similar performance as the multimedia extension in the ISA of some cores. So it is even possible to use MicroBlaze in situations where high computational performance is required.

#### Configuration for the Processing Tile

In this work, the MicroBlaze can be configured according to the requirement of the application. Typically we have a MicroBlaze processor with 5-stage pipeline, a 32-bit integer multiplier and a barrel shifter. Such configuration consumes about 1200 slices on a Virtex2-Pro FPGA.

#### 3.2.2 Power Management Infrastructure

Power management unit consists of two sub-modules, the system timer and the frequency generator, as shown in Fig. 3.6.

Figure 3.6: Power Management Unit

#### System Timer

The main purpose of the system timer is to provide a time reference. Here we define *wall time* as the absolute time, which can be measured by number of cycles of a clock. The system timer provides the following services for the system:

- Provide wall time reference to the frequency generator. The system timer is readonly in this case. The purpose is to enable the frequency to work in a predictable way.

- Provides wall time reference to the processor. In this case, the system is a programable timer, which is writable. It provides wall time reference to the processor in two ways: by generating an interrupt request signal (IRQ), and by allowing the processor to read the timer value.

The system timer is implemented by a simple programable counter which counts the global clock signal. In this work it is usually set to a down counter. When the timer value reaches zero, an interrupt request signal is generated if the interrupt of the timer is enabled.

Since the processor may change the operating frequency, it is very important that the system timer is always running at the maximum frequency, which enables it to give the wall time reference to the processor and the frequency generator.

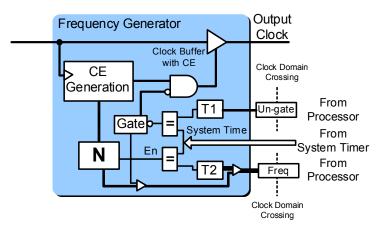

#### **Frequency Generator**

Frequency generator is designed for two purposes:

- For setting output frequency to  $\frac{n}{d}f_{in}$  at a given wall time, where n and d are programable parameters. This functionality allows the processing tile to set its own operating point.

- For gating the output clock, i.e. set output frequency to 0, and un-gate it at a required moment. This functionality could be used to stop the processor in order to achieve constant execution time for certain programs, and to emulate the idle state, e.g. sleep mode or power gating. As the *halt* instruction is not available in MicroBlaze's ISA, this capability is very useful.

On existing FPGAs, there is no infrastructure for implementing complete DVFS. In particular there is no on-chip regulator available to change the supply voltage at runtime. So the PMU should include a module for emulating DVFS. For emulation, the absence of on-chip voltage regulator is not a hard limit, as the voltage level itself does not have direct impact on the behavior on the application.

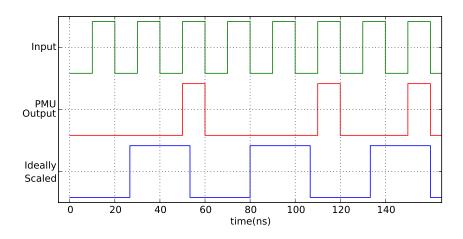

For frequency scaling, a few options are available. The partial reconfiguration of the digital clock manager (DCM) on the Xilinx FPGA implements a real frequency scaling. However it introduce a lot of extra overhead such as the relocking of the phase locked loop (PLL), which limits flexibility of the frequency generator, so it is not suitable for our system. Alternatively, the frequency can be generated by fine-grained clock gating, i.e. deciding whether to enable the clock for each cycle. Although no actual frequency scaling is implemented, the processor, as well as the software running on it, get the same number of clock cycles as the ideally scaled clock, but the exact time of the clock pulse is different. The algorithm of generating the frequency is given in Algorithm 1. With this algorithm, the clock pulse is distributed in the most uniform way, i.e. closest to the ideally scaled clock. And it does not cost extra hardware compared to implementations that give all the clock pulses in the beginning of the end of a period.

| Algorithm 1: Clock-Generation                                            |  |  |

|--------------------------------------------------------------------------|--|--|

| Input: $ClkIn, N, D$ ,                                                   |  |  |

| <b>Output</b> : ClkOut, where $f_{ClkOut} = \frac{N}{D} \cdot f_{ClkIn}$ |  |  |

| 1 $acc \leftarrow 0;$                                                    |  |  |

| 2 for each cycle of ClkIn do                                             |  |  |

| $acc \leftarrow acc + N;$                                                |  |  |

| 4 if $acc \ge D$ then                                                    |  |  |

| 5 $acc \leftarrow acc - D;$                                              |  |  |

| $6 		ClkOut \longleftarrow ClkIn;$                                       |  |  |

| 7 else                                                                   |  |  |

| $8 \qquad ClkOut \longleftarrow 0;$                                      |  |  |

| 9 end                                                                    |  |  |

| 10 end                                                                   |  |  |

Figure 3.7: Example of  $\frac{3}{8}$  Output Frequency

In the implementation, to ease the calculation of the software and allow the processor to set the frequency using only one command word, d is fixed to 16, so the output frequency is  $\frac{n}{16}f_{in}$ , where n is a programmable parameter.

Figure 3.8: Architecture of the frequency generator

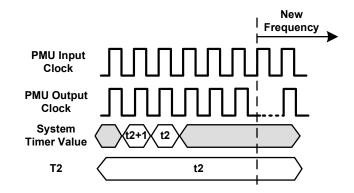

Fig. 3.8 gives the architecture of the frequency generator. The clock enable (CE) generation module uses Algorithm 1 to generate the CE signal. The processor can program the frequency parameter N through a FIFO. Note that the processor may run at a different frequency, therefore the latency of the FIFO is not constant. To eliminate the uncertainty caused by the variable frequency and clock domain crossing, a programmable time value register T2 is introduced. The parameter N does not affect the CE generation until the system timer reaches the value set in T2, as shown in Fig. 3.9. The algorithm in Algorithm 1 works in a periodic way, of which the period is 16. In order to keep the frequency scaling factor valid for the period before the frequency switch, the frequency switch is only allowed when the system timer value is multiple of 16, i.e. the value of T2 is aligned with 16.

Figure 3.9: Frequency switch in the frequency generator

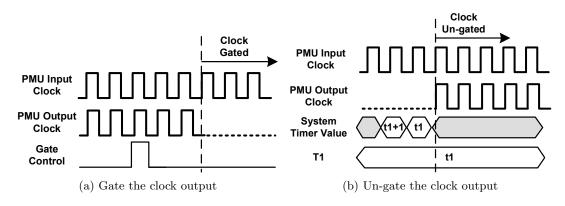

When a gate command is sent to the frequency generator, it sets the *Gate* register which disables the output clock. When the system time reaches the value of register T1, the *gate* register will be reset and the output clock will continue. The timing of gate and un-gate of the clock is shown in Fig. 3.10.

Figure 3.10: Gate and un-gate of the clock

#### **PMU Interface to Processor**

There are three input ports and one output port in the PMU interface. In principle they can be mapped to any interface that is accessible for the processor, including a bus. But in order to build a predictable system, it is important to make sure that these ports are mapped to a predictable interface. In our design, we map these ports to the FSL of MicroBlaze, which is fast and more importantly, completely predictable.

As shown in Fig. 3.6, a FIFO from the processor to the system timer is used for configuring the timer, which is also used for clock domain crossing. The timer value is sent to the processor via a synchronizer, which is implemented by two flip-flops.

The processor can perform the following operations on the system timer:

1. Start and stop the timer.

- 2. Read and/or set the timer value.

- 3. Enable or disable the timer interrupt.

Note that due to the clock domain crossing, reading of the system timer value is not cycle accurate, and cannot be used directly used as the cycle-level wall time reference. The processor has to compensate for the latency according to the frequency it is running at, or use the time reference in a coarse granularity.

As shown in Fig. 3.6, two FIFOs from the processor to the frequency generator are used for configuring the frequency generator. The processor can perform the following operations on the system timer:

- 1. Set new frequency and its effective time. Done by sending a 32-bit word via the *Freq* FIFO, the lower 4 bits are the frequency parameter N and the rest are the effective time, which is aligned to 16.

- 2. Gate the clock output. Done by sending a command word via the *Freq* FIFO with the control bit [48] set to 1. In this case the content of the command is ignored.

- 3. Set un-gate time. Done by sending the effective time via the Un-gate FIFO.

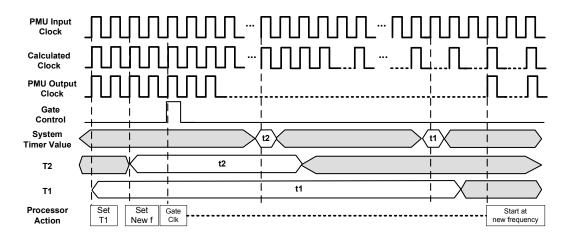

In a system with DVFS, the transition between different frequencies may introduce a state in which the clock is unstable and cannot be used to drive the circuit. Moreover, the frequency switch latency at different frequencies are different, due to the variable latency of the frequency generation and the asynchronous communication. Here we introduce a method to perform predictable frequency switch using the PMU described before. The typical timing of using all three operations to switch frequency is shown in Fig. 3.11. The processor sets the new frequency and un-gate time, then gate the clock. The frequency switching happens when the processor is not running. When the processor comes back, it is already running at the new frequency. The switching in Fig. 3.11 can be used to get the WCET of the frequency switching by setting T1 to the proper value.

Figure 3.11: Frequency switching with gate and un-gate

# 3.2.3 Tile Communication Infrastructure

As described in section 3.1.1, the NoC provides connections between nodes in the network. A connection allows the tile processor to access remote resources. Here we assume the connection is between a tile and a memory or peripheral with memory-mapped I/O (MMIO), and both ends of the connection use DTL-MMIO protocol [40]. In such a connection, the processor is the initiator and the remote device is the target. Note that the remote resource for one processor may be the local resource of another processor.

## Trade-offs in Designing the Interface to the NoC

To connect the MicroBlaze processor to the NoC, the following options are available:

- Map the remote memory into the processor's memory space, so the processor accesses data on remote location by load/store instructions.

- Use a communication unit that supports Direct Memory Access (DMA), which requires explicit control over the transactions over the NoC.

The memory-mapped solution is simple and straight forward. It provides transparent access to remote resources to the processor. The major drawback is that the processor is exposed to the large latency cause by the NoC and/or remote resource, e.g. the access of off-chip DRAM can easily cost hundreds of cycles. For simple processor cores like MicroBlaze, this causes loss in not only performance, but also predictability. Large latency of memory access results in long stalling of the processor pipeline, and consequently significant increases of worst-case interrupt response time, which makes it difficult to derive a useful bond for the system behavior and the predictability of the processor is jeopardized.

The use of DMA controller is a solution to this problem as the use of a DMA controller only requires local accesses. The DMA controller supports block transaction and runs in parallel with the processor, hence there is a potential for getting a better performance than the memory-mapped communication. The downside is that the communication is no longer transparent to the software. For applications that do not decouple communication from computation, it may be very difficult to adapt the remote access in the software code to the communication unit. A well known example of system with similar solution is the CELL processor, on the synergistic processing elements (SPE) in CELL, all remote access through the element interconnect bus (EIB) is performed by a DMA controller [2].

In this work, we choose the second option for the processing tile, based on the following consideration,

- The MicroBlaze does not support block transaction on the data bus, which limits the performance. A communication unit with DMA support gives better performance than a direct connection.

- The data-flow programming model used in this work provides a clean separation between computation and communication, therefore it is easy to use such module in the application. More details can be found in Chapter 4.

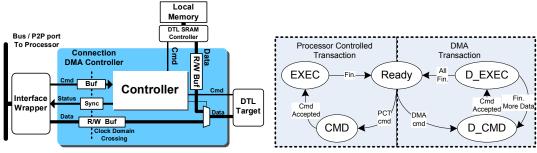

(a) Structure of the Connection DMA Controller (b) Finite State Machine of the DMA Controller

Figure 3.12: Connection DMA controller

A communication unit is designed for the processing tile. In this communication unit, each outgoing NoC connection on the tile has a DMA controller, called connection DMA controller (CDMAC). In the remainder of this section, we discuss the design of the CDMAC, and the management of multiple connection on the processing tile.

#### **Connection DMA Controller**

In our design, the connection DMA controller supports the following two kinds of transactions:

- 1. Processor controlled transaction: in this type of transaction, data is transfer between the processor and the remote location. The processor writes to and reads from the data buffer inside the controller, the block size in this case is limited by the DTL protocol. This kind of operation is useful in transferring small data unit as it provides lower latency than the DMA transaction.

- 2. DMA transaction: in this type of transaction, the controller moves data between the on-tile memory and remote location, while the processor is doing other things. It supports larger block size than processor controlled transaction. The DMA transaction is efficient in transferring large amount of data, which is chopped into multiple DTL transactions.

The structure of the CDMAC is in Fig. 3.12a. The control logic is implemented as a finite state machine (FSM), as shown in Fig. 3.12b. Note that there are two parts in the FSM, the first part that controls the processor controlled transaction, and the other part that controls the DMA transaction. Either part is optional, for example if the processor controlled transaction is not necessary, it is possible to reduce the FSM, as well as the corresponding hardware in the DMA controller.

Listing 3.1 is the pseudo code of the use of the CDMAC. Note that the programming of CDMAC in a DMA transaction should be atomic, otherwise the behavior of the CDMAC might be incorrect.

Listing 3.1: Transaction on CDMAC (Blocking)

$<sup>1 / *</sup> conn_id$  is the id of the connection being used \* /

<sup>2</sup>

<sup>3</sup> while (ConnectionIsBusy (conn\_id)=true)

```

NOP

4

5

6 if transaction is DMA transaction

7

SetSourceAddress(source_addr, conn_id)

8

SetDestinationAddress (destination_addr, conn_id)

9

if transaction is read

SendCommand(dma_read, conn_id)

10

11

else

12

SendCommand(dma_write, conn_id)

13 else

if transaction is read

14

15

SetSourceAddress (source_addr, conn_id)

16

SendCommand(pct_read, conn_id)

17

ReadBuffer()

else

18

19

SetDestinationAddress (destination_addr, conn_id)

20

SendCommand(pct_write, conn_id)

21

WriteBuffer (output_data)

```

#### **Multi-connection Management**

For multiple connections, if there is any incoming connection to the local data memory, a scheduler is needed in order to share the memory port between incoming connections and outgoing connections.

If there are multiple outgoing connections, two options are available:

- Extend the DMA controller to support multiple outgoing connections.

- Each outgoing connection that needs to be composable uses a DMA controller of its own.

The first option probably results in a complex DMA controller. As we want the controller to provide composable and predictable service for multiple applications on the processor, the scheduler inside the controller has to be composable and predictable. Moreover, if both incoming and outgoing connections exist, we need a scheduler for the memory port anyway. In Æthereal, such a scheduler is implemented in the initiator bus [22].

Since the scheduler at the memory port cannot be avoided, the second option is a more reasonable choice. In this solution, we keep the DMA controller simple and small. For outgoing connections, each of them has a connection DMA controller.

The resulting architecture is shown in Fig. 3.13. Here a separate communication memory (C-Mem) is used for two reasons: first, the memory map in inter-processor communication is easier if there is any incoming connection. Second, if single port memory is preferred for the local memory, such a separate memory for communication reduces the performance loss of the processor caused by sharing memory port with the NoC connections. If there is no incoming connection, it is possible for the communication unit to use the other port of the processor data memory (D-Mem).

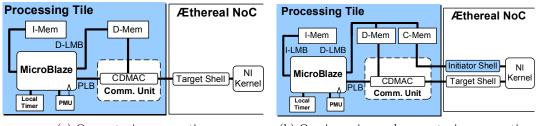

Figure 3.13: Tile Communication Infrastructure for Multi-connection

In the current implementation, because the composable and predictable memory controller is not available yet, each composable connection has a separate communication memory. Fig. 3.14 shows two examples. The tile in Fig. 3.14a has only one outgoing connection, the CDMAC of this connection is connect to D-Mem of the tile. In Fig. 3.14b, the tile has one incoming connection and one outgoing connection. The outgoing connection is connected to D-Mem while the incoming connection is connected to a C-Mem.

(a) One outgoing connection

(b) One incoming and one outgoing connection

Figure 3.14: Communication unit examples

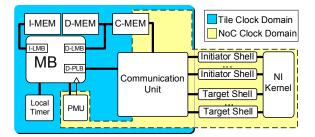

## 3.2.4 Clock Domains on the Processing Tile

There are multiple clock domains on a processing tile. We assume that the NoC is running at a constant frequency  $f_{noc}$ .

The processor and local buses use the clock signal generated by PMU, of which the frequency is variable, denoted as  $f_{tile}$ . The input clock of the PMU is assumed to have a constant frequency  $f_{sys}$ . In the design of this thesis, we assume that  $f_{sys} = f_{noc} = f_{max}$  where  $f_{max}$  is the maximum frequency in the system, and the clock of the NoC is synchronous with the input clock of the PMU. Note that this is not a restriction but a design choice, it's possible to have a different clock for the NoC.

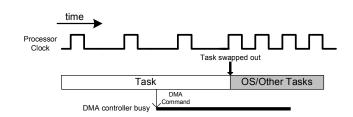

The operating frequency of the connection DMA controller can be either  $f_{noc}$  or  $f_{tile}$ . In this work, we chose to run the DMA controller at  $f_{noc}$ . The motivation is to

Figure 3.15: Overlap of DMA transaction and task execution

avoid the unintended interference between tasks. When a DMA controller receives a command, it executes it and waits until it is completed, even if the task that gives the command is swapped out, as shown in Fig. 3.15. The new task (or OS) swapped in is probably running at a different frequency, which means  $f_{tile}$  is changed. If the DMA controller is running at  $f_{tile}$ , interference between tasks is introduced, which is unintended and hard to detect and cope with at design time. If the two tasks belong to different applications, the interference is between applications, and consequently the composability of the system is compromised.

The standard processing tile architecture is shown in Fig. 3.16. There are two clock domains on the tile, PMU and communication module running at  $f_{noc}$  and the other parts of the tile running at  $f_{tile}$ . The clock domain boundary runs through FIFOs between PMU and the processor, and the FIFOs inside the CDMAC in the communication unit, see Fig 3.6 and Fig. 3.12a. Another clock domain crossing in the processing tile is within the C-Mem and/or D-Mem, which is true dual port memory that allow separate clock on each port.

Figure 3.16: Tile Architecture and Clock Domains

# 3.3 Monitor Tile Design

The main purpose of the monitor tile is to gather trace data from the processing tiles in the system. It monitors the processing tiles by recording the events of interest. There are two ways to do that, to actively detect the events of interest happen on the processing tiles and record them, or to let the processing tiles send the messages to the monitor when events of interest happen, i.e. the monitor collects information passively.

In this work, most events of interest are high level events, e.g. task switching in the OS. It is difficult for the monitor to detect such events for each processing tile, so we decide to use the passive method and let the processing tiles send messages to the monitor when events of interest happen. The FSL of the monitor is used for this propose. The trace data from the processing tiles is stored in memory and sent to the host PC via the serial port when enough data is collected. The architecture of the monitor tile is shown in Fig. 3.17.

The processing tiles use non-blocking FSL instructions [49] to send messages to the monitor tile, hence if the monitor tile fails to empty the FIFOs in time, the processing tiles do not stall. Here the FIFO size is set to 64 words, which is enough for the message from one tile in a time slice, which usually has a length of over 15000 cycles. The load of the monitor is light, thus no data loss is expected during the execution.

Figure 3.17: Monitor Tile Architecture

# 3.4 System Configuration