# **MASTER** Modeling and implementation of an interface adapter between wide format printers and finishers Tirupalathurai Kannan, B. Award date: 2013 Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

#### Where innovation starts

Department of Mathematics and Computer Science

Software Engineering and Technology Group

### Modeling and Implementation of an Interface Adapter between Wide Format Printers and Finishers

Master Thesis

Author: B. Tirupalathurai Kannan

Supervisors:

Dr. Lou Somers (TU/e)

Ing. Stephan Derks (Océ)

Venlo, August 2013

#### **Abstract**

Interface implementation between different software components usually takes a considerable amount of time and effort. Océ faces a similar problem in the area of wide format printers. The wide format printers produced by Océ have to be interfaced with finishers from Océ and other companies. Finishers are devices which are connected to printers and perform ancillary activities like folding and stacking of papers with sheets delivered from a printer. The project aim was to develop a generic adapter which takes care of the electrical and functional interface incompatibilities between Océ wide format printers and finishers. The software adapter was designed using a model based approach which reduces the functional interface implementation time. The main contributions of the project are architecture and design for the adapter, design of a generic protocol between Océ wide format printers and the adapter, selection of a modeling approach for the adapter design and a prototype implementation of the adapter (deployed on an interface board) to test the feasibility of the design.

Keywords: Océ wide format printers, finishers, adapter, modeling approach

| Modeling and Implementation of an Interface Adapter between Wide Format Printers and Finishers |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

| Dedicated to my belove | ed parents who h | ave alwavs be | en a source of | inspiration and | motivation in |

|------------------------|------------------|---------------|----------------|-----------------|---------------|

|                        | <i>T</i>         |               |                | T               |               |

| every step of my life. |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

|                        |                  |               |                |                 |               |

| Modeling and Implementation of an Interface Adapter between Wide Format Printers and Finishers |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

### **Preface**

This thesis is a result of the graduation project as part of the curriculum for the degree MSc in Embedded Systems at TU/e. The project was carried out within the Software Engineering and Technology group of the Mathematics and Computer Science department of the TU/e in collaboration with the System and Development department in the Océ-Technologies. The project duration was from February 2013 to August 2013 at Océ-Technologies, Venlo. The project had a preparation phase from December 2012 to February 2013 as part of the MSc curriculum.

Barath Tirupalathurai Kannan August, 2013

| Modeling and Implement | ation of an Interfa | ce Adapter betwee | en Wide Format I | Printers and Finish | ers |

|------------------------|---------------------|-------------------|------------------|---------------------|-----|

|                        |                     |                   |                  |                     |     |

### Acknowledgments

I wish to thank the TU/e and the management of Océ-Technologies for providing me with the scholarship to finance my studies in the Netherlands. I would like to thank the management of Océ-Technologies for providing me opportunity to participate in a summer internship, master thesis project and other activities related to the company. My special thanks to Lou Somers who has been guiding me in my summer internship and my master thesis. His expertise, practical approach and risk analysis helped me to foresee most of the risks at an earlier stage of the project. My sincere thanks to Stephan Derks who has guided me in my master thesis. He gave me good amount of freedom to work in the project and was willing to accept new ideas from me. I will miss my weekly meetings with my supervisors.

The working environment in Océ has been very amicable and there are several colleagues who helped me in my project. I thank Erik Schoenmakers for helping me with the generic protocol design and the ASD. I thank Louis Van Gool for helping me with the ASD and interface language. I would like to thank Henri Hunnikens, Ralph Woltering, Gert Voets, Sidney Laracker, Bart van der Meulen, Harald Schwindt, Richard van Enckevort, Robert Jacobs, Rob Janssen, Kim Leeks and Hans Derks who facilitated my successful completion of this work in different capacities which space will not permit me to elaborate then.

I would like to give warm regards to Reinder J. Bril and Tom Verhoeff who gave valuable feedback during my kickoff and midterm presentations which helped me to improve the project. I extend my regards to Arjan Mooij from the Embedded Systems Institute who gave initial insight into several modeling approaches using Petri nets and the ASD.

Last, but not least, I would like to thank my parents and friends. Without your support and prayers it would not have been possible for me to succeed in life.

Barath Tirupalathurai Kannan August, 2013

| Modeling and Implementation of an Interface Adapter between Wide Format Printers and Finishers |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

### **Table of Contents**

| LIST OF FIGURES                                      | XII |

|------------------------------------------------------|-----|

| LIST OF TABLES                                       | XIV |

| LIST OF ACRONYMS                                     | xv  |

| 1 INTRODUCTION                                       | 1   |

| 1.1 BACKGROUND                                       | 1   |

| 1.1.1 Wide Format Printers                           | 2   |

| 1.1.2 Wide Format Finishers                          | 3   |

| 1.1.3 Current Setup                                  | 3   |

| 1.2 PROBLEM DESCRIPTION                              | 4   |

| 1.3 GOALS                                            | 5   |

| 1.4 Approach Taken                                   | 5   |

| 1.4.1 Proposed Solution                              | 5   |

| 1.4.2 Research Challenges                            | 7   |

| 1.4.3 Project Life Cycle                             | 10  |

| 1.5 REPORT ORGANIZATION                              | 11  |

| 2 DOMAIN ANALYSIS                                    | 12  |

| 2.1 Finisher Capabilities                            | 12  |

| 2.1.1 Present Capabilities                           | 12  |

| 2.1.2 Future Capabilities                            | 13  |

| 2.2 FINISHER PROTOCOL ANALYSIS                       | 14  |

| 2.2.1 Message Formats                                | 14  |

| 2.2.2 Protocol Details                               | 15  |

| 2.2.3 Message Categories                             | 18  |

| 2.2.4 Message Conversion Complexities                | 19  |

| 2.3 Cut-sheet Printer Interface Solutions            | 20  |

| 2.4 CONCLUSION                                       | 22  |

| 3 ARCHITECTURE                                       | 23  |

| 3.1 REQUIREMENT ANALYSIS                             | 23  |

| 3.2 CONCEPTUAL VIEW                                  | 25  |

| 3.3 LOGICAL VIEW                                     | 26  |

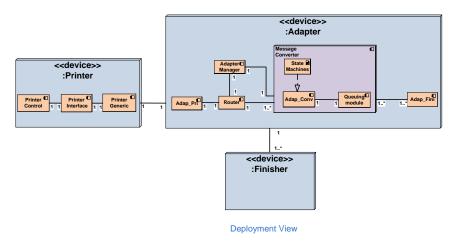

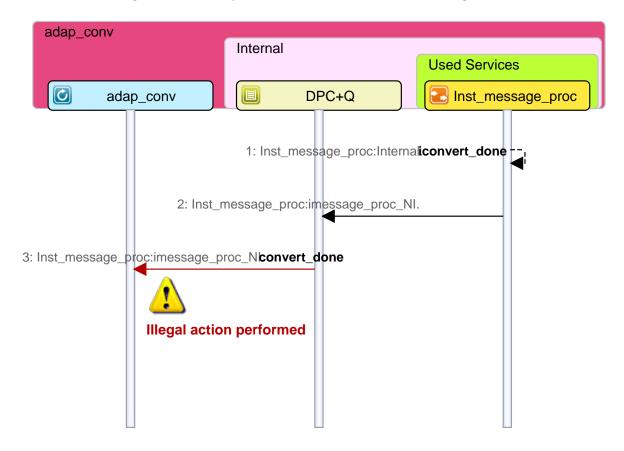

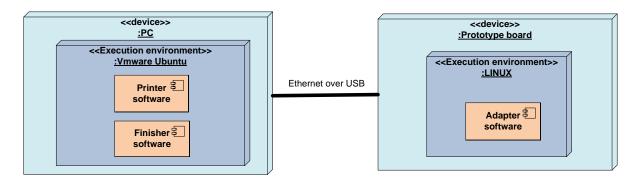

| 3.4 DEPLOYMENT VIEW                                  | 27  |

| 3.5 COMPONENT VIEW                                   | 29  |

| 3.6 BOUNDARIES OF THE ARCHITECTURE                   | 31  |

| 3.7 CONCLUSION                                       | 32  |

| 4 GENERIC PROTOCOL AND MODELING APPROACH SELECTION   | 33  |

| 4.1 TYPICAL ADAPTER SCENARIO                         | 33  |

| 4.2 GENERIC PROTOCOL                                 | 35  |

| 4.2.1 Domain Concepts                                | 35  |

| 4.2.2 Analysis of Complexities in Message Conversion | 37  |

| 4.3 TOOLS INVESTIGATED                               | 38  |

|    | 4.3.1   | Petri nets                                                                     | 38 |

|----|---------|--------------------------------------------------------------------------------|----|

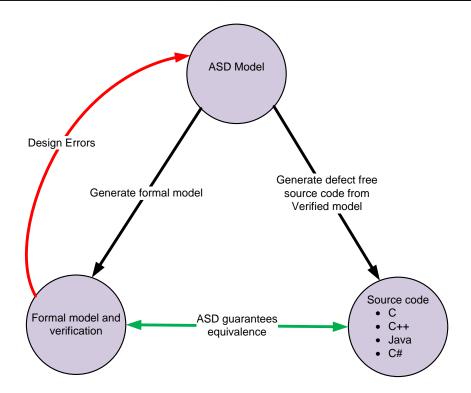

|    | 4.3.2   | ASD                                                                            | 41 |

|    | 4.3.3   | Event-B                                                                        | 43 |

|    | 4.3.4   | Rational Rose – Real Time                                                      | 43 |

|    | 4.3.5   | Interface Language                                                             | 44 |

|    | 4.3.6   | SDL                                                                            | 45 |

|    | 4.4     | Selection Criteria                                                             | 45 |

|    | 4.5     | Modeling Selection Chart                                                       | 47 |

|    | 4.6     | CONCLUSION AND RECOMMENDATIONS                                                 | 49 |

| 5  | ASD     |                                                                                | 50 |

|    | 5.1     | Modeling using ASD                                                             | 50 |

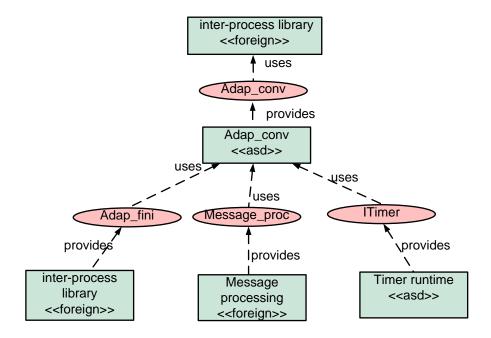

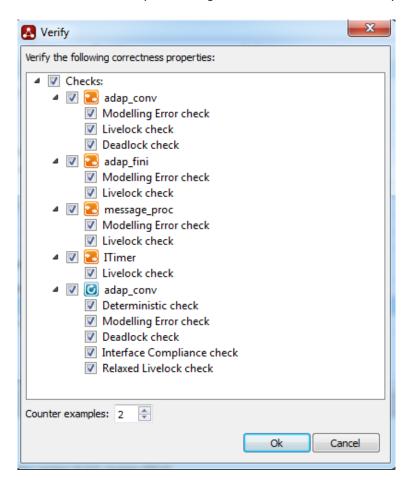

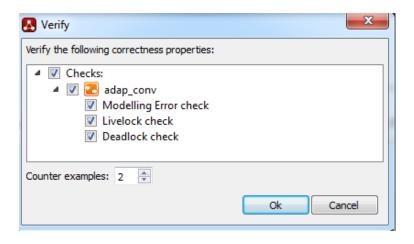

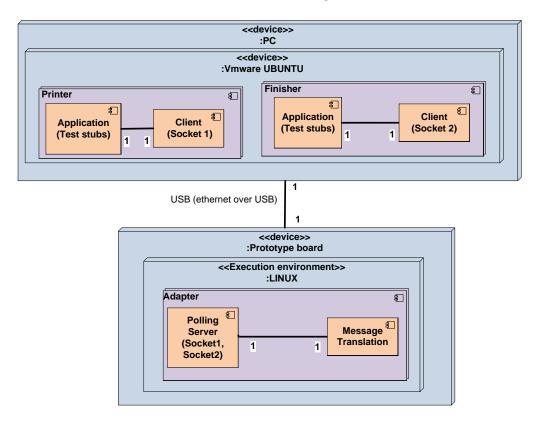

|    | 5.2     | Design Verification using ASD                                                  | 55 |

|    | 5.3     | CODE GENERATION AND INTEGRATION                                                | 57 |

|    | 5.4     | Conclusion                                                                     | 59 |

| 6  | PROT    | DTYPING                                                                        | 60 |

|    | 6.1     | TEST SETUP                                                                     | 60 |

|    | 6.2     | TESTING THE PROTOTYPE BOARD                                                    | 61 |

|    | 6.3     | Interfacing with Inter-process Communication Library                           | 63 |

|    | 6.4     | IMPLEMENTATION OF TYPICAL SCENARIOS                                            | 65 |

|    | 6.5     | IMPLEMENTATION OF LINK HANDLING                                                | 73 |

|    | 6.6     | Conclusion                                                                     | 74 |

| 7  | CONC    | LUSIONS                                                                        | 75 |

|    | 7.1     | MAIN CONTRIBUTIONS                                                             | 75 |

|    | 7.2     | LIMITATIONS AND FUTURE WORK                                                    | 76 |

|    | 7.3     | FINAL OUTCOME                                                                  | 77 |

| RI | EFERENC | ES                                                                             | 78 |

| A  | PPENDIX | A: "MESSAGE LIST FOR VARIOUS FINISHERS"                                        | 80 |

| A  | PPENDIX | B: "OCÉ PROTOTYPE BOARD SPECIFICATION"                                         | 81 |

| A  | PPENDIX | C: "GENERIC PROTOCOL FOR ADAPTER INTERFACE"                                    | 82 |

|    |         | D: "ASD SPECIFICATION FOR THE PROTOTYPES: TYPICAL ADAPTER SCENARIO AND LINK    |    |

| H  | ANDLING | n e e e e e e e e e e e e e e e e e e e                                        | 83 |

|    |         | E: "INTER-PROCESS COMMUNICATION SPECIFICATION FOR THE PROTOTYPE OF TYPICAL ADA |    |

| SC | CENARIO | S"                                                                             | 84 |

## **List of Figures**

| FIGURE 1.1.1. FRINTER CONNECTED TO A FINISHER                                           | 2  |

|-----------------------------------------------------------------------------------------|----|

| FIGURE 1.1.2: OCÉ PLOT WAVE 350 PRINTER                                                 | 2  |

| FIGURE 1.1.3: OCÉ 4311-FULLFOLD FINISHER                                                | 3  |

| FIGURE 1.1.4: SIMPLIFIED CURRENT SETUP OF THE PRINTER-FINISHER INTERFACING              | 3  |

| FIGURE 1.4.1: PROPOSED SOLUTION FOR THE PRINTER-FINISHER INTERFACING                    | 6  |

| FIGURE 1.4.2: PROJECT LIFE CYCLE                                                        | 10 |

| FIGURE 2.1.1: SOFTWARE DOWNLOAD FEATURE                                                 | 13 |

| FIGURE 2.1.2: MULTIPLE FINISHERS FEATURE                                                | 14 |

| FIGURE 2.2.1: LOW LEVEL MESSAGE FORMAT TYPE 1                                           | 15 |

| FIGURE 2.2.2: LOW LEVEL MESSAGE FORMAT TYPE 2                                           | 15 |

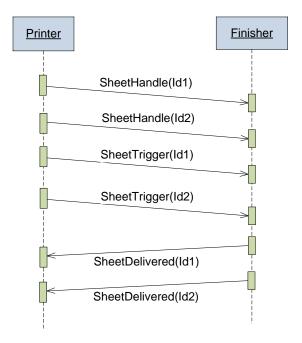

| FIGURE 2.2.3: PARALLEL PAPER TASK HANDLING                                              | 16 |

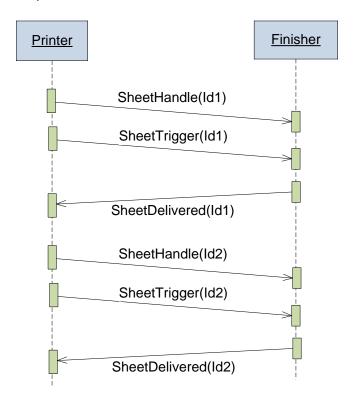

| FIGURE 2.2.4: SEQUENTIAL PAPER TASK HANDLING                                            | 17 |

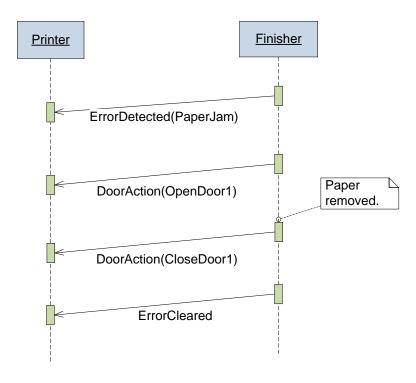

| FIGURE 2.2.5: ERROR HANDLING PROCEDURE FOR A PAPER JAM                                  | 18 |

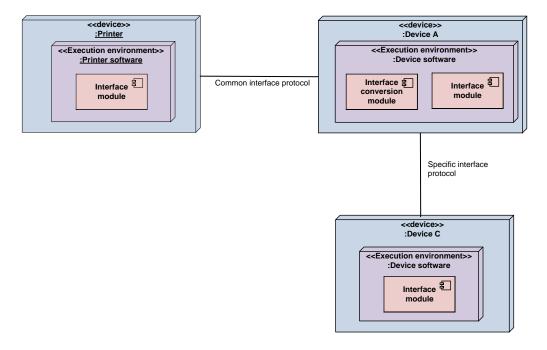

| FIGURE 2.3.1: COMMON INTERFACE PROTOCOL                                                 | 20 |

| FIGURE 2.3.2: PAPER HANDLING PROCEDURE IN CUT-SHEET ENVIRONMENT WITH MULTIPLE FINISHERS | 22 |

| FIGURE 3.2.1: CONCEPTUAL VIEW                                                           | 25 |

| FIGURE 3.3.1: LOGICAL VIEW                                                              | 26 |

| FIGURE 3.4.1: REAL DEPLOYMENT VIEW                                                      | 28 |

| FIGURE 3.4.2: PROTOTYPE DEPLOYMENT VIEW                                                 | 28 |

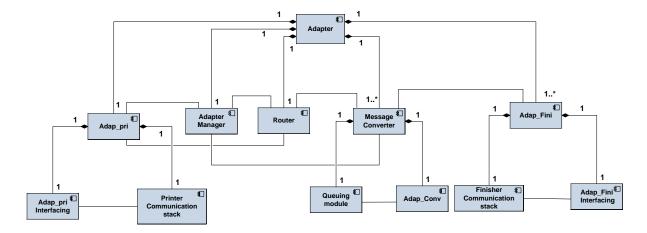

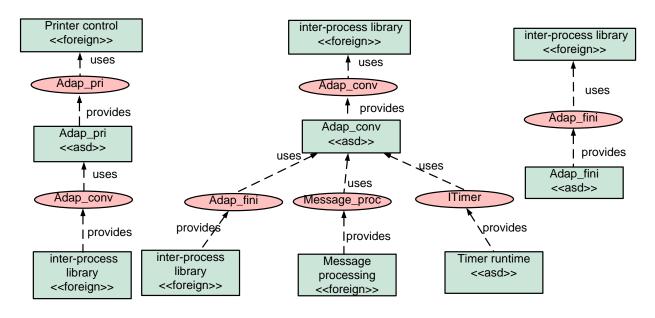

| FIGURE 3.5.1: COMPONENT STATIC VIEW                                                     | 29 |

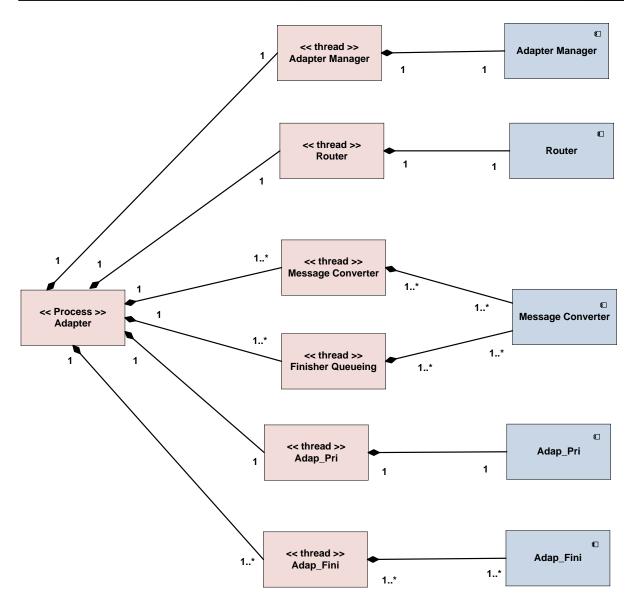

| FIGURE 3.5.2: COMPONENT DYNAMIC VIEW                                                    | 31 |

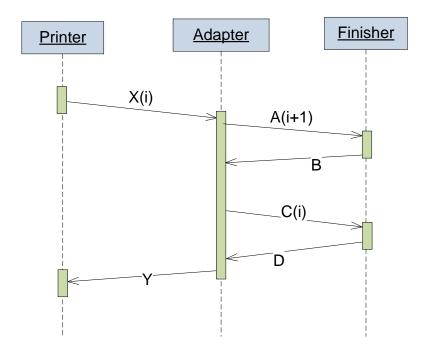

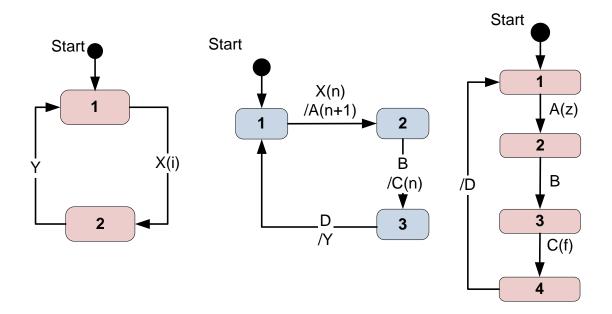

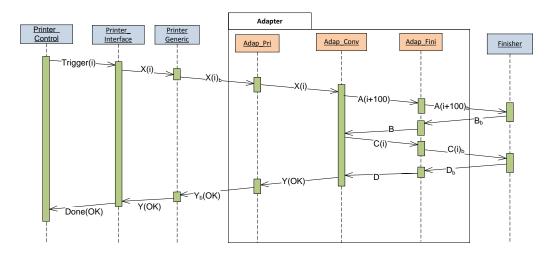

| FIGURE 4.1.1: TYPICAL ADAPTER SCENARIO                                                  | 34 |

| FIGURE 4.1.2: STATE MACHINES FOR THE TYPICAL ADAPTER SCENARIO                           | 34 |

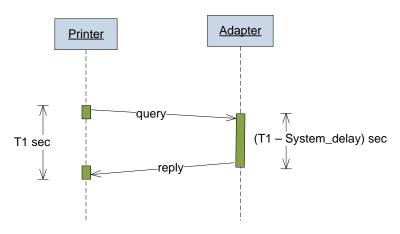

| FIGURE 4.2.1: IMPACT OF SYSTEM_DELAY IN TIMEOUT CALCULATION                             | 37 |

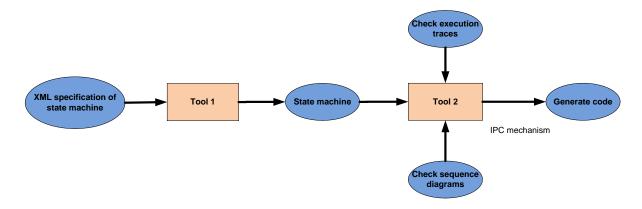

| FIGURE 4.3.1: TOOL CHAIN                                                                | 39 |

| FIGURE 4.3.2: ARCHITECTURE OF THE TOOL                                                  | 40 |

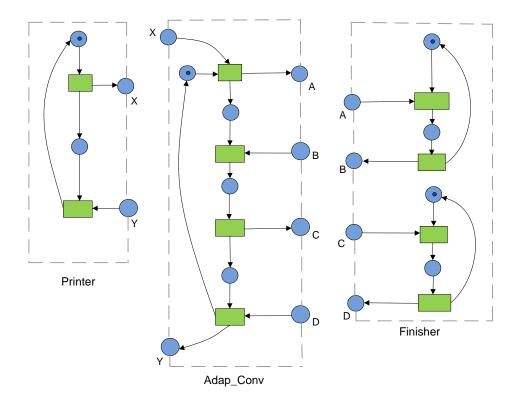

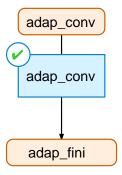

| FIGURE 4.3.3: BEHAVIORAL INPUT MODELS AND THE SYNTHESIZED ADAP_CONV MODULE              | 41 |

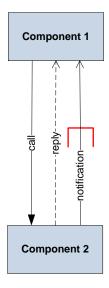

| FIGURE 4.3.4: ASD FUNCTIONALITY                                                         | 42 |

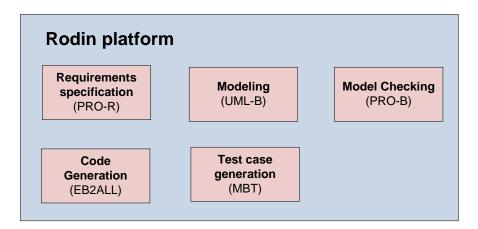

| FIGURE 4.3.5: EVENT-B TOOLSET                                                           | 43 |

| FIGURE 4.3.6: INTERFACE LANGUAGE FUNCTIONALITY                                          | 44 |

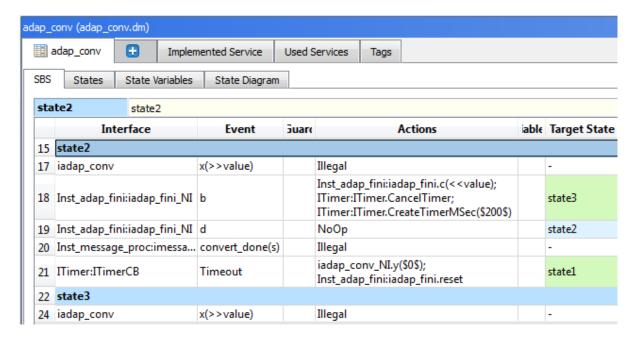

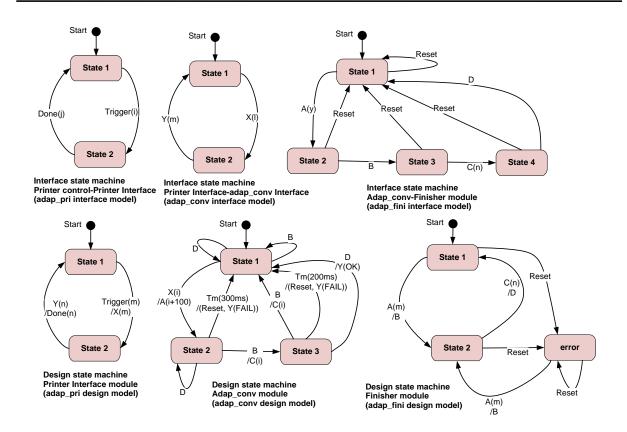

| FIGURE 5.1.1: ASD COMPONENTS OF AN ADAPTER                                              | 50 |

| FIGURE 5.1.2: ASD COMPONENT INTERACTIONS                                                | 51 |

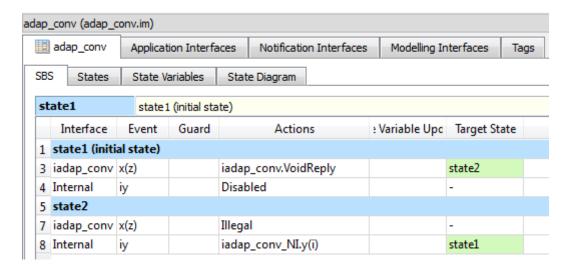

| FIGURE 5.1.3: EXAMPLE OF AN ASD TABLE (INTERFACE MODEL)                                 | 52 |

| FIGURE 5.1.4: EXAMPLE OF AN ASD TABLE (DESIGN MODEL)                                    | 52 |

| FIGURE 5.1.5: EXAMPLE OF A COMPLETE ASD MODEL OF THE ADAPTER                            | 54 |

| FIGURE 5.2.1: EXAMPLE OF DESIGN MODEL VERIFICATION USING ASD                            | 55 |

| FIGURE 5.2.2: EXAMPLE OF INTERFACE MODEL VERIFICATION USING ASD                         | 56 |

| FIGURE 5.2.3: EXAMPLE OF AN INTERFACE VIOLATION CAPTURED BY ASD                         | 56 |

| FIGURE 5.3.1: EXAMPLE OF STUB GENERATION USING ASD                                      | 58 |

| FIGURE 6.1.1: PROTOTYPE TEST SETUP                                                      | 60 |

| FIGURE 6.2.1: INITIAL TESTING OF PROTOTYPE BOARD                                        | 62 |

| FIGURE 6.3.1: PROTOCOL STACK                                                            | 63 |

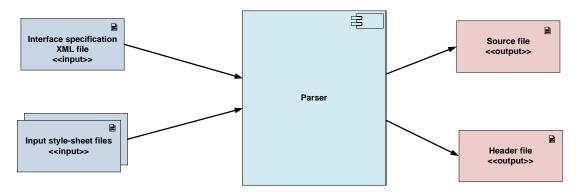

| FIGURE 6.3.2: TOOL FUNCTIONALITY                                                        | 64 |

| FIGURE 6.3.3: TESTING THE ADAPTER ARCHITECTURE USING THE INTER-PROCESS LIBRARY          | 64 |

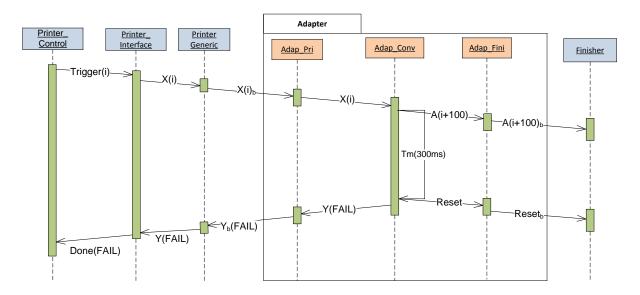

| FIGURE 6.4.1: ADAPTER SCENARIO 1                                                        | 65 |

| Figure 6.4.2: Adapter scenario 2                                          | 66 |

|---------------------------------------------------------------------------|----|

| Figure 6.4.3: Adapter scenario 3                                          | 66 |

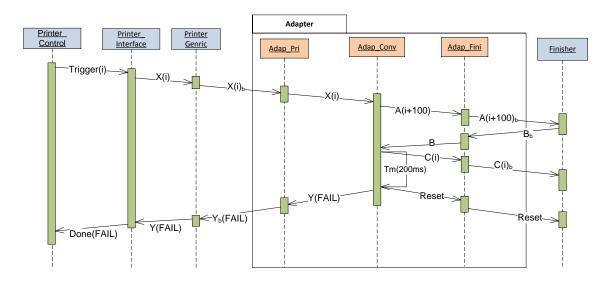

| Figure 6.4.4: State machines for typical adapter scenarios                | 67 |

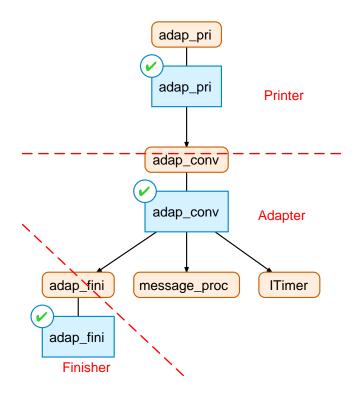

| FIGURE 6.4.5: COMPONENTS OF ASD FOR TYPICAL ADAPTER SCENARIOS             | 68 |

| FIGURE 6.4.6: COMPLETE SOFTWARE COMPONENTS FOR TYPICAL ADAPTER SCENARIOS  | 69 |

| Figure 6.4.7: ASD generated files                                         | 69 |

| Figure 6.4.8: Code snippet for the interfacing of ASD client stubs        | 70 |

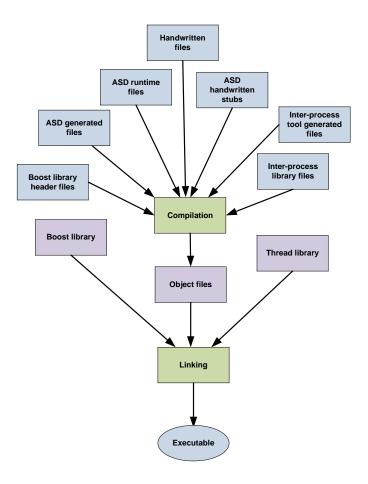

| FIGURE 6.4.9: COMPILATION AND LINKING PROCEDURE FOLLOWED                  | 71 |

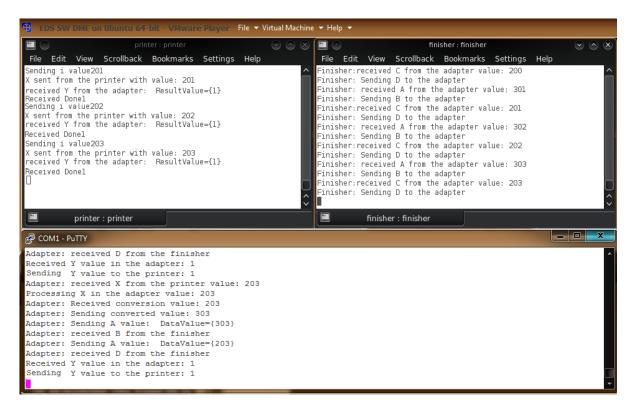

| Figure 6.4.10: Screenshot of the prototype testing                        | 72 |

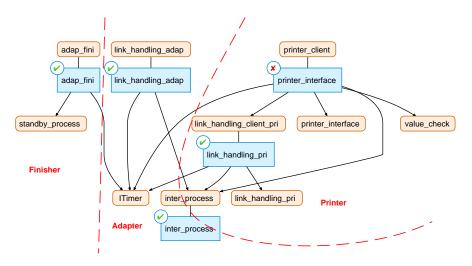

| FIGURE 6.5.1: ASD COMPONENTS FOR LINK HANDLING MESSAGE CATEGORY (PARTIAL) | 73 |

### **List of Tables**

TABLE 4.5.1: MODELING SELECTION CHART

48

### **List of Acronyms**

| CRC  | Cyclic Redundancy Check                |

|------|----------------------------------------|

| PC   | Personal Computer                      |

| CPU  | Central Processing Unit                |

| XML  | Extensible Markup Language             |

| IPC  | Inter Process Communication            |

| CASE | Computer-aided Software Engineering    |

| SEA  | Specification of Elementary Activities |

| SBS  | Sequence based Specifications          |

| DPC  | Deferred Procedure Call                |

| ASD  | Analytical Software Design             |

| SDL  | Specification and Description Language |

| OS   | Operating System                       |

| USB  | Universal Serial Bus                   |

| ECB  | Ethernet Control Model                 |

| TFTP | Trivial File Transfer Protocol         |

| IP   | Internet Protocol                      |

| GUI  | Graphical User Interface               |

### Chapter 1

### Introduction

Wide format printers operate on a continuous sheet of paper. Finishers perform ancillary activities like folding, and stacking with sheets coming out of the printer. The wide format printers from Océ need to interoperate with various types of finishers from Océ and other companies. The interface specification between a printer and a finisher involves mechanical, electrical and functional descriptions. The mechanical interface description decides upon the physical connection between the printer and the finisher. The electrical interface description decides upon the type of communication, communication media and electrical connectors. The functional interface specification decides upon the functional interface protocol employed between the printer and the finisher. The interface specification differs from one finisher to another. The interfacing of a printer and a finisher takes a considerable amount of time and effort due to the varied interface specification across finishers. The objective of this thesis is to find a solution for this interfacing problem with respect to the electrical and functional interface between Océ wide format printers and finishers.

This chapter emphasizes the aforementioned problem and related concepts in a detailed manner. Section 1.1 explains the background domain concepts necessary to understand the problem. Section 1.2 explains the problem description in detail. Section 1.3 explains the goals associated with this project. Section 1.4 explains the approach taken in solving the problem. Section 1.5 explains the organization of rest of the report.

### 1.1 Background

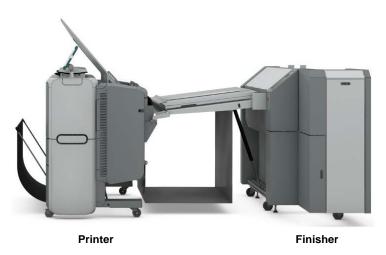

Océ is a leading player in the area of wide format printing systems. The products are primarily printers and copiers and may consist of other modules like an external PIM (paper input module), a scanner and a finisher. Figure 1.1.1 shows a printer connected to a finisher. The printer configures the finisher for handling finishing jobs and signals the finisher about the arrival of the sheets to the

finisher. The behavior of the system can be compared to a master and slave relationship where the printer is the master sending commands to the finisher and the finisher is the slave responding to the printer's commands.

Figure 1.1.1: Printer connected to a finisher

#### 1.1.1 Wide Format Printers

Wide-format printers are generally printers with a print width between 17" and 100". These are used to print banners, posters, Architecture/Engineering/Construction (AEC) diagrams, computer aided design (CAD) diagrams and geographic information system (GIS) data. These generally use a roll of print material rather than individual sheets and may incorporate hot-air dryers to prevent prints from sticking to themselves as they are produced [7]. An example of a wide format printer, the Océ plot wave 350 printer is shown in Figure 1.1.2. The Océ plot wave printer produces up to six A1 or D-size plots per minute.

Figure 1.1.2: Océ plot wave 350 printer

#### 1.1.2 Wide Format Finishers

Wide format finishers perform post-printing actions such as folding or stacking. These are manufactured by Océ or by other companies. These have to be connected mechanically and electrically with a printer in order to operate. These interact with the printer through a functional interface protocol. A printer can set finishing specification like folding length for the sheets through the functional interface. The interfacing of finishers with printers takes a considerable amount of time and effort due to the fact that finishers can be from other companies with different interface requirements. Some of the finisher's vendors do not provide complete dynamic specification of the functional interface making it tougher for the printer integration. An example of a wide format finisher, the Océ 4311-fullfold finisher is shown in Figure 1.1.3. The Océ 4311 finisher produces folded copies and drawings that are accurate up to the millimeter scale.

Figure 1.1.3: Océ 4311-fullfold finisher

#### 1.1.3 Current Setup

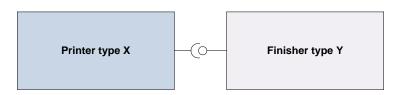

Figure 1.1.4 shows the simplified current setup of the printer-finisher interfacing. Printer type X, here is any wide format printer from Océ and finisher type Y is any wide format finisher from Océ or other companies. The term 'type' is mentioned here to stress the differences in the interface across finishers. The term 'X' represents any number to signify an individual printer. The term 'Y' represents any number to signify an individual finisher. The setup is simplified because some printers can interface with more than one type of finisher. The important point to stress here is that the most of the current wide format printers from Océ can interface with only one type of finisher. Currently, a printer can interface with only one finisher at a time.

Figure 1.1.4: Simplified current setup of the printer-finisher interfacing

The current generation of finishers uses RS-232 or RS-232 variants (RS-232 with an additional pin for power control) or serial or parallel connectors for electrical connectivity. The finishers from other vendors have their own functional interface specification which has to be used for printer-finisher interfacing. Due to the above mentioned reasons, the printers can interoperate with only one or two types of finishers. The problem with this approach is that the finisher usage is restricted to some printers. The interface implementation with a new finisher involves re-work every time. Océ wide-format printer's electrical interface will be changed in the future to universal serial bus (USB) connectors to bring uniformity at the level of electrical interface and to support increased data rates. This change should be accompanied with the support for existing finishers since these are already interfaced with the printers. The idea is that the printers should be able to interface with all finishers. First, this demands a hardware converter for interfacing different electrical connectors. A typical example justifying the above statement is that the converter for USB to RS-232 variants is not readily available in the market. Second, there is a necessity for a functional interface converter to support different functional interfaces across finishers.

### 1.2 Problem Description

Océ faces a challenge in interfacing their printers with finishers from Océ and other companies. Finishers communicate with printers using specific functional and electrical interfaces. The current printer's software has been designed to interface a particular finisher. This approach limits the interoperability of finishers with printers and affects the software development time needed for the interface implementation. The approach also affects the maintainability of the printers with a necessity to change the printer's software for every finisher related software patches. The requirement is that any type of Océ wide format printer must be able to communicate with any type of finisher. The idea is to come up with a model based framework which eases the integration (with respect to time and effort) of the existing finishers and robust enough to integrate future generation of finishers. The approach should also improve the maintainability of the printer's software.

**Business Motivation:** Océ sells printers and finishers separately to its customers. Currently, customers pay for the printer which includes the price for finisher's interfacing hardware and software. This situation is unwarranted since some customers do not require finishers but they have to pay extra money indirectly. This affects the competitive pricing of Océ printers in the market. The new framework must ensure that the finisher software is not part of the printer in order to conform to this business interest. Another motivation is to reduce the additional time and effort spent in the interface implementation which ultimately adds to the cost of the printer. The ambition is to make the design reusable as much as possible for finisher integration thereby gaining an advantage on the cost.

**Problem Statement:** To propose a model based framework for interfacing Océ wide format printers with any type of wide format finisher and to prototype a model based framework to test the feasibility.

#### 1.3 Goals

Given the problem definition in the previous section, the goals of the projects are the following:

- Propose a solution for printer-finisher interfacing at the product level

- Identify the present and future interface requirements of finishers

- Construct an architecture that supports finisher interface requirements

- Specification and design of an interface protocol introduced due to the new architecture

- Investigate different model based approaches for the adapter software design

- Identify a suitable modeling approach for the project

- Prototype using the modeling approach to test the feasibility of the modeling approach

The scope of the thesis is limited to wide format printers and not cut-sheet printers. The cut-sheet printers work on individual sheets of paper like A4 and A3. The cut-sheet printers have different functional interface requirements for finisher operations.

**Note:** The term 'adapter' refers to a finisher adapter which takes care of the electrical and functional interface incompatibilities between the printer and finishers. This terminology will be used in rest of the document.

#### 1.4 Approach Taken

This section explains the research approach employed in this project. The global solution for the problem, research challenges considered in the project and the project life cycle are discussed in detail.

#### 1.4.1 Proposed Solution

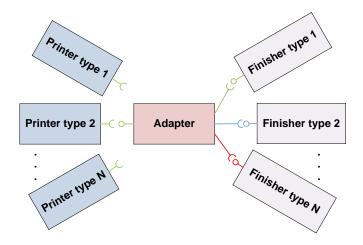

The problem requires a hardware and software converter to translate different finisher interfaces. The proposed solution is to deploy an adapter, a combination of hardware and software converters. The adapter takes care of both the electrical connection incompatibilities and functional interface differences. Figure 1.4.1 shows an adapter which can interface different types of printers with different types of finishers (adapter can interface only one printer/finisher at a time).

The interface between the printer and the adapter remains the same irrespective of the finisher. The interface between the adapter and the finisher is based on the specific finisher protocol. The location of the adapter was decided from the business motivation. Hence, the plan was to run interface software in a separate hardware board outside the printer with its own operating system.

Figure 1.4.1: Proposed solution for the printer-finisher interfacing

The introduction of an adapter between printers and finishers introduces two interfaces following different protocols which are explained below:

**Generic protocol**: Interface protocol that specifies the functional interface between all Océ wide format printers and the proposed adapter. This terminology will be used in the rest of the document for referring to the printer-adapter functional interface protocol.

**Specific protocol**: Interface protocol that specifies the functional interface between a finisher and the proposed adapter. This interface protocol is the same as the finisher protocol of this finisher. This terminology will be used in the rest of the document for referring to the finisher-adapter functional interface protocol.

The following advantages are achieved in the proposed solution:

- There is a clear separation of concerns. The finisher interfacing software is isolated from the printer software.

- The customer has to pay only the correct amount of money based on his/her requirements.

- The printer remains numb to the changes in the finisher. This is due to the introduction of the generic protocol between the printer and the adapter.

- The technology and the tooling can be selected irrespective of the printer's technology. For example, the adapter software is aimed to be developed using a model based approach which reduces development time and effort.

- The maintenance of the adapter software is simpler. More finisher related patches can be delivered without changing the printer's software.

- There is no necessity to change the printer's hardware for finisher interfacing since the electrical connectivity with the adapter is fixed.

**Alternative Solution**: The alternative solution is to run the adapter software in the printer and to have a separate hardware converter outside the printer. The adapter software can be made as a plug-in which can be incorporated when required. This solution conforms to the business interests

and tackles the problem. But the solution does not provide the same clear separation of concerns as the proposed solution. The patches related to the finisher will be incorporated in the printer's software thereby not improving the maintainability of the printer's software. But, this solution avoids the additional marshalling/unmarshalling performed between the printer and the adapter in the proposed solution which in turn improves the timing performance.

#### 1.4.2 Research Challenges

The previous section shows the proposed solution and the implementation of this solution poses research challenges at various levels in the project. The approach followed in solving these research challenges is mentioned briefly in this section. The following research challenges were considered in the thesis:

Making the adapter software architecture to handle different finisher capabilities

**Motivation**: The purpose of making an adapter is to use it for present and future generations of finishers. The adapter architecture should be robust enough for changes in the finisher capabilities. For example, one of the changes expected in the future is the use of multiple finishers. The identification of expected future capabilities is crucial in achieving this type of architecture.

**Approach**: Different architectural views were created to understand the fit with the finisher requirements. Alternative architectures were considered to check the validity of the proposed architecture. Chapter 4 explains different architectural views of the adapter software.

Making the adapter software architecture suitable for model based design

**Motivation**: The solution is aimed at incorporating a model based design. The architecture should provide a clear separation of concerns indicating the exact location to fit in model based software in the architecture. This helps in the unbiased evaluation of the modeling tools.

**Approach**: The focus of the model based adapter lies in the logical message conversion ignoring bit level information. The architecture was made to provide clear separation of marshalling/unmarshalling blocks from the message conversion block. Chapter 4 explains different building blocks of the adapter software when it is deployed.

• Making the generic protocol design to fit with the existing finisher protocols

**Motivation:** The existing protocols differ from one finisher to another. The generic protocol has to fit the existing protocols. The protocol design has to be simple since the effort spent in the adapter state machine depends on the design of this protocol.

**Approach**: A top-down approach was employed where in a generic protocol was proposed based on the domain requirements. Then, the protocol was checked for the fit with existing

**Note:** Marshalling is the process of gathering data and transforming it into a byte stream before it is transmitted over a network and unmarshalling is the reverse process of converting byte stream back to the original data.

finisher protocols. Appendix C: "Generic protocol for adapter interface" contains detailed sequence diagrams showing the mapping of the generic protocol with different finisher protocols.

Making the generic protocol design robust for future changes in the finisher protocols

**Motivation:** The changes in finisher capabilities in the future will introduce changes in the finisher protocols. The adapter software must be able to handle these changes without the necessity to modify the generic protocol messages. This is a critical factor to consider while coming up with a generic protocol otherwise considerable re-work has to be done on the printer and adapter interface protocol state machines which will dilute the purpose of having a generic adapter.

**Approach**: The generic protocol was classified into different categories with some sections for the expected future capabilities. The interrelation between different sections was considered during the protocol specification. For example, to support multi finisher capabilities in the future requires a finisher identifier in all the messages. Chapter 4 briefly explains the generic protocol design decisions. The complete information regarding the generic protocol is available in the Appendix C: "Generic protocol for adapter interface".

• Analysis of complexities for message conversion in the adapter software

**Motivation:** The adapter has to perform message conversion in order to interface different type of printers and finishers. The identification of message conversion complexities is critical in verifying the feasibility of a generic adapter.

**Approach**: The different types of message conversion complexities were identified before the generic protocol specification in section 2.2.4. Then, the conversion complexity threshold was determined in section 4.2.2 after the generic protocol specification.

Handling of concurrency in the adapter

**Motivation:** The adapter has to interface with a single printer and one or more finishers at the same time. This introduces the question of handling concurrent messages from different components. This question has to be answered starting from the architecture to the implementation.

**Approach**: The adapter has different marshalling/unmarshalling components for the printer and finishers. The message conversion module implementation gives priority to messages from the printer. If there is a concurrent message both from the printer and finishers, then printer message is processed immediately and the finisher messages are placed in a queue. Chapter 3 and chapter 6 explain the concurrency handling in the adapter.

Verification of generic protocol consistency

**Motivation:** The generic protocol will be implemented as a separate state machine in the printer and the adapter. Both the state machines have to be consistent with the protocol state machine. This is necessary to avoid run time inconsistencies like deadlock and livelock.

**Approach**: The modeling selection criteria in chapter 4 included this aspect before choosing the modeling approach. The modeling tool is used to verify the generic protocol consistency.

Selection procedure of a modeling approach for the adapter

**Motivation:** Model based software is a very generic term and the project aims to find software suitable for the design of adapter software with certain message conversion complexities.

**Approach**: The selection procedure was divided into three broad categories comprising of model based aspects, quality aspects and engineering aspects. The details are explained in chapter 4.

Handling incomplete dynamic behavior of the finisher protocol specification

**Motivation:** The finisher protocol specification especially from other vendors sometimes has an incomplete dynamic specification. This means the adapter software should implement a mechanism to report the inconsistent protocol behavior.

**Approach**: The approach employed is to have a strict finisher protocol state machine in the adapter and to use additional component to detect the occurrence of illegal behavior. Chapter 6 explains about the details of this additional component.

• Selection of scenarios for the prototyping of the adapter software

**Motivation:** The aim of the project is to test the feasibility of the model based framework which includes the architecture, protocol and model based approach for the adapter. The scenarios chosen for testing the feasibility must include all message conversion complexities which make the feasibility more concrete.

**Approach**: The scenarios were selected based on message conversion complexities especially to test different message conversion complexities. The scenarios which require different threads to communicate were also tested. Chapter 6 explains about the choice of scenarios for prototyping the adapter software.

• Testing strategy employed to test the entire setup

**Motivation:** The main objective of the thesis is to come up with a generic adapter. The testing of the adapter is possible only with printer and finisher modules. The project should also look into different possibilities of testing the adapter.

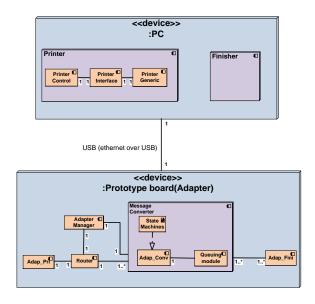

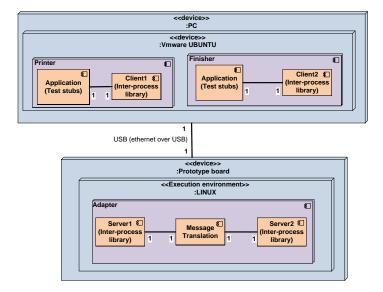

**Approach**: The adapter software was made to run in a prototype board with its own operating system. The printer and the finisher run in the PC connected to the board via USB. Ethernet over USB is used for communication between different modules. Printer and finisher stubs were created to test the functionality of the adapter. Section 6.1 explains the test setup used in this project.

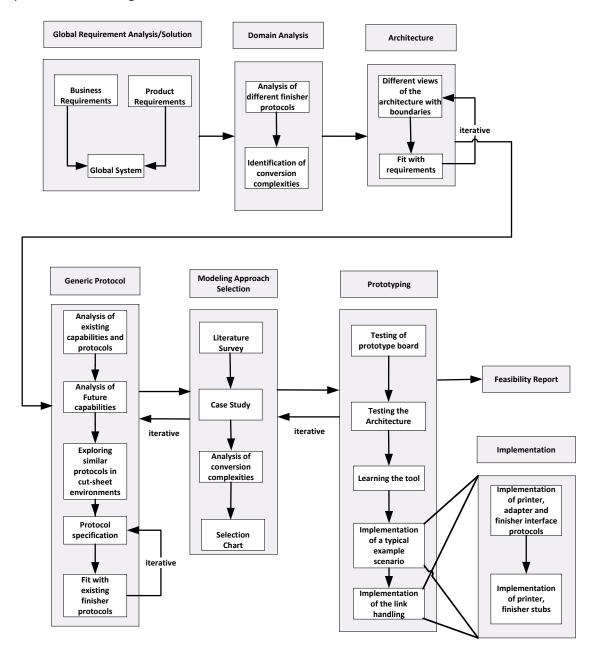

#### 1.4.3 Project Life Cycle

The 'Agile' software development methodology was followed in the project. Figure 1.4.2 gives the overall picture of the tasks involved in the project but the flow was not strictly followed. The major activities in the project are given at the top block with internal activities at the bottom. There are several activities carried out in parallel especially among modeling approach selection, generic protocol design and prototyping phases in making the adapter software. This approach helped to reduce the risks at an earlier stage in the project. For example, the testing of the prototype board and testing of the architecture in the board was carried out before the modeling approach was selected. This ensured that there were no setbacks at the last stage of the project due to lack of experience in handling the hardware.

Figure 1.4.2: Project life cycle

The major phases of the project are listed below:

**Global Requirement Analysis/Solution:** This phase is the initial phase in the project. This phase is explained in the previous sections of this chapter.

**Domain Analysis:** This phase is explained in the chapter 2 in a detailed way. This phase comprises of understanding different finisher protocols and identification of type of complexities involved in the message conversion.

**Architecture:** Chapter 3 explains the details behind this phase. This phase involved identification of a suitable architecture for the adapter software.

**Generic Protocol:** The generic protocol specification and design are performed in this phase. Chapter 4 describes the various aspects involved in designing the generic protocol.

**Modeling approach selection:** Chapter 4 explains this phase in a detailed manner. This phase involves comparing different modeling approaches and the identification of a suitable modeling tool for designing the adapter software.

**Prototyping:** Chapter 6 describes the details of this phase. This phase involves the actual prototyping to verify the feasibility of the solution.

#### 1.5 Report Organization

The rest of the chapters in the report are organized as follows. Chapter 2 describes the domain analysis carried out in the thesis. Chapter 3 construes the architecture of the adapter software in a detailed manner. Chapter 4 describes the generic protocol and the modeling approach selection in a detailed way. Chapter 5 explains the analytical software design (ASD) in a detailed manner. Chapter 6 describes the prototyping carried out in the project. Chapter 7 explains the conclusions derived from the project and future possibilities. The UML diagrams shown in different chapters follow UML 2.2 standard.

### Chapter 2

### **Domain Analysis**

This chapter explains the different activities performed in the domain analysis phase. Finisher protocols, both from Océ and from other companies were analyzed. The finisher protocol from another company has an incomplete dynamic functional interface specification. The identification of different finisher capabilities and framing of message categories is essential in understanding the complexities involved in the adapter logic and framing the architecture of the adapter software.

Section 2.1 lists the finisher capabilities which include the present capabilities and expected capabilities in the future. Section 2.2 explains the finisher protocol analysis carried out to understand the nature of different finisher protocols. Section 2.3 describes the interface adapter solutions available in the cut-sheet environment. This chapter is concluded in section 2.4 which outlines the important findings of this chapter.

#### 2.1 Finisher Capabilities

The finisher capabilities represent the behavior and functionalities of the finisher. The present capabilities can be understood from the existing finisher protocols. The expected future capabilities are obtained from discussion with the stakeholders especially architects of the Océ wide format printers.

#### 2.1.1 Present Capabilities

The present finishers behave like a slave to the printer and carry out jobs assigned by the printer. Most of the finishers has their own power supply and can be turned on/off independently. For some finishers, an additional power signal has to be received from the printer in order to turn on/off. The establishment of a connection with the printer happens by sending link establishment messages. Once the finisher is connected to the printer, the finisher can perform sheet related tasks

sent by the printer. The printer can configure the finisher differently for every job sent. The finisher can report errors to the printer and vice-versa. The finisher can also work under the direct control of the operator without the requirement for a printer. The tasks performed by the wide format finishers include the following:

- Stacking creating a pile of sheets

- Folding bending the sheets by applying pressure

- Stickers pasting labels in the sheets

- Turn table changing the orientation of the sheets

#### 2.1.2 Future Capabilities

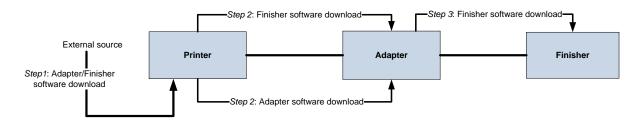

Three future capabilities that are expected in the future were identified from discussion with the stakeholders. The expected future capabilities are software download, power cycling and multiple finishers.

**Software Download:** This is a feature by which the device can update the firmware. The device can either download the firmware directly (internet or USB device) or get the firmware through another device like a printer. There are two types of software downloads that needs to be incorporated. The two types are adapter software download and finisher software download. Figure 2.1.1 shows the process involved in the two software download features. For the adapter software download, the adapter firmware will be downloaded by the printer from external source like a USB device or internet and then transferred to the adapter. The finisher software download feature is currently not available in finishers. This feature has three steps, the printer downloads the finisher's firmware from an external source, then transfers it to the adapter and finally the adapter transfers it to the finisher. The generic protocol and the adapter software must ensure that this feature can be achieved in the future.

Figure 2.1.1: Software download feature

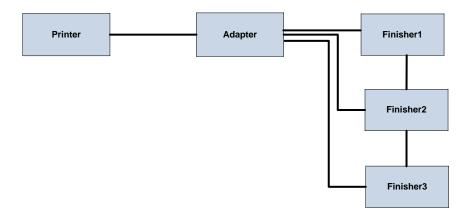

**Multiple finishers:** In the multiple finishers' environment, finishers are stacked one behind the other allowing finishing tasks to be performed continuously on the sheets. The adapter software should be able to communicate with all the finishers. The current generation of finishers does not support this multiple finisher functionality. In the domain of graphical art printing, there is a possibility of this feature being incorporated in the future. At a conceptual level, the adapter software and the generic protocol must be able to handle multiple finishers. Figure 2.1.2 shows an example case where three finishers are stacked one behind another in the order of their

numbering. The adapter can communicate with all the finishers independently and there is a communication link between the immediate finishers. The details regarding the support for the multiple finishers will be explained in chapter 3 and chapter 4.

Figure 2.1.2: Multiple finishers feature

**Power Cycling:** This is a concept to save energy consumption in electrical devices. It is the concept of changing power states based on the usage of the device in order to conserve power. Power cycling can be done both for the finisher and the adapter. The scenarios when the finisher/adapter must be power cycled must be identified in order to power cycle the finisher/adapter. The generic protocol and the adapter software must ensure that this feature can be included in the future.

#### 2.2 Finisher Protocol Analysis

This section explains different message formats, protocol details like electrical interface, message categories and expected message conversion complexities for the adapter software.

#### 2.2.1 Message Formats

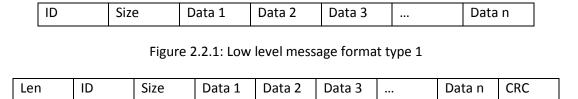

There are two different message types available in the finisher interface protocols and they are explained as follows:

**Logical messages:** Raw functional interface messages independent of the electrical channel related information. This terminology will be used in the rest of the document. Appendix A: "Message list for various finishers" provides a complete list of logical messages with parameters and their range for different finishers.

**Low level messages:** Functional interface messages with framing details specific to the electrical communication channel.

The logical level message format used in the analyzed finishers is shown below:

{Identifier, Data length, Data array}

The identifier represents the type of the message, direction of the message and expected functionality. There are two types of messages possible: event messages and data messages. Event messages contain only an identifier and they initiate an action in the receiver. Data messages contain data along with the identifier. The data array has a maximum range beyond which the data length parameter's value cannot be set.

Examples of different low level message formats are shown below:

Figure 2.2.2: Low level message format type 2

A low level message format is shown in Figure 2.2.1. The first parameter – ID corresponds to the identifier in the logical message format, the second parameter – size corresponds to the data length in the logical message format and the data block corresponds to the data array in the logical message format. Another low level message format is shown in Figure 2.2.2. The first parameter – Len represents length of the entire message and this parameter is included since the size of a CRC varies from one message to another. The last parameter is the cyclic redundancy checks (CRC) which is a check sum used to verify the integrity of the message. The rest of the message parameters are same as in the low level message format type 1.

From the message format analysis of finishers, it can be seen that there are two levels of message conversion needed in the adapter software. First level, conversion of logical messages transferred between the finisher and the printer. Second level, conversion of low level messages transferred between the printer and the finisher. These two messages have to be dealt differently in the adapter software. The number of logical messages used in the protocol ranges from 25 to 50. The number of arguments in logical level in each message varies from 0 to 8. The one of the focus of the thesis is to work on the logical message conversion in the adapter software.

#### 2.2.2 Protocol Details

This section explains several aspects of the finisher protocols: electrical interface, maintenance of connectivity, paper handling procedure, error handling procedure and incomplete dynamic specification case.

**Electrical interface:** The finisher interface protocol specification contains electrical and functional details. There is a dedicated communication channel between the printer and the finisher. The current finishers communicate using RS-232, RS-232 variants, serial connector and parallel connector. The baud rate, number of data bits, parity bit availability, stop bit value and other parameters depend on the type of the connector used. The communication links are expected to

work without disturbances and there is no retry mechanism is available in the communication protocol (low level protocol specific to the connector RS-232).

**Maintenance of connectivity:** The communication request can be started by the printer or finisher depending on the protocol. Once the link has been established between the printer and the finisher, the maintenance of the link would be done by using one of the two methods mentioned below:

- Link check messages: These messages are transferred continuously between the printer and the finisher in order to ensure the working of the link. Once the link is broken, it can be understood from the non-arrival of these messages.

- Timeout for every reply message: For every message sent from the printer and finisher, a timer is started and the reply is expected to arrive within a certain time period. If the timer expires, then the link is assumed to be broken.

Both the methods have their advantages and disadvantages. In the link check method, there would be overcrowding of messages in the channel during peak traffic time. But the loss of link can be detected immediately once the link has been broken. In the timeout method, the loss of link can be detected only after a message has been sent but there would be no overcrowding of messages in the channel.

**Paper handling:** Every sheet of paper is identified by a unique identifier present in the message. There are two methods to handle paper related messages in the finisher protocols.

Parallel paper task handling: Figure 2.2.3 illustrates the parallel paper task handling feature in finishers. The finishers are informed in advance about the sheets with their finishing procedure that they are going to handle before the sheets actually arrive.

Figure 2.2.3: Parallel paper task handling

There is a maximum limit on the number of such handle messages that can be sent to the finisher before the sheets are delivered by the finisher. The actual arrival of sheets is indicated by the printer through a sheet trigger message. Several such triggers can be sent for which the handle message has been sent already. The finisher replies to the printer once the sheet has been delivered.

Sequential paper task handling: Some finishers do not have the above feature. Figure 2.2.4 illustrates the sequential paper task handling feature in such finishers. They expect the sheet trigger message about the arrival of a sheet immediately after the handle message (indicating the finishing procedure). The finisher completes the particular sheet and sends delivered message back to the printer. Then, finisher gets ready to receive another handle message from the printer.

Figure 2.2.4: Sequential paper task handling

**Error handling:** In case of communication hardware errors (framing, parity bit violation), size check failures and identifier failures, the finisher reports a communication error and tries to re-establish the connection. The range checks for incoming messages are performed in the functional interface software and if there are interface violations then these errors are reported to the printer. Errors related to a paper jam are reported by the finisher when it occurs, the procedure to resolve the paper jam is sent to the printer, the operator gets notification about the error from the printer and finally, when the paper jam gets cleared it is sent to the printer. The errors related to the paper jam in the printer are sent to the finisher.

Figure 2.2.5 shows an example error handling procedure followed in case of a paper jam. The finisher tells the printer to inform the operator that an error has occurred and the type of the error

is a paper jam. Then, the finisher informs the printer to open the door1. Once the jammed paper has been removed from the finisher by the operator, the finisher informs the printer to close the door1. Finally, the finisher informs that the error has been cleared.

Figure 2.2.5: Error handling procedure for a paper jam

**Incomplete dynamic specification**: A finisher which has to be integrated with an Océ printer via adapter in the future is a finisher from another company. The dynamic behavior of its interface was not captured completely in the protocol specification, and logging of messages is not possible from the finisher side. There is a difference in working of the finisher with the serial interface and parallel interface. The adapter must be able to incorporate a parallel interface if required. This shows the necessity to design the adapter software keeping in mind that the finisher protocol specification is incomplete in nature.

#### 2.2.3 Message Categories

The message category refers to the purpose of a message. Each message will fit into one message category. The rationale behind fitting each message to one category is that the isolation of scenarios becomes simpler providing separation of concerns. The categories are framed based on the activities happening in the finisher and they are inclusive of the expected future capabilities. The message category list is shown below:

Link handling: This refers to the messages responsible for establishing connection, maintaining the connection and termination of the connection between the printer and the finisher.

• Paper handling: This refers to the messages responsible for fetching details of the finisher, configuring finishing properties for every paper and sending triggers for arrival of jobs to the finisher.

- **Operational state management:** This refers to the messages responsible for the maintenance of operational states of the finisher. For example, the online state where the printer can send finishing jobs and the offline state where the operator has direct control over the finisher and the finisher are decoupled from the printer.

- **Error handling:** This refers to the messages responsible for reporting errors both from the finisher and the printer and messages sent to resolve these errors.

- **Power state management:** This refers to the messages responsible for the maintenance of the power states in the finisher. These messages can be used to get/set the power state of the finisher and messages sent to initiate the sending of power signals to start the finisher.

- **Diagnostics management:** This refers to the messages responsible for testing performed by a service engineer to test the behavior of a finisher. These messages are sent from the printer and the reply is sent from the finisher.

- **Software download management:** This refers to the messages that are sent to update the firmware of the finisher and adapter.

- **Multiple finishers' mode management:** This refers to the messages that are used to configure the printer and finishers to operate in multiple finishers' mode.

#### 2.2.4 Message Conversion Complexities

The finisher protocol reveals the expected complexities in message conversion of the adapter software. The exact complexity can be understood only after designing the generic protocol and mapping it to specific finisher protocols. The complexity classification was done to understand different complexities possible in the message conversion of the adapter software. The three different complexities expected in the adapter software are the following:

- Data: This type of complexity is the complexity involved in the parameter or data conversion from generic protocol messages to specific protocol messages and vice-versa. This will not be complicated and the reason is that the parameters in the finisher protocol messages include commands, status information, and configuration information. The parameters do not include information with a large amount of data, like for example a JPEG image. There is no interrelation between parameters present in several messages for the same message type, for example video streaming.

- Control: This type of complexity is the complexity involved in the number and type of messages during message conversion from generic protocol messages to specific protocol messages and vice-versa. The challenge in designing the adapter software lies mostly in the control part. For example, a specific combination of messages from the printer to the adapter may be converted to another combination for a finisher. The most complex scenario would be identified after the specification of the generic protocol.

Domain Analysis 20

• Timing: This type of complexity is the complexity involved in the adapter software in handling the timing requirements from both the software modules for message conversions. The timing related messages usually occur not in the happy case scenarios for finisher protocols. Hence, the normal operation of the adapter will not require much timing information make it simple. The timing information has to be incorporated as timeouts to handle unexpected behaviors in the protocol for example loss of a communication link.

### 2.3 Cut-sheet Printer Interface Solutions

The cut-sheet printer environment comes under the category of a related domain for wide-format printers. The printer-finisher interface implementation in the cut-sheet printer environment was investigated to find suitable techniques that can be applied in the wide format environment. The important fact is that the concept of an interface adapter is well established in the cut-sheet environment. The solution is not applicable straightaway since the finisher capabilities, electrical interface and the functional interface protocols are different.

**Common interface protocol**: One of the techniques used in the cut-sheet environment related to the interface adapter is the usage of the common interface protocol. The protocol is used for the communication interface specification of the printer with other devices. If some external device is not following the protocol but needs to communicate with the printer, then the device is connected to the interface adapter. The printer addresses the device as a normal device following the common interface protocol. The printer's commands will be sent to the interface adapter and the adapter translates the message and then sends it to the external device. An example of the common interface protocol usage is shown in Figure 2.3.1.

Figure 2.3.1: Common interface protocol

Domain Analysis 21

The printer can communicate with device A and device C directly using the interface protocol. There is a specific protocol interface between device A and device C. The messages sent to the device C are received by device A and converted before reaching the destination. In this way, the printer can communicate with the device C as if the device was following the common interface protocol. The example explained here is a proxy pattern, a software design pattern.

**Logical message format**: The common interface protocol uses a similar type of logical message format as that of the wide format finisher protocols. An example of the logical message format used in the common interface protocol is shown below:

{*Priority*, *Direction*, *Sub* – *protocols*, *Command*, *Mode*, *Node Id*, *Data array*}

'Priority' tells whether the message has high or low priority, 'Direction' tells whether the message is from the printer to the finisher or vice-versa, 'Sub-protocols' tells the message category of the message and this is applicable only in application mode, 'Command' is the identifier used to map the functionality of the message, 'Mode' describes whether the device operation is in download or application mode, 'Node Id' describes the node identity of the printer or the finisher, 'Data Array' is the fixed data array which is the data transferred from printer to devices and vice-versa. The concept of 'Node-Id' is to incorporate multiple finishers.

**Message Categories**: These helps to identify messages for the generic protocol since the common interface protocol use similar type of messages. An example message category list in the cut-sheet environment is shown below:

- System: Messages to set up and maintain communication with the finisher.

- Status: Messages related to controlling the operational status of the finisher.

- Action: Messages related to the handling of sheets. This does not include the sheet trigger messages.

- Trigger: Indicates the (non-) arrival of sheets. These messages are used for timing of sheets.

- Error: Messages related to reporting and handling of errors.

- Information: Messages related to information exchange between the printer and the finisher.

- Diagnostics: Messages related to the execution of diagnostic tests.

- Development Support: Messages to support development and analysis.

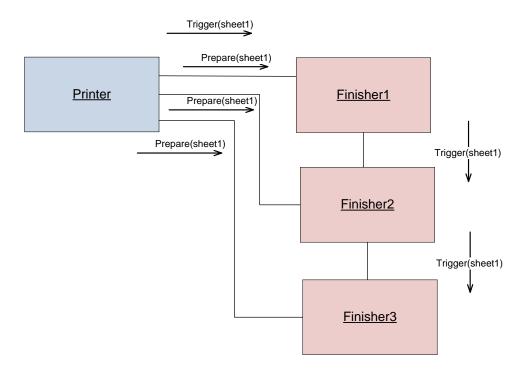

Working of multiple finishers: The cut-sheet printers handle multiple finishers and the common interface protocol can support them. Figure 2.3.2 shows the paper handling procedure in the cut-sheet environment with multiple finishers. There are two types of messages: a 'prepare' message to inform the finisher about the type of action required on a specified sheet and a 'trigger' message to inform the finisher about the actual arrival of a sheet. Prepare message is sent from the printer to all the finishers informing the finishing details and the trigger message is sent only to the immediate node in the paper path. Here, the paper path is follows: printer, finisher1, finisher2 and finisher3. Hence, the finishers have to implement part of the common interface protocol related to the 'trigger' message.

Domain Analysis 22

Figure 2.3.2: Paper handling procedure in cut-sheet environment with multiple finishers

### 2.4 Conclusion

In this chapter, a domain analysis was performed to understand the finisher capabilities and different finisher protocols. The printer-finisher behavior reflects a master and slave relationship. The expected future capabilities of the wide format finishers include software download, multiple finishers and power cycling. The finisher protocols comprise mostly of a query and reply based messages. The message conversion of the adapter will be limited to logical messages of finishers to test the feasibility of the adapter design. The number of logical messages in the protocol is limited to around 50 and the number of parameters in each message is limited to around 8. The finisher protocol messages can be grouped into eight different categories. This shows that the generic protocol messages will be grouped into these eight categories. The message conversion complexity for the adapter is expected to be in the control part. This chapter also discusses an example interface adapter solution in the cut-sheet printer environment. The common interface protocol is used by the printer to communicate with different devices. The implication is that the common interface control can be used as a reference for designing the generic protocol in the wide format environment. The multiple finishers' support using the common interface protocol would help in framing a working procedure for wide format printers.

# **Chapter 3**

# **Architecture**

This chapter explains different architectural views of the proposed adapter. The different architectural views (naming and scope) were framed based on the architecture specification procedure followed in Océ. The first step was to identify different stakeholders of the project and the project requirements which are explained in section 3.1. The next step was to create different architectural views in order to map different requirements. The conceptual view of the adapter is explained in section 3.1. Section 3.2 explains the logical view. The component view of the adapter is explained in section 3.5. The deployment view of the adapter is described in section 3.4. The boundaries of the adapter architecture are explained in section 3.6. Section 3.7 concludes the chapter with important details from different sections. The specification of the architecture is not done in an extensive manner since the idea is to identify the different software blocks and their responsibilities. This activity can be taken up as future work.

### 3.1 Requirement Analysis

The requirements are classified into four categories: functional, platform, process and non-functional requirements. The important requirements are functional and process requirements since the idea is to test the feasibility of the adapter software. The MoSCoW<sup>1</sup> prioritization scheme was followed in order to assign priorities on the requirements.

### **Main Stakeholders:**

• Software Architects (SA) are interested in the architecture, the modeling approach applied for designing the software and the business aspects of the adapter.

**Note:** MoSCoW<sup>1</sup> "is a prioritization technique used in business analysis and software development to reach a common understanding with stakeholders on the importance they place on the delivery of each requirement - also known as MoSCoW prioritization or MoSCoW analysis" (see http://en.wikipedia.org/wiki/MoSCoW\_Method)

• *Print System Architects (PSA)* whose focus points are the product evolution and the roadmap of printers are interested in the impact of the adapter on mechanical interfaces.

- Software integrators (SI) are interested in the integration aspects of the adapter software with printers and finishers.

- Software developers (SM) are interested in the design of the adapter software and modeling tools used in the project.

### **Functional Requirements:**

- FR\_1 The adapter software must be able to communicate with the printer using the generic protocol [input/output]

- FR\_2 The adapter software must be able to communicate with different finishers using their specific protocol [input/output]

- FR\_3 The adapter software must be able to perform message conversions based on the state machine/state machines [processing]

- FR\_4 The adapter software must be able to handle timing issues for messages based on the state machine/state machines [timing/synchronization]

- FR\_5 The adapter software should be able to implement power cycling feature in the future [general]

- FR\_6 The adapter software should be able to incorporate multiple finishers in the future [general]

- FR\_7 The adapter software should maintain a file regarding the finisher capabilities. The details of the file can be provided online or offline [data]

### **Platform Requirements:**

The prototype board and the test step were chosen to enable rapid prototyping of the adapter software. Hence, the adapter software was implemented in a prototype board with CPU capability which is overkill for running the adapter software. Driver software for electrical interfacing and transport layer stack were provided by Océ. The details of the prototype board are given in the Appendix B: "Océ prototype board specification".

#### **Process Requirements:**

These were the procedures followed like tools, programming languages in realization of the software. The one of the focus point of the thesis is the selection of the modeling approach. Section 4.4 contains the selection criteria for the modeling approach that explain the process requirements in a detailed manner.

#### **Non-functional Requirements:**

NFR\_1 Maintainability: The adapter software should be able to implement software download feature in the future.

NFR\_2 Robustness: The adapter software should be able to implement link check mechanism feature to maintain the link between a printer and the adapter.

NFR\_3 Extensibility: The architecture should give guidelines on handling different versions of the adapter software in the adapter and the printer interface software in the printer.

# 3.2 Conceptual View

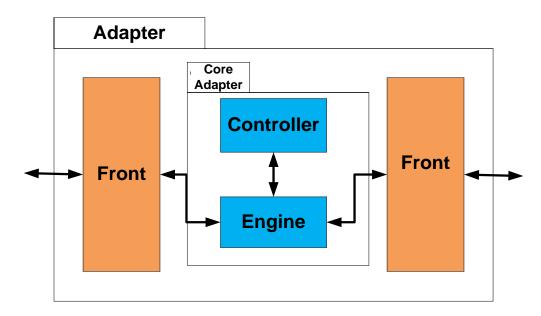

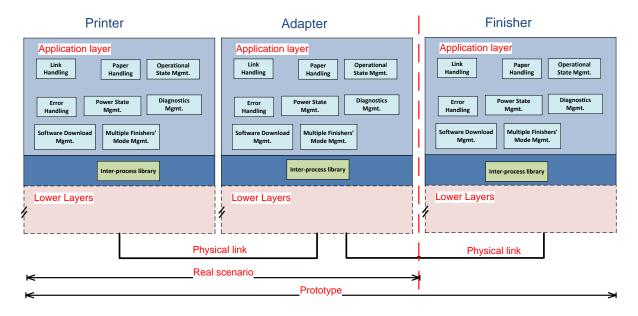

This view represents the black box view of the adapter software describing its context and the user's view. Figure 3.2.1 shows the conceptual of the adapter with its interfaces. The adapter interfaces a single printer with one or more finishers.

Figure 3.2.1: Conceptual view

The components and their interfaces are defined as follows:

#### **Components:**

### Printer:

- Printers are Océ wide format printers.

- The printer behaves like master sending instructions to finisher/finishers.

### Adapter:

- Adapter should support present and future wide format printers and finishers.

- Adapter converts the generic protocol to the specific protocol of the finisher connected to the adapter and vice-versa.

- As a design constraint, the adapter should not have any functional requirement for printer-finisher operations. The adapter behaves like a transparent device performing message conversions and does not tries to emulate the printer behavior.

### Finisher:

Finishers are Océ developed wide format finishers and wide format finishers from other companies.

#### Interfaces:

Printer-Adapter: Generic interface between an Océ wide format printer and the adapter. Adapter-Finisher: Specific interface between the adapter and finisher/finishers.

### 3.3 Logical View

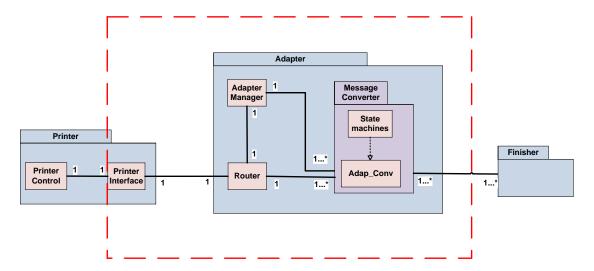

This view represents the white box view of the adapter software describing the top level design. Figure 3.3.1 shows the different packages with its interfaces and also classes within these packages. The dotted boundary shown in the figure is done to indicate the focus area of the architecture in the thesis.

Figure 3.3.1: Logical view

The different blocks: packages and classes are explained below:

#### Packages/Classes:

#### **Printer Control:**

- This module interacts with the printer interface module.

- This module decides a printer action based on the message from the printer interface module. This module acts as a proxy class interfacing printer interface with other modules of the printer.

#### Printer Interface:

- This module connects the printer with the adapter.

- This module handles exceptions made by the adapter.

#### Router:

- This module is present to support multiple finishers.

- This module performs routing of messages from the printer to a specific message converter or adapter manager based on the identifier present in the message.

#### Adapter Manager:

- This module interacts with the adapter hardware

- This module takes care of the non-functional adapter requirements like software download and link maintenance

#### Message Converter:

- Adap\_Conv module converts generic messages from the printer to specific messages of the finisher and vice-versa.

- The conversion is based on the state machine or state machines available