#### MASTER

Model-based design of systems running software defined radios

Waqas, U.

Award date: 2012

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# Model-based design of systems running software defined radios

Master's Thesis

August 2012

> EINDHOVEN UNIVERSITY OF TECHNOLOGY NXP SEMICONDUCTORS

### Abstract

Wireless communication has become an integral part of our everyday life. In order to meet the current requirements of wireless operators and technology providers, Software Defined Radios (SDRs) are used. SDR is a form of radio that performs the signal processing in software. The requirements include flexible design, upgrade and reuse of radios. In this thesis, we propose a model based design approach to develop SDRs. Specifically, we present constructs to model the digital baseband processing in an SDR. As a case study, we model a Digital Video Broadcasting Terrestrial (DVBT) decoder over a heterogeneous Multi Processor System-on-Chip (MPSoC) which is MARS.

A typical SDR may have data and reception dependent operations referred to as scenarios during its operation. These operations have varying resource requirements. We present constructs to model scenarios. Moreover, we identify the scenarios present in a DVBT decoder. SDRs usually have a high data rate that requires efficient implementation and dynamic memory management. In this thesis, we describe how to model one such implementation aspect, namely, packet pools. In a MPSoC, several masters accessing a shared slave may interfere with each other. In order to take this interference into account, we model the AXI based interconnect present in the MARS platform.

In this thesis, we propose a technique to reduce the complexity of an FSMSADF graph. This technique reduces the number of initial tokens and/or the number of actors present in an FSMSADF graph while preserving the timing behavior of the graph and decreasing the analysis time. For experimental evaluation of the constructs presented in this thesis, we developed a tracing framework and algorithms to compare traces generated from the models with the traces generated from the actual system. Collectively, these constructs contribute to the model based design of SDRs which in turn allows us to meet the requirements of wireless communication and technology providers.

### Acknowledgments

This thesis describes the work performed in a graduation project conducted at NXP Semiconductors in approximately seven months. The graduation would have been very difficult without inspiration, guidance and support from several people. I would like to express my gratitude to them.

The foremost, I would like to mention Sander Stuijk, my supervisor at TU/e, who introduced me to this project at NXP Semiconductors. During the tenure of the project, he has always been a source of motivation and guidance. His keen supervision increased the quality of the work performed and urged me to find better solutions. He helped me to realistically plan the project activities and make practical decisions. It has been a privilege to work with him.

I would like to thank Peter Kourzanov, my supervisor at NXP Semiconductors for several lengthy but fruitful discussions. I appreciate his valuable feedback on the tools and techniques developed in the project. He motivated me to go beyond the horizon and explore things further.

I appreciate the guidance from Artur Burchard on understanding the architecture of the MARS platform. His explanations clarified several architectural concepts. I would like to thank Hong Li for several discussions on the operation of a DVBT decoder. He always answered my questions on an urgent basis providing detailed explanations. I appreciate the support from David Riemens for explaining concepts related to the MARS SDK. I appreciate his efforts for arranging a MARS board and for setting it up.

I appreciate the coffee break discussions with Luuk Loeffen. He always provided food for thoughts. I appreciate suggestions from Sunil John for the tracing framework designed in the project. I would like to thank him for providing valuable feedback on my presentations. I would like to thank Ruxandra Bobiti and Salman Shafqat for proof reading this thesis and for cooking for me in the busy times during the project. Finally, I would like to appreciate the support from my family and friends. Without these contributions, it would have been more difficult to achieve the current form of the project.

### Contents

#### Contents

| 1        | Intr                               | Introduction 1                                                       |    |  |  |

|----------|------------------------------------|----------------------------------------------------------------------|----|--|--|

|          | 1.1                                | Radio: the past, present and future                                  | 1  |  |  |

|          | 1.2                                | Motivation                                                           | 2  |  |  |

|          | 1.3                                | Software defined radios                                              | 3  |  |  |

|          |                                    | 1.3.1 DVBT decoder                                                   | 4  |  |  |

|          | 1.4                                | Bus based systems-on-chip                                            | 6  |  |  |

|          |                                    | 1.4.1 Architecture of the MARS platform                              | 6  |  |  |

|          | 1.5                                | Model based design and challenges in designing SDRs $\ .\ .\ .\ .$ . | 8  |  |  |

|          | 1.6                                | Contributions                                                        | 9  |  |  |

|          | 1.7                                | Report overview                                                      | 9  |  |  |

| <b>2</b> | Ove                                | erview of the Design Approach                                        | 10 |  |  |

|          | 2.1                                | Goals                                                                | 10 |  |  |

|          | 2.2                                | Challenges                                                           | 11 |  |  |

|          | 2.3                                | Conclusion                                                           | 12 |  |  |

| 3 Data   |                                    | aflow Preliminaries                                                  | 13 |  |  |

|          | 3.1                                | Synchronous DataFlow Graphs                                          | 13 |  |  |

|          | 3.2                                | Finite State Machine based Scenario Aware DataFlow                   | 15 |  |  |

|          | 3.3                                | Conclusion                                                           | 16 |  |  |

| 4        | Modeling Software Defined Radios 1 |                                                                      |    |  |  |

|          | 4.1                                | Modeling digital baseband processing                                 | 17 |  |  |

|          | 4.2                                | Modeling the AXI interconnect                                        | 20 |  |  |

ii

|    | 4.3             | Bounding FSMSADF statespace                                         | 23        |  |

|----|-----------------|---------------------------------------------------------------------|-----------|--|

|    | 4.4             | Related work                                                        | 23        |  |

|    | 4.5             | Conclusion                                                          | 24        |  |

| 5  | Rec             | luction of FSMSADF Graphs                                           | <b>25</b> |  |

|    | 5.1             | Motivation                                                          | 25        |  |

|    | 5.2             | Reduction approach                                                  | 26        |  |

|    | 5.3             | Max-Plus representation of HSDF graphs                              | 27        |  |

|    | 5.4             | Reduction                                                           | 28        |  |

|    | 5.5             | Conversion to an HSDF graph                                         | 30        |  |

|    | 5.6             | Reduction of FSMSADF                                                | 32        |  |

|    | 5.7             | Related work                                                        | 32        |  |

|    | 5.8             | Conclusion                                                          | 33        |  |

| 6  | Tra             | ce Extraction                                                       | 34        |  |

|    | 6.1             | Motivation                                                          | 34        |  |

|    | 6.2             | Challenges                                                          | 35        |  |

|    | 6.3             | Architecture                                                        | 35        |  |

|    | 6.4             | Tracing API                                                         | 36        |  |

|    | 6.5             | Trace comparison                                                    | 37        |  |

|    | 6.6             | Conclusion                                                          | 37        |  |

| 7  | Cas             | e Study                                                             | 39        |  |

|    | 7.1             | SDF model of the DVBT decoder                                       | 39        |  |

|    | 7.2             | FSMSADF model of the DVBT decoder                                   | 43        |  |

|    | 7.3             | Early evaluation and improvements                                   | 45        |  |

|    | 7.4             | Bottlenecks in the approach and the model                           | 47        |  |

|    | 7.5             | Upper and lower bounds for the DVBT decoder                         | 49        |  |

|    | 7.6             | Comparison of the DVBT model trace with the system trace $\ldots$ . | 50        |  |

|    | 7.7             | Conclusion                                                          | 50        |  |

| 8  | Cor             | nclusion and Future Work                                            | 51        |  |

|    | 8.1             | Conclusion                                                          | 51        |  |

|    | 8.2             | Future work                                                         | 52        |  |

| Bi | Bibliography 54 |                                                                     |           |  |

| Α | Reduction of AXI models                    | 57        |

|---|--------------------------------------------|-----------|

| в | Modeling packet resizers in a DVBT decoder | <b>58</b> |

### CHAPTER 1

## Introduction

Over the last few decades, technology has influenced how we disseminate information. The invention of telegraph, telephone, radio and television has laid the foundations for modern day communications. With these advances in technology, communication got better, faster and more reliable. Modern day communication allows seamless connectivity, high transfer rates, reliable and secure transmission for both short range and distant communication.

Wired and wireless communication are two broad types of communication. In general, wired communication is faster and more reliable than wireless communication but facilitates fixed point communications only. Wireless communication is suitable for nomadic, mobile and distant communication. In the sequel, we refer to the devices that wirelessly communicate as *radios*. With the evolution of wireless communication, it gradually became an integral part of our everyday life. In the following section, significant inventions during the evolution of wireless communication are described. Section 1.2 presents the motivation behind this thesis. In Section 1.3 software defined radios are introduced. Section 1.4 introduces bus-based systems-on-chips. The contributions of this thesis are described in Section 1.6. In Section 1.7, the organization of this thesis is described.

#### 1.1 Radio: the past, present and future

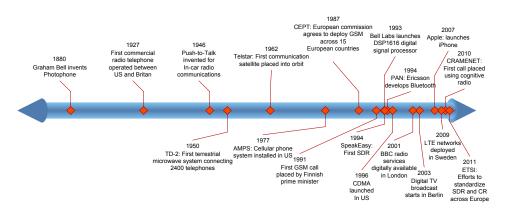

The *photophone* is considered as the first operational wireless communication device. Articulated sounds were transmitted using photophones between two points that were 200 meters apart. Increasing the range, improving the reliability and standardization were important objectives of the inventions succeeding the photophone. Figure 1.1 presents significant inventions during the evolution of wireless communication, focusing on scientific, commercial and public successes.

In 1927, it became possible to wirelessly communicate between the US and Britain. This marked a significant increase in the range of radio as well as it indicated the ease of access to the technology. In 1962 the placement of *Telstar* into orbit facilitated transatlantic reception of a television feed. From commercial to personal use, the radio was emerging and spreading across the globe as a key enabler of the kind of wireless communication

Figure 1.1: The evolution of radio over the last century.

man had ever dreamed of. The quality and coverage of wireless communication had a significant impact on the (commercial) success of radios. Advanced Mobile Phone System (APMS) was designed and deployed in US to provide better (compared to 0G systems) coverage and quality of wireless communication. GSM introduced digital circuit switching techniques in wireless communication that led to transmission of digital data along with articulated sounds. Eventually, in 1991, GSM became operational across Europe.

Wireless communication incorporates several signal processing techniques which make the connectivity possible. Different wireless communication standards perform the required signal processing differently. As the radio evolved; new standards emerged. It became infeasible to design a new integrated circuit to perform signal processing for every emerging standard. The *SpeakEasy* was the first radio in which the signal processing was performed in software (described in Section 1.3). The British Broadcast Company (BBC) started digital radio transmission in London in 2001. Similarly, digital TV transmission started in Berlin in 2003. Digital processing techniques were now an integral part of many wireless communication standards. *Cognitive radio*, a type of radio that is intelligent, is an active research topic in the field of wireless communication. A cognitive radio considers the user behavior and its environment during its operation. For example, it is able to sense the interference, the available standards and the carrier state in order to communicate. Software defined radios (SDRs) are key enablers of cognitive radios. With the standardization of cognitive and software defined radios, the wireless communication will enter an era where the radios are intelligent and efficient.

#### 1.2 Motivation

Wireless operators and the technology providers need to cope with an increasing demands for high data rates and enhanced quality of communication while reducing the cost of consumer products. Innovations and improvements in the technology increase the quality of wireless communication resulting in new wireless communication standards [AAG<sup>+</sup>11]. SDR brings in the flexibility to upgrade a device that implements an existing standard and the addition of new standards to a device, by downloading improved software to the device. Thus SDR enables an existing device to upgrade to a new standard (by reconfiguration), where in case of a complete hardware implementation, it would have been required to redesign the hardware.

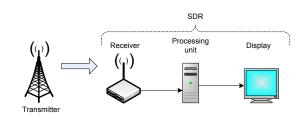

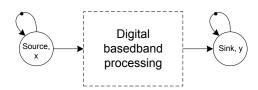

Figure 1.2: An example of an SDR.

Model based design allows to evaluate the design choices without implementing the system (completely). Model based design of SDRs will facilitate designers to analyze implementations of SDRs during the early design phases. Moreover, for existing systems, model based design allows to identify potential improvements by early evaluation of design decisions. For example, it allows to assess the feasibility of adding more applications to the system, analyze the resource utilization and identification of bottlenecks present in the system. These improvements either reduce the system cost or allow effective use of the existing resources contributing to fulfillment of the requirements of the wireless operators and the technology providers. In this thesis, we provide constructs to model SDRs over bus based system on chips thus contributing to model based design of SDRs.

#### **1.3** Software defined radios

Software defined radio (SDR) is a type of wireless communication that implements all or part of the signal processing techniques in software. Figure 1.2 presents an example of an SDR based digital television (TV). The *transmitter* broadcasts the TV signal which is received by the *receiver*. The receiver digitizes the signal and passes it to the *processing unit*. The *processing unit* performs *digital baseband processing* which generally consists of 1) *filtration* 2) (*de*)modulation and (*de*)coding. As a result of the digital baseband processing, the TV feed is extracted and displayed.

Figure 1.2 is a primitive example of an SDR. An SDR based system usually has 3 components: 1) an analog-digital front end, 2) a processing unit and 3) an input-output subsystem. The front end serves as an interface facilitating wireless communication. The processing unit performs the signal processing. The type of input-output device depends on the application for which the SDR is designed. For instance, in case of a visual feed, the output device is a display terminal. In case of an audio feed the output device is typically a speaker. However, the input-output subsystem can be any other application specific system e.g a fax machine. Moreover, according to the application requirements, the number of front ends, processing units and the input-output subsystems may vary. In the sequel we refer to this component based model of SDRs as the *conceptual model of SDRs*.

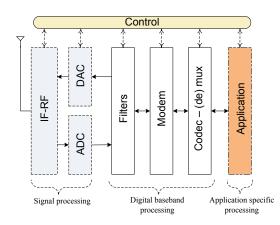

Figure 1.3 illustrates the layered processing in a typical SDR [BHM<sup>+</sup>05]. The first layer, radio frequency - intermediate frequency (RF-IF) is a front end. The incoming signal is converted to a stream of digitized data by the analog-to-digital converter (ADC). The digital stream is passed to the digital baseband processing layers. The filters usually remove unwanted frequencies and suppress noise present in the signal. The filtered data is then demodulated by the modem. Subsequently, the data stream is decoded by the codec and handed over to the application for further processing. In case of a transmission, the sequence starts in the reverse order from the application layer towards

Figure 1.3: The architecture of a crude SDR [BHM<sup>+</sup>05].

the transceiver as is also illustrated in Figure 1.3.

#### 1.3.1 DVBT decoder

Digital Video Broadcasting Terrestrial (DVBT) [DVBa] is an international standard for broadcasting of digital television feeds. Since its inception, DVBT has become one of the most widely accepted digital video broadcasting standards [DVBb]. In this section we introduce the operation of a typical DVBT decoder. However, for theoretical details about the DVBT standard, we refer the reader to [DVBa].

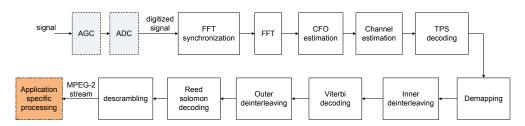

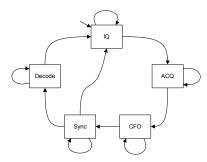

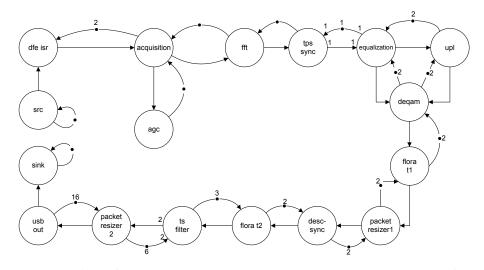

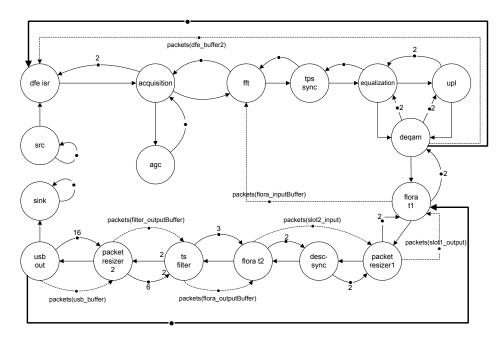

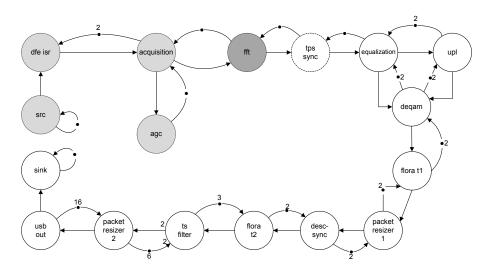

Figure 1.4 presents the block diagram of a typical DVBT decoder. The incoming signal, that is received by the signal processing component (dashed blocks), is processed by the Automatic Gain Control (AGC) that adjusts the signal (e.g amplitude) according to the signal strength. This adjusted signal is then digitized by the Analog-to-Digital Converter (ADC). The digitized signal is input to the digital baseband processing (non-dashed blocks). FFT synchronization is the first operation performed in the digital baseband processing layer of a typical DVBT decoder. Based on the input, this operation computes the transmitter characteristics, for example, size of the FFT window, fractional part of the Carrier Frequency Offset (CFO) (i.e. the crystal clock difference between the transmitter and receiver) and the OFDM symbol timing. The input data along with the estimated characteristics is used to perform a Fast Fourier Transform (FFT) that converts the input signal from the time domain to the frequency domain. Using the converted signal, the CFO operation computes the integer part of the CFO. A DVBT transmitter can operate in many transmission modes [DVBa]. Moreover, due to the possible existence of multiple paths of the signal traverses between the transmitter and receiver, and the mobility of the transmitter or receiver, the so called *Doppler compen*sation and channel equalization needs to be performed. Collectively, these operations are referred to as *channel estimation*.

In order to extract the modulation and channel coding configuration, Transmission Parameter Signaling (TPS) bits are encoded by the transmitter in the OFDM symbols. The *TPS decoding* operation decodes these TPS bits. In an OFDM symbol, the data carriers contain the data bits that are mapped using Quadrature Amplitude Modulation (QAM) or Quadrature Phase-Shift Keying (QPSK). The QAM/QPSK demapping operation demodulates these data bits which are interleaved by the transmitter in order to support *long burst error correction*. The *Inner deinterleaver* operation deinterleaves

Figure 1.4: Block diagram of a typical DVBT decoder [YWC, DVBa].

Figure 1.5: FSM representing scenarios present in a typical DVBT decoder.

the data bits that are convolutionally decoded using *Viterbi decoding*. The bit stream obtained after Viterbi decoding is rearranged as bytes by the *Outer deinterleaver*. This byte stream is further processed by the *Reed Solomon decoding* and subsequently *Descrambled*. Finally, the transport stream (multiplexed MPEG-2 stream) is handed over to the application for application specific processing.

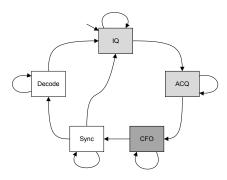

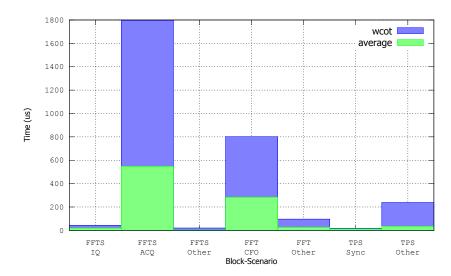

The DVBT decoder implemented on the MARS platform operates in five scenarios during its execution<sup>1</sup>. Figure 1.5 presents these scenarios along with their transitions. Initially, the decoder is in the IQ scenario. In this scenario the decoder estimates the so called In-phase and Quadrature-phase (IQ) imbalance to obtain the channel response. This estimation is performed by the FFT synchronization block. Note that in each scenario, the DVBT decoder may require many OFDM symbols (depending on the carrier state) to perform its computation and switch to the next scenario. Once the IQ balance is estimated, the DVBT decoder switches to the ACQ scenario. In this scenario, the Acquisition (ACQ) is performed to find the OFDM symbol boundary, the FFTwindow size used by the transmitter, and the cyclic prefix length. ACQ is performed by the FFT synchronization block. Once all parameters are found, the DVBT decoder switches to the next scenario i.e. CFO. In this scenario, the Carrier Frequency Offset (CFO) is computed by the CFO block. Once CFO is estimated, the DVBT decoder switches to the SYNC scenario. In this scenario, the DVBT decoder estimates the so called time tracking parameter e.g. common phase estimation, frequency tracking etc. This estimation is performed by the channel estimation and TPS decoding blocks. Once the parameter estimation is complete, the DVBT decoder switches to the decode scenario in which the demapping and subsequent blocks start decoding the incoming MPEG stream.

$<sup>^{1}</sup>$ The terms 'scenarios' and 'operating modes' are sometimes used interchangeably. However, we reserve the term 'operating mode' exclusively for the set of transmission modes used in the DVBT transceiver. The term 'scenario' is used to refer to the distinct execution behaviors when executing in a particular operating mode.

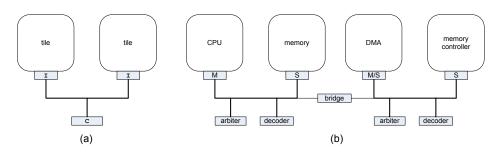

Figure 1.6: An example of a bus based SoC.

#### 1.4 Bus based systems-on-chip

A *bus* is a group of wires used to transfer data between several components present in a system. Due to its simplicity and low cost, bus based communication is one of the most widely used communication architecture in embedded systems.

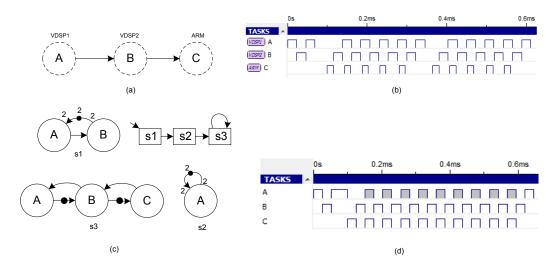

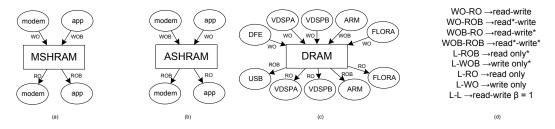

Figure 1.6 (a) presents a bus based Multi Processor System-on-Chip (MPSoC) template. This template consists of 3 components, a *tile*, an *interface* (denoted as I) and a *control component* (denoted by C). The interface and the control components facilitate connectivity between tiles. Figure 1.6 (b) provides an example of a SoC based on the template. It consists of 4 tiles. The CPU tile consists of a central processing unit. The CPU tile is connected to the bus through the master interface (M). A *master* is an interface that initiates the transfers over the bus. On the other hand, a *slave* interface (S) only responds to the incoming requests and cannot initiate transfers. For example, the *memory* tile is connected to the bus through the slave interface. A hybrid interface is a component that can act both as a master or as a slave. For example, the *DMA* tile is connect two buses. It acts as a hybrid interface connected on each bus. An *arbiter* is a control component that decides who gets access to the bus to initiate transfers to its intended destination.

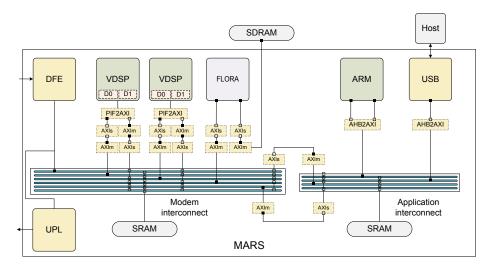

#### 1.4.1 Architecture of the MARS platform

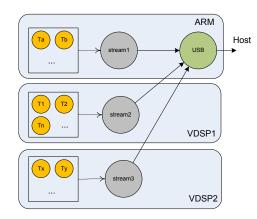

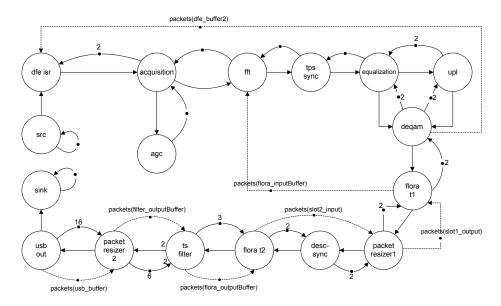

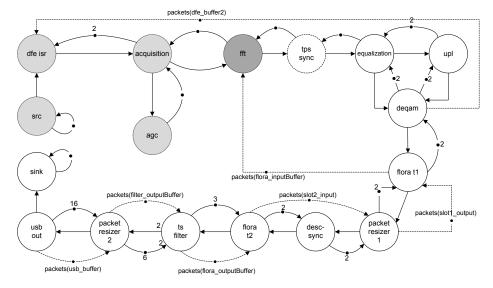

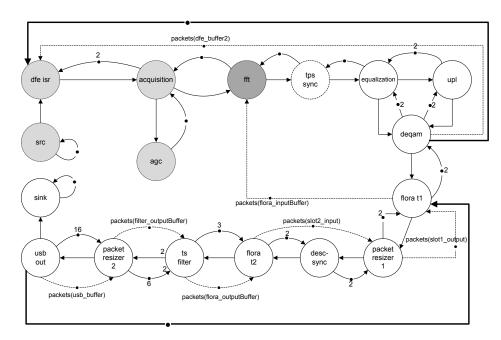

Multi Application Radio System (MARS) [MAR] is a bus based multiprocessor systemon-chip (MPSoC). Figure 1.7 presents the hardware architecture of the MARS platform. It consists of a digital front-end (DFE) that receives the data provided by an external source (transmitter). In the MARS platform, there is an uplink that is capable to transmit the data to an external receiver. Both the DFE and the uplink facilitate the front end of the conceptual model of the SDRs (see Figure 1.3).

There are two vector digital signal processors (VDSPs) present in the MARS platform. These processors facilitate the *filtration* and the *modem* layers of the digital baseband processing (presented in Section 1.3). Moreover, these processors have two local memories (D0 and D1). The MARS platform contains a hardware accelerator i.e. FLORA to accelerate the *decoding* layer of the digital baseband processing. The ARM processor present in the MARS platform is a general purpose processor that configures the VDSPs and the FLORA accelerator. The ARM processor, the VDSPs and the FLORA accelerator constitute the processing unit of the conceptual model of SDRs.

Figure 1.7: The architecture of the MARS platform.

There are two static random access memories (SRAMs) present in the MARS platform that are used to store program instructions and data. Moreover, the MARS platform also connects to an external synchronous dynamic random access memory (SDRAM). The output of the MARS platform, i.e. a processed signal, is accessed by the host system through the USB interface. In terms of the conceptual model of SDRs, the USB interface acts as an interface to the input-output subsystem.

The components described so far were tiles. These tiles are connected using several protocols from the Advanced Microcontroller Bus Architecture (AMBA) protocol suite and the Processor InterFace (PIF) bus. A bus based interconnect groups several buses together and provides standard interfaces to them. The MARS platform contains 2 64-bit Advanced Extensible Interface (AXI) bus based interconnects from the AMBA 3.0 protocol suite. One interconnect is responsible to transfer data across the modem subsystem that comprises of the DFE, uplink, VDSPs, SRAM and the FLORA tiles. There are 6 buses present in the modem interconnect. The VDSPs have PIF based interfaces that connect to the modem interconnect using AXI2PIF and AXI master-slave converters. The application subsystem consists of ARM, SRAM and USB tiles. The application interconnect consists of 4 buses. Both ARM and USB tiles are connected through the AHB2AXI converters. The application and the modem interconnect are connected with each other using an AXI bridge that comprises of 2 pairs of AXI master-slave converters.

There is only a single master present on a bus present in the application or the modem interconnect. The master ports connected to the bus are depicted as black squares where the slave ports are depicted as white squares. Possibly, a slave could be connected to several buses. For example, the SRAM slave present in the modem subsystem is connected to 5 buses which in turn requires arbitration. An AXI interconnect contains address decoder and arbitres (one for every shared slave).

The components present in the platform influence the behavior of an application running on the platform. For example, the communication between VDSP1 and SRAM (in the modem subsystem) will interfere with the communication of VDSP2 with the same SRAM. In order to consider this interference in the timing analysis, the communication over the interconnect needs to be modeled explicitly. We model the communication over the AXI interconnect in this thesis as described in Section 4.2.

#### 1.5 Model based design and challenges in designing SDRs

Early evaluation of the choices made during the design of SDRs is a non-trivial task. We present several such choices and motivate how model based design facilitates early evaluation of these choices. Furthermore, we exemplify the challenges in implementing a DVBT decoder over the MARS platform.

**System complexity and abstraction.** SDRs usually consist of several functional blocks or components interacting with each other. SDRs are complex due to this interaction. During early design phases, these interactions are usually not completely known and require abstraction. Moreover, as the design proceeds, the abstractions are elaborated allowing to incrementally decide on these design choices. Model based design facilitates such an incremental approach by modeling relevant aspects of the system and abstracting from irrelevant details. We exemplify such aspects present in the DVBT decoder in the case study presented in Chapter 7.

**Splitting computation.** The functional blocks present in an SDR are implemented as tasks. There exist several choices when distributing (splitting) the computation present in the blocks over these tasks. For example, for the DVBT decoder, one possible split is to have a task implementing the computation performed in a functional block or another choice is to split the computation present in a functional block across multiple tasks. Implementing each design choice is a time consuming and error prone process. Due to the abstraction, model based design reduces the time consumed in evaluation of these splits.

**Communication choices.** The split of computation influences the communication overhead which in turn affects the timing behavior. For example, tasks mapped on different processing units communicate through the interconnect and interfere with each other. This interference must be considered while taking these design choices. We present, in Chapter 4, constructs to model the AXI interconnect.

**Optimizations.** There are several optimizations possible while implementing SDRs. If known at an early design phase, these optimizations must be taken into consideration. One such optimization for the DVBT decoder is as follows.

The input to a DVBT decoder is an OFDM symbol. The size of each OFDM symbol depends on the mode of transmission. For example, for 8K, 64QAM, 1/4 guard rate mode the OFDM symbol size is 10240 bytes. For the same mode, approximately 872 symbols are received per second. Moreover, the input OFDM symbol is accessed by many blocks. For example, all blocks till the demapping block in the decoder chain (see Figure 1.4) access the input OFDM symbol as well as the outputs of the predecessor blocks in order to generate their outputs. As soon as the demapping has been performed, the OFDM symbol is no longer required. The large size of the OFDM symbol and high data rate make it challenging to implement a DVBT decoder as an embedded system and appeals for efficient (space and time) memory management.

The incoming OFDM symbols are analogous to packets of data. A *packet pool* is a collection of preallocated packets that are used to fulfill the memory requirements of an application dynamically. Many embedded kernels like OpenComRTOS [OPE], Nexos [BR09] and SoD [BB04] offer packet pools. Packet pools fall into the category of *region based memory management* [TT97]. In order to reduce the overhead of dynamic memory

management, region based memory management requires that the packets are released (freed) in the same order as they are acquired. This invariant prohibits the possibility of producing so called *holes* in the memory which in turn requires *defragmentation* for efficient memory management. This assumption typically holds in a DVBT decoder implementation as the OFDM symbols are processed in the digital baseband processing layer in FIFO order. Moreover, the overhead of copying data from block to block is usually reduced by incorporating *copy by reference* i.e. sending the address of the packet instead of copying data. Hence the memory requirements of a DVBT decoder can be fulfilled using packet pools over low cost of dynamic memory management.

**Model validation.** Model validation assesses how near the model is to the actual system. Furthermore, it identifies improvements in a model. In order to validate a model with its implementation, execution of the system and the model needs to be compared. Implementing such a comparison is non-trivial as it requires to record the execution of the system. Due to scarcity of resources in embedded platforms, implementing such a recording is difficult (see Section 6.2). In Chapter 6 we present a tracing framework that facilitates model validation.

In this thesis, we demonstrate model based design focusing to model the aspects presented above. Moreover, Chapter 7 presents a case study that evaluates the model based design approach presented in this thesis on a DVBT decoder which is implemented on the MARS platform.

#### **1.6** Contributions

We contribute the following to the model based design of SDRs:

- Constructs to model digital baseband processing in software defined radios over bus based MPSoCs.

- Constructs to model AXI interconnect in the presence of shared slaves.

- Constructs to model packet pools.

- Implementation of a tracing framework to trace an SDR application running on the MARS platform.

- An evaluation on the accuracy of an SDR modeled with the FSMSADF MoC compared to an actual implementation of the application on the MARS platform.

- A technique to reduce the number of initial tokens and actors present in an FSM-SADF graph.

#### 1.7 Report overview

An introduction to the evolution of the wireless communication, SDRs and bus based MPSoCs is presented in this chapter. In Chapter 2 the problem addressed in this thesis is described. Chapter 3 presents the preliminaries to the model of computations used in this thesis. In Chapter 4, constructs to model digital baseband processing in software defined radios is presented. Chapter 5 presents a technique to reduce FSMSADF graphs. Chapter 6 presents the tracing framework. In Chapter 7 the constructs presented in this thesis are evaluated by modeling a DVBT decoder implementation over the MARS platform. Finally, Chapter 8 concludes this thesis and proposes future work.

### Chapter 2

# Overview of the Design Approach

Modern day wireless communication aims to provide high data rates to realize enhanced quality while reducing the cost of consumer products. As described in Section 1.2, it is desired to increase the quality of communication while reducing the cost and time to market of wireless consumer products. Model based design allows to analyze these products. Section 1.5 describes challenges faced during design of SDRs. In this chapter, the problem addressed in this thesis is described in more detail. Section 2.1 lists the goals of this thesis that contribute to a model based design approach for SDRs. Section 2.2 identifies the challenges involved in achieving these goals. Finally, Section 2.3 concludes this chapter.

#### 2.1 Goals

Model based design steers the design process. It starts with *modeling the application* i.e. its functionality, *modeling the underlying* platform on which the application runs and *modeling the mapping* of the application to the resources offered by the platform. The results obtained from the timing analysis performed on the model facilitate making design choices. In this thesis we contribute to model based design of SDRs as follows:

- Provide constructs to model and analyze bus based SoCs. These constructs must model the components present in a SoC which influence the behavior of an application running on the SoC. These constructs must model the processing as well as the communication in the SoC.

- Model the mapping of an SDR on the resources offered by a bus-based SoC. The analysis must capture the associated trade offs which occur in different mappings.

- Provide constructs to model and analyze SDRs using measures like throughput, latency and operation in bounded memory. The modeling constructs must allow to capture the (relevant) behavior and implementation details of SDRs.

• Verify the outcomes of the modeling and analysis by comparing the system traces to the model traces.

The models, analysis, mapping and trace comparison should be performed automatically. This will require using an analysis toolkit, possibly extending it and implementing trace extraction on the platform. Collectively, these goals will contribute to the model based design of SDRs.

#### 2.2 Challenges

Modeling SDRs and platforms which facilitate implementation of SDRs have several challenges. Specifically, the following challenges are identified:

- The digital baseband processing layer present in an SDR typically has data and carrier state dependent behavior leading to several scenarios. For example initialization, carrier parameter extraction and decoding. Moreover, the computation and hence the time required to perform the computation in each scenario differs. This difference must be considered during the analysis of the temporal properties e.g throughput. One may suggest to only consider the worst case execution scenario during the analysis which turns out to be pessimistic. Explicitly considering the scenarios will reduce this pessimism.

- Due to the high data rate and large packet sizes, the implementation of the digital baseband processing layer is usually optimized. One such optimization is the use of packet pools (see section 1.3.1). There are 3 properties of packet pools that influence the behavior of the implementation. These are 1) the size of the packet pool i.e. the number of packets present in it 2) the location where a packet pool resides i.e. local or remote memory in a SoC and 3) the amount of bytes accessed from each packet. Modeling these properties is a challenging task as the packet pool might be shared among many tasks and may be located on a shared memory. Moreover, mapping of packet pools to one of the available memories may have several trade offs. For example, mapping a packet pool to a remote memory (accessed over the bridge) will incur more latency than accessing the memory directly (without using the bridge).

- In a bus based SoC, simultaneous communication between pairs of tiles may cause interference. Modeling this interference requires modeling of the components present in the interconnect which is a challenging task. In order to model this interference in the MARS platform, the AXI based interconnect and the converters need to be modeled. For example, the packet pool might reside on a shared memory and two tiles accessing (same or different) packets from a packet pool will cause interference. In addition, the interconnect model must capture the trade offs present in accessing remote versus local memories.

- Validation of the designed model is a must. The model must be compared to the implementation in order to access the precision of the model<sup>1</sup>. This might require extensions to the analysis toolkit and to the SDR itself. For example, for

$<sup>^{1}</sup>$ The mentioned approach requires implementation of the system to be available (which is usually not available in early design phases). Model based design does not require the implementation to be available. However, in presence of such a implementation, it is desired to evaluate the model with the implementation

the DVBT decoder and the MARS platform it is required to record the events occurring in the system in order to compare them with the events present in the model. This recording and comparison will allow validation and be performed by development of a tracing framework. Efficient (space and time) design of such a tracing framework for an embedded system is a challenging task.

#### 2.3 Conclusion

The problem addressed in this thesis was described in this chapter. The first problem addressed is to provide constructs to model SDRs. There are several challenges present in providing such constructs like modeling the scenarios and the memory managers used in the platform. Moreover, the communication architecture needs to be modeled in order to analyze the communication overhead. Finally, once the models are developed; their accuracy must be verified.

### Chapter 3

# **Dataflow Preliminaries**

The dataflow model of computation is often used to model digital baseband processing and other types of streaming applications [Gei09, SGB06, Stu07, SGM<sup>+</sup>11]. A comparison of dataflow MoCs is described in [PRE] and is not repeated in this thesis. In this chapter, we formally introduce two dataflow model of computations, namely, *Synchronous DataFlow* (SDF) [LM87], which is introduced in Section 3.1 and *Finite State Machine based Scenario Aware DataFlow* (FSM-SADF) [SGTB11], which is introduced in Section 3.2.

#### 3.1 Synchronous DataFlow Graphs

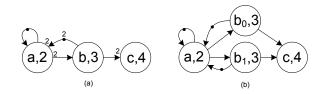

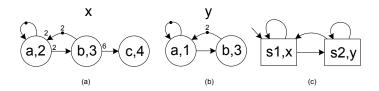

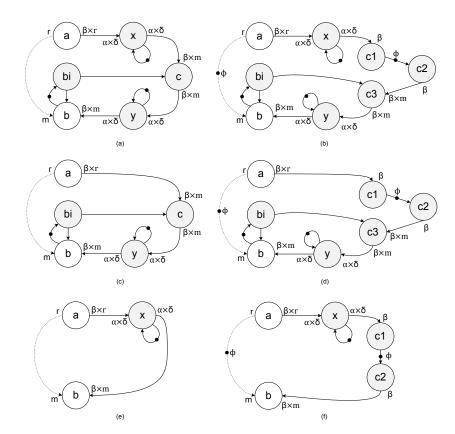

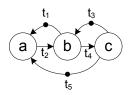

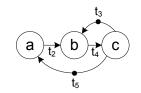

SDF is a dataflow model of computation [LM87]. It consists of actors connected through dependency edges. The actors models atomic execution of computation. The edges model data or control dependencies between actors. Let the set A denote the set of actors present in the SDF graph. Let the set D denote the set of dependencies between the actors in the SDF graph. Let  $\mathbb{N}$  denote the set of natural numbers and  $\mathbb{N}_0$  denote the set of natural numbers including 0. For illustration, we use the example SDF graph shown in Figure 3.1.

There are three actors present in Figure 3.1(a), namely, a, b and c. An actor is represented as a *circle* with its name inside the circle. For the example SDF graph the set of actors  $A = \{a, b, c\}$ .

**Definition 3.1:** (DEPENDENCY EDGE) A dependency edge  $d \in D$  is a tuple (*srcActor*, *destActor*, *srcRate*, *dstRate*, *initialTokens*) where *srcActor*  $\in$  *A* is the source actor of *d* denoted by *srcActor*(*d*), *dstActor*  $\in$  *A* is the destination actor of *d* denoted by *dstActor*(*d*), *srcRate*  $\in$   $\mathbb{N}$  is the number of data items (tokens) produced by the *srcActor*(*d*) after an execution, *dstRate*  $\in$   $\mathbb{N}$  is the number of data items (tokens) required by the *dstActor*(*d*) in order to execute and *initialTokens*  $\in$   $\mathbb{N}_0$  is the number of tokens denoted by *initialTokens*(*d*) initially present on *d*.  $\diamond$

There are four dependencies present in the SDF graph specified in Figure 3.1 (a). A dependency is pictorially represented as a *directed edge* from a source actor to a des-

Figure 3.1: An example of an SDF graph (a) and its HSDF graph (b).

tination actor. For example, actor c is dependent on actor b which is denoted by a directed edge from b to c. Actor a produces two tokens, on the dependency edge from a to b upon completion of its execution (source rate) which is denoted by the number on the start of the edge. Actor c requires one token in order to fire (destination rate). Initial tokens are presented as a *dot* on a directed edge. For example, there are two initial tokens present on the directed edge from b to a. Notice that rates and initial token counts equal to one are omitted for clarity and we follow this convention in the sequel. The set of dependencies D for the example SDF graph is  $D = \{(a, a, 1, 1, 1), (a, b, 2, 1, 0), (b, a, 1, 2, 2), (b, c, 6, 1, 0)\}$ . Each actor in an SDF graph has an execution time written next to its name (after a comma inside the circle). For example, in Figure 3.1 (a) , actor a has execution time of two time units, b has three time units and c has 4 time units.

**Definition 3.2:** (SDF) A synchronous dataflow (SDF) graph G is tuple  $(A, D, \Upsilon)$  where A is the set of actors present in the SDF, D is the set of dependencies between actors present in the SDF graph and  $\Upsilon : A \to \mathbb{N}_0$  is a function that determines the execution time  $e \in \mathbb{N}_0$  for a given actor  $a \in A$ .

**Definition 3.3:** (HSDF) A homogeneous synchronous dataflow (HSDF) graph is an SDF graph  $(A,D,\Upsilon)$  in which all dependencies  $d \in D$  have unit source and destination rates i.e. srcRate(d) = dstRate(d) = 1.

Figure 3.1(b) shows an equivalent HSDF graph [LM87] for the SDF graph shown in Figure 3.1(a). This graph has been obtained using the conversion algorithm presented in [LM87]. It consists of four actors, namely, a,  $b_0$ ,  $b_1$  and c. There are 7 dependencies present in the HSDF graph. As specified in Definition 3.3, the source and destination rates of the dependencies are one. Algorithms to convert an SDF graph to an equivalent HSDF graph are presented in [SB09] and [Gei09]. We discuss the pros and cons of each algorithm in detail in the following chapter. As compared to the SDF shown in Figure 3.1(a), the number of actors and dependencies has increased in the HSDF. This increase is exponential in worst-case.

**Definition 3.4:** (REPETITION VECTOR AND CONSISTENCY) A repetition vector  $\gamma$  of an SDF graph G(A, D) is a function  $\gamma : A \to \mathbb{N}_0$  such that for every dependency  $d = (s, d, p, q, n) \in D$  it holds that  $\gamma(s) \times p = \gamma(q) \times q$ . An SDF graph G is consistent if it holds that  $\forall a \in A \ \gamma(a) > 0$ .

The repetition vector for the actors [a,b,c] present in the SDF graph shown in Figure 3.1(a) is [1,2,1]. A non-consistent SDF graph is not useful in practice as it either deadlocks (due to insufficient tokens in a cyclic dependency) or it needs an infinite amount of memory. In this thesis, we verify that every proposed SDF graph is consistent.

**Definition 3.5:** (ITERATION) An iteration I of an SDF graph G(A, D) is a collection of actor executions of the SDF graph in which an actor  $a \in A$  fires exactly  $\gamma(a)$  times.

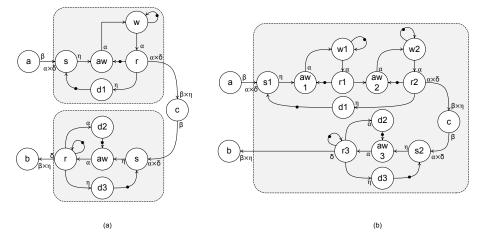

Figure 3.2: An example FSMSADF graph with SDF graphs (a) and (b) corresponding to each scenario and an FSM (c).

Intuitively, the repetition vector specifies when an *iteration* of the graph is completed. An iteration for the example SDF graph completes when the actor a fires one time, actor b fires two times and actor c fires one time.

#### 3.2 Finite State Machine based Scenario Aware DataFlow

The Finite State Machine based Scenario Aware Dataflow (FSMSADF) [SGTB11] is a dataflow model of commutation. Figure 3.2 presents an example FSMSADF. It consists of two scenarios x and y. Each scenario in an FSMSADF graph contains a corresponding SDF graph. The SDF graphs for the scenarios x and y are shown in Figure 3.2 (a) and (b) respectively. Moreover, the transitions between the scenarios are specified in the FSM Figure 3.2(c). In many cases the name of a scenario and the name of a corresponding state is same. Due to this similarity, the scenario name may not be shown in the FSM. In the sequel this convention is followed.

**Definition 3.6:** (SCENARIO FSM) A scenario FSM F on a set of scenarios S is a tuple  $(Q,q_0,\delta,\Sigma)$  where Q is a finite set of states,  $q_0 \in Q$  is the initial state,  $\delta \subseteq Q \times Q$  is a transition relation between the states present in the FSM and  $\Sigma : Q \to S$  is a function that maps a state to its corresponding scenario.  $\diamond$

The FSM specified in Figure 3.2 consists of a set of states  $Q = \{s1, s2\}$  with initial state  $q_0 = s1$ . There are four transitions present in the FSM. The transition relation  $\delta = \{(s1, s1), (s1, s2), (s2, s1), (s2, s2)\}$ . The function  $\Sigma$  maps  $s1 \to x$  and  $s2 \to y$ .

**Definition 3.7:** (FSMSADF) An FSMSADF graph  $G_F$  is a tuple (S, F) where S is set of SDF graphs corresponding to each scenario and F is a scenario FSM.

Figure 3.2 presents an FSMSADF with 2 scenarios, namely, x and y and a scenario FSM with two states s1 and s2. The SDF graphs corresponding to scenario x and y are specified in Figure 3.2 (a) and (b) respectively. Note that the number of initial tokens present in the scenario graphs must be equal. In the sequel we only present the tokens required to model an application. However, the number of initial tokens in the SDF graphs is made same as follows. First the maximum number of initial tokens present in the SDF graphs in an FSMSADF is computed. Secondly, to each SDF graph the difference between the number of initial tokens in the SDF graph and the maximum computed in the first step is computed. Finally, initial tokens, equal to the difference computed in the second step, are added to a self edge on a dummy actor. This dummy actor has an execution time equal to 0 and is connected to an arbitrary actor.

#### 3.3 Conclusion

An introduction to SDF and FSMSADF MoCs is presented in this chapter. The actors and dependencies between them are formally defined in this chapter. In Chapter 4 the streaming tasks present in the digital baseband processing layer are modeled as actors and data passing across different functional blocks is modeled as dependencies. The FSMSADF MoC facilitates modeling of dynamism present in an SDR. In Chapter 7, the dynamism present in the DVBT decoder is modeled using the FSMSADF MoC.

### CHAPTER 4

# Modeling Software Defined Radios

Software defined radios (SDRs) were introduced in Section 1.3. This chapter describes constructs to model SDRs. Section 4.1 describes generic constructs to model the computation present in the digital baseband processing layer of an SDR. Once the computation is modeled, usually in the next design phase, the communication is taken into account. Section 4.2 presents constructs to model an AXI-based interconnect. The FSMSADF MoC facilitates *scenarios* which model the dynamism present in an SDR. The statespace of an FSMSADF graph [SGTB11] can be large leading to long run times of the analysis algorithms. In Section 4.3 we present a technique to limit the statespace of an FSMSADF graph (which may potentially introduce inaccuracies in the analysis result). Section 4.4 discusses the work related to modeling SDRs. Finally, Section 4.5 concludes this chapter.

#### 4.1 Modeling digital baseband processing

The digital baseband processing layer is implemented as a set of streaming tasks that process data in a chained fashion. We model each task present in the system as an SDF actor. The streamed operation of these tasks give rise to data dependencies. The tasks and dependencies in the implementation of the DVBT decoder are presented in Chapter 7. In this section we present generic constructs to model operations usually performed in SDRs.

Modeling a periodic source and sink. The incoming signal is periodically broadcasted by a transmitter in the form of a symbol. This symbol is received by the front end. In Figure 4.1, a construct to model a periodic arrival of symbols is shown. The actor *Source* models the periodic arrival of incoming data. Each firing of this actor produces a symbol (i.e. a token in SDF terminology). The execution time of this actor is equal to the period of the incoming symbol. Every input symbol is processed by the digital baseband processing layer of an SDR (shown as a block in Figure 4.1). The signal processing layer processes the input data and the output is handed over to the application for application specific processing (see Section 1.3 for details of layered processing).

Figure 4.1: Modeling periodic source and sink typically present in SDRs.

Figure 4.2: Operations supported on a packet pool (a) and a construct to model the size of the packet pool (b).

We model this hand over with a *Sink* actor. Note that the size of the output symbol is usually different from the size of the input symbol. For example, in the DVBT decoder, the size of the input symbol is equal to the size of the OFDM symbol specified by the DVBT specification [DVBa] and the size of the output packet is 16 KB<sup>1</sup>. Moreover, the processed data is typically handed over to the application through an USB interface and in that case the execution time of the *Sink* actor is equal to the time required by the USB interface to transmit a single packet of data.

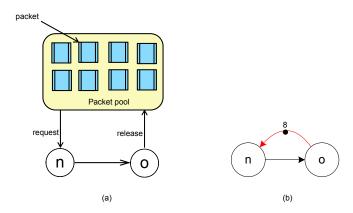

**Modeling packet pools.** Packet pools facilitate copy by reference which optimizes the sharing of incoming symbols across tasks in an SDR. In this section we present constructs to model packet pools. There are 3 properties of a packet pool which influence the execution of task that manipulates packets from a packet pool. These properties are 1) number of packets in the packet pool, 2) the size of each packet and 3) the memory where the packet pool resides. In this section we present SDF constructs to model the first property. The constructs to model second and third property are presented in Section 4.2.

Figure 4.2(a) illustrates possible operations on a packet pool. The two operations allowed on a packet pool are 1) *request* a packet and 2) *release* a packet. Figure 4.2(b) presents a construct to model the size of the packet pool. Note that we assume that the requester and releaser tasks are known at design time and are fixed in a scenario of an application. Moreover, we assume that there is only one requester and releaser task for a packet pool. Modeling multiple requester and releaser tasks for a packet pool is proposed as future work.

Modeling the packet resizer. During processing, a symbol is processed by several

$<sup>^1\</sup>mathrm{The}$  output of the DVBT decoder is a MPEG stream transmitted in the form of packets. On the MARS platform, the MPEG stream is transmitted over USB where the size of a USB packet is 16 KB. However, this size may vary from one platform to another platform.

Figure 4.3: Modeling packet resizers present in the system.

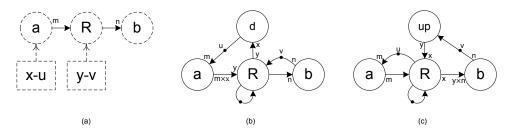

tasks present in the digital baseband processing layer. The input/output sizes of these intermediate symbols typically vary. For example, in case of a DVBT decoder, the size of the output of *Viterbi* decoding equals to 4536 bytes (for 64QAM, 8K FFT window size and 1/4 guard interval [DVBa]). This output is processed by the *Reed Solomon* decoder that needs the size of the input packet to be equal to 208 bytes. This size conversion requires packet resizers.

Figure 4.3 presents constructs to model packet resizers when region based memory management is used. Figure 4.3 (a) presents a task graph consisting of 3 tasks (shown in dashed circles), namely, a, b and R and 2 packet pools (shown in dotted rectangles). Task a requests m packet(s), where  $m \ge 1$ , from the packet pool x-u where x is the size of each packet and u is the number of packets present in the packet pool. Once task a gets m packet(s), it fills the data into them and passes them to the resizer R. The resizer is responsible to resize the packets from size of x to y. For that purpose, task R requests n packet(s), where  $n \ge 1$ , from the packet pool y-v. After resizing the packet(s), task R passes the packets to task b.

Modeling the packet resizers becomes non-trivial when the resizers use packet pools which have less packets than required. It either blocks the sender or the receiver task. For example, assume that the resizer R in Figure 4.3(a) resizes from x to y where x equals 1, u equals 6, y equals 2 and v equals 2. In this case task a blocks after sending the first packet. The resizer needs 3 packets to resize and send the data to b, however, there are only 2 packets present in packet pool y-v. The resizer holds the incoming packet from a (and a remains blocked) until task b returns a packet packet back to the pool. The constructs which model packet resizers must take this blocking due to unavailability of packets into account.

Packet resizers can resize for both cases i.e. when x > y and when y > x. Figure 4.3(b) presents an SDF model for the resizer when x > y. It models the packet resizing between actor a and b. The actors R and d collectively model the packet resizing and requests to the packet pool. The actor a fires  $m \times x$  tokens (analogous to m packets having size x). The resizer reads in y tokens and passes them to actor b. The task R in (a) buffers the additional data. This buffering is modeled in (b) by the dependency from actor a to R. The actor d models the requests from a packet pool x-u. The dependency from d to a models the packets present in the packet pool. Initially, there are u packets in the packet pool. Afterwards, for each x bytes received from R, one token is added to the dependency which is analogous to one packet. Similarly, the dependency from actor b to actor R models the packets in the packet pool y-v.

Figure 4.3(c) presents an SDF model for the resizer when x < y. The dependency from actor R to a models the packet requests to the packet pool x-u. The dependency from actor b to up models the packet requests from the packet pool y-v. While resizing, the task R buffers the additional data. This buffering is modeled by the dependency from

Figure 4.4: AXI write burst (a) with its signal waveform (b) and read burst (c) with its signal waveform (d).

actor R to b. Note that these SDF models will deadlock in case when m > u or n > v. This means that the packet pools have less packets than the actors request. Clearly, the system is not operational in that case.

#### 4.2 Modeling the AXI interconnect

The SDF and the FSMSADF MoC assume that there is no communication overhead. In a real system there is however an overhead when communicating data between processors and/or memories. This overhead is due to the time taken by the interconnect to transfer data. We explicitly model this communication overhead. In an MPSoC, multiple masters accessing a shared slave interfere with each other. This interference influences the execution of a task. In this section, we present constructs to model the communication overhead and the interference over the AXI interconnect. In addition, these constructs will model the two properties of the packet pool (see Section 4.1) that are 1) size of a packet present and 2) the location where the packets reside. We model the communication between two tasks (read and write) and insert the model between them according to the interconnects that are accessed and the memory mapping. In particular, we model an AMBA3 AXI interconnect [AXI].

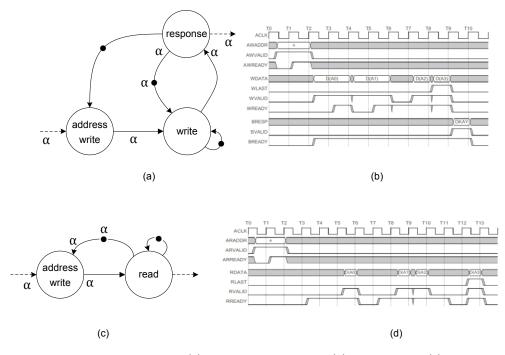

AXI interconnect facilitates *read* and *write* bursts for communication. Figure 4.4 illustrates the operation of read/write bursts (for a detailed discussion of AXI interconnect the reader is referred to [AXI]). An AXI write operation (Figure 4.4 (b)) is initiated by the master by writing the address on the AWADDR register followed by transmission of data in the form of burst (burst length of size 4). The slave confirms the reception of the burst by sending an acknowledge response. This is done by putting the BRESP signal high. Note that the address, data and acknowledgment transmission are governed

Figure 4.5: AXI read-write model (a), read-write model with initial tokens (b), write only model (c), write only model with initial tokens (d), read only model (e) and read only model with initial tokens (f).

by VALID and READY handshakes. Figure 4.4(a) presents an SDF construct to model an AXI write operation (dotted arrows indicate dependencies to source and destination actors). It consists of 3 actors, namely, *address write*, *write* and *response*. The parameter  $\alpha$  denotes the burst length with which the AXI interconnect is configured (4 in our examples). Moreover, for the MARS platform, the execution times for *address write*, *write* and *response* actors is, in worst case, 8 ns (as each operation requires 2 clock cycles in worst case<sup>2</sup>). Similarly, the AXI read burst is presented in Figure 4.4 (d). The read burst does not have a response when the burst ends. The SDF graph to model an AXI read is presented in Figure 4.4 (c). The AXI read model has one actor less compared to the AXI write model as there is no acknowledgment in the read burst but it has VALID/READY handshakes (see Figure 4.4(b) and Figure 4.4(d)).

Assume an SDF graph in which an actor a is connected to an actor b through a dependency edge. Actor a is the source of this edge and has a production rate of r tokens. Actor b, the destination of the edge, has a consumption rate of m tokens. Assume further that the memory used to implement the edge between a and b is located in separate memory which the processors on which a and b are running need to access using the AXI interconnect. This situation models the case in which a source task writes to a memory and a destination task reads it. Figure 4.5 presents parametrized

$<sup>^{2}</sup>$ In the MARS platform, the interconnect is clocked at 300MHz with each tick 3.333ns apart. For worst case analysis, we round the ticks to 4ns. However, the models are generic and the time taken for an operation can be specified according to the clock in an arbitrary system.

SDF constructs to model such a transmission of data. The actors colored gray are which model the communication between the source and the destination actors. These constructs are obtained by combining the AXI read/write models shown in Figure 4.4. The number of initial tokens in the combined model was reduced using the reduction technique described in Chapter 5. For instance, the combined (but not reduced model) contains  $2 \times \alpha + 3$  initial tokens. The reduced model (Figure 4.5 (a)) contains only 3 initial tokens.

The parameters used in the model are listed in Table 4.1. The parameter r denotes the rate of the source actor. Similarly, m denotes the read rate of the destination actor.  $\phi$  denotes the number of initial tokens present on a dependency edge between a source and a destination actor. The burst length of an AXI interconnect is denoted by  $\alpha$ . The sharing degree determines, in worst case, the number of masters accessing a shared slave simultaneously and is denoted by  $\kappa$ . This sharing degree is computed for each dependency by analyzing the memory mappings. This degree is used to compute the execution times of actors.  $\beta$  denotes the size of a packet used to communicate. The word size of the interconnect is denoted by  $\delta$ . The parameter  $t_c$  determines the time taken by 2 clock cycles.

| Parameter | Description                   |

|-----------|-------------------------------|

| r         | source write rate             |

| m         | destination read rate         |

| α         | AXI burst length              |

| β         | packet size                   |

| δ         | word size of the interconnect |

| $\phi$    | number of initial tokens      |

| $t_c$     | time for 2 clock cycles       |

| $\kappa$  | sharing degree                |

Table 4.1: Parameters in the AXI read-write models.

Figure 4.5(a) presents an AXI read-write model. It assumes that the source writes the data (modeled by actor x) to the memory and the destination reads the data from this memory (modeled with actor y). This assumption generally holds for SDF actors. Actor c models the completion of transmission of data. Actor bi models the read request from the destination actor to the memory controller to initiate the memory transfer. It ensures that the task which is modeled by actor b is ready to receive incoming data. The execution times of actors bi and c are 0. The execution time of x is computed as  $\Upsilon(x) = 2 \times t_c \times \kappa + t_c \times \alpha \times \kappa$ . The  $2 \times t_c \times \kappa$  represents the time required for address write and the acknowledgments. This formula assumes that in worst case all masters interfere in the transmission. The  $t_c \times \alpha \times \kappa$  represents the time required by the interconnect to perform the write burst. Note that if the write operation is using the bridge then the execution time for the actor x is  $\Upsilon(x) = 2 \times t_c \times \kappa + 2 \times t_c \times \alpha \times \kappa$ . In a write burst over the bridge the data is written twice during the transmission between the master and the memory slave. Thus the time required to perform a write over the bridge doubles.

Similarly, the execution time for the read actor y is computed as  $\Upsilon(y) = t_c \times \kappa + t_c \times \alpha \times \kappa$ . In case the read is over the bridge then the execution time is  $\Upsilon(y) = t_c \times \kappa + 2 \times t_c \times \alpha \times \kappa$ . Figure 4.5(b) presents a variant of the model presented in 4.5(a) which models the initial tokens present on the elaborated buffer (shown in dotted arrows). The actors c1, c2and c3 model the initiation of a read request from the task modeled by actor b. These actors have an execution time equal to 0. Note that it is possible to model the initiation

Figure 4.6: Bounding scenario transitions in an FSMSADF graph.

with a single actor (instead of three) but this will make the number of initial tokens present in the construct dependent on other construct parameters. We will show during the case study that reducing the initial tokens reduces the time required by the analysis algorithms. Therefore we prefer to have a model with fewer tokens instead of a model with fewer actors.

Figure 4.5 (c) and (e) presents models for situations when the transmission is write or read only respectively with their variants modeling initial tokens presented in 4.5(d) and (f). The execution times of the tasks present are computed in the similar way as described for 4.5(a) and (b). Note that the read only and write only constructs model the incoming stream from the DFE (write only) and the outgoing stream over the USB interface (read only).

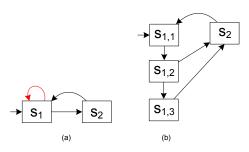

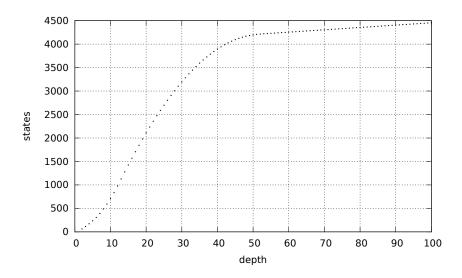

#### 4.3 Bounding FSMSADF statespace

The FSM present in an FSMSADF models the scenario transitions in an application. In the FSMSADF MoC, it is allowed to infinitely stay in a state. Figure 4.6(a) presents an FSM in which the graph can stay in state  $s_1$  infinitely. It is often desired to limit the stay of a state in itself. For example, to incorporate designer feedback to the model. Moreover, the FSMSADF statespace may be too large due to store the complete statespace in the memory (which is required by the analysis algorithms). We bound the transitions by expanding the FSM and removing the self loops on the bounded state. For example, Figure 4.6(b) presents an FSM in which the number of times the FSM stays in state  $s_1$ , denoted by x, is bounded by  $2 \le x \le 3$ . This bounding is performed by replacing  $s_1$  with 3 states,  $s_{1,1}$ ,  $s_{1,2}$  and  $s_{1,3}$  and allowing transitions from  $s_{1,i}$  to  $s_2$  only when  $a \le i \le b$  where a and b are the lower and upper bounds respectively. The bounding of transitions for each state increases the number of states in the FSM to b - a + 1. We define *depth* as the number of states expanded when removing a self edge. For example, the depth for  $s_1$  in Figure 4.6(b) is 2. The effect of bounding the statespace for the DVBT model is described in Section 7.4.

#### 4.4 Related work

Modeling SDRs using dataflow MoCs is studied in [Yan09, BBL08, SGM<sup>+</sup>11]. A Mode Controlled DataFlow (MCDF) graph is used to model a DVBT decoder in [Yan09]. The modeling in [Yan09] aims to find a feasible schedule for an MCDF graph satisfying the real time requirements of a DVBT decoder. An FSMSADF based model of the Long Term Evolution (LTE) SDR is presented in [SGM<sup>+</sup>11]. It models the dynamism present in an LTE baseband processing tasks. However, [Yan09, BBL08, SGM<sup>+</sup>11] do not provide constructs to model typical operations like periodic sources and sinks, packet pools and the communication over an interconnect. These constructs are essential to model the system level operation of an SDR. Analysis of suitable MoCs to model SDRs is described in [BBL08]. It concludes that statically scheduled dataflow graphs pessimistically model SDRs. This conclusion coincides with the results of our experiments performed in Chapter 7. Moreover, it discusses applicability of other MoCs to model SDRs. A detailed comparison of dataflow MoCs is described in [PRE], based on which, the FSMSADF MoC is proposed in this thesis to model the dynamism present in an SDR.

The Fractional Rate Dataflow (FRDF) extension to SDF is described in [OH04]. This extension allows to have fractional read and write rates on a dependency. FRDF closely relates to the packet resizers described in Section 4.1. However, FRDF requires an extension to model packet pools. As shown in an example in Section 4.1, the packet resizers may block actors in the case when the number of packets in a packet pool is less than the required number of packets. This blocking influences the timing analysis, thus is essential to be modeled.

The AXI models described in Section 4.2 are inspired from the interconnect models discussed in [JSS<sup>+</sup>11, ASSG08, Stu07]. [JSS<sup>+</sup>11] describes a parametrized SDF graph to model communication between two tiles present in an MPSoC. It models buffering, serialization and deserialization of packets in the interconnect present in the MAMPS platform [Kum09]. However, [JSS<sup>+</sup>11] assumes homogeneous interconnect i.e. the communication overhead is the same for all tiles<sup>3</sup>. The AXI models described in Section 4.2 facilitate different models for different types of communications in an MPSoC i.e. when the communication is heterogeneous. An SDF graph to model bi-rate communication service provided by an interconnect is presented in [ASSG08]. Using bi-rate communication model provides tighter estimates for timing requirements. However, [ASSG08] does not specify how to combine multiple bi-rate SDF graphs to model multiple masters present in an MPSoC.

#### 4.5 Conclusion

In this chapter, constructs to model SDRs were presented. The tasks present in the digital baseband processing layer are modeled as actors and the data passing between the tasks are modeled as dependencies between the actors. Usually, SDRs consist of periodic source/sinks, packet resizers and packet pools. Constructs to model such operations in an SDR were presented. Moreover, constructs to model the AXI interconnect were presented in this chapter. These constructs are evaluated in Chapter 7.

$<sup>^{3}</sup>$ The communication model can be used with different parameters for different types of communication. In order to estimate the interference caused by multiple masters (to compute parameters) the models require extensions.

Chapter 5

# **Reduction of FSMSADF Graphs**

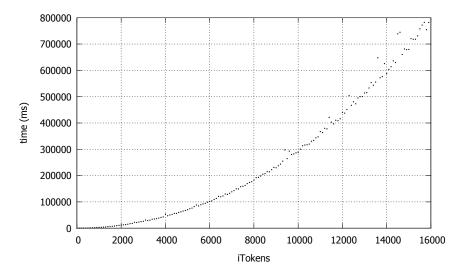

The Finite State Machine based Scenario Aware DataFlow (FSMSADF) model of computation (MoC) was introduced in Chapter 3. A dependency edge between actors is *redundant* if removing the edge does not change the start times of the actors present in an application. In this chapter we focus on reducing an FSMSADF graph by removing redundant dependencies and actors present in an FSMSADF. Removal of redundant dependencies may lead to removal of initial tokens which in turn reduces time taken by the analysis algorithms (see Section 7.4 for details).

In the following section, we motivate the reduction of FSMSADF graphs. Section 5.2 describes the reduction approach. Section 5.3 introduces the Max-Plus algebra [BCOQ92] which is used in the reduction technique. In Section 5.4 the reduction approach itself is described. Section 5.5 presents an algorithm to convert the simplified Max-Plus matrix to an HSDF graph. In Section 5.6 the reduction approach is extended to reduce FSM-SADF graphs. Section 5.7 describes work related to the reduction technique. Finally, Section 5.8 concludes this chapter.

#### 5.1 Motivation

It is desirable to have intuitive and simple dataflow models. Models near to the concept are intuitive. Simpler models capture the same behavior but require less analysis time and effort. The technique proposed in this chapter reduces the number of initial tokens present in an FSMSADF graph while preserving the timing behavior of an application.

Figure 5.1 presents examples of a model with the same throughput but varying number of initial tokens and actors. In Figure 5.1(a) an SDF model for an AXI *write* burst is described (this model is discussed in detail in Section 4.2). The actor a models the address write, c models a write and b models the write response sent back by the slave.  $\alpha$  models the burst length of the AXI interconnect.

Figure 5.1(b) presents an equivalent model, in terms of throughput, to Figure 5.1(a) but it has two actors a and v compared to three actors in Figure 5.1(a). The number of dependencies and initial tokens has also reduced from five to two and from three to one

Figure 5.1: The reduction approach (d) and illustrative SDF graphs (a, b, c).

Figure 5.2: An illustrative HSDF graph.

respectively. The SDG graph shown in Figure 5.1(b) abstracts from the AXI write and just account for the time required to perform writes (hence the throughput is equal) or in other words it clusters  $\alpha$  writes and groups the time needed with the time required to write the response. To ensure that the timing behavior of the actors in the resulting graph is identical to the original graph, v has an execution time equal to  $\alpha \times \Upsilon(c) + \Upsilon(b)$ where  $\Upsilon(b)$  and  $\Upsilon(c)$  denotes the execution times of actors b and c in Figure 5.1(a). The SDF graph presented in Figure 5.1(c) has equal throughput as Figure 5.1(a) and Figure 5.1(b). It has only one actor with a dependency to itself. The execution time of this actor is equal to  $\Upsilon(a) + \alpha \times \Upsilon(c) + \Upsilon(b)$  where  $\Upsilon(a)$ ,  $\Upsilon(b)$  and  $\Upsilon(c)$  denote the execution times of actors a, b and c in Figure 5.1(a).

Clearly, we preserve the throughput of the SDF graphs shown in Figure 5.1(a), Figure 5.1(b) and Figure 5.1(c) but we lose the buffer requirements and the applicable analysis techniques (buffer throughput trade off [Stu07]). The technique proposed in this chapter preserves the throughput as well as the timing behavior of an application. The technique aims to reduce the number of initial tokens present in an FSMSADF graph preserving the start times of actors present in the FSMSADF graph. In the sequel, we refer to this technique as *reduction*.

#### 5.2 Reduction approach

The overall approach of the reduction technique is presented in Figure 5.1(d). An FSMSADF is composed of an FSM which models the transitions of the system between *scenarios* and an SDF graph for each *scenario*. We simplify the SDF graphs present in the FSMSADF by converting the SDF graphs to equivalent HSDF graphs and then simplifying the HSDF graphs while preserving the schedule of the SDF graphs (In case an actor is removed, the remaining actors have the same schedule which may have different execution times). We focus to reduce the number of initial tokens present in the model in order to reduce the analysis time. The reduced HSDF graphs are used to create a reduced FSMSADF graph.

The reduction technique described in this chapter requires the SDF graphs present in a FSMSADF to be converted to an equivalent HSDF. Any arbitrary SDF can be

Figure 5.3: An illustrative HSDF graph showing redundant dependencies.

converted to an equivalent HSDF as specified in [LM87, SB09]. However, the conversion may lead to an exponential increase in the number of actors present in the HSDF graph compared to the SDF graph. Moreover, [Gei09] presents a Max-Plus based SDF to HSDF conversion technique, which, in many cases shows a smaller increase in the number of actors present in the HSDF. For our reduction technique, any SDF to HSDF conversion technique suffices. In this chapter, we assume that the SDF graph to HSDF is converted using any of the well known methods [LM87, Gei09]. The HSDF graph is converted to its Max-Plus representation as described in the following section.

#### 5.3 Max-Plus representation of HSDF graphs