| MASTER                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------|

| Synchronous dataflow graph (SDFG) modeling and performance analysis of multiprocesso NoC based system on chip (SoC) |

|                                                                                                                     |

|                                                                                                                     |

| Hassoun, M.                                                                                                         |

| Award date: 2009                                                                                                    |

|                                                                                                                     |

| Link to publication                                                                                                 |

|                                                                                                                     |

|                                                                                                                     |

|                                                                                                                     |

#### Disclaimer

Discaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

## TECHNISCHE UNIVERSITEIT EINDHOVEN

Department of Mathematics and Computer Science

### Master's thesis

Synchronous Dataflow Graph (SDFG) Modeling and Performance Analysis of Multiprocessor NoC Based System on Chip (SoC)

> by Maissa Hassoun

> > Committee:

prof. dr. ir. J. J. Lukkien (TU/e) dr.ir. M. C. W. Geilen (TU/e) ir. J. Boonstra (NXP Semiconductors)

Eindhoven / High Tech Campus December, 2008

## Abstract

Design of systems-on-chip (SoCs) for modern consumer electronic devices is getting more and more complexer with the advancing semiconductors technology. Many software and hardware intellectual property components (IP cores) are integrated on a single sub-micron chip. Communication between these large numbers of cores in modern SoC is realized by Network-on-Chip (NoC). NoC became the paradigm for designing scalable SoC and is common in the implementation of SoC for many application areas like real time multimedia applications. These applications share resources on-chip and often share off-chip memory with real-time requirements, therefore the NoC needs to provide performance guarantees (throughput and latency) to fulfil the performance constraints of these realtime applications. Tooling for analyzing the performance of NoC based SoC are still in the area of research and development. In this thesis we introduce a method to model a NoC based SoC for a multimedia application by constructing a Synchronous Dataflow Graph (SDFG) model. We analyze the throughput of the constructed model, make trade-off between throughput and buffer size, and compute latency. We apply the method on a video decoder H.263 and analyse its performance. We improve the performance results further by applying the Latency-Rate (LR) analysis to the shared memory controller. We show the impact of of the arbitration schemes on the latency computation and modeling in general. Our method in modeling and analyzing the performance of NoC based SoC is independent of the scheduling algorithm and platform architecture.

#### **General Terms:**

Modeling, Performance analysis

#### Key words:

SoC, NoC, SDF, WCET, Latency, Throughput, Arbitration

## Acknowledgments

I would like to take the opportunity to thank all who have supported me with my master thesis at the TU/e and NXP Semiconductors, especially to Joep Boonstra for his supervision and feedback during the progress meetings, to my colleagues Henk Hamoen and Joost Laarakkers for offering me this assignment and for their support.

Many thanks to Sander Stuik for his input in the initial phase of this master thesis and to Johan Lukkien for taking a place in my graduation commission and for his feedback and suggestions on the presented work.

My appreciation and gratitude to my gradation supervisor at the TU/e, Marc Geilen, for the opportunity to do my master thesis under his guidance. His suggestions, feedback and support have been of great value throughout the graduation period and writing of this thesis.

Finally, warmest thank to my family abroad for their moral support, and to my husband and best friend Kazik for being my greatest support during those years of study. Without his encouragement and confidence in me I would not have been able to accomplish this work.

## Contents

| 1        | Intr         | roduction                                             | 1       |  |  |  |  |  |  |

|----------|--------------|-------------------------------------------------------|---------|--|--|--|--|--|--|

|          | 1.1          | Purpose of the assignment                             | 1       |  |  |  |  |  |  |

|          | 1.2          | Related work                                          | 2       |  |  |  |  |  |  |

|          | 1.3          | Structure of this thesis                              | 2       |  |  |  |  |  |  |

| <b>2</b> | Uni          | versal Network Interconnect on-Chip (U-NIC)           | 3       |  |  |  |  |  |  |

|          | 2.1          | Performance                                           | 5       |  |  |  |  |  |  |

|          | 2.2          | Quality of service                                    | 5       |  |  |  |  |  |  |

|          | 2.3          | Arbitration                                           | 5       |  |  |  |  |  |  |

|          |              | 2.3.1 Time-division-multiple-access (TDMA) scheduling | 6       |  |  |  |  |  |  |

|          |              | 2.3.2 Round-robin (RR) scheduling                     | 8       |  |  |  |  |  |  |

|          |              | 2.3.3 Weighted round-robin (WRR) scheduling           | 9       |  |  |  |  |  |  |

|          |              | 2.3.4 Priority-based scheduling                       | 10      |  |  |  |  |  |  |

|          | 2.4          | Buffering                                             | 11      |  |  |  |  |  |  |

| 3        | Syn          | achronous Data Flow Graph (SDFG)                      | 13      |  |  |  |  |  |  |

| _        | 3.1          | 1                                                     | 13      |  |  |  |  |  |  |

|          | 3.2          |                                                       | 14      |  |  |  |  |  |  |

| 4        | SDI          | $F^3$ Design flow and tooling                         | 19      |  |  |  |  |  |  |

| _        | 4.1          | , e                                                   | 21      |  |  |  |  |  |  |

|          | 4.2          |                                                       | 21      |  |  |  |  |  |  |

|          |              |                                                       | 21      |  |  |  |  |  |  |

|          |              | 8 I                                                   | 22      |  |  |  |  |  |  |

| 5        | Mot          | thod for modeling NoC based SoC                       | 25      |  |  |  |  |  |  |

| J        | 5.1          | 8                                                     | 26      |  |  |  |  |  |  |

|          | $5.1 \\ 5.2$ | Application model                                     | 27      |  |  |  |  |  |  |

|          | 5.2 $5.3$    | * *                                                   | 28      |  |  |  |  |  |  |

|          | 5.4          | Memory model                                          |         |  |  |  |  |  |  |

|          | 5.4 $5.5$    |                                                       |         |  |  |  |  |  |  |

|          | 5.5          |                                                       | 30      |  |  |  |  |  |  |

|          |              | 11 9                                                  | 30      |  |  |  |  |  |  |

|          |              | • • • • • • • • • • • • • • • • • • • •               | 31      |  |  |  |  |  |  |

|          |              | o.o.o for take specification                          | $o_{T}$ |  |  |  |  |  |  |

iv CONTENTS

|                  |           | 5.5.4 Minimum buffer allocation                                  | 31  |

|------------------|-----------|------------------------------------------------------------------|-----|

|                  | 5.6       | Place in a design flow                                           | 32  |

| 6                | H26       | 3 Video Decoder Case Study                                       | 35  |

|                  | 6.1       | Model H.263 video decoder                                        | 35  |

|                  | 6.2       | Model U-NIC baseline                                             | 37  |

|                  | 6.3       | SDFG model of the H.263 SoC                                      | 38  |

|                  |           | 6.3.1 Application communication pattern through the interconnect | 38  |

|                  |           | 6.3.2 Model construction                                         | 39  |

|                  |           | 6.3.3 Worst Case Execution Time assignment                       | 43  |

| 7                | Exp       | perimental results                                               | 51  |

|                  | $7.1^{-}$ | Throughput analysis                                              | 51  |

|                  | 7.2       | Critical cycle                                                   | 51  |

|                  | 7.3       | Latency analysis                                                 | 52  |

| 8                | Late      | ency-Rate SDFG model                                             | 55  |

|                  | 8.1       | Latency-rate server                                              | 55  |

|                  | 8.2       | Memory controller LR model                                       | 56  |

|                  | 8.3       | DDR SDRAM preliminaries                                          | 58  |

|                  | 8.4       | Request path through U-NIC to memory controller                  | 59  |

| 9                | H26       | 33 Video Decoder Case Study - Revisited                          | 61  |

|                  | 9.1       | Improved SDFG model for H263 video decoder                       | 61  |

|                  | 9.2       | Performance analysis results                                     | 63  |

| 10               | Sun       | nmary and conclusion                                             | 67  |

| 11               | Pra       | ctical Guide SDF3                                                | 69  |

|                  | 11.1      | Tool Installation                                                | 69  |

|                  | 11.2      | SDFG to XML Transformation                                       | 69  |

|                  |           | Graph Consistency                                                | 70  |

|                  |           | Throughput Analysis                                              | 71  |

|                  | 11.5      | Latency Analysis                                                 | 71  |

| $\mathbf{A}_{1}$ | ppen      | dix 1: XML file for initial SDFG model                           | 73  |

| $\mathbf{A}_{1}$ | ppen      | dix 2: XML file for improved SDFG model                          | 87  |

| $\mathbf{R}$     | efere     | nces                                                             | 102 |

|                  |           |                                                                  |     |

## Chapter 1

## Introduction

NXP Semiconductors (former Philips Semiconductors) is developing a state of the art network-on-chip known as: Universal Network Interconnect on-Chip (U-NIC) which will replace the legacy interconnect (dedicated point-to-point signal wires, shared buses, or segmented buses with bridges) in the design of future SoC for multimedia and automotive applications.

U-NIC needs to provide performance guarantees for the real-time applications that will be integrated in the future SoC.

## 1.1 Purpose of the assignment

Systems-on-chip (SoC) are composed of multiple processing elements or IP cores (e.g. in a multimedia SoC the processing elements represents the application's code segments) that interconnect through communication elements (e.g. network-on-chip). A challenging aspect in the design of SoC is to guarantee that the SoC fulfills the application's hard real-time requirements and that sufficient bandwidth is offered by the interconnect (NoC) to each of the processing elements at all times as required. In order to configure the network and evaluate the performance of the SoC, there is a need for an adequate tooling to perform these tasks at the design time. The purpose of this assignment is to provide a method to configure and analyse the performance of multimedia applications when mapped to NoC-based SoC which helps the SoC designers to map, schedule and analyse the performance of a multimedia NoC based SoC at the design time.

The main contribution in this report is a method to construct an SDFG model for U-NIC based multimedia SoC (U-NIC interconnect, a multimedia application mapped to U-NIC platform and an external memory controller) and analyzing the performance of the SoC based on the SDFG Design Flow and Tooling SDF<sup>3</sup> [26]. Our method fits in a NoC design flow which consists of iterative steps to configure and analyse the performance of a network based on a given application, network topology and performance constraints. The steps will be repeated until the performance evaluation fulfills the applications constraints. Our method provides worst-case performance guarantees since it requires that upper bounds

on the latency (Worst Case Execution Times) are known upfront for each of the processing elements as well as the the network components and the shared memory.

## 1.2 Related work

Available design flows and tools such as SDFG-based  $SDF^3$  (SDFG For Free) [26] and UMARS [19] provide solutions for NoC generation and performance analysis at design time. UMARS requires that time-division-multiple-access (TDMA) time-slots are allocated on the network to guarantee that the application's constraints are met. The same perquisite applies to the  $SDF^3$  design flow. If the network architecture can fulfil this requirement then either of these design flows can be used with minor modifications. However, this limiting factor makes these design flow unsuited for the U-NIC based SoC design since U-NIC architecture that is studied in this report does not implement TDMA time-slot allocation. Our method doesn't put any limitations on the network architecture, however it requires that the latency at the network elements are known. This will be discussed in greater details in the next chapters.

### 1.3 Structure of this thesis

This report is organized as follows: chapter 2 provides a general introduction to NXP U-NIC interconnect and arbitration schemes. Chapter 3 describes the structure of the SDFG and provides related definitions and notions. Chapter 4 gives an overview of the SDF<sup>3</sup> design flow, tooling and analysis algorithms with illustration on the differences between the proposed platform in [26] and U-NIC platform. Chapter 5 introduces the method for modeling a SoC in SDFG. Chapter 6 provides details on the performed experiment on a multimedia application (H.263) mapped onto U-NIC based SoC. Chapter 7 gives the results of the performance analyses applied to the case study. Chapter 8 proposes a memory controller model based on a combination of network calculus and dataflow analyses. Chapter 9 proposes an improved model of the H.263 case study and performance results. Chapter 10 provides summary and conclusions with recommendations for future work. Chapter 11 provides a guide for tool installation and running the analysis algorithms.

## Chapter 2

# Universal Network Interconnect on-Chip (U-NIC)

In this chapter we provide a general overview of U-NIC interconnect architecture and components. Additionally, we give some preliminaries on network-on-chip (NoC) arbitration and performance analysis that are relevant to the scope of this assignment.

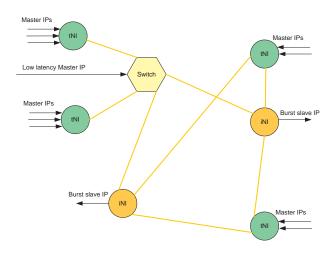

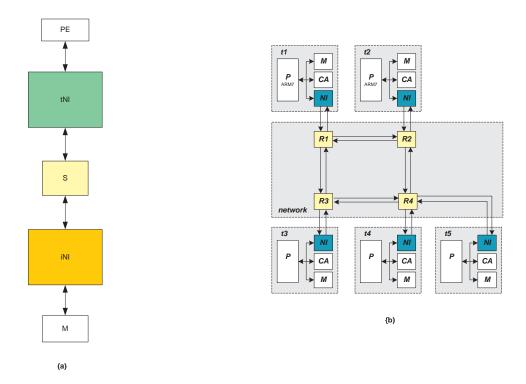

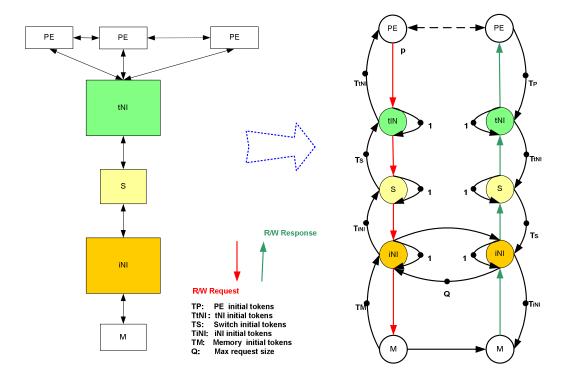

U-NIC is a high performance on-chip interconnect that will gradually replace legacy interconnects in future NXP systems-on-chip (SoCs). Figure 2.1 shows U-NIC topology that consists of network interfaces (NIs) on the boundary of the network and switches within the network. There are two types of network interfaces: target (tNI) which allows the master IP (processing element) to initiate a transaction request on the network; and initiator (iNI) which allows the slave IP, typically an off-chip shared memory controller, to respond to the transactions on the network. U-NIC supports connection of IP devices with AXI [7], AHB [4], DTL [5], MTL [6] interfaces.

U-NIC supports 32-bit memory-mapped data transactions. If the transmitted data is not 32-bit wide, data-width conversion to 32-bit (U-NIC word) takes place at the tNI, similarly conversion from 32-bit to different data-width occurs at the iNI.

U-NIC is a layered, packet based protocol, based on an OSI stack model [31]. The basic idea of layering is that each layer adds value to services provided by the set of lower layers in such a way that the highest layer is offered the set of services needed to run distributed applications according to the OSI model. On the top of the stack U-NIC has the application interfaces like AHB, DTL and AXI. On the bottom the stack a component connects to another component through a U-NIC link as shown in figure 2.2.

When transmitting, while going down the stack each layer encapsulates the transmitted packet of the upper layer and forwards the encapsulated packet to the next layer. When receiving, while going up the stack each layer strips the encapsulation information and forwards the stripped packet. Each layer can add new packets for communication between same level layers. At the *Application* layer, U-NIC network interfaces provide network access for master and slave IPs. At the *Transport* layer U-NIC network interfaces take

## 4 CHAPTER 2. UNIVERSAL NETWORK INTERCONNECT ON-CHIP (U-NIC)

Figure 2.1: U-NIC Network Topology

Figure 2.2: U-NIC OSI Model

packets from different resources, buffering the packets, mapping the packets to virtual channels and arbitrate between multiple sources that are mapped to the same virtual channel and forward packets to the data-link. At the *Network* layers, U-NIC switches take care of packets routing through the network where the route through the network is determined at the source of the packet (source routing). At the *Data Link* layer, U-NIC links take care of robust link-level data transfers, flow control and data interleaving. At

the *Physical* layer, U-NIC PHY links convey the data streams through the network at the electrical level by encoding it to PHY symbols so that it can be transmitted over a hardware transmission medium.

#### 2.1 Performance

The performance of NoC based SoCs is known to be the throughput and latency that a network-on-chip can offer as guarantees to fulfill the requirements of the applications that are mapped on these systems. We distinguish between two types of performances, worst-case and average-case. In worst-case performance, guarantees are provided for real-time critical applications where the application tasks should be performed within strict deadlines, while in average-case performance, best-effort for non-critical applications is given. For the worst-case, it is possible to analyse the performance analytically, however for the average-case a probability theory can help in analyzing the performance since it is difficult to predict what is the average traffic [29]. Alternatively, simulation can provide average-case performance analysis but it gives no performance guarantees.

## 2.2 Quality of service

An on-chip communication network should provide deterministic bounds on delays and throughput for communication among pairs of cores on the chip. This is generally achieved by special designs of network routers which have capabilities of reserving channels or bandwidth for certain traffic and/or by allowing packets transmission with different priorities [11].

U-NIC is a virtual channel (VC) based network. Per physical link there are max 16 virtual channels, which share the link in time-division-multiple-access fashion.

Virtual channels can lead to an increase in the throughput of the network and avoid the occurrence of deadlock. This is because a blocked packet in one virtual channel does not affect a packet progressing on another virtual channel [11]. However, the more virtual channels the more buffers are required and accordingly the more silicon area which results in increasing the SoC price and of course the power consumption.

## 2.3 Arbitration

Systems-on-chip (SoCs) contain many applications with real-time requirements. Resources like the interconnect and memory are often shared between the applications to reduce the costs of a SoC. However, sharing the resources between the applications means that the processing elements representing the applications will compete to use these resources therefore arbitration is required to organize access to the shared resources in the SoC. For a NoC, arbitration influences the latency of the network elements. Each of the arbitration points contributes to the delay on the message passing through the network. Latency is an important parameter for the performance analysis.

In our SDF modeling method, we provide hard guarantees for real-time applications, therefore the knowledge of the worst-case execution time is essential for providing an accurate performance analysis of the system. Arbitration have impact on computing the worst-case execution times. We will briefly present some of the most common arbitration/scheduling schemes and show the impact on the performance analysis.

#### 2.3.1 Time-division-multiple-access (TDMA) scheduling

A time-division-multiple-access (TDMA) arbiter uses a time-wheel that rotates periodically and consists of time-slots that are fractions of the time-wheel. A task (code segment of an application) is assigned slot(s) in the time-wheel that would allow the task to execute when the scheduler is within the allocated time slot(s) and if needed multiple slots can be allocated to the task to obtain more bandwidth (weighted TDMA). TDMA provides worst-case guarantees on the maximum latency [12]. Per TDMA wheel rotation a predefined number of words (network words) can be sent over the network, the latency of a request due to TDMA arbitration depends on the number of TDMA wheel rotations that are necessary for processing a request. However, TDMA provides conservative upper bounds on the latency for average-case traffic because even when part of the time wheel is not allocated, a scheduled task has to wait for its allocated time-slot to execute and cannot make use of the free time-slots that might belong to an idle task. We can compute the time required by a task (read or write request) on a TDMA scheduler if we know the size of the request, the TDMA time-wheel and the size of the TDMA time-slot. The number of time-slots required by a task i to submit its read or write request can be computed as follows:

$$N_{tsi} = \lceil \frac{S_i(byte)}{S_{ts}(byte)} \rceil$$

Where  $N_{tsi}$  is the number of time-slots required by request i,  $S_i$  is the size of request i in bytes and  $S_{ts}$  is the size of the time-slot in bytes. The number of time-slots required by request i is rounded up incase the size of the request is not a product of the time-slot size.

The latency of request i depends on its time-slots allocation on the TDMA time wheel. If the needed time-slots per request is a multiple of the allocated slots in the time-wheel, then the worst-case latency can be computed as follows:

$$L_i = \left(\frac{S_{tw}(slots)}{AL_{tsi}(slots)} \times N_{tsi}\right) \times N_{cc/ts}$$

Where  $L_i$  is the latency of request i,  $S_{tw}$  is the size of TDMA time-wheel in slots,  $AL_{tsi}$  is the allocated time-slots for task i and  $N_{cc/ts}$  is the number of cc per time-slot.

A more general formula for computing the worst-case latency at a scheduler when the needed time-slots per request is not a multiple of the allocated slots in the time-wheel, independent of the slot distribution across the time-wheel is as follows:

$$L_i = \left( \left\lceil \frac{N_{tsi}(slots)}{AL_{tsi}(slots)} \right\rceil \times S_{tw} - \left( \left\lceil \frac{N_{tsi}(slots)}{AL_{tsi}(slots)} \right\rceil \times AL_{tsi} - N_{tsi} \right) \right) \times N_{cc/ts}$$

If we have no knowledge about the slots distribution in a time-wheel, we consider the slots to be located at the end of the time-wheel, in this way we guarantee the worst-case latency, since in the worst-case the last slot in the time-wheel is needed. However, if in the last time-wheel cycle less slots than the allocated ones are needed by the request, then these un-used slots (which reside at the end of the time-wheel) are excluded from the worst-case latency computation as shown in the second term of the formula.

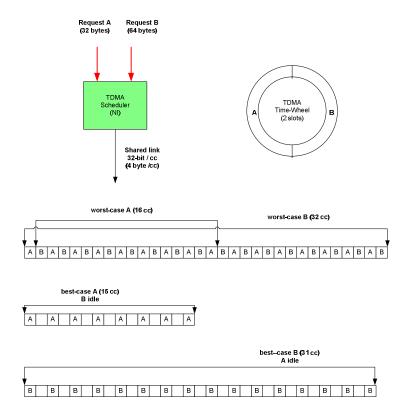

Figure 2.3: Example 2 requests on TDMA scheduler

Figure 2.3 provides an example of two concurrent requests A and B that are scheduled on a TDMA scheduler with request size 32 byte and 64 byte respectively. We consider a time-wheel with 2 time-slots, each time-slot has the size of 4 bytes (which is in this case the link bandwidth that the 2 requests want to share), each request is allocated 1 time-slot in the time-wheel, the wheel turns every clock cycle 1 time-slot. Table 2.1 shows the worst-case latency of request A and B computed according to the above formulas. If we want to compute the best-case latency where for example request A is idle, we notice that the best-case latency is almost equal (depends on the arrival of task B) to the worst-case latency since the reserved time-slot for request A will not be available for the use by request B. The same applies if request B is idle, request A will still have a

| Task           | $N_{ts}$ (slots) | $AL_{ts}$ (slots) | $S_{tw}(slots)$ | WCase latency (cc) | BCase latency (cc) |

|----------------|------------------|-------------------|-----------------|--------------------|--------------------|

| $\overline{A}$ | 8                | 1                 | 2               | 16                 | 15                 |

| B              | 16               | 1                 | 2               | 32                 | 31                 |

Table 2.1: Latency of example requests on TDMA scheduler

best-case latency that is almost equal to the worst-case latency as indicated in Figure 2.3. The average-case latency is between the worst-case and the best-case, which is for TDMA almost the value of the worst-case latency. Table 2.1 provides the computed worst-case and best-case for example requests A and B when scheduled on TDMA scheduler.

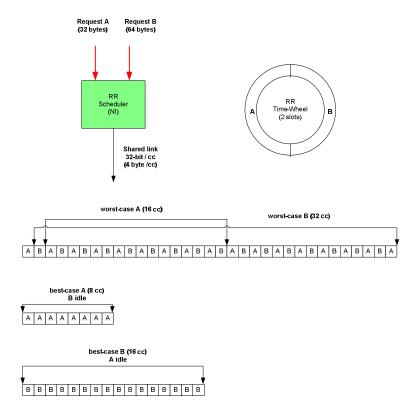

## 2.3.2 Round-robin (RR) scheduling

Round-robin is known to be the simplest scheduling algorithm where equal time-slots are assigned in order to the tasks that share the same resource, without priority assignment to the tasks. Round-robin scheduling is both simple and easy to implement, and starvation-free. In round-robin the highest performance is guaranteed when the tasks have uniform size. If the tasks have variable sizes, then round-robin is not desired since a task with large size would be favored over other tasks [1]. For tasks with varying sizes, time-slots are assigned so that a task can be interrupted in one round if it uses the allocated bandwidth and it continues in the next round.

In round-robin the average-case latency depends on the number of the 'active' tasks that are scheduled on the same resource and the tasks arrivals in the time wheel. If a task is 'inactive'/idle, its allocated slot(s) can be used by the other requests which are scheduled on the same scheduler. The average-case performance in round-robin is better than that of TDMA scheduler, since in an average-case performance the available time-slots for a request might exceed its original allocation.

The worst-case latency for a request scheduled on round-robin is identical to that of TDMA scheduler, because in the worst-case performance all the scheduled requests on round-robin scheduler make use of their allocated time-slots (no idle requests). The formulas used in computing the latency for TDMA scheduler apply to round-robin.

Figure 2.4 provides an example of the previous requests A (size 32 bytes) and B (size 64 bytes) when scheduled on round-robin scheduler. For 2 requests there are 2 time-slots that are allocated fairly in order for request A and B.

The best-case latency of task A occurs when task B is idle = 8cc. Similarly, the best-case latency of task B is when task A idle = 16cc. Table 2.2 provides the computed worst-case and best-case of the example requests A and B when scheduled on round-robin scheduler. The average-case latency is between the worst-case and best-case latency.

Figure 2.4: Example 2 requests on round-robin scheduler

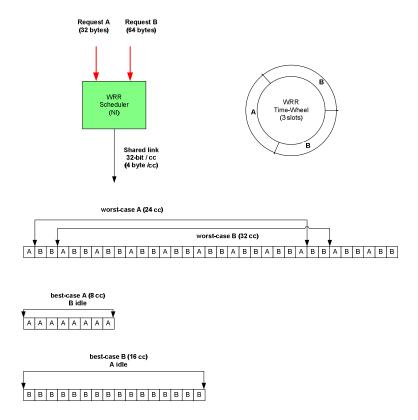

## 2.3.3 Weighted round-robin (WRR) scheduling

Weighted round-robin scheduling is used for traffic of the same priority, with weights proportional to the bandwidth allocations of the tasks. The weights determine the number of bytes that a task is allowed to send at each round. A variation of weighted round-robin is that if a task sends more than its allocated bandwidth, the same task receives less bandwidth in the next round [14]. The formulas used in computing the latency for TDMA scheduler apply to weighted round-robin.

Figure 2.5 provides and example of the same 2 requests A and B on weighted round-robin scheduler whith 3 time-slots with allocation of 1 time-slot for takes A and 2 time-slots for

| Task           | $N_{ts}$ (slots) | $AL_{ts}$ (slots) | $S_{tw}(slots)$ | WCase latency (cc) | BCase latency (cc) |

|----------------|------------------|-------------------|-----------------|--------------------|--------------------|

| $\overline{A}$ | 8                | 1                 | 2               | 16                 | 8                  |

| B              | 16               | 1                 | 2               | 32                 | 16                 |

Table 2.2: Latency of example requests on RR scheduler

Figure 2.5: Example 2 requests on weighted round-robin scheduler

task B. Table 2.3 provides the worst-case and best-case latency for tasks A and B where the best-case latency computation of task A we assume that task B is idle and vice versa. The value of the average-case latency is between the worst-case and best-case as explained above.

## 2.3.4 Priority-based scheduling

In a priority-based scheduling each task is given a predefined priority to share the network resources. Tasks with the highest priority have the least latency. Often, tasks with stringent real-time requirements receive the highest priority, while tasks with less critical

| Task           | $N_{ts}$ (slots) | $AL_{ts}$ (slots) | $S_{tw}(slots)$ | WCase latency (cc) | BCase latency (cc) |

|----------------|------------------|-------------------|-----------------|--------------------|--------------------|

| $\overline{A}$ | 8                | 1                 | 3               | 24                 | 8                  |

| B              | 16               | 2                 | 3               | 24                 | 16                 |

2.4. BUFFERING

real-time requirements get lower priorities. Accordingly, upper bounds on latency can be put for high priority tasks, while the latency computation for low priority tasks is harder because of the dependency on the arrival of higher priority traffic. The queueing theory [2] provides means to compute the waiting time of a lower priority traffic based on the arrivals of higher priority traffic and the available requests with higher priority in the queue of the shared resource.

A variation of priority-based scheduling is the rate monotonic algorithm (RMS) which maximizes the schedulability of tasks by assigning fixed priorities to the tasks so that a set of tasks is considered chedulabile if all the tasks in the set meet all their deadlines at all times. The RMS is a simple algorithm based on assigning the priority of each task according to its period, thus the higher priority is given to the tasks with the shortest period. More about the RMS can be found in [24].

[9] presents a static-priority scheduler which provides guaranteed bandwidth allocation and a maximum latency bound that is decoupled from the allocated bandwidth. The computation of the maximum delay of a request with priority is out of the scope of this report, more details can be found in [9].

In U-NIC round-robin scheduling [22] is implemented in several arbitration points, in the switch and in the network interfaces (iNI and tNI) as follows:

- Intra VC arbitration: Between requests on the same VC. Implements weighted round-robin scheme.

- Inter VC arbitration: Between multi VC wanting to transmit packets on the same link. Access will be granted to requests with highest priority.

The choice of round-robin scheduling is mainly to have a better average-case latency compared to TDMA scheduling, while worst-case latency remains comparable to that provided by the TDMA as shown earlier.

## 2.4 Buffering

In a network-on-chip, throughput guarantees depend on the availability of sufficient buffer space in the network. Buffers are required for the data communication through the network. Buffers can at the same time contribute to reducing the latency as it influences the time needed to process the data (pipelining). Thus increasing the buffer size results in increased throughput and possibly reduced latency in the network. At the same time, increasing the buffer size mean that more memory is required and accordingly increase in the area and power costs. Therefore, the system designer should try to minimize the buffering while meeting the throughput and latency constraints. Throughput-buffering trade-off is studied in [27].

The above applies to U-NIC, since buffers are required in the network components to guarantee the application's desired throughput, however for cost reasons there is a need

to reduce the number of buffers. In every U-NIC component (NI or Switch), there is a FIFO buffer per virtual channel that supports data transfer between these network components. It is also possible that a NI contains 2 SRAM one for requests (TX) and one for responses (RX) since write requests and read response require significant buffer size. iNI resides at the memory side and therefore should have enough buffer capacity to buffer data for all outstanding read and write requests to the memory.

## Chapter 3

# Synchronous Data Flow Graph (SDFG)

In this chapter we provide formal and informal definitions of a Synchronous Data Flow Graph and the notions that are used in this report. The formal definitions are obtained from the literature [26] [15] [16].

### 3.1 Informal definition

An SDFG consists of finite sets of actors and channels. An actor can be seen as a task of an application for example. A channel in an SDFG refers to either dependency edge or sequence edge. The dependency edge between two actors models a data dependency while the sequence edge models the execution order. The data sent on the edges are called tokens and the execution of the task is called firing. A channel can carry an unbounded number of tokens called initial tokens. The initial tokens are required for an actor to start its firing. Communication between two actors is done by sending data via the edge that connects the output of the source actor with the input of the destination actor.

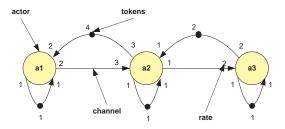

Figure 3.1: Simple SDF graph

When a source actor fires it consumes tokens from its input channel(s), performs computation on these tokens and produces tokens on its output channel(s), the amount of

produced and consumed tokens are fixed and called *rates*. The produced tokens on the output edge(s) of the source actor are consumed by the destination actor and so on. Actors in the SDFG synchronize only by communicating tokens over edges.

In Figure 3.1 we show an example of a dataflow graph with three actors. Each edge is annotated with the port rate of the corresponding source and destination actors. The single token of the self-edge of an actor prevents multiple firings of the actor simultaneously ensuring that the next firing of the actor will occur only after the execution of the previous firing is finished. The backwards edge models dependency such that an actor can fire only when there is enough storage space at the destination actor, this is called the *firing rules* of an actor. The number of initial tokens on the backwards referrers to the buffer size of the destination actor.

## 3.2 Formal definition

Definition 1. [Actor] An actor is a tuple (I,O) that consists of a set of input ports  $I \subseteq Ports$  and a set of output ports  $O \subseteq Ports$  where an input port cannot be an output port at the same time  $I \cap O = \emptyset$ .

Definition 2. [SDFG] An SDFG is a tuple (A,C) with a finite set of A of Actors and a finite set  $C \subseteq Ports^2$  of channels (or edges). The source of a channel is the output port of some actor and the destination is an input port of some actor. A port is connected to exactly one channel and a channel is connected to ports of some actor. For every actor  $a = (I,O) \in A$  we denote the set of all channels that are connected to ports in I(O) by InC(a) (OutC(a)).

A channel in an SDFG referrers to either dependency edge or sequence edge. The dependency edge between two actors shows data dependency while the sequence edge shows the execution order. A channel can carry an unbounded number of tokens called initial tokens. The initial tokens are required for an actor to start its firing.

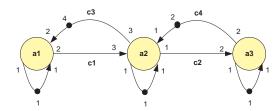

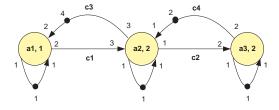

An example of an SDFG with three actors a1, a2 and a3 is shown in Figure 3.2. Actors a1 and a2 are connected via edge c1. Actors a2 and a3 are connected via edge c2. The execution of an actor is defined in terms of *firings*. When an actor a starts its firing, it removes Rate(q) tokens from all  $(p,q) \in InC(a)$ . When the firing ends, it produces Rate(p) tokens on every  $(p,q) \in OutC(a)$ . The rates determine how often the actors have to fire with respect to each other so that the distribution of tokens over all the channels is not changed. Actors synchronies by communicating tokens over the channels.

The backward edge models dependency such that an actor can fire only when there is enough storage space at the destination actor (firing rules of the source actor). The single token of the self-edge of an actor prevents multiple firings of the actor simultaneously ensuring that the next firing of the actor will occur only after the execution of the previous firing is finished.

Figure 3.2: Example of an SDFG

Definition 3. [Repetition vector and consistency] A repetition vector of vector q of an SDFG (A,C) is a function  $A \to 0$  in a way that for each channel  $(i,o) \in C$  from actor  $a \in A$  to  $b \in A$ ,  $Rate(o) \cdot \gamma(a) = Rate(i) \cdot \gamma(b)$ . A repetition vector  $\gamma$  is called non-trivial if and only if q(a) > 0 for all  $a \in A$ . An SDFG is called consistent if it has a non-trivial repetition vector. For a consistent graph, there is a unique smallest non-trivial repetition vector, which is designated as the repetition vector of the SDFG.

The repetition vector of an SDFG determines the firing frequencies of its actors. The repetition vector of the SDFG actors (a1,a2,a3) in Figure 3.2 are (3,2,1) respectively. The repetition vector of the graph is non-trivial meaning that the graph is consistent. Consistency and deadlock free are important properties for an SDFG. Deadlock results when there are insufficient number of tokens in a cycle of the graph.

Definition 4. (Timed SDFG) A timed SDFG is a triple  $(A, C, \Upsilon)$  consisting of an SDFG (A, C) and a function  $\Upsilon: A \to 0$  that assigns to every actor  $a \in A$  the time it takes to execute the actor once.

In Figure 3.3, the execution time of each actor is denoted with a number in the actor.

Figure 3.3: Example of a Timed SDFG

Definition 5. [State] The state of a timed SDFG  $(A,C,\Upsilon)$  is a pair  $(\delta, v)$ . Edge quantity  $\delta$  associates with each dependency edge  $c \in C$  the amount of tokens in that edge in that state. To keep track of time progress, an actor status  $v : A \to N^N$  associates with each actor  $a \in A$  a multiset of numbers representing the remaining times of different ongoing

firings of a. We assume that the initial state of an SDFG is given by some initial token distribution  $\delta$ , which means the initial state equals  $(\delta,\{(a,\{\ \})\mid a\in A\})$  (with  $\{\ \}$  denoting the empty multiset).

Definition 6. [Self-timed execution] An execution is self timed if and only if clock transitions only occur when no start transitions are enabled.

In the self timed execution of an SDFG, from one clock transition to the next, there can be some interleaving of simultaneously enabled start and/or end transitions. However, because these start and end transitions are completely independent of each other, independent of the order in which these transitions are applied, the final state before each clock transition, and hence also the state after each clock transition, is always the same. Self timed SDFG behavior is therefore deterministic in the sense that all the states immediately before and after clock transitions are completely determined and independent of the selected execution. In a self timed SDFG an actor fires as soon it can (i.e. as soon as it is enabled).

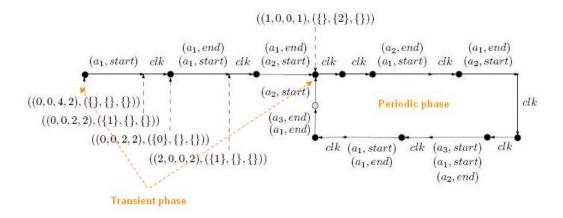

Figure 3.4: State-space of example SDFG showing the transient and periodic phases

Figure 3.4 shows the transition system of the self timed execution of the timed SDFG shown in Figure 3.3. All clock transitions are shown explicitly. Between clock transitions, there can be multiple start and/or end transitions enabled simultaneously. These start and end transitions are independent of each other. Independent of the order in which they are applied, the final state before each clock transition, and the first state after each clock transition, are always the same. Therefore, all start and end transitions are shown as one annotated step. A transition system consists of a finite sequence of states and transitions called the *transient phase* followed a sequence of states and transitions that is repeated infinitely often called the *periodic phase* as marked in Figure 3.4.

Definition 7. [Strongly-connected SDFG] A strongly connected SDFG is a graph of which every actor depends in its firing on tokens from another actor.

Strongly connected self timed SDFGs, the *transient phase* and *periodic phase* are important in the throughput calculation which will be discussed in the next chapter.

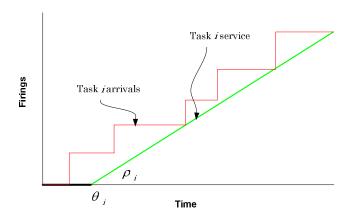

Definition 8. [Throughput] The throughput Th(a) of an actor a for the self-timed execution  $\sigma$  of a consistent and strongly connected timed SDFG  $G = (A, D, \Upsilon)$  is defined as the average number of the firings of actor a per time unit in  $\sigma$ . The throughput of G is defined as:

$$Th(G) = \frac{Th(a)}{\gamma(a)}$$

where  $\gamma$  is the repetition vector (in Definition 3) of G and a an arbitrary actor. The throughput of G gives the average number of iterations of the graph per time unit in  $\sigma$ .

Definition 9. [Latency] Latency between two actors a and b is defined as the time delay between the k-th firing of the source (src) actor a and the corresponding fining of the destination (dst) actor b within an execution  $\sigma$ :

$$\mathbf{L}_k \sigma = \mathbf{F}_{dst,cf(src,k,dst)} \sigma$$

-  $\mathbf{F}_{src,k} \sigma$

In the above formula, F refers to the finishing time of the k-th firing of an actor and  $\sigma$  represents an execution. When computing the latency, only an execution of a complete iteration is considered.

## Chapter 4

## $SDF^3$ Design flow and tooling

The  $SDF^3$  tool is the implementation of the SDFG-based design flow and algorithms presented in [26] which provides techniques for mapping streaming applications with time constraints to a NoC-based MP-SoC.

The design flow objective is to minimize the resource usage (processing, memory, communication bandwidth) while at the same time offering guarantees on the throughput of the application when mapped to the system. The design flow consists of the following four iterative phases:

- Memory dimensioning: In this phase enough storage-space is made available for the tokens that communicate over the edges of the SDFG. This includes modeling the access to a memory tile when the token does not fit in the local memory of a processing tile. In this phase trade-off is made between the storage-space that is allocated to the edges in the SDFG and the maximal throughout that can be achieved under these allocation. The trad-off space is used to put constraints on the storage-space of the edges in the application SDFG.

- Constraint refinement: In this phase the storage constraints defined in the previous phase are used to compute latency and bandwidth constraints on the edges of the SDFG. The constrains all together are used in the next phase to bind the application actors to the tiles of the MP-SoC architecture.

- Tile binding and scheduling: In this phase, application actors that are bound to the same tile receive static-order scheduling to perform their tasks. TDMA timeslots on the tiles are also allocated in this phase and the storage-space allocation is minimized when possible.

- NoC routing and scheduling: In this phase TDMA time-slots are allocated on the links of the NoC by first extracting the NoC scheduling from the previous phase of the flow and then find a solution for the NoC scheduling, then the actual bandwidth used by the NoC schedule is computed.

All the information from the previous steps are used to determine the resources that are available for the next application that need to be mapped to the same NoC-based MP-SoC

Figure 4.1: Platform Architecture

#### architecture.

In order to use the  $SDF^3$  design flow, an application needs to be modeled as an SDFG specifying the execution time of the application's tasks (actors) when executed on a defined processor. In addition to that, the size of tokens communicated over the edges should be known. It is also required to provide the SDFG for the platform and interconnect. In [26] the platform architecture consists of processor tiles and memory tiles, each tile contains the NI of the NoC interconnect, computation and storage elements. Tiles communicate through links via the interconnect routers as shown in figure 4.1.b.

The result of the design flow is a multiprocessor SoC configuration that specifies a binding of the actors to the processor tiles and memory tiles, a schedule for the actors on the processors and a schedule for the token communication over the NoC.

The presented platform architecture and interconnect differ from U-NIC platform architecture in Figure 4.1.a. In U-NIC there are no fixed tiles structure, instead a processing element is connected to a network interface. Another difference is the scheduling algorithm of the NoC. U-NIC uses virtual channels for resource sharing and round-robin schemes for scheduling tasks on the same resource, while in the proposed design flow Æthereal [18] NoC architecture is used, which is based on TDMA time-slot allocations for sharing the network resources.

$4.1. SDF^3 TOOL$  21

In order to use the design flow for U-NIC based SoC, minor modification to the platform architect can be conducted since every processing element can have its own internal memory and the NI in every tile can be mapped to the same NI, but the scheduling remains a major difference that require substantial modification in the proposed design flow. However, if U-NIC arbiters can provide the same guarantees of the TDMA scheduler, then the design flow can be modified for U-NIC use.

Due to the mentioned differences, the proposed design flow and the  $SDF^3$  tool capabilities in generating the design space of a SoC cannot be used for U-NIC based SoC design as is in this assignment. However, the  $SDF^3$  tool can still be used for analyzing the throughput and latency of a system that is modeled in an SDFG.

In this report we present a method to model, map and schedule a multimedia application onto U-NIC based SoC. The results is an SDFG of the SoC that can be analyzed via the  $SDF^3$  tool.

## 4.1 $SDF^3$ Tool

$SDF^3$  is the implementation of the SDFG-based design flow and analysis algorithms in [26]. The input to the tool is the streaming application SDFG and platform architecture both in XML format. Example of the XML input files are included in the tool software package [28]. The tool performs automatically the steps described in the design flow and as output it generates a complete state of the design flow in XML. The outputted design flow provides the tile binding, NoC routing and scheduling. It is possible for the designer to modify the output file manually in order to change the design flow suggested by the tool.

$SDF^3$  implements various techniques and algorithms. The algorithms are outside the scope of this report, however for the purpose of the experiments performed in this report, a brief introduction to the algorithms for the throughput and latency analysis is provided, where more details can be found in [26] [16] [27] [15].

## 4.2 $SDF^3$ Performance analysis

#### 4.2.1 Throughput

In multimedia applications, throughput is an important indicator to the performance constraints. The throughput is influenced by the available buffers in the system. More buffer means more data can be transmitted through the system and accordingly an increase in the throughput. However, more buffers means more silicon area (high cost) and power consumption (undesired), therefore trade-off between the throughput and buffer size [27] need to be made. The SDFG model allows the SoC designer to explore this trade-off using the throughput analysis capabilities of the  $SDF^3$  tool as will be shown in a later chapter. In [26], "the throughput of an SDFG refers to how often the actor produces an output token". Traditionally the SDFG throughput is defined as 1 over the maximal cycle mean (MCM) of the corresponding Homogeneous Synchronous Data Flow Graph (HSDFG) [23].

The corresponding HSDFG of a SDFG is an SDF graph where the execution of any actor in the graph results in the consumption of one token from each incoming edge of the actor and the production of one token on each outgoing edge. The transformation of an SDFG to a HSDFG can lead to an exponentially larger size than the size of the original graph in terms of the number of actors and edges, and accordingly this traditional method for analyzing the SDFG throughput is inefficient. As an alternative, [15] presented a method for analyzing the throughput of an SDFG based on state-space exploration of a self-timed strongly-connected SDFG. This method is implemented in the  $SDF^3$  tool. The method states that the notion in Definition 8 is equivalent to 1 over the maximal cycle mean of the corresponding HSDFG by using two propositions related to the transient and periodic phase in Figure 3.4.

**Proposition 1.** For every consistent and strongly connected timed SDFG, the self-timed state-space consists of a transient phase, followed by a periodic phase.

**Proposition 2.** For every consistent and strongly connected timed SDFG  $(A, C, \Upsilon)$ , the throughput of an actor  $a \in A$  is equal to the average number of firings per time-unit in the periodic part of the self timed state space.

The buffer capacity of an actor is modeled in SDF by the number of initial tokens on a backwrds edge from the actor to the source actor that attempts to communicate with it. In Figure 4.2 we show how the buffer capacity can be modeled in SDF graph by the backwards edge.

The throughput of an SDFG is limited by its critical cycle [23]. The critical cycle in an SDFG is the cycle with the maximal cycle mean, that is the total execution time over the number of tokens in that cycle.

By knowing the critical cycle of an SDFG, we know which components (actors, channels) in the graph that are limiting the throughput. In order to increase the throughput of the graph we can look at these limiting components and try to improve either the execution time of the involved actors or the capacity of the channels. By increasing the channel capacity, the flow of more tokens through the channel is utilized and accordingly the throughput increases.

Although the  $SDF^3$  finds the critical cycles in the throughput computation, it does not indicate them in the output of the tool. Possible method to find a critical cycle in an SDFG is by examining the effect on the graph throughput when the execution time of an actor is modified. If no major change to the throughput, then that specific actor is not in the path of the critical cycle. In our experiment with U-NIC we will use this method to find the critical path in the obtained SDFG model.

## 4.2.2 Latency

In real-time applications that execute concurrently on NoC based SoC, the latency is an important performance indicator. In [16] the latency is defined by "the time delay between

Figure 4.2: Buffer and latency model in SDF

the moment that a stimulus occurs and the moment that its effect begins or ends". In an SDFG, the actors firings and producing of tokens respond to the stimuli, while their effects are the consumption of the produced tokens by other actors.

The exsection order of the actors in an SDFG influences the latency. Since the execution order of the actors in an SDFG can be fixed at the design time (static scheduling), this makes the SDFGs statically analyzable. The execution order of the graph actors is called "the class of static order schedulers" [16].

An algorithm to determine the minimal achievable latency between the executions of any two actors in an SDFG is described in [16] and implemented in the  $SDF^3$  tool. Latency computation is performed on a timed SDFG where the minimum latency is achieved by obtaining a class of static order schedules.

Resource arbitration strategy that uses a static order schedule starts with waiting till the first task in the sequence is ready to execute. After executing this task, the scheduler executes the next task in the sequence if it is ready, or it waits till the task becomes ready to be executed. Once this task is executed, it continues with the next task. This process is repeated till the schedule is finished or it continues indefinitely in the case of an infinite schedule.

Latency is modeled in SDF by the execution time of the actors in the graph as indicated in Figure 4.2.

## Chapter 5

## Method for modeling NoC based SoC

In this chapter we will present a method to construct an SDFG model for a multimedia system-on-chip (SoC). The method will help the SoC designers to model and analyse the performance of the system with the  $SDF^3$  tool at design time.

In a multimedia SoC, the applications (e.g. video, audio and graphics) are implemented in tasks. These tasks are in turn implemented as software on programable processors or as hardware IPs known as processing elements (PEs). The processing elements in a SoC require certain data to perform their computation. For that data Read requests are submitted to a shared memory, then after performing the computation the data is updated by the PEs, for that data Write requests are submitted to a shared memory. Often this is an off-chip shared memory due to the size of data that need to be processed by the application, like video frames for example. Access to the shared memory is arranged by the network-on-chip and memory controller.

To be able to model a multimedia SoC, we need to understand the applications that are running on the system, their communication patterns and traffic characteristics when accessing the shared memory through the network.

Another aspect that needs to be considered is the buffer capacity in the system that ensures sufficient throughput to fulfil the application's constraints.

As a start point, we will build basic SDFG models for the application, the network and the memory, then connect the graphs based on the communication pattern of the application. Essential prerequisites for building the models are:

- the communication patterns and traffic characteristics of the application are known upfront;

- the statistical analysis of the application (worst case execution times of the processing elements) is available;

• worst case execution times (WCETs) at the network elements and memory are available.

The above perquisites are necessary when mapping the application actors to the network and when allocating the memory resources. The size of data that is communicated through the network via the external memory influences the allocated network resources and the required buffering space. Also the execution time of each task (code segment) is required to perform the throughput and latency analysis.

The WCETs at the network elements depend on the scheduling algorithms implementation and can be provided either by careful analysis of the implemented scheduling algorithms or from simulation results, however, simulation provides no guarantees or upper bounds on the latency.

Static-code analysis of the application source code can be extracted by specialized tools [21]. These tools take an application as input and analyze its memory and execution time requirements.

The method incorporates the following steps:

- 1. model the application's main code tasks

- 2. model the network-on-chip request and response paths

- 3. build basic model for the external memory

- 4. construct the SoC model: analyse and map the application to the network based on the application traffic characteristics.

### 5.1 Formal definitions

The following definitions will be used in describing the above steps.

Definition 10. [Request] A Request is either a read or write transition from the application actors through the network.

Definition 11. [Master actor] A master actor is an actor that issues read or write requests to the network.

Definition 12. [Slave actor] A slave actor is an actor that receives a read or write request from a master actor through the network.

Definition 13. [Request path] A request path is the path that a request takes through the network from the master actor to the slave actor.

27

Definition 14. [Response path] A request path is the path that a request takes through the network from the slave actor to the master actor.

Definition 15. [Execution actor] An execution actor is an application actor that performs the computation of a code with the actual execution time as estimated in the static-code analysis.

Definition 16. [Auxiliary actor] An auxiliary actor is an actor with an execution time equals to 0. Often required to mimic the internal communications between some other actors.

Definition 17. [Sequence edge] A sequence edge is a channel from a source actor to a destination actor.

Definition 18. [Dependency edge] A dependency edge is a channel with tokens from a destination actor to a source actor.

## 5.2 Application model

We start by analyzing the application to determine the main processing elements (PEs) and the communication characteristics between the PEs, mainly the size of the communicated data, the sequence of which data is communicated and the data dependency between the PEs.

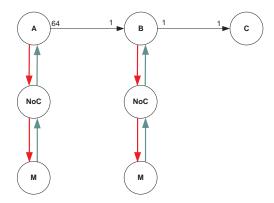

Per each processing element, we assign an actor named by the processing element and repeat until all PEs have assigned actor. The actors are connected by channels where the in/out port rates of the actors depends on the size of communicated data in tokens. Figure 5.1 shows an SDFG model of an application that consists of three processing elements (ABC). Actor A performs its computation on 64 data units, each data unit is presented by a token. Actors B and C perform computation on 1 data element.

Figure 5.1: SDFG of an example application

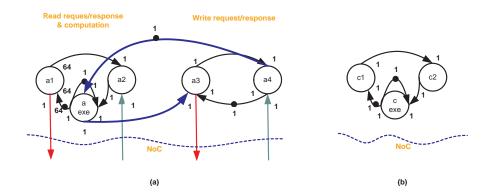

In Chapter 2 we showed that for round-robin arbitration (as for TDMA and weighted round-robin) the worst-case latency of one request at any shared resource can be computed independently of the other requests that share the same resource. Based on this observation, we can model each read/write request (application task) to the shared memory through the network as if it communicate via a separate network. Therfore, the

application SDFG is fine grained (see Figure 5.2) by replacing each actor that communicates data through the network by five actors: (a) three actors for the read request of which one execution actor performs the actual computation on the data and two auxiliary actors; (b) two actors for simulating the write request of which both are auxiliary actors since in the write request no computation is performed. The auxiliary actors simulate the read/write request/response as well as for the sequence and data dependency between the read and write requests. The arrows to and from the NoC represents the requests and responses respectively. The horizontal thick arrows represent the sequence and dependency edges. Figure 5.2.a. shows the fine grained SDFG for actor A where actor a1 sends read request of 64 data elements to the network; actor a2 receives the read responses of 1 data element at a time and sends 1 token on its output edge to actor aexe; actor aexe requires 1 token to start its computation then it fires 1 token on its output edge to actor a3 indicating the completion of its computation on one data element so that actor a3 can send write request through the network, actor a4 receives the write response and sends 1 token on its output edge to aexe indicating that the next data element can be sent. The edge from aexe to a3 is a sequence edge while the edge from a4 to aexe is a dependency

If an actor doesn't communicate data through the network, it will be replaced by three actors, one actor for the actual computation and two *auxiliary actors* for the sequence and data dependency with the other actors in the graph. Figure 5.2.b gives the fine grained SDFG for actor C which doesn't communicate data via the network.

Figure 5.2: Fine grained SDFG of actors A and C in the example application

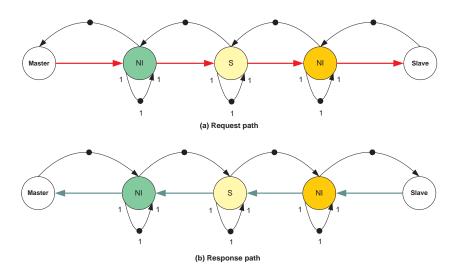

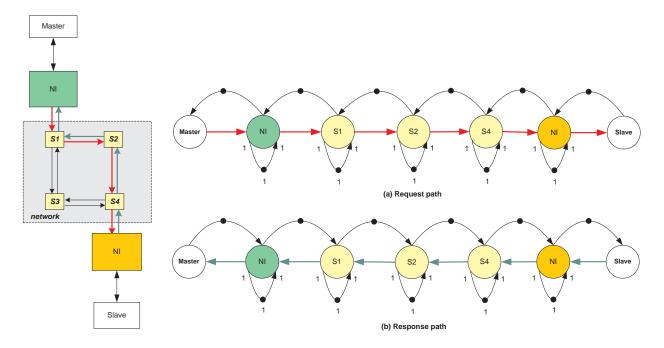

#### 5.3 Network model

Most network-on-chip (NoC) architectures consist of network interfaces (NI) and switches or routers [18] [10]. The network model consists of two type actors, NI and Switch. The NI connects *master* and *slave* actors to the network, while the switch connects NIs. Figure 5.3 provides a basic network channel model for an example NoC which consists of two net-

work interfaces and one switch. The NI are connected to *master* and *slave* actors. Both request and response paths are illustrated. NoC with different topology, can be modeled in a similar way. The only difference is that the channel model shall contain multiple switches depending on the route that is taken through the network. Figure 5.4 shows an example of a network channel model for multiple routers mesh topology. In this example the request and response follow the same path as the case in the study network U-NIC, but in general the response path can be different depending on the network architecture and routing schemes.

Figure 5.3: NoC channel model

The backwards edges with tokens model the buffer capacity of a network elements. In the network, buffers are needed for the data and the flow control communication between the network elements. Tokens are sent from a source actor to a destination actor when there is sufficient buffer space at the destination actor, flow control provides the information on the available buffer space at the destination actor so that the source actor can send more tokens depending on the free buffer space.

## 5.4 Memory model

The memory model consists of two actors, one actor for receiving the read/write requests from the network and processing the request and one *auxiliary actor* for sending the read/write responses via a network as shown in Figure 5.5.

Figure 5.4: NoC channel model for multiple mesh topology

Figure 5.5: Basic Memory model

## 5.5 Construct the SoC model

### 5.5.1 Application mapping

First we analyse the application's traffic characteristics and identify the actors (master actors) that communicate data through the network. We proceed by building a simple model of the SoC to reflect the application's communication patterns through the NoC on a high level where the network is modeled by one actor for simplicity. In the example application, actors A and B communicate by sending data to a shared memory (slave actor) through the network. This is illustrated in Figure 5.6.

For every main actor in the application, we built a fine grained SDFG. The arrows that represent the read/write requests and responses through the network are replaced by the

Figure 5.6: Abstract SoC SDFG for example application

network channel models.

#### 5.5.2 Application scheduling

We schedule the execution sequence of the application actors via sequence and dependency edges as indicated previously in Figure 5.2.a. The scheduling is based on the execution sequence of the code segments and the size of communicated data. The dependency edges are used as control channels between the code main actors similar to the use of flags in the code.

#### 5.5.3 Port rate specification

Every actor in the SoC SDFG has a total number of (input and output) ports equals to the number of input and output channels that are connected to the actor. A port rate depends on the read/write request size, the network data width (word size) and the communication unit (tokens) representation. Often the read/write requests are converted to different data size before sending it to the network. In Figure 5.2.a of the example application, actor A sends read request to the shared memory of 64 bytes, performs computation and sends write request of 64 bytes to the shared memory. If we consider the network word size 64-bit=1 token, then for writing 64 bytes to the memory, a total of  $(64 \times 8 \times \frac{1}{64(bits)}) = 8$  transactions are required which means actor that issues the write request of 64 bytes has an output port rate on the channel to the network equals to 8 tokens.

#### 5.5.4 Minimum buffer allocation

To avoid any deadlock in the dataflow graph sufficient tokens should be available on every cycle in the graph. The minimum number of the initial tokens on a dependency edge from destination actor b to source actor a must be  $\geq$  the output port rate of the source actor a on the channel to the destination actor b. However, when we consider the resources sharing, not only the availability of sufficient tokens on an actor input can guarantee its

immediate firing, but also the schedule that is used on the shared resources. In an SDFG an actor fires when it has sufficient tokens and when the actor's firing is scheduled on the shared resource. This property is referred to by causal dependency in [30]. When this property holds for all actors sharing resources in the graph, then we can guarantee by providing sufficient tokens on every cycle in the graph that it will not deadlock. In case more than one task send data on the same channel (share the same resource), then the buffer size of the shared resource in the implementation should be the sum of the sized buffers required by each of the concurrent tasks.

Finally to complete the SDFG model of the example application SoC, the worst case execution times are added to the SoC actors. In the case study of the next chapter the above steps are discussed in more details.

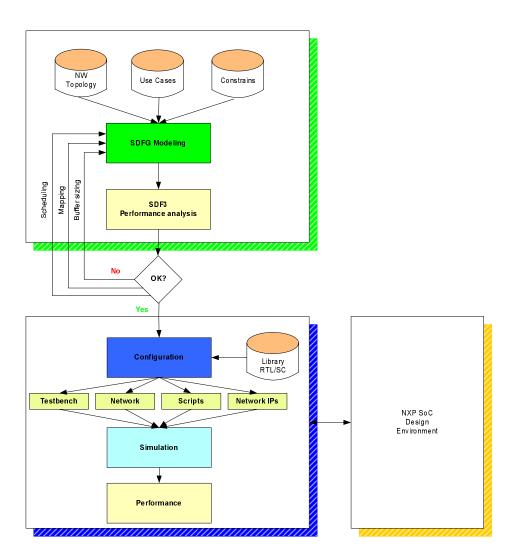

## 5.6 Place in a design flow

Typical NoC implementation design flow consists of iterative steps to generate, configure and analyse the network performance [17]. A NoC design flow proposed in NXP incorporates similar iterative steps where the required inputs to the design flow are the application communication requirements, the network topology and performance constraints (throughput, latency, power, area). Our method to model and analyse the performance of NoC based SoC can be placed on top of the implementation design flow as shown in Figure 5.7. The SoC designer can construct an SDFG model of the system as described above and run the performance analysis to check if the application constraints are met, if not, then the designer can check the critical cycle in the model and try to resize the buffers in the path of the critical cycle or change the application mapping or scheduling until the constraints are met.

The performance of the constructed SDFG provides guarantees on throughput and latency provided that the latency is accurately computed and that no component that can influence the latency computation is missed in the model.

Once the required performance constraints are achieved, the implementation phase can start. In the implementation phase the network is generated with NXP SoC design environment using the RTL and SystemC libraries. The generated RTL and SystemC views of the network are used to verify the network performance through simulation (SystemC and RTL VHD).

Figure 5.7: Place in NXP NoC design flow

# Chapter 6

# H263 Video Decoder Case Study

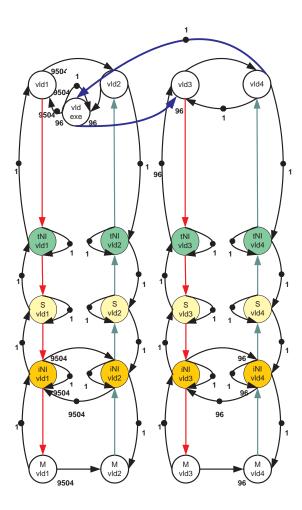

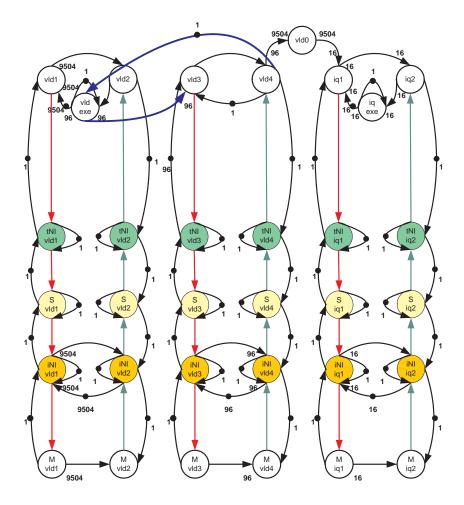

We apply the method to a multimedia application (H.263 video decoder) running on a SoC. The application consists of four cores (processing elements) performing the code computation on U-NIC based SoC and an external memory.

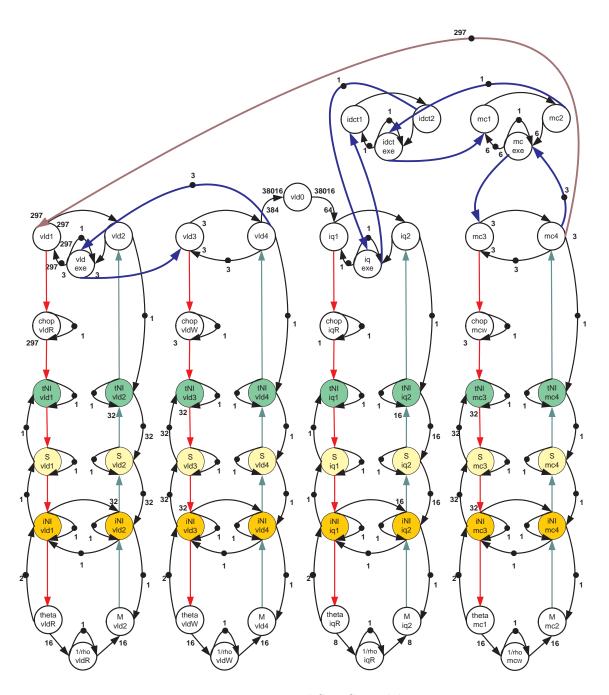

Based on the Synchronous Dataflow (SDF) model of computation [26], we measure the throughput and latency of H.263 video application when mapped on a U-NIC base line network using the analysis capabilities of the  $SDF^3$  tool. The full XML file of the SDFG model is enclosed in appendix 1.

#### 6.1 Model H.263 video decoder

The H.263 standard is intended for video compression of streams with low resolutions. The decoder performs the reversed operations of a H.263 encoder [3] in order to reconstruct the original video stream.

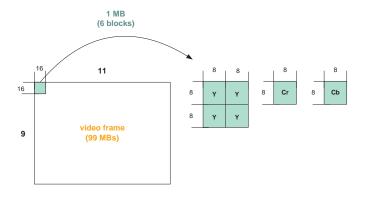

In this experiment, we assume that the H.263 decoder operates on frames with QCIF resolution (176  $\times$  144 pixels) and that the received video stream has a maximal frame rate of 15 frames per second known as **throughput constraints** of the application.

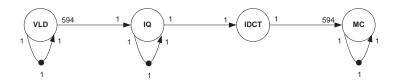

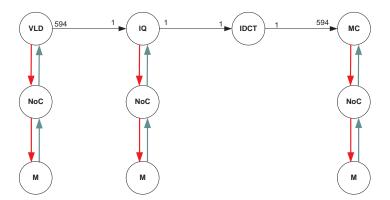

In [26] the SDFG for the H.263 application is modeled by 4 actors; each actor corresponds to one of the code main tasks and edges for the tasks to communicate as shown in Figure 6.1. The H.263 application has the following main tasks:

- Variable Length Decoder (VLD) decompresses the data streams

- Inverse Quantization (IQ) de-quantizes elements in a block of 8X8 data elements

- Inverse Discrete Cosine Transform (IDCT) transforms blocks from frequency domain to space domain.

- Motion Compensation (MC) reconstructs the original video frame

#### Model description

The VLD actor, on each firing, produces decompressed data or encoded macro blocks

Figure 6.1: H.263 SDFG Model

(MBs) for a complete video frame. Each macro block captures the image data for a region of  $16 \times 16$  pixels. Inside the macro block, the image data is divided to 6 blocks, each block of  $8 \times 8 = 64$  data elements. 4 blocks contain the luminance values of the pixels inside the MB and 2 blocks contain the chrominance values as shown in Figure 6.2. The macro block represents  $6 \times 8 \times 8 = 384$  data elements. In a video frame with QCIF resolution, we have in total  $11 \times 9 = 99$  MBs and accordingly  $99 \times 6 = 594$  blocks.

Figure 6.2: Video frame size

The inverse quantization (IQ) and inverse discrete cosine transformation (IDCT) actors revert the MB encoding.

The IQ and IDCT actors operate on a single block of encoded pixel data instead of a complete MB. This allows smaller memory requirements for these actors when compared to the full frame decoding.

The motion compensation (Motion comp.) actor takes a group of 594 blocks to reconstruct the original video frame.

The self-edges with one token on VLD, IQ and MC actors prevent simultaneous firings of the corresponding actor and ensure that the next firing of the actor will occur only after the execution of the previous firing has finished.

#### 6.2 Model U-NIC baseline

U-NIC baseline platform which is considered in this experiment consists of:

- Target network interface (tNI): Interfaces with the processing element

- Initiator network interface (iNI): Interfaces with the external shared memory

- Switch (S): Interfaces between the iNI and tNI

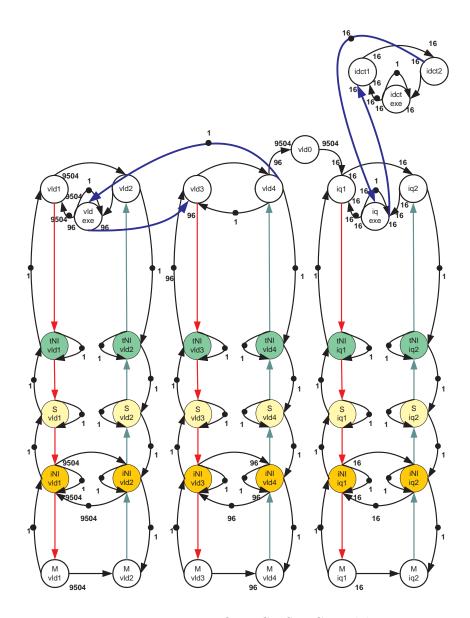

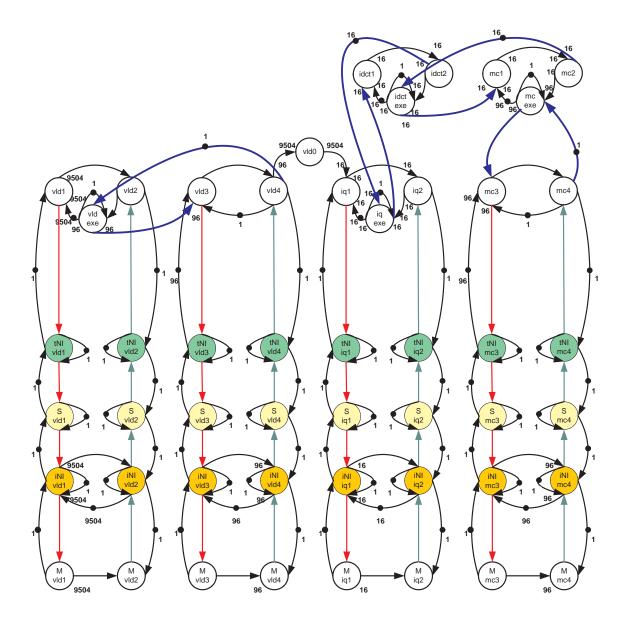

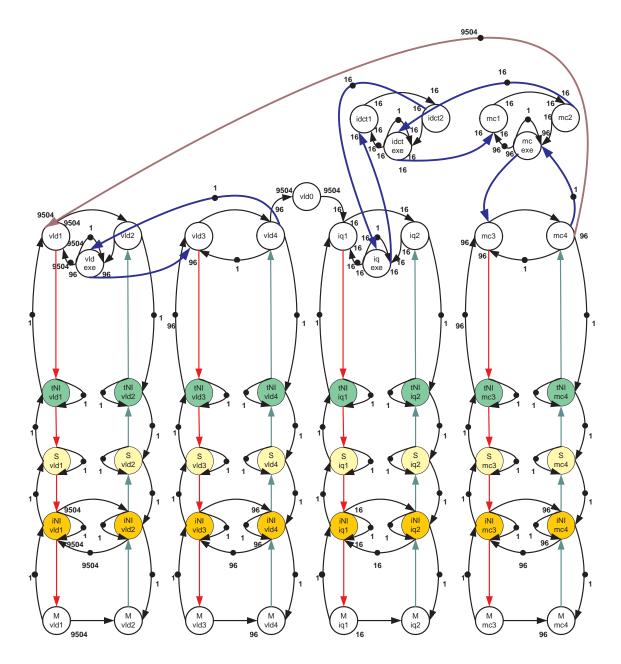

Figure 6.3 shows the SDF model for U-NIC network connection with a processing element and an external memory. For the purpose of this case study, and since U-NIC architecture doesn't allow the requests and responses to be on the same VC, we consider the use of two separate virtual channels (VCs), one VC for the Read/Write requests (request path) to the memory and one VC for the Read/Write responses (response path) from the memory. Since the worst-case latency at any shared resource is computed independently from the other requests that share the same resource (discussed in Chapter 2), we can model the requests sharing the network resources independently in a SDFG as if each request is connected to a separate network.

Figure 6.3: U-NIC SDFG Model

#### **Model Description**

The network components are modeled in the SDF graph as actors named by the corresponding network component (tNI, S, iNI) as shown in Figure 6.3. The processing

elements and the memory are actors labeled by PE and M respectively. Each network actor has self-edge with one token to ensure that tokens are processed one by one; in this way auto-concurrency is prevented.

Communication between the actors is modeled by edges. Each edge is annotated with the port rates of the corresponding output/input actors. These rates refer to the produced and consumed tokens when the actor executes/fires (In Figure 6.3 the rates of the ports are not indicated). The dotted arrow corresponds to the internal communications between the PE actors.

U-NIC link between any two actors can process only 1 word (32-bit word) per cycle. The port rates of U-NIC actors (tNI, S, iNI) is equal to 1.

When the processing element actor fires it produces 'p' tokens, the fired tokens represents either read or write request to the memory. The number of fired tokens depends on the size of the read or write request. In this base line model, the tNI actor requires 1 token on all its input ports to fire. In order to ensure that the graph will not deadlock, which is an important property for the SDFG [26], sufficient number of initial tokens on each cycle in the graph should be available assuming that the *causal dependency* property which is discussed in the previous chapter holds.

The number of initial tokens on the edges influences the actors' firings. In Figure 6.3 the backwards edges are labeled with the number of initial tokens equal to the buffer capacity of the destination actors respectively. This is to guarantee that no overflow will occur in any of the network components. In other words, tokens may be transmitted from one actor to another if there is enough buffer space at the receiving actor. Buffer size is illustrated by the number of tokens Tx (x: actor name) on the backward edge. When multiple processing elements share the same resource in parallel execution, then the buffer size of the shared resource in the implementation is the sum of the required buffers for each task. U-NIC requires that the iNI at the response side has sufficient buffer capacity to accommodate the full request before the tokens of the full request are sent to the memory, therefore in order to fulfill this requirement edges between the iNI on the response channel and the iNI on the request channel are added to the model (horizontal dependency edges). The initial number of tokens on the horizontal edge is at least equal to the maximum request size of the application (Q).

#### 6.3 SDFG model of the H.263 SoC

The communication pattern between the application actors and the memory actors through the network is essential in building the SoC SDFG model, therefore we discuss in details how the application communicates through the network.

#### 6.3.1 Application communication pattern through the interconnect

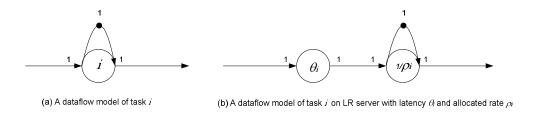

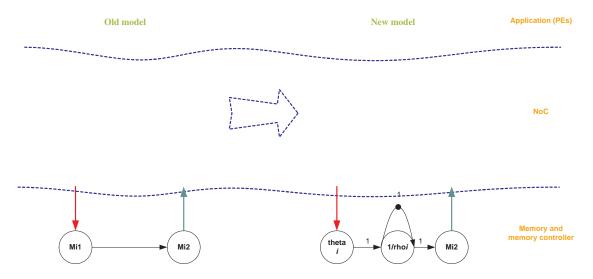

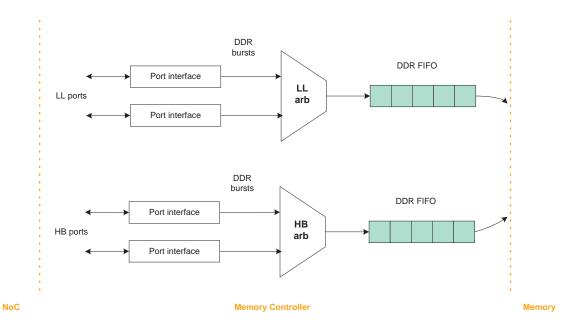

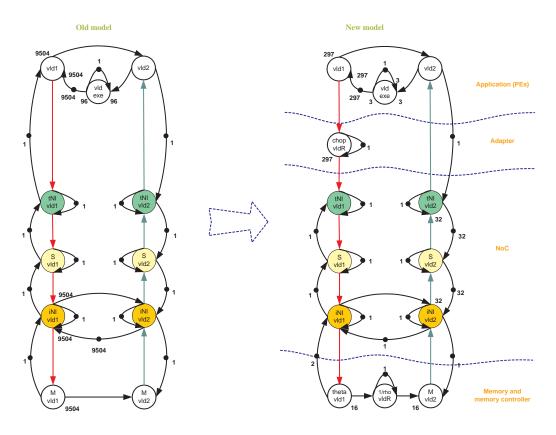

The following communication scenario of the video decoder H.263 is considered: