## MASTER

Extracting SDF from sequential applications for MSPoC and implementation on FPGA

Gielen, T.P.C.

Award date: 2008

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Faculty of Electrical Engineering Section Electronic Systems (ICS/ES) ICS-ES 901

Master's Thesis

# EXTRACTING SDF FROM SEQUENTIAL APPLICATIONS FOR MSPOC AND IMPLEMENTATION ON FPGA.

•

**TPC** Gielen

Supervisor: Coach: prof.dr.H. Corporaal dr.ir. Y. Ha MTD A. Kumar Dr.ir. T.P. Stefanov December 2008

The Faculty of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of Master's Theses

Date:

## Abstract

Future embedded systems have to combine low energy consumption with high computational power. Multi-processors provide a solution and therefore SoC platforms become increasingly multi-processor architectures. Furthermore the number of processors in these architectures rises as well. This implies a shift in emphasis from processor design towards compiler design. A major challenge is parallelising applications to run on these MPSoCs and most methodologies rely on error-prone and time consuming design by hand. This thesis presents a design methodology to extract the parallelism from an application. Synchronous Dataflow (SDF) is used to express the parallelism because it allows easy worstcase behaviour analysis. The SDF graph is derived from an intermediate analysis of the application provided by a tool called DAT. This DAT tool profiles the application and generates an intermediate graph with data dependencies. From that intermediate graph a new tool called C2SDF derives the SDF graph. This include the actors, channels and various properties of the SDF. This output can be used by the MAMPS framework to implement and map the application directly to a MPSoC on FPGA. MAMPS has been prepared to take the generated parallel source code into account. For simple cases the DAT and C2SDF flow can derive an SDF graph. Improvements can be made to the handling of conditional statements and the sharing of variables between potential actors in the input application. The profiling approach is unsafe and requires checking of input applications for conditions on input data values.

# Acknowledgement

I was very lucky to get the opportunity to work for one year on my graduation project at the National University of Singapore. The research done in this excellent environment eventually led to this thesis. I would like to thank my supervisor and graduation professor Henk Corporaal for arranging that great experience for me. I would also like to thank my NUS supervisor Dr. Ha Yajun of NUS for providing a place for me at NUS and giving me valuable feedback in our many meetings.

Special thanks goes to Akash Kumar for helping me in the first months in Singapore and introducing Singapore and his many friends to me. Next to his personal help he also offered me a lot of feedback in numerous discussions allowing me to greatly improve my understanding of the problem. Thanks to him this year in Singapore and the travels to India became a very useful and enjoyable experience.

Furthermore I would like to thank Sean Rul for giving his research tool and support to me. I would also like to thank Dr. Todor Stefanov for giving me insight into the world of models of computation and the discussions about my work. I finish with thanking Shakith Fernando, Abhinav Krishna, Priyantha De Silva and Zhu Guolei for bringing some life into the lab and the members of the ES group for their support and help.

# Contents

| 1 | Intro<br>1.1<br>1.2<br>1.3 | Proble  | n<br>round             | <b>4</b><br>4<br>7<br>7 |  |  |  |  |  |

|---|----------------------------|---------|------------------------|-------------------------|--|--|--|--|--|

| 2 | Aspects of Partitioning 9  |         |                        |                         |  |  |  |  |  |

|   | 2.1                        |         |                        | 9                       |  |  |  |  |  |

|   | 2.2                        |         |                        | 11                      |  |  |  |  |  |

|   |                            | 2.2.1   |                        | 11                      |  |  |  |  |  |

|   |                            | 2.2.2   | Communication          | 13                      |  |  |  |  |  |

|   | 2.3                        | Program |                        | 14                      |  |  |  |  |  |

|   |                            | 2.3.1   | •                      | 16                      |  |  |  |  |  |

|   |                            | 2.3.2   |                        | 18                      |  |  |  |  |  |

| 3 | Prol                       | olem De | finition               | 21                      |  |  |  |  |  |

| 5 | 3.1                        | Paralle |                        | 21                      |  |  |  |  |  |

|   | 5.1                        | 3.1.1   |                        | 21                      |  |  |  |  |  |

|   |                            | 3.1.2   | -F                     | 23                      |  |  |  |  |  |

|   |                            | 3.1.3   |                        | 24                      |  |  |  |  |  |

|   |                            | 3.1.4   |                        | 25                      |  |  |  |  |  |

|   | 3.2                        |         |                        | 26                      |  |  |  |  |  |

|   | 5,2                        | 3.2.1   |                        | 28                      |  |  |  |  |  |

|   |                            | 3.2.2   |                        | 29                      |  |  |  |  |  |

|   |                            | 3.2.3   |                        | 30                      |  |  |  |  |  |

|   |                            | 3.2.4   |                        | 30                      |  |  |  |  |  |

|   | 3.3                        | SDF G   |                        | 31                      |  |  |  |  |  |

|   |                            | 3.3.1   |                        | 31                      |  |  |  |  |  |

|   |                            | 3.3.2   | Functions              | 32                      |  |  |  |  |  |

|   |                            | 3.3.3   |                        | 33                      |  |  |  |  |  |

|   |                            | 3.3.4   |                        | 33                      |  |  |  |  |  |

|   |                            | 3.3.5   | Conditional Statements | 39                      |  |  |  |  |  |

|   |                            | 3.3.6   |                        | 40                      |  |  |  |  |  |

|   |                            | 3.3.7   |                        | 41                      |  |  |  |  |  |

|   |                            | 3.3.8   |                        | 41                      |  |  |  |  |  |

|   |                            | 3.3.9   |                        | 41                      |  |  |  |  |  |

| 4 | Parallelisation engines                 |                                                                   |    |  |  |  |  |

|---|-----------------------------------------|-------------------------------------------------------------------|----|--|--|--|--|

|   | 4.1                                     | FP-MAP                                                            | 43 |  |  |  |  |

|   | 4.2 Compaan & PNgen                     |                                                                   |    |  |  |  |  |

|   | 4.3 SPRINT                              |                                                                   |    |  |  |  |  |

|   | 4.4                                     | Data Analysis Tool                                                | 51 |  |  |  |  |

|   | 4.5                                     |                                                                   |    |  |  |  |  |

|   |                                         | 4.5.1 Requirements                                                | 53 |  |  |  |  |

|   |                                         | 4.5.2 Comparison and reasons for choosing DAT                     | 54 |  |  |  |  |

| 5 | Mul                                     | Multi-Application Multi-Processor Synthesis                       |    |  |  |  |  |

|   | 5.1                                     | Design Space Exploration                                          | 56 |  |  |  |  |

|   | 5.2                                     | MAMPS                                                             | 57 |  |  |  |  |

|   | 5.3                                     | Modifications                                                     | 59 |  |  |  |  |

| 6 | C2S                                     | C2SDF Implementation                                              |    |  |  |  |  |

|   | 6.1                                     | C2SDF                                                             | 63 |  |  |  |  |

|   |                                         | 6.1.1 Output                                                      | 63 |  |  |  |  |

|   |                                         | 6.1.2 Input                                                       | 64 |  |  |  |  |

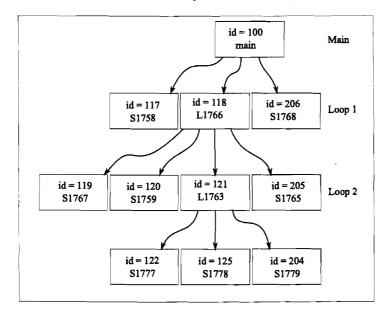

|   |                                         | 6.1.3 Actor values                                                | 65 |  |  |  |  |

|   |                                         | 6.1.4 SDF Graph structure                                         | 67 |  |  |  |  |

|   | 6.2 Experiments, results and evaluation |                                                                   |    |  |  |  |  |

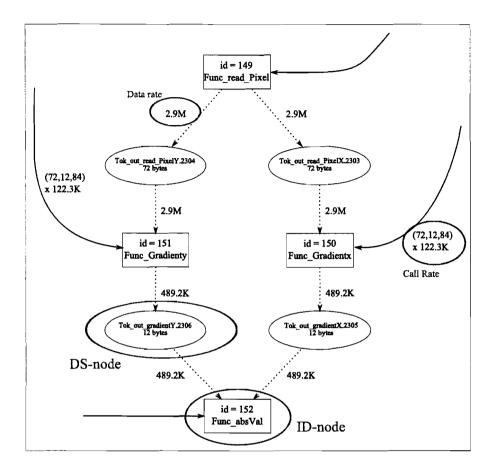

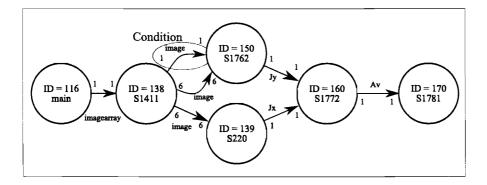

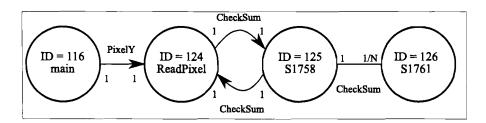

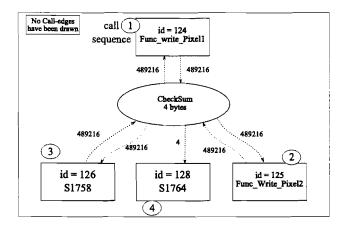

|   |                                         | 6.2.1 Experiment I : A Sobel filter with a single double-for-loop | 70 |  |  |  |  |

|   |                                         | 6.2.2 Experiment II : Multiple double-for-loops                   | 72 |  |  |  |  |

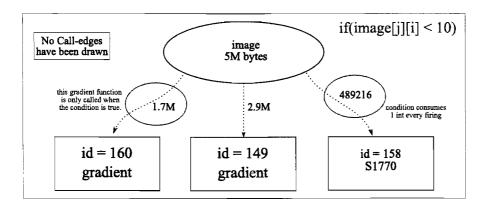

|   |                                         | 6.2.3 Experiment III : Double-for-loops with a condition          | 72 |  |  |  |  |

|   |                                         | 6.2.4 Experiment IV : Limits of DAT                               | 73 |  |  |  |  |

|   |                                         | 6.2.5 Experiment V : Dynamic memory allocation                    | 78 |  |  |  |  |

|   | 6.3                                     | Evaluation                                                        | 79 |  |  |  |  |

| 7 | Rela                                    | ited Work                                                         | 81 |  |  |  |  |

| 8 | Conclusion and Recommendations          |                                                                   |    |  |  |  |  |

# **Chapter 1**

# Introduction

# 1.1 Background

In recent years we have seen an explosion of new devices for domestic or for mobile use. The numerous new devices include smart phones, set-top boxes, navigation systems, multimedia players, PDAs and many others. These types of electronic devices are called *embedded systems*. An embedded system can be defined as a computer system dedicated to a single task or multiple tasks. They are characterised by containing one or more processors. Typically it is part of a larger machine with other mechanical, optical or electronic parts. Basically every modern device in a common household contains one or more processors combined with some of the other parts and can be considered an embedded device. General purpose computers like a Personal Computer are not considered embedded devices because they can be programmed to perform any arbitrary task.

Figure 1.1: Examples of Embedded Systems

If we compare embedded systems designed a decade ago with those designed nowadays, we can see a major difference. In the past the overall majority of embedded devices consisted of devices where the processing unit would take care of the user interface and settings management but most signal processing would be done by independent electronics. Modern embedded systems tend to integrate all functions in a single chip. Additionally there is a shift towards digital signal processing for tasks that would have been done with analog electronics before. So overall we see a trend towards sharply increasing demands for processing power.

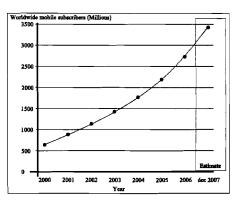

A second trend is the demand for less power consumption. From the early nineties onwards we saw a huge increase in the use of mobile phones which exploded to 3.3 billion mobile phones at the end of 2007 [1]. In recent years we saw a similar trend with portable multimedia players. Many new devices are handhelds running on batteries where the time between battery recharges and weight of the handheld are major points of competition. Therefore when designing these systems we need to consider how to minimise the energy usage.

Third, where in the past a device would have to provide a single application, nowadays it has to provide many. For example a modern multimedia player supports several audio and video standards standards, recording functionality, FM radio and numerous smaller applications like organizers. And these specifications can change with time like recently many manufacturers adding support for MPEG4 in their players.

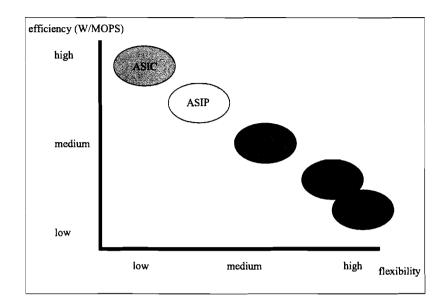

Concluding we can identify three major trends, increasing processing power, less energy consumption and a high level of flexibility. A possible solution for these challenges is the use of ASICs that implement the tasks in fixed hardware being more power efficient. This has as disadvantage its limited flexibility. Consumer and commercial demands for product specifications may change and might require changes to the underlying system design. The solution central to this thesis, is the use of multi-processor systems.

In modern chip design the power dissipation determines the limit on integration on a single chip and not the available area. This implies a design choice for multiple processors running on lower clock speed instead of a single processor running on a high clock speed. The former occupies more area, which is not a limiting factor nowadays, and thus the generated energy can dissipate over a larger area. Another dimension can be the use of multiple simple processors instead of one complex processor.

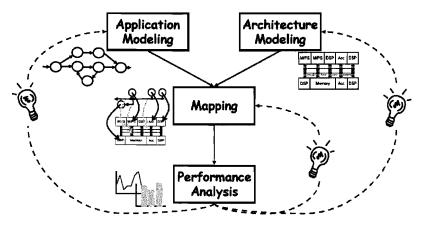

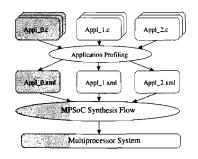

Figure 1.2: Y-chart for DSE

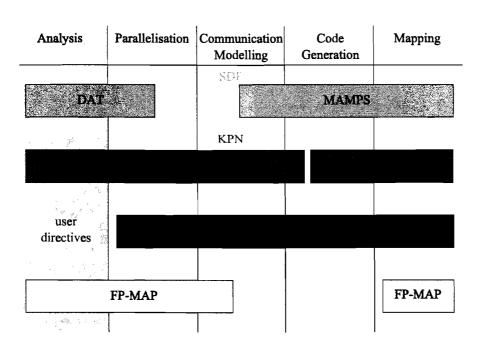

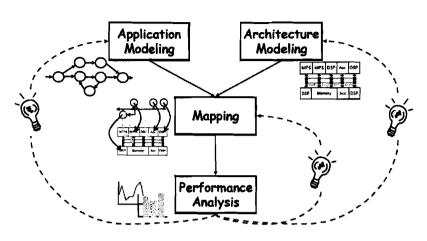

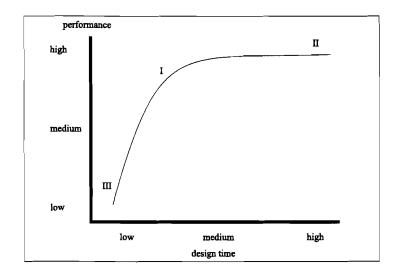

Many parameters come together in the design of new embedded systems. Next to the previously mentioned energy consumption, processing requirements and flexibility, we also must consider limitations due to resource constraints, like available memory, heterogeneous processors (different types of processors in one system), multiple applications and several more. All these lead to a complex multi-dimensional design space. The process of determining a viable solution for designing an embedded system with certain design constraints is called *Design Space Exploration*. A typical approach often followed, is shown in figure 1.2. Exploring by hand is error-prone and time consuming for large complex designs and thus a need exists for an automated approach. The Multi-Application Multi-Processor Synthesis [21](MAMPS) framework is such an automated approach and provides the base of the work outlined in this thesis.

The trend to multi-processor architectures combines the solutions for many of the current challenges, but unfortunately this change does not come for free. The problem we face is the way most software has been written. Typically programmers write software for single processor systems in a sequential way. Except for some approaches with parallel programming languages or parallel extensions to popular existing languages, writing software for parallel multi-processor systems is not a common procedure. If we want to use the huge amount of existing software or offer the possibility to the programmer to write in a familiar style, we have to find a way to split the software over the multiple processors automatically.

To split the software we have to find those parts of it that can be executed at the same time, otherwise it would not lead to a speed-up. We have to analyse the program and extract the parallelism. In order to find the parallelism we need to determine the dependencies in the code. This can be done by either *static or dynamic analysis*. The former analyses the source code where the program is not compiled or executed, the latter measures the compiled program. Static analysis tends to return conservative results because it cannot take input data into account and thus has to cover all possible control paths. On the other hand dynamic analysis, or profiling, knows which control paths have been taken because it executes the program. The problem here is to judge if the followed control paths are constant for different inputs. Certain dependencies only occur when a condition tests true. If that condition depends on the value of input data some dependencies might disappear with different inputs.

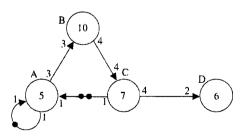

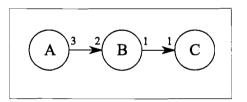

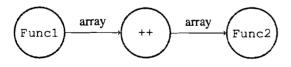

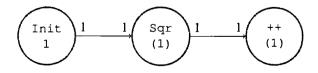

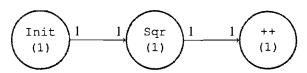

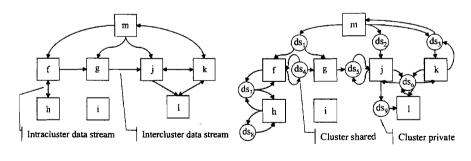

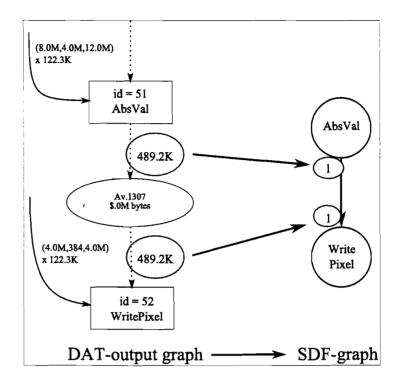

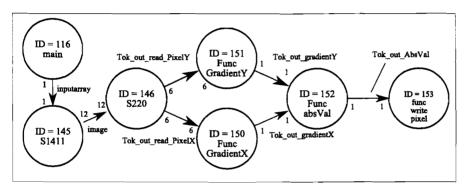

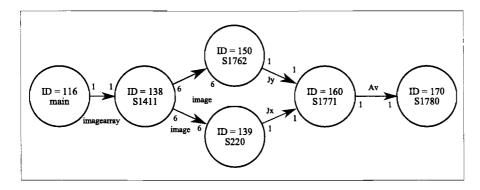

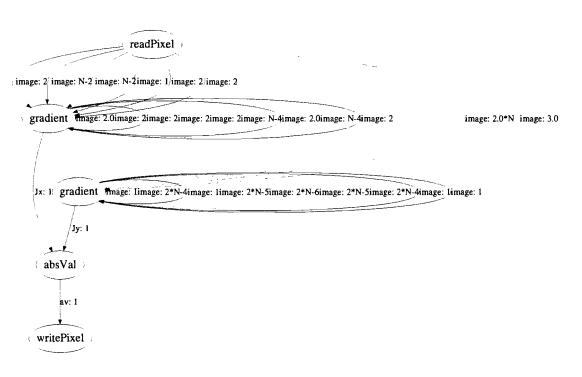

From the analysis we need to derive the actual parallel parts of the program. From the profiling information we can extract the sequence of writing to and reading from memory locations and from that the dependencies. Finally we need a way to present the extracted parallel information. A typical representation used for that is a *Model of Computation* (MoC). We define an MoC as a formal mathematical structure that reflects some aspects of the behaviour of a real-time computational system. One particular MoC and the subject of this thesis is a model called Synchronous Data Flow (SDF). In this thesis I explain how to derive an SDF graph from sequential C source code. Figure 1.1 shows an example of an SDF graph (SDFG).

Figure 1.3: Example of a Synchronous Data Flow Graph

## **1.2 Problem Definition**

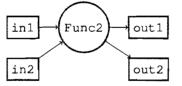

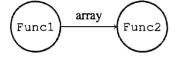

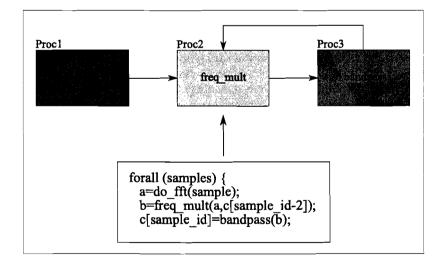

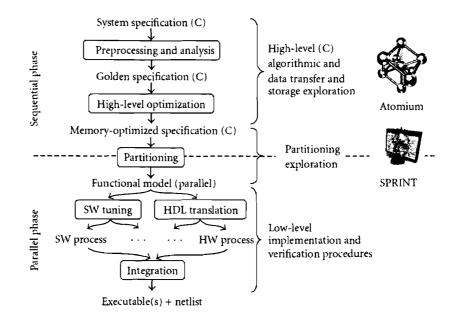

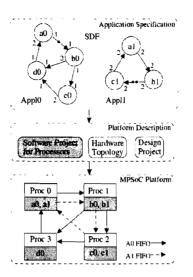

The subject of the work presented in this thesis is about filling the gap between the applications and the SDF specification. More specifically, determining an approach to extract the parallelism from an application written in the C language and specify an SDF graph as output. The tool from this research should be able to generate an SDF description file which can directly be used by MAMPS, which in turn can generate the MPSoC design for synthesis on an Xilinx FPGA. In fact the resulting tool will become an integral part of MAMPS to form a single Design Space Exploration tool. Central to the research is to define how an SDF can be derived from its corresponding source code and which limitations are involved.

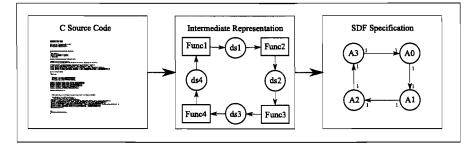

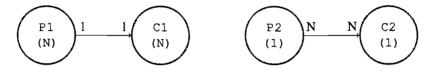

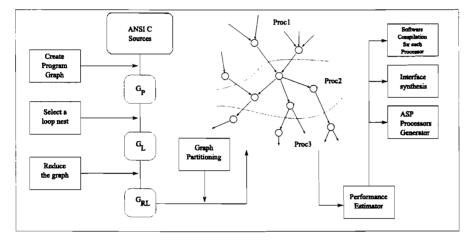

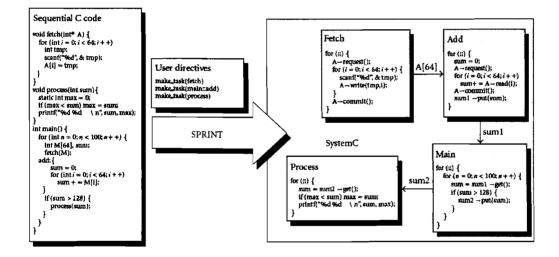

The work can be split in two parts. The first part deals with finding a method to extract the parallelism from the application and express it in an intermediate format. A number of parallelisation engines exist already as partially discussed in Chapter 4, like FP-MAP and PN-gen. Considering the available time for the work and the complexity of the problem making use of one of the existing parallelisation engine seems the pre-ferred choice. Considering the inherent limitations of SDFGs, the set of accepted input applications can also be limited, more particularly limited to DSP and/or multimedia applications.

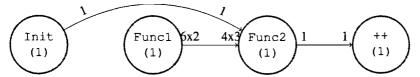

Figure 1.4: Problem overview.

The second part involves deriving the SDF representation from the intermediate format from part 1. The SDF should contain all the common properties and have some support for further automatisation of the flow. Common properties are the actors, channels, worst-case execution time for actors and most challenging, the channel rates. Figure 1.4 illustrates the problem description.

## **1.3 Thesis Organisation**

This thesis is organised as follows. Chapter 2 discusses the various aspects of partitioning. Especially it focuses on the underlying hardware and the communication between parts. Chapter 3 describes the problem definition with a introduction about Models of Computation and describing the limitations of expressing parallelism of both practical and fundamental nature. It continues with an explanation on how to extract the parallelism from the source code and distil an SDF graph. Chapter 4 gives an overview of the related work regarding parallelisation and design tools with multi-processor approaches and explains which tool has been chosen for experimenting. The actual implementation is presented in chapters 5 and 6. Chapter 5 covers the modifications made to the existing MAMPS code and chapter 6 presents the new C2SDF tool. The short chapter 7 gives an overview of the remaining related work. Finally chapter 8 concludes the thesis and gives recommendations for future work.

# **Chapter 2**

# **Aspects of Partitioning**

In this chapter I provide some foundations for the next chapters. I start with an more extensive overview of the various trends introduced in the previous chapter. Then I continue with common hardware architectures in embedded multi-processor systems. After that I describe the two main programming models used in multi-processor systems, Message Passing and Shared Memory Architectures.

## 2.1 Trends

In Chapter 1 I have identified three major trends in embedded systems.

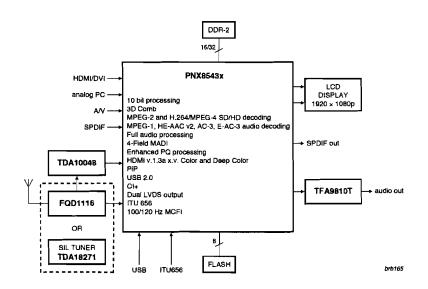

- First I mentioned *rapidly increasing computational power demands*. This has various reasons but the main reason is the implementation of many new multimedia technologies in embedded devices. For example where television for decades were largely analog devices with analog signal processing, we see that nowadays LCD televisions require extensive digital video processing. This is illustrated by example 2.1 which shows the schematic of a chip used in LCD televisions. As can be seen in the schematic, the list of supported techniques for video processing. The amount of required computational power for these applications contrasts heavily with the analog televisions of earlier decades. A second reason for increased demand for computational power is the digitalisation of analog signal processing techniques.

- Second, a trend towards mobile devices is obvious. In recent years especially we have seen an explosive growth of mobile devices such as mobile phones and multimedia players. Figure 2.2 illustrates the growth over the period from 2000 until the end of 2007. We can see identical trends for multimedia devices like iPods. Typical for mobile devices is the dependency on batteries as energy source and therefore it is important for mobile embedded system designer to minimise the energy consumption. A mobile device that needs recharging too soon can hardly be considered mobile. The time between recharging and the weight of the device (largely due to battery weight) is a major point of competition between manufacturers. That means designers have to *limit the energy consumption* as much as possible.

Figure 2.1: Schematic of NXP PNX8543x Home Entertainment Engine

• Third, as already could be seen in the example of the first point, modern devices have to support many different standards and applications. The example of figure 2.1 shows a chip schematic but we can expand that to the feature list of a modern multimedia device such as in figure 2.3. The list of supported standards in the example is extensive and includes next to obvious applications such as video and audio playback also applications like a task planner and a contact organiser. The combination of many different applications on a single embedded device is the third trend we can identify. Additionally the set of applications is subject to changing demands due to marketing and technological advances in general. Manufacturers attempt to share a common platform among all similar products to limit the design cost. However that *requires a certain degree of flexibility*.

Figure 2.2: Growth of mobile subscriptions 2000-2007, source: ITU

| Baltery Life <sup>2</sup> : | Up to 30 hrs audio playtime<br>Up to 5 hrs video playtime                        |                  |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------|------------------|--|--|--|--|

| Video Playback Formats      | MJPEG, WHIVS, MPEG4-SP <sup>3</sup> , DivX <sup>3</sup> 4/5 and XvD <sup>3</sup> |                  |  |  |  |  |

| Audio Playback Formats:     | MP3, WMA, AAC <sup>4</sup> (.m4a), WAV (ADPCM), Audible 2,3,4                    |                  |  |  |  |  |

| Photo Formals Supported:    | IPEG (BMP/GIF / PNG / TIFF) <sup>5</sup>                                         |                  |  |  |  |  |

| Battery                     | Embedded L-ion battery                                                           |                  |  |  |  |  |

| FM Radio:                   | 32 preset stations                                                               | - M 1870 - 🛹 👘 🥾 |  |  |  |  |

| EQ Saltings:                | 8 presets and 5 band custom EQ                                                   |                  |  |  |  |  |

| Geganizae:                  | Calendar, Contact, Task List                                                     |                  |  |  |  |  |

| Power Charging:             | Yes                                                                              |                  |  |  |  |  |

| Allenn Art:                 | Yes                                                                              |                  |  |  |  |  |

| Yoka Recordings             | Yes                                                                              |                  |  |  |  |  |

| Connectivity:               | USB 2.0<br>SD card                                                               |                  |  |  |  |  |

Figure 2.3: Features of a common multimedia player. Source: Creative

# 2.2 Architecture

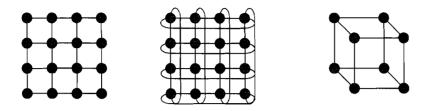

For efficient mapping of applications to an embedded system we need to take the target platform architecture into regard. In general we can split the architecture in two parts. First the processing units like processors, specific hardware accelerators or I/O devices and second the connections between the first. The connections can consist of point to point connections, buses, crossbar switches and Networks-on-Chip (NoCs). The last category contains meshes, tori and cubes.

## 2.2.1 Processors

We have identified three major trends which led to demands for increasing computational power, less energy consumption and a high level of flexibility. A possible solution for these demands lies in the use of ASICs that implement the tasks in fixed hardware being more power efficient. This has as disadvantage its limited flexibility. Consumer and commercial demands for product specifications may change and might require changes to the underlying system design. ASIC designs usually cost several millions and this amount increases with newer technologies like smaller feature sizes. It only pays off to design an ASIC for large production volumes. Another solution uses FPGAs for implementation. This offers maximum flexibility but scores worse on energy consumption, which makes it unsuitable for mobile applications. Also the relatively high pricing of FPGAs make them only suitable for smaller niche markets and not for the typical high volume multimedia consumer products. Yet another option is the implementation of all applications on a single processor. Unfortunately general purpose CPUs don't score very well on energy consumption for specialised tasks. Although general purpose CPUs maximise the flexibility. Figure 2.4 summarises various trade-offs between technologies. The ideal solution would be placed in the upper right corner, maximum flexibility with maximum efficiency. All proposed solutions can be considered a variant of Systems-On-Chip (SoC). These are usually defined as integration of computer components on a single integrated circuit. The components are not limited to digital parts only, but can also consist of analog and mixed-signal parts.

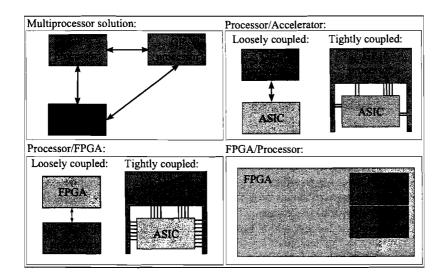

Several solutions have been proposed to approach the trade-off between flexibility and efficiency. Figure 2.5 shows the most common as proposed in [31]. These solu-

Figure 2.4: Flexibility versus Efficiency for various processing technologies. Source: [14]

tions are called *heterogeneous* System-on-Chip designs which are characterised by a combination of two or more blocks from Figure 2.4.

The processor/accelerator couple gains from the speed-up of certain tasks by the accelerator. Data traffic between the two is dependent on the given application. If we use a loosely coupled accelerator, it can be used by several units in the system coupled by a common bus. This set-up is suitable for a low-traffic application. In case of a high-traffic application a tightly coupled accelerator is preferable, directly connected to a host processor and triggered by specific instructions in that processor. Drawbacks we find in the lack of flexibility of the architecture. If we replace the accelerator by an FGPA we partially eliminate the drawback of the combination. We still face the fixed interface between the two parts which restricts optimisation of the architecture and design space. FPGA vendors offer FPGA with integrated processors and often other building blocks such as DSP modules. Unfortunately it hardly provides an optimal solution with regards to efficiency. Application-Specific Instruction-Set Processors gain from the elimination of the interface between accelerator and processor, but require a much more complex design process, including the development of specific compilers.

Trying to reach the optimal solution in the corner of Figure 2.4, a comprised solution central to this thesis, is the use of *multi-processor systems*. It offers lower energy use than FPGAs and general purpose CPUs while retaining some of the flexibility that ASICs lack. It also implies a shift from hardware to software design. The advantage of multiprocessor systems comes from two sources. On one side splitting the computational load over multiple processor allows these processors to run on a lower clock speed and thus be more efficient than a comparable single CPU. This is related to limitations on chip design. Modern applications in chips are limited by the amount of heat that can be dissipated and not by the available chip surface area. Basically the computational power of a chip design is limited by the energy it can dissipate per surface area

Figure 2.5: Heterogeneous architecture types as SoC building blocks. Source: [31]

available. This is advantageous for multiprocessors because running on a lower clock speed while using more chip area reduces the energy dissipation per square surface area. Another advantage lies in the adaptation of certain processors in the multiprocessor design for their particular task. Since specialised hardware in general is much more energy conserving than general purpose CPUs, we can save in that area as well. However it requires that we map that task to that processor, sacrificing some flexibility for energy conservation. A system with only one type of processor is called homogeneous, with multiple types it is called heterogeneous.

Drawbacks are the lack of linear scaling of the performance with the number of processors and the impact of the communication interface on the whole system. On one hand the amount of parallelisation is limited to some degree. I will explain this subject in sections 3.1, 3.1.3, and 3.1.3. On the other hand the performance of the interconnection network will worsen significantly if we keep scaling up. More on that in the next section (2.2.2).

## 2.2.2 Communication

In a multi-processor system running parallel programs we need to transfer information from a source processor to a destination processor. Three main criteria are considered for this task:

- 1. Minimize latency.

- 2. Support a high amount of concurrent transfers.

- 3. The network should be inexpensive compared to the processing units.

In this context we define a number of concepts. A *link* is the physical wire on which a signal gets transmitted. On one end a transmitter converts digital values into analog signal which are converted back by the receiver at the other end. In the OSI model

of network design this protocol for conversion forms the lowest layer in addition to all electrical and physical properties. The combination of the transmitter, link and receiver is called a channel. The link-level provides the segmentation into packets or messages for the network. Channels can be connected to switches as well and those switches use the information in the packets for forwarding to the final destination.

I will discuss shortly the most commonly used connection approaches [5].

- First there is the well-known *bus*. It typically uses a single shared medium for communication between the connected devices which is split in control, data and address signals. For deciding access to the bus it requires an arbiter following a protocol for priorities. The arbiter decides which device becomes master when two or more device require simultaneously access. A bus can be either synchronous or asynchronous. The former shares a common clock among all devices on the bus but allows for less complicated logic. The latter gives more flexibility to the connected devices but requires handshaking protocols implemented [7].

- Another approach is the crossbar network which avoids the main disadvantage of the bus. It allows multiple concurrent communications instead of a single as in the case of the bus. The crossbar consists of many small switches organised into a grid and has N inputs and M outputs. That allows for min(N, M) of connections without overlapping. Typically these crossbars are used in small-scale shared memory multiprocessor systems to let each process read from a different memory at the same time. A simple arbiter is included for the occasional situation when two processors read from the same memory.

- The third category are *Networks-on-Chips* (NoC), to which several types belong. Some of the more important ones are the *mesh*, *torus*, *cube* and the *tree*. As shown in figure 2.6 a mesh is a *n*-dimensional network and can be defined as an interconnection structure that has  $K_1 \times K_2 \times \cdots \times K_n$  nodes where *n* is the number of dimensions of the network and  $K_i$  is the radix of the dimension *i*.

The torus has wrap-around connections to turn every axis into a circular bus. The cube is a particular form of a 3-dimensional mesh. All these networks require some kind of routing mechanism. For example *dimension-ordering routing* the message travels in dimensions in a consecutive order. Other routing mechanisms include *dimension reversal routing*, the *turn model routing*, and *node labelling routing*. MPSoCs with mesh networks perform efficiently for many scientific computations and scale very well. Finally in the tree network, nodes exist in a hierarchical network. Every node (except the root) can have multiple children and a single parents. Communication between children always requires sending a packet to the common parent first.

## 2.3 Programming Model

In this section I discuss the general concepts relevant for the work in this thesis. The first concept is the programming model. Culler [5] describes the programming model as the conceptualization of the machine that the programmer uses in coding applications. It specifies how parts of the program running in parallel communicate information to one another and what synchronization operations are available to coordinate

Figure 2.6: Mesh, Torus and Cube. Source: [5]

their activities. On top of the programming model the designer writes the applications. Programming models range from a system similar to modern multi-processor desktop systems, where multiple processors execute a number of independent sequential programs to more advanced parallel programming models such as shared memory/address, message passing and data parallel programming.

These models can be described as:

- Shared address programming where one can communicate with others by posting information at known, shared location.

- Message passing where information from a specific sender is sent to a specific receiver.

- Data parallel processing where several processing units perform an action on separate elements of a data set simultaneously and then exchange information globally before continuing.

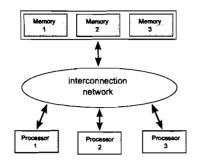

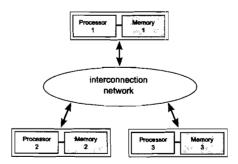

These programming models offer us the possibility to implement parallel applications on a parallel system. However they don't give us a way to express the parallelism in an application. The following sections describe the two most common basic programming models for multi-processor systems, Shared Memory and Message Passing Architecture. When mapping an application to a multi-processor system we face a dilemma. If we consider a computer program as an assembly of dependent tasks, we see that a task might require data from another task. We call this requirement a dependency. This dependency represents actual data which we have to transfer between the tasks. In a single processor system the program runs with a single memory and there is obviously no requirement for transferring the data. However when we run the parallel program on a multi-processor system we need to actually transfer the data to other processors. The first proposed architecture is very similar to the original single-processor system. All processors share a common memory accessed through an interconnection network as shown in Figure 2.7. Communication between processors occurs through shared memory locations. From the figure we can easily see the major disadvantage of this solution, all memory communications share a single connection. The memory access becomes quickly a bottleneck when scaling the design. Subsection 2.3.1 gives a more detailed overview of the shared memory architecture and its (dis)advantages.

An alternative architecture is called *Message Passing Architecture* (MPA), in which all processors have their own local memory. The bottleneck to a single memory does not exist but the communication between tasks/processors becomes much more complicated. As shown in Figure 2.8 a typical MPA system consists of multiple processors with each its own memory, all connected by an interconnection network. Because it lacks a shared memory, data must be passed to other processors by other means. Every processor can send packets with data to the other processors through the interconnection network. Typically some addressing system is required to assure packets arrive at the right destination. Subsection 2.3.2 deals with MPA in more detail. When using a suitable interconnection network MPA scales much better than Shared Memory but it is not straightforward to get functional communication between the processors. Every processor requires code to be added for handling the communication.

## 2.3.1 Shared Memory

A shared memory model is defined as a model in which the processors communicate by reading and writing locations in shared memory. These locations are equally accessible to all processors. Next to the common memory processors can have local memories as well, for instances caches are widely used in Shared Memory models for performance reasons. We can identify 3 properties that a shared memory system needs to function correctly.

- Access control manages the access of processes to resources. If a processor wants to access a shared memory location the access control checks whether it is possible. It usually keeps track of accesses in a table and blocks any attempt until the resource has been cleared.

- Synchronisation provides a set of rules to ensure system functionality and that information flows properly. For example it can limit the time processors can use a resource.

- Protection takes care of shielding processes from memory locations of other processes.

The two main challenges for designing a shared memory system are performance degradation due to contention, and coherence problems. When too many processors want to access the memory it becomes a bottleneck. The most common solution adds caches to the processors to solve the problem. In an extreme case contention can be reduced to zero when all data is stored in the local caches. Unfortunately this creates the other problem, coherence. If there are multiple copies of data, in the caches and memory, it might lead to coherence problems. Incoherent means that not all copies are equal because a processor has overwritten a particular copy. Several solutions exist to solve this problem, but these are beyond the scope of this thesis.

#### Hardware

A simple shared memory system consists of a single dual-ported memory connected to 2 processors. An arbiter inside the memory decides which processor gets access to the memory. In case only a single request is received, it will be granted and the processor gains access to the memory. The status of the memory will be set to busy. Any request from the other processor will be put on hold as long as the other is being serviced.

We can identify two major classes of Shared Memory architectures, Uniform Memory Access (UMA) and Non-Uniform Memory Access (NUMA). In an UMA system all processors can access the shared memory through an interconnection network. In

Figure 2.7: Shared Memory Architecture.

this way it is very similar to the way a single processor system accesses its memory. The interconnection network can be a bus, multiple buses or a crossbar switch. Because of the balanced memory access these systems are referred to as Symmetric Multi-Processor systems (SMP). It is a very popular architecture in shared memory systems. The second class NUMA differs from UMA in the way the memory is organised. For NUMA each processor has its own part of the shared memory directly attached, but still the whole system has a single address space and therefore all processors can access any memory location. Obviously the access times depend on the distance to the processor and that leads to non-uniform access times. The interconnection network can be formed by a tree or a hierarchical bus network.

#### Software

The parallel programming of Shared Memory systems is similar to the programming of operating systems and general multiprogramming. It can be done by extensions of existing programming languages, operating systems, and code libraries. In a parallel program we must be able to identify three constructs:

- 1. *Task Creation* We can divide the task creation in coarse- and fine-grained levels. On the coarse level the shared memory system can provide time-sharing, where new processes are assigned to the processor with the least amount of work. In case the process is a large task with page tables, memory and file descriptions in addition to the program code and data the process will have a high overhead and is most suitable for heterogeneous tasks. The fine-grained tasks are more suitable for homogeneous tasks and allow parallelism in single applications. This pattern is called supervisor-workers model.

- 2. Communication Parallel and sequential processes don't have identical memory spaces. Where a sequentially executing process has 3 segments called text, data and stack, a parallel process has an additional segment called shared data. In the text segment the process stores the binary code for execution. In data the program's data is stored like variables and in stack dynamic data is stored, like the data to be stored when calling a function. The latter two expand and contract while executing the program and have a gap between them. There is no sharing of addresses between processes, except for parallel process by means of their shared data section. This shared data section is located between the data and

stack segments and can also change sizes. Communication can be performed by writing or reading to variables in these shared data sections.

3. Synchronisation Because it is undetermined what happens if two processes write the same variable simultaneously, we require a mechanism to avoid this. This synchronisation mechanism must provide mutual exclusive access to processes. It also coordinates the execution of parallel processes and can synchronise at certain points in execution. It uses two main synchronisation constructs, locks and barriers. A lock blocks access to other processes while a process accesses the resource. A barrier blocks a process until all other processes reach the same barrier.

## 2.3.2 Message Passing Architecture

The main difference of the Message Passing Architecture (MPA) model to the Shared Memory model lies obviously in the lack of a shared memory. Every processor in MPA has its own local memory and communication has to happen through send and receive operations. The combination of a processor and its memory is typically called a node. A node has the ability to store message temporarily in buffers until it can be sent or received. Processing can happen at the same time as sending or receiving. The nodes are connected by an interconnection network which can range from an architecture-specific structure to a world-spanning network like the internet. A major advantage is the high scalability without significant decreases in efficiency.

## Hardware

Various networks are used for connecting the nodes, these include hypercubes, 2D and 3D mesh networks. When designing these networks the most important design factors to consider are link bandwidth and network latency. We define the link bandwidth as the number of bits that can be transmitted per unit time. The message latency stands for the time needed to complete a message transfer. On top of this principal improvements have been made such as wormhole routing where messages are sent in parts to reduce the required buffer size.

Figure 2.8: Message Passing Architecture.

When executing an application, the program is divided into concurrent processes that are executed on separate processors. In case that there are more processes than processors, some processes have to share a processor in a time-sharing fashion. Communication between processes running on the same processor use internal channels to exchange messages. Communication with processes on other processors use external channels. We define a message as a logical unit for inter-node communication. It is considered a collection of related information travelling together. It can consist of instructions, data, synchronisation, or interrupt signals. There is no sharing of data, only copying and sending in messages. This way of communication leads to performance gains because there is no need for synchronisation constructs. Another advantage is the excellent scalability. A large number of nodes can be included in the system without significant performance issues. A node can execute multiple processes and they usually are of medium or coarse granularity.

The technique to find a path in the network from origin to destination is called routing. A more formal definition according to el-Rewini: routing involves the identification of a set of permissible paths that may be used by a message to reach its destination, and a function, h, that selects one path from the set of permissible paths. One way to classify routing techniques is whether they are adaptive or deterministic. Adaptive techniques decide their path based on current network conditions, deterministic use only the source and destination information. Deterministic techniques can possibly be inefficient. Another classification method is based on where the routing decision is made. Either centralised, where the path is decided before sending or distributed, where every node decides itself about the next destination. Centralised routing require knowledge of the whole network contrary to distributed that only requires knowledge of the neighbouring nodes.

Routing is not without problems. The three most important problems include *deadlock*, *livelock* and *starvation*. Deadlock can occur when two messages hold the resources required by the other one. This happens whenever a cyclic dependency exists for resources. A flow control mechanism can be used to avoid this situation. The most simple but inefficient solution is to allow re-routing of messages or resending messages. The second problem livelock happens in an adaptive routing system when a message never reaches its destination because of continuous re-routing due to network contention. It can only occur when using dynamic injection routing, which allows nodes to transmit messages at any arbitrary time. A possible solution makes use of priorities for message routing. Finally starvation occurs when a node never gets the opportunity to send messages. Also starvation can only occur in dynamic injection systems. The solution here is to keep track of a queue for send and receive operations.

The mechanisms used for remove data from an input channel and place it on an output channel we call switching mechanisms. The chosen mechanism has a high influence on the latency. I give a short overview of the various mechanisms:

- In *circuit-switching* the whole path for the message is determined beforehand and all links are reserved. This eliminates the need for buffering. After the transfer the path is released for other messages. It guarantees a maximum routing latency and a certain bandwidth. It is advantageous to use it in a system with a large number of message transfers.

- Alternatively in *store-and-forward (packet-switched)* switching the message is split in smaller parts, called packets. A complete path might not be available at transmission start, but packets are moved from node to node as links become available.

- Store-and-forward (virtual cut-through) is similar to packet-switched but when a

packet arrives at a node, it is forwarded if channels are available without waiting for the whole message. Because unnecessary buffering is avoided this gives an advantage regarding latency.

• With *wormhole* routing the packet is further split into smaller units called flits. The first (header) flit finds a way through the network and the following flits cannot overtake it. It results in an latency independent of the path length and requires less storage than the other techniques.

## Software

Next to the underlying hardware we also require software support to run the communication. Usually a message passing architecture uses a set of primitives that allow the processors to communicate. Typical primitives are send, receive, broadcast and barrier. The basic programming model attempts to match a send in one processor with a receive in another processor. These commands are blocking, meaning that send blocks until receive is executed. In a blocking architecture we need to implement a 3-way communication protocol, involving a *request-to-send* by the sender, a *ready to receive* reply by the receiver and finally the *data transfer*. This protocol takes a long time to complete because it involves a full round trip. That means the sender and receiver are blocked during that time and for that reason most MPAs utilise a non-blocking operation. The send appears immediate for the user program, although the message layer buffers the message until it can be transmitted. At the receiver's side the message is buffered until it can be received in the program. Popular software implementations are *Pthreads*, *CSP* and *MPI*.

The first implementation *POSIX Threads* (Pthreads) is a library that offers programmers the possibility to create, manipulate and manage threads, as well as techniques for synchronisation between threads. Threads can be described as the execution state of a program instance with just enough properties to be able to run independently. Pthreads provides a standardised implementation of threads for UNIX, BSD and Windows operating systems. It requires design by hand and offers little analysability.

Another approach is *Communicating Sequential Processes* (CSP) [29]. CSP uses formal methods to describe a system in terms of component processes and events. These processes are independent and interact through message-passing communication. Processes can be both sequential and parallel. The designer specifies the whole behaviour of the system in terms of algebraic operators. The events represent communications or interactions. CSP is strong on modelling and analysing systems with complex communication behaviour.

Finally it is worth mentioning the *Message Passing Interface* (MPI). MPI provides a standard library of routines for writing portable and efficient message passing programs. It is not a language but programs can call its functions to simplify the programming of message passing architectures. Included are many point-to-point communication routines and operations for data movement, global computation, and synchronisation. MPI has been extended in the MPI-2 standard which adds support for dynamic processes, client-server support, one-sided communication, parallel I/O, and non-blocking collective communication functions. An MPI application consists of a collection of concurrent communicating tasks. This program includes code, written by the application designer, that calls standard functions in the MPI library. Every tasks receives a unique rank to identify it in the network. This rank can be seen as an address. The tasks run both on single processors and multi-processors.

# **Chapter 3**

# **Problem Definition**

## 3.1 Parallelism

The trend to multi-processor architectures offers a promising solution for many of the current challenges, but unfortunately this change does not come for free. The problem we face is the way most software has been written. Typically programmers write software for single processor systems in a sequential way. Except for some approaches with parallel programming languages or parallel extensions to popular existing languages, writing software for parallel multi-processor systems is not a common procedure. If we want to use the huge amount of existing software or offer the possibility to the programmer to write in a familiar style, we have to find a way to split the software over the multiple processors automatically.

Many computer programs used in embedded and desktop systems fall into the category of sequential programs. They have not been optimized for use in a multiprocessor system. This wastes a large part of the potential computing power of the multiprocessor system because the program only keeps a single processor occupied. Obviously this could have a negative impact on the performance of the system as well. Some code might execute faster on a certain type of processor. In this and the following subsections I will provide a theoretical foundation for parallelism.

### 3.1.1 Dependencies

#### **Data Dependencies**

We can view a sequential program as long chain of instructions. In a fully parallelised program all these could be executed independently. The other extreme is the situation where all instructions would depend on each other. The defining factor here is whether instructions read and write the same data. In other words, dependencies between instructions exist when one writes to a particular data location and the other reads from it [2] [16]. I'll explain here the work of Bernstein.

Let us consider a sequential program which consists of a set of  $P_1, P_2, ..., P_k$  of program fragments. Every fragment can contain multiple instructions. For every fragment  $P_i$  we define an input set  $I_i$  with all variables read by  $P_i$ . Similarly we define an output set  $O_i$  for all variables written by  $P_i$ . Bernstein considers two fragments  $P_i$  and  $P_j$  independent and parallel executable if they satisfy his three conditions:

1)

$$I_j \cap O_i = \emptyset$$

,

2)

$$I_i \cap O_j = \emptyset$$

and

3)  $O_i \cap O_j = \emptyset$ .

which means that the inputs of one fragment cannot be the output of another fragment if the fragments run in parallel (first 2 conditions). The third condition specifies that the outputs of parallel fragments must be different.

A violation of each Bernstein condition leads to a certain type of dependency:

- 1. Flow dependence: when the second fragment uses an result produced by the first fragment. Violation of the first condition.

- 2. Anti-dependence: when the second fragment overwrites the result of the first. Violation of the second condition.

- 3. Output dependence: when both fragments write to the same variable the second fragment must provide the final value. This is a violation of the last condition.

#### **Control Dependencies**

Next to data dependencies we also have to take control dependencies into account. They form a problem when the condition is data-dependent. It occurs when a statement gets executed only if a condition is true and this condition is determined in a previous statement. It is possible to convert a control dependency to a data dependency. In some languages a special keyword exists like where in Fortran 90 to to split the original ifthen-else contruct. In C no such keyword exists, but one can split the if-else construct into loose and independent if statements. In the case of nested if statements the new conditions will be the logical-and of all nested if statements.

#### **Resource Dependencies**

The third kind of dependency is about the underlying hardware. In case code requires access to a certain type of hardware like a divider or FFT block, two fragments cannot access at the same time and thus cannot be considered to be parallel. It applies mainly to heterogeneous SoCs with dedicated hardware for certain tasks. It is considered more a scheduling problem than a parallelising problem.

#### Variable Names and Pointers

Up to this point it we did not discuss how to deal with the variables in the input and output sets. These variables have been kept abstract but in fact they represent a location in the system's memory. At compile time variable names get assigned to this memory location and the program uses that information every time it is executed. However this does not cover all situations. In C the use of pointers is very common and usually pointers get assigned at run-time. Because of this connection between names and memory locations we cannot determine all dependencies at compile-time. Signal processing applications depend heavily on arrays for their algorithms and in C the difference between pointers and arrays is small. Thus for this class of applications the problem could be considerable.

## 3.1.2 Granularity

#### Loops

Loops are especially for signal processing applications of high importance. Many applications require repeated execution of the same processing steps, so obviously these programs contain loops. For a loop we can define a dependence distance between two statements. The formula for this distance D is equal to  $D = \lambda - \kappa$ , where  $\lambda$  and  $\kappa$  stand for integers calculated by taking the indices of the arrays called in the loop. D being equal to zero corresponds to a intra-loop dependency, i.e. one that would also exist without a loop. D being one or larger means that the dependence is loop-carried or an inter-loop dependency, i.e. it will carry on to one of the consecutive iterations of the loop. A D of 2 means that a particular array location gets read 2 iterations after it was written.

#### Nested Loops

For nested loops the problem gets more complicated. In the equation for simple loops we substitute all variables by vectors. In addition to the dependence distance vector  $D_{Dist}$  we also get a dependence direction vector  $D_{DirV}$ . The latter indicates how a particular dependence in the  $D_{Dist}$  vector behaves, i.e. if it crosses over to other iterations. If no dependence distance vector exists the statements can be executed safely in parallel. In general there are two widely used graphs to show these dependencies:

#### **Dependencies and FIFOs**

Loops follow a certain pattern for accessing memory locations in their body. Often this pattern is straightforward with the index variable running from 0 to N incrementing by 1 every iteration. With a nested loop the pattern follows usually row after row. If we have two or more consecutive nested loops and a statement in the second depends on a statement the first sharing the same memory location the situation can occur that the second nested loop requires data from the first which has not been processed. In a sequential program the problem does not occur because the first loop completes before the second. Obviously you need then a relatively large buffer for the intermediate data. In a parallel system where we cannot assume that the previous loop has been completed we have to assure that the second doesn't have to wait for the first to send the correct data packets. In practice this can mean that the sequence of data calculation should be carefully scheduled according to the read and write sequence of the two loops or that a large enough buffer gets included which would at the same time eliminate the parallelism.

#### Functions

Next to loops we can look at the structure of a program also in a different way. A function is defined as a portion of a program which performs a certain task relatively independent. Functions serve both the readability of a program and the reduction of code size and its compiled binaries. A function takes a number of parameters as input and can return a single value back to the calling function. Parameters can act as inputs or outputs by using call by reference.

#### Statements

Another level of granularity are statements or the set of statements which we call snippets. They form a set because they can be grouped together with a common set of dependencies. A function consists of a number of statements. If no dependencies interfere a number of snippets can be executed in parallel, similar to functions and loops.

### 3.1.3 Measuring Parallelism

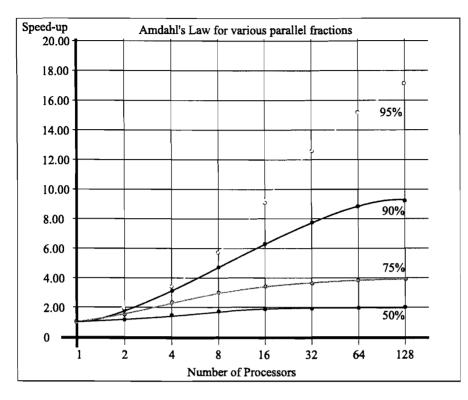

#### Amdahl's Law

One of the most fundamental questions for parallelisation is how much parallelism we can expect. Amdahl's law is a simple and general model for the expected performance after parallelisation. Basically it provides a measure for the percent speed-up of the parallelised performance compared to the full sequential performance. It is important to realize that not every part of a program can be fully parallelised. The following formula is Amdahl's law for the speed-up:

$$S_{Parallel}(f,n) = rac{1}{(1-f) + rac{f}{n}}$$

- with n the number of processors.

- with f the fraction of a program which can be parallelised.

A modern version of Amdahl's original law is [15]:

$$S_{enhanced}(f,S) = \frac{1}{(1-f) + \frac{f}{S}}$$

with S the speed-up of fraction f.

Figure 3.1 shows the speed-up for different percentages of the parallelised part.

For the problem definition we can draw the conclusion that parallelising a small portion of the total program already can lead to a significant speed-up, but the total execution time of the program after parallelisation can never be smaller than that part that cannot be parallelised.

### Gustafson's Law

The disadvantage of Amdahl's law is that it assumes a constant problem size. In practice we solve larger problems with larger computers. Gustafson [13] proposed his law where the sequential part is independent of the problem size. He assumes that the parallelism increases with the problem size. Where Amdahl assumed the execution on the serial system to take 1 unit of time, Gustafson assumes that the execution on the parallel system takes 1 unit of time. The time spent on the serial system is equal to  $N(1 - F_s) + F_s$ , which leads to a speed-up of:

$$S = N(1 - F_s) + F_s$$

$F_s$  is the time spent in sequential code. N is the number of processors. Now the speed-up scales up with the number of processors.

Figure 3.1: Speed-up for different percentages of the parallelised part. Source: [15]

## 3.1.4 Partitioning

Generally parallelism can be exploited on several levels. The most common are the Instruction-Level, Data-Level and Task-Level parallelism.

## **Instruction-Level Parallelism**

Instruction-Level Partitioning (ILP) exploits the situation where two or more instructions are independent of each other. It allows these independent instructions to be executed simultaneous or in reversed order. As the name suggests this parallelism occurs on the instruction-level and is typically addressed on the processor architecture level. This includes both improvements in the field of compilers and processor architecture design. Typically scientific applications have a large amount of ILP contrary to application like cryptography. Several techniques and processor architectures have been proposed to exploit the ILP. These include the well-known Instruction Pipelining where multiple instructions executed in parallel by using different parts of the processor. It makes more efficient use of the processor resources by keeping them almost fully occupied. Superscalars where the processor contains multiple instantiations of each of the basic building blocks like instruction fetching unit or ALUs. Out-of-order Execution allows changing the program execution order to avoid idle cycles because of delay due other instructions.

### **Data-Level Parallelism**

Data-Level Parallelism (DLP) exploits the parallelism in program loops. The idea is to split the data among separate processing units performing the same calculations on different parts of the input data. For example processor 1 can process the first 50% of the data set, processor 2 takes care of the second 50%. Both processors execute in parallel and optimally they finish in half the time.

#### **Task-Level Parallelism**

In contrast with DLP *Task-Level Parallelism* (TLP) splits along the lines of different tasks. It assigns in general different tasks to each of the various processors. For example in a program with two tasks, task A and B, processor 1 will process task A, task B will be processed by processor 2. Most applications show some degree of both Task-Level and Data-Level Parallelism, including the work presented in this thesis.

## 3.2 Models of Computation

In the previous sections I elaborated about models for implementing parallel applications. These models are of high practical use but are limited in analysing the properties and behaviour of a parallel program. The numerous steps in the design of a new product often require some form of modelling. We use functional modelling for specifying the functional behaviour and performance modelling for determining other characteristics of the system. The correct behaviour of the final implementation is validated to its specifications.

Since the real product is not yet available while designing and prototypes are prohibitively expensive we have a clear need for models. Modern electronic products might need hundreds of models which makes prototypes even less attainable, but we still want a optimum solution with correct timing and minimum use of resources. This would lead to a time consuming and error-prone design space exploration (DSE) by hand. Furthermore modern designs are so complex that we need mathematical models to realise predictable designs. The formal features of mathematical models guarantee certain properties and allow us to use efficient synthesis tools. Before we give a definition of such models of computation we first explain the building blocks.

The basic concepts of MoCs are processes, events and signals. Events are the elementary units of information exchange between processes. Processes receive or consume events, and they send or emit events over a medium called signal. One process at a time can only emit into a signal but multiple can receive. Also the order in which events are received is preserved. This is not unlike how digital logic behaves.

Internally processes are divided into evaluation cycles. This cycle consists of a consumption of input events, computation of the new internal state and emission of the output events. Only the rules of the MoC limit how a process can be modelled. Components of the process are the initial state, an output encoding function and a next-state function. During an evaluation cycle the process consumes exactly one input event for each incoming signal and produces exactly one output event for each outgoing signal. There are two more concepts to introduce: Process constructors and combinators. The former is similar to the C++ constructor because it defines a process and its properties. Examples include a constructor with one input and one output, another one with no internal state and one with an internal state. The properties are determined by the parameters of the constructor and include how the next-state function, the output

encoding function and other properties behave. The latter, combinators, allow us to compose process networks out of simpler parts. The combinators are parallel composition, sequential composition and a feedback operator. We are now ready to define a Model of Computation:

A Model of Computation is defined as the set of processes and process networks that can be constructed by a given set of process constructors and combinators.

Furthermore, we also define a untimed MoC:

An untimed Model of Computation is characterised by the absence of timing information for use by processes.

Finally we need to define the behaviour of a process and how it interacts with other the signals. We represent this functional behaviour by the characteristic function and the signature of a process. The characteristic function determines the behaviour in each evaluation cycle. The process signature describes the input and output behaviour. Uprating a process means that it consumes and produces twice as many events in each cycle, identical to execute the process twice.

Processes communicate with other processes by writing to and reading from signals. Events represent the value or are values themselves. We mention three types of events: Untimed, Timed, and Synchronous events. Untimed events only contain values, timed and synchronous events include a time value, where timed events occur at a much finer granularity. Timed events are used for psychical times like nanoseconds while synchronous are used for abstract time values such as clock cycles. Signals are sequences of events. Other properties are that they are ordered, can be finite or infinite, and three types exist: untimed, synchronous and timed. We can consider processes as functions because for a particular input signal we'll always get the same amount of output signal. This still allows processes to have an internal state. The resulting output event might not have the same value at different times though.

Three important properties of processes are monotonicity, continuity, and sequentiality.

- *Monotonicity* indicates that more input data leads to more output data without changing the data that has been output already. For example a sorting process is not monotonic because a new input value would change the sequence of the current output.

- Continuity allows a process to start producing output before all input events have been received.

- Sequentiality involves processes with more than one input and a process is sequential if the inputs are not independently processed. It means that if a process is waiting for an event on one signal, it does not consume more events on any other signals. We say the process blocks then.

- Another concept related to processes is the *characteristic function*. This function defines the relationship between the input and output signals. The function generates all output signals of the process and a process can have numerous characteristic functions.

Several models of computation are suitable for designing multimedia applications. These models differ in aspects like expressiveness and analysability. Obviously designers have to make trade-offs between thee aspects. We will take a closer look at two MoCs, Synchronous Dataflow and Kahn Process Networks.

## 3.2.1 SDF

Synchronous Dataflow (SDF) is a special case of the untimed model of computation, where, to avoid confusion, synchronous has the meaning of static or regular. Its main advantage lies in the suitability for multimedia applications due to its high level of analysability, but its disadvantage is the limited expressiveness. Typical of an SDF is the constant relationship between input and output. Processes always consume and produce the same number of events on their signals, in other words the data rates are constant. This constant behaviour makes SDF very suitable for modelling applications. SDFs are monotonic, sequential but not continuous.

monotonicity, continuity, and sequentiality

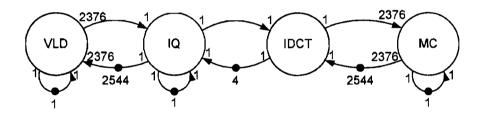

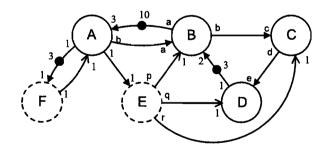

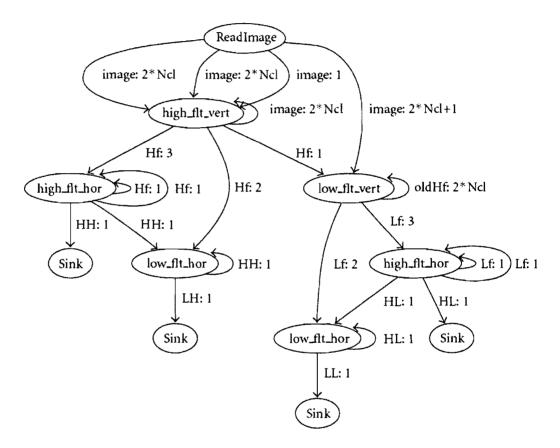

Figure 3.2: The SDF model of an H.263 decoder. Source: [12]

Depending on available resources each process can either be mapped to its own resource like a processor or custom hardware block, or usually several processes will share a single resource. Basically possibilities range from one resource per process to all processes on a single resource. When sharing resources we need a way to divide the resources. The two principal ways of *scheduling* are *static* and *dynamic* scheduling. Static scheduling precomputes a schedule while dynamic computes a schedule during runtime. Obviously dynamic scheduling is more suitable for less predictable systems but also causes significant overhead. The predictability of static scheduling fits SDF quite well. In fact if a static schedule exist for SDF, it can always be found. The schedule will be applied periodically since inputs streams will be very long or possibly infinite.

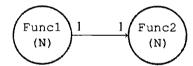

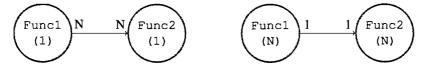

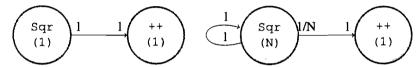

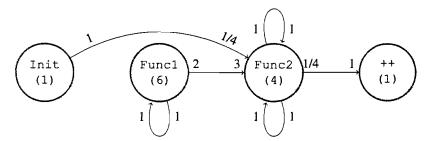

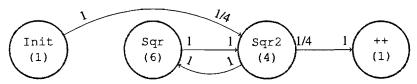

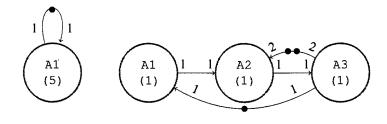

The naming for SDFs is different from the untimed MoC introduced in the previous section. We call processes in an SDF graph (SDFG) *Actors*, signals become *Channels* and events become *Tokens*. Tokens already present at the start are called *Initial Tokens*. Figure 3.2 shows an example of an SDF graph from [12]. This SDFG represents an H.263 decoder, which is a video codec often used for video-conferencing. We see four actors VLD, IQ, IDCT and MC each performing a part of the frame decoding. The channels between the actors have two numbers assigned, the channel rates. Actor VLD produces 2376 tokens for every firing and consumes 2376 on the incoming channel. A firing is a single execution of an actor and for each firing it also consumes a token on the self-channel which represents the data crossing the iteration boundary. Actor

firings are atomic operations and cannot be interrupted. The duration of the firing is set by a property called execution time. A token models a particular amount of data, which is not necessarily identical for all channels in the graph. Initial tokens are modelled by the black bullets on the channels. They are necessary to execute the SDF graph because without any initial tokens no actor would have tokens on its inputs and would thus not fire. The four initial tokens on the channel from IDCT leftwards to IQ model the buffer sizes of the rightward channel from IQ to IDCT. In case IQ fires more often than IDCT it can consume the four initial tokens. After it runs out of these four it has to wait until IDCT outputs a new token. In this way we model a four-position buffer for the rightward channel because the channels in SDFGs have no value for buffer size. The H.263 example displays the expressiveness of SDF graphs for multimedia applications. Most multimedia applications will be similar to the H.263 example and therefore can be modelled by SDFGs.

An SDF graph has to follow a schedule which can be expressed by a vector. The *repetition vector* is one particular instance of the vector. The existence of this vector proves that the SDF graph has a correct schedule and therefore is correct itself. We can calculate the repetition vector by satisfying this balance equation [23]:

$\Gamma \times \vec{q} = \vec{0}$

with  $\Gamma$  representing the topology matrix. This topology matrix is a compact description of the SDF graph. In the matrix there is one column for each actor and one row for each channel of the SDF graph. There are 3 possible entries for each position in the matrix:

- 1. A zero means there is no edge to or from the actor.

- 2. A positive number means there is an outgoing edge from the actor.

- 3. A negative number means there is an incoming edge to the actor.

Figure 3.3: SDF example.

The SDF graph in Figure 3.3 can be represented by the following topology matrix:

$$\Gamma = \begin{pmatrix} 3 & -2 & 0 \\ 0 & 1 & -1 \end{pmatrix}$$

which leads to a repetition vector  $\vec{q} = \begin{pmatrix} 2 \\ 3 \\ 3 \end{pmatrix}$ .

## 3.2.2 CSDF

Cyclo-Static Data Flow [27] (CSDF) is a generalisation of SDF. CSDF allows actors to have cyclicly changing firing rules (or functions). In SDF an actor behaves exactly the