Janssen, E.J.G.

Award date: 2008

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# Fully Balanced LNA 58 - 64 GHz with 3.8 dB NF, 10 dB $G_t$ and constant group delay in CMOS 65 nm

Master Thesis

Erwin Janssen

Mixed-signal Microelectronics,

Eindhoven University of Technology

# Contents

| 1 | Intr | roduction                                                   |

|---|------|-------------------------------------------------------------|

|   | 1.1  | LNA                                                         |

|   |      | 1.1.1 Noise                                                 |

|   |      | 1.1.2 Gain                                                  |

|   |      | 1.1.3 IP3                                                   |

|   | 1.2  | Specifications                                              |

| 2 | Top  | ologies                                                     |

|   | 2.1  | Common source                                               |

|   | 2.2  | Common gate                                                 |

|   | 2.3  | Discussion CS - CG                                          |

|   | 2.4  | $G_m$ -boosted common gate                                  |

|   |      | 2.4.1 Input impedance                                       |

|   |      | 2.4.2 Noise factor                                          |

|   |      | 2.4.3 Loop gain                                             |

|   |      | 2.4.4 Voltage gain                                          |

|   | 2.5  | Voltage-voltage transformer feedback LNA                    |

|   |      | 2.5.1 Output isolation                                      |

|   |      | 2.5.2 Voltage gain                                          |

|   |      | 2.5.3 Input impedance                                       |

|   |      | 2.5.4 Noise factor                                          |

|   | 2.6  | Discussion $g_m$ -boosted CG - V-V transformer feedback LNA |

|   |      | 2.6.1 Noise performance                                     |

|   |      | 2.6.2 Gain                                                  |

|   |      | 2.6.3 Input impedance                                       |

|   |      | 2.6.4 Simulations                                           |

|   |      | 2.6.5 Decision                                              |

| 3 | мо   | ST modeling CMOS 65 nm TSMC                                 |

| 4 | Tra  | nsformers 38                                                |

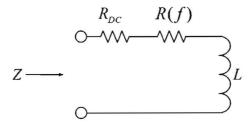

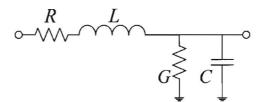

|   | 4.1  | Simple transformer model                                    |

|   | 4.2  | Multi-turn inductor                                         |

|   | 4.3  | Q-factor                                                    |

|   | 4.4  | Positive and negative coupling                              |

|   | 4.5  | Transformer model using parasitics 4                        |

CONTENTS

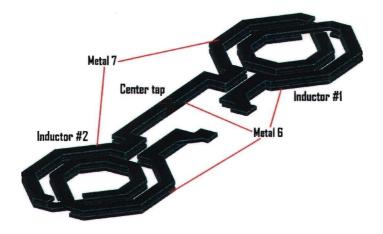

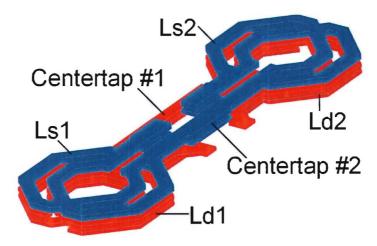

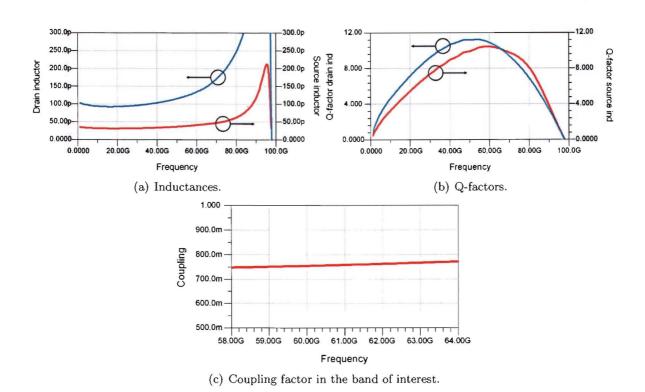

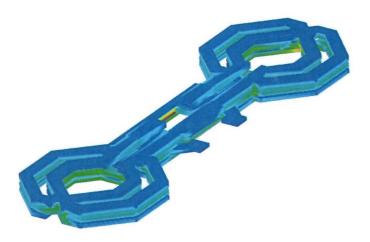

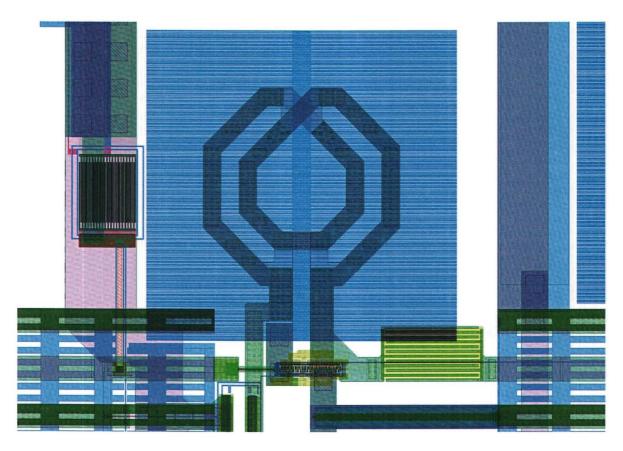

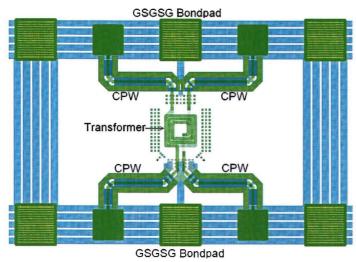

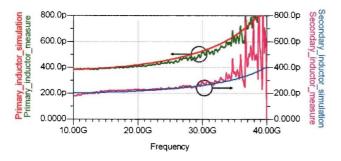

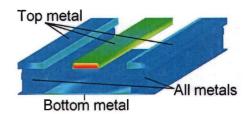

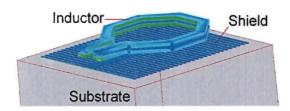

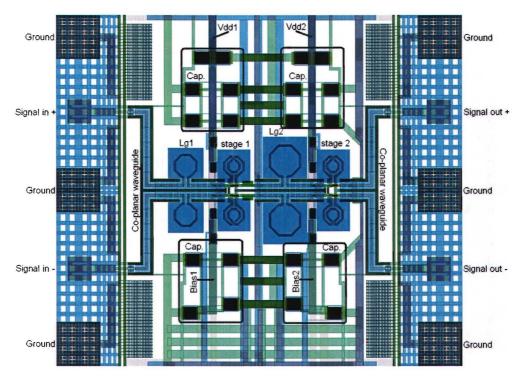

|   | 4.6<br>4.7<br>4.8                                                                | Starting point for the design of a transformer Single transformer tape-out 4.7.1 Simulation 4.7.2 Layout 4.7.3 Measurement Transformer implemented LNA 4.8.1 Stack information 4.8.2 Design goals and how to get there 4.8.3 Design source inductor 4.8.4 Design drain inductor 4.8.5 Transformer layout and simulations                                                                                                                                                                                                                                           | 46<br>48<br>48<br>51<br>53<br>55<br>55<br>55<br>56<br>57<br>58                                                   |

|---|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| _ | D                                                                                | 2 3/ 3/ C 11 1. T 3/ A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00                                                                                                               |

| 5 |                                                                                  | sign V-V feedback LNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                                                               |

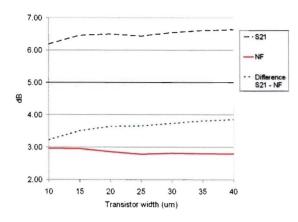

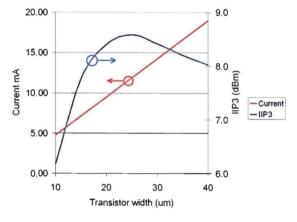

|   | 5.1                                                                              | Single stage design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                                                                                                               |

|   |                                                                                  | 5.1.1 Starting point based on calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                                                               |

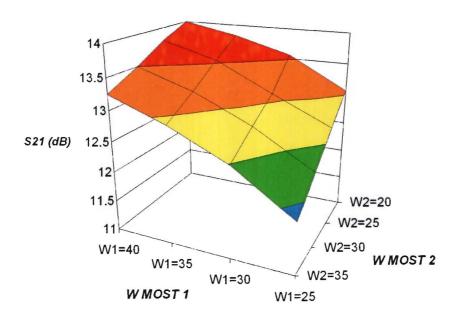

|   |                                                                                  | 5.1.2 Noise figure and $s_{21}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                               |

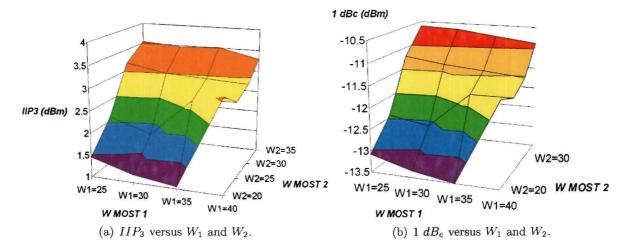

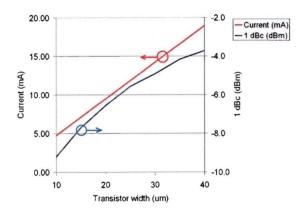

|   |                                                                                  | $5.1.3$ IIP <sub>3</sub> and $1 dB_c \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                                                                               |

|   |                                                                                  | 5.1.4 In and output impedances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                                                               |

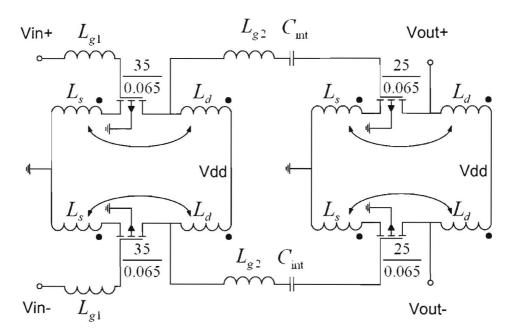

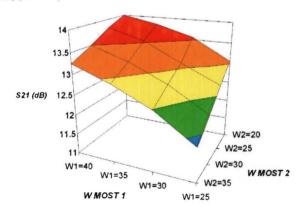

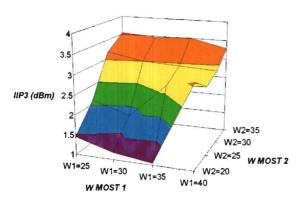

|   | 5.2                                                                              | Dual stage design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                                                                                                               |

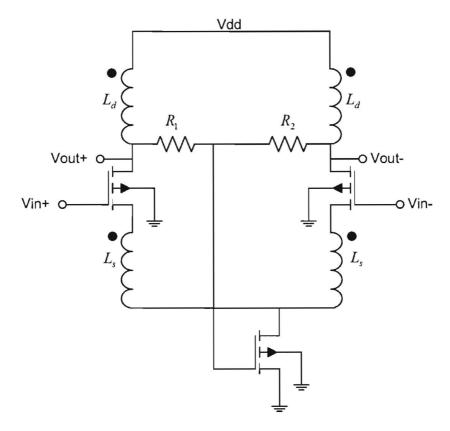

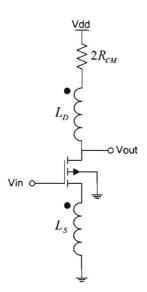

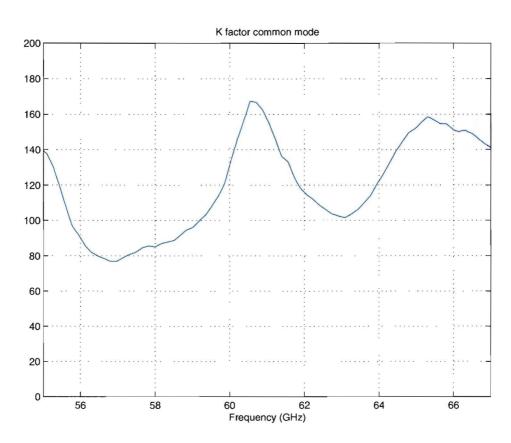

|   | 5.3                                                                              | Common mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66                                                                                                               |

|   |                                                                                  | 5.3.1 Current source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                                               |

|   |                                                                                  | 5.3.2 Current source with common mode feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68                                                                                                               |

|   |                                                                                  | 5.3.3 Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69                                                                                                               |

|   |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                  |

| C | T                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71                                                                                                               |

| 6 | _                                                                                | pact of layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71                                                                                                               |

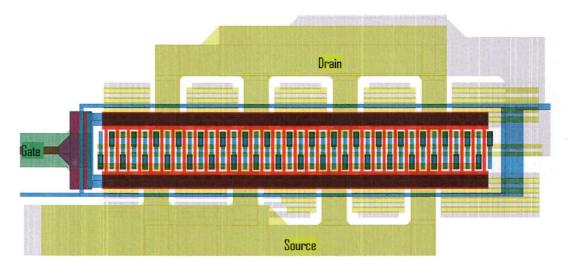

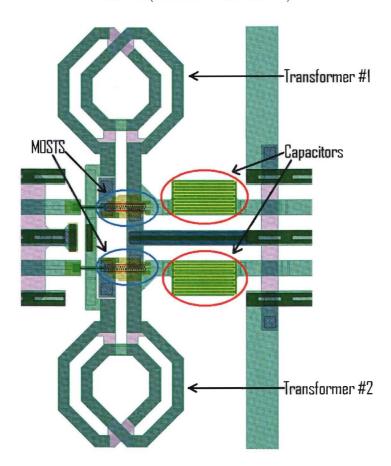

| 6 | 6.1                                                                              | MOST's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                               |

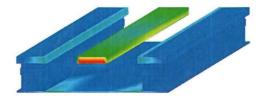

| 6 | 6.1<br>6.2                                                                       | MOST's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73                                                                                                         |

| 6 | 6.1<br>6.2<br>6.3                                                                | MOST's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73<br>74                                                                                                   |

| 6 | 6.1<br>6.2<br>6.3<br>6.4                                                         | MOST's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73<br>74<br>75                                                                                             |

| 6 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                  | MOST's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73<br>74<br>75<br>76                                                                                       |

| 6 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                           | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73<br>74<br>75<br>76<br>76                                                                                 |

| 6 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                    | MOST's Transformer Coplanar wave guide Shielding inductors and transformer Inductors Capacitances Resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72<br>73<br>74<br>75<br>76<br>76<br>77                                                                           |

| 6 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                           | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72<br>73<br>74<br>75<br>76<br>76                                                                                 |

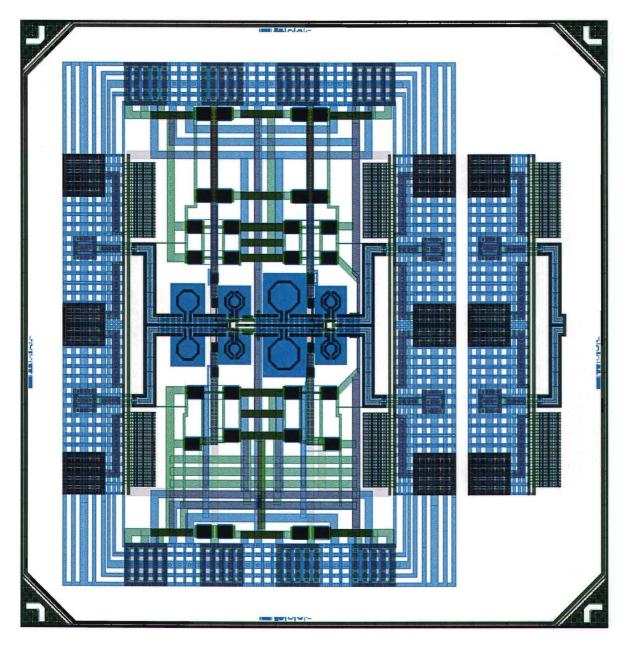

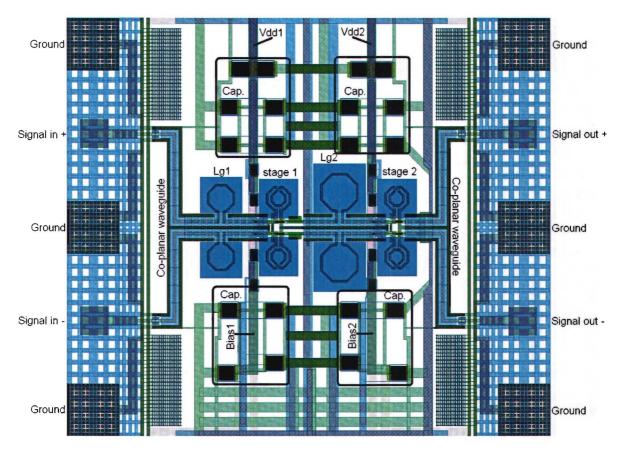

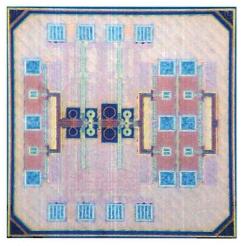

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                             | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances  Resistors  Total layout                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78                                                                     |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                             | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances  Resistors  Total layout                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78                                                                     |

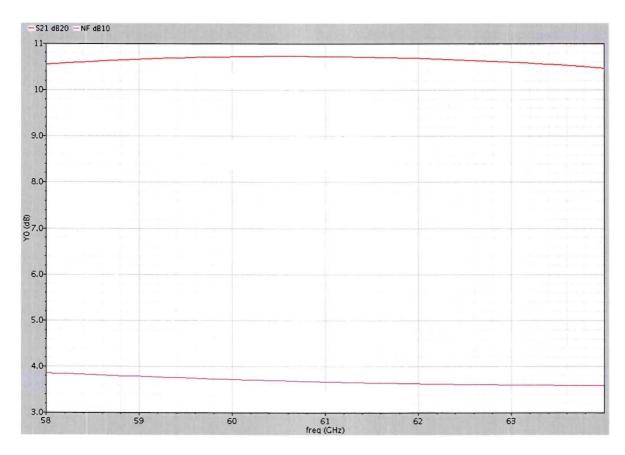

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1               | MOST's Transformer Coplanar wave guide Shielding inductors and transformer Inductors Capacitances Resistors Total layout  Noise figure and Gain                                                                                                                                                                                                                                                                                                                                                                                                                    | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82                                                  |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2        | $\operatorname{MOST}$ 's $\operatorname{Transformer}$ $\operatorname{Coplanar}$ wave guide $\operatorname{Shielding}$ inductors and transformer $\operatorname{Inductors}$ $\operatorname{Capacitances}$ $\operatorname{Resistors}$ $\operatorname{Total}$ layout $\operatorname{Noise}$ figure and $\operatorname{Gain}$ $\operatorname{IP_3}$ and $\operatorname{1} dB_c$                                                                                                                                                                                        | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87                                            |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1               | MOST's Transformer Coplanar wave guide Shielding inductors and transformer Inductors Capacitances Resistors Total layout  Noise figure and Gain                                                                                                                                                                                                                                                                                                                                                                                                                    | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82                                                  |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | $\operatorname{MOST}$ 's $\operatorname{Transformer}$ $\operatorname{Coplanar}$ wave guide $\operatorname{Shielding}$ inductors and transformer $\operatorname{Inductors}$ $\operatorname{Capacitances}$ $\operatorname{Resistors}$ $\operatorname{Total}$ layout $\operatorname{Noise}$ figure and $\operatorname{Gain}$ $\operatorname{IP_3}$ and $\operatorname{1} dB_c$                                                                                                                                                                                        | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87                                            |

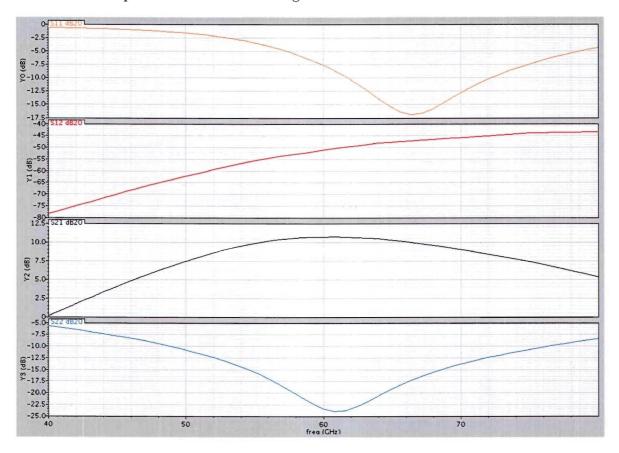

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | $\operatorname{MOST}$ 's $\operatorname{Transformer}$ $\operatorname{Coplanar}$ wave guide $\operatorname{Shielding}$ inductors and transformer $\operatorname{Inductors}$ $\operatorname{Capacitances}$ $\operatorname{Resistors}$ $\operatorname{Total}$ layout $\operatorname{Total}$ layout $\operatorname{Inductors}$ $\operatorname{Noise}$ figure and $\operatorname{Gain}$ $\operatorname{IP}_3$ and $\operatorname{Id}_c$ $\operatorname{S-parameters}$                                                                                                   | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89                                      |

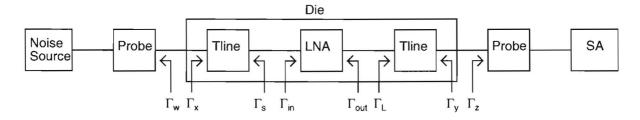

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | $\operatorname{MOST}$ 's $\operatorname{Transformer}$ $\operatorname{Coplanar}$ wave guide $\operatorname{Shielding}$ inductors and transformer $\operatorname{Inductors}$ $\operatorname{Capacitances}$ $\operatorname{Resistors}$ $\operatorname{Total layout}$ $\operatorname{Noise}$ figure and $\operatorname{Gain}$ $\operatorname{IP}_3$ and $\operatorname{IdB}_c$ $\operatorname{S-parameters}$ asurement results                                                                                                                                         | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89                                      |

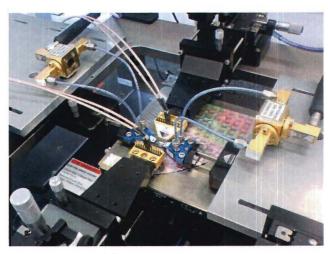

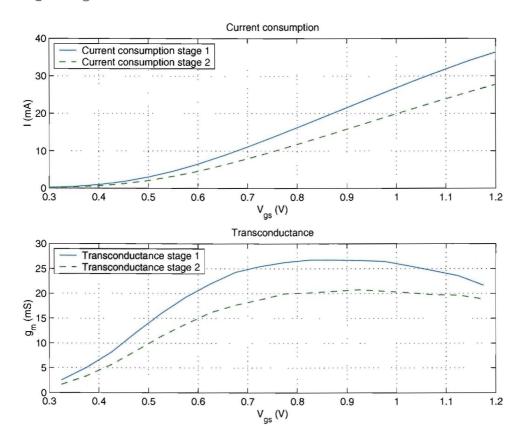

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | $\operatorname{MOST}$ 's $\operatorname{Transformer}$ $\operatorname{Coplanar}$ wave guide $\operatorname{Shielding}$ inductors and transformer $\operatorname{Inductors}$ $\operatorname{Capacitances}$ $\operatorname{Resistors}$ $\operatorname{Total}$ layout $\operatorname{nulations}$ $\operatorname{Noise}$ figure and $\operatorname{Gain}$ $\operatorname{IP}_3$ and $\operatorname{1}$ $\operatorname{dB}_c$ $\operatorname{S-parameters}$ $\operatorname{asurement}$ results $\operatorname{DC}$ measurement and power consumption at constant biasing | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89<br><b>90</b><br>91                   |

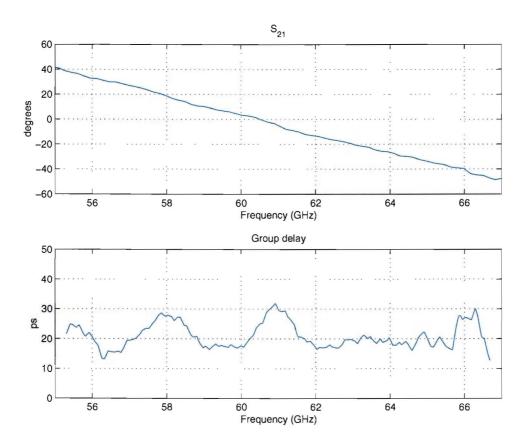

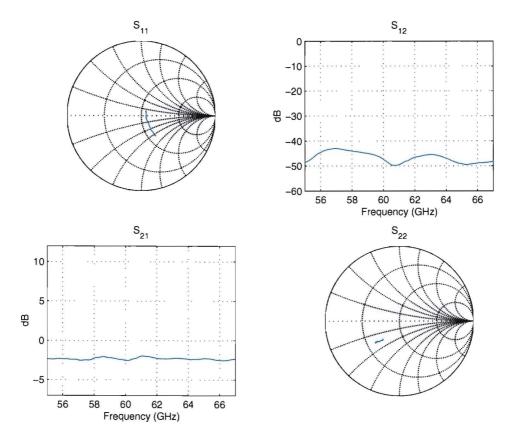

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | $\operatorname{MOST}$ 's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances  Resistors  Total layout $\operatorname{India}$ Noise figure and Gain $\operatorname{IP}_3$ and $\operatorname{IdB}_c$ $\operatorname{S}$ -parameters  asurement results  DC measurement and power consumption at constant biasing  S-Parameters                                                                                                                                                                                          | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89<br><b>90</b><br>91<br>92             |

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances  Resistors  Total layout  nulations  Noise figure and Gain $IP_3$ and 1 $dB_c$ $S$ -parameters  asurement results  DC measurement and power consumption at constant biasing  S-Parameters  8.2.1 De-embedding structures                                                                                                                                                                                                                                    | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89<br><b>90</b><br>91<br>92<br>92       |

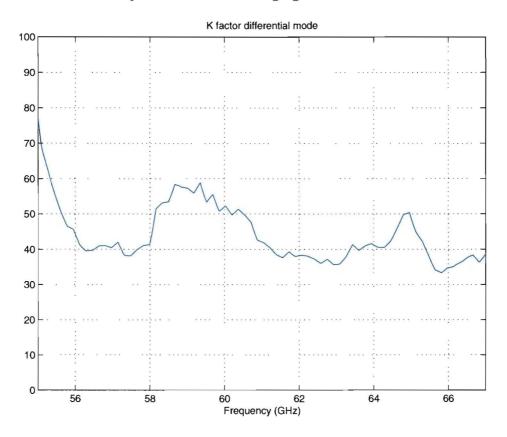

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>Sim<br>7.1<br>7.2<br>7.3 | MOST's  Transformer  Coplanar wave guide  Shielding inductors and transformer  Inductors  Capacitances  Resistors  Total layout  nulations  Noise figure and Gain $IP_3$ and $1 dB_c$ $S$ -parameters  asurement results  DC measurement and power consumption at constant biasing  S-Parameters  8.2.1 De-embedding structures  8.2.2 Differential mode response                                                                                                                                                                                                  | 72<br>73<br>74<br>75<br>76<br>76<br>77<br>78<br><b>82</b><br>82<br>87<br>89<br><b>90</b><br>91<br>92<br>92<br>94 |

III CONTENTS

|    | 8.5 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$   | 108 |

|----|-----|--------------------------------------------------------|-----|

| 9  | Con | clusions and recommendations                           | 110 |

| 10 | My  | own contributions                                      | 111 |

| A  | App | pendix                                                 | 113 |

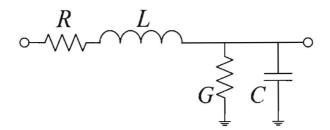

|    | A.1 | Telegrapher's equations                                | 113 |

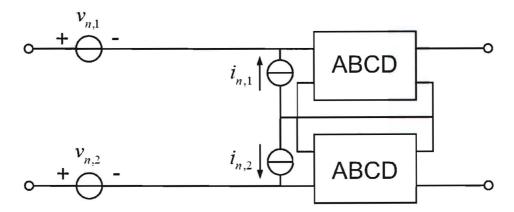

|    |     | Linearity, differential vs. single ended               |     |

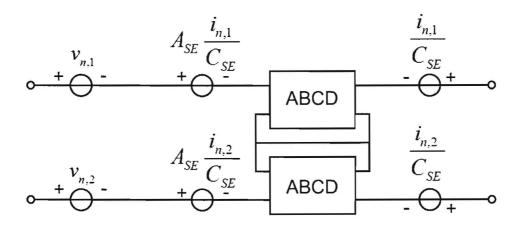

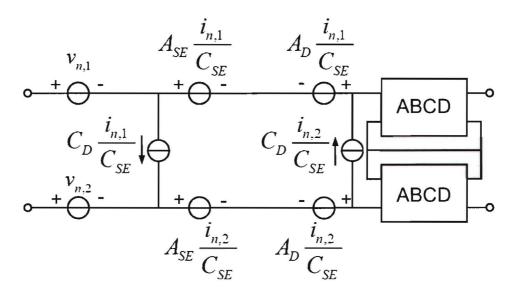

|    | A.3 | Noise factor, differential vs. single ended            | 116 |

|    |     | Noise factor calculation of the $g_m$ -boosted CG LNA  |     |

|    |     | Noise factor calculation of the V-V transformer FB LNA |     |

|    | A 6 | Paper                                                  | 128 |

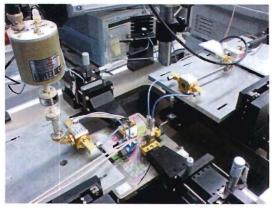

# Acknowledgment

The author would like to thank Reza Mahmoudi of Eindhoven University for his helpful support and suggestions during the project and the co-workers of NXP Semiconductors for enabling the tape-out and for their helpful support during the layout phase, especially Edwin van der Heijden, Anton de Graauw and Dennis Jeurissen. The author would like to thank Philips research for enabling the tape-out of the transformer and Pooyan Sakian of Eindhoven University for his help during the noise figure measurement.

## Chapter 1

## Introduction

The increasing demand for higher data rate in RF communication links requires the use of more bandwidth. Around 60 GHz, 6 GHz of unlicensed bandwidth is available which enables data rates of several gigabits per second. To implement such systems, modern CMOS technology is interesting because of its promise to use digital signal processing combined with RF front end electronics. This enables the integration of a full system on chip. In this report the design, simulation and layout of a 60 GHz differential LNA using 65 nm CMOS is discussed. Because the  $f_t$  of the used CMOS device is approximately twice the operating frequency, many problems arise.

One of those difficulties is the existence of many parasitic effects. To model these, an EM-simulator has been used in combination with RC-extraction techniques performed on the layout. During the design one of the goals is to minimize the effect of these parasitics.

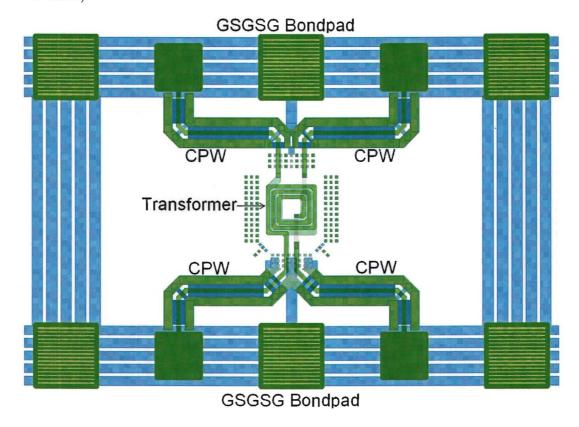

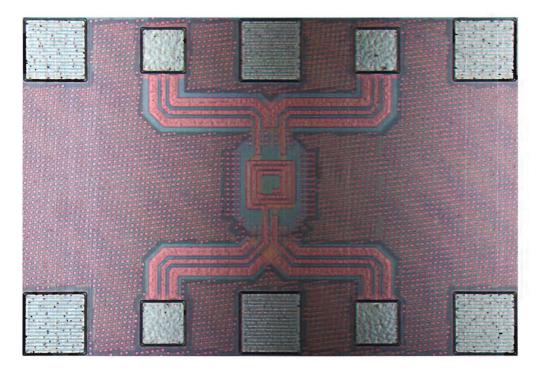

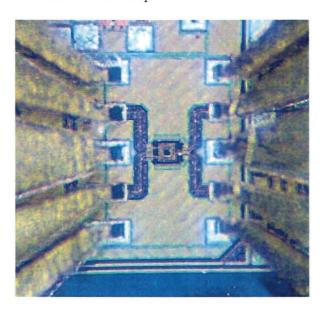

In order to achieve the required 6 GHz bandwidth ( $\approx 10$  %), feedback is applied. At these high frequencies the use of coupled structures such as transformers to apply this feedback become interesting because of their low noise contribution, low DC-voltage drop and because their dimensions are not such a big issue anymore. Therefore a search was done for designs that make use of transformers for feedback purposes. Several designs have been compared in order to decide which topology to choose. In order to accurately model the behavior of a transformer on chip, an EM simulator was used. To verify the behavior predicted by the EM-simulator a transformer was designed, simulated, taped out and measured.

Another problem is the low supply voltage of 1.2 Volt. Because of this, it is not possible to stack many transistors. This results in solutions that make use of as little stacked devices as possible.

## 1.1 LNA

The LNA is the first system block after the signal source, the antenna. It's main task is to retrieve and amplify the signal from the source with the least possible deterioration. Main design criteria are noise figure, gain, and linearity  $(IP_3)$ .

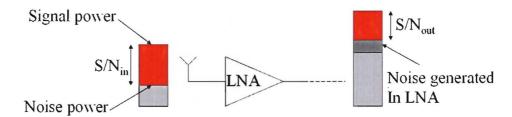

#### 1.1.1 Noise

In all electronic systems there are random fluctuations in the current and voltage caused by the random movement of electrons. This phenomenon is called noise. The noise adds to the signal causing a deterioration of the signal quality. If the signal strength is weak compared to this noise it is hard to retrieve the information carried by the signal. So to have a reliable communication link, a certain ratio is required between the signal and noise power. This is called the signal to noise ratio, SNR. It sets a lower bound to the minimum signal power level possible at the input source of the receiver while still having a reliable communication.

The noise factor F, is defined as the ratio between the SNR at the output and the input of an electronic system.

$$F_{LNA} = \frac{SNR_{out}}{SNR_{in}} = \frac{P_{in}N_{out}}{G_aP_{in}N_{in}} = \frac{N_{out}}{G_aN_{in}} = \frac{G_a(N_{in} + N_{LNA})}{G_aN_{in}} = 1 + \frac{N_{LNA}}{N_{in}}$$

$P_{in}$  = Input Signal Power  $N_{in}$  = Input Noise Power  $N_{out}$  = Output Noise Power

$N_{LNA}$  = Noise Power added in LNA

$G_a$  = Available Gain

To obtain a sensitive receiver the noise factor should be kept as small as possible, so  $N_{LNA}$  should be kept low. The LNA is the first system block of the receiver after the antenna and maybe some filtering. Due to this the noise factor of the LNA,  $F_{LNA}$ , adds directly to the noise factor of the total system.

Figure 1.1: The LNA is the first system block in a receiver and its noise adds directly to the noise figure.

This can be verified by Friis' formula.

$$F_{total} = F_{LNA} + \frac{F_2 - 1}{G_{a,LNA}} + \frac{F_3 - 1}{G_{a,2}G_{a,LNA}} + \dots$$

As can be seen by this formula, the contribution of the noise factor of the second system block,  $F_2$ , will be divided by the available gain of the LNA,  $G_{a,LNA}$ . So for a LNA it is desirable to have a low noise factor and a high gain. Often the noise figure is given instead of the noise factor. It is defined as follows:

$$NF = 10\log_{10} \frac{SNR_{out}}{SNR_{in}} = 10\log_{10} F$$

1.1. LNA

## 1.1.2 Gain

3

Because the noise factor of the subsequent stages can be divided by the available gain  $(G_a)$  of the LNA, it is preferable to have high  $G_a$ . The definition of available gain is as follows:

$$G_a = \frac{\text{Power available from the network}}{\text{Power available from the source}} = \frac{1 - |\Gamma_s|^2}{|1 - s_{11}\Gamma_s|^2} |s_{21}|^2 \frac{1}{1 - |\Gamma_{out}|^2}$$

$\Gamma_s$  = Source reflection Coefficient

$\Gamma_{out}$  = Output reflection Coefficient

$s_{xx}$  = Scattering Parameters

"Power available" is defined as the maximum power that can be delivered to the next stage, so the power transfer when  $Z_{out}$  of the first stage, source or network, is equal to  $Z_{in}^*$  of the next stage, so network or load. This gain is independent of source or load impedance, and it's eventual mismatch. Maximizing  $G_a$  means maximizing the  $s_{21}$ -parameter as can be seen by the formula. This is the forward transmission coefficient with the output properly terminated, so  $Z_{out} = Z_{load}^*$ .

This might lead to the wrong reasoning the source and load mismatch does not affect the overall noise factor. These mismatches do affect the noise factor because a mismatch leads to less power in both signal and noise, but the noise generated in the next stage still has the same power. This will eventually result in a lower SNR, so a higher F. Therefore it is important to have  $Z_{in} = Z_{erc}^*$  and  $Z_{out} = Z_{lead}^*$ .

important to have  $Z_{in} = Z_{src}^*$  and  $Z_{out} = Z_{load}^*$ . On the other hand, the noise factor is also dependent of  $Z_{src}$ . In designing an LNA it is therefore interesting to have  $Z_{src} = Z_{src,opt,NF} = Z_{in}^*$ . If this cannot be accomplished a tradeoff will result, to minimize the overall noise factor.

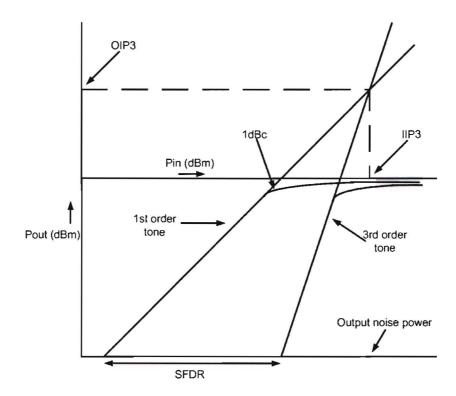

#### 1.1.3 IP3

Apart from the lower bound of the signal strength there is also an upper bound. This is given by the linearity of the system. If the signal strength increases the non-linear behavior of the active devices become more dominant. This gives rise to intermodulation products.

$$V_{out}(t) = \alpha V_{in}(t) + \beta V_{in}^{2}(t) + \gamma V_{in}^{3}(t) + \dots$$

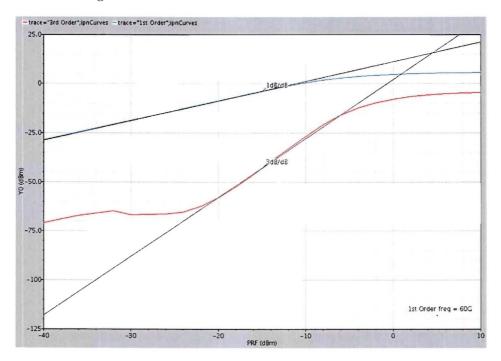

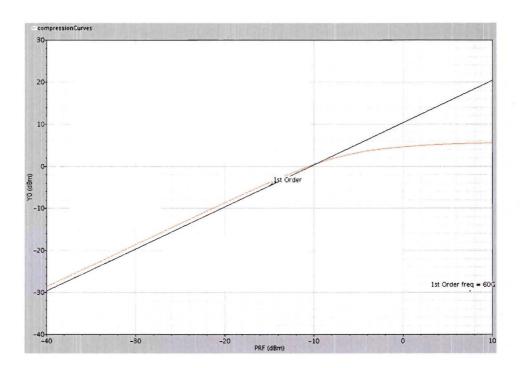

Where the third order intermodulation product has the same (extrapolated) strength as the output signal,  $IP_3$  is defined. This is shown in figure 1.2.

The  $IP_3$  can be referred to the input or the output power. It then is defined respectively as  $IIP_3$  and  $OIP_3$ . The 1  $dB_c$  point indicated in the figure shows where the gain has dropped by 1 dB. This point is approximately 10 dB lower than the  $IIP_3$  point (input referred).

When cascading different subsystems the first subsystem (LNA) is not dominant in the total  $IIP_3$  of the system. The total  $IIP_3$  is defined as follows (this formula is not valid or all cascaded systems but it gives a nice indication):

$$\frac{1}{IIP_{3,total}} = \frac{1}{IIP_{3,1}} + \frac{G_{a,1}}{IIP_{3,2}} + \frac{G_{a,1}G_{a,2}}{IIP_{3,3}} + \dots$$

In the region between the noise floor and where the third order intermodulation product is equal to the noise floor, the system can handle the signal in a reliable fashion. This range is called the spurious free dynamic range, SFDR. It is defined as follows:

Figure 1.2:  $IIP_3$ ,  $OIP_3$ ,  $1dB_c$ , noise floor and spurious free dynamic range.

$$SFDR(dB) = \frac{2}{3} \Big( OIP_3(dBm) - \text{Output noise power}(dBm) \Big)$$

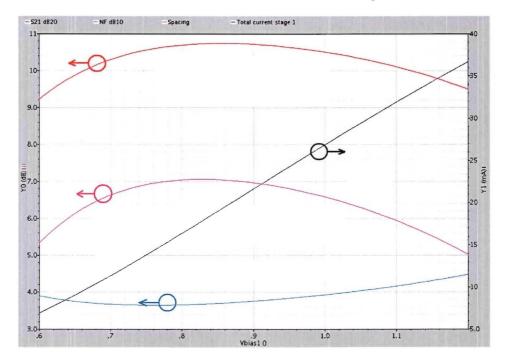

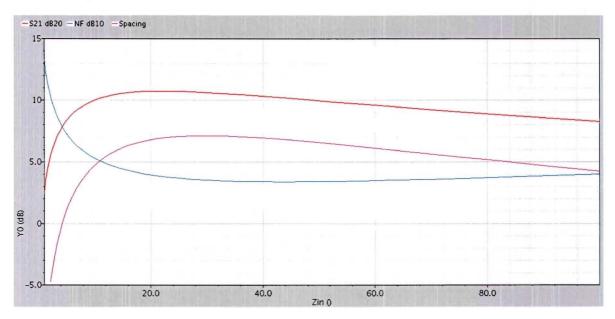

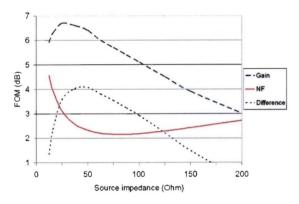

Concluding the previous sections the main objectives of the LNA are a low noise figure, high gain and high  $IP_3$ . To find an optimum, the spacing between the noise figure and gain has to be maximized. Afterwards the  $IP_3$  will determined at this optimum. Then an optimal  $IP_3$  will be located in the range for optimal noise figure - gain spacing.

## 1.2 Specifications

The topology of this LNA has to be differential to improve local oscillator leakage resistance and linearity (see appendix section A.2). Another reason to choose for the differential topology is it's immunity to the impact of the bond-wire gain reduction. Furthermore the differential amplifier can be directly connected to a differential antenna. To implement the LNA the TSMC 65 nm CMOS technology has to be used. Main specifications for this design are gain ( $s_{21}$ ) of at least 15 dB, noise figure of 5 dB at maximum and  $IIP_3$  of at least 0 dBm.

The frequency range the LNA has to cover is 58 to 64 GHz. This is 9.8 % of the center frequency at 61 GHz. A certain gain flatness over this frequency band has to be accomplished. Design goal is 0.5 dB over the entire bandwidth. To achieve this, feedback can be used. Different feedback topologies have to be investigated considering alternatives such as inductive or transmission line feedback coupling.

To remove common mode signals there has to be a common mode rejection. To include this a CMRR design goal of at least  $10~\mathrm{dB}$  has to be met. A summary of all design specifications is given below:

| Gain $(s_{21})$                  | > 15 dB   |

|----------------------------------|-----------|

| Noise figure                     | < 5  dB   |

| $IIP_3$                          | > 0  dBm  |

| Gain flatness in 6 GHz Bandwidth | < 0.5  dB |

| CMRR                             | > 10  dB  |

## Chapter 2

## **Topologies**

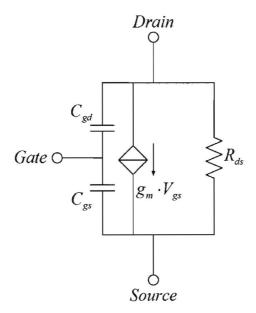

In a literature search different topologies were investigated for the LNA. Starting point for this search is the use of feedback. Applying feedback is possible over some different active topologies such as common gate and common source. To make a decision how to implement the active part, first a comparison will be given for these two topologies. After this comparison several topologies will be investigated for the 60 GHz LNA. Eventually a decision will be made between the different topologies. During the analysis the following variables will be used to model the behavior of the MOST:

$R_q$  = Gate resistance

$R_{ds}$  = Drain source resistance

$C_{gs}$  = Capacitance between gate and source  $C_{gd}$  = Capacitance between gate and drain

$q_m$  = Transconductance

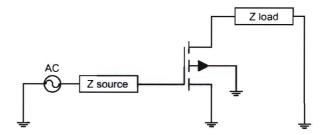

## 2.1 Common source

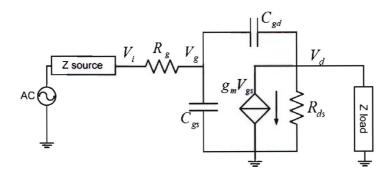

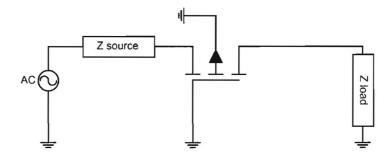

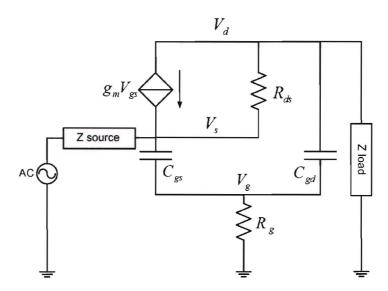

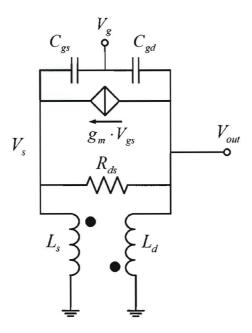

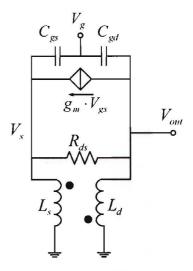

With the common source topology the source is connected to AC ground and the gate is connected to the signal source. The schematic is shown in figure 2.1 and the small signal model is given in figure 2.2.

Figure 2.1: Common source

$$V_s = V_b = 0V$$

For this topology the ABCD-parameters, input impedance and noise figure will be determined to make a good comparison. The ABCD-parameters of the common source topology

Figure 2.2: Small signal equivalent circuit common source topology

are given below:

$$\mathbf{ABCD} = \begin{bmatrix} \frac{sR_gC_{gd}(sC_{gs} + g_m) + \frac{R_g}{R_{ds}}(sC_{gd} + sC_{gs}) + \frac{1}{R_{ds}} + sC_{gd}}{sC_{gd} - g_m} & \frac{1 + sR_g(C_{gs} + C_{gd})}{sC_{gd} - g_m} \\ \frac{s^2C_{gd}C_{gs} + sC_{gd}(g_m + \frac{1}{R_{ds}}) + \frac{sC_{gs}}{R_{ds}}}{sC_{gd} - g_m} & \frac{s(C_{gs} + C_{gd})}{sC_{gd} - g_m} \end{bmatrix}$$

In general  $R_g$  is very small. This results in an A-parameter (unloaded voltage gain) as follows:

$$A \approx \frac{\frac{1}{R_{ds}} + sC_{gd}}{sC_{gd} - g_m}$$

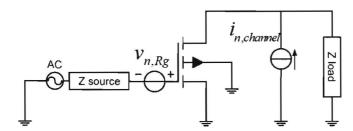

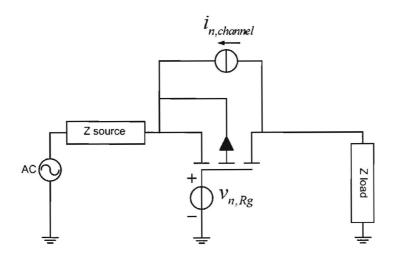

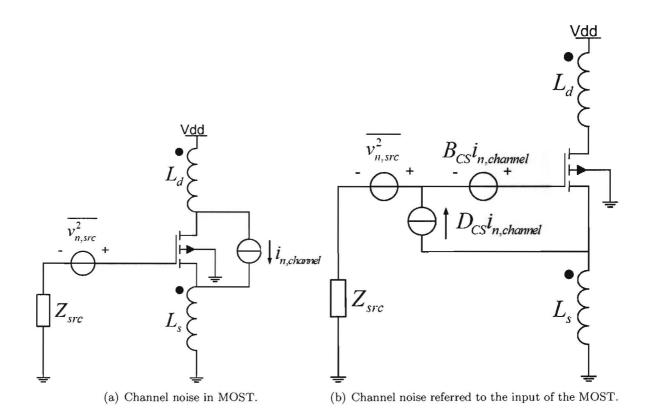

Because  $g_m > \frac{1}{R_{ds}}$ , the common source topology has both voltage, and current gain bigger than one possible (up to a certain frequency). Using the ABCD-parameters the noise performance of the common source can be investigated. To calculate the noise factor, the noise generated in the transistor channel and the noise due to the gate resistance have been taken into account, see figure 2.3.

Figure 2.3: Channel noise in MOST and noise due to  $R_q$

$$\overline{i_{n,channel}^2} = 4kT\gamma g_m$$

$$\overline{v_{n,R_g}^2} = 4kTR_g$$

k = Boltzmann constant  $\approx 1.38 \cdot 10^{-23}$  T = Absolute temperature = 300K $\gamma$  = Technology dependent constant

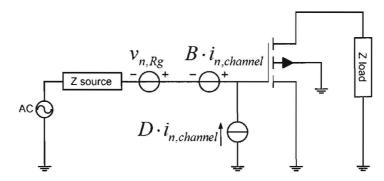

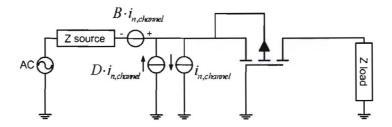

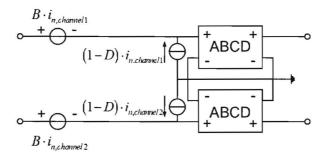

To calculate the noise factor, the output noise has to be referred to the input. To do this, the output noise current will be multiplied by B and D to get an input noise voltage and current source respectively, as shown in figure 2.4.

Figure 2.4: Noise sources referred to the input

$$v_{n,in} = B\sqrt{4kT\gamma g_m}$$

$$i_{n,in} = D\sqrt{4kT\gamma g_m}$$

The current source can be modeled as a voltage source. To do this the current source has to be multiplied by  $Z_{src}$ , the source impedance. Because of the correlation between the input current and voltage source they have to be added before squaring. Because of the small value of  $R_g$ , B can be approximated by the following formula:

$$B \approx \frac{1}{sC_{gd} - g_m}$$

$$\overline{v_{n,in}^2} = 4kTR_g + |B + Z_{src}D|^2 4kT\gamma g_m$$

$$\overline{v_{n,in}^2} \approx 4kTR_g + \left|\frac{1 + Z_{src}(sC_{gs} + sC_{gd})}{sC_{gd} - g_m}\right|^2 4kT\gamma g_m$$

$$F_{CS} \approx \frac{4kTR_{src} + 4kTR_g + \left|\frac{1 + Z_{src}(sC_{gs} + sC_{gd})}{sC_{gd} - g_m}\right|^2 4kT\gamma g_m}{4kTR_{src}}$$

$$F_{CS} \approx 1 + \frac{R_g}{R_{src}} + \frac{\gamma g_m}{R_{src}}\left|\frac{1 + Z_{src}(sC_{gs} + sC_{gd})}{sC_{gd} - g_m}\right|^2}{sC_{gd} - g_m}$$

The equation of the noise factor consists a (double) zero and a pole, with the position of the pole as follows:

$$\omega_{pole} = \frac{g_m}{C_{qd}} > \frac{g_m}{C_{qs} + C_{qd}} = \omega_t$$

The position of the pole is beyond the  $\omega_t$  of the device so this effect can be ignored. To minimize the contribution of the input referred current sources,  $Z_{src}$  is chosen to have a certain inductance. This inductance can be chosen to resonate with the capacitive effects present in the transistor and thereby lower the noise factor. The noise factor then looks as follows:

$$F_{CS} \approx 1 + \frac{R_g}{R_{src}} + \frac{\gamma g_m}{R_{src}} \left| \frac{1 + (R_{src} + sL_{src})(sC_{gs} + sC_{gd})}{q_m} \right|^2$$

To determine the optimal value for  $L_{src}$ , the derivative is taken and made equal to zero:

$$\frac{\partial F_{CS}}{\partial L_{src}} = 0$$

$$\rightarrow L_{src,opt,NF} = \frac{1}{\omega^2(C_{qs} + C_{qd})}$$

The noise factor then becomes:

$$F_{CS} \approx 1 + \frac{R_g}{R_{src}} + \frac{\gamma g_m}{R_{src}} \Big| \frac{R_{src}(sC_{gs} + sC_{gd})}{g_m} \Big|^2$$

$$F_{CS} \approx 1 + \frac{R_g}{R_{src}} + \frac{\gamma}{g_m} R_{src} \omega^2 (C_{gs} + C_{gd})^2$$

$$\to \omega_t = \frac{g_m}{C_{qs} + C_{qd}}$$

$$F_{CS} \approx 1 + \frac{R_g}{R_{src}} + \frac{\gamma \omega^2}{\omega_t^2} g_m R_{src}$$

As can be seen from this formula, maximizing  $\omega_t$  lowers the noise factor. Therefore  $g_m$  must be maximized, at the cost of power consumption. Because  $\omega/\omega_t \approx 1/2$  for 60 GHz in CMOS 65 nm (at optimal biasing),  $F_{CS}$  is approximately equal to:

$$F_{CS} \approx 1 + \frac{R_g}{R_{erc}} + \frac{\gamma}{4} g_m R_{src}$$

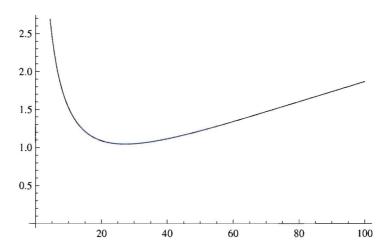

To determine the optimal source resistance, again the derivative is taken (this time to  $R_{src}$ ) and made equal to zero:

$$\frac{\partial F_{CS}}{\partial R_{src}} \approx \frac{\gamma g_m}{4} - \frac{R_g}{R_{src}^2} = 0$$

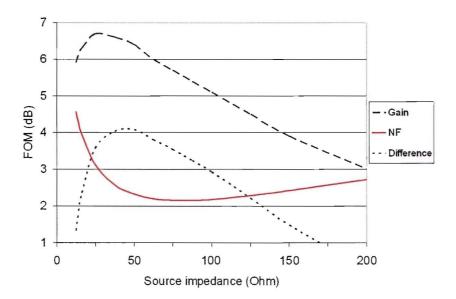

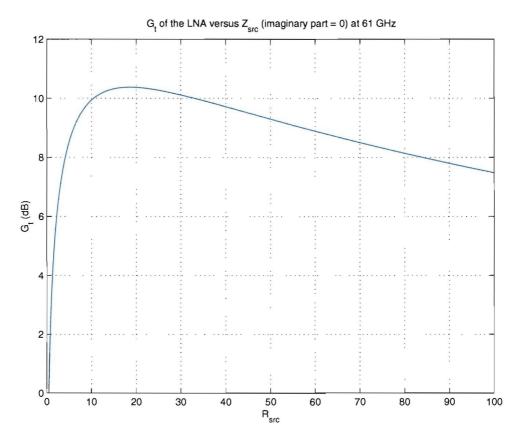

Figure 2.5: Calculated noise figure ( $10\log F_{CS}$ ) as function of  $R_{src}$  with  $L_{src} = L_{src,opt,NF}$  and  $W_{MOST} = 30 \mu \text{m}$ .

$$\rightarrow R_{src,opt,NF} \approx 2 \sqrt{\frac{R_g}{\gamma g_m}}$$

If  $R_g$  is small,  $R_{src,opt,NF}$  also becomes small. The resulting  $F_{min}$  is equal to:

$$F_{CS,min} pprox 1 + rac{R_g}{2\sqrt{rac{R_g}{\gamma g_m}}} + rac{\gamma g_m}{2}\sqrt{rac{R_g}{\gamma g_m}}$$

$$\rightarrow F_{CS,min} \approx 1 + \sqrt{\gamma g_m R_g}$$

As can be seen the minimum noise factor becomes small for small  $R_g$ . Last feature to determine is the input impedance. This can be done by using the ABCD-parameters. To also take into account the effect of  $Z_{load}$ , the ABCD-parameters of the total system have to be calculated:

$$ABCD_{Total} = ABCD_{MOST} \cdot ABCD_{Z_{load}}$$

$$\mathbf{ABCD}_{Z_{load}} = \left[ egin{array}{cc} 1 & 0 \ rac{1}{Z_{load}} & 1 \end{array}

ight]$$

$$Z_{in} = \left. \frac{V_o}{Vi} \right|_{I_o = 0} = \frac{A_{Total}}{C_{Total}} = \frac{A_{MOST} A_{Z_{load}} + B_{MOST} C_{Z_{load}}}{C_{MOST} A_{Z_{load}} + D_{MOST} C_{Z_{load}}}$$

$$Z_{in} = \frac{A_{MOST} + \frac{B_{MOST}}{Z_{load}}}{C_{MOST} + \frac{D_{MOST}}{Z_{load}}}$$

$$\rightarrow Z_{in} = R_g + \frac{sC_{gd}(R_{ds}||Z_{load}) + 1}{s^2C_{gd}C_{gs}(R_{ds}||Z_{load}) + sC_{gd}(g_m(R_{ds}||Z_{load}) + 1) + sC_{gs}}$$

As can be seen by the formula the effect of  $C_{gd}$  on the input impedance is being multiplied by  $g_m(R_{ds}||Z_{load})$ . This is the Miller effect. This Miller effect also causes a path from the drain to the source, so from output to input. When the common source topology is used in a LNA, this signal path should be blocked to prevent instability. To further investigate the behavior due to this Miller capacitance,  $g_m(R_{ds}||Z_{load})C_{gd}$  is now further called  $C_M$ .

$$Z_{in} = R_g + \frac{s\frac{C_m}{g_m} + 1}{s\frac{C_m}{g_m} \cdot sC_{gs} + sC_m + sC_{gd} + sC_{gs}}$$

If the effect of the Miller capacitance is big, the input impedance converges to:

$$Z_{in} = R_g + \frac{1}{sC_{gs} + g_m} =$$

$$\rightarrow R_{in} = R_g + \frac{g_m}{\omega^2 C_{gs}^2 + g_m^2}$$

$$\rightarrow X_{in} = -\frac{\omega C_{gs}}{\omega^2 C_{gs}^2 + g_m^2}$$

On the other hand, if the effect of the Miller capacitance is small, the input impedance converges to:

$$Z_{in} = R_g + \frac{1}{s(C_{gd} + C_{gs})}$$

$$\rightarrow R_{in} = R_g$$

$$\rightarrow X_{in} = -\frac{1}{\omega(C_{ad} + C_{as})}$$

So the input impedance will be some where between these extremes, depending on  $Z_{load}$ . Under input matching conditions  $R_{in}$  has to be equal to  $R_{src}$ . Also  $X_{in}$  then has to be equal to  $-X_{src}$ . This means an inductance equal to (for high Miller effect):

$$L_{src,match} = rac{\omega C_{gs}}{g_m^2 + \omega^2 C_{gs}^2}

eq L_{src,opt,NF}$$

or (for small Miller effect):

$$L_{src,match} = \frac{1}{\omega^2(C_{gs} + C_{gd})} = L_{src,opt,NF}$$

Depending on  $Z_{load}$ . As can be seen the situation with little Miller effect has the same inductance for both power match and minimum noise factor.

## 2.2 Common gate

With the common gate topology the gate of the MOST is connected to AC ground and the source terminal is connected to the signal source. The schematic is drawn in figure 2.6. The equivalent small signal model is shown in figure 2.7. To be able to do easy calculations on the common gate topology the ABCD-parameters are calculated.  $R_g$  is neglected in the matrix shown because in general it has small influence on the behavior of the parameters but formulas become quite big.

Figure 2.6: Common gate

Figure 2.7: Small signal equivalent circuit common gate topology.

$$\mathbf{ABCD} \approx \left[ \begin{array}{cc} \frac{sR_{ds}C_{gd}+1}{g_{m}R_{ds}+1} & \frac{R_{ds}}{g_{m}R_{ds}+1} \\ \frac{s^{2}R_{ds}C_{gs}C_{gd}+sC_{gd}(g_{m}R_{ds}+1)+sC_{gs}}{g_{m}R_{ds}+1} & \frac{sR_{ds}C_{gs}+g_{m}R_{ds}+1}{g_{m}R_{ds}+1} \end{array} \right]$$

The value of D is defined as  $\frac{I_i}{I_o}\Big|_{V_o=0}$ . Because this value is always  $\geq 1$ , the current gain of the common gate topology is  $\leq 1$ . This means there is no current gain but only voltage gain possible in the common gate topology.

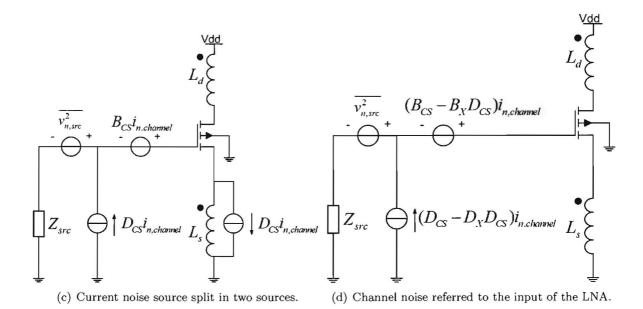

To calculate the noise factor, the noise generated in the transistor channel has to be taken into account as well as the noise generated in  $R_g$ .

Figure 2.8: Noise source present in the transistor channel.

$$\overline{i_{n,channel}^2} = 4kT\gamma g_m$$

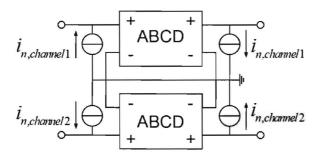

The channel noise has to be referred to the input. To do this, it is moved to the output and input. To get the output source to the input it has to be multiplied by B and D to get a voltage and current source respectively, see figure 2.9.

Figure 2.9: Referring the channel noise to the input.

$$\overline{v_{n,in,channel}^2} = \left| B + (D-1)Z_{src} \right|^2 4kT\gamma g_m$$

$$\overline{v_{n,in,channel}^2} = \left| \frac{R_{ds}}{g_m R_{ds} + 1} + \left( \frac{sR_{ds}C_{gs} + g_m R_{ds} + 1}{g_m R_{ds} + 1} - 1 \right) Z_{src} \right|^2 4kT\gamma g_m$$

$$\overline{v_{n,in,channel}^2} = \left| \frac{R_{ds} + sR_{ds}Z_{src}C_{gs}}{g_m R_{ds} + 1} \right|^2 4kT\gamma g_m$$

Also the noise generated by  $R_g$  has to be referred to the input. Therefore the noise voltage source can be shifted to the in and output. Then the noise source at the output can be brought

Figure 2.10: Referring the noise due to  $R_g$  to the input.

back to the input by multiplying it with A and C. The resulting input referred noise due to  $R_q$  is shown in figure 2.10.

By doing this the following formula for the noise contribution due to the gate resistance results:

$$\overline{v_{n,in,R_g}^2} = \left| 1 - A - C \cdot Z_{src} \right|^2 4kTR_g$$

$$\overline{v_{n,in,R_g}^2} \approx 4kTR_g \left| \frac{g_m R_{ds} - sR_{ds}C_{gd}(sC_{gs}Z_{src} + g_m Z_{src} + 1) - Z_{src}s(C_{gs} + C_{gd})}{g_m R_{ds} + 1} \right|^2$$

The resulting noise factor is equal to the following expression:

$$F_{CG} \approx \frac{4kTR_{src} + 4kTR_g \left| \frac{g_m R_{ds} - sR_{ds}C_{gd}(sC_{gs}Z_{src} + g_m Z_{src} + 1) - Z_{s}_{rc}s(C_{gs} + C_{gd})}{g_m R_{ds} + 1} \right|^2 + 4kT\gamma g_m \left| \frac{R_{ds} + sR_{ds}Z_{src}C_{gs}}{g_m R_{ds} + 1} \right|^2}{4kTR}$$

$$1 + \frac{R_g}{R_{src}} \Big| \frac{g_m R_{ds} - s R_{ds} C_{gd} (s C_{gs} Z_{src} + g_m Z_{src} + 1) - Z_{src} s (C_{gs} + C_{gd})}{g_m R_{ds} + 1} \Big|^2 + \frac{\gamma g_m}{R_{src}} \Big| \frac{R_{ds} + s R_{ds} Z_{src} C_{gs}}{g_m R_{ds} + 1} \Big|^2$$

An approximation is made by neglecting  $R_{ds}$ :

$$\lim_{R_{ds}\to\infty} F_{CG} \approx \\ 1 + \frac{R_g}{R_{src}} \left| \frac{g_m - sC_{gd}(sC_{gs}Z_{src} + g_mZ_{src} + 1)}{g_m} \right|^2 + \frac{\gamma g_m}{R_{src}} \left| \frac{1 + sZ_{src}C_{gs}}{g_m} \right|^2$$

If a source impedance is formed with a resistive and an inductive part, again the inductance can be chosen to resonate with the capacitive effects present in the transistor. Thereby it is possible to lower the noise factor. To find the optimal value of  $L_{src}$ , the derivative of the noise factor is taken and made equal to zero:

$$\frac{\partial F_{CG}}{\partial L_{src}} = 0$$

$$L_{src,opt,NF} \approx \frac{R_g C_{gd} (\omega^2 C_{gd} C_{gs} - g_m^2) + C_{gs} \gamma g_m}{\omega^2 R_g C_{gd}^2 (\omega^2 C_{gs}^2 + g_m^2) + \omega^2 C_{gs}^2 \gamma g_m}$$

If  $R_g$  is very small, the optimal source inductance converges to:

$$L_{src,opt,NF} pprox rac{1}{\omega^2 C_{qs}}$$

Figure 2.11: Calculated noise figure  $(10\log F_{CG})$  as function of  $R_{src}$  with  $L_{src} = L_{src,opt,NF}$  and  $W_{MOST} = 30 \mu \text{m}$ .

To find the optimal value for  $R_{src}$ , also the derivative is taken and made equal to zero:

$$\frac{\partial F_{CG}}{\partial R_{src}} = 0$$

$$R_{src,opt,NF} \approx g_m \omega (C_{gd} + C_{gs}) \frac{\sqrt{\omega^2 R_g^2 C_{gd}^2 + R_g \gamma g_m}}{\omega^2 R_g C_{gd}^2 (\omega^2 C_{gs}^2 + g_m^2) + \omega^2 C_{gs}^2 \gamma g_m}$$

If  $R_g$  is again small, the optimal source resistance also becomes small. The resulting  $F_{min}$  is approximately equal to:

$$\begin{split} F_{CG,min} &\approx 1 + 2\omega\sqrt{R_g}\frac{(\omega\sqrt{R_g})^2C_{gd}^2 + \omega\sqrt{R_g}C_{gd}\sqrt{\omega^2R_gC_{gd}^2 + \gamma g_m} + \gamma g_m}{\omega_t\sqrt{\omega^2R_gC_{gd}^2 + \gamma g_m}} \\ \\ F_{CG,min} &\approx 1 + \omega R_gC_{gd} + 2\frac{\omega\sqrt{R_g}}{\omega_t} \cdot \frac{\omega^2R_gC_{gd}^2 + \gamma g_m}{\sqrt{\omega^2R_gC_{gd}^2 + \gamma g_m}} \\ \\ F_{CG,min} &\approx 1 + \omega R_gC_{gd} + 2\frac{\omega}{\omega_t} \cdot \sqrt{\omega^2R_g^2C_{gd}^2 + R_g\gamma g_m} \end{split}$$

As can be seen from this formula, also for the common gate topology maximizing  $\omega_t$  lowers the noise factor. Therefore  $g_m$  must be maximized, at the cost of power consumption. Because  $\omega/\omega_t \approx 1/2$  for 60 GHz in CMOS 65 nm,  $F_{CG,min}$  is approximately equal to:

$$F_{CG,min} \approx 1 + \omega R_g C_{gd} + \sqrt{\omega^2 R_g^2 C_{gd}^2 + R_g \gamma g_m}$$

If realistic values are filled in, the expression converges to:

$$\rightarrow F_{CG,min} \approx 1 + \sqrt{R_q \gamma g_m}$$

As can be seen the  $F_{min}$  becomes small for small  $R_g$ . Next feature is the input impedance. This is calculated in the following formula using the same approach as in the previous section:

$$Z_{in} = \frac{s^2 R_g C_{gd} C_{gs} + s C_{gd} g_m R_g + s C_{gd} + \frac{R_g s (C_{gs} + C_{gd}) + 1}{R_{ds} || Z_{load}}}{s^2 C_{gs} C_{gd} + s C_{gd} g_m + \frac{s C_{gd}}{R_{ds}} + \frac{s C_{gs}}{R_{ds} || Z_{load}} + \frac{s^2 R_g C_{gd} C_{gs} + s C_{gd} g_m R_g + g_m}{Z_{load}} + \frac{R_g s (C_{gs} + C_{gd}) + 1}{R_{ds} Z_{load}}}$$

If  $Z_{load}$  is assumed small, the input impedance reduces to

$$Z_{in} pprox rac{1 + sR_g(C_{gd} + C_{gs})}{s^2 R_g C_{gd} C_{gs} + sC_{gd} g_m R_g + rac{R_g}{R_{ds}} s(C_{gd} + C_{gs}) + sC_{gs} + g_m + rac{1}{R_{ds}}}$$

$$Z_{in} \approx \frac{1 + jg_m R_g \frac{\omega}{\omega_t}}{-\omega^2 R_g C_{gd} C_{gs} + j\omega (C_{gd} g_m R_g + \frac{g_m R_g}{\omega_t R_{ds}} + C_{gs}) + g_m + \frac{1}{R_{ds}}}$$

Because  $R_g$  is usually small and  $g_m R_g \frac{\omega}{\omega_t} \approx \frac{1}{2} g_m R_g < 1$ ,  $Z_{in}$  can be approximated by:

$$Z_{in} pprox rac{1}{g_m + rac{1}{B_{sh}} + j\omega C_{gs}}$$

$$Z_{in} pprox rac{g_m + rac{1}{R_{ds}} - j\omega C_{gs}}{(g_m + rac{1}{R_{ds}})^2 + \omega^2 C_{gs}^2}$$

$$\rightarrow R_{in} \approx \frac{g_m + \frac{1}{R_{ds}}}{(g_m + \frac{1}{R_{cr}})^2 + \omega^2 C_{as}^2} \approx \frac{g_m}{g_m^2 + \omega^2 C_{as}^2}$$

$$\rightarrow X_{in} \approx \frac{-\omega C_{gs}}{(g_m + \frac{1}{R_{ds}})^2 + \omega^2 C_{gs}^2} \approx \frac{-\omega C_{gs}}{g_m^2 + \omega^2 C_{gs}^2}$$

If  $Z_{load}$  is assumed big, the input impedance neglecting  $R_g$  becomes:

$$Z_{in} pprox rac{R_{ds} + rac{1}{sC_{gd}}}{g_m R_{ds} + 1 + sR_{ds}C_{gs} + rac{ar{C}_{gs}}{C_{gd}}}$$

This input impedance converges to the same situation with small  $Z_{load}$  if  $R_{ds}$  is big, which is usually the case. Therefore the input impedance of the common gate topology has little

dependence on  $Z_{load}$ . This input impedance is an important feature of the common gate topology. It gives the designer the freedom to choose an input impedance by setting the biasing of the transistor. By doing this, matching between the LNA and the antenna can be provided.

Under input matching conditions  $R_{in}$  has to be equal to  $R_{src}$ . Also  $X_{in}$  then has to be equal to  $-X_{src}$ . This means an inductance equal to:

$$L_{src,match} = \frac{\omega C_{gs}}{g_m^2 + \omega^2 C_{gs}^2} \neq L_{src,NF}$$

As can be seen there is a tradeoff between the optimal inductance concerning noise performance and input match.

## 2.3 Discussion CS - CG

In the following table the common source topology is compared with the common gate topology concerning gain and noise performance based on the previous sections:

| Topology | Voltage gain | Current gain | Noise performance | Input impedance          |

|----------|--------------|--------------|-------------------|--------------------------|

| CS       | +            | +            | +                 | depends on Miller effect |

| CG       | +            | -            | +                 | +                        |

As can be seen from this table, both common source and common gate topology have nice properties. The common source stage has both high current and voltage gain. It thereby makes sure the noise generated in the following stage can not flow directly to the input. So in a total system, the noise performance will be better. The noise performance of the topologies themselves are approximately the same for both stages.  $F_{min}$  for both topologies are approximately equal and is given below:

$$F_{CS,min} \approx F_{CG,min} \approx 1 + \sqrt{R_g \gamma g_m}$$

If the Miller effect is big in the common source topology, it's input impedance is approximately equal to the input impedance of the common gate. If the Miller effect on the other hand is small, the input impedance becomes mainly capacitive, which is less attractive for matching. Also the Miller effect present in the common source topology creates a path from output to input, causing a possibility for instability. It should therefore be blocked somehow. A choice was made to look at both a common source and common gate topology using feedback to see the effect of the feedback elements on the performance, and make a decision then.

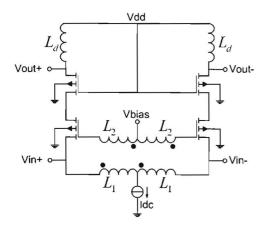

## 2.4 $G_m$ -boosted common gate

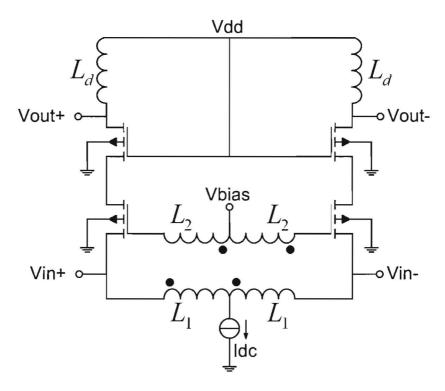

The first topology discussed as a candidate for the 60 GHz LNA is the  $g_m$ -boosted common gate LNA. For the active part this topology makes use of a common gate stage. As seen in the previous part this topology has as an advantage that there is an easy way of providing a wideband input match. After applying this, the biasing of the transistor is set to a certain value resulting in a certain noise figure. When using  $g_m$ -boosting, a lower noise figure can be

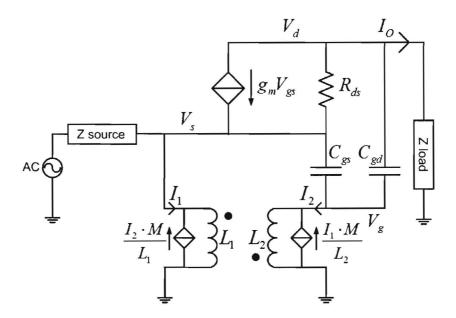

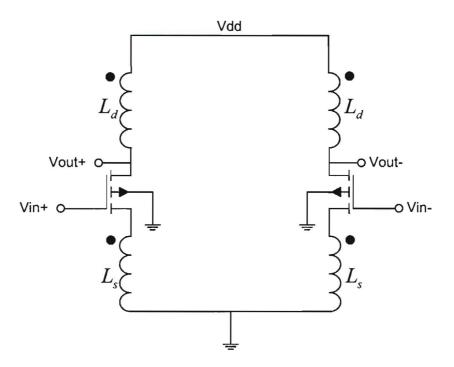

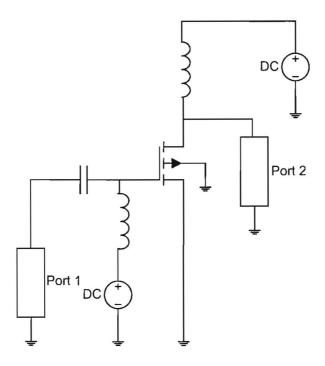

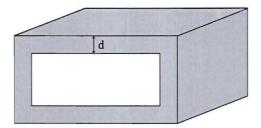

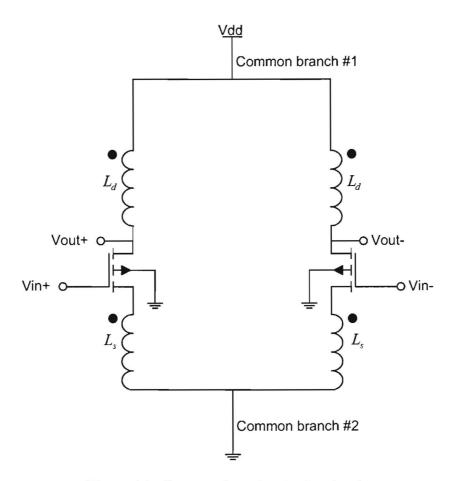

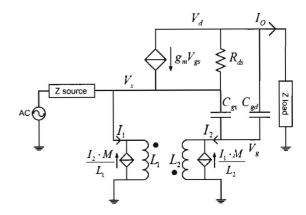

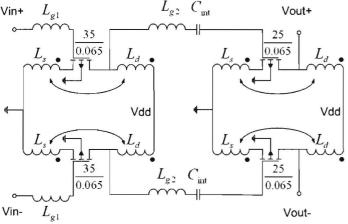

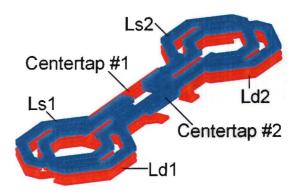

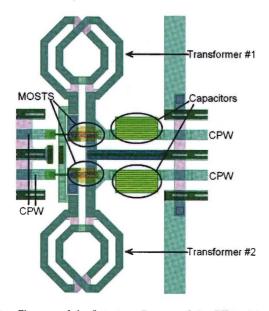

Figure 2.12:  $G_m$ -boosted common gate LNA. The left combination of  $L_1$  and  $L_2$  forms a transformer as well as the right combination.

achieved with the common gate stage while still maintaining the input match criterion [1]. The schematic of the  $g_m$ -boosted CG LNA is shown in figure 2.12.

As can be seen in the schematic the input stage is followed by another common gate stage, so a cascode. This is done to increase the output impedance and isolate the output from the input. Because the common gate topology only gives voltage gain, the output impedance must be high to have enough gain. The biasing of the transistors is done at the inductors. Inductors are interesting because they have no DC voltage drop and add little noise.

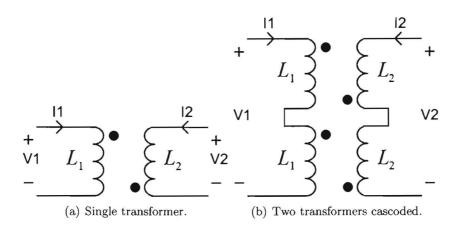

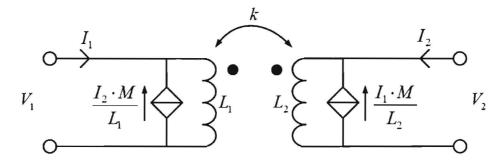

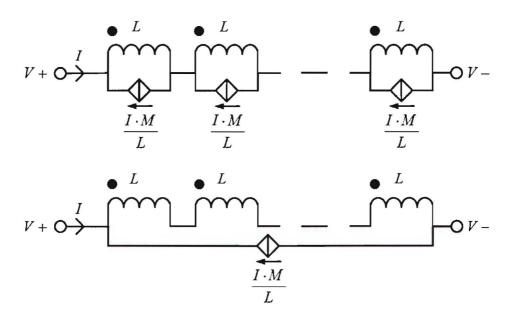

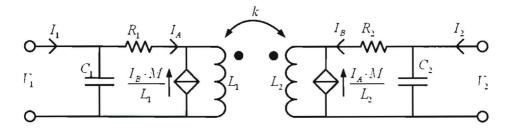

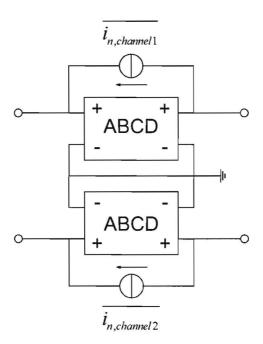

To be able to use the half circuit concept, the transformer needs to be cut in two parts. To see what effect this has on the inductance and the coupling, the Z-parameters are used. In figures 2.13(a) and 2.13(b) a single and a cascoded transformer are shown.

The Z-parameters of the single transformer look as follows:

$$\mathbf{Z}_{single} = \left[ \begin{array}{cc} sL_1 & sM \\ sM & sL_2 \end{array} \right]$$

With M being the mutual inductance defined as  $k\sqrt{L_1L_2}$  (k = the coupling factor). To obtain the Z-parameters for the cascoded transformers, the Z-matrix of the single transformer must be multiplied by two (because of the series connection and the fact that both transformers are identical):

$$\mathbf{Z}_{casc} = \begin{bmatrix} s \cdot 2L_1 & s \cdot 2M \\ s \cdot 2M & s \cdot 2L_2 \end{bmatrix} = \begin{bmatrix} sL_{1,casc} & sM_{casc} \\ sM_{casc} & sL_{2,casc} \end{bmatrix}$$

Figure 2.13: Single and cascoded transformer

This means all inductances double. For the coupling factor this means:

$$M_{casc} = 2M_{single} = 2k\sqrt{L_1L_2} = k\sqrt{2L_1 \cdot 2L_2} = k\sqrt{L_{1,casc}L_{2,casc}}$$

So the coupling factor stays the same, and the inductances halve when using the half circuit concept.

## 2.4.1 Input impedance

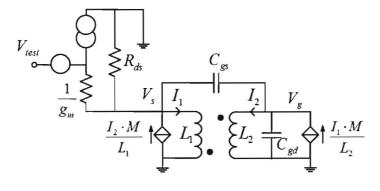

To calculate the input impedance the small signal circuit shown in figure 2.14 is used ( $R_g$  has been neglected because of it's little influence).

Figure 2.14: Small signal equivalent circuit of the  $g_m$ -boosted common gate LNA

An ideal cascode is assumed, so  $Z_{load} = 0$ . The Y-parameters of the network look as follows:

$$\mathbf{Y} = \begin{bmatrix} sC_{gs} + g_m + \frac{1}{R_{ds}} + \frac{1}{s(1-k^2)L_1} & -sC_{gs} - g_m - \frac{k}{s(1-k^2)\sqrt{L_1L_2}} & -\frac{1}{R_{ds}} \\ -sC_{gs} - \frac{k}{s(1-k^2)\sqrt{L_1L_2}} & s(C_{gs} + C_{gd}) + \frac{1}{s(1-k^2)L_2} & -sC_{gd} \\ -g_m - \frac{1}{R_{ds}} & g_m - sC_{gd} & \frac{1}{Z_{load}} + sC_{gd} + \frac{1}{R_{ds}} \end{bmatrix}$$

$$\mathbf{Y} \cdot \left[egin{array}{c} V_s \ V_g \ V_d \end{array}

ight] = \left[egin{array}{c} I_{in} \ 0 \ 0 \end{array}

ight]$$

If  $C_{gd}$  and  $R_{ds}$  are neglected because of their little effect on  $Z_{in}$  the input impedance looks as follows, with  $n = \sqrt{\frac{L_2}{L_1}}$ :

$$Z_{in} \approx \frac{s^2(1-k^2)L_2C_{gs}+1}{sC_{gs}(n^2-2kn+1)+g_m(1-kn)+\frac{1}{sL_1}}$$

Because the  $(1 - k^2)$  term in the numerator becomes small when  $k \to -1$ , the input impedance can be approximated by the following formula for high coupling:

$$Z_{in} \approx \frac{1}{sC_{gs}(1+n)^2 + g_m(1+n) + \frac{1}{sL_1}}$$

If  $L_1$ ,  $C_{gs}$  and n are chosen in such a way that they become resonant at the operating frequency (which is the same frequency for minimum noise, see appendix), the input impedance at resonance reduces to:

$$Z_{in} pprox rac{1}{g_m(1+n)}$$

So for the differential situation the input impedance is:

$$Z_{in_{diff}} = 2 \cdot Z_{in_{SE}} \approx \frac{2}{g_m(1+n)}$$

As can be seen from this formula, the real part of the input impedance of the  $g_m$ -boosted CG LNA is approximately lowered by a factor of  $\frac{1}{1+n}$  in comparison of the conventional CG stage. This is due to the amplification between the source and gate.

## 2.4.2 Noise factor

In the appendix the noise factor is calculated. The resulting noise factor looks as follows:

$$F_{g_m-boosted} \approx 1 + \frac{2R_g}{(1+n)^2 R_{src}} \left| 1 + \frac{Z_{src}}{2sL_1} \right|^2 + \frac{2\gamma}{g_m(1+n)^2 R_{src}}$$

As can be seen the noise factor can be lowered by increasing  $g_m$ , n and  $R_{src}$ , and lowering  $R_g$ . If  $X_{src}$  is chosen capacitive, the noise due to  $R_g$  can be made very small and neglected, resulting in:

$$F_{g_m-boosted} \approx 1 + \frac{2\gamma}{g_m(1+n)^2 R_{src}}$$

If now a power match is created between the antenna and the LNA,  $\frac{g_m(1+n)}{2}R_{src}=1$  (for high coupling), the noise figure for the  $g_m$ -boosted CG LNA looks as follows:

$$F_{g_m-boosted} \approx 1 + \frac{\gamma}{1+n}$$

As can be seen from this formula, for high transformer coupling the noise factor is lowered by (1+n). This quantity can be identified as the voltage gain between the source and gate due to the transformer. This formula suggests the noise figure can be made arbitrarily low by increasing n. This is not true because there are also other noise sources present in the LNA such as the induced gate noise [1]. Also the presence of the cascode transistor will deteriorate the noise figure. The noise figure will therefore be higher in reality and n will have a certain optimum. Simulations will be used to determine the exact value of the noise factor and optimal n, using more realistic models for the used components taking various non-idealities into account.

## 2.4.3 Loop gain

For the lowering of the noise factor, a negative coupling is needed. To avoid instability it is needed to avoid positive feedback. Therefore the loop gain  $A\beta$  of the  $g_m$ -boosted CG LNA has to be calculated. To determine the open loop gain, the loop has to be broken somewhere. In figure 2.15 it is shown where the loop is opened. The transistor model is replaced by a combination of a nullator and a norator.

Figure 2.15: Opening the loop to calculate the open loop gain

The resulting loop gain with  $C_{qd}$  and  $R_{ds}$  ignored looks as follows:

$$A\beta = \frac{g_m(s^2(1-k^2)L_2C_{gs} + kn)}{g_m(s^2(1-k^2)L_2C_{gs} + 1) + sC_{gs}(n^2 - 2kn + 1) + \frac{1}{sL_1}}$$

At the operating frequency  $L_1$ ,  $C_{gs}$ , n and k are again chosen to resonate, so the loop gain looks as follows:

$$A\beta = \frac{(kn - \omega^2(1 - k^2)L_2C_{gs})}{(1 - \omega^2(1 - k^2)L_2C_{gs})}$$

With  $|k| \to 1$ , the expression converges to kn. This means the loop gain is negative when the coupling is negative. This holds as long as the denominator does not become negative as well. So to have negative feedback the following equations must hold:

And

$$\omega^2 (1 - k^2) L_2 C_{gs} < 1$$

This is in agreement with the constraint for lowering the noise figure, namely a negative coupling.

## 2.4.4 Voltage gain

The output signal of the  $g_m$ -boosted CG LNA has been shorted to ground so far, because of the use of a cascode and to ease calculations. To determine the voltage gain there has to be some kind of load, which will be modeled by  $Z_{load}$ . To model the behavior of the cascode,  $C_{gd}$  and  $R_{ds}$  are disconnected from the drain and connected to ground. The voltage gain is given by the following formula (assuming an ideal cascode):

Figure 2.16: Small signal equivalent circuit to determine the voltage gain

$$\frac{V_{out}}{V_{in}} = \frac{g_m Z_{load}(s^2(1-k^2)L_2C_{gd} + 1 - kn)}{s^2(1-k^2)L_2(C_{gd} + C_{gs}) + 1}$$

As can be seen from this formula, if  $k \to -1$ , the transfer gain increases. So also for high gain,  $k \to -1$  is preferred. The resulting voltage gain is then:

$$\frac{V_{out}}{V_{in}} = g_m(1+n)Z_{load}$$

To maximize the voltage gain, the denominator can to be made equal to zero, so:

$$\omega^2 (1 - k^2) L_2 (C_{gd} + C_{gs}) = 1$$

The resulting value of  $L_1$  should then be:

$$L_1 = \frac{L_2}{n^2} = \frac{1}{\omega^2 n^2 (1 - k^2)(C_{qd} + C_{qs})}$$

This formula is not in accordance with the optimal value of  $L_1$  for noise performance and input impedance. So there has to be made some kind of compromise.

The transfer function also consists a double zero resulting in a notch in the transfer at:

$$\omega_{zero} = \frac{1 - kn}{(1 - k^2)L_2C_{gd}}$$

Operation around this frequency should be prevented.

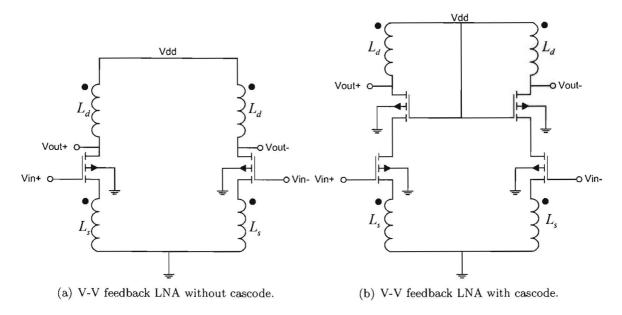

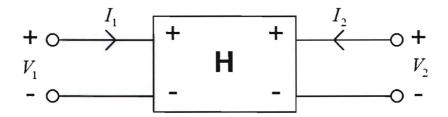

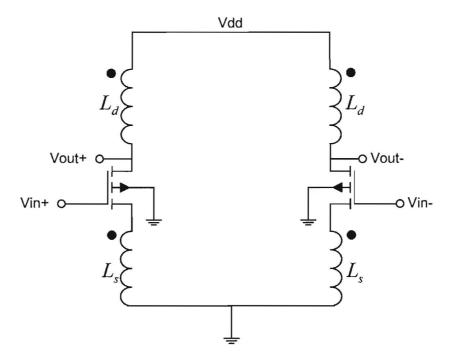

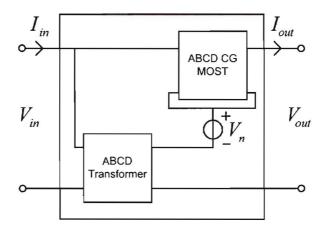

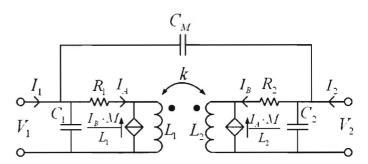

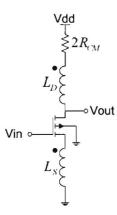

## 2.5 Voltage-voltage transformer feedback LNA

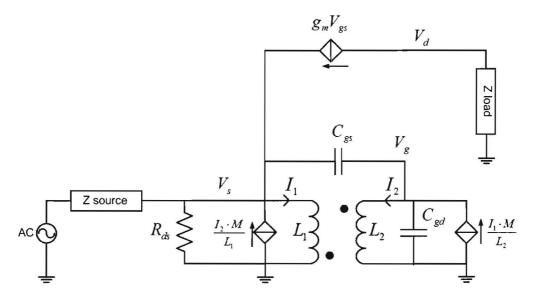

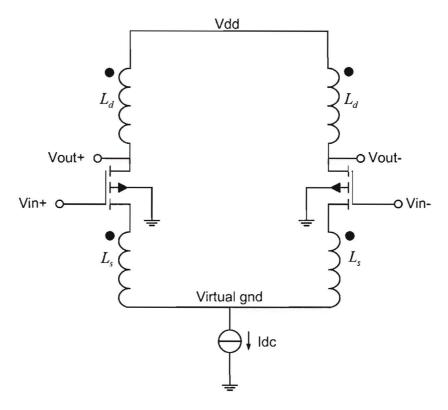

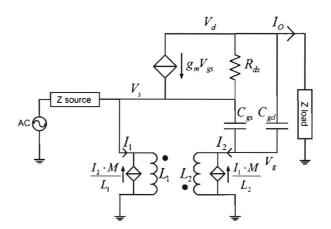

The second topology discussed as a candidate for the implementation of the 60 GHz LNA is the voltage-voltage transformer feedback LNA (see figure 2.17). This topology uses a CS MOST as an active part. Big advantage of a common source MOST is the combination of both high voltage gain and current gain. Disadvantage is the signal path from output to input through  $C_{gd}$ , the Miller capacitance. This increases the possibility of instability. Measures have to be taken against this reverse signal path. By using the voltage-voltage transformer feedback LNA topology this is possible without the use of the conventional cascode. This increases voltage headroom for the MOST and lowers the noise factor of the total LNA. In most calculations  $R_g$  is neglected because of its little influence on most parameters. Only for the noise performance and the input impedance it has been taken into account.

## 2.5.1 Output isolation

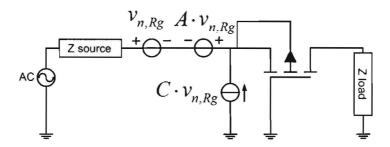

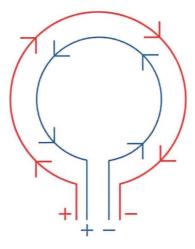

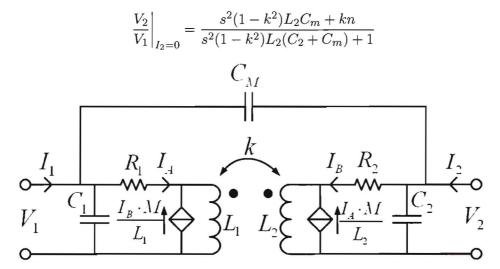

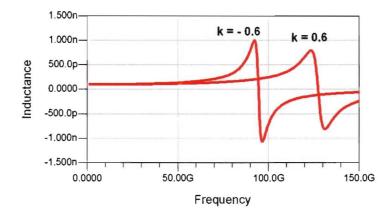

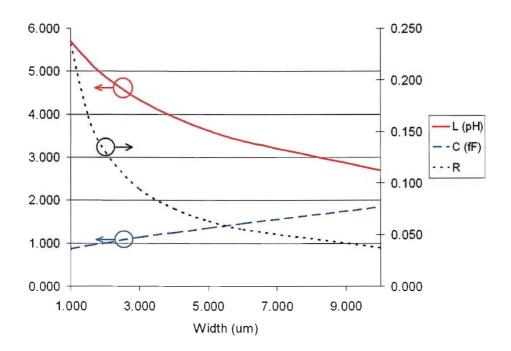

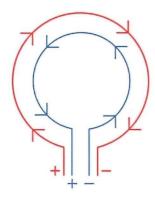

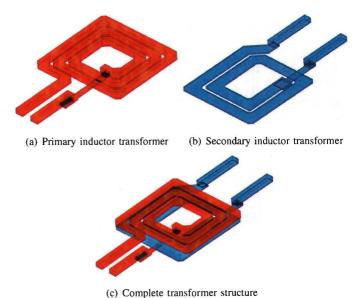

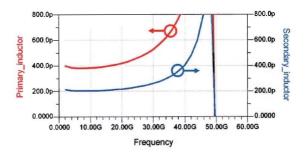

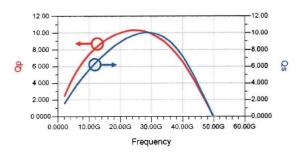

Because the active part of the voltage voltage feedback topology is a common source MOST, there has to be some kind of output isolation to minimize the signal path from output to input. The output signal at the drain  $(V_{out})$  is connected via  $C_{gd}$  to  $V_g$ , as is shown in figure 2.18. Because of the transformer being connected between the drain and source of the transistor the signal at the drain is being copied to the source. The signal at the source is the inverse of the signal at the drain because of the negative coupling. The signal at the source is connected to the gate through  $C_{gs}$ . Because of the opposite effects of the signals through  $C_{gs}$  and  $C_{gd}$  the output signal can be canceled at  $V_g$  [3]. The transfer function  $\frac{V_g}{V_{out}}$  of the circuit is calculated using the half circuit concept and looks as follows:

$$\frac{V_g}{V_{out}} =$$

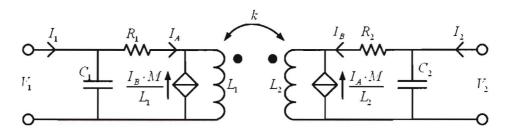

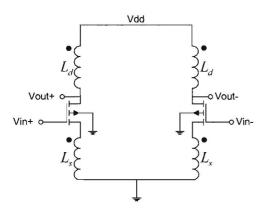

Figure 2.17: Voltage voltage transformer feedback LNA. The left combination of  $L_s$  and  $L_d$  forms a transformer as well as the right combination

$$\frac{s^2(1-k^2)L_sC_{gs}R_{ds}+s(1-k^2)L_s(g_mR_{ds}+1+\frac{C_{gs}}{C_{gd}})+R_{ds}(1+\frac{kC_{gs}}{nC_{gd}})}{s^2(1-k^2)L_sC_{gs}R_{ds}+s(1-k^2)L_s(g_mR_{ds}+1+\frac{C_{gs}}{C_{gd}})+R_{ds}(1+\frac{C_{gs}}{C_{gd}})}$$

To see the low frequency behavior the limit for  $s \to 0$  is taken:

$$\lim_{s \to 0} \frac{V_g}{V_{out}} = \frac{R_{ds}(1 + \frac{kC_{gs}}{nC_{gd}})}{R_{ds}(1 + \frac{C_{gs}}{C_{gd}})} = \frac{nC_{gd} + kC_{gs}}{nC_{gd} + nC_{gs}}$$

$$\frac{V_g}{V_{out}} = 0 \quad \text{if} \quad nC_{gd} + kC_{gs} = 0$$

$$\rightarrow \frac{n}{k} = -\frac{C_{gs}}{C_{ad}}$$

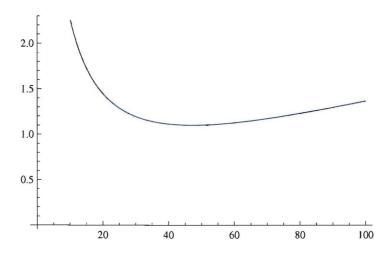

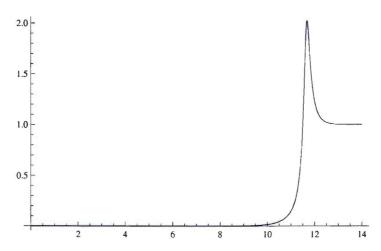

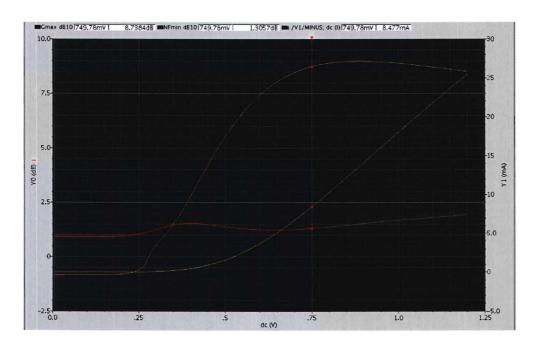

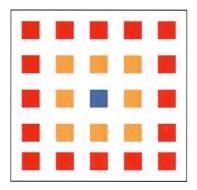

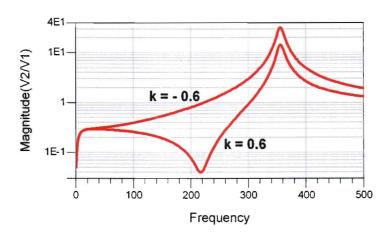

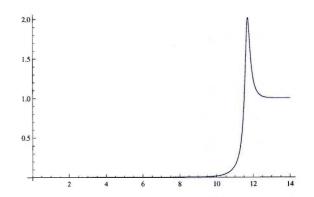

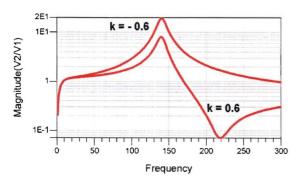

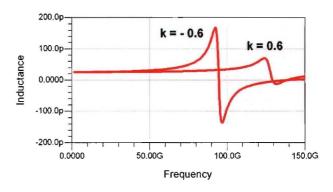

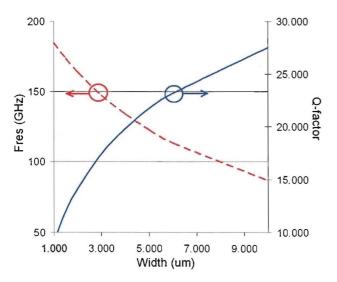

To see the output isolation versus frequency, values for a 30  $\mu m$  MOSFET are taken in combination with a transformer with n=2, k=-0.667 and  $L_s=30pH$ . The values for the transformer are chosen such that  $-\frac{n}{k}=\frac{C_{gs}}{C_{gd}}$ . For technologies such as CMOS 65nm this ratio is approximately equal to 3. The magnitude of  $V_g$  versus  $V_{out}$  is shown in figure 2.19.

Figure 2.19 shows good output isolation for frequencies below 1-10 GHz. For frequencies from 10-200 GHz the output isolations becomes worse. Above 200 GHz there is no isolation anymore under the given circumstances, but because the used MOST model is not valid anymore for these high frequencies, these results cannot be trusted.

Figure 2.18: Lumped element model of the V-V transformer feedback topology (single ended).

Figure 2.19: Magnitude response  $\frac{V_g}{V_{out}}$  with  $\frac{n}{k} \approx -\frac{C_{gs}}{C_{gd}} = -3$ . The horizontal axis shows the frequency on a logarithmic scale.

## 2.5.2 Voltage gain

To calculate the voltage gain, also the half circuit concept is used, because it is equal to the voltage gain of the differential implementation. To determine the voltage gain, the limit is taken for  $R_{ds} \to \infty$ . Simulations show small deviation due to this, but calculations become much easier.

$$\lim_{R_{ds}\to\infty}\frac{V_{out}}{V_{in}} = \frac{s^3(1-k^2)L_dC_{gs}C_{gd} + s^2(1-k^2)g_mL_dC_{gd} + sn^2C_{gd} + knsC_{gs} - g_mn(n-k)}{s^3(1-k^2)L_dC_{gd}C_{gs} + s^2(1-k^2)g_mL_dC_{gd} + sn^2C_{gd} + sC_{gs} + g_m(1-kn) + \frac{1}{sL_s}}$$

If  $-\frac{n}{k}$  is chosen to be  $\frac{C_{gs}}{C_{gd}}$  to provide output isolation, the  $sn^2C_{gd}+knsC_{gs}$  term in the numerator cancels:

$$\lim_{R_{ds}\to\infty} \frac{V_{out}}{V_{in}} \bigg|_{-\frac{n}{k} = \frac{C_{gs}}{C_{ad}}} =$$

$$\frac{s^3(1-k^2)L_dC_{gs}C_{gd} + s^2(1-k^2)g_mL_dC_{gd} - g_mn(n-k)}{s^3(1-k^2)L_dC_{gd}C_{gs} + s^2(1-k^2)L_dC_{gd}g_m + sn^2C_{gd} + sC_{gs} + g_m(1-kn) + \frac{1}{sL_s}}$$

For high coupling, the higher order terms disappear:

$$\lim_{k \to -1} \lim_{R_{ds} \to \infty} \left. \frac{V_{out}}{V_{in}} \right|_{-\frac{n}{k} = \frac{C_{gs}}{C_{od}}} = \frac{-g_m n(1+n)}{sn^2 C_{gd} + sC_{gs} + g_m(1+n) + \frac{1}{sL_s}}$$

If we choose the value of  $L_s$  to resonate with  $C_{gs}$  and  $C_{gd}$ , the gain is maximal. To do so, the value of  $L_s$  should be:

$$L_s = \frac{1}{\omega^2 (n^2 C_{gd} + C_{gs})}$$

The voltage gain at resonance then reduces to:

$$\lim_{k \to -1} \lim_{R_{ds} \to \infty} \frac{V_{out}}{V_{in}} \bigg|_{-\frac{n}{k} = \frac{C_{gs}}{C_{od}}} = \frac{-g_m n(1+n)}{g_m(1+n)} = -n$$

So to have high gain, n should be high. Combining this with the criterion for output isolation, n and k should both be high. In practical situations the highest possible coupling on chip is approximately 0.7 - 0.8. This results in a transformer windings ratio of 2.1 - 2.4. These are also practical values for implementation on chip.

## 2.5.3 Input impedance

Also for the calculation of the input impedance, the half circuit concept is used. Afterwards, to get the input impedance of the differential structure the impedance has to be multiplied with 2. To determine the input impedance the schematic of figure 2.18 is used,  $R_{ds}$  has been neglected because it has little effect on the input impedance but it makes calculations more complex:

$$\mathbf{Y} = \begin{bmatrix} \frac{1}{R_g} & -\frac{1}{R_g} & 0 & 0\\ 0 & s(C_{gs} + C_{gd}) & -sC_{gs} & -sC_{gd}\\ 0 & -(sC_{gs} + g_m) & \frac{1}{R_{ds}} + g_m + sC_{gs} + \frac{1}{s(1-k^2)L_s} & -\frac{1}{R_{ds}} + \frac{-k}{s(1-k^2)\sqrt{L_dL_s}}\\ 0 & -(sC_{gs} - g_m) & -\frac{1}{R_{ds}} - g_m - \frac{k}{s(1-k^2)\sqrt{L_dL_s}} & \frac{1}{R_{ds}} + sC_{gd} + \frac{1}{s(1-k^2)L_d} \end{bmatrix}$$

$$\mathbf{Y} \cdot \left[egin{array}{c} V_i \ V_g \ V_s \ V_{out} \end{array}

ight] = \left[egin{array}{c} I_{in} \ 0 \ 0 \ 0 \end{array}

ight]$$

$$\lim_{R_{ds}\to\infty} Z_{in} =$$

$$R_g + \frac{s^3(1-k^2)L_dC_{gd}C_{gs} + s^2(1-k^2)L_dC_{gd}g_m + s(n^2C_{gd} + C_{gs}) + g_m(1-kn) + \frac{1}{sL_s}}{sC_{gd}(n^2 - 2kn + 1)(sC_{gs} + g_m) + \frac{C_{gd} + C_{gs}}{L_s}}$$

For high coupling, the high order terms in the denominator disappear:

$$\lim_{k \to -1} \lim_{R_{ds} \to \infty} Z_{in} = R_g + \frac{s(n^2 C_{gd} + C_{gs}) + g_m(1+n) + \frac{1}{sL_s}}{sC_{gd}(1+n)^2(sC_{gs} + g_m) + \frac{C_{gd} + C_{gs}}{L_s}}$$

When  $L_s$  is chosen to have the value for maximal voltage gain, the input impedance at resonance reduces to:

$$\to L_s = \frac{1}{\omega^2 (n^2 C_{gd} + C_{gs})}$$

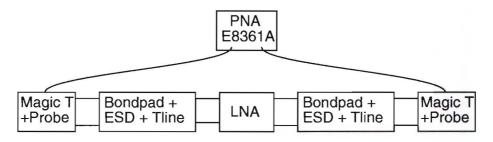

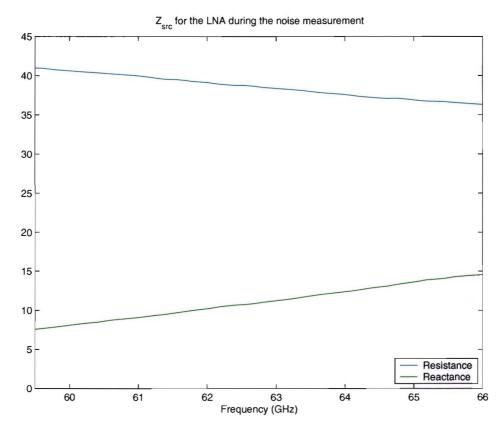

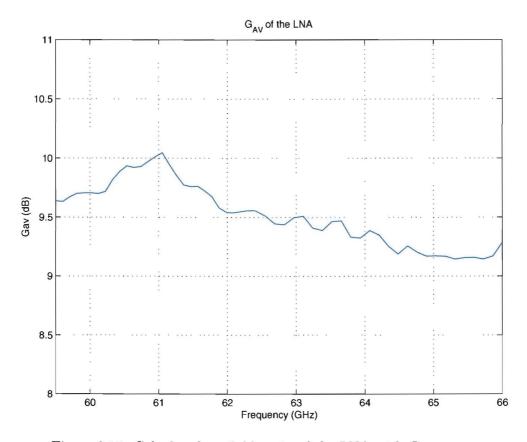

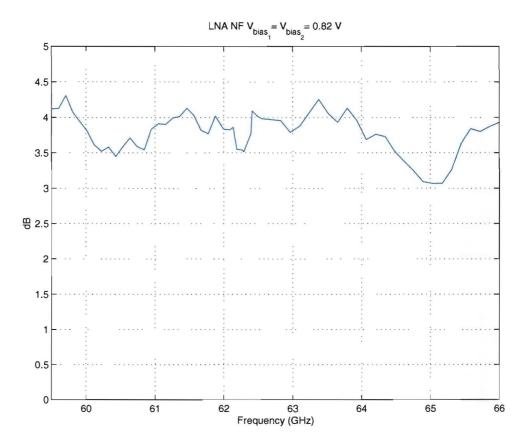

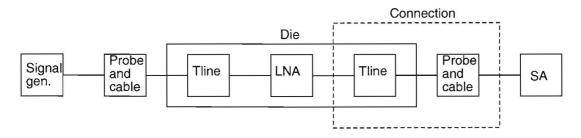

$$\lim_{k \to -1} \lim_{R_{ds} \to \infty} Z_{in} = R_g + \frac{g_m(1+n)}{\omega^2 (nC_{gd} - C_{gs})^2 + j\omega C_{gd}g_m(1+n)^2}$$