#### MASTER

A framework for data-access strategies in GPGPU programs

Mallens, L.F.C.C.

Award date: 2013

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

TU/e Technische Universiteit Eindhoven University of Technology

#### Department of Mathematics and Computer Science

Den Dolech 2, 5612 AZ Eindhoven P.O. Box 513, 5600 MB Eindhoven The Netherlands http://w3.win.tue.nl/nl/

Series title: Graduation report, Embedded Systems

**Commissioned by Professor:** prof. dr. H. Corporaal

Group / Chair: Electronic Systems

Date of graduation symposium: March 25, 2013

# A framework for data-access strategies in GPGPU programs

by

Author: L.F.C.C. Mallens

Internal supervisor: prof. dr. H. Corporaal, Technische Universiteit Eindhoven

External supervisor: Drs. S. Holdermans, Vector Fabrics B.V.

#### Abstract

In recent years, graphics processing units (GPUs) became more and more popular as high performance processing units. Due to the availability of hundreds of cores, code fragments speed up significantly when they are transformed from CPU functions to GPU kernels.

The transformation process is non-trivial and therefore error prone. Developing correct and efficient GPU accelerated programs is time consuming.

One of the aspects that has to be considered is the logically and physically separation of a GPU's address space from the CPU. In order to enable kernel execution on the GPU, data transfers between the CPU and GPU need to be explicitly scheduled in the code. Since the CPU-GPU communication bandwidth is relatively low, compared to the computational power of the GPU, the number of transferred bytes should be minimised.

A GPU is equipped with an advanced hierarchy of scratchpad memories, that is different from CPU memory hierarchies. When these differences are not taken into during the development of the GPU kernel, the computational power of the GPU is not fully exploited. Memory access patterns need to be adapted to take full advantage of this memory hierarchy.

In order to decrease development time, there is an increasing interest in tools that can assist in the transformation process from CPU programs to GPU accelerated programs.

In this thesis, we propose a set of analysis tools and code optimisations to aid the transformation of CPU code fragments to GPU kernels. The tools focus on optimising the CPU-GPU communication strategy and optimising the kernels for the GPU's advanced memory hierarchy.

## Contents

| 1 | Introduction 3                   |                                                                                                                                                                         |                              |  |  |  |  |  |  |  |  |  |

|---|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|--|--|--|

|   | 1.1                              | Challenges in GPGPU-programming                                                                                                                                         | . 3                          |  |  |  |  |  |  |  |  |  |

|   | 1.2                              | Contributions                                                                                                                                                           | . 5                          |  |  |  |  |  |  |  |  |  |

|   | 1.3                              | Organisation of thesis                                                                                                                                                  | . 5                          |  |  |  |  |  |  |  |  |  |

| 2 | Bac                              | Background 6                                                                                                                                                            |                              |  |  |  |  |  |  |  |  |  |

| L | 2.1                              | -                                                                                                                                                                       | -                            |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.1.1 Hardware architecture                                                                                                                                             |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.1.2 CUDA programming model                                                                                                                                            |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.1.3 CUDA execution model                                                                                                                                              |                              |  |  |  |  |  |  |  |  |  |

|   | 2.2                              | OpenACC programming model                                                                                                                                               |                              |  |  |  |  |  |  |  |  |  |

|   | 2.3                              | Program analysis                                                                                                                                                        |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.3.1 Static program analysis                                                                                                                                           |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.3.2 Dynamic program analysis                                                                                                                                          |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.3.3 Extended call graph                                                                                                                                               |                              |  |  |  |  |  |  |  |  |  |

|   |                                  | 2.3.4 Data dependency analysis                                                                                                                                          |                              |  |  |  |  |  |  |  |  |  |

| 3 | Rela                             | ated work                                                                                                                                                               | 17                           |  |  |  |  |  |  |  |  |  |

|   | <b>6</b> D I                     |                                                                                                                                                                         | •                            |  |  |  |  |  |  |  |  |  |

| 4 |                                  | U data-transfer and allocation                                                                                                                                          | 20                           |  |  |  |  |  |  |  |  |  |

|   | 4.1                              | Individual kernels                                                                                                                                                      |                              |  |  |  |  |  |  |  |  |  |

|   | 4.2                              | Intra-kernel optimisations                                                                                                                                              |                              |  |  |  |  |  |  |  |  |  |

|   | 4.3                              | Location of copy, allocation and synchronisation actions                                                                                                                | . 25                         |  |  |  |  |  |  |  |  |  |

| 5 | _                                |                                                                                                                                                                         |                              |  |  |  |  |  |  |  |  |  |

| 3 | GPl                              | U kernel optimisations                                                                                                                                                  | 32                           |  |  |  |  |  |  |  |  |  |

| 9 | <b>GPl</b><br>5.1                | <b>U kernel optimisations</b> Extraction of linear access patterns                                                                                                      | . 34                         |  |  |  |  |  |  |  |  |  |

| 5 |                                  | Extraction of linear access patterns                                                                                                                                    | . 34<br>. 35                 |  |  |  |  |  |  |  |  |  |

| 3 | 5.1                              | Extraction of linear access patterns                                                                                                                                    | . 34<br>. 35<br>. 36         |  |  |  |  |  |  |  |  |  |

| 3 | 5.1                              | Extraction of linear access patterns                                                                                                                                    | . 34<br>. 35<br>. 36<br>. 38 |  |  |  |  |  |  |  |  |  |

| J | 5.1                              | Extraction of linear access patterns                                                                                                                                    | . 34<br>. 35<br>. 36<br>. 38 |  |  |  |  |  |  |  |  |  |

| 6 | 5.1<br>5.2<br>5.3                | Extraction of linear access patterns                                                                                                                                    | . 34<br>. 35<br>. 36<br>. 38 |  |  |  |  |  |  |  |  |  |

| _ | 5.1<br>5.2<br>5.3                | Extraction of linear access patterns                                                                                                                                    |                              |  |  |  |  |  |  |  |  |  |

| _ | 5.1<br>5.2<br>5.3<br><b>Perf</b> | Extraction of linear access patternsCoalesced memory access5.2.1Coalescing optimal thread-configuration5.2.2Further coalescing optimisationsReuse through shared memory |                              |  |  |  |  |  |  |  |  |  |

| _ | 5.1<br>5.2<br>5.3<br><b>Perf</b> | Extraction of linear access patterns                                                                                                                                    |                              |  |  |  |  |  |  |  |  |  |

|   | 6.2                                                           | Performance |                                |    |  |  |  |  |

|---|---------------------------------------------------------------|-------------|--------------------------------|----|--|--|--|--|

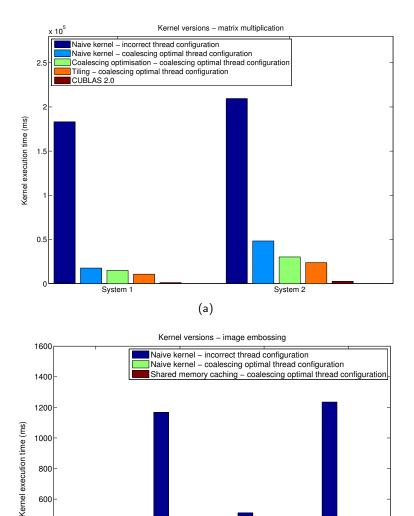

|   |                                                               | 6.2.1       | Kernel optimisations           | 48 |  |  |  |  |

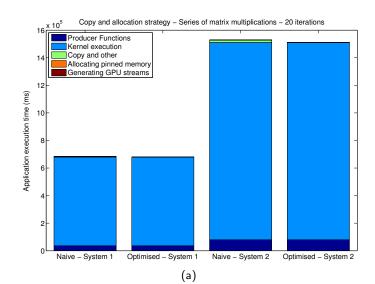

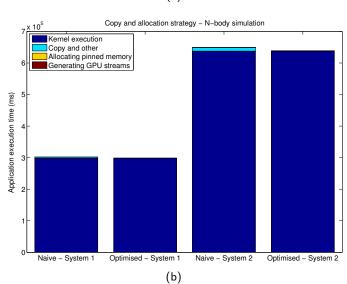

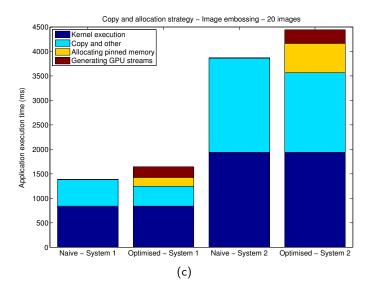

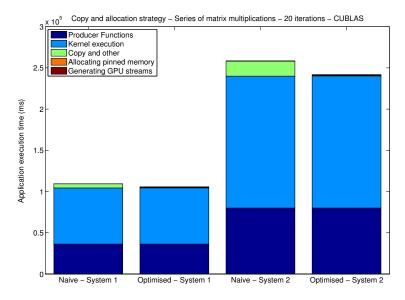

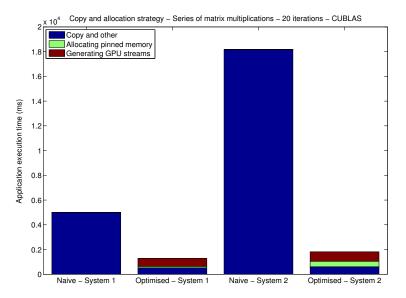

|   |                                                               | 6.2.2       | Copy and allocation strategies | 50 |  |  |  |  |

| 7 | 7 Future work                                                 |             |                                |    |  |  |  |  |

| 8 | 3 Conclusions                                                 |             |                                |    |  |  |  |  |

| Α | A Data-transfer strategy in matrix multiplication application |             |                                |    |  |  |  |  |

### Chapter 1

### Introduction

Nowadays, hardware vendors resort to the development of multi-processor platforms, to satisfy the ever increasing hunger for processing power. Multi-processor platforms have a better performance-to-watt ratio compared to single processor platforms [1]. Programs need to be adapted to these new platforms. Hereto they need to be divided in tasks that are assigned to threads. Threads are assigned to different processing units to be executed in parallel.

Graphical processor units (GPUs) become more and more popular as a multi-processor platform. GPUs evolved from devices that could only render three-dimensional graphics to *accelerators* that can execute a wide range of computational tasks. An accelerator is a device that executes tasks in parallel to a *host* (device containing the CPU). GPUs that can execute non-graphical tasks are called General Purpose GPUs (GPGPUs). GPGPUs have a large number of processing units that together offer high computational performance (hundreds of GFLOPS). Large speedups are achieved when CPU code fragments that expose a high level of data-parallelism are transformed into GPU *kernels*. GPU kernels are code-fragments that are executed on a GPU. Unfortunately, the transformation process is often non-trivial and far from easy. Therefore, transformation frameworks are developed that can aid programmers to generate GPGPU accelerated programs, i.e. code fragments are transformed into GPU kernels. This thesis presents a set of tools that fits in such a framework.

#### 1.1 Challenges in GPGPU-programming

Programmers face a number of challenges in order to design correct and efficient GPGPU accelerated applications. Some of these challenges are listed in this section.

The majority of GPUs have a logically separated memory space from the CPU, that is explicitly managed by software. Therefore a programmer has to state explicitly which data-structures need to be transferred between the host and the GPU. In the case that a CPU program is transformed into a GPGPU accelerated program, generating a correct data transfer strategy can be a time consuming task. Indirect addressing, pointer modification and aliasing can make it challenging for a programmer to observe which data-structures need to be transferred.

When the programmer has designed a correctly behaving GPGPU accelerated program, the resulting performance may be disappointing due to the following two reasons.

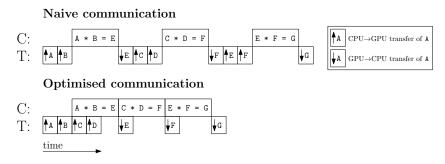

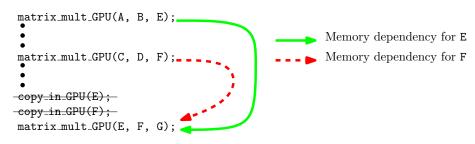

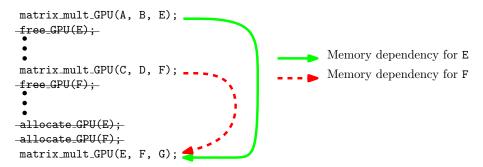

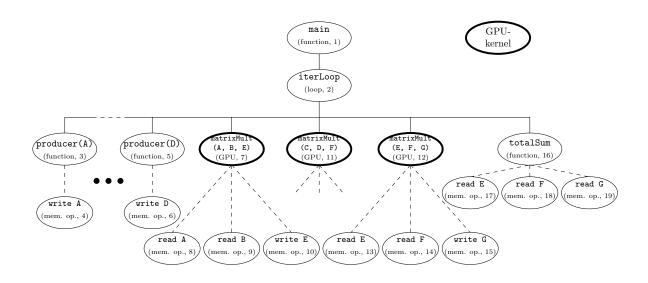

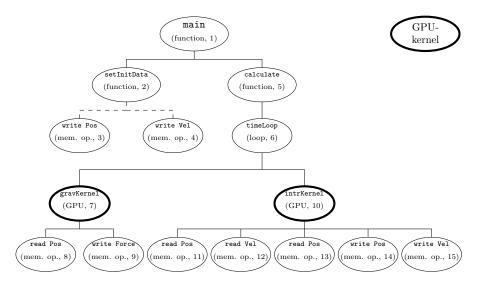

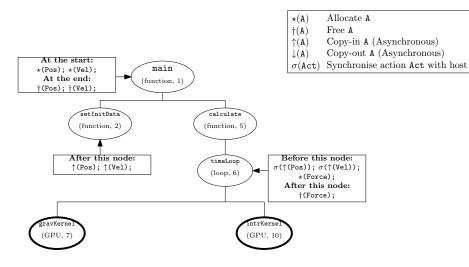

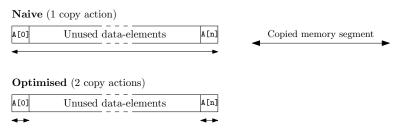

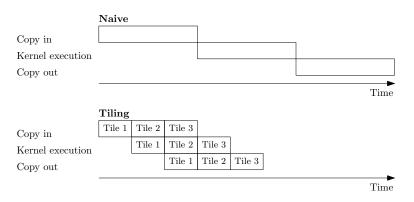

First, the overhead in CPU-GPU data communication can be considerably large. The memory hierarchy of a GPU is typically physically separated from the CPU's memory hierarchy. Communication is performed over a low-bandwidth system bus. Therefore, the contribution of data transfers in the overall execution times can be significantly large. Hence, effort needs to be made to reduce this overhead. Figure 1.1 shows the effect of optimising data transfer strategies. In this example, a naive data-transfer strategy is shown, where required data is transferred to the GPU before the start of the kernel and all data-elements that are produced in the kernel are transferred back to the host after the kernel has ended. Two optimisations can be identified to reduce the overhead. The first one is the reduction of redundant copy actions by considering multiple kernels together. By applying this step, the copy-in actions for E and F are removed. These arrays are already available on the GPU since they were produced in previous kernels. Allocation and free actions have to be scheduled accordingly to guarantee correct behaviour. The second optimisation is to schedule copy actions asynchronously to the host and GPU. In this way they are overlapped with computations. By carefully scheduling all required copy and allocation actions throughout the code, the transfer and allocation overhead is minimised.

Figure 1.1: Computation (C) and data transfers (T) involved in 3 consecutive matrix multiplications executed on the GPU.

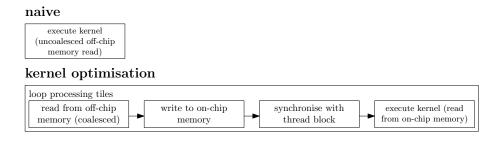

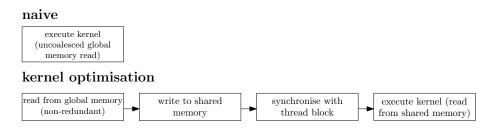

Secondly, a typical GPU has an advanced memory hierarchy of scratchpad memories and caches, each with different performance characteristics. Inefficient utilisation of the GPU's memory hierarchy significantly reduces overall performance. The basis of the GPU memory hierarchy is the GPU's off-chip memory. This explicitly managed memory is the largest memory available on the GPU and can be accessed by all threads on the GPU and by the host. However, accessing the off-chip memory is an expensive operation in terms of latency, therefore available bandwidth should be utilised most efficiently. In order to increase bandwidth utilisation, GPUs group memory operations of multiple threads into larger memory transactions. This technique of grouping is called *coalescing*. However, coalescing is not always possible.

Another way to reduce kernel execution time is to cache data on the on-chip scratchpad memory. The on-chip memory provides significantly better access latencies and communication bandwidths. Though, this memory has a small size (kilobytes) and can only be accessed by a subset of all threads throughout the kernel.

As can be concluded from previous issues, a large burden is placed on the programmer to design a correct and efficient GPGPU accelerated application. Development of GPGPU accelerated programs takes more time than the development of its CPU equivalent. Therefore, the need

arises to develop tools that can aid programmers in solving these issues in order to decrease development time. The ultimate goal is to come to a framework that can automatically generate GPGPU accelerated programs from sequential CPU programs, without any involvement of the programmer.

### 1.2 Contributions

This thesis presents a set of analysis tools that can aid programmers or automatic transformation frameworks to transform a CPU program to a GPGPU accelerated program. The tools provide information to optimise the data-access strategies within GPU kernels and to generate efficient CPU-GPU data-transfer and GPU allocation strategies. The main goal is to optimise GPGPU accelerated programs for execution time.

The tools use the dynamic analysis framework as is provided by Vector Fabrics. Dynamic analysis uses execution traces of the application for input. Where a typical static analysis is unable to infer properties from applications that have a complex program-structure (containing pointer aliasing, pointer modification, indirect addressing, etc.), these properties can be inferred with dynamic analysis. However, the tools can easily be transformed to make use of static analysis.

The main contributions of this thesis are methods to:

- generate efficient copy and allocation strategies in GPGPU accelerated programs (Chapter 4);

- 2. observe linear memory access patterns from program execution traces (Section 5.1);

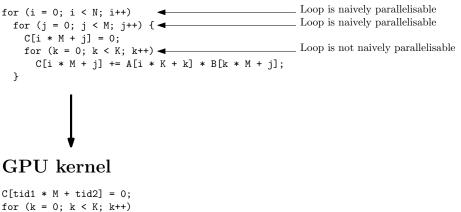

- 3. map loops over the GPU's thread configuration, such that the level of memory coalescing is maximal (Section 5.2.1). Whenever memory operations are still uncoalesced, a code transformation is applied to optimise these operations for coalescing (Section 5.2.2);

- 4. discover reuse of data within thread blocks. This enables a code transformation to cache data on the GPU's on-chip memory (Section 5.3)

While this thesis restricts the programming model to CUDA and OpenACC, the presented tools are applicable to all GPGPU programming models.

#### 1.3 Organisation of thesis

The remainder of this thesis is organised as follows. Chapter 2 gives all required background information on the GPU's hardware and software architecture and the program analysis techniques that are used by our tools. Chapter 3 gives a summary of the related work. The next two chapters elaborate on our contributions. Chapter 4 discusses the generation of efficient copy and allocation strategies. Chapter 5 focusses on optimising the GPU kernel (coalescing and reuse analysis). In Chapter 6 the proposed tools are evaluated for a set of applications. Chapter 7 touches the topic of future work. Finally, Chapter 8 gives a conclusion on the work that is presented in this thesis.

### Chapter 2

## Background

Our research is related to the following two fields: *GPGPU programming* and *program analysis*. In order to understand the issues and solutions that are discussed in the remainder of this thesis, this chapter gives an introduction to each field. Furthermore, this chapter serves as a foundation for the notions needed in later chapters.

Although our research can be applied to every GPGPU platform, we use the NVidia CUDA (Compute Unified Device Architecture) platform [2] in this thesis. The design of other GPGPU platforms is similar. Section 2.1 elaborates on this platform and its corresponding programming model.

In addition to the CUDA platform, the OpenACC programming model [3] is considered in this thesis (Section 2.2). The OpenACC programming model defines a set of compiler directives to indicate loop nests in a CPU program that have to be transformed into GPU kernels by an OpenACC compiler. This compiler is able to transform the indicated loop nests into kernels for a range of accelerators (including CUDA GPUs). OpenACC provides portability over different accelerator platforms and ease-of-programming since the programming model abstracts away from platform dependent details. This comes at the cost of decreased fine-tuning possibilities.

Finally, Section 2.3 addresses the program analysis techniques that are used in this thesis.

### 2.1 CUDA platform

This thesis focusses on the NVidia CUDA (Compute Unified Device Architecture) platform [2]. The CUDA platform breaks down into two layers: the CUDA hardware architecture and the CUDA programming language (as defined by the CUDA programming model). The hardware architecture is discussed in Section 2.1.1. Section 2.1.2 elaborates on the CUDA programming model. Finally, Section 2.1.3 discusses the CUDA execution model.

#### 2.1.1 Hardware architecture

The computational power of CUDA GPUs is formed by an array of computational components called Streaming Multiprocessors (SMs). In each SM, computations are performed by a set of

execution units called symmetric processors (SPs) or CUDA cores. Each CUDA core consists of a fully pipelined integer arithmetic logical unit (ALU) and floating point logical unit (FPU).

For example the NVidia GeForce 640 GT has 2 SMs, each consisting of 192 CUDA cores which amounts to a total of 384 CUDA cores. Thus, the device is capable of sustaining 384 parallel hardware threads.

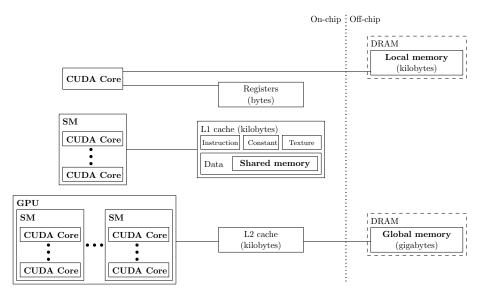

The SMs and CUDA cores communicate and synchronise with each other through an advanced memory hierarchy (Figure 2.1). The hierarchy is composed of registers, per-SM L1 caches, a GPU-common L2 cache and off-chip DRAM memory. The architecture of the memory hierarchy varies over different versions of the CUDA hardware architecture. In the description that follows, we focus on the most recent versions of the architecture, codenamed *Kepler* and *Fermi*.

Figure 2.1: CUDA memory hierarchy

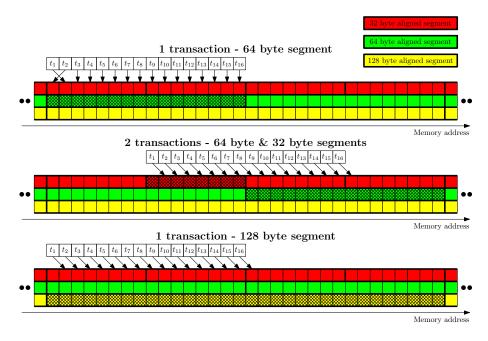

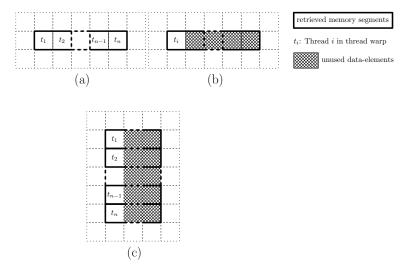

At the base of the memory hierarchy, there is the global memory. This memory has the largest capacity among all memories on the GPU and can be accessed by all CUDA cores and the CPU. It is located on the off-chip DRAM of the GPU, which implies large access latencies. In order to reduce the average access costs, the GPU features an on-chip L2 cache which caches recently used data and instructions. In addition to this cache, a GPU relies on the technique of memory coalescing to optimise the bandwidth utilisation. Groups of threads (organised in warps, Section 2.1.3) execute instructions in a single instruction multiple data (SIMD) fashion. Whenever a warp reads neighbouring data-elements on the global memory, these accesses are grouped (coalesced) into larger aligned memory transactions by the memory access unit of the SM. Figure 2.2 shows the coalescing capabilities in different situations.

Each SM has four types of caches: instruction, data, constant and texture cache. All four caches together form the L1-cache of the GPU. In this thesis, we focuss on the data cache. The data cache is configured in two parts. The first part is used for implicit caching of data by hardware <sup>1</sup>. The other part of this cache is called *shared memory*. The shared memory is explicitly managed by software.

<sup>&</sup>lt;sup>1</sup>NVidia GPUs with older architectures then Kepler or Fermi do not have this hardware managed data cache.

Figure 2.2: Memory accesses within a warp are grouped into memory transactions of 32, 64 or 128 byte aligned memory segments. In this example, warps consist of 16 neighbouring threads.

Access latencies to the L1 cache are significantly lower compared to global memory accesses. In order to decrease average access latencies, the L1 cache is organised in banks. Accesses to addresses that fall into different banks are served simultaneously. However, if the accesses are within the same bank, a *bank conflict* occurs and the accesses are serialised.

Each SM has a set of registers that are shared among all CUDA cores. If all registers are occupied, data is spilled to the off-chip local memory that is located on the DRAM of the GPU.

#### 2.1.2 CUDA programming model

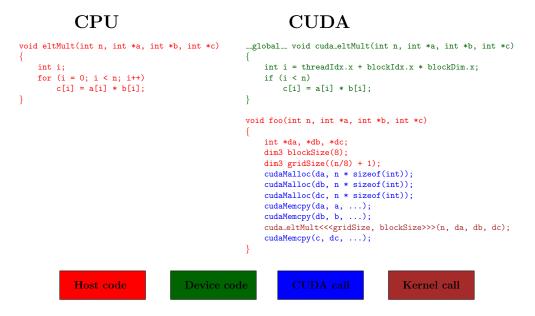

The CUDA programming model is a heterogeneous programming model that hides the complexity of the GPU hardware architecture from the programmer. This is achieved through a set of abstractions concerning the organisation of threads, the memory hierarchy and synchronisation primitives. The CUDA programming language is implemented in the C language (ANSI C99 standard). Figure 2.3 emphasises important concepts of the CUDA programming model by giving the native C implementation of an array-multiplication function and its CUDA equivalent kernel.

A CUDA program is composed of a *host part* (executed by the CPU) and a *GPU part* (executed by the GPU). The GPU part is composed of a set of computational units (kernels) which are invoked by the host.

The host specifies the thread configuration for each invocation of a GPU kernel, stating the number of GPU threads that are launched. The main idea of GPGPU programming is to divide the work over a large number of threads, preferably more as the number of available CUDA cores. In this way CUDA cores can always be occupied and memory access latencies are hidden with computations. Kernels are launched asynchronously to the host.

Figure 2.3: CUDA code example

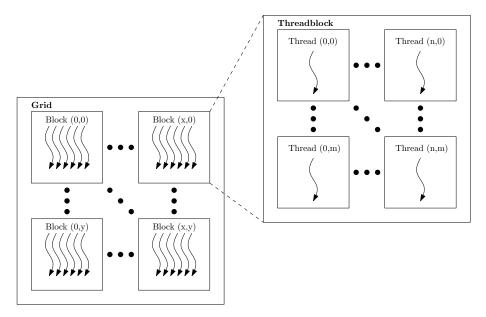

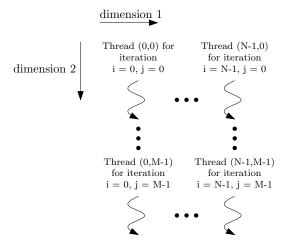

Threads are organised in a grid of *thread blocks* (groups of threads). The grid of thread blocks and the individual thread blocks can have up to three dimensions. Threads are identified by means of its corresponding thread block identifier and thread identifier within the thread block. With this information a programmer can coordinate the work that is done by individual threads. Figure 2.4 gives an example of the CUDA thread configuration.

Figure 2.4: Example CUDA thread configuration. This thread configuration consists of a twodimensional grid with two-dimensional thread blocks.

The programming model assumes that both the host and the GPU have their own separate memory spaces, and the host part manages the GPU memory through calls to the CUDA runtime. Copy

actions between the CPU and GPU can either be executed synchronously or asynchronously to the host. For a synchronous copy action, the CUDA runtime returns the call after the copy action has been completed. For a asynchronous copy action, the CUDA runtime returns the call directly after the copy action has been started.

In the CUDA programming model, host memory can be allocated in two ways: *pageable* and *pinned*. By default, host memory is allocated as pageable memory. Pageable memory can be swapped out from the CPU's DRAM memory to the hard drive to facilitate infinite address spaces on limited sized memory. When memory is allocated in a pinned fashion, the allocated memory segment always resides in the CPU's RAM memory. The GPU fetches pinned memory through direct memory access (DMA) which implies higher CPU-GPU communication bandwidths, compared to pageable memory. Pageable memory cannot be fetched through DMA. Furthermore, pinned memory facilitates asynchronous communication. Allocating pinned memory takes significantly more time compared to allocating pageable memory. By experiments, we found that allocating 100 megabyte of pinned CPU memory takes more then 100 ms of time. Allocating pageable memory takes less then 5 ms. In this report we use pageable memory by default, unless pinned memory is required for asynchronous data transfers.

Copy actions or kernel launches can be divided over multiple *streams*. A stream is a sequence of operations that are executed on the GPU in-order. Streams may be executed concurrently.

To make sure that asynchronous actions of the CUDA runtime have been finished at certain points in the host code, synchronisation barriers can be called.

In the GPU kernel, threads within a thread block can be synchronised by using barrier synchronisations at indicated moments in the kernel's code. Barrier synchronisation between thread blocks can not be performed, due to the freedom of the CUDA execution model to schedule thread blocks freely over the SMs (Section 2.1.3).

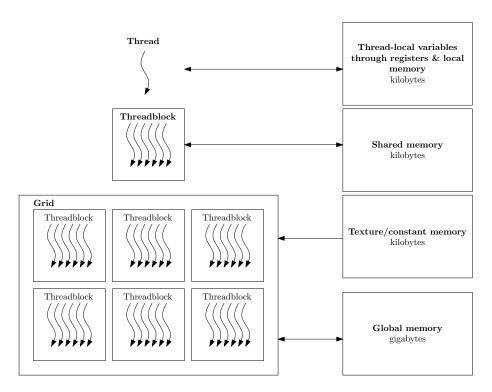

As discussed in Section 2.1.1, a GPU has a heterogeneous memory hierarchy. Figure 2.5 shows the range of memories that is available through software. Data that is stored in the texture/constant and global memory persists across multiple kernel invocations. Other memories are not persistent.

#### 2.1.3 CUDA execution model

Upon the host invoking a GPU kernel, all thread blocks are distributed over the SMs with available compute capacity by the GPU's scheduling unit. On the SMs, the thread blocks are split into groups of threads which are called *warps*. A warp is a group of consecutive threads in the X-dimension of the thread block. The size of a warp is fixed by the GPU's architecture. Warps are in one of the following three states: *ready, active, waiting-for-memory*. Warps in the ready-state are ready to execute a set of instructions. The SM's warp scheduler assigns a warp to a group of available CUDA cores. The warp becomes active. The CUDA cores execute instructions in a Single Instruction Multiple Data (SIMD) fashion. When memory is being accessed, execution of the warp is blocked and the warp is in the waiting-for-memory state. When data is available, the warp will go to the ready state again to execute new instructions.

Threads occupy registers and memory space. Since a SM is equipped with limited memory and registers, there is a maximum on the number of warps that is scheduled simultaneously on a SM. The ratio of active warps to the maximum number of warps that is supported by the warp

Figure 2.5: Threads to memory mapping

scheduler is called the *occupancy factor*. When the occupancy factor decreases, the number of active warps decrease and the kernel's execution time increases.

### 2.2 OpenACC programming model

As discussed in Section 2.1.2, GPU programming models expose GPU specific concepts to the programmer (advanced memory hierarchy, the concept of thread blocks and synchronisation primitives). Therefore, generating GPGPU accelerated programs is a time consuming task for programmers who are no expert in the domain of GPU programming. Furthermore, every GPU programming model has its own architecture specific artefacts. Hence, porting code from one programming model to the other is non-trivial.

In order to abstract these issues away, the OpenACC programming model [3] is developed by CAPS, CRAY, PGI and NVidia. The OpenACC programming model consists of a set of compiler directives. With these directives, programmers can annotate loop nests in a CPU program. These loop nests are transformed into GPU kernels by an OpenACC compiler. Listing 2.1 shows an example of an OpenACC annotated program.

If an annotated loop nest can be parallelised, the OpenACC compiler generates the GPU kernels and the control code fragments that are executed by the host. Furthermore, the compiler schedules copy and allocation actions for the data-structures that are used in the GPU kernel and searches for an optimal thread configuration.

The majority of OpenACC compilers performs static analysis (Section 2.3.1) of the program

during compilation. These compilers have limitations in the code constructions that can be analysed (Section 2.3.1). A typical OpenACC compiler is unable to handle pointer arithmetic; therefore compilation fails. The compiler cannot determine upfront the value of pointers. Different pointers may map to the same data-structure, therefore imposing dependencies (Section 2.3.4) that limit parallelism in the GPU kernel. In order to succeed, programmers have to add extra directives to aid the compiler in solving these issues. For example, a programmer can add the independent directive to annotated loops to ensure an OpenACC compiler that a loop nest contains no obstructing dependencies and can therefore safely be parallelised.

By default, copy actions and kernel launches are performed synchronously with the host. However, a programmer can add directives to launch kernels and copy-actions asynchronously. Synchronisation barriers can be inserted to synchronise GPU activities with the host.

The programmer can insert directives to optimise or correct the implicit data-management strategy chosen by the compiler. By adding directives like create, copy, copy-in and copy-out, he is able to control the moment where data-structures should be copied or allocated, together with the exact size of the data-structures.

Listing 2.1: OpenACC example

```

1 void eltMult(int n, int *a, int *b, int *c)

2 {

3     int i;

4     #pragma acc kernels loop independent

5     for (i = 0; i < n; i++)

6        c[i] = a[i] * b[i]

7  }</pre>

```

One of the main benefits of the OpenACC programming model is the abstraction from GPU specific parameters like thread configurations and the GPU's advanced memory hierarchy; the responsibility for these low-level GPU programming issues is delegated to the compiler. This decreases development time at the cost of less optimisation possibilities. Another benefit is portability over different accelerator platforms. Currently, OpenACC compilers are capable to translate OpenACC annotated programs into CUDA and OpenCL [4] compatible kernels or multithreaded CPU code if no GPU is available. This makes the programming model suitable for a wide range of accelerators.

Currently, CAPS, CRAY and PGI have commercially available OpenACC compilers. In this thesis, the OpenACC compiler of PGI is used.

#### 2.3 Program analysis

Program analysis is the process of inferring properties by analysing the behaviour of a computer program. Examples of properties that can be inferred are accessed address ranges of a memory operation, data dependencies or the life-span of variables. Applications that rely on program analysis techniques are for example compilers (using program analysis for code improvement) and software validation frameworks (using program analysis for error detection). Two main approaches for program analysis can be distinguished: static analysis and dynamic analysis. The framework that is designed in this thesis uses dynamic analysis to infer properties of a program. However, the tools can easily be transformed to make use of static analysis.

The remainder of this section is organised as follows. In Section 2.3.1, we touches the topic of static analysis techniques. Section 2.3.2 focusses on dynamic analysis techniques and describes the analysis framework of Vector Fabrics that is used as a basis for our tools. Section 2.3.3 discusses the *extended call graph*. An extended call graph gives a representation of a program's execution flow and is used throughout this thesis. Finally, in Section 2.3.4 we discuss the topic of dependency analysis.

#### 2.3.1 Static program analysis

With static analysis, properties are inferred by analysing the source (either source code or object code) of a program, with formal methods like data flow analysis [5] and the polyhedral model [6]. The properties that are inferred by static analysis are sound [5]. That is, the properties can always be proven correct, regardless of the program's input.

However, static analysis may fail on complex programs. For example, it is hard to infer data dependencies statically if the code uses indirect addressing, pointers recursion and indirect function calls. This is in line with Rice's theorem [7] which states that only trivial properties of programs are algorithmically computable.

#### 2.3.2 Dynamic program analysis

Dynamic analysis uses execution traces for analysis. By observing these traces, dynamic analysis can solve issues like indirect addressing, pointer recursion and indirect function calls, since the analysis has knowledge about the actual program's execution flow. These issues are hard to solve by static analysis approaches.

The properties as inferred by dynamic analysis may not be sound. The set of observed execution traces is a subset of all program flows that are possible. Therefore, the inferred properties may not hold for those cases that are not observed during analysis. However, it is programmers best practice to have a large set of test cases that cover all practical situations.

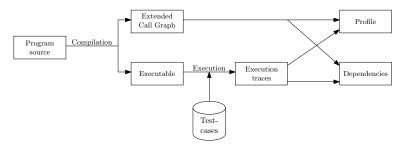

**Base-line analysis** The tools that are proposed in this thesis are using dynamic analysis. The base-line framework for this analysis is implemented by Vector Fabrics and is schematically shown in Figure 2.6. The analysis framework takes a program's source code as an input. The source

Figure 2.6: Base-line analysis framework

code is compiled to an executable. As a side effect of this, the extended call graph (ECG) (Section

2.3.3) is created, representing the execution flow throughout the program. The ECG is lacking information about issues like the number of iterations that are executed for each loop or the number of times a branch is taken. To retrieve this information, the program is executed for a set of test cases. Based on the observed execution traces and the ECG, the base-line analysis framework generates a profile that contains execution specific information for each operation or code fragment that is represented by a node in the ECG.

The base-line analysis framework uses the ECG and execution traces to detect data dependencies (Section 2.3.4) that impose constraints on the execution order of operations.

#### 2.3.3 Extended call graph

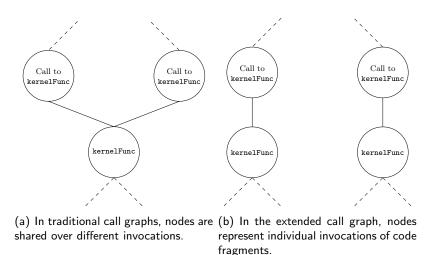

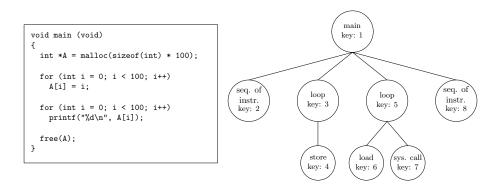

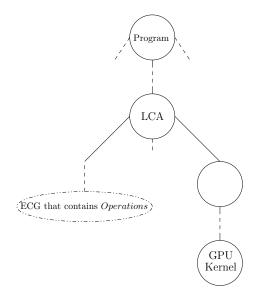

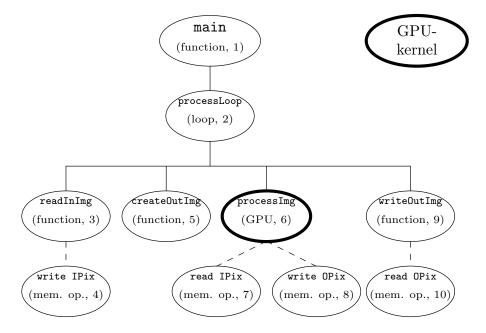

An extended call graph (ECG) is a tree-like structure that represents the execution flow throughout the program. Each node in the graph represents a function, a sequence of instructions, a loop, a call, a load or a store operation. This graph is an unfolded version of a call graph [8] extended with extra information like the number of invocations and executed iterations. In traditional call graphs, different invocations of the same code fragment map to the same node in the call graph (Figure 2.7(a)). In the extended call graph, different invocations are mapped to different nodes (Figure 2.7(b)). Each statement in the original source code maps to a set of nodes in the ECG. Each node in the ECG maps to a set of statements in the source code. As an example, Figure 2.8 shows the resulting ECG for a given input program.

Figure 2.7: A extended call graph is an unfolded version of a traditional call graph

Each node is indicated by a key. With this key the position of two nodes within the ECG can be compared. Based on this key, information about the order, in which nodes are executed, is found. When the key of a node X is smaller than the key of a node Y, it means that the code fragment of node X is invoked earlier in the program than the code fragment of node Y.

Figure 2.8: resulting ECG for input program

#### 2.3.4 Data dependency analysis

Data dependency analysis is the technique of finding data dependencies in a program. Data dependencies impose constraints on the execution order of instructions. In this thesis we use data dependencies to reveal the data flow throughout the program. A data dependency is defined by a group of source operations S and a group of destination operations D. All operations in S are invoked before the operations in D. Both groups of operations are related to each other since they operate on the same registers or memory locations. Table 2.3.4 shows the three types of data dependencies together with the function of the source S and destination D nodes.

| Table 2.1. Types of data dependencies |       |       |  |  |  |

|---------------------------------------|-------|-------|--|--|--|

| Data-dependency                       | S     | D     |  |  |  |

| Write-after-write                     | Write | Write |  |  |  |

| Write-after-read                      | Read  | Write |  |  |  |

| Read-after-write                      | Write | Read  |  |  |  |

Table 2.1: Types of data dependencies

The tools of Vector Fabrics are able to observe these three kinds of data-dependencies. However, only the read-after-write data dependencies are relevant within the scope of this thesis, since these dependencies reveal data flow throughout the program.

A read-after-write data dependency d is defined by a set of operations  $P_d$  that produces the related value and the operations  $C_d$  that consume the value after  $C_d$  is finished (2.1). All operations in  $P_d$  and  $C_d$  relate to different nodes in the ECG.

$$d = P_d \times C_d \tag{2.1}$$

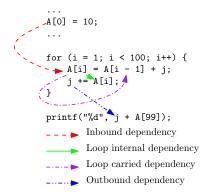

Figure 2.9 shows the four types of read-after-write dependencies that can be identified in relation to a code fragment.

- Inbound dependencies Data is produced by  $P_d$  before the code fragment and is consumed by  $C_d$  inside the code fragment.

- **Outbound dependencies** Data is produced by  $P_d$  inside the code fragment and is consumed by  $C_d$  after the code fragment finished.

- Internal dependencies Data is produced and consumed within the same iteration of the code fragment.

- Loop-carried dependencies This type of dependencies can only occur in loops. Data is produced and consumed in different iterations of the loop. Hence, data needs to be carried over to later iterations of the loop.

Figure 2.9: Different types of data dependencies

The dependencies carry information on the data-structures and the data-elements that are involved.

# TU/e Vector Fabrics

### Chapter 3

### **Related work**

The idea of designing tools to aid programmers or automatic frameworks in the generation process of GPGPU accelerated programs is not new. Work has been done on both the generation of efficient data-transfer and allocation strategies and optimising GPU kernels. However, the majority of related work uses a static analysis approach, due to the soundness properties. The analysis capabilities of these approaches are more limited compared to dynamic approaches (that are used in this thesis). Code fragments that use indirect addressing, pointer aliasing or pointer arithmetic are difficult to analyse. Parts of the proposed techniques can also be applied in a dynamic analysis context.

We present the related work in two parts: In the first part we focus on the work that is related to the generation of efficient data-transfer and allocation strategies. In the second part we present the work that is related to optimising GPU kernels. This is a broad field of research. We only discuss work that proposes techniques for coalescing analysis and data caching on on-chip memory.

**Data transfer and allocation strategies** To the best of our knowledge, this is the first work that uses a fully dynamic analysis approach for the generation of data transfer strategies between a host and an accelerator.

Custers et al. [9] propose a framework to classify loop nests for parallelisation opportunities. Classification is based on matching code fragments to predefined patterns. The classification framework observes the set of data-structures that needs to be transferred between the host and the accelerator in order to execute the application correctly. This information is used to construct *memory-regions*. A memory-region for a data transfer action t is defined by a pair of points in the source code  $pos_{start} \times pos_{end}$  between which t is to be executed. At  $pos_{start}$  the transfer action can be started asynchronously to the host. At  $pos_{end}$  the data transfer should be finished. A set of optimisations is proposed to position the memory regions such that the data transfer overhead is minimised. The performance of the framework of Custers in generating data transfer and allocation strategies is limited by the number of patterns that are supported by the framework, for classification. Whenever a loop nest cannot be classified for parallelisation by the framework, the memory regions cannot be generated. Hence, no data transfer strategy is generated. Our framework depends on information that is extracted from observing dependencies and is therefore decoupled from the parallelisation classification.

Amini et al. [10] propose a compiler step to generate an efficient data transfer strategy. The control and data flow graph of the application is used for analysis. The tool of Amini uses two simple heuristics in scheduling transfer actions: schedule transfer actions to the GPU as early as possible and schedule transfer actions back to the host as late as possible. Redundant communications due to data reuse between kernel executions are avoided. Allocation and free actions of the corresponding data-structures are managed by a run-time library that uses the global memory as a cache memory. Data-structures are preserved on the GPU as long as there is enough memory on the GPU. When a kernel execution requires more memory than is available, the run-time library frees memory ranges that are the least recently used. The compiler step of Amini is unable to deal with issues like indirect addressing and pointer aliasing since static analysis is used. Since we use dynamic analysis for our tools, we can solve these issues.

Jablin et al. [11, 12] introduce a CPU-GPU communication framework that uses a combination of static and dynamic analysis to generate a data transfer and allocation strategy. The framework consists of two parts, a run-time library and an optimising compiler. The compiler schedules copy and allocation actions efficiently throughout the program in the same way as is done by Amini. Data transfers to the GPU are scheduled early in the program and retrieving it only when necessary. However, questions that are difficult to answer (like the size and shape of copied data-structures) are postponed to the runtime library. The runtime library tracks GPU memory allocations and transfers data between the CPU memory and GPU memory. By dividing responsibilities over a compiler step and a runtime library, CPU-GPU communication does not need to depend on the strength of static compile-time analysis or on programmer-supplied annotation. Compared to Amini et al., more complex code structures can be analysed. However, this comes at the cost of extra overhead due to the runtime library. Our work can solve the issues that cannot be solved by the compiler of Jablin. Therefore, there is no need for adding runtime libraries.

**Optimising the GPU kernel** In literature, a wide set of GPU kernel optimisations is proposed. Mostly they are implemented as compiler steps that use static analysis. In what follows next, research is highlighted that is related to the work as presented in this thesis: coalescing analysis (contribution 3 of Section 1.2) and caching on on-chip memories (contribution 4 of Section 1.2).

Yang et al. [13] propose a set of optimisations to improve the performance of naive GPU kernel implementations. One of these optimisations is to use buffers in the shared memory to allow threads to read from global memory in a coalesced way. In order to use this optimisation, access patterns of the read operations are reconstructed by using static analysis. The analysis of Yang is unable to deal with indirect addressing. Whenever array indices (e.g. x in a[x]) are loaded from memory, the analysis for optimisation is skipped. The static analysis cannot calculate the value of these indices. Our tools reconstruct access patterns by observing execution traces and can therefore reconstruct access patterns where indirect addressing is used.

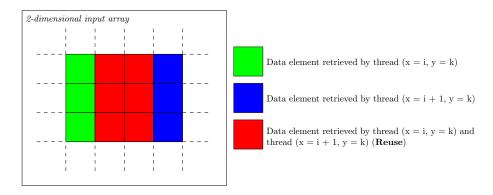

Baskaran et al. [6] present a framework to efficiently map data segments over an advanced memory hierarchy of DRAM memory and scratchpad memories. By caching data on high bandwidth and low latency scratchpad memories, performance increases. The polyhedral model is used for analysis. Baskaran focusses in his work on the GPU's memory hierarchy. More specifically, opportunities are explored to use the GPU's on-chip scratchpad memory. Baskaran states that since processing units can use both the GPU's off-chip and on-chip scratchpad memory throughout the program, mapping data to the scratchpad memory is only beneficial when there is sufficient reuse between

threads in a thread block. In order to determine the level of reuse for a data-structure, overlap is determined in the range of data-elements that is accessed by neighbouring threads. To obtain this information the shapes of the accessed data-structures should be known. However, with dynamic analysis these shapes cannot be observed. Dynamic analysis can only observe accesses in a linear address space. Only by using symbol information (as can be extracted with static analysis), shapes with a higher dimensionality can be reconstructed.

Within Vector Fabrics, a series of projects were done on the topic of GPGPU programming. The following project relates to the kernel optimisations that are proposed in this thesis.

Juravle et al. [14] propose a set of analysis tools that enable automatic and guided transformation of sequential programs to GPU kernels. Part of this is a tool to explore kernel optimisations (coalesced memory access and shared memory exploration). The toolset checks for coalescing behaviour of a GPU kernel based on expression reconstruction analysis. Juravle states that a memory read operation is only coalesced when its corresponding access function has the property of monotonicity. However, monotonicity cannot be determined for every symbolic expression due to the static analysis techniques. Based on the coalescing analysis, a thread configuration is generated that maximises the coalescing capabilities. Furthermore, Juravle also presents a tool to check for reuse of data between threads in a thread block by using static symbol range analysis. The tools of Juravle use static analysis and do therefore not fit into the dynamic analysis framework of Vector Fabrics.

# TU/e Vector Fabrics

### Chapter 4

### **GPU** data-transfer and allocation

This chapter proposes a tool to generate efficient data-transfer and allocation strategies in GPGPU programming. By considering memory dependencies (as generated by the dynamic analysis of Vector Fabrics), the tool schedules a minimal set copy and allocation actions in a GPGPU program; i.e. the amount of transferred data and allocation overhead is minimised.

As stated in Chapter 2, the memory space of a GPU is logically separated from the CPU's memory space. OpenACC compilers can schedule transfer and allocation actions automatically. However, this is only successful for simple programs. The static analysis fails, if pointer arithmetic is involved. For example, the OpenACC compiler of PGI cannot parallelise a matrix multiplication function (matrixMult(A, B, C)) into a GPU kernel when A, B and C are pointers to dynamically allocated data-structures. The compiler can not calculate the addresses of pointers A, B and C. A, B and C may point to the same data-structure, and can therefore impose dependencies that obstruct parallelisation. A programmer must help the compiler by adding extra compiler directives. In the example of the matrix multiplication kernel, the programmer indicates that A, B and C do not point to the same data-structures. In the CUDA programming model, all transfer actions have to be scheduled by the programmer. For both programming models, manually generating a correct data transfer and allocation strategy takes time, especially when sequential programs need to be ported to GPU kernels. Data-flow patterns, as generated by other programmers may be complex. Understanding these patterns is a time-consuming task.

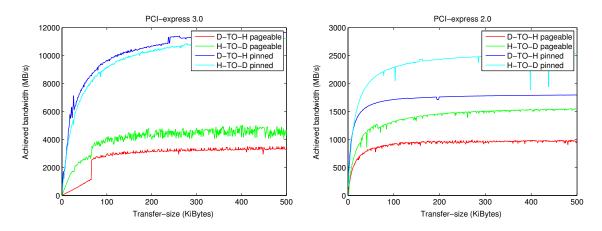

Besides the logical separation of memory hierarchies, the memory hierarchy of a typical GPU is also physically separated from the host. Data-transfers between the CPU's RAM memory and the GPU are executed over a system bus that has relatively low bandwidth compared to the GPU's computational power. Figure 4.7 shows the achieved bandwidths of the PCI-express 2.0 and PCI-express 3.0 system busses of the systems we use for evaluation (Chapter 6). The PCI-express 3.0 bus achieves a maximal bandwidth of 11 GB/s for pinned memory and 5 GB/s for pageable memory. The results for a PCI-express 2.0 bus are worse (2.5 GB/s for pinned memory and 1.5 GB/s for pageable memory). Bandwidth decreases dramatically when smaller data-segments are transferred. The low bandwidth of the system bus can annihilate all gain obtained by using a GPU for computations.

Because of the large costs of transferring data between the CPU and GPU, the amount of bytes that is transferred between CPU and GPU should be minimised. A typical OpenACC compiler

Figure 4.1: Achieved bandwidth in CPU-GPU communication. H-to-D: Data-transfers from the host (CPU) to the device (GPU). D-to-H: Data-transfers from the device (GPU) to the host (CPU).

will always schedule data transfers around the kernel's boundaries. This is a naive approach that causes significant overhead. Data-structures may be transferred between the CPU and GPU redundantly (as was seen in Figure 1.1). The data transfer strategy can be optimised by adding compiler directives throughout the code to modify the position of transfer and allocation actions. Finding the optimal position for data transfer and allocation actions is a time consuming process for programmers in both the CUDA and OpenACC programming model.

Besides optimising the position of transfer actions, memory transfers can be performed asynchronous to the CPU and GPU to hide them with computations. This is possible since GPUs are equipped with Direct Memory Access controllers to directly access the memory spaces of the GPU and the CPU, without intervention of the CPU. To enforce correct behaviour a programmer needs to insert synchronisation barriers, to ensure data-transfers have completed at certain moments.

This chapter describes a tool to generate optimised data-transfer strategies. In order to generate a transfer and allocation strategy the framework performs the following three steps:

- 1 Find all variables that should be transferred, allocated and freed on the GPU for each individual kernel function (Section 4.1)

- 2 Reduce the number of redundant copy, allocation and free actions by considering all GPU kernels together (Section 4.2)

- 3 Schedule data-transfer, allocation and synchronisation actions throughout the code (Section 4.3)

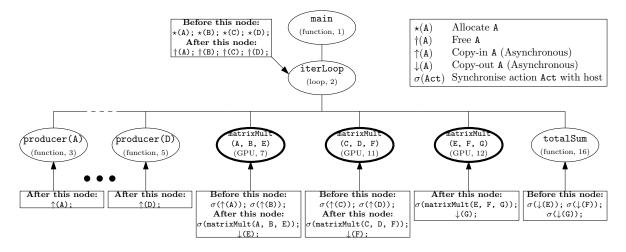

As a running example through this chapter we use the program as is shown in Listing 4.1. It is an extended version of the matrix multiplication application that is shown in Figure 1.1. In the application a series of calculations are performed in a loop. During each iteration of the loop, matrices A, B, C and D are filled with random floating point numbers. Matrix-multiplication is applied to matrices A, B and C, D. The results are stored in E and F. Matrices E and F are again multiplied and the results are stored in G. As a final step matrices E, F and G are consumed in a CPU function (totalSum). Each invocation of the matrix multiplication function is transformed in a

separate GPU kernel. Listing A.1 shows a naive data-transfer strategy as is generated by a typical OpenACC compiler. All required data-structures are copied in to the GPU before a kernel starts and all data-structures that are used after the kernel execution are transferred back to the CPU after the kernel ends. In this strategy redundant copy actions are produced. An example is the copy-in action for matrices E (line 39) and F (line 40) before matrix\_mult(E, F, G). Listing A.2 shows the data-transfer and allocation strategy as is generated by our framework. The redundant copy-in actions for matrices E and F are removed. All remaining copy actions are scheduled at an optimal (i.e. the number of transferred bytes is minimal) position and executed asynchronously to overlap with computations. The allocation and free actions of the corresponding data structures are scheduled outside the loop. The chapter shows how the optimal strategy is generated step by step.

| Listing 4.1: | Input | program |

|--------------|-------|---------|

|--------------|-------|---------|

```

void main(void)

1

2

{

3

for (i = 0; i < N; i++) {

4

5

randomize_array(A);

randomize_array(B);

6

randomize_array(C);

7

randomize_array(D);

8

matrix_mult(A, B, E);

9

10

matrix_mult(C, D, F);

matrix_mult(E, F, G);

11

total_sum(E, F, G);

12

13

}

14

15

}

```

#### 4.1 Individual kernels

In the first step (of the three steps) in generating an efficient data transfer and allocation strategy, all information is gathered on the set of data-structures that is used in each individual GPU kernel. More specifically, this step gathers all information to generate the allocation and data-transfers actions that are required for an individual kernel in order to be executed correctly.

The tool retrieves the set of read-after-write dependencies  $D_k$  that is related to a kernel k. These dependencies describe the flow of data in relation to k. As explained in Section 2.3.4, three types of dependencies can be related to a kernel: inbound, outbound and internal dependencies. For every dependency d, symbol information can be retrieved, to retrieve the data-structure x that is involved in a dependency.

All dependencies in  $D_k$  are grouped in the set of inbound  $(D_{inbound,k,x})$ , outbound  $(D_{outbound,k,x})$ and kernel internal  $(D_{internal,k,x})$  dependencies for every data-structure x. These groups of dependencies contain all information to generate all transfer and allocation actions that need to be executed for k.

This step generates a initial set of *kernel actions* for every kernel k. A kernel action is a datatransfer or allocation action that needs to be done in relation to k. A kernel action is represented by a set of dependencies that causes this action to be scheduled.

The tool generates four types of actions for a data-structure x in a kernel k.

- Copy-in For data-elements that are produced before an invocation of kernel k and are used inside k, a copy-in action (a<sub>copy-in,k,x</sub>) is generated to transfer these data-elements from the CPU to the GPU. This copy-in action is described by the set of inbound dependencies (4.1).

- **Copy-out** For data-elements that are produced inside k and are used afterwards, a copy-out action  $(a_{copy-out,k,x})$  is generated to transfer these data-elements from the GPU to the CPU. This copy-out action is described by the set of outbound dependencies (4.2).

- Allocation & Free Data-elements that are somehow used inside k, since they are either consumed or produced, should be allocated (*a<sub>allocation,k,x</sub>*) before the kernel and freed (*a<sub>free,k,x</sub>*) after the kernel. The data-elements that are used in the kernel are reflected by the inbound, outbound or internal memory dependencies (4.3) (4.4).

$$a_{copy-in,k,x} = D_{inbound,k,x} \tag{4.1}$$

$$a_{copy-out,k,x} = D_{outbound,k,x} \tag{4.2}$$

$$a_{allocation,k,x} = D_{inbound,k,x} \cup D_{outbound,k,x} \cup D_{internal,k,x}$$

$$(4.3)$$

$$a_{free,k,x} = D_{inbound,k,x} \cup D_{outbound,k,x} \cup D_{internal,k,x}$$

$$(4.4)$$

The kernel actions for data-structures  $x_1, \ldots, x_n$  that are used inside kernel k are grouped according to the 4-tuple as shown in (4.5). All 4-tuples that are generated for the individual GPU kernel are taken to the next step.

$$A_{k} = \{a_{copy-in,k,x_{1}}, \dots, a_{copy-in,k,x_{n}}\} \times \{a_{copy-out,k,x_{1}}, \dots, a_{copy-out,k,x_{n}}\} \times \{a_{allocation,k,x_{1}}, \dots, a_{allocation,k,x_{n}}\} \times \{a_{free,k,x_{1}}, \dots, a_{free,k,x_{n}}\}$$

$$(4.5)$$

Table A.1 shows the actions that are generated for the example program.

#### 4.2 Intra-kernel optimisations

The resulting 4-tuples as generated by the previous step (Section 4.1) consider GPU kernels separately. However, when this set of kernel actions (as represented by the set of corresponding dependencies) are scheduled around each kernel, this may result in redundant data-transfers.

The optimisation step that is explained in this section reduces the number of redundant kernel actions when multiple kernels exist in the input program. In the naive transfer and allocation strategy which is shown in Listing A.1, the copy-in actions of matrices E and F (lines 38 & 39)

are redundant since the data is not modified by the host between the producing GPU kernels (lines 16 & 29) and the consuming GPU kernel (matrix\_mult\_kernel(E, F, G) on line 40). Furthermore, matrices E and F are allocated and freed multiple times (lines 13, 20, 25, 29, 35, 36, 37, 42, 43, 44) for each iteration of the surrounding loop (lines 4-49).

**Copy-in & Copy-out** In order to reduce the number of copy-in actions, each non-empty  $a_{copy-in,k,x}$  is considered for kernel k and data-structure x. Each dependency  $d \in a_{copy-in,k,x}$  is examined in the following way. When the complete set of producing operations  $P_d$  for d is located inside GPU kernels, this means that all data-elements that are related to this dependency are produced by GPU kernels. Hence, the related data-elements already reside on the GPU's memory. Therefore d can be removed from  $a_{copy-in,k,x}$  in the further process of generating a transfer and allocation strategy.

In the case of copy-out actions, the consumer operations  $C_d$  of each related outbound memory dependency  $d \in a_{copy-out,k,x}$  are considered. When all instructions in  $C_d$  are located inside GPU kernels, this means that all data-elements that are related to the copy-out action are never consumed by the CPU. d is left out from  $a_{copy-out,k,x}$ .

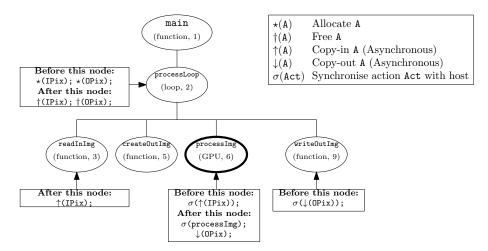

In the running example, the copy-in actions of matrices E and F (lines 38 and 39 in Listing A.1) are removed. The tool observes that all inbound data-dependencies for matrix\_mult(E, F, G), related to E and F, have all producing instructions in the GPU kernels. Therefore these dependencies are removed from further analysis. This situation is depicted in Figure 4.2.

Figure 4.2: copy\_in\_GPU(E) and copy\_in\_GPU(F) are removed

Allocate & Free In order to reduce the number of allocation actions for data-structure x, all non-empty actions  $a_{allocation,k_1,x}, \ldots, a_{allocation,k_m,x}$  are considered for all GPU kernels  $k_1, \ldots, k_m$ . All dependencies that are related to these allocation actions are transferred to  $a_{allocation,k_i,x}$ , where kernel  $k_i$  is the first kernel in the program that uses data-structure x. The first kernel has the lowest key in the extended call graph, and will therefore be invoked first.  $k_i$  is the first moment in the program where data-structure x should be allocated. All dependencies are transferred to  $a_{allocation,k_i,x}$ , to ensure that all data-elements of x that are used in at least one of the GPU kernels are allocated at once.

A same approach holds for free actions. In this case all non-empty actions  $a_{free,k_1,x}, \ldots, a_{free,k_m,x}$  are considered for all GPU kernels  $k_1, \ldots, k_m$ . All dependencies that are related to these free actions are transferred to  $a_{free,k_i,x}$ , where kernel  $k_i$  is the last kernel in the program that uses data-structure x. After this kernel is invoked for the last time, x can be freed from the GPU.

In the running example, the tool observes that matrices E and F are used across multiple GPU kernels. Therefore, the number of required allocation and free actions for these matrices can be reduced. It is even required since redundant copy-in actions (copy\_in\_GPU(E, N \* size) and copy\_in\_GPU(F, N \* size)) are removed. These matrices are required to be resident on the GPU's global memory. Therefore, the allocation actions for matrices E and F before kernel matrix\_mult\_GPU(E, F, G), the free action for matrix E after matrix\_mult\_GPU(A, B, E) and the free action for matrix F after matrix\_mult\_GPU(E, F, G) are removed. This situation is depicted in Figure 4.3.

Figure 4.3: allocate\_GPU(E), allocate\_GPU(F), free\_GPU(E), free\_GPU(F) are removed

Table A.2 shows the modified actions that result from the second step to generate efficient copy and allocation strategies.

#### 4.3 Location of copy, allocation and synchronisation actions

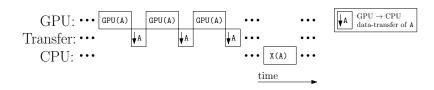

In the final step of the generation process of efficient data transfer and allocation strategies, each kernel action is scheduled in the program code. The actions are scheduled such that the number of redundant data-transfer and allocation actions is minimised. Consider for example the situation of Listing 4.2 where a GPU kernel is nested in a loop that is executed on the host. Scheduling the copy-out action for A (that is produced by the GPU kernel GPU(A) and consumed by X(A)) directly after line 3 (inside the loop) results in redundant invocations of this action (Figure 4.4).

Listing 4.2: GPU kernel GPU(A) is nested in a loop. A is produced by GPU(A) and is consumed by function X(A)

```

for (i = 0; i < N; i++) {

GPU(A);

}

...

X(A);

...</pre>

```

1

2

3 4

> 5 6 7

8

To reduce the transfer overhead even further, memory transfers are launched asynchronously to the host code and the GPU kernels. In this way data-transfers can overlap with computations. Synchronisation barriers have to be scheduled throughout the program to guarantee that copy actions have ended at a certain point in the code. An example situation is shown in Figure 4.5.

Figure 4.4: Scheduling the copy out action of A right after GPU(A) results in redundant invocations.

Figure 4.5: The copy-out action for A  $(\downarrow A)$  is performed asynchronous to computations on the GPU and host. A synchronisation barrier is inserted  $(sync(\downarrow A))$  to ensure that  $\downarrow A$  has finished before the first consumption on the host in X(A).

To schedule all kernel actions as generated by the previous step, we propose Algorithm 1. The algorithm schedules a kernel action a in the program in relation to kernel k. A kernel action is represented by a set of related dependencies. The next paragraphs explain this algorithm in more detail. In the final paragraph we focus on the size of the copy and allocation actions.

**Get the boundary operations (line 1)** In the first step of the algorithm, the *boundary operations* are retrieved in the analysed program. Boundary operations, together with the GPU kernel, define a window in the extended call graph where action *a* has to take place. The calculated window depends on the context of the action (copy-in, copy-out, allocation or free).

- Copy-in (line 2) The function GETLASTPRODUCEROPERATIONS retrieves the latest producing operation  $p_l$  among all producing operations  $P_a$  that are related to a. After  $p_l$  has been executed for the final time, all data related to a is ready to be transferred to the GPU.  $p_l$  has the highest key among all instructions  $P_a$  in the extended call graph.

- Copy-out (line 4) The function GETFIRSTCONSUMINGOPERATION retrieves the first consuming instruction  $c_f$  among all consuming instructions  $C_a$  that are related to a. When  $c_f$  is executed for the first time, all data related to a should be copied out from the GPU to the CPU.  $c_f$  has the lowest key among all instructions  $C_a$  in the extended call graph.

- Allocation & Free (line 6) The set of retrieved instructions consists of the final producing instruction  $p_f$  and the first consuming instruction  $c_l$  over all dependencies that are related to a. This set of operations represents the lifespan of the related data-structure over the set of kernels.

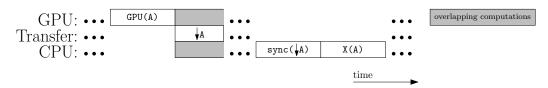

**Calculate the least-common-ancestor (line 10)** For copy actions, a relationship is identified between the position of an action in the extended call graph (i.e. the depth in the extended call graph) and the number of invocations of the action that is executed. At the extremes, the copy actions can be positioned close to the kernel boundary or close to the operations that are assigned to *Operations*; copy actions are scheduled in the deepest level of the extended call

```

Algorithm 1 Scheduling of copy, allocation and synchronisation actions

SCHEDULEACTION(a, k)

1 \triangleright Get the boundary operations

2

if CONTEXT(a) = COPY-IN

3

then Operations \leftarrow \{GetLastProducerOperation(a)\}

4

elseif CONTEXT(a) = COPY-OUT

5

then Operations ←GETFIRSTCONSUMEROPERATION(a)

else \triangleright CONTEXT(a) = ALLOCATION \lor CONTEXT(a) = FREE

6

7

then Operations \leftarrow \{GetFirstProducerOperation(a), \}

GetLatestConsumerOperation(a)

8

9

10

▷ Calculate the least-common-ancestor

LCA \leftarrow GETLCA(Operations, k)

11

12

13 \triangleright Schedule the action

14 if CONTEXT(a) = COPY-IN

15

then SCHEDULECOPYINACTION(a, GETPRODUCINGCHILD(LCA))

16 elseif CONTEXT(a) = COPY-OUT

17

then SCHEDULECOPYOUTACTION(a, GETCONSUMINGCHILD(LCA))

18

elseif CONTEXT(a) = ALLOCATION

19

then SCHEDULEALLOCATIONACTION(a, LCA)

20

else \triangleright Context(a) = Free

21

then SCHEDULEFREEACTION(a, LCA)

```

graph as possible. Figure 4.4 shows a situation where this strategy implies non-efficient datatransfer strategies. Data elements are copied redundantly. By scheduling the copy actions around surrounding loops, the number of invocations of the copy actions reduces. Allocation and free actions are to be scheduled accordingly, such that memory is allocated when a related copy-in action starts and memory is not freed before corresponding copy-out actions are completed.

The highest level in the extended call graph where a data copy action can be scheduled is defined by the *Least-Common Ancestor* of the indicated GPU kernel and the operations that reside in *Operations* (Figure 4.6). The Least-Common Ancestor (LCA) is the deepest node in the extended call graph that shares both the GPU kernel and the operations of *Operations*.

Figure 4.6: Least Common Ancestor of a GPU kernel and a set of operations (*Operations*)

**Schedule the action (line 13)** In the code fragment that represents the LCA, the algorithm defines a period p in the code where a copy action takes place. At the start of p, the copy action is started asynchronously to the host and the accelerator. At the end of p, the copy action must be finished. A synchronisation barrier is inserted to synchronise the copy action with the host. This period is maximised in length to get maximal overlap with computations on the host and the GPU.

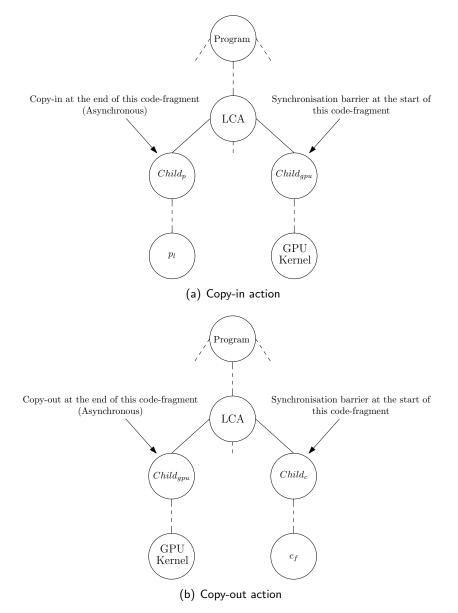

The procedure of scheduling copy-in actions is defined by INSERTCOPYIN. Figure 4.7(a) gives a schematic overview of the period where a copy-in action takes place. A copy-in action a is started right after the code fragment, that is represented by the *LCA's child node*  $Child_p$ , is ended. A LCA's child node is a node in the extended call graph that is a direct child of the LCA. The LCA's child node is invoked directly from the LCA.  $Child_p$  contains the last producing operation  $p_l$  that is related to a. After  $p_l$  was invoked for the last time (i.e. after  $Child_p$ ), all related data-elements are ready to be copied from the host to the GPU. At this moment in the code, the related copy-in action is started.

Since the copy-in action is launched asynchronously, the tool inserts a synchronisation barrier just before the LCA's child node  $Child_{qpu}$  to synchronise the copy-in action with the host. After this

moment, all data-elements that are related to a reside on the GPU's memory.

Figure 4.7: Scheduling of copy actions in the extended call graph

Copy-out actions a (that are related to a specific kernel k) are scheduled similarly. Figure 4.7(b) gives a schematic overview of the period where a copy-out action takes place. The copy-out action is started right after the end of the LCA's child node that contains the GPU kernel  $Child_{gpu}$ . Since GPU kernels are launched asynchronously to the host and CPU-GPU copy actions can only be started from the host, a synchronisation barrier is scheduled before the copy-out action to make sure that the final invocation of kernel k has been finished. After this moment, all related data-elements are ready to be transferred. The copy-out action must be finished just before the start of the LCA's child node  $Child_c$ .  $Child_c$  is the node in the extended call graph that contains the first consuming operation  $c_f$  of the data-elements that are involved in a. Therefore, a synchronisation barrier is scheduled before consumption

on the host. The scheduling process of a copy-out action and its corresponding synchronisation barriers is performed with INSERTCOPYOUT.

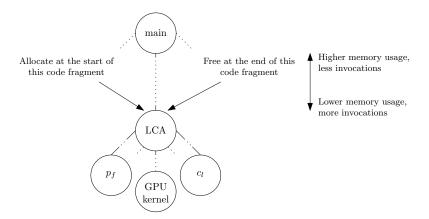

Scheduling allocation (INSERTALLOCATION) and free (INSERTFREE) actions for data-structures that are used on the GPU take a different approach. These actions cannot be performed asynchronously from the host code. Allocation and free actions on the GPU take little time. We observed that allocation and free actions generally take less then 5 ms, independent of the memory size that is being allocated. The tool identifies a window in the ECG where allocation and free actions can take place. This window is depicted in Figure 4.8.

Figure 4.8: Scheduling of allocation & free actions

The effect of scheduling the allocation and free actions at the extremes of the window is explained next. Allocation and free actions can be scheduled at the highest level in the order tree. This implies that the allocation actions are done at the start of the program and free actions are done at the end of the program. This causes the smallest number of invocations. However, memory is allocated over a long period of time. Therefore, the GPU's limited memory space is used inefficiently. Memory is allocated while not being used by the GPU.

By scheduling allocation and free actions lower in the tree, i.e. deeper in the program, the GPU's memory space is utilised more efficiently. The time where data-elements are allocated but not used on the GPU decreases. The lowest level in the extended call graph, where allocation and free actions can be scheduled, is indicated by the least-common-ancestor of the first producing operation  $p_l$  and the last consuming operation  $c_l$ .  $p_f$  and  $c_l$  indicate the maximal life-span of the data-structure that has to be allocated or freed. Scheduling allocation and free actions at this level causes the largest number of invocations of the action (surrounding loops cause redundant invocations of the allocation and free actions). However, memory space is used most efficiently. Scheduling allocation and free actions at deeper level causes incorrect behaviour, since copy actions will then be started before the allocation and will end after the free action.

In the remainder of this thesis, we schedule allocation and free actions at the deepest possible level in the extended call graph; at the position as indicated in Figure 4.8.

By executing this algorithm, the actions that are stated in Table A.2 are translated to the transfer and allocation strategy as stated in Listing A.2.

**Size of copy & allocation actions** In both the CUDA and OpenACC programming models, all copy and allocation actions have to be annotated by the range of data-elements that need to be copied. As discussed in Section 2.3.4, the tools of Vector Fabrics return information about the set of data-elements  $data_{x,d_a}$  that is accessed within a data-structure x for a dependency  $d_a$ . The set of data elements that has to be copied or allocated for an action a is defined by (4.6).

$$DATA_a = \bigcup_{d_a \in a} data_{d_a} \tag{4.6}$$

Out of  $DATA_a$ , the tool annotates each copy and allocation action by the smallest continuous memory-segment that contains all data-elements in  $DATA_a$ .

# TU/e Vector Fabrics

### Chapter 5

## **GPU** kernel optimisations