| MASTER                                                           |

|------------------------------------------------------------------|

| Feasibility of formal model checking in the Vitatron environment |

|                                                                  |

| Wiggelinkhuizen, J.E.                                            |

| Award date: 2008                                                 |

|                                                                  |

| Link to publication                                              |

|                                                                  |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# TECHNISCHE UNIVERSITEIT EINDHOVEN Department of Mathematics and Computer Science

#### Master's Thesis

# Feasibility of formal model checking in the Vitatron environment

J.E. Wiggelinkhuizen

Public version

December 2007

Carried out at: Medtronic SQDM/Vitatron in Arnhem

Period: April 2007 - December 2007

Supervisors: prof.dr.ir. J.F. Groote (TU/e)

dr.ir. G.J. Tretmans (ESI)

ing. E. Hendriksen (Medtronic SQDM/Vitatron)

## Summary

Implantable medical devices that are developed at Medtronic SQDM/Vitatron (Vitatron in the sequel), such as pacemakers, are highly safety critical. Because errors in these devices could potentially harm humans, their behavior must be absolutely reliable. This behavior is to a large extent determined by the device firmware. This report describes the investigation of the feasibility of applying formal model checking to the design of device firmware in order to verify this design more extensively. For this investigation, the firmware design of Vitatron's DA+ pacemaker is used as a case study.

The model checking tools mCRL2 and UPPAAL are considered as a verification environment for formal models that represent a firmware design of Vitatron's devices. mCRL2 is a formal model specification language with accompanying toolset, which contains several analysis and verification tools. mCRL2 is available at [2]. UPPAAL is an integrated tool environment for modeling, validation and verification of real-time systems and is available at [3].

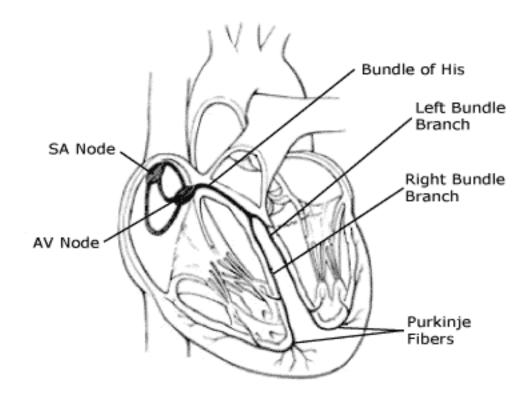

A human heart can show a wide range of rates depending on the activity level of the rest of the body and the heart can suffer from several arrhythmias; such arrhythmias are often the reason that a patient needs a pacemaker. A pacemaker maintains an adequate rate in the patient's heart by delivering electrical stimuli (paces) to the chambers of the heart. The pacemaker firmware determines when these paces must be delivered through calculations that are based on the timing of incoming contraction events. The firmware must deal with all possible rates and arrhythmias, which makes it a complex composition of collaborating and interacting processes.

From the firmware design, we have translated the most characteristic elements, elements that have the largest influence on the external behavior, and elements with a large flaw risk to a formal model in the model checker languages. Firmware elements with a large flaw risk are elements with a high complexity (e.g. firmware parts consisting of many collaborating and interdependent processes) through which it is hard to evaluate their behavior 'manually' by exploring the firmware design specification. Which specific firmware elements we have modeled is mainly determined through consultations with Vitatron, because of our limited domain knowledge.

To investigate the verification of a pacemaker firmware design by formal model checking, we have exploited several model checking approaches on the created formal models.

The main approach consists of verifying the firmware model in the context of a formal heart model, showing the natural behavior of the human heart for several heart rates and some important arrhythmias, and a formal model of a hardware module that forms the interface between the pacemaker firmware and the patient's heart. In this approach we have verified three important requirements, which form a representative subset of all requirements to the external behavior of the firmware design.

Unfortunately we were not able to verify the formal model, corresponding to this approach, for a full range of rates that can be shown by the formal heart model. To provide an extensive verification of the firmware model, this was required, but when we allowed the heart model to show high heart rates, the model state space exploded dramatically, thus making verification infeasible. For heart rates in a range from low to 'average', we have successfully verified the corresponding formal model. This resulted in a validation of all three specified requirements to the firmware model.

Another model checking approach has led to the most promising results of our investigation. In this approach we have verified a firmware design part that is responsible for handling one specific arrhythmia, because this part is a complex composition of collaborating processes and because Vitatron had found a deadlock in this part some time ago. The part has been verified by placing it in the context of some driver processes that provide all combinations of input event sequences and external variable values to the part.

We have succeeded to verify this design part and found the known deadlock rather soon. Verification of a design part was very feasible in this case, mainly because the specific part had little dependencies on external variables, through which we were able to verify the design part extensively for all possible variable value combinations. These results show that model checking certainly is a valuable verification technique, although this is mainly the case for limited design parts.

From our investigations, we have drawn some important recommendations to Vitatron. For the specification of future firmware designs, it is recommended to increase the determinism and the clarity of these designs in order to ease the translation to formal models that are suitable for model checking. Furthermore from the successful approach in which a design part was verified, it appeared to be very valuable from model checking perspective, to design according to the 'low coupling/high cohesion' design pattern. Applying model checking onto parts that are designed according to this design pattern can lead to important results.

For the application of model checking in general, we recommend to start the application of the technique already early in the design stage. This will provide early insight and understanding of the consequences of made design decisions and might prevent expensive corrections.

From our comparison between mCRL2 and UPPAAL in this project, we recommend the use of mCRL2 as a model checking tool for firmware designs, because of the limited results that we obtained from using UPPAAL. However, it is also recommended to further investigate the usability of other available model checking tools.

For the nearby future, it is recommended that Vitatron tries to apply model checking to design components of limited size. It is recommended that the formal models of such design components are created by the firmware designers during the design specification stage, because formally modeling can provide much insight about the consequences of made design decisions. Next to this, it is recommended to state the requirements to the modeled design components also already during the design stage.

## Contents

| 1 | Intr | Introduction       |                                       |    |  |  |  |

|---|------|--------------------|---------------------------------------|----|--|--|--|

| 2 | Mo   | Model checking 1   |                                       |    |  |  |  |

|   |      | 2.0.1              | State space generation                | 13 |  |  |  |

|   |      | 2.0.2              |                                       | 15 |  |  |  |

|   |      | 2.0.3              | Model checking tools                  | 16 |  |  |  |

|   |      | 2.0.4              | The state space explosion problem     | 17 |  |  |  |

|   | 2.1  | mCRL               | .2                                    | 17 |  |  |  |

|   |      | 2.1.1              | The process specification language    | 18 |  |  |  |

|   |      | 2.1.2              | Modal $\mu$ -calculus                 | 22 |  |  |  |

|   |      | 2.1.3              | mCRL2 toolset                         | 23 |  |  |  |

|   | 2.2  | UPPAA              | AL                                    | 25 |  |  |  |

|   |      | 2.2.1              | Timed automata                        | 25 |  |  |  |

|   |      | 2.2.2              |                                       | 26 |  |  |  |

|   |      | 2.2.3              | Simulation and verification           | 29 |  |  |  |

| 3 | The  | the human heart 32 |                                       |    |  |  |  |

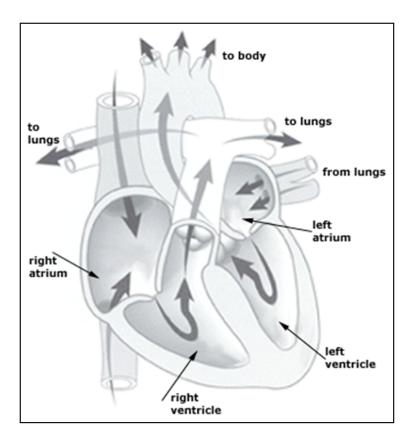

|   | 3.1  | The he             | eart function                         | 32 |  |  |  |

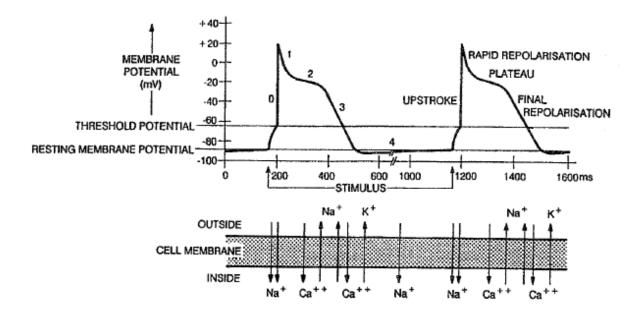

|   | 3.2  | The ele            | ectrical conduction system            | 32 |  |  |  |

|   |      | 3.2.1              | · · · · · · · · · · · · · · · · · · · | 32 |  |  |  |

|   |      | 3.2.2              |                                       | 35 |  |  |  |

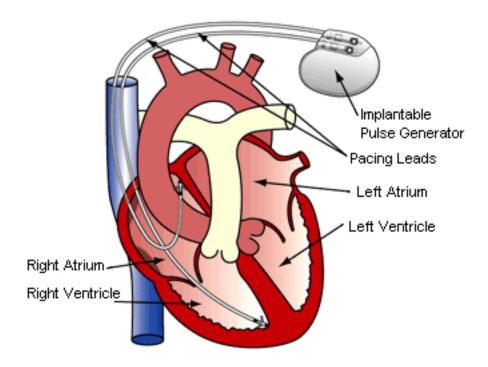

|   | 3.3  | Artific            | · · · · · · · · · · · · · · · · · · · | 36 |  |  |  |

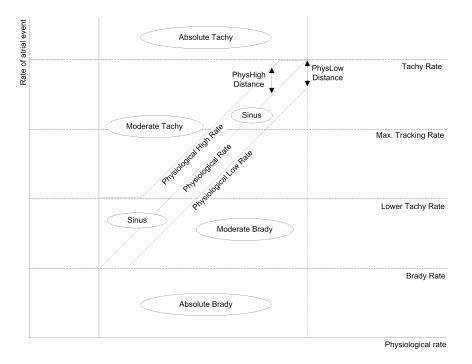

|   | 3.4  |                    |                                       | 37 |  |  |  |

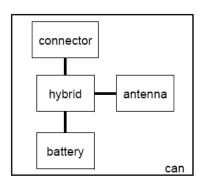

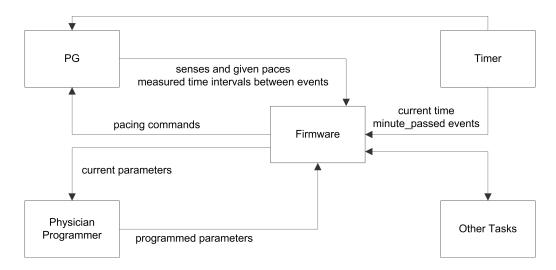

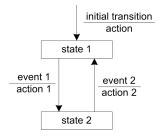

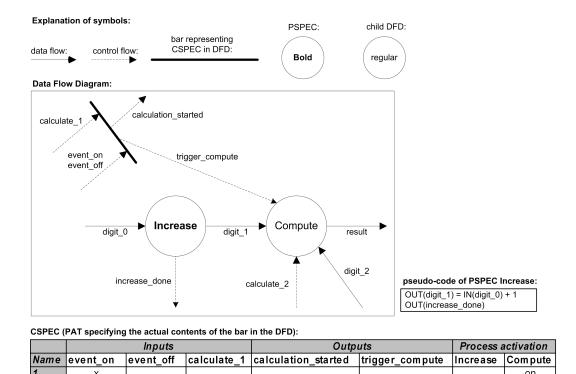

| 4 | Pac  | emakeı             | r architecture 4                      | .0 |  |  |  |

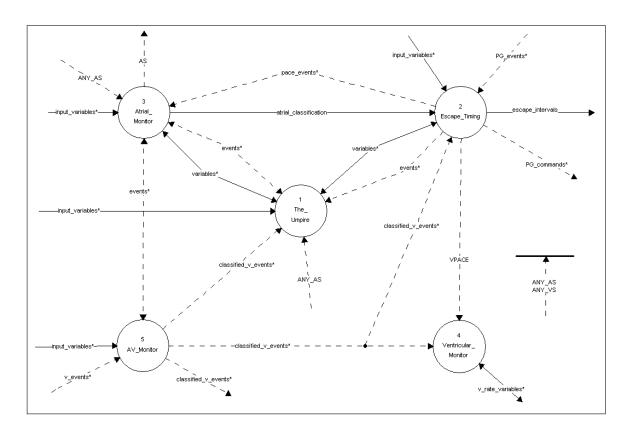

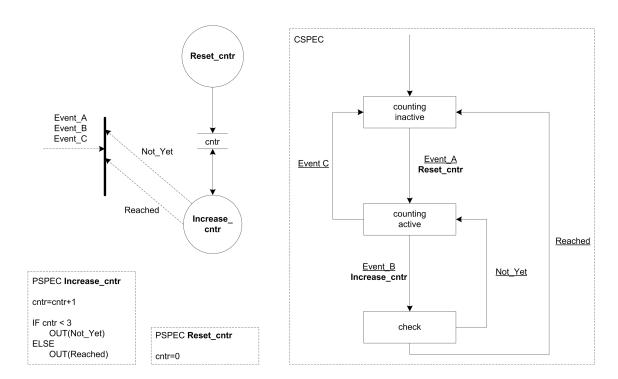

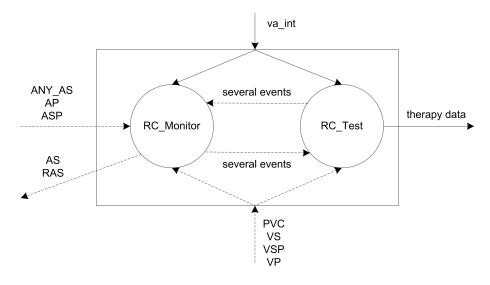

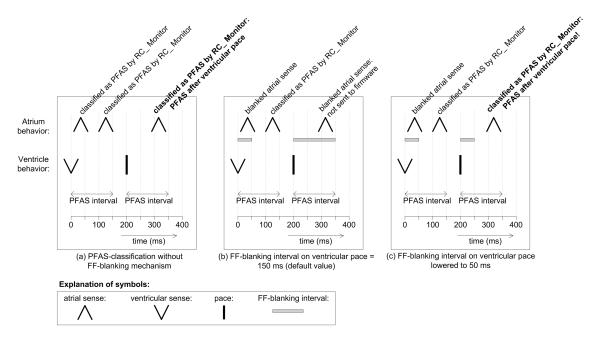

|   | 4.1  | The H              | atley and Pirbhai method              | 12 |  |  |  |

|   | 4.2  | Pacem              | aker H&P model                        | 14 |  |  |  |

| 5 | For  | mal mo             | odeling of pacemaker firmware 4       | 8  |  |  |  |

|   | 5.1  |                    | 9 -                                   | 19 |  |  |  |

|   | 5.2  |                    |                                       | 52 |  |  |  |

|   | 5.3  |                    | 1                                     | 53 |  |  |  |

|   | 5.4  |                    | 1                                     | 54 |  |  |  |

|   | 5.5  |                    |                                       | 56 |  |  |  |

| 6  | Mod                         | del checking approaches and results                   | 60 |  |  |  |  |

|----|-----------------------------|-------------------------------------------------------|----|--|--|--|--|

|    | 6.1                         | Verified requirements                                 | 61 |  |  |  |  |

|    | 6.2                         | Heart model approach                                  | 64 |  |  |  |  |

|    |                             | 6.2.1 mCRL2 results                                   | 65 |  |  |  |  |

|    |                             | 6.2.2 Uppaal results                                  | 67 |  |  |  |  |

|    | 6.3                         | Heart model approach extended with RC functionality   | 67 |  |  |  |  |

|    |                             | 6.3.1 mCRL2 results                                   | 68 |  |  |  |  |

|    | 6.4                         | Isolated RC functionality approach                    | 68 |  |  |  |  |

|    |                             | 6.4.1 mCRL2 results                                   | 71 |  |  |  |  |

|    |                             | 6.4.2 Uppaal results                                  | 74 |  |  |  |  |

|    |                             | 6.4.3 mCRL2 verification of the deadlock consequences | 74 |  |  |  |  |

| 7  | Recommendations to Vitatron |                                                       |    |  |  |  |  |

|    | 7.1                         | 'Model checking aimed'-design                         | 76 |  |  |  |  |

|    | 7.2                         | Application of model checking                         | 80 |  |  |  |  |

|    | 7.3                         | Model checking resources and skills                   | 82 |  |  |  |  |

|    | 7.4                         | Future research                                       | 83 |  |  |  |  |

| 8  | 8 Conclusions               |                                                       |    |  |  |  |  |

| Bi | Bibliography                |                                                       |    |  |  |  |  |

## Glossary

atrium upper chamber of the heart

**bpm** beats per minute

cardiac arrhythmias conditions in which the electrical activity of

the heart is not appropriate

counterexample/witnessing trace sequence of actions leading to a state in which

the requirement is violated/satisfied

crosstalk ventricular sense atrial pace that is detected in the ventricu-

lar and wrongly interpreted as a ventricular

depolarization

CSPEC Control SPECification in an H&P system re-

quirements model

deadlock state state of a formal model from which no transi-

tions are possible

**DFD** Data Flow Diagram in an H&P system re-

quirements model

distributed system whose functionality is distributed over

two or more components

IPG Implantable Pulse Generator (other term for

an artificial pacemaker)

model checking problem the problem of proving that a requirement

holds for a given model

PAT Process Activation Table which can occur as

part of a CSPEC in an H&P system require-

ments model

**PG** Pulse Generator: hardware module in Vita-

tron's DA+ pacemaker that forms the interface between the pacemaker leads and the

pacemaker firmware

PSPEC Process SPECification in an H&P system re-

quirements model

PVC Premature Ventricular Contraction (a ven-

tricular contraction which is not the result of an earlier atrial contraction or a stimulus from

an artificial pacemaker)

refractory period period after depolarization in which cell tissue

is less or not at all excitable, meaning that it

does not react to stimulations

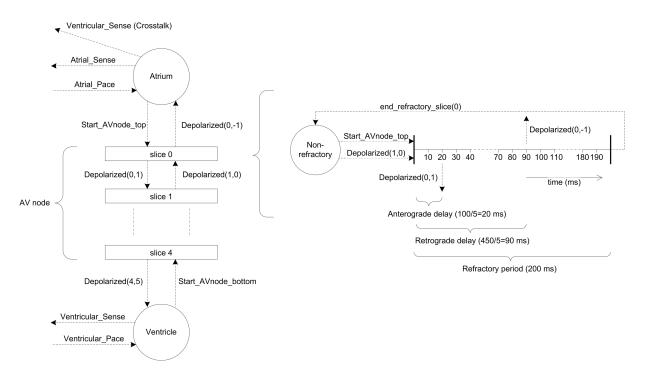

retrograde conduction (RC) conduction of a stimulus in reverse direction,

from the ventricles via the AV node to the

atria

system behavior all possible sequences of actions that a system

can perform during its lifetime

ventricle lower chamber of the heart

## Chapter 1

## Introduction

Medtronic is the global leader in medical technology. With deep roots in the treatment of heart disease, Medtronic now provides a wide range of products and therapies.

Medtronic Subcutaneous Diagnostics and Monitoring (SQDM) is a recently established organization residing in the Medtronic Arnhem facility, where also the Medtronic Vitatron organization is located (in the sequel we will depict these two organizations by Vitatron). Vitatron focuses on subcutaneous (under the skin) implantable medical monitoring devices, used for diagnostic data collection during a number of years. Before the switch to these implantable monitoring devices, pacemakers were developed at Vitatron.

This project is carried out at the firmware development department. This department is responsible for designing, implementing and testing all firmware located in the pacemakers and implantable monitors based on requirements delivered by the system department. A considerable amount of the development effort consists of testing.

Besides the firmware development department, the Research&Development organization consists of a software group, basically developing Object-Oriented, PC-based software and a hardware development group developing the chip-set used in the pacemakers and implantable monitors. Basically Vitatron works from idea until production preparation for their products.

The firmware forms the intelligent core of the devices that are developed at Vitatron, i.e. it controls the behavior of the device hardware. In a pacemaker the firmware controls the hardware such that an adequate heart rate is maintained in the patient's heart, which is necessary either because the heart's native pacemaker is insufficiently fast, or there is a block in the heart's electrical conduction system. An adequate heart rate is required to ensure that the heart pumps enough blood into the body, according to the patient's activity level. To accomplish this adequate heart rate, the pacemaker is connected to the chambers of the heart by electrodes (pacemaker leads). Via these leads, electrical stimuli (paces) can be delivered to force a contraction of the heart's muscle cells.

The pacemaker also retrieves information from the heart via these leads; contractions of the heart are measured and result in input signals on the pacemaker leads. Together with hardware notifications that indicate a delivered pace, these are the main inputs for the pacemaker firmware, which calculates whether the current heart rate is appropriate on every input signal. These calculations always result in commanding the hardware to deliver a pace to the heart on a certain moment in time. The planned pace will ensure a heart contraction and prevents that the heart stops pumping blood into the body if it does not contract spontaneously anymore.

Because errors in Vitatron's medical devices could potentially harm humans, testing of the firmware that controls these devices is extremely important. Vitatron spends a lot of effort in testing and verification of their firmware designs and implementations. Currently this is mainly done by reviewing and functional testing, but the coverage of these techniques is not optimal. Therefore it could be the case that certain errors are not discovered. Combining the current test methods with formal methods is perhaps a solution to test the firmware designs more extensively. But at this moment, Vitatron is unaware of the possibilities of formal methods in their environment.

Formal methods are based on solid mathematical principles and increase understanding of systems, increase clarity of descriptions and help solve problems and remove errors. The use of formal methods for software and hardware designs is motivated by the expectation that performing appropriate mathematical analyses can contribute to the reliability and robustness of these designs. However, the high cost of using formal methods means that they are usually only used in the development of safety-critical systems.

Model checking is one of these formal methods that can be used to verify whether a model of a system design satisfies its requirements. Models of hardware designs, software designs and also communication protocols can be verified by means of model checking. The technique is called model checking because it is used to *check* whether a system requirement holds in a formal *model* that represents the verified system design. The great advantage of design verification by using model checking is the completeness of the verification; after validation of a requirement on a formal model of the system design, it is absolutely sure that this model contains no behavior that violates the requirement. Of course such a validation is only useful if the verified model is a valid representation of the system design.

To make model checking feasible, simplifications must be applied when a system design is translated to a formal model. Without these simplifications the model verification generally needs too much time and space resources. Because of this need for simplifications, it generally appears to be very hard to create a formal model that is a valid representation of the system design. Furthermore inventing the right requirements to the system design and correctly formulating them is often not straightforward.

This makes clear that the application of formal model checking to Vitatron's firmware designs is certainly not straightforward. Therefore this project investigates the feasibility of model checking in the Vitatron environment. For this investigation, the firmware design of Vitatron's DA+ pacemaker is used as a case study. We investigate how formal models can be developed that represent (parts of) the firmware design, which requirements to the firmware design (parts) are suitable candidates to be formally verified, and whether the verification of these requirements on the formal models is feasible. In these investigations, we consider two different model checking tools, i.e. mCRL2 and UPPAAL.

Developing a formal model that represents a system design, means that the behavior and the responsibilities of all components in the system design and the communications between them are made explicit. As described above, the challenge in formally modeling a system design consists of inventing the right simplifications without letting the formal model deviate too much from the meant behavior in the system design. In our investigation of the development of formal models representing the pacemaker firmware design, we also address this point of inventing the right simplifications.

The final goal of these investigations is providing recommendations to Vitatron, concerning the applicability of model checking as a minimum. To achieve this final goal, we try to verify requirements on (parts of) the firmware design by means of model checking in both mCRL2 and UPPAAL.

The report is divided into two parts. The first part consists of chapters 2, 3, and 4 and describes the background of the project. Chapter 2 introduces the model checking technique and the used model checking tools, chapter 3 describes some important aspects of the physiology of the human heart, and chapter 4 describes the architecture of the DA+ pacemaker and the design of the pacemaker firmware.

The second part consists of chapter 5, 6, and 7 and describes the investigation that has been carried out during this project. Chapter 5 describes the translation of the pacemaker firmware design to formal models, and chapter 6 describes how model checking is applied on these formal models and which results we have obtained. Chapter 7 describes the recommendations to Vitatron about how they could apply model checking on their firmware designs in the future.

Finally, chapter 8 presents our main conclusions and gives a summary of our recommendations from chapter 7.

Note that the formal models that are produced in this project are not included as appendices to this report for confidentiality reasons. This report is accompanied by a CD on which all relevant formal models can be found.

Furthermore, in this version of the report some parts of the text are removed or changed for confidentiality reasons. These changes all concern pacemaker details which are not crucial for understanding the results of the investigations.

## Chapter 2

## Model checking

More general information about model checking can be found in [6] and [14].

Many software and hardware systems are composed of separate components that are being executed in parallel and together define the behavior of the system by interacting with each other. The *system behavior* is represented by all possible sequences of actions that a system can perform during its lifetime. Such a system whose functionality is distributed over two or more components is also called a *distributed system*. A component of a distributed system does not contain any concurrency and is described as a sequence of operations on a set of inputs, possibly resulting in one or more outputs.

When designing a large distributed system consisting of several components, it is generally very hard to maintain a clear picture of the overall behavior of the system. The number and the size of all possible executions of a distributed system are exponential in the number of possible input combinations and in the number and the size of the system components. Execution must be understood as the action sequence that is performed by the system in response to one particular set of inputs. It is often impossible to analyze all these executions separately when one wants to check whether the system behavior satisfies its requirements. One possible tactic to verify such systems could be verifying whether the executions that result from the mostly occurring input combinations, are valid. But this generally leaves a rather big number of executions unverified, which could possibly contain an execution that does not satisfy the requirements.

Model checking is a formal method that has been developed for extensively analyzing and verifying complex distributed systems. The model checking method aims at guaranteeing that all executions of the analyzed system satisfy the system requirements, or if these requirements are not met, the method tries to provide information about the circumstances (the particular inputs and system settings) in which the system is not correct.

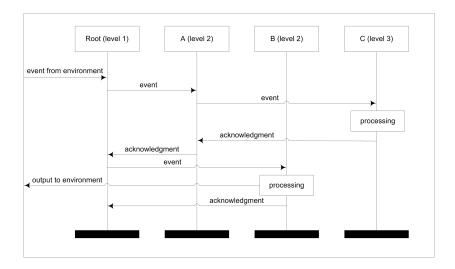

To provide such an automatic and complete verification method of distributed systems, formal analysis techniques and tools are developed. These techniques require a formal model which is an abstraction of the behavior of the analyzed system. By modeling the system behavior, the responsibilities of the system components and the communication between them are made explicit. Often the system is only partially formalized, because some parts are not relevant for the system requirement that is verified. Each modeled system component translates to one or more concurrent processes in the formal model. Depending on the nature

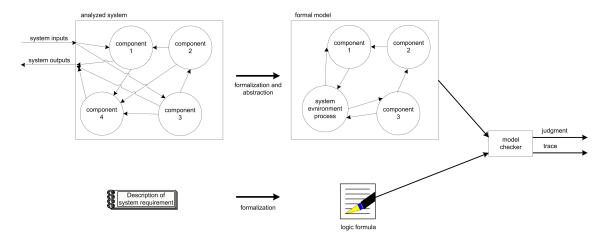

of the system, one or more concurrent processes can be contained to provide inputs to the processes that represent the system. Figure 2.1 shows how system, formal model and model checking relate to each other.

Figure 2.1: The model checking process

Because the modeled system can be very complex, it is generally also difficult to get a valid formal model of the system. Therefore it is wise to use a kind of iterative modeling approach in which the formal analysis techniques are used to find flaws in the model. These flaws can be corrected after which the model can again be analyzed, etc. Eventually this hopefully will result in a valid formal model of the system.

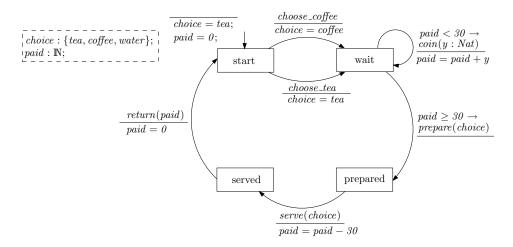

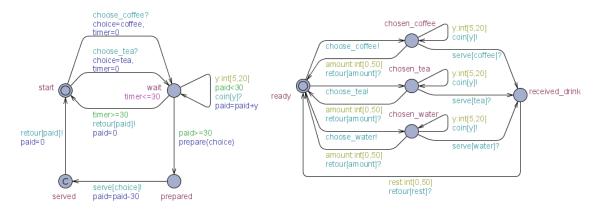

As a running example for this chapter consider a simple coffee machine system. The system is designed to deliver coffee, tea or water to the user; the user should be able to choose for coffee, tea or water by pushing the button <code>choose\_coffee</code>, <code>choose\_tea</code>, or <code>choose\_water</code> respectively. After choosing a drink, the user can insert money and the machine starts preparing when at least 30 cents are inserted by the user. When the drink has been prepared, the machine serves the drink to the user and returns the money that is paid too much.

The coffee machine system is represented as a state transition diagram in figure 2.2. Unfortunately the required 'choose water' option has not been included in the design, which is reflected by the absence of a *choose\_water* transition in the figure. Although the coffee machine system is not a real distributed system, because it consists of only one component, it will be useful to explain the basic notions of model checking.

Figure 2.2: Coffee machine system

Because we do not use a standard notation in figure 2.2, a few notation issues must be addressed. In the dashed rectangle the variables *choice* and *paid* are declared that are set when the user chooses a drink or inserts a coin, respectively. A label on a transition may consist of the following fields: a guard followed by an arrow which indicates under which condition this transition may be taken, the action that will cause the transition to be taken, and assignments to variables of the process (below a horizontal line). Each transition must have exactly one action in its label, but there may be zero or multiple guards and variable assignments in a label. Note that a small incoming arc to state 'start' indicates that 'start' is the initial state of the process. This arc also has a label in which the variables *choice* and *paid* are initialized. The action *coin* has an argument y to indicate what value the inserted coin has.

The problem of proving that a requirement holds for a given model is called the *model checking problem*. In our coffee machine example, you want to be sure that the user always gets the drink of his or her choice, provided that enough coins are inserted. If you are verifying a data communication protocol, you want to make sure that a sent message always will eventually reach its recipient and nobody else than the recipient. Such requirements can be expressed in a logic formula, which together with the formal model forms the input to a model checker. The model checker either reports that the requirement holds or does not hold. Depending on the kind of formula and the result of the verification, the model checker can provide a *counterexample trace* or *witnessing trace*, which is a sequence of actions leading to a state in which the requirement is violated or satisfied, respectively. Such a counterexample potentially can provide useful feedback to improve the model and the modeled system itself.

Notice that the described behavior of a model checker is somewhat idealized. Often the available resources are not sufficient to analyze the complete model and then simplifications of the model are needed to make model checking possible. The challenge is to choose the right simplifications to be sure that the analyzed model still represents the behavior of (the modeled part of) the original system. Otherwise a confirmation of the verified requirement is of limited value, because there could be a flaw in a part of the system behavior that is left out due to simplifications.

#### 2.0.1 State space generation

To describe the basic mechanism of a model checker, we first introduce the notion of the model state space. Depending on all previously performed actions the model of the analyzed system resides in a certain state which can be seen as a vector of the values of all component variables and the states of the individual components. For example, the coffee machine system from our example can be straightforwardly translated to a formal model in which the states are depicted by (state, choice, paid) vectors. In such a formal model, the initial state is given by (start, tea, 0) and performing action choose(coffee) in the initial state will move the model to state (wait, coffee, 0).

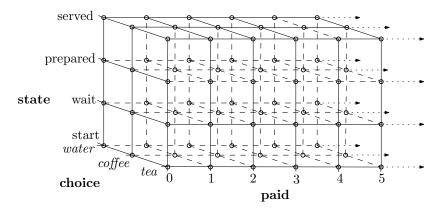

Each model has an associated state space, consisting of all states that are reachable from the model's initial state. Under the assumption that all states of the formal model of the coffee machine system are reachable from its initial state, the state space of this model would be infinitely large, because the variable *paid* is a natural number. In figure 2.3 a schematic overview of all combinatorial possibilities is given.

Figure 2.3: Possible states of the coffee machine system

Though in reality there are limitations: the values of the coins that can be inserted are discrete; assume for now that only coins of 5, 10 and 20 cents are accepted by the coffee machine. Furthermore, the system's state transition diagram of figure 2.2 makes clear that it is not possible to insert any more coins when already at least 30 cents have been inserted and that the user can not choose for water. We shall see that these limitations make the actual state space of the coffee machine model finite.

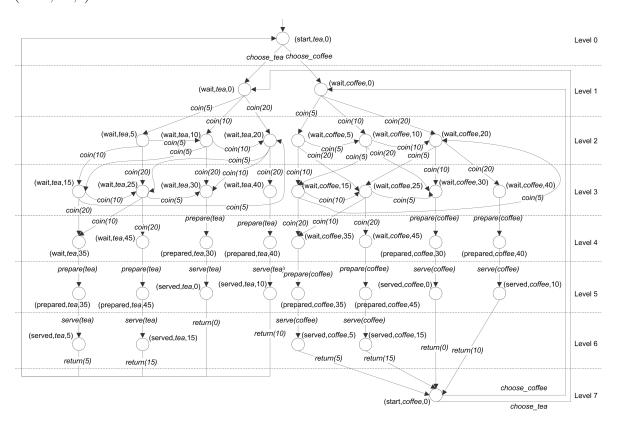

A model checker generates the state space in order to make requirement verification possible. For this generation an algorithm is used that explores the state space from the initial state until it no longer finds new states. The precise order in which the states are explored depends on the used algorithm; this can for instance be a breadth-first search, a depth-first search or a random search algorithm. Here we only address the breadth-first search algorithm; this algorithm starts by exploring which states are reachable from the initial state by taking all possible transitions out of the initial state. The newly discovered states are added to the state space together with the transitions leading to them. The added states are said to be on level 1 of the state space, because they are reachable in one step from the initial state. When all discovered states are added to level 1, the initial state is said to be 'explored'. In the second iteration the algorithm explores which states are reachable from the states on level 1; any newly found state is added to the state space again (on level 2) together with the

transition leading to it, except when a found state is already present in the state space only the transition leading to it is added. If all states of level 1 are addressed by this procedure, the second iteration is finished and the algorithm iterates by exploring the states on level 2. The iteration stops if exploration of the states on a certain level does not discover new states, which means that all states in the state space have been explored after the exploration of this level.

The state space generation results in a labeled transition system in which all transitions represent one single atomic action. For the coffee machine example, the state space is shown in figure 2.4. Note that the initial state is again marked with a small incoming arc. However there is no action on this arc, because variable initialization is made implicit by entering state (start, tea, 0).

Figure 2.4: State space of the coffee machine system

Although the state space of the coffee machine model is finite, its size can be even more reduced by improving the system's state transition diagram of figure 2.2. The money that is paid too much is returned after serving the requested drink through which there are eight states in the state space for the machine state 'served'. If the too much paid money should be returned before serving the drink there would be only two states (one for each possible drink) for 'served' in the resulting state space. This is a small example of how the architecture of the modeled system influences the size of the state space.

The generated state space is explored by the model checker in order to verify the given requirement to the system. Basically it traverses all states consecutively and continuously checks whether the current state satisfies the requirement. Sometimes it is not required to traverse all states, but this depends on which kind of property is verified. For example, if it is questioned whether action a is ever performed in the state space, the verification can stop on the detection of one single a action, which possibly can be very soon. But when the state space does not contain any a action the complete state space must be explored before the algorithm can give its judgment.

#### 2.0.2 Formulating model requirements

As already noted, a system requirement must be formulated in some kind of logic before a model checker can verify it. Propositional formulas over state variables are the most basic formulas. In such formulas, it can for instance be specified that a certain variable is at most 10 in the entire state space. Presuming that the user of our coffee machine is not able to choose water can be the reason that we want to verify whether the variable *choice* ever gets the value water in the state space of the coffee machine model. The model checker then traverses all states to check whether choice = water and will report that there is no state that satisfies the specified property.

Clearly propositional logic is not expressive enough, because we can not specify anything about actions that are performed by the modeled system. Therefore there are more expressive logics which can be classified into non-temporal and temporal ones; temporal logics are the more expressive of the two types. Which specific logics can be used in model checking depends on the used tool, but generally all model checkers accept formulas in propositional, non-temporal, and temporal logics. We give some examples in temporal and non-temporal logic in order to indicate their differences. It is important to notice that the initial state is the reference point of all formulas in temporal and non-temporal logics.

For explaining non-temporal logics and giving examples for these logics we use the Hennessy-Milner logic ([13]; also introduced in chapter 4 of [11]). Its syntax is given by the following grammar:

$$\phi ::= true \mid false \mid \neg \phi \mid \phi \land \phi \mid \phi \lor \phi \mid \langle a \rangle \phi \mid [a] \phi.$$

The primitive formula true is valid in all states of a model and false is never valid in any state. The logical operators have their usual meaning and can be used to compose logic formulas. The two special constructs of the Hennessy-Milner logic are the diamond modality and the box modality. The diamond modality  $\langle a \rangle \phi$  expresses that there is a transition labeled with action a and leading to a state in which the formula  $\phi$  holds. The box modality  $[a]\phi$  expresses that all transitions labeled with action a lead to a state in which formula  $\phi$  holds.

Now if we want to verify whether the user can choose coffee in our coffee machine system we formulate a formula as follows:  $\langle choose\_coffee \rangle true$ . The formula  $[choose\_water]false$  expresses that whenever an action  $choose\_water$  is done, a state is reached where false is valid. Because false is not valid in any state, the formula expresses that an action  $choose\_water$  is not possible. The formula  $\langle choose\_coffee \rangle \langle coin(20) \rangle \langle prepare(coffee) \rangle true$  expresses that the action sequence  $choose\_coffee$ , coin(20), prepare(coffee) is possible from the initial state, which is clearly not valid, because the machine can not start preparing coffee before enough money is inserted.

As mentioned above, all logic formulas are evaluated in the initial state of the system. Because non-temporal logics do not provide the ability to specify an arbitrary action sequence, we can not specify that a certain requirement must hold during the entire lifetime of the system. Should the coffee machine model contain a flaw such that the coffee machine runs into a deadlock after serving the first drink in its lifetime, the truth values of the above

mentioned formulas will remain the same, although the model behavior certainly does not satisfy its requirements. You want to make sure that the coffee machine operates as required during its entire lifetime. For this purpose, the property must be specified in a temporal logic. For example, the property "after choosing coffee the machine *always eventually* serves my coffee" is not expressible in non-temporal logics, though it is expressible in temporal logics.

As the word temporal already says, a temporal logic deals with 'time', where performing actions must be understood as passage of 'time'. In a temporal logic it is possible to express that a formula is *always* valid, *eventually* valid or valid *until* some other formula is valid. We give some examples in temporal logic, using the same Hennessy-Milner logic extended with regular expressions. In this extension more than just a single action is allowed in a diamond or box modality. See [11] for a description of this extension. With this extension it is possible to formulate the above property. We give the corresponding logic formula for the interested reader:

$$[true^* \cdot choose\_coffee] \langle true^* \cdot serve(coffee) \rangle true.$$

Literally this formula says that if after a certain sequence of zero or more arbitrary actions (expressed by  $true^*$ ) an action  $choose\_coffee$  is possible, then after that an action serve(coffee) is possible after a certain sequence of zero or more arbitrary actions. A stronger property that can be formulated in temporal logic would be "after choosing coffee the machine will not process any other request before serving my coffee". This is formulated as follows:

$$[true^* \cdot choose\_coffee] \langle \overline{choose\_coffee} \cup \overline{choose\_tea} \cup \overline{choose\_water}^* \cdot serve(coffee) \rangle true.$$

Literally this formula says that if after a certain sequence of zero or more arbitrary actions an action  $choose\_coffee$  is possible, then after that an action serve(coffee) is possible after a certain sequence of actions, not containing choose actions.

Sometimes the nature of the model makes it hard to translate a requirement into a logical formula. Then an alternative option is to add an action to the model which can only be performed if the requirement is not satisfied. Assume that we want to verify that the variable paid in the coffee machine model never becomes greater than 50 in state 'wait'; then we add a loop transition (a transition from a state to itself) to 'wait' with a guard 'paid > 50' that performs the action alarm. Verifying the requirement then is a matter of specifying in a simple logic formula that the action alarm can be performed after zero or more arbitrary actions:  $\langle true^* \cdot alarm \rangle true$ . If the model checker reports that the formula is true, it is guaranteed that the requirement is not true; the model checker might provide a witnessing trace which specifies an action sequence that leads to the performance of action alarm. This trace can be inspected to find the flaw in the system. On the other hand, if the model checker reports that the formula is false, the model is guaranteed to satisfy the requirement. Some model checkers also can be instructed to detect certain actions during state space generation; then a message is printed to the screen or to an output file for each such action that is detected during state space generation. Whether this method is suitable heavily depends on the model and the requirement in question.

#### 2.0.3 Model checking tools

As already said, there are various model checking tools available. Some of the most known tools are SMV, SPIN, CADP, mCRL2, and UPPAAL. In this project mCRL2 and UPPAAL are

investigated as a model checking environment for the formal models representing the firmware designs of Vitatron. In sections 2.1 and 2.2 these tools are introduced.

#### 2.0.4 The state space explosion problem

The generated state space can become very large for many real-world problems. This is a well-known problem in the field of model checking and is called the state space explosion problem. Not only the time and space resources to generate such large state spaces can be a problem, but also the model checking on a large state space is a difficult job even for the most efficient algorithms.

Most model checkers provide techniques to enable model checking without generating the complete state space. Such techniques can have drastic influence on the time and space required for model checking and can be of various kinds:

- "on-the-fly"-verification of properties during state space generation. In some cases it is not even necessary to explore the complete state space when verifying a property; this happens when a witness or, on the contrary, a counterexample is found during the process of verification. This technique is used by the pbes2bool tool in mCRL2 (see section 2.1.3) and also in UPPAAL (see section 2.2). Also SPIN and CADP are "on-the-fly" model checking tools.

- Symbolic model checking; algorithms for symbolic model checking avoid ever generating and storing the state space. Instead, they generally represent the state space using a formula in propositional logic. On such a formula, properties can be verified purely by manipulations of the formula. See [16] for more information about symbolic model checking. Recently also the use of resolution provers has become popular in the field of model checking. Symbolic model checking forms the basis of the tool SMV and is also used by the model checking tools in the mCRL2 toolset (see section 2.1.3).

- Partial order reduction or  $\tau$ -confluence can be used to reduce the number of independent executions of concurrent processes that need to be considered. The basic idea is that if it does not matter for the property that you want to check whether a or b is executed first, then it is useless to consider both the ab and the ba executions.

- Abstraction; when using this technique, you first simplify the model by abstracting from the internal behavior of the model that is not relevant for the property that is verified. The simplified system usually does not satisfy exactly the same properties as the original one, but generally, it is required that the abstraction is sound (properties that are proved on the abstraction are true of the original system). However, most often, the abstraction is not complete (not all true properties of the original system are true of the abstraction).

### 2.1 mCRL2

mCRL2 is a formal model specification language with an associated toolset. The toolset is available at [2]. mCRL2 stands for milli Common Representation Language 2 and is the successor of  $\mu$ CRL. The language and its toolset are developed at the department of Mathematics and Computer Science of the TU/e, in collaboration with LaQuSo and CWI.

This section introduces the main concepts of mCRL2, heavily based on [9] and [10]. For more information see these papers.

The mCRL2 language can be used to specify formal models, representing the behavior of distributed systems and protocols; using its accompanying toolset models can be analyzed and verified automatically. The 'about'-section of [2] contains a good description of the mCRL2 philosophy:

"mCRL2 is based on the Algebra of Communicating Processes (ACP) which is extended to include data and time. Like in every process algebra, a fundamental concept in mCRL2 is the process. Processes can perform actions and can be composed to form new processes using algebraic operators. A system usually consists of several processes (or components) in parallel.

A process can carry data as its parameters. The state of a process is a specific combination of parameter values. This state may influence the possible actions that the process can perform. In turn, the execution of an action may result in a state change. Every process has a corresponding state space or Labeled Transition System (LTS) which contains all states that the process can reach, along with the possible transitions between those states.

Using the algebraic operators, very complex processes can be constructed containing, for example, lots of parallelism. A central notion in mCRL2 is the linear process. This is a process from which all parallelism has been removed to produce a series of condition - action - effect rules. Complex systems, consisting of hundreds or even thousands of processes, can be translated to a single linear process. Even for systems with an infinite state space, the linear process (being an abstract representation of that state space) is finite and can often be obtained very easily. Therefore, most tools in the mCRL2 toolset operate on linear processes rather than on state spaces."

It should be noticed that the mentioned built-in concept of time is somewhat premature and therefore this concept is not used in this project. Instead, the passing of time is explicitly modeled in all time-dependent processes. The mCRL2 model description in section 5.2 comes back to this point.

#### 2.1.1 The process specification language

This section describes the mCRL2 language followed by the mCRL2 specification of the coffee machine model, which might clarify how the contents of the language relate to each other.

Processes and actions are the fundamental concepts in the mCRL2 language. A process in mCRL2 describes the behavior of a component in the modeled distributed system. Actions represent atomic events, which possibly can be synchronized with other actions. When two actions are declared synchronous, the actions can be performed by two different processes truly in parallel. By this synchronization mechanism communication and interaction between processes can be modeled.

Processes are defined by *process expressions*, which are compositions of actions using a number of operators. The basic operators are as follows (let a and b be arbitrary actions and let p and q be arbitrary process expressions):

• Deadlock or inaction  $\delta$ , which does not display any behavior.

- Alternative composition, written as p + q. This represents a non-deterministic choice between p and q.

- Sequential composition, written as  $p \cdot q$ . This expression first executes p and then q (assuming p terminates).

- Recursion describes iterating behavior of a process. A simple example of recursion is the process expression  $X = a \cdot X + b$ . This process describes a sequence of a actions of arbitrary length (as long as the first alternative is chosen) followed by a single b action.

- Parallel composition or merge, written as  $p \parallel q$ , which interleaves and synchronizes the actions of p with those of q.

- Synchronization operator p|q, which synchronizes the first actions of p and q and combines the rest of p and q like the parallel composition.

- Multiaction a|...|b, which is a special instance of the synchronization operator where the arguments are single actions (or multiactions). The meaning of a multiaction is that all actions occurring in it happen at the same moment (i.e. truly in parallel).

Furthermore there are some operators to restrict the behavior of process expressions in order to model the interaction between processes. The restriction operator( $\nabla$ ) and blocking operator( $\partial$ ) can be used to specify explicitly which multiactions are allowed to occur or are not allowed to occur, respectively. With the communication operator( $\Gamma$ ) a set of allowed communications can be defined, for example a communication  $a_0 | \dots | a_n \to c$  means that every group of actions  $a_0, \dots, a_n$  within a multiaction is replaced by c (this is expressed by  $\Gamma_{\{a_0 | \dots | a_n \to c\}}(p)$  where p is the process expression on which the communication operator is applied).

When we for instance want to model communication from process X to process Y, we declare three actions send, receive, and communicate and we define the process expressions of X and Y as follows: X = send and Y = receive. Then we use the communication operator to specify that the send action and the receive action synchronize to the communicate action  $(send|receive \rightarrow communicate)$ . Because we do not want X to send without Y receiving and vice versa, we use the restriction operator to specify that only the communicate action can occur. This combination of the synchronization and restriction operators is often used in modeling communicating processes.

Before we move on to the data aspects of the language, the notion of abstraction has to be mentioned in the context of mCRL2. Usually the requirements of a system are defined in terms of external behavior (i.e. the interactions of the system with its environment), while one wishes to check these requirements on an implementation of the system which also contains internal behavior (i.e. the interaction between the components of the system). So it is desirable to be able to abstract from the internal behavior of the implementation. This is possible 'hiding' internal actions in a mCRL2 specification. This abstraction can be useful in reducing state space sizes. When internal actions are hidden and the state space is generated, reduction techniques based on bisimulation equivalence can be applied to the state space. More information can be found in [11].

#### Data

There are some standard data sorts and functions included in mCRL2. Unbounded positive  $(\mathbb{N}^+)$ , natural  $(\mathbb{N})$ , integer  $(\mathbb{Z})$  and real numbers  $(\mathbb{R})$  are included with all relational and arithmetic operators. Note that real numbers are only used in the time functionality, which will not be covered here. Booleans  $(\mathbb{B})$  are included with all elementary operators. Boolean expressions can be used in *conditions*, which are used together with the conditional operator, written as  $c \to p \diamond q$ , where c is a boolean data expression. This process expression behaves as an if-then-else construct: take for example the process expression  $X = (n \geq 10) \to a \diamond b$ , which expresses that action a is performed for a at least 10, otherwise action a is performed. Note that the else-branch is optional;  $c \to p$  is a valid expression which expresses that a is only performed if a holds.

Besides these standard data sorts it is possible to declare custom sorts together with functions on these sorts. This can be done by declaring constructors, functions and their definitions manually or by using one of the type constructors. There is a type constructor for structured types, for list types, for sets, and finally one for bags. These type constructors automatically provide some standard functions to the type, for example comparing functions.

Data can be used to parameterize actions and processes. As an example, actions can be declared as follows:

```

\begin{array}{ll} \mathbf{act} & & a; \\ & b, c, d: \mathbb{N}; \\ & e & : \mathbb{B} \times \mathbb{N}^+; \end{array}

```

This declares parameterless action a, actions b, c and d with a data parameter of sort  $\mathbb{N}$ , and action e with two parameters of sort  $\mathbb{B}$  and  $\mathbb{N}^+$ , respectively. For the above declaration, a, b(0) and e(false,6) are valid actions. For all operators, except the communication operator, the data parameterization doesn't change much; the data parameters are just retained when an operator is applied. The communication operator  $\Gamma_C(p)$  has become stricter: for each communication  $a_0|\ldots|a_n\to c, n\geq 1$ , multiactions  $a_0(\ldots)|\ldots|a_n(\ldots)$  in p are only replaced by  $c(\ldots)$  when the data parameters of all  $a_i$  are equal (both the number of parameters and their values). The data parameters are retained in action c. For example  $\Gamma_{\{b|c\to d\}}(b(0)|c(0)) = d(0)$ , but also  $\Gamma_{\{b|c\to d\}}(b(0)|c(1)) = b(0)|c(1)$ . Furthermore  $\Gamma_{\{b|c\to d\}}(b(1)|b(0)|c(1)) = b(0)|d(1)$ .

Processes can be parameterized as follows:

```

P(d: \mathbb{B}, e: \mathbb{N}^+) = a \cdot P(d, e)

+b(d) \cdot P(\neg d, e+1)

+c(d, e) \cdot P(false, max(e-1, 1));

```

This declares the process P with data parameters d and e of sort  $\mathbb{B}$  and  $\mathbb{N}^+$ , respectively. Note that the data parameters can be seen as local variables in the process, which are declared in the left-hand side of the equation. In the process references on the right-hand side it is specified how the values of the data parameters are changed when the corresponding action(s) in front of it are performed.

There is also the ability to quantify over (possibly infinite) data types in process expressions. This is provided through the *summation* operator  $\sum_{d:D} p$  where p is a process expression in

which data variable d may occur. The corresponding behavior is  $p[d_0/d] + \cdots + p[d_n/d] + \cdots$ ,  $n \geq 0$ , for all elements  $d_i \in D$ . Here,  $p[d_i/d]$  stands for p in which each free occurrence of d (i.e. not bound by another  $\sum_{d:D}$ ) is replaced by  $d_i$ .

Summations over a data type are particularly useful to model the receipt of an arbitrary element of a data type. For example the following process is a description of a single-place buffer, repeatedly reading a natural number using action name r, and then delivering that value via action name s.

```

act r, s : \mathbb{N};

proc Buffer = \sum_{n:\mathbb{N}} r(n) \cdot s(n) \cdot Buffer;

```

After this overview of the mCRL2 process specification language, we give an mCRL2 model of our coffee machine system. This model includes a process that represents the machine and a process that represents a user of the machine, which communicate with each other. As all mCRL2 models this model is structured as follows: first the custom sorts and all used actions are declared, next the process expressions that define the machine process (line 13-32) and the user process (line 34-49) are given and finally the initial state of the model is defined. Note that alternative composition (+) is used in combination with conditions to specify all transitions of the state transition diagram in figure 2.2 in process *Machine*. The communication and restriction operator are used in the initial state definition to specify the possible communications between the processes. In the model we have given comments on some lines by stating them after the comment operator %.

```

% line 2-4 declare three structured data types

sort_choice: struct tea | coffee | water;

2.

machine_state: struct start | wait | prepared | served;

3.

4.

user_state: struct ready | chosen;

5.

act

r\_choose\_tea, s\_choose\_tea, c\_choose\_tea;

6.

r\_choose\_coffee, s\_choose\_coffee;

7.

r\_choose\_water, s\_choose\_water, c\_choose\_water;

r_{-}coin, s_{-}coin, c_{-}coin: \mathbb{N};

8.

9.

prepare : sort_choice;

10.

r\_serve, s\_serve, c\_serve : sort\_choice;

11.

r\_return, s\_return, c\_return : \mathbb{N};

12.

Machine(state : machine\_state, choice : sort\_choice, paid : \mathbb{N}) =

13. proc

% line 15-19 define the behavior of Machine if state equals start

14.

(state \approx start) \rightarrow

15.

% line 17: receive of choose_coffee changes state to (wait, coffee, paid)

16.

r\_choose\_coffee \cdot Machine(wait, coffee, paid) +

17.

r\_choose\_tea \cdot Machine(wait, tea, paid)

18.

19.

(state \approx wait) \rightarrow

20.

(paid < 30) \rightarrow

21.

% accept receive of coin with any natural valued parameter y

22.

23.

% such a message changes state to (wait, choice, paid + y)

24.

\sum_{y:\mathbb{N}} r_{-}coin(y) \cdot Machine(\text{wait}, choice, paid + y) +

25.

% paid at least 30, so perform prepare action

26.

27.

prepare(choice) \cdot Machine(prepared, choice, paid)

```

```

)+

28.

29.

(state \approx prepared) \rightarrow

s\_serve(choice) \cdot Machine(served, choice, paid - 30);

30.

(state \approx served) \rightarrow

31

s\_return(paid) \cdot Machine(start, choice, 0);

32.

33.

User(state : user\_state) =

34. proc

(state \approx \text{ready}) \rightarrow

35.

s\_choose\_coffee \cdot User(chosen\_coffee) +

36.

37.

s\_choose\_tea \cdot User(chosen\_tea) +

s\_choose\_water \cdot User(chosen\_water)

38.

39.

(state \approx \text{chosen\_coffee} \vee state \approx \text{chosen\_tea} \vee state \approx \text{chosen\_water}) \rightarrow

40.

% drink is chosen, perform s_{-}coin action for a possible coin value

41.

42.

% or perform r_serve action with any parameter of sort sort_choice,

% followed by r_return action with any natural valued parameter

43.

s\_coin(5) \cdot User(state) +

44.

s\_coin(10) \cdot User(state) +

45.

46.

s\_coin(20) \cdot User(state) +

\sum_{drink: sort\_choice} r\_serve(drink) \cdot \sum_{remainder: \mathbb{N}} r\_return(remainder) \cdot

47.

48.

User(ready)

);

49.

50.

51. % line 52-65 define the initial state of the complete model

52. init

% line 53 uses the restriction operator to allow only c<sub>-</sub> actions and prepare

53.

\nabla_{\{c\_choose\_tea,c\_choose\_coffee,c\_choose\_water,c\_coin,prepare,c\_serve,c\_return\}} (

% line 55-60 uses the communication operator to specify the communications

54.

55.

\Gamma_{\{r\_choose\_tea|s\_choose\_tea\rightarrow c\_choose\_tea,\}}

56.

r\_choose\_coffee | s\_choose\_coffee \!\rightarrow\! c\_choose\_coffee,

57.

r\_choose\_water|s\_choose\_water {\rightarrow} c\_choose\_water,

58.

r\_coin | s\_coin \rightarrow c\_coin,

59.

r\_serve | s\_serve \rightarrow c\_serve,

60.

r\_return | s\_return \rightarrow c\_return \}

% line 63 and 64 give the initial states of the individual processes

61.

% parallel composition (||) is used to place the processes in parallel

62.

63.

Machine(start, tea, 0)

User(ready)

64.

));

65.

```

#### 2.1.2 Modal $\mu$ -calculus

The mCRL2 model checking tools accept properties that are formulated in the modal  $\mu$ -calculus, which is an extension to the Hennessy-Milner logic as described in section 2.0.2. Although the Hennessy-Milner logic with regular expressions is already very expressive and most behavioral properties can be specified in this logic, the modal  $\mu$ -calculus is even more expressive through the addition of minimal and maximal fixed point operators. However, this addition also makes it rather difficult to formulate correct properties in the modal  $\mu$ -calculus. Note that all formulas in the Hennessy-Milner logic can also be used in mCRL2, because this logic is a true subset of the modal  $\mu$ -calculus. We give a brief introduction of the modal  $\mu$ -calculus for the interested reader.

The syntax of the modal  $\mu$ -calculus is as follows:

$$\phi ::= true \mid false \mid \neg \phi \mid \phi \land \phi \mid \phi \lor \phi \mid \phi \rightarrow \phi \mid \langle a \rangle \phi \mid [a]\phi \mid \mu X.\phi \mid \nu X.\phi \mid X.$$

The formula  $\mu X.\phi$  is the minimal fixed point and  $\nu X.\phi$  is the maximal fixed point. X is just a variables which is typically used in fixed points together with other capitals Y,Z,... A fixed point  $\mu X.\phi$  or  $\nu X.\phi$  only exists if X occurs positively in  $\phi$ , meaning that X in  $\phi$  must be preceded by an even number of negations. For counting negations  $\phi_1 \to \phi_2$  should be read as  $\neg \phi_1 \lor \phi_2$ . So, for instance  $\nu X.\neg X$  and  $\nu X.\neg([a]\neg X\lor X)$  are not allowed; in the first formula X occurs with one preceding negation, in the second formula only the former occurrence of X is fine because it is preceded by two negations.

To understand fixed point modalities it is useful to consider X as a set of states. Formula  $\mu X.\phi$  is valid for all states in the smallest set X that satisfies the equation  $X=\phi$ , where X generally occurs in  $\phi$ . Here we abuse notation, by thinking of  $\phi$  as the set of states where  $\phi$  is valid. Similarly,  $\nu X.\phi$  is valid for the states in the largest set X that satisfies  $X=\phi$ . As an example we can look at two simple fixed point formulas  $\mu X.X$  and  $\nu X.X$ . Because  $\phi=X$ , we are interested in the smallest and largest set of states X that satisfies the equation X=X, respectively. Of course every set satisfies this equation. Hence, the smallest set to satisfy it, is the empty set. This means that  $\mu X.X$  is not valid in any state, which is equivalent to saying that  $\mu X.X = false$ . The largest set X that satisfies X=X is the set of all states, so  $\nu X.X$  is valid in all states which means that  $\nu X.X = true$ .

As another example we look whether the formulas  $\mu X.\langle a \rangle X$  and  $\nu X.\langle a \rangle X$  are valid in the following transition system:

The only sets of states to be considered are the empty set  $X = \emptyset$  and the set of all states  $X = \{s\}$ . Both satisfy the 'equation'  $X = \langle a \rangle X$ . Namely, if  $X = \emptyset$ , then the equation reduces to  $false = \langle a \rangle false$ , which is valid. If  $X = \{s\}$  it is also clear that this equation holds. So,  $\mu X.\langle a \rangle X$  is valid for all states in the empty set. Hence, this formula is not valid in s. However,  $\nu X.\langle a \rangle X$  is valid for all states in the largest set, being  $\{s\}$  in this case. So,  $\nu X.\langle a \rangle X$  is valid.

This example concludes our small introduction to modal  $\mu$ -calculus. For more details, see [11].

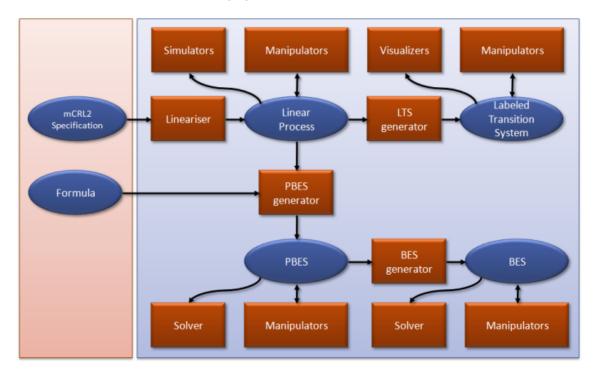

#### 2.1.3 mCRL2 toolset

Now we have seen the basics of both the mCRL2 process specification language and the property language modal  $\mu$ -calculus. Using these two languages as recipes one could specify a formal model of the considered system and a property of the system that must be verified by means of model checking. Model checking is one of the purposes of the mCRL2 toolset, but besides that the toolset can be also be used to analyze and explore the model by simulation and visualization of the model's state space. Furthermore the toolset contains tools to optimize the model automatically. It should be noted that the toolset is subject to continuously development; here we give a description of the toolset version (SVN revision 3626) that we have used in this project.

Figure 2.5 gives an overview of the use of the mCRL2 toolset. On the left the figure shows the inputs of the toolset, which are a model of a system expressed in the mCRL2 language and possibly a formula that must be verified. The first step in model analysis is always the generation of a Linearized Process Specification (LPS) for the model by using the linearizer tool mcrl22lps. This tool first performs a syntax check and then starts the linearization, which can be seen as compiling the model to a more strict format that is well suited for analysis and manipulation by the tools in the toolset. An LPS can be seen as a symbolic representation of the transition system of a model. For more information about linearizing mCRL2 process specifications, see [10].

Figure 2.5: Overview of the mCRL2 toolset (picture taken from [2])

An LPS is unreadable for humans, but sometimes it is needed to inspect the LPS. For this purpose the toolset contains a tool to pretty print the LPS and a tool which provides some basic information about the LPS (these tools are not present in figure 2.5). This basic information contains for example the number of summands in the LPS, which is often indicative for the size of the model's state space. The LPS can be optimized by some manipulator tools; there is a tool for removing process parameters which are constant in the (reachable) state space, a tool for removing unused process parameters, and a rewriting tool. This rewriting tool evaluates conditions in the LPS by rewriting and then decides which alternatives are unused and can be removed. These optimization tools can have a substantial effect on the final size of the state space and/or the resources needed for the generation of the state space.

Besides these manipulator tools there is a simulator tool available which can be used to get more insight in a model without generating its state space. The user explores the model with this tool by manually performing individual (multi)actions. After an action has been performed the simulator shows a representation of the new state (a state vector), and the actions that are possible from this state. The simulator also offers the ability to save action

traces and load them again on a future moment.

To generate the state space from an LPS the tool lps2lts can be used. This tool generates a Labeled Transition System (LTS) that represents the complete behavior of the model. On the LTS the manipulator tool ltsconvert can be used to convert between different formats of LTSs and to minimize the state space modulo (branching) bisimulation equivalence. This minimization is effective when several internal actions are hidden (abstraction) in the model. For example, if the state space contains a sequence of internal actions, this sequence can be collapsed in many cases. Then all intermediate states in the sequence are removed, which leads to a smaller state space. Furthermore there are several tools to visualize the state space, which again can help in finding specification errors or in getting more insight in the model.

When analysis and simulation show that the formal model conforms to the modeled system well enough, one can start model checking. Model checking in mCRL2 is provided using Parameterized Boolean Equation Systems (PBES), which can be generated by the tool 1ps2pbes from an LPS and a modal  $\mu$ -calculus formula. For PBESs there is again a tool to print it in human readable format and using pbes2bes one can try to remove data from the PBES in order to get a BES, which is often easier to solve. The actual model checking can be done by the tool pbes2bool, which internally uses pbes2bes and then solves the BES by rewriting the boolean equations in the BES. If requested, the tool returns a trace that indicates how pbes2bool came to the validity or invalidity of the PBES. Such a trace can again be useful to improve the model or the modeled system itself.

This description of the mCRL2 toolset concludes the introduction to mCRL2. In later chapters we will see how mCRL2 can be useful in formal modeling the pacemaker firmware design and in verification of the resulting models.

#### 2.2 Uppaal

UPPAAL is an integrated tool environment for modeling, validation and verification of realtime systems. The tool has been developed in collaboration between the Department of Information Technology at Uppsala University, Sweden and the Department of Computer Science at Aalborg University in Denmark; the tool is available at [3]. In this project, we have used version 4.0.6 of UPPAAL. Based on [4], this section gives an introduction to UPPAAL.

In UPPAAL it is possible to model the behavior of real-time systems as concurrent processes via a (Java-based) graphical interface. The tool contains a graphical simulator which constantly shows the actual state of the model and enables the user to explore the possible executions of the model by manually performing actions. During the design or modeling of the system this can provide useful information to improve the model or the modeled system itself. Then there is the model checker which covers the complete behavior of the system by exploring all possible executions. The model checker can check invariant properties (properties that must hold in every reachable state of the model) and reachability properties (properties that must hold in at least one reachable state of the model) that are formulated in (temporal) logic.

#### 2.2.1 Timed automata

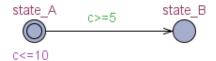

UPPAAL is designed to verify systems that can be modeled as a composition of *timed automata*. Timed automata are especially useful to model components of real-time systems. A timed automaton is a finite state machine extended with clock variables which evaluate to a

nonnegative real number. The timed automata in a model and the way they interact with each other together define a *timed transition system*. Besides ordinary action transitions that can represent input, output and internal actions, a timed transition system has time passage transitions. Such time passage transitions result in synchronous progress of all clock variables in the model. This makes it possible to base decisions on the moment in time on which they are taken, which is done by so-called clock constraints. A clock constraint depends on one or more clock values and can either be an invariant of a component state (defining the time period(s) in which the component may reside in this state) or a guard on a transition (defining under which time conditions this transition may be taken).

Figure 2.6 shows a timed transition system that consists of one process. We see that state\_A has an invariant, which is a clock constraint specifying that the clock variable c may be at most 10 in that state. Furthermore, the transition to state\_B has a guard, which is a clock constraint specifying that this transition may only be taken if c is at least 5. Because state\_A is the initial state of this process (indicated by the double circle) and c is initialized to 0 (clock variables are always initialized to 0), the system first performs a time passage action in state\_A through which time passes by any value between 5 and 10. After this time passage action the value of c has been increased to a value between 5 and 10, hence the system can perform the ordinary transition to state\_B.

Figure 2.6: Example of time passage action

[5] contains a useful description of the formal semantics of timed automata and of algorithms and tools that are developed to analyze and verify timed automata.

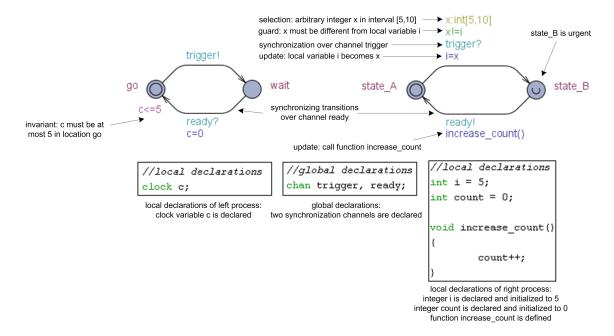

#### 2.2.2 Model specification

In UPPAAL, timed automata are specified as graphs by putting locations, and edges between those locations, onto a worksheet and by editing the special properties of the locations and edges. Note that UPPAAL depicts process states as locations and process transitions as edges to make clear the difference with the state of the complete system and a transition in the system.

Besides clock variables, an UPPAAL model can contain bounded discrete variables that are part of the system state. These variables are used as in programming languages: they are read, written, and are subject to common arithmetic operations.

In the model, one can declare local constants, variables and functions for each process and global constants, variables and functions, which can be used by all processes. UPPAAL provides predefined types for these constants and variables: integers, booleans and clocks and also custom types can be used, including (multidimensional) arrays, records, and structured types. The notational style of the declarations is based on that of C.

A state of the system is defined by the locations of all automata, the clock constraints, and the values of the discrete variables. The system as a whole moves to another state in three cases: if a time passage action is performed in the complete system (which increases all clock values with the same value and possibly changes the truth value of the clock constraints),

if an (ordinary) action is performed by one of the automata, and if two (or more) different automata synchronize over a channel, which means that transitions of these automata are performed in parallel.

The behavior of each individual automaton is defined by the locations and the edges of the automaton and their (optional) properties. We first describe the properties of edges:

- Selection: Selections non-deterministically bind a given identifier to a value in a given range. The other three properties of an edge are within the scope of this binding. It is also possible to bind multiple identifiers. This mechanism corresponds to quantifying over a data type.

- **Guard**: An edge is *enabled* in a state if and only if the guard evaluates to true. A guard must be a conjunction of simple conditions on clocks, differences between clocks, and boolean expressions not involving clocks. The bound must be given by an integer expression.

- Synchronization: Processes can synchronize over channels. The channel, on which there is communication, must be globally declared. The intuition is that two processes can synchronize on enabled edges annotated with complementary synchronization labels, i.e. two edges in different processes can synchronize if the guards of both edges are satisfied, and they have synchronization labels e1? and e2! respectively, where e1 and e2 evaluate to the same channel. When two processes synchronize, both edges are fired at the same time, i.e. the current location of both processes is changed. The update expression on an edge synchronizing on e1! is executed before the update expression on an edge synchronizing on e2?.

It's also possible to define a channel as a broadcast channel. On a broadcast channel there can be multiple receivers synchronizing with one sender.

• **Update**: When executed, the update expression of the edge is evaluated. The side effect of this expression changes the state of the system. An update expression can consist of variable assignments and function calls.

Locations can have the following (optional) properties:

- Name: a unique name of the location. Necessary when a location must be referenced in a property (which is verified by model checking).

- Invariant: constraint on clock variables that must always hold when the timed automaton is in this location. System states which violate the invariants of locations are undefined; by definition, such states do not exist. An invariant is an expression that satisfies the following conditions: it is side-effect free; only clock, integer variables, and constants are referenced; it is a conjunction of conditions of the form x < e or  $x \le e$  where x is a clock reference and e evaluates to an integer.

- **Initial**: boolean property that indicates whether or not the location is the initial location of the process.

- **Urgent**: boolean property that indicates whether or not a location is 'urgent'. Urgent locations are semantically equivalent to adding an extra clock x, that is reset on all

incoming edges, and having an invariant  $x \leq 0$  on the location. Hence, time is not allowed to pass when the system is in an urgent location.

• Committed: boolean property that indicates whether or not a location is 'committed'. Committed locations are even more restrictive on the execution than urgent locations. The system state is committed if any of the locations in the state is committed. A committed state cannot delay and the next transition must involve an outgoing edge of at least one of the committed locations.