#### MASTER

Comparison of computer architectures and design of a multi-core solution for an industrial control application

Brondsema, Y.W.

Award date: 2011

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

#### **Eindhoven University of Technology**

Department of Electrical Engineering Master's Thesis Report

# Comparison of computer architectures and design of a multi-core solution for an industrial control application

Yoran W. Brondsema

Supervised by Prof. M.C.W. Geilen, Eindhoven University of Technology Micha Nelissen, Prodrive BV

# Comparison of computer architectures and design of a multi-core solution for an industrial control application

Son, August 26, 2011

| Course<br>Master      | : Graduation project<br>: Embedded Systems                                               |                                                                       |

|-----------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Department<br>Faculty | : Electrical Engineering - Eindhoven Univers<br>: Embedded Systems - Eindhoven Universit |                                                                       |

| Supervisors           | : For Eindhoven University of Technology:<br>Prof. M.C.W. Geilen                         | TU/e Technische Universiteit<br>Eindhoven<br>University of Technology |

|                       | For Prodrive B.V.:<br>Micha Nelissen                                                     | <u>- PRODRIVE</u>                                                     |

| Author                | : Yoran W. Brondsema<br>Runstraat 28<br>5622 AZ Eindhoven<br>The Netherlands             |                                                                       |

#### Copyright 2011 Prodrive B.V.

All rights are reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted , in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission from the copyright owner.

Prodrive B.V. P.O. Box 28030 Science Park 5501 5692 EM Son The Netherlands ☎ +31 (0)40 2676 200 ➡ +31 (0)40 2676 201 ➡ http://www.prodrive.nl ⊠ info@prodrive.nl Eindhoven University of Technology Den Dolech 2 5612 AZ Eindhoven The Netherlands ☎ +31 (0)40 247 47 47 ☜ http://www.tue.nl ⊠ info@tue.nl

# Abstract

The purpose of this study is to investigate on the implementation of an industrial control system on various computer architectures. The system under consideration consists of two applications: the host and the HPPC application. The host application is responsible for the configuration and the control of the system while the HPPC application implements the control loop, i.e. it calculates the new set points for the actuators based on the sensor data. The objective of the first part of the study was to make a comparison of the performance of the two applications on different general-purpose processors. The choice for the processors was based on three criteria. First, the owner of the system was interested in a comparison of PowerPC and Intel processors in order to help determining their long-term roadmap. Secondly, the processors were chosen such that they represent a wide spectrum in the power-performance range. Thirdly, due to practical availability, we could only effectively benchmark four processors. For the host application, several benchmarks were selected to measure the performance of the memory hierarchy, the integer performance and the floating-point performance. To investigate the performance of the HPPC application, a model that simulates its computational behaviour was used as a benchmark. The results of the performance measurements revealed that both applications achieve their highest performance on an Intel Nehalem architecture. However, non-performance related criteria like power consumption, documentation and availability favour a PowerPC processor. Therefore, the owner of the system must evaluate the importance of the different criteria in order to make a decision.

The second part of the thesis investigates the implementation of the HPPC application on a multi-core platform. The first reason for an evolution to a multi-core platform is an increase in performance demanded from the hardware as the complexity of the application increases and the timing requirements become more stringent. Secondly, there is a demand to reduce the number of processor boards necessary to implement the system. By using multi-core processors, it is possible to combine several single-core boards onto a single board. First, two different alternatives for a mapping of tasks to cores were compared. Their performance was compared based on the amount of overhead that they introduce. Experimental measurements of the latencies of the different components of the overhead indicate that one of the alternatives offers more performance than the other. Next, using a model of its computational behaviour, the scalability of the performance of the application was analysed. It shows that, assuming a perfect division of the application over the cores, it scales in a supra-linear way. Lastly, the thesis investigates the usage of barriers as a synchronization mechanism between tasks executing on separate cores. Two different implementations of a barrier were proposed and their overhead was measured for the worst-case scenario. The results of these

measurements will guide the task of parallelizing the application into threads that can be executed on separate cores. In overall, the study revealed that the HPPC application has the potential to be parallelized in an efficient way.

# Acknowledgements

This thesis is the result of my graduation project which completes my master in Embedded Systems at the Eindhoven University of Technology. The project was performed within Prodrive BV, a company that I got to know via the recruitment days at the university and where I worked part-time prior to this master project.

First of all, I would like to thank Prodrive for giving me the opportunity to perform my master thesis project here. I would like to thank them for providing me with the topic of this thesis. It is not easy to come up with a subject for a thesis and I want to thank Roel Loeffen for introducing me to this interesting topic.

Next, I want to thank Steven, Eric and Micha for their guidance throughout the project. When I talk to my fellow students from the master's project, I realise that the guidance and supervision at Prodrive is very good compared to some other companies. Combined with the opportunity to work on interesting thesis topics, I can conclude that Prodrive is an excellent company for a student to perform his master thesis.

I would like to thank Nikola for helping me defining the outline and the goals of my thesis, for being a guide to the system and for answering my numerous questions. I also want to thank Jeroen for providing technical help. Along with them, I want to thank Jan, Erik and John for their input during the many meetings that we had.

Also, I would very much like to thank Marc Geilen, my supervisor at the university. He dedicated much time and attention to my project. Furthermore, his extensive and detailed feedback during our regular meetings was very helpful.

I want to thank Levent very much for our friendship during the whole master's program. He has been an amazing friend and I hope that, although I am sure that it will be the case, our friendship will last even after the Eindhoven era.

Finally, I want to warmly thank my mother, my father and my sister for everything they have done for me. I know that they want the best for me and their support has been very important for me. It is comforting to have a warm home to fall upon when things go less well.

# Contents

| At  | ostrac             | ct                                                     | i    |

|-----|--------------------|--------------------------------------------------------|------|

| Ac  | knov               | wledgements                                            | iii  |

| Lis | st of I            | Figures                                                | viii |

| Lis | st of <sup>·</sup> | Tables                                                 | xi   |

| 1   | Intro              | oduction                                               | 1    |

|     | 1.1                | Motivation                                             | 1    |

|     | 1.2                | Problem statement                                      | 2    |

|     | 1.3                | Thesis outline                                         | 3    |

| 2   | Ove                | erview of the applications                             | 5    |

|     | 2.1                | The HPPC application                                   | 5    |

|     |                    | 2.1.1 Structure of the application                     | 5    |

|     |                    | 2.1.2 Software implementation                          | 6    |

|     | 2.2                | The host application                                   | 7    |

|     | 2.3                | Relationship between the host and the HPPC application | 7    |

|     | 2.4                | Hardware implementation                                | 8    |

| 3   | Des                | cription of the architectures                          | 9    |

|     | 3.1                | Factors of performance                                 | 9    |

|     |                    | 3.1.1 Clock frequency                                  | 10   |

|     |                    | 3.1.2 Memory hierarchy                                 | 10   |

|     |                    | 3.1.3 Instruction-level parallelism                    | 11   |

|     |                    | 3.1.4 SIMD architectures                               | 12   |

|     |                    | 3.1.5 Simultaneous multithreading                      | 12   |

|     |                    | 3.1.6 Multi-core architectures                         | 12   |

|     | 3.2                | Candidate hardware architectures                       | 13   |

|     |                    | 3.2.1 Intel Atom Z530                                  | 14   |

|     |                    | 3.2.2 PowerPC MPC8548                                  | 16   |

|     |                    | 3.2.3 PowerPC P4080                                    | 17   |

#### CONTENTS

|   |     | 3.2.4 PowerPC P5020                                   | 20 |

|---|-----|-------------------------------------------------------|----|

|   |     | 3.2.5 Intel Xeon E5540                                | 21 |

|   |     | 3.2.6 Cell processor                                  | 25 |

|   |     | 3.2.7 Digital signal processor                        | 27 |

|   | 3.3 | Architectures to be benchmarked                       | 31 |

|   | 3.4 | A first comparison                                    | 32 |

|   |     | 3.4.1 Power consumption                               | 32 |

|   |     | 3.4.2 Platform documentation                          | 32 |

|   |     | 3.4.3 Duration of supply                              | 33 |

| 4 | Ben | chmarks for the host application                      | 35 |

|   | 4.1 | Characteristics of the host application               | 35 |

|   | 4.2 | Micro- and macro-benchmarks                           | 35 |

|   | 4.3 | Benchmarking methodology                              | 36 |

|   |     | 4.3.1 Micro-benchmark                                 | 36 |

|   |     | 4.3.2 Macro-benchmark                                 | 36 |

|   | 4.4 | Performance of the memory hierarchy                   | 37 |

|   |     | 4.4.1 Memory read latency                             | 37 |

|   |     | 4.4.2 Memory bandwidth                                | 40 |

|   |     | 4.4.3 Memory bandwidth: expectations                  | 41 |

|   |     | 4.4.4 Memory bandwidth: assessing the expectations    | 43 |

|   |     | 4.4.5 Memory bandwidth: conclusion                    | 47 |

|   | 4.5 | Integer and floating-point performance                | 49 |

|   |     | 4.5.1 Integer performance                             | 49 |

|   |     | 4.5.2 Floating-point performance                      | 50 |

|   | 4.6 | Conclusion                                            | 52 |

|   | 4.7 | Future work                                           | 53 |

| 5 | Ben | chmarks for the HPPC application                      | 55 |

|   | 5.1 | Model of the HPPC application                         | 55 |

|   |     | 5.1.1 Introduction                                    | 55 |

|   |     | 5.1.2 Arithmetic intensity                            | 56 |

|   |     | 5.1.3 Analysis of the test application on the MPC8548 | 57 |

|   |     | 5.1.4 Conclusion                                      | 60 |

|   | 5.2 | Benchmarking methodology                              | 60 |

|   | 5.3 | Expected results                                      | 62 |

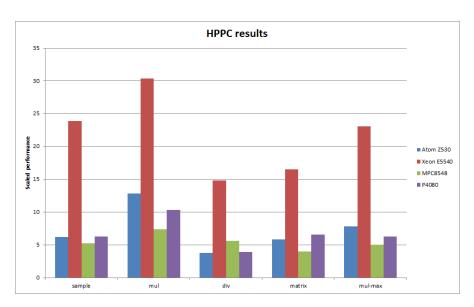

|   | 5.4 | Results                                               | 63 |

|   | 5.5 | Conclusion                                            | 65 |

|   | 5.6 | Future work                                           | 66 |

| 6 | Por   | ting the HPPC application to a multi-core platform | 67  |

|---|-------|----------------------------------------------------|-----|

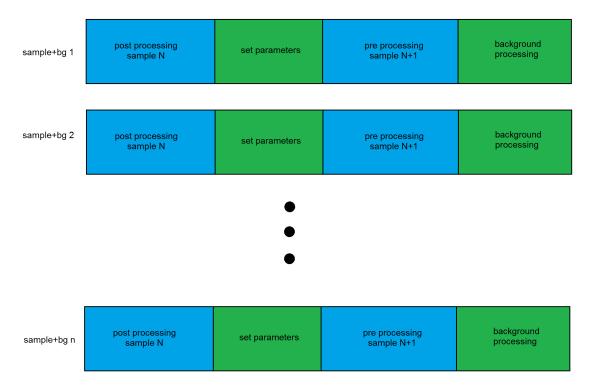

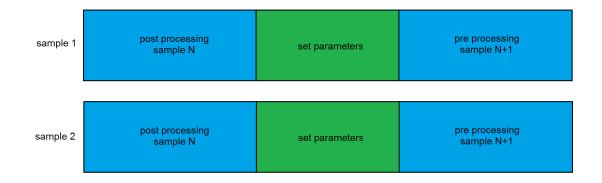

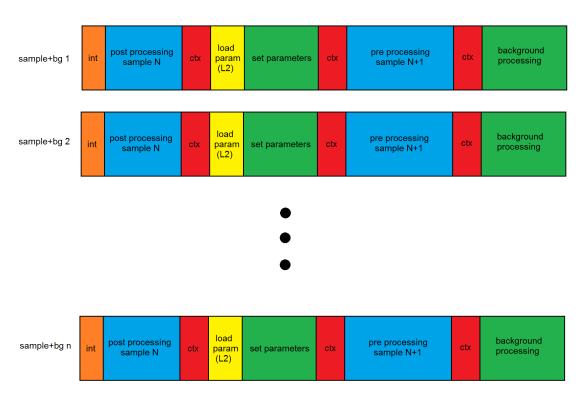

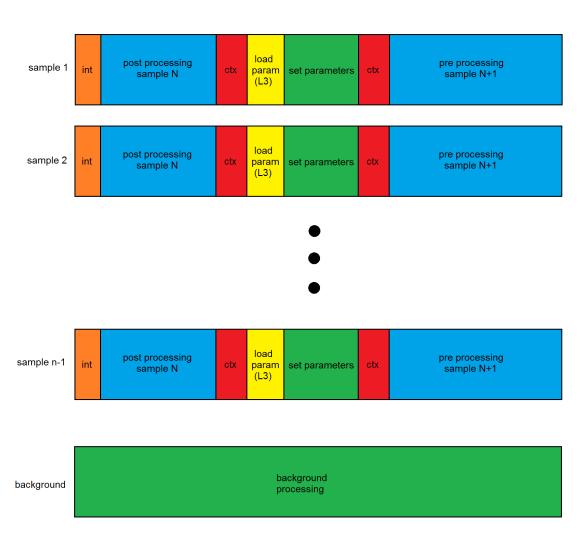

|   | 6.1   | Two alternatives for a mapping                     | 67  |

|   |       | 6.1.1 Introduction                                 | 67  |

|   |       | 6.1.2 Parallelizing the application                | 69  |

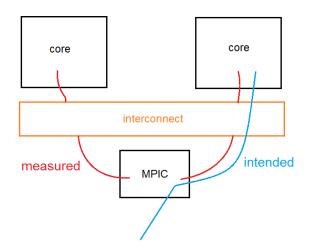

|   | 6.2   | Measurements of the overheads                      | 72  |

|   |       | 6.2.1 Introduction                                 | 72  |

|   |       | 6.2.2 Environment of the measurements              | 73  |

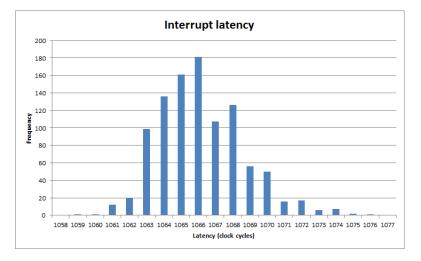

|   |       | 6.2.3 Interrupt latency                            | 74  |

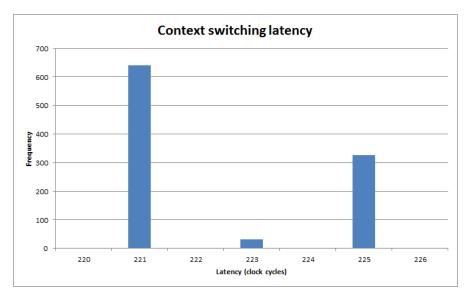

|   |       | 6.2.4 Context switching latency                    | 77  |

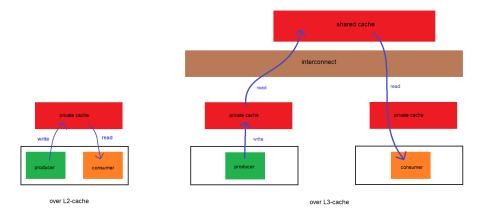

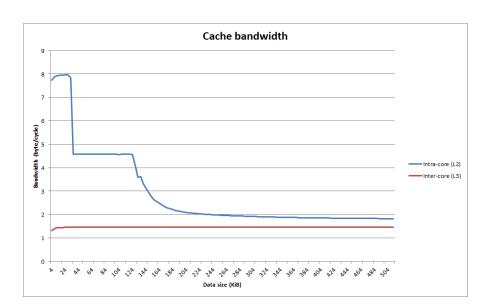

|   |       | 6.2.5 Cache bandwidth                              | 78  |

|   | 6.3   | Comparison of the two solutions                    | 79  |

|   | 6.4   | Scalability of the sample task                     | 82  |

|   | 6.5   | Synchronization on the P4080                       | 85  |

|   |       | 6.5.1 Barrier as a synchronization mechanism       | 85  |

|   |       | 6.5.2 Overhead of a barrier                        | 87  |

|   |       | 6.5.3 Busy-waiting and interrupt-based waiting     | 93  |

|   | 6.6   | Conclusion                                         | 95  |

|   | 6.7   | Future work                                        | 96  |

| 7 | Con   | nclusion                                           | 97  |

|   | 7.1   | Comparison of processors                           | 97  |

|   | 7.2   | The HPPC application on a multi-core platform      | 98  |

| 8 | Fut   | ure work                                           | 101 |

| G | ossa  | ıry                                                | 103 |

| A | crony | /ms                                                | 105 |

# **List of Figures**

| 1.2  | Diagram of an ATCA shelf.                                          | 2  |

|------|--------------------------------------------------------------------|----|

| 2.1  | Structure of a HPPC application.                                   | 6  |

| 2.2  | Relationship between the host and the HPPC modules.                | 8  |

| 3.1  | '                                                                  | 10 |

| 3.2  | Mechanism of simultaneous multithreading                           | 13 |

| 3.3  | Diagram of an SMP system [4]                                       | 13 |

| 3.4  | Architecture of the Intel Atom core                                | 15 |

| 3.5  | Architecture of the e500v2 core in the MPC8548                     | 17 |

| 3.6  | Architecture of the P4080 SoC                                      | 18 |

| 3.7  | Architecture of the e500mc core in the P4080.                      | 19 |

| 3.8  | Architecture of the P5020 SoC                                      | 21 |

| 3.9  | Architecture of the e5500 core in the P5020.                       | 22 |

| 3.10 | Architecture of the Intel Xeon E5540 processor.                    | 23 |

| 3.11 | Architecture of the Intel Xeon E5540 execution pipeline.           | 24 |

| 3.12 | Architecture of the Cell processor.                                | 28 |

| 3.13 | Architecture of the PPE in the Cell processor.                     | 29 |

| 3.14 | Architecture of an SPE in the Cell processor.                      | 30 |

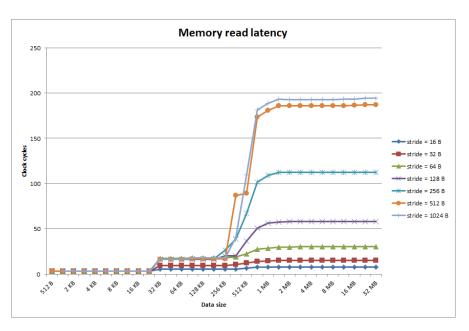

| 4.1  | , , , , , , , , , , , , , , , , , , ,                              | 38 |

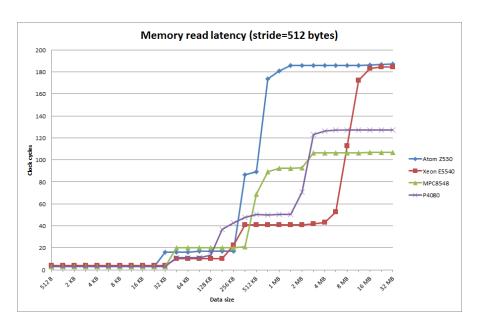

| 4.2  | Results of the memory read latency benchmark for all architectures | 39 |

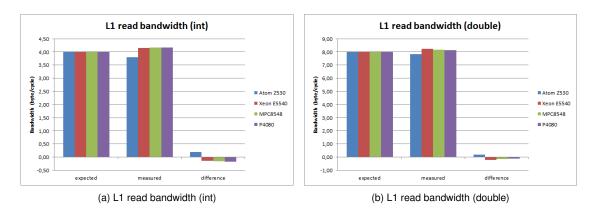

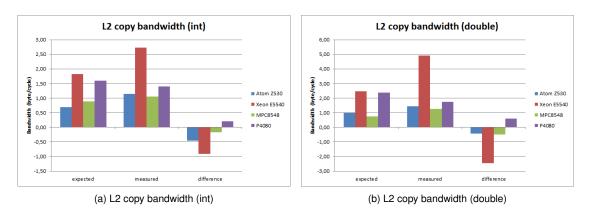

| 4.3  | Bandwidth results of the L1 cache for the read operation           | 44 |

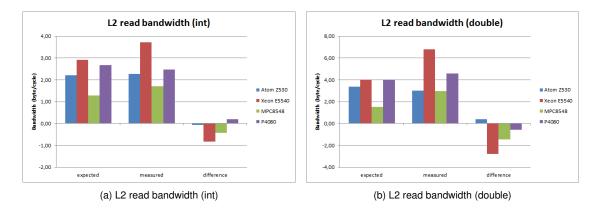

| 4.4  |                                                                    | 44 |

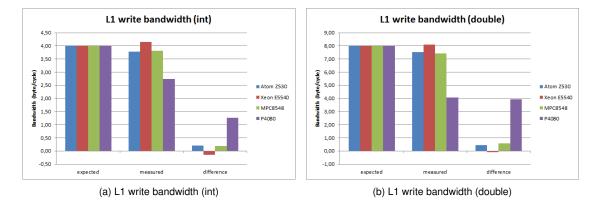

| 4.5  | Bandwidth results of the L1 cache for the write operation.         | 45 |

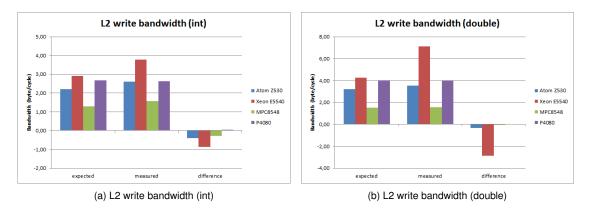

| 4.6  | Bandwidth results of the L2 cache for the write operation.         | 45 |

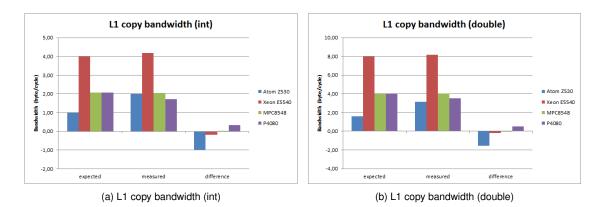

| 4.7  | Bandwidth results of the L1 cache for the copy operation.          | 46 |

| 4.8  | Bandwidth results of the L2 cache for the copy operation.          | 47 |

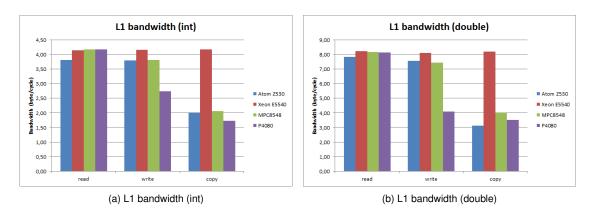

| 4.9  | L1 bandwidth results.                                              | 48 |

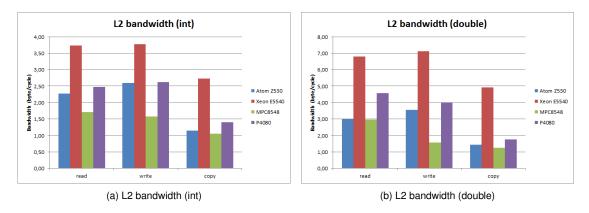

| 4.10 | L2 bandwidth results.                                              | 48 |

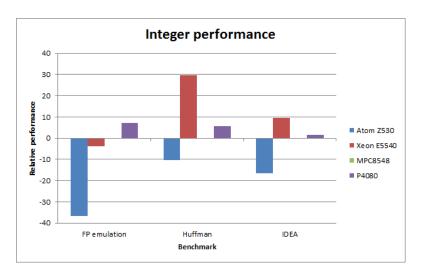

| 4.11 | Results of the benchmarks for the integer performance.             | 50 |

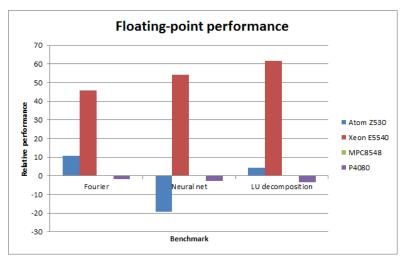

| 4.12 | Results of the benchmarks for the floating-point performance                         | 51         |

|------|--------------------------------------------------------------------------------------|------------|

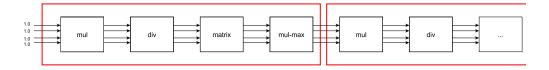

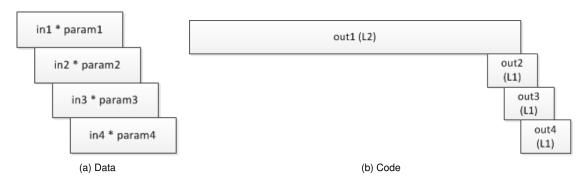

| 5.1  | Model for the sample task of the HPPC application.                                   | 56         |

| 5.2  | Model for the sample task of the HPPC application.                                   | 59         |

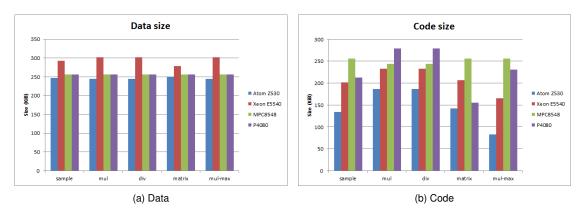

| 5.3  | Data and code sizes of the benchmark applications on the different platforms.        | 60         |

| 5.4  | Data and code sizes of the benchmark applications on the different platforms.        | 61         |

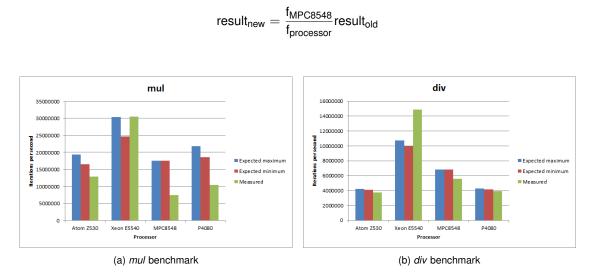

| 5.5  | Comparison of the expected results with the measured results for the mul and div     |            |

|      | benchmarks                                                                           | 63         |

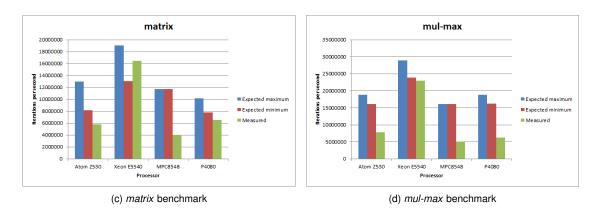

| 5.5  | Comparison of the expected results with the measured results for the matrix and mul- |            |

|      | max benchmarks                                                                       | 64         |

| 5.6  | Results of the benchmarks for the sample task                                        | 65         |

|      |                                                                                      | ~~         |

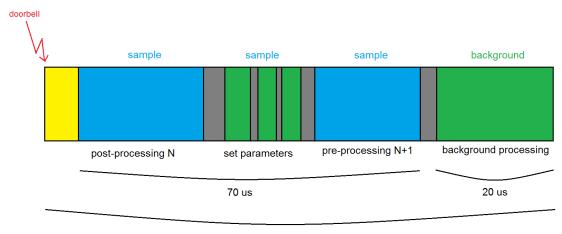

| 6.1  | Timing details of the current implementation of the HPPC application.                | 68<br>70   |

| 6.2  | Illustration of the first solution.                                                  | 70<br>71   |

| 6.3  | Illustration of the second solution.                                                 | 71         |

| 6.4  | Overheads involved in solution 1                                                     | 73         |

| 6.5  | Overheads involved in solution 2                                                     | 74         |

| 6.6  | Illustration of the interrupt mechanism.                                             | 75         |

| 6.7  | Histogram of the interrupt latency.                                                  | 76         |

| 6.8  | Histogram of the context switching latency.                                          | 77         |

| 6.9  | Setup for the measurement of the cache bandwidth.                                    | 78         |

|      | Results of the cache bandwidth.                                                      | 79         |

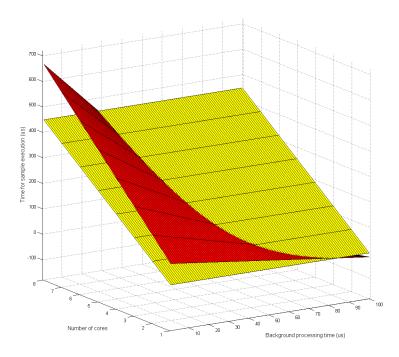

| 6.11 | Sample execution time in function of the number of cores and the background pro-     | <b>.</b> . |

|      | cessing time.                                                                        | 81         |

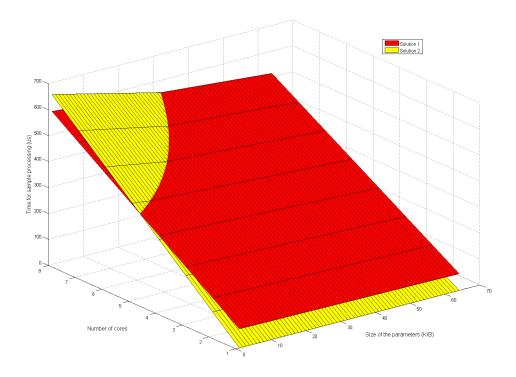

| 6.12 | 2 Sample execution time in function of the number of cores and the data size for the |            |

|      | parameters.                                                                          | 82         |

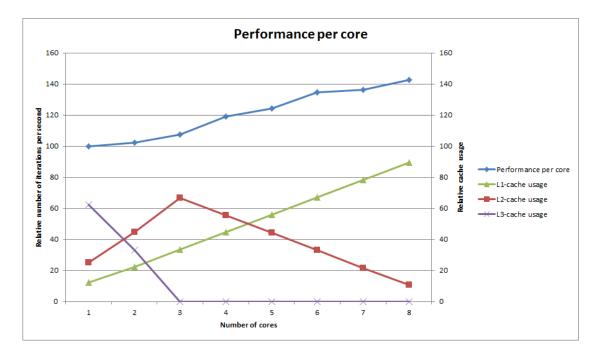

|      | B Division of the 2516 code blocks among 2 cores.                                    | 83         |

|      | Scalability of the sample task.                                                      | 84         |

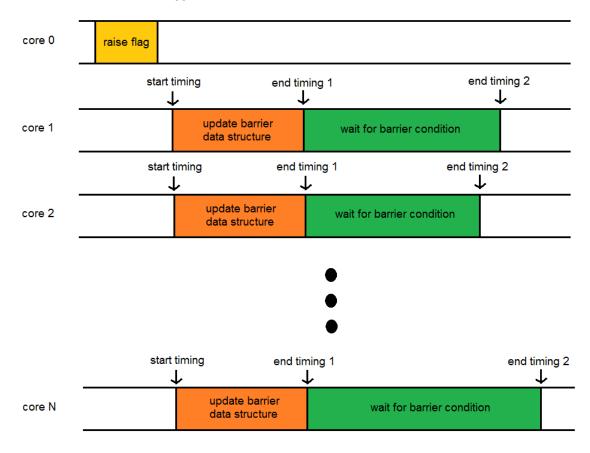

|      | Experimental setup for the measurement of the overhead introduced by a barrier       | 88         |

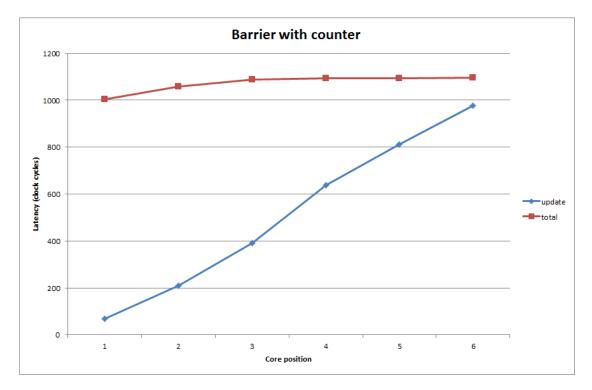

|      | Results of the barrier overhead for the implementation with a counter                | 90         |

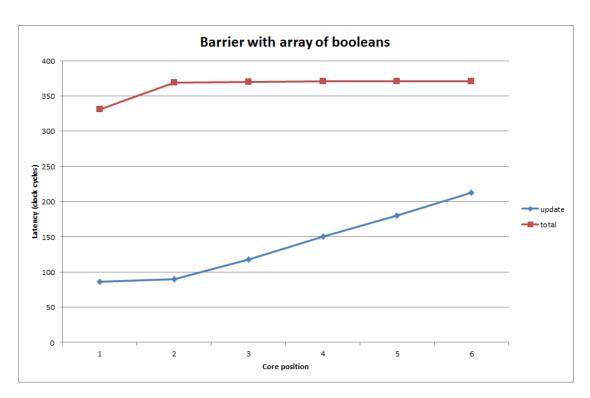

|      | Results of the barrier overhead for the implementation with an array of booleans     | 92         |

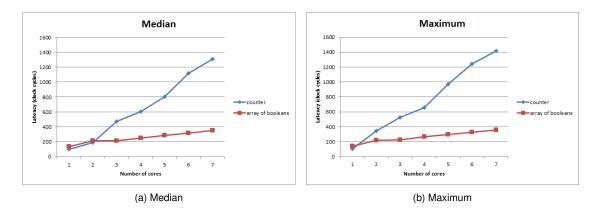

|      | B Comparison of the two implementations of a barrier.                                | 93         |

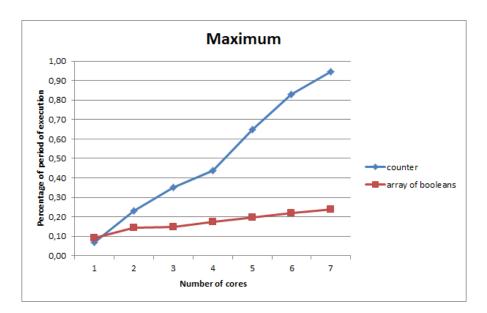

|      | Relative overhead introduced by a barrier in the application.                        | 94         |

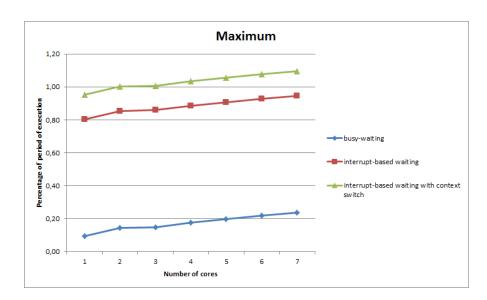

| 6.20 | O Comparison of busy-waiting and interrupt-based waiting.                            | 95         |

# **List of Tables**

| 3.1  | Important characteristics of the benchmarked architectures                                | 31 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.2  | TDP values of the various processors                                                      | 32 |

| 4.1  | Results of the cache latencies.                                                           | 39 |

| 4.2  | Estimated bandwidth for the read operation in bytes per cycle                             | 41 |

| 4.3  | Estimated bandwidth for the write operation in bytes per cycle                            | 42 |

| 4.4  | Estimated bandwidth for the copy operation in bytes per cycle                             | 43 |

| 4.5  | Comparison of the estimated bandwidths and the measured bandwidths for the read           |    |

|      | operation                                                                                 | 44 |

| 4.6  | Comparison of the estimated bandwidths and the measured bandwidths for the write          |    |

|      | operation                                                                                 | 46 |

| 4.7  | Comparison of the estimated bandwidths and the measured bandwidths for the copy           |    |

|      | operation.                                                                                | 47 |

| 4.8  | Results of the benchmarks for the integer performance                                     | 49 |

| 4.9  | Results of the benchmarks for the floating-point performance                              | 51 |

| 4.10 | Timings for the floating-point instructions.                                              | 52 |

| 4.11 | Final comparison of the four benchmarked architectures                                    | 53 |

| 5.1  | Description of the different types of blocks in the simulation application for the sample |    |

|      | task                                                                                      | 56 |

| 5.2  | Operations performed by the types of blocks in the simulation application for the sam-    |    |

|      | ple task.                                                                                 | 57 |

| 5.3  | Instruction timings of the MPC8548.                                                       | 58 |

| 5.4  | Arithmetic intensity of the different types of blocks                                     | 59 |

| 5.5  | Sizes of the benchmarks on the MPC8548                                                    | 61 |

| 5.6  | Expected performance on the four different types of blocks.                               | 62 |

| 5.7  | Results of the benchmarks for the sample task                                             | 64 |

| 6.1  | Intersection points between solution 1 and solution 2                                     | 80 |

| 6.2  | Example of the utilization of a barrier.                                                  | 85 |

| 6.3  | Two ways of implementing a barrier.                                                       | 86 |

| 6.4  | Necessity of atomic operations                                                            | 87 |

## **Chapter 1**

# Introduction

### 1.1 Motivation

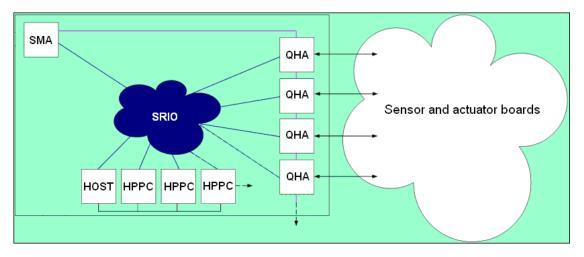

Figure 1.1: Overview of the system

One of Prodrive's clients currently has a platform that was designed to run a control loop. It is based on the Advanced Telecommunications Computing Architecture (AdvancedTCA), Serial RapidIO (SRIO) and the PowerPC architecture. An overview of the system is shown in Figure 1.1. It consists of several components that are implemented on Advanced Mezzanine Card (AMC) modules and which are interconnected with an SRIO network:

Single MoSync AMC (SMA) synchronizes the system.

Quad High Speed Serial Link AMC (QHA) are the interfaces between the system and the outside world (sensor and actuator boards).

Host configures and manages the components and the SRIO network.

High-Performance Process Controller (HPPC) processing elements that implement the control loop.

The SMA and the QHAs are implemented on dedicated Field-Programmable Gate Array (FPGA) hardware boards. The host and the HPPCs run on general-purpose single-core processor boards. At the moment, there are two motivations to upgrade the hardware platform of the host and the HPPCs to a different architecture.

- **performance** The system that has to be controlled is becoming increasingly complex. Therefore, the application is constantly growing and an increase in performance is demanded from the hardware.

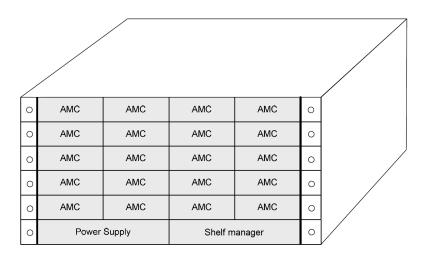

- space The different components are stored as AMC modules in an AdvancedTCA shelf. Such a shelf has a limited number of slots for the AMC modules. Figure 1.2 shows a diagram of an AdvancedTCA shelf that can store 20 AMC modules. A different hardware architecture would allow to combine several modules onto a single module and therefore leave room for more modules.

Figure 1.2: Diagram of an ATCA shelf.

### 1.2 Problem statement

The thesis is centred around two problems.

**comparison of different processor architectures** for both the host and the HPPC application. Performance is the most important criterion but non-performance related criteria dictated by the environment in which the applications must run are also taken into account in order to come to a conclusive comparison. We only perform a core-to-core comparison, i.e. for multi-core platforms we only measure the performance of a single core. **mapping the application to a multi-core system** motivated by the performance and space reasons mentioned above. We consider only the HPPC application because it is a bigger performance bottleneck than the host and due to its nature it is more challenging to parallelize.

### 1.3 Thesis outline

Chapter 2 introduces the host and the HPPC applications, both from a software and from a hardware perspective. Chapter 3 discusses the topic of computer architectures. Factors that affect the performance are discussed and a selection of different computer architectures is presented. Furthermore, a first comparison of the architectures that are going to be benchmarked is made. Chapters 4 and 5 present the results of the comparison for respectively the host application and the HPPC application. Then, Chapter 6 discusses the mapping of the HPPC application to a multi-core platform. It compares two alternatives for a mapping of tasks to cores, investigates the scalability of the HPPC application and discusses the topic of inter-core synchronization. Chapter 7 formulates a conclusion of the thesis. Finally, Chapter 8 discusses future work arising from this project.

### **Chapter 2**

# **Overview of the applications**

This chapter starts with the description of the HPPC and the host application in respectively Section 2.1 and 2.2. Section 2.3 explains the relationship between the host and the HPPC application. Finally, Section 2.4 introduces the hardware platform on which the applications run. It will be described in more detail in the next chapter.

### 2.1 The HPPC application

Section 2.1.1 discusses the structure of the HPPC application and Section 2.1.2 explains how the application is implemented in software.

#### 2.1.1 Structure of the application

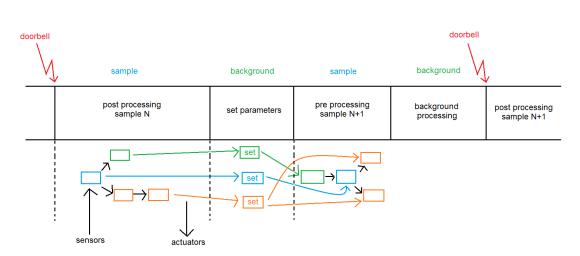

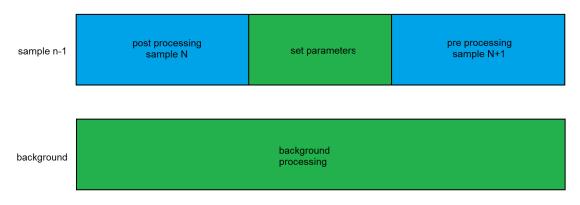

The HPPC modules implement the control loop and do the actual computations for the control system. Each HPPC application is different as each controls a different mechatronic device; however, they all have the same structure. This structure is shown in Figure 2.1.

Each application implements a control loop that runs at a specific frequency. This means that periodically, sensor data is read, new set points are computed and sent to the actuators. The frequency of operation is defined externally by the SMA. At the start of every new execution period, the SMA sends a doorbell notification to each HPPC module via the SRIO network. During each period of execution, the following steps are performed:

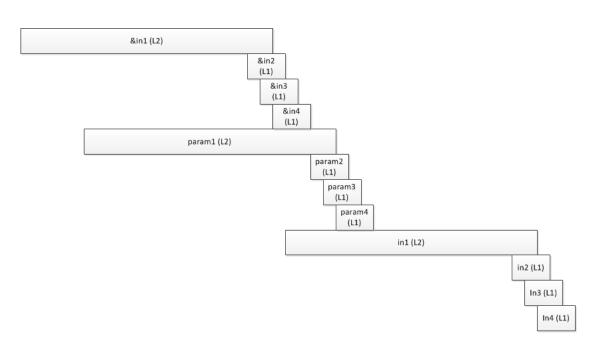

**post-processing of sample N** The state-space of the controlled system is continuous. Since the processing system is discrete, we have to take samples of the system state by reading the sensors at discrete moments in time. At the moment of the doorbell notification that indicates the start of a new period, the sensor data that represents the current state of the system is available. With this data, the new set points destined for the actuators are computed. The computation is modelled as a computational network. Blocks represent units of computation that take an input and produce an output. Arrows between blocks define dependencies. As soon as the new set points are ready, they are sent to the actuators.

Figure 2.1: Structure of a HPPC application.

- **set parameters** The blocks of the computational network are parametrisable. Before we start computing the next sample, we may have to update the parameters of some of these blocks. In order to avoid consistency problems, we can only update the parameters of a block when that block has finished its execution and has not started its next execution.

- pre-processing of sample N+1 Before the next sensor data has arrived (corresponding to sample N+1), we can already perform a pre-processing step for the next sample. The parameters of the blocks have been updated in the previous step. Just like for the post-processing step, the computation is implemented as a computational network.

- **background processing** During the slack time between the end of the pre-processing step and the arrival of the next doorbell interrupt, non-critical background tasks are executing.

At deployment, the different HPPC applications are mapped onto physical HPPC modules.

#### 2.1.2 Software implementation

On a software level, the loop depicted in Figure 2.1 is implemented by means of two types of tasks:

- **sample task** This is the task that is triggered by the doorbell notification. It effectively implements the control loop because it runs the computation networks for the calculation of new set points (i.e. the *pre-processing* and *post-processing* steps).

- **background task** These tasks serve as an interface between the host and the sample task. They fulfil two functions.

- They implement Remote Procedure Calls (RPCs) coming from the host. When the host issues an RPC call, a new background task that executes the appropriate function is spawned. The background task is only allowed to execute during the *background processing* step in Figure 2.1.

• They set the parameters of the computation blocks between the post- and pre-processing steps (see the *set parameters* step in Figure 2.1).

The HPPC software runs bare-board, meaning that it does not run a conventional operating system. It is supported by a custom library, denoted by HPPC-OS, that was built to offer the OS services needed by the application. In the first place, this was done to improve the predictability of the implementation. The requirements specify an upper bound of 5  $\mu$ s on the interrupt latency of the system. The reason for the requirement is that there will not be enough time left to execute all the steps described above if the interrupt latency is longer. Experiments showed that the Linux kernel can not guarantee a jitter that is low enough to satisfy the requirement. With the bare-board-based solution, the jitter on the interrupt latency is low and the maximal latency is low enough for the application. Another advantage of a custom operating system is a reduction in overhead and memory footprint. This leaves more execution time for the actual applications running on the system.

### 2.2 The host application

The host application acts as a controller for the whole system shown in Figure 1.1. It consists of a large number of soft real-time tasks (about 30) that run as processes on a Linux kernel. Since there are many different processes running concurrently, there is not a clear dominating type of computation. Both floating-point and integer computations are performed, as well as communication over Ethernet and SRIO. The distribution of the load over time is bursty. This means that the average load is low but it can become very high at specific moments.

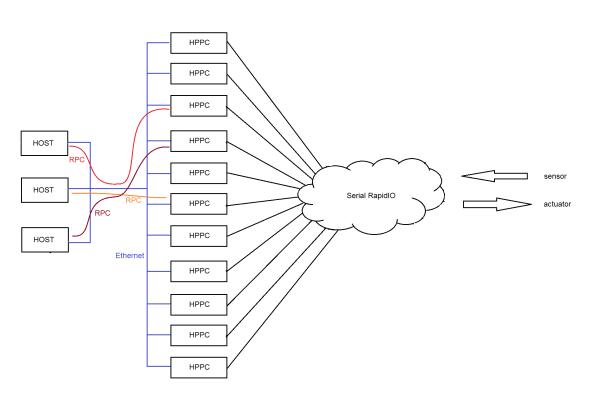

### 2.3 Relationship between the host and the HPPC application

Figure 2.2 shows the relationship between the host and the HPPCs. There are 11 HPPC applications in total, each mapped onto one physical AMC module. The host configures and manages the different components of the system, including the HPPCs. Due to its size, the host application is divided over three physical AMC boards. The HPPCs are connected to the SRIO network in order to communicate with the sensors and the actuators. The communication between the host and the HPPCs happens only over the Ethernet bus by means of RPC calls.

Figure 2.2: Relationship between the host and the HPPC modules.

### 2.4 Hardware implementation

Both the host and the HPPC run on the same type of AMC modules. The processing component of the board is the Freescale MPC8548 System-On-a-Chip (SoC) [1]. This processor architecture will be discussed in more detail in the next chapter.

### **Chapter 3**

# **Description of the architectures**

This chapter discusses different computer architectures. In Section 3.1, important factors that influence the performance of an architecture are described. A selection of candidate hardware architectures is presented in Section 3.2. Then in Section 3.3 the actual architectures that are going to be benchmarked are presented and a first comparison is made in Section 3.4.

#### 3.1 Factors of performance

Without assuming anything about an application, we can state characteristics of microprocessor architectures that influence the performance of any application. An important measure that allows us to assess the impact of a factor quantitatively is the Cycles Per Instruction (CPI) metric. Any processor architecture has a fixed Instruction Set Architecture (ISA) which defines the set of native commands implemented by the processor. Let *Instr* be the set of instructions in the ISA. Then the CPI is defined as the average latency (in clock cycles) per instruction.

$$CPI = \frac{1}{|Instr|} \sum_{i \in Instr} \text{clock cycles}(i)$$

A lower CPI indicates a better architecture in overall. Techniques that are used to optimize computer architectures affect the CPI in some way. However, there are limits to the usage of the CPI as a measure of performance. First, not all instructions are equally likely to be present in an application. For example, load and store instructions are much more common than integer divide instructions. Secondly, the performance of an architecture is also dependent on the application that is running. Some architectures are tailored for a particular kind of application. Therefore, the CPI measure should not be taken as an absolute metric for the comparison of architectures but it can be used to quantify the effect of an optimization technique for an architecture.

To define a processor architecture, the following aspects are important and they will be discussed in the next paragraphs.

- clock frequency

- memory hierarchy

- exploitation of instruction-level parallelism

- exploitation of data-level parallelism

- simultaneous multithreading

- multiple execution cores

#### 3.1.1 Clock frequency

The clock frequency defines the operating speed of the processor. Therefore, it determines the speed at which the instructions are executed. An instruction can have the same latency on two different processors in terms of clock cycles but it will execute faster on the processor that has a higher clock frequency. However, the clock frequency is, strictly speaking, not a property of a computer architecture. Instead, it is mainly defined by the Complementary Metal-Oxide-Semiconductor (CMOS) technology that is used to implement the processor. For this reason, we will normalize the results of the measurements performed in this thesis in order to discard the effect of the clock frequency.

#### 3.1.2 Memory hierarchy

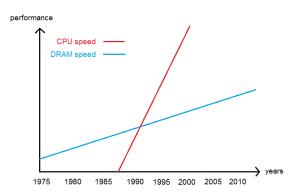

Figure 3.1: The disparity in speed between CPUs and DRAM modules causes the memory wall.

The memory hierarchy is an important factor in the performance. In the middle of the 1980s, Central Processing Units (CPUs) became faster than Dynamic Random-Access Memory (DRAM) memories and the difference in speed has kept increasing ever since (see Figure 3.1). The disparity in operating speed between the CPU and the DRAM is called the memory wall. The main consequence is that the CPU wastes hundreds of cycles when it has to wait for data from the main memory. This causes very big stalls. Modern superscalar processors try to hide this latency by exploiting instruction-level parallelism (ILP) or by applying techniques such as out-of-order execution. These mechanisms enable the simultaneous execution of independent instructions. Therefore, when the processor is stalling on a memory access, instructions that do not depend on this memory access can be executed concurrently. However, insurmountable data and control dependences put a fundamental limitation on these methods. That is why caches have become increasingly important.

Caches exploit the spatial and temporal locality of memory accesses by temporarily storing data that is prone to be used again soon in a faster, smaller memory that is close to the CPU and that can be accessed within a few clock cycles. Most processors have multiple levels of cache; the caches close to the processor are fast but have a small capacity while the levels higher up have a greater capacity but also have longer access times. The average latency for instructions that perform a memory access is reduced by the presence of multiple cache levels. Therefore, cache levels have a positive effect on the CPI.

When the CPU loads data from memory, the cache checks whether it has a copy of the data. If that is the case, we speak of a cache hit. Otherwise, the result of the operation is a cache miss and the data will have to be fetched from either the next cache in the memory hierarchy or from main memory. The performance of a cache is indicated by its hit rate, i.e. the percentage of cache hits compared to the total number of memory accesses. The following properties of a cache are important for its performance:

cache size A larger cache can store more items and therefore produces more hits.

- **cache line size** A cache stores data as blocks of a certain size (typically 32 bytes or 64 bytes). A larger cache line size is therefore good for the performance of sequential access as more data can be loaded from the cache before having to fetch the next cache line.

- **associativity** The replacement policy decides where in the cache a copy of an entry of main memory will go. If the replacement policy is free to choose any entry in the cache to hold the copy, the cache is called fully associative. At the other extreme, if each entry in main memory can go in just one place in the cache, the cache is direct mapped. A fully associative cache has the lowest miss rate but it requires to search the entire cache when looking for an entry. Therefore, implementations make a compromise; if an entry can go to any of *N* places in the cache, then that cache is *N*-associative.

#### 3.1.3 Instruction-level parallelism

In order to increase the number of executed instructions per cycle, microprocessor designers have tried to exploit ILP. This technique consists of executing instructions of a same thread in parallel. Not all instructions can be executed in parallel; they must be independent, i.e. there must not be a data dependency or a control dependency between them. The effect of the exploitation of ILP is a reduction of the CPI by a factor.

$$\mathsf{CPI} = \frac{\mathsf{CPI}_{\mathsf{base}}}{\mathsf{exploited ILP}}$$

The main goal of ILP is to keep the instruction pipeline running. When the processor is stalling on a high-latency instruction, for instance a memory load, ILP allows it to execute independent instructions in parallel. Therefore, ILP is also a solution for the memory wall. In order to be able to execute instructions in parallel, a CPU that exploits ILP needs

• Multiple execution units that can execute in parallel.

- The ability to look ahead in the instruction flow and make a distinction between instructions that depend on the outcome of the current instruction and independent instructions. For most architectures that exploit ILP, this is done by the hardware at run-time. These processors are then called superscalar processors.

- Support of out-of-order execution: the execution of the instructions does not have to follow the instruction flow but the results have to be written back in program order.

For these reasons, exploitation of ILP does not come for free but requires complex hardware that adds up to the power consumption of the processor.

#### 3.1.4 SIMD architectures

When a same operation has to be performed on many independent pieces of data, these computations can be executed in parallel. This type of parallelism is called data-level parallelism. A typical field where this is heavily used is computer graphics. Many algorithms from the graphics domain consist of doing the same computations on all pixels. In Flynn's taxonomy [2], an architecture that exploits this type of parallelism is a Single Instruction, Multiple Data (SIMD) architecture.

These architectures provide instructions that perform an operation on a vector of input data instead of on a scalar. What needs to be specified in a loop on a scalar processor can be stated with a single instruction on an SIMD processor. Graphical Processing Units (GPUs) fall in this category. Due to the field of application they were designed for, they have a vast amount of floating-point units that can be used in parallel. This allows them to perform an operation on many data inputs simultaneously.

#### 3.1.5 Simultaneous multithreading

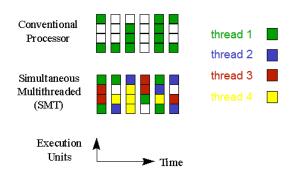

Simultaneous Multithreading (SMT) is a technique that improves the overall efficiency of superscalar CPUs (i.e. processors that exploit ILP dynamically) by hardware multithreading. A normal superscalar processor runs a single thread of execution at a time. Therefore, every clock cycle, it can only issue instructions from a single thread. Due to dependencies between instructions, an application has only a limited amount of ILP. Therefore, the idea of hardware multithreading is that the processor can issue instructions of several threads simultaneously, instead of considering only one thread. If a thread is waiting on data from the main memory and thus has to stall, instructions from another thread can be executed instead. The mechanism is shown in Figure 3.2. Note that the overall CPI of the processor increases by the use of SMT but the CPI of an individual thread actually decreases because it has to share the processor with another thread.

#### 3.1.6 Multi-core architectures

Multiprocessor systems exploit another type of parallelism called task parallelism. It focuses on the distribution of execution threads across different parallel computing nodes. Compared to instruction-level and data parallelism, the granularity of task parallelism is much higher.

Figure 3.2: Simultaneous multithreading enables parallel scheduling of instructions from several threads [3].

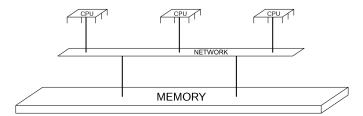

The most widely used multi-core architecture is the Symmetric Multiprocessing (SMP) architecture. There, multiple identical processors are connected to a single shared main memory. A network connects the cores with each other and with the memory. Figure 3.3 shows a diagram of a typical SMP system.

Figure 3.3: Diagram of an SMP system [4].

### 3.2 Candidate hardware architectures

In this part, we will discuss several candidate hardware architectures. The processors were selected on the basis of:

- The roadmap of the company that owns the system. Currently, the system uses PowerPC processors. However, to support their decisions on the long-term roadmap, the company is interested in how well Intel processors perform on their applications compared to PowerPC processors. Therefore, processors from both Intel and PowerPC were included in the study.

- Their position on the power-performance line. A low-power processor typically also has a lower performance and vice-versa for a high-power processor. The intention is to compare processors on a wide range of this line.

- Two architectures that are optimized for specific applications: the Cell architecture and a digital signal processor. They were included for their expected performance on the applications.

The following architectures were selected.

Intel Atom Z530 low power consumption, low performance

PowerPC MPC8548 current hardware platform, mid power consumption, mid performance

PowerPC P4080 octo-core evolution of the MPC8548, mid power consumption, mid performance

PowerPC P5020 dual-core evolution of the P4080, mid power consumption, mid performance

Intel Xeon E5540 quad-core, high power consumption, high performance

Cell mix of a general-purpose and an SIMD processor, high power consumption, high performance

**digital signal processor** processor dedicated for Digital Signal Processor (DSP) applications, low power consumption, mid performance (for certain applications)

#### 3.2.1 Intel Atom Z530

The Intel Atom architecture is a 32-bit single-core general-purpose processor architecture that aims to provide modest performance with a low power-consumption. It implements the x86 instruction set.

#### Memory hierarchy

The Z530 has two levels of cache with a 64 bytes cache line size.

- L1 instruction cache It has a 32 KiB 8-way associative L1 cache dedicated for instructions.

- L1 data cache It has a 24 KiB 6-way associative L1 cache dedicated for data. The motivation for this asymmetric L1 cache is power saving. For the data cache, Intel decided to use 8 transistors to store one bit instead of the conventional 6 transistors. The addition of two extra transistors allows to reduce the voltage applied to the cache resulting in a reduced power consumption.

- L2 unified cache It has a 512 KiB 8-way associative unified L2 cache.

#### Instruction-level parallelism

The Intel Atom has a limited form of instruction-level parallelism. It follows an in-order execution flow, meaning that the execution of instructions strictly follows the program order. However, it can dispatch two instructions simultaneously. This allows for parallel execution of two instructions. This can only happen under strict conditions however, such as no dependencies between the instructions and the usage of different types of execution units.

Figure 3.4: Architecture of the Intel Atom core [5].

#### SIMD

Figure 3.4 shows the architecture of the Intel Atom core. The execution unit consists of two clusters: a SIMD/floating-point cluster and an integer cluster. The Intel Atom supports a limited form of SIMD because the SIMD/floating-point cluster can execute instructions where multiple data items are packed in a 128-bit register. Computations are done on all data items in parallel. For instance, it is possible to do four 32-bit integer additions in parallel.

#### Simultaneous multithreading

The Intel Atom supports hyper-threading, which is Intel's implementation of simultaneous multithreading. The core can execute instructions from two threads simultaneously.

#### Strengths and weaknesses

Due to its low-power properties, the Intel Atom processor is typically used in mobile applications. In these environments, power consumption is equally or more important than the computational performance. Therefore, the Intel Atom lacks two important features for performance:

• The smaller L1 data cache (24 KiB instead of the conventional 32 KiB) will cause more L1

cache misses and in the end, will also result into more L2 cache misses.

• The in-order execution flow is a weakness for computation-intensive applications, i.e. applications that have a relatively low factor of branching.

On the other hand, the Intel Atom also has some strengths:

- it provides limited multiprocessing capabilities due to its support of SMT.

- floating-point computations can be accelerated by using the SIMD instructions.

#### 3.2.2 PowerPC MPC8548

The MPC8548 is a SoC manufactured by Freescale Semiconductor. It contains an e500v2 core, which is a 32-bit Power Architecture-based microprocessor core.

#### **Memory hierarchy**

Just like the Intel Atom Z530, the e500v2 core has two levels of cache. One difference is that its cache line size is 32 bytes.

L1 instruction cache It has a 32 KiB 8-way associative L1 cache dedicated for instructions.

L1 data cache It has a 32 KiB 8-way associative L1 cache dedicated for data.

L2 unified cache It has a 512 KiB 8-way associative unified L2 cache.

#### Instruction-level parallelism

Figure 3.5 shows the architecture of the e500v2 core. The e500v2 is a true superscalar processor. It can dispatch at most 2 instructions per cycle to the various reservation stations. When an instruction has executed in its appropriate execution unit, it is sent to the completion and write-back stage. These stages maintain the correct architectural machine state and commit results to the registers in the proper order.

#### SIMD

Just like the Atom, the e500v2 core supports a limited form of SIMD. However, as the Atom supported packed data of 128 bits, the e500v2 supports only 64-bit data. It allows to perform arithmetic operations on two 32-bit integers that are packed in a 64-bit register.

#### Simultaneous multithreading

The e500v2 core does not support simultaneous multithreading. At any moment, only one thread is using the processor.

Figure 3.5: Architecture of the e500v2 core in the MPC8548 [6].

#### Strengths and weaknesses

The MPC8548 is quite similar to the Intel Atom Z530. One important difference is that it exploits ILP with an out-of-order execution flow. This provides advantages for applications with low branching, where a large scheduling window allows many independent instructions to be executed in parallel.

The main disadvantage of the MPC8548 is the lack of SMT. The processor executes only one thread of execution at a time. This reduces the overall throughput of the software running on the processor but it has one advantage: it increases predictability of the software. Indeed, when using SMT, the performance of a thread becomes dependent on the behaviour of the other thread that is running simultaneously. This is bad for real-time behaviour and the lack of SMT support illustrates the domain that the MPC8548 targets, i.e. mainly industrial applications that often have real-time requirements.

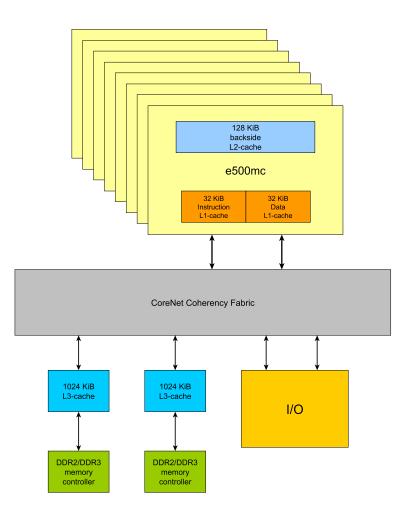

#### 3.2.3 PowerPC P4080

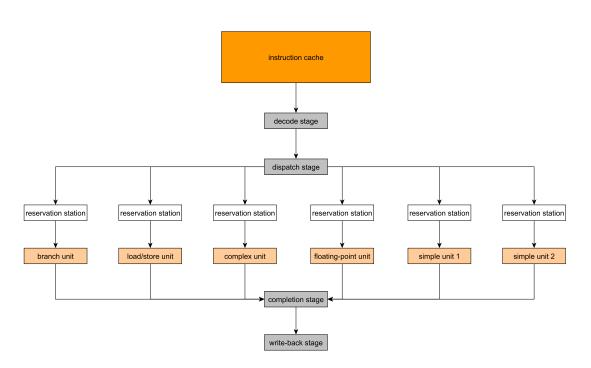

The P4 series is the evolution of the MPC8548 SoC. The P4080 is an octo-core SoC based on the e500mc core. The architecture of the SoC is shown in Figure 3.6. The e500mc core is very similar to the e500v2 core of the MPC8548 except for a few differences.

#### Memory hierarchy

Each core has its private two-level cache hierarchy. Furthermore, there is an additional L3 cache that is shared among all cores. The cache line size is 64 bytes, as opposed to 32 bytes for the e500v2

Figure 3.6: Architecture of the P4080 SoC [7].

core.

L1 instruction cache Each core has a 32 KiB 8-way associative L1 cache dedicated for instructions.

- L1 data cache Each core has a 32 KiB 8-way associative L1 cache dedicated for data.

- L2 unified cache Each core has a 128 KiB 8-way associative unified L2 cache.

- L3 unified cache All eight cores share 2 MiB of 32-way associative unified L3 cache. The cache is split in two blocks of 1 MiB, where each one is attached to a separate memory controller. The mapping of memory address to memory controller is determined by the interleaving mechanism. Some possible configurations are cache line interleaving (meaning 64 bytes are mapped onto one controller, the next 64 bytes onto the other controller, and so on), bank interleaving or page interleaving.

#### Instruction-level parallelism

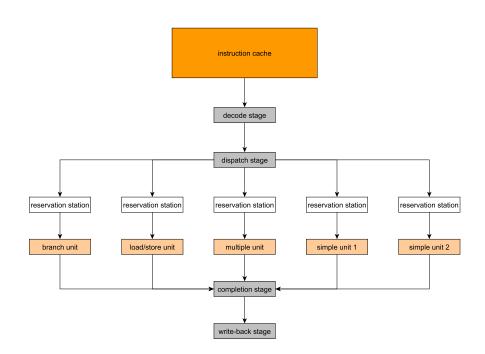

Just like the e500v2 core, the e500mc core exploits ILP and can execute instructions out-of-order. It can dispatch 2 instructions per cycle. When comparing Figures 3.5 and 3.7, we can notice a difference in the execution units. The 'multiple unit' of the e500v2, which executed both integer multiplies and divides as well as floating-point instructions, has been replaced by a 'complex unit' and a 'floating-point unit' in the e500mc. Now the complex integer operations (multiply and divide) are executed by the 'complex unit' while the floating-point instructions execute in a dedicated 'floating-point unit'.

Figure 3.7: Architecture of the e500mc core in the P4080 [8].

#### SIMD

In contrast to the e500v2 core, the e500mc does not support SIMD instructions.

#### Simultaneous multithreading

Just like the e500v2 core, the e500mc does not support simultaneous multithreading.

#### Strengths and weaknesses

The P4080 is essentially an octo-core version of the MPC8548 except for three main differences:

each core possesses less private cache: the L2 cache is only 128 KiB compared to 512 KiB on the MPC8548.

- it does not support SIMD instructions which makes it less suitable for applications with some form of data-parallelism.

- the 'multiple unit' on the MPC8548 has been split into two separate units on the P4080: a 'complex unit' for complex integer operations (division and multiplication) and a 'floating-point unit' for floating-point operations.

The latter can be an advantage if an application performs integer and floating-point computations in parallel. However, we do not expect this to be a big advantage in practice as an application is often divided into parts where only a single type of computation is performed in each part.

Due to the high number of cores and the relatively small private cache of each core, it is expected that the P4080 performs well for applications that can be divided into many light-weight threads where each thread has a small memory footprint. It is not suited for large sequential applications as many cache misses will degrade the performance and the available cores will be underutilized.

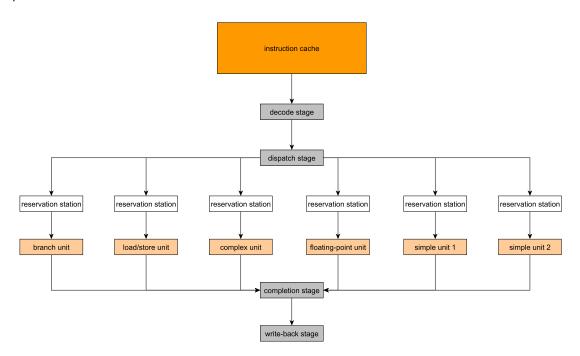

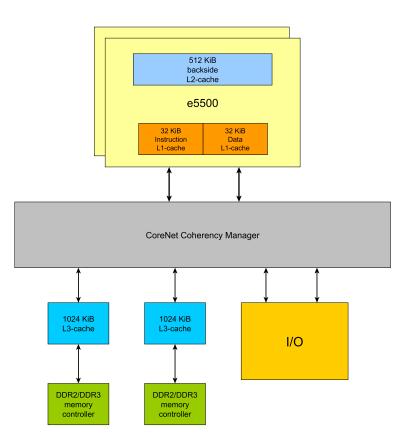

# 3.2.4 PowerPC P5020

The P5 series is also a successor to the MPC8548. The P5020 is a dual-core SoC based on the 64-bit e5500 core. Its architecture is shown in Figure 3.8. When comparing it with the architecture of the P4080 in Figure 3.6, we can notice that they have the same structure. The main difference is that the amount of cache per core is much higher on the P5020 than on the P4080.

## **Memory hierarchy**

Just like the P4080, each e5500 core of the P5020 has two levels of cache. Also, the cache line size is 64 bytes. Furthermore, there is an additional L3 cache that is shared by both cores.

L1 instruction cache Each core has a 32 KiB 8-way associative L1 cache dedicated for instructions.

- L1 data cache Each core has a 32 KiB 8-way associative L1 cache dedicated for data.

- L2 unified cache Each core has a 512 KiB 8-way associative unified L2 cache.

- **L3 unified cache** The two cores share 2 MiB of unified L3 cache with a 32-way associativity. The cache is split in two blocks of 1 MiB, where each one is attached to a separate memory controller. Just like for the P4080, the mapping of memory address to memory controller is determined by the interleaving mechanism.

On average, each core in the P5020 has 1600 KiB of cache. This is only 448 KiB per core on the P4080.

## Instruction-level parallelism

As can be seen in Figure 3.9, the structure of the e5500 core is the same as the e500mc core. Also, the ILP mechanism is the same.

Figure 3.8: Architecture of the P5020 SoC [9].

## SIMD

Just like the e500mc core, the e5500 does not support SIMD instructions.

## Simultaneous multithreading

Just like the e500mc core, the e5500 does not support simultaneous multithreading.

## Strengths and weaknesses

Whereas the P4080 targets applications that are composed of many small threads, the P5020 is more suited for applications that can be decomposed into fewer but larger threads. Its main strength compared to the other processors is that each core has a very large cache: on average, each core has 1312 KiB cache of which 576 KiB is private.

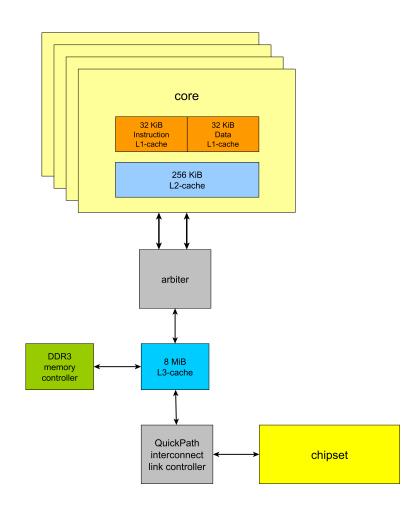

# 3.2.5 Intel Xeon E5540

The Intel Xeon 5500 series are microprocessors based on the Nehalem-EP architecture. The processor we consider is the E5540 model. This is a quad-core multiprocessor. The architecture of the

Figure 3.9: Architecture of the e5500 core in the P5020 [10].

processor is shown in Figure 3.10.

# Memory hierarchy

Each core has two levels of cache, with a cache line size of 64 bytes. Furthermore, there is an additional L3 cache that is shared by both cores.

L1 instruction cache Each core has a 32 KiB 4-way associative L1 cache dedicated for instructions.

L1 data cache Each core has a 32 KiB 8-way associative L1 cache dedicated for data.

L2 unified cache Each core has a 256 KiB 8-way associative unified L2 cache.

L3 unified cache The cores share 8 MiB of 16-way associative L3 cache.

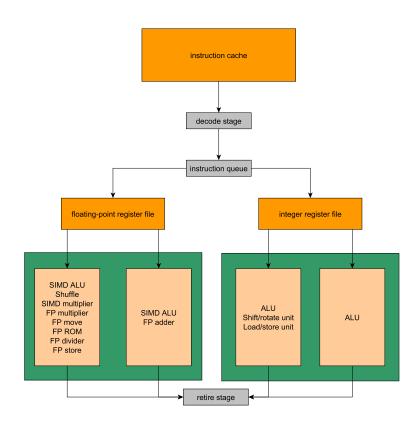

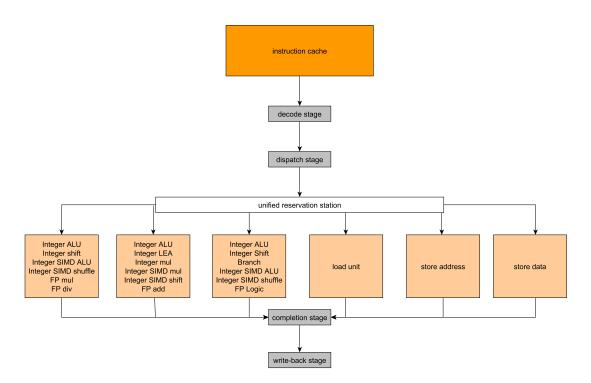

# Instruction-level parallelism

The Nehalem-EP architecture is a superscalar architecture. This means that it exploits instructionlevel parallelism. Its execution pipeline is shown in Figure 3.11. When comparing it with the pipeline of the e5500 (see Figure 3.9), we can notice several differences. First of all, the reservation station for the execution units is unified, i.e. there is one queue for all execution units instead of a separate queue for each execution unit. Secondly, the computational operations are divided among the execution units in a different way. In the PowerPC architectures, the division is 'cleaner': each execution

Figure 3.10: Architecture of the Intel Xeon E5540 processor [11].

unit has a clear function. For instance, the 'floating-point unit' solely executes floating-point instructions. In the Nehalem architecture, this distinction is much less clear. For instance, the floating-point operations are divided over three different execution units. The reason is performance as different instructions that belong to the same domain (for instance floating-point operations) can be scheduled on different execution units, therefore allowing parallel execution. The downside is duplication of hardware as similar logic must be implemented in multiple execution units. The following properties are characteristic for the Xeon execution pipeline:

- All execution units that perform computations (i.e. not the load and store units) perform both integer and floating-point computations.

- There is no separate branching unit but it is integrated in one of the execution units.

- There is a separate execution unit for loading data, storing addresses and storing data. These three operations can be executed in parallel.

Another architectural difference is that the decoding stage is much more complex in the Nehalem architecture. The PowerPC ISA follows a Reduced Instruction Set Computing (RISC) architecture. However, the x86 instruction set is a Complex Instruction Set Computing (CISC) architecture. For performance reasons, the x86 instructions (called macro-ops) are converted to a sequence of smaller RISC-instructions (called  $\mu$ -ops) that are executed instead. This conversion happens during the decoding stage.

Figure 3.11: Architecture of the Intel Xeon E5540 execution pipeline [11].

## SIMD

Nehalem supports the Streaming SIMD Extensions (SSE) instruction set. Just like the Atom architecture, it has support for data items that are packed in 128-bit registers. Then it is possible to do simultaneous operations on two double-precision 64-bit floating-point elements or four single-precision floating-point elements.

## Simultaneous multithreading

As the Intel Atom, the Xeon processor supports SMT through hyper-threading. A core can execute instructions from two thread simultaneously.

## Strengths and weaknesses

The Nehalem architecture is often used for server applications, for instance to host a database or a web server. This has several reasons:

- the total amount of cache in the processor is high which is important to speed up memoryintensive applications.

- the memory performance is expected to be good because the conventional load/store unit is implemented as three separate execution units.

- due to its four cores and support of SMT, the degree of multiprocessing that can achieved is high. This allows it to handle multiple server requests concurrently.

Moreover, we also expect it to perform well computation-wise. For instance, the division of the floating-point operations over the execution units (multiplication and division are on one unit, the addition is on another and floating-point logic is on a third one) combined with an out-of-order execution flow allows it to achieve a high performance on floating-point applications.

The biggest weakness of the Xeon processor is its high power consumption. This can become a problem when the cooling capacity of the environment is limited.

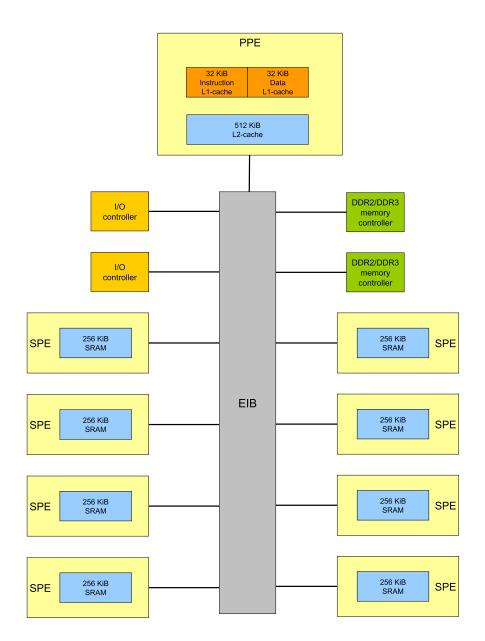

# 3.2.6 Cell processor

Cell is a multiprocessor architecture jointly developed by IBM, Sony and Toshiba. It combines a general-purpose PowerPC host processor, called the Power Processing Element (PPE), with 8 coprocessors, called Synergistic Processing Elements (SPEs). In an application, the programmer can indicate parts of the program that should execute on an SPE. SPEs are fast SIMD processors and can therefore perform integer and floating-point operations much faster than the PPE. The basic idea is that the PPE is used for the control flow of the application while the SPEs are used to accelerate certain portions of the application. The Cell architecture is shown in Figure 3.12.

## Memory hierarchy

As can be seen in Figure 3.12, the PPE has two levels of cache with a cache line size of 128 bytes.

L1 instruction cache It has a 32 KiB 2-way associative L1 cache dedicated for instructions.

L1 data cache It has a 32 KiB 4-way associative L1 cache dedicated for data.

L2 unified cache It has a 512 KiB 8-way unified L2 cache.

An SPE has no hardware-controlled cache but instead has a fast 256 KiB Static Random-Access Memory (SRAM) scratchpad. The motivation is to reduce hardware complexity and increase performance. However, it also makes it harder to program because the task of managing the memory hierarchy is assigned to the programmer.

#### Instruction-level parallelism

Neither the PPE nor the SPEs exploit ILP. Both have an in-order execution flow. The main motivation is power consumption because, as was mentioned before, out-of-order execution requires complex hardware.

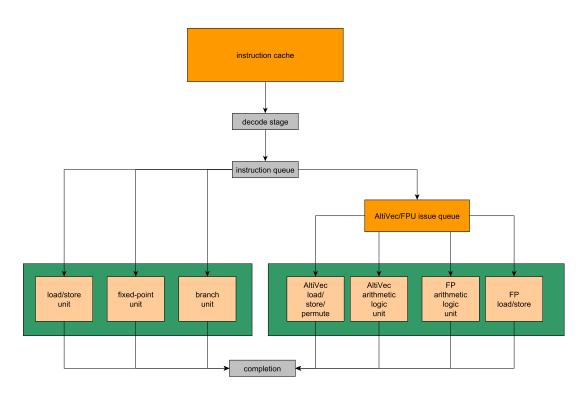

The execution pipeline of the PPE is shown in Figure 3.13. It features a load/store unit, a fixedpoint unit and a branch unit in one cluster and two AltiVec (SIMD) and two floating-point units in the other cluster. It can issue up to two instructions per cycle, i.e. one instruction per cluster.

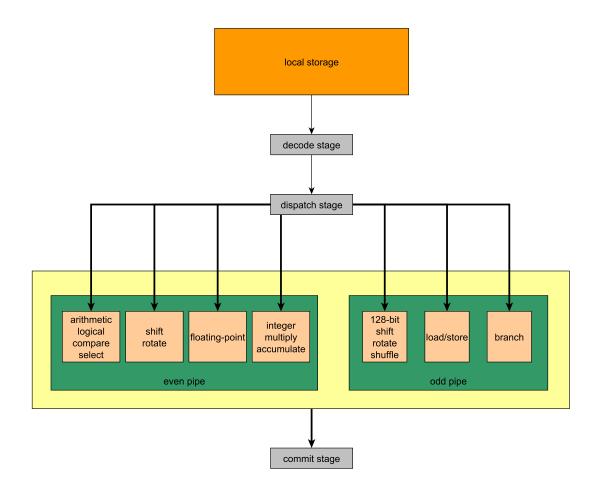

The execution pipeline of the SPE is shown in Figure 3.14. It consists of 7 execution units that are organized into an even and an odd pipe. Just like the PPE, it can issue an instruction in both pipes every cycle.

## SIMD

Just like the Intel Xeon and the Intel Atom, the PPE supports a limited form of SIMD. It supports AltiVec instructions, which is the PowerPC variant of the SSE instruction set for x86. This means that it can operate on data items that are packed in 128-bit registers.

The SPE is an SIMD architecture. It has one register file that contains 128 128-bit registers. Each instruction can read up to three 128-bit source operands and write back one 128-bit result. Alternatively, it can also do operations on single scalar 128-bit elements.

#### Simultaneous multithreading

The PPE supports SMT in the same way the Intel processors support it with hyper-threading. The SPE is single-threaded however.

## Strengths and weaknesses

Originally, Cell is an architecture for high-performance distributed computing. It targets applications that are computationally intensive, often data-parallel and that can be divided into threads that can execute concurrently. The SPEs must be seen as units that can accelerate the execution of certain portions of the application.

For these reasons, the Cell is not suited for applications that have a complicated control flow, i.e. with many branches, and that have few parts that require heavy computations. Such an application would run on the PPE only and would leave the SPEs unutilised.

One disadvantage of the Cell compared to other high-performance processors such as the Intel Xeon E5540 is that it requires a lot of effort from the programmer to achieve a high performance on the platform. For instance, the SPEs have scratchpad memories instead of hardware controlled caches. Therefore, the programmer must manage the memory in an efficient way. However, if the application is programmed wisely, the fast SIMD computations, the fast scratchpad memories and the high-bandwidth interconnect of the Cell architecture can provide a very high performance.

# 3.2.7 Digital signal processor

Compared to the general-purpose processors that were discussed before, DSPs relinquish flexibility for more efficiency. They are targeted towards a specific application domain, i.e. digital signal processing applications, which makes them more performant in that domain than a general-purpose CPU but less efficient in other domains.

They have special hardware features that allow them to perform DSP operations in an efficient way. Typical techniques are

- fast multiply-accumulate units

- memory architectures that support several accesses per instruction cycle (modified Harvard architecture)

- special addressing modes such as bit-reversed addressing (for instance to calculate FFTs) or modulo addressing

- · special loop controls that reduce the loop overhead

However, they often lack units that increase the flexibility of the processor. For instance, DSPs often do not have a memory management unit. They have no support for virtual memory or memory protection because it increases the context switching latency. Also, they often have limited I/O capabilities. Because a DSP has an architecture targeted to provide acceleration for certain parts of an application, there is limited support of operating systems for DSPs. Also, like the Cell, it is required that the application is specially optimized by hand in order to take advantage of the features of a DSP. Therefore, porting an application is very time-consuming.

As a conclusion, a DSP is most often used as a co-processor to accelerate a certain portion of an application and rarely used stand-alone.

Figure 3.12: Architecture of the Cell processor [12].

Figure 3.13: Architecture of the PPE in the Cell processor.

Figure 3.14: Architecture of an SPE in the Cell processor.

# 3.3 Architectures to be benchmarked

Due to practical availability, it was only possible to benchmark the following processors:

- Intel Atom Z530

- Intel Xeon E5540

- PowerPC MPC8548

- PowerPC P4080

Their properties are summarized in Table 3.1. We will not further discuss the other architectures that were introduced in the previous paragraphs, i.e. the P5020, DSPs and the Cell processor.

| Architecture     | cores | alaak fraguanay | L1 cad      | che    | L2 cache | L3 cache       |  |

|------------------|-------|-----------------|-------------|--------|----------|----------------|--|

| Architecture     |       | clock frequency | instruction | data   | L2 Cache |                |  |

| Intel Atom Z530  | 1     | 1596 MHz        | 32 KiB      | 24 KiB | 512 KiB  | -              |  |

| Intel Xeon E5540 | 4     | 2527 MHz        | 32 KiB      | 32 KiB | 256 KiB  | 8 MiB (shared) |  |

| MPC8548          | 1     | 1333 MHz        | 32 KiB      | 32 KiB | 512 KiB  | -              |  |

| P4080            | 8     | 1500 MHz        | 32 KiB      | 32 KiB | 128 KiB  | 2 MiB (shared) |  |

Table 3.1: Important characteristics of the benchmarked architectures.

The benchmarks are presented in the following two chapters. On the Intel Atom processor, the BIOS settings could not be altered. Therefore, it should be noted that the benchmarks were run with the following settings:

- The hardware prefetchers for the cache are enabled. This is a mechanism that speculatively pre-fetches cache lines from memory before they are actually used. We do not expect this to have a big impact on the results as the experiments performed in the thesis are run from the cache levels.

- Hyper-threading (SMT on Intel platforms) is enabled. This slows down the execution of the

experiments because another process can be scheduled on the same core. However, when

running the experiments, we try to minimize the number of running processes in order to reduce

the impact.

- The Intel SpeedStep technology is enabled. This is Intel's implementation of dynamic frequency scaling. This means that depending on the usage of the processor, the clock frequency is scaled dynamically to optimize power consumption. The consequence is that the clock frequency is not constant which makes it harder to establish expectancies for the benchmarks. Also, since we normalize the results of the benchmarks to remove the effect of the clock frequency, the normalized results will be less accurate.

# 3.4 A first comparison

Although the main focus of the study is performance, there are additional criteria that demand to be taken into account by the application environment:

- power consumption

- platform documentation

- duration of supply

# 3.4.1 Power consumption

The processors will be put upon AMC modules and will be placed in an AdvancedTCA shelf. A shelf has a limited cooling capacity and an upper bound on the power consumption of a module is defined in the AdvancedTCA specification. For this reason, the power consumption can be determinant in the choice for an architecture.

The Thermal Design Power (TDP) values of the architectures to be benchmarked are shown in Table 3.2. The following remarks apply to the table. Because the MPC8548 and the P4080 are SoCs, a single chip contains the core, the memory controllers and the controllers for the I/O peripherals. This is in contrast with the Atom and the Xeon processors. These chips only contain the processing core; an additional chipset is needed for the memory controller (called northbridge) and the peripherals (called southbridge). That is why we have to take into account the power consumption of these additional circuits in order to make a comparison.

| Architecture     | thermal design power (W) |             |             |       |  |  |  |

|------------------|--------------------------|-------------|-------------|-------|--|--|--|

|                  | processor                | northbridge | southbridge | total |  |  |  |

| Intel Atom Z530  | 2.2                      | 2           | 4.5         |       |  |  |  |

| Intel Xeon E5540 | 80.0                     | 27.1        | 4.5         | 111.6 |  |  |  |

| MPC8548          |                          | 6.5         |             |       |  |  |  |

| P4080            |                          | 19.0        |             |       |  |  |  |

The AdvancedTCA specification puts a limit of 60 W on the power consumption of an AMC board. The maximum power consumption can be increased by leaving some slots in a row unused such that the cooling capacity of an entire row is divided among the remaining slots. However, the resulting cooling capacity is still too low for the Intel Xeon processor which rules it out at first sight. Nonetheless, it is still worthwhile to investigate the performance of the Xeon processor because in principle, it is possible to step away from the usage of an AdvancedTCA shelf.

# 3.4.2 Platform documentation

The system under consideration is an industrial, real-time application. This means that

- the system must not show unpredicted behaviour

- the system must be fast so that the deadlines set by the application are met

To satisfy those requirements, it is important that the platform is well documented. This allows the software developers to thoroughly understand the architecture in order to provide a reliable application and to get the maximum performance out of the platform. In this area, the PowerPC processors manufactured by Freescale Semiconductor are much better documented than the Intel processors. The main reason for this difference is that Freescale Semiconductor essentially serves a different market than Intel: it focuses more on the industrial sector (automotive, medical) which typically have stricter requirements in terms of reliability and predictability.

# 3.4.3 Duration of supply

Intel ends the lifetime of a processor 5 years after its introduction. This means that neither the processor, neither support for it will be available after this time. In the case of Freescale Semiconductor, the end of life is minimum 10 years after a processor has been released. Depending on the estimated life-time of the system, this can be a determinant factor to choose for a Freescale processor instead of an Intel processor.

# **Chapter 4**

# Benchmarks for the host application

This chapter presents the comparison of the architectures presented in the previous chapter for the host application. Section 4.1 gives an overview of the characteristics of the application. Then, Section 4.2 introduces the concepts of micro- and macro-benchmarks. The benchmarking methodology is presented in Section 4.3. Section 4.4 presents the results of the memory benchmark while Section 4.5 discusses the benchmarks for the integer and floating-point performance. Finally, Section 4.6 formulates a conclusion of the benchmarks and Section 4.7 discusses future work.

# 4.1 Characteristics of the host application

The host application acts as a controller for the whole system and therefore its tasks are very diverse. In the software deployment, the application consists of about 30 Linux processes, divided over 3 AMC modules. Since the performed tasks are very diverse, there is not a clear dominating type of computation. Both floating-point and integer computations are performed, as well as communication over Ethernet and SRIO. Because of this computational diversity, we chose to run different types of benchmarks.

# 4.2 Micro- and macro-benchmarks