## MASTER

Power model for wireless sensor node

van Emden, J.

Award date: 2007

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

TECHNISCHE UNIVERSITEIT EIDHOVEN Department of Mathematics and Computer Science

# Power model for wireless sensor node

By: Joris van Emden

Supervisors: Jef van Meerbergen (TU/e) Martijn Bennebroek (Philips research)

Eindhoven, October 2007

# Contents

| 1        | Intr | oduction                                       | 4  |

|----------|------|------------------------------------------------|----|

|          | 1.1  | Problem statement                              | 4  |

|          | 1.2  | Wireless body sensors and ECG                  | 5  |

|          | 1.3  | WSN architecture and power dissipation         | 7  |

|          | 1.4  | WSN optimizations                              | 7  |

|          |      | 1.4.1 Memory architectures and implementations | 8  |

|          |      | Volatile memory                                | 8  |

|          |      | Non-volatile memory                            | 9  |

|          |      | 1.4.2 Circuit implementation techniques        | 9  |

|          |      | 1.4.3 IC technology scaling trends             | 11 |

|          | 1.5  | Summary                                        | 11 |

| <b>2</b> | Mo   | del description                                | 12 |

|          | 2.1  | Application                                    | 13 |

|          | 2.2  | System model                                   | 15 |

|          |      | 2.2.1 Processor                                | 16 |

|          |      | 2.2.2 Radio                                    | 20 |

|          |      | 2.2.3 Sensors                                  | 21 |

|          |      | 2.2.4 Peripherals                              | 22 |

|          |      | 2.2.5 Clock                                    | 22 |

|          |      | 2.2.6 Power manager                            | 23 |

|          | 2.3  | Model calibration on Chipcon 2430 SoC          | 23 |

|          |      | 2.3.1 Estimation of instruction count          | 23 |

|          |      | 2.3.2 Estimation of component power            | 27 |

|          | 2.4  | Model Validation on Chipcon 2430 SoC           | 32 |

|          | 2.5  | Summery                                        | 33 |

| 3        | Syst | em optimization results       | <b>34</b> |

|----------|------|-------------------------------|-----------|

|          | 3.1  | Reference system              | 34        |

|          | 3.2  | Processor optimization        | 35        |

|          |      | 3.2.1 Single processor design | 35        |

|          |      | 3.2.2 Dual processor design   | 40        |

|          | 3.3  | Radio optimization            | 41        |

|          |      | 3.3.1 Radio Technology        | 42        |

|          |      | 3.3.2 Protocol                | 42        |

|          | 3.4  | Sampling optimization         | 43        |

|          | 3.5  | Batch Program execution       | 44        |

|          | 3.6  | Clock generation optimization | 45        |

|          | 3.7  | Program memory optimization   | 46        |

|          | 3.8  | Summary                       | 47        |

|          |      |                               |           |

| 4        |      | cussion                       | <b>48</b> |

|          | 4.1  | Radio assumptions             | 48        |

|          | 4.2  | Processor state retention     | 49        |

|          | 4.3  | ADC at higher speeds          | 49        |

|          | 4.4  | Power gating                  | 50        |

|          | 4.5  | ROM as an instruction memory  | 50        |

|          | 4.6  | Change crystal earlier        | 50        |

|          | 4.7  | Effective energy per bit      | 50        |

| <b>5</b> | Con  | clusions                      | 52        |

| 0        | 5.1  | Summary                       | 54        |

|          | 0.1  | Jummary                       | 01        |

| 6        | Fut  | ıre work                      | 55        |

|          | 6.1  | Peripherals                   | 55        |

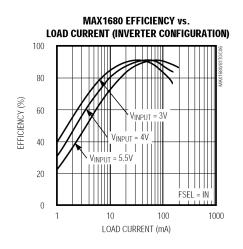

|          | 6.2  | DC:DC efficiency              | 55        |

| A        | 805  | 1 to ARM: instruction count   | 59        |

| в        | Cyc  | les Per Instruction (CPI)     | 62        |

This chapter starts with the problem statement which is followed by the explanation of Wireless Sensor Nodes (WSN) and Electrocardiogram (ECG). Next, the WSN architecture and power dissipation is discussed followed by possible optimizations of the WSN.

## **1.1** Problem statement

A big change is anticipated in modern healthcare from traditional care in hospitals toward remote care at home. The main drive is to counteract the ever increasing costs in the modern healthcare system. To enable this change, wireless body sensor nodes will be required that are able to monitor physiological parameters like ECG, blood pressure, oxygen saturation outside the hospital setting. These devices must be reliable, easy to use and have a long operation time. Ultimately one would like to develop devices that can operate without batteries enabling "unlimited" lifetime. Such low power devices pose a big challenge for the electronics because energy scavengers are only able to harvest  $100\mu$ W whereas current systems consume a factor of 50 to 1000 more power.

In this study, the lower limit of energy-efficient device operation is investigated to check if a device is able to run on scavenged energy. For this, a model is created to give insight of the power usage of all system components. The model is first verified to a state-of-the-art System On Chip (SoC), this verification is done using all major system components. The system component will be exchanged to check their impact on total power usage and to locate bottlenecks in the device. Different applications will have diverse bottlenecks on power consumption while running on the same SoC. While one application may use the major part of the energy budget for computation, others may dissipate most for transmitting the data wirelessly. The model must be able to accommodate such application dependent features.

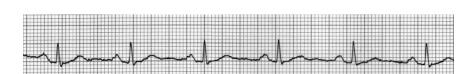

Figure 1.1: An ECG of a heart

This study focuses on electrocardiogram (ECG) applications to asses if it is possible to build a system able to run on scavenged energy. The results and underlying model can be readily reused to assess energy boundaries for other applications.

# 1.2 Wireless body sensors and ECG

The aging society lays a heavy burden on the economy nowadays. The number of patients needing care is increasing rapidly and this is overwhelming the the expensive care institution with work. To keep the cost of healtcare affordable, a shift from hospital-centric to remote care is needed. Remote healthcare needs Wireless Sensor Nodes (WSN) for remote monitoring and (in future) treatment. Next to long operation time and small dimensions, such WSN's must be extremely reliable and easy-to-use for (non-technical) patients and care givers. Examples of on-body worn monitors are temperature, blood pressure and ECG sensors. The latter will be discussed below because it is the focus of this study. Future treatment devices can also be placed inside the body, in this case artificial retina, pancreas and cochlear implants are made possible. In-body devices should work without batteries and use energy scavengers as power supply. The in-body WSN could save lives due to fewer operations needed for the patient. It could also change modern healthcare convenience to another level for patients, think for example about diabetic patients not needing to think about a shot of insulin after they have eaten or drunk something.

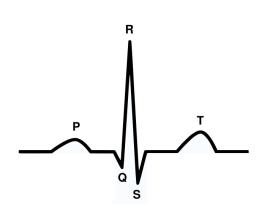

An ECG is the graphical representation of the electrical activity of the heart, as shown in Figure 1.1. It gives information about how the heart works and if any disorders are occurring. An important feature in the ECG is the QRS complex, seen in Figure 1.2, which shows the depolarization of the ventricles. The QRS is depicted in amplitude and duration. These parameters can be calculated by preparing the data first through (digital) filtering and beat detection, after which the QRS parameters can be easily extracted.

Figure 1.2: The QRS complex

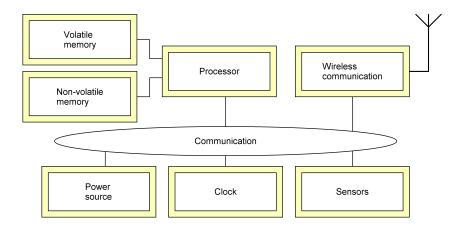

Figure 1.3: Architecture of a WSN

# 1.3 WSN architecture and power dissipation

This section describes the components from which a WSN is build. An architectural view is depicted in Figure 1.3 which shows the following components: processor with storage, wireless communication, sensors, real time clock generation, communication between the blocks and a power source. The storage is partly non-volatile memory to store the program and partly volatile memory for storing the data. State-of-the-art WSN SOC's, like the Chipcon 2430 (from now on is referred to as "Chipcon"), provide power modes in which one or more components are simultaneous active. To achieve low power consumption for a given application, efficient power modes needs to be enforced which basically aims to wake up only the required components while keeping all other components in deep sleep. The power consumption of component not being in deep sleep is unneeded. In a parallel study [8], low power operation at 5.60mW and 7.31mW is demonstrated on an ECG application build on a Chipcon 2430, transmitting RAW and QRS ECG data respectively. Figure 2.11 on page 33 depicts the underlying power usage which reveals wireless power dissipation can be relieved by sending local processed data instead of the RAW data.

# 1.4 WSN optimizations

This section gives insight into memory architectures and implementations, circuit implementation techniques and ends with the general expected result when an Integrated Circuit (IC) is scaled to another technology feature size. The most promising optimization techniques described in this section will be used to optimize the SoC in Chapter 3.

If feasible, battery less devices will undoubtedly have a huge potential. However, running without batteries has a big impact on the design of a system. Energy must be scavenged from the surrounding environment, implying that the system has very low power consumption. Current systems like the Chipcon 2430 are not capable to run solely on scavenged energy. Power optimizations need to be done to enable energy scavengers to completely power a WSN.

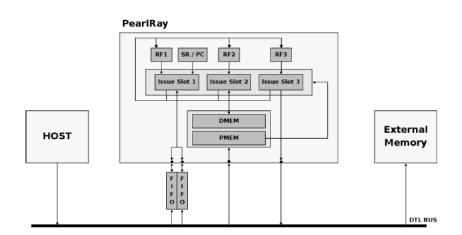

A lot of related research is currently done on battery- and wireless devices. However, these studies typically focus on one aspect of the device. In [3] for example, a Pearl processor is optimized for executing an ECG application, the software for this application is optimized in [4]. Other research focuses on energy scavengers [19], memory technology [16] [17] [18], radio technology (Philips), radio protocols [8], Analog to Digital Converters (ADC) [7] and clock generation [10]. The approach in the thesis is focused to get a global insight of the total power consumption of a complete SoC.

## 1.4.1 Memory architectures and implementations

Memory is needed to store the program being executed and program variables. We can distinguish different types of memory; volatile and nonvolatile.

Non-volatile memory can retain the stored information even when it is not connected to a power source. This type of memory is normally used to store the program of the device because no power is needed to retain the data. Various types of non-volatile memory exist but all have some sort of disadvantage; Read Only Memory (ROM) can only be written once while FLASH can be rewritten but only a limited amount of times.

Volatile memories, like Random Access Memory (RAM) needs power to retain the contents. RAM has the advantage of an unlimited amount of read/write cycles, making it ideal to store data used by the executed algorithm.

## Volatile memory

#### Filter cache

Large memories have a disadvantage over small memories; they consume more power and have a higher access time. Cache is used as an intermediate level because it uses less energy and time usage to access the data. Cache has copies of the data from the large memory. Disadvantage of the cache is that when the requested data is not available, time and energy is waisted in trying to get the data from the cache. The time penalty can be solved by setting up the regular memory transfer parallel with the cache, but only access the normal memory when the data is not available in the case. Solving the time penalty uses power and decreases the power savings of having a cache. The filter cache is a unusually small cache positioned between the core and the normal L1 memory of cache. A filter cache can save 58% power while the performance is reduced with 21%[12]. Other papers [13] show an average of 34% reduction in power while the performance reduction is less than 1%. On average, 15% of the requests to the filter cache result in a cache miss due to the small size. More about filter cashes can be found in [12], [13] and [14].

## Actively reducing memory size

A way to save power in the data memories is to reduce the size of the memory, this is possible if it is not completely utilized. A memory can be constructed out of multiple memories while logically it looks like one big memory. Every small memory block of this logical big memory is power gated as explained in section 1.4.2. To use this technique the programmer of the system must be aware of how much and what part of the memory can be powered down.

The programmer of the system might not be able to fully utilize this technique. To solve this, new cache technologies in [16] [17] [18], in here

they are investigated how to automatically disable memory parts which are not used.

### Non-volatile memory

#### FLASH endurance problem

FLASH is ideal to store instructions for the processor because it is able to retain the data without a power source and can be reprogrammed. With low DC systems it is an interesting idea to use FLASH also as data storage because it can be disconnected from the power source to save leakage energy which is used in SRAM to maintain the data. The endurance (which means the number of cycles a block or chip can be reprogrammed) for FLASH is however limited. Typically FLASH has an endurance of one million<sup>1</sup> erase/write cycles which limit the usage of FLASH as data storage. With this endurance and a rewrite frequency of for instance 1Hz, the one millionth erase/write cycle limit is reached after 11.6 days.

FLASH might be used when the data is rewritten on a much slower frequency, but this is not feasible for a many applications. Other current technologies, like Ferroelectric Random Access Memory (FRAM), have a higher endurance (10 billion rewrite cycles<sup>2</sup>) but cannot be integrated into a SoC at the moment of writing and is not investigated further for this reason.

#### FLASH versus ROM

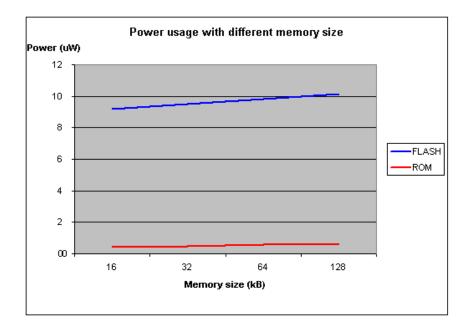

Non-volatile memory, like FLASH for instance, is needed to store the instructions of the device when it is not in use. A disadvantage of FLASH, being a high power consumption when active, can be solved by replacing it with ROM. The power usage of different memory sizes for FLASH and ROM are depicted in Figure 1.4. The drawback of ROM is that is can not be reprogrammed after fabrication. This limits the usage of ROM to high volume systems that are proven to work correctly. In this setting ROM has also another advantages over FLASH: it is a factor 2 to 5 times denser, reducing the cost of the device. Another advantage is, that ROM is available in the latest technology while FLASH is mostly lagging 2 feature sizes behind making it impossible to use the least power efficient technologies.

The advantage of being able to reprogram the FLASH will be traded to the lower power consumption of ROM in one optimization step executed in Chapter 3.

## 1.4.2 Circuit implementation techniques

### **Power gating**

Power gating is a technique where the leakage of a (sub)component in a system is decreased when it is not active by removing the power supply to

$<sup>\</sup>label{eq:source:toshiba:www.dataio.com/pdf/NAND/Toshiba/NandDesignGuide.pdf.pdf \end{tabular}$

Figure 1.4: The power consumption for FLASH and ROM running on 32MHz with a duty cycle of 1%.

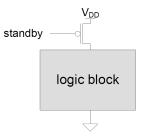

that component. An extra transistor is inserted between the power rail and the component to accomplish this, as shown in Figure 1.5. This technique can be applied for instance on the core of the processor when it is not active. External circuitry is needed to revive the processor. SRAM memories can also be power gated, however if done so, the contents will be lost when the supply voltage is removed.

The extra standby transistor will increase the active power consumption but this is neglectable with the power saved by this technique.

Threshold voltage of transistors: high  $V_t$  against normal  $V_t$

The way how a transistor is made influences the threshold voltage. The threshold voltage describes the point where the transistor starts conducting.

Figure 1.5: With the standby signal the logic block can be disconnected from the power rails, saving leakage when not used

A high threshold voltage will lead to less leakage when turned off, however it lowers the frequency at which the transistor is able to switch between states. If speed is not an issue, high  $V_t$  transistors should be used to save leakage.

To illustrate the difference in power consumption, a 8192 by 8-bit memory from [2] at 90nm is used. Both have the same active usage: 10 pJ/access, while the leakage is  $1.2 \mu\text{W}$  and  $11.3 \mu\text{W}$  for high V<sub>t</sub> and normal V<sub>t</sub> respectively.

## 1.4.3 IC technology scaling trends

Energy consumption can be differentiated into static and dynamic. Static energy is the leakage of transistors, while dynamic energy is induced by the switching of transistors and (dis-)charging of the capacity in the circuit.

The technology depended feature size will influence the power consumption of digital circuitry. A smaller feature size will decrease the dynamic power (also known as active power), while the static power (also known as leakage) increases. Scaling the active power consumption between different technologies can can be calculated with the next formula:

$$P_{active}^{new} = \left(\frac{V_{dd}^{new}}{V_{dd}^{current}}\right)^2 \cdot \frac{FeatureSize_{new}}{FeatureSize_{current}} \cdot P_{active}^{current}$$

(1.1)

## 1.5 Summary

Power hungry WSN need to be optimized before they can be powered with scavenged energy. This thesis focuses on a global insight and optimization of a complete WSN SoC by means of a model The created model must be able to predict the power difference of the optimizations discussed in this chapter. The variety of optimization is huge; from technology implementation to component and architectural decisions. The most promising energy saving techniques, if applicable, are used to optimize the SoC in Chapter 3.

# 2 Model description

TU/e

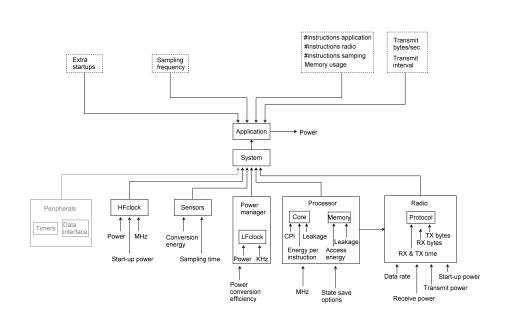

This chapter will describe how the WSN model is constructed. The model is parameterized in variables, the parameters together with the formulas explained in this chapter is the created model. The top view of the model, with all its subsystems, is depicted in Figure 2.3. The top view of the model will be explained before the explanation of the subsystem. The hardware of the WNS is divided into components which are specified by leakage, active energy and power consumption. In some cases, a duration of handling an event is added to the hardware description. The application will specify the activity of the components so that the energy consumption can be calculated.

The model is created in Microsoft Office Excel because this software package is widely used and known while it is still possible to expand the model for future use. It is build in a way that even non experienced Excel users can add new components. Excel offers the possibility to use Visual Basic for Applications (VBA), a programming language, so that even complex formula's can be composed. Another advantage of VBA is the possibility to add comments in the formula so that future users are able to understand what (and how) is calculated in the case they need to change or extend something.

The formulas used in this Chapter are constructed out of the next variables names followed by the explaination:

- P Power

- E Energy

- V Voltage

- I Current

- N Amount

- T Time

- au Fraction

- f Frequency

The rest of this section starts with explaining the application part of the model, followed by the explanation of the hardware components in the model. After the model is explained it will be trimmed in Section 2.3 to a System on Chip (SoC) to verify the model in Section 2.4. Fast readers go to the next chapter.

# 2.1 Application

The following list shows all application parameters to be set by the user:

- Amount of instruction for the application

- Amount of instruction for transmitting a radio packet (Medium Access Control, MAC)

- Amount of instruction for acquiring a single sample

- Amount of transmitted bytes per second

- Transmit interval

- Sampling frequency

- Extra high frequency crystal oscillator start up

- Level 1 Data memory activity

- Level 2 memory activity

- State save size

In Figure 2.1 the application parameters are named in the first row and the values for different systems are listen below that parameter. For instance, the "extra startups" apply to the high frequency crystal oscillator. This setting is made available to set extra startups of the processor to do application processing, which might not be triggered by a sampling or wireless communication event. The sampling frequency indicates obviously at what rate the sensor acquires data. Three different parameters can be given to state the amount of instructions the processor(s) has(have) to do, as indicated in Figure 2.1. The difference between them is when they are scheduled to execute. If the processor is needed to acquire a sample, for instance to copy the sample, it should be filled in at the amount of instructions needed to acquire one sample. The amount of instructions filled in for the sample will be multiplied with the sampling frequency of the sensor to come to the total

|                                      | 1         | Processor    | Extra     | Processor        | 1     |          |          | Radio processor  |            |               |                         |

|--------------------------------------|-----------|--------------|-----------|------------------|-------|----------|----------|------------------|------------|---------------|-------------------------|

|                                      | sample    | instructions | processor | instructions for |       | transmit | Transmit | instructions per | L1 Data    |               |                         |

| NAME                                 | frequency | for sampling | startups  | processing       | state | Byte/sec | interval | packet           | active use | L2 active use | System                  |

| OpD START                            | 200       | 726          | C         | 930892           | 0     | 11.0     | 1.1      | 113475           | 34         | 10            | Op0 START               |

| Op1 asynchronous 8051 (HS)           | 200       | 284          | 0         | 930892           | 0     | 11.0     | 1.1      | 19291            | 34         | 10            | Op1 8051(HS)            |

| Op2 asynchronous RISC (HS)           | 200       | 47           |           | 155149           | 0     | 11.0     | 1.1      | 4823             | 34         | 10            | Op2 RISC (HS)           |

| Op4 Pearl                            | 200       | 47           | 0         | 63845            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op4 Pearl               |

| Op5 Radio technology (ULP PRE)       | 200       | 47           | C         | 63845            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op5 Radio technology    |

| Op6 Protocol: (GTS Alex)             | 200       | 47           | 0         | 63845            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op6 Protocol            |

| Op8 Sensor                           | 200       | 12           | 200       | 63845            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op8 Sensor              |

| Op9 Batch,data ADC in private memory | 200       | 0            | 4         | 66248            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op9 Batch processing    |

| Op9b CLOCK                           | 200       | 0            | 4         | 66248            | 0     | 11.0     | 1.1      | 4823             | 100        | 0             | Op9b clock              |

| Op10 ROM                             | 1000      | 0            | 4         | 66248            | 0     | 11.0     | 1.1      | 4823             | 100        | 15            | Op10 memory optimizatio |

Figure 2.1: Snapshot of the input application worksheet

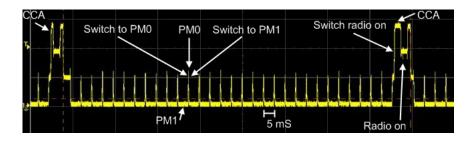

Figure 2.2: Current consumption of Chipcon in the "RAW" ECG application. Here, the device switches every 5ms from sleep mode (PM1) to active mode (PM0) to acquire a sample and wirelessly transmits groups of 32 samples

amount of executed instructions for sampling. The amount of instructions for radio processing will be multiplied with the amount of transmitted packets (called transmit interval) and executed on the processor selected by the radio (which can be another than the processor used for the application). All other instructions needed to be executed can be put at the amount of instructions for the application.

The usage of the different memories in the system depends on the application and must therefore be set in the model, a typical memory usage for data is 30%. The instruction memory is fully utilized for most processors and therefore it is automatically set to 100% active.

The state save size it the amount of data needed to be saved to L2 when the processor is power gated, how this works is explained further in Section 2.2.1.

Two parameters are used to describe the application side of the radio, transmit Byte/sec specifies how much data will be send wireless per second, while transmit interval specifies in how many packets per second this data will be put. The division in these two characteristics is needed to enable the packet rate to be easily changed without recalculating the amount of data transmitted per packet.

Figure 2.3: Model top view. Gray part are future extensions

# 2.2 System model

In Figure 2.2 the power consumption of a typical WSN is depicted, which the model must be able to predict. In this figure the power consumption of the Chipcon [1] is depicted when it executes the RAW ECG algorithm. The algorithm acquires samples that will be send by a radio. Figure 2.2 shows the different power consumptions of the Chipcon; PM1 where the processor is in sleep mode and PM0 where the processor is active.

The power consumption of the complete system will be modeled by the summation of the different system components in Formula 2.1.

$$P_{total} = P_{sensor} + P_{radio} + P_{processor} + P_{PM} + P_{HF} + P_{peripheral} (2.1)$$

The power of the different components used in Formula 2.1 can be decomposed into a summation of the different power modes of the component and the summation of the power used to switch between these power modes, as depicted in Formula 2.2. These two formulas can calculate the power used in Figure 2.2.

$$P_{\text{component}} = P_{\text{mode0}} + f_{\text{to \& from mode0}} \cdot E_{\text{switch}}^{\text{to and from mode0}} + P_{\text{mode1}} + f_{\text{to \& from mode1}} \cdot E_{\text{switch}}^{\text{to and from mode1}}$$

(2.2)

Figure 2.3 shows that the system is constructed out of components, which are subsequently divided in even smaller blocks. Take for instance the processor; it is constructed out of a core (which does the logical calculations) and memories(used to store the program and data). From Figure 2.3 it can

| Name                     | DSP                        | radio                             | Crystal                   | Sensor 1                            | Sensor 2 | Sensor 3 | PM             |

|--------------------------|----------------------------|-----------------------------------|---------------------------|-------------------------------------|----------|----------|----------------|

|                          | Opt 1 Pearl 🔻              | CC_rebuild TXCTL SR •             | PLL NXP C18PL160M         | Michiel Elzakker 10 bit CO 🔻        | none 🔻   | none -   | Opt6           |

| CC verification          | CC verification            | CC verification                   | PLL NXP C18PL160M         | 2430 ADC 10 bit verification        | none     | none     | CC verificatio |

|                          | 8051 Handsha -             | CC_org TXCTL SR -                 | Gautham 🔫                 | Michiel Elzakker 10 bit COt -       | none -   | none     | CC org         |

| system2                  | 8051 Handshake instruction | CC_org TXCTL SR                   | Gautham                   | Michiel Elzakker 10 bit C065        | none     | none     | CC org         |

| CC org PM2_SR            | CC org                     | CC_org TXCTL SR                   | PLL NXP C18PL160M startup | 2430 ADC 10 bit inclusief dc-dc     | none     | none     | CC org         |

| CC decomposed PM2_SR     | CC decomposed              | CC_decomposed TXCTL SR            | PLL NXP C18PL160M         | 2430 ADC 10 bit                     | none     | none     | CC decompo     |

| CC org QRS               | CC org                     | CC_org TXCTL SR                   | PLL NXP C18PL160M startup | 2430 ADC 10 bit inclusief dc-dc     | none     | none     | CC org         |

| CC decomposed QRS        | CC decomposed              | CC_decomposed TXCTL SR            | PLL NXP C18PL160M         | 2430 ADC 10 bit                     | none     | none     | CC decompo     |

| CC decomposed QRS star   | t CC decomposed            | CC_decomposed TXCTL SR            | PLL NXP C18PL160M         | 2430 ADC 10 bit                     | none     | none     | CC start       |

| CC verification2         | CC verification2           | CC verification2                  | verification              | verification 2                      | none     | none     | CC verificatio |

| Op0 START                | CC start                   | CC decomposed TXCTL SR            | verification              | verification 2                      | none     | none     | CC start       |

| Op1 8051(HS)             | 8051 Handshake instruction | 8051HS - Chipcon TXCTL SR         | verification              | verification 2                      | none     | none     | CC start       |

| Op2 RISC (HS)            | Async ARM 180nm            | ARM - Chipcon TXCTL SR            | verification              | verification 2                      | none     | none     | CC start       |

| Op4 Pearl                | Pearl                      | ARM - Chipcon TXCTL SR            | verification              | verification 2                      | none     | none     | CC start       |

| Op5 Radio technology     | Pearl                      | ARM - ULP Philips 180nm           | verification              | verification 2                      | none     | none     | CC start       |

| Op6 Protocol             | Pearl                      | ARM - ULP Philips GTS protocol 18 | verification              | verification 2                      | none     | none     | CC start       |

| Op7 clock WEGWEGWEG      | Pearl                      | ARM - ULP Philips GTS protocol 18 | verification              | verification 2                      | none     | none     | CC start       |

| Op8 Sensor               | Pearl                      | ARM - ULP Philips GTS protocol 18 | verification              | Michiel Elzakker2 10 bit C180       | none     | none     | CC start       |

| Op9 Batch processing     | Pearl + L2                 | ARM - ULP Philips GTS protocol 18 |                           | Michiel Elzakker2 10 bit C180 + MEM | (none    | none     | CC start       |

| Op9b clock               | Pearl + L2                 | ARM - ULP Philips GTS protocol 18 | Michiel Elzakker 180nm    | Michiel Elzakker2 10 bit C180 + MEN | Inone    | none     | CC clock       |

| Op10 memory optimization | Pearl + L2 + ROM +reduce   | ARM ROM- ULP Philips GTS protoc   | Michiel Elzakker 180nm    | Michiel Elzakker2 10 bit C180 + MEN | Inone    | none     | CC clock       |

Figure 2.4: Snapshot of the input system worksheet

also be seen that the radio uses a processor as a component. A processor is also used for the radio, this may or may not be the same processor used for application processing. The model enables to construct a system bottom-up by selecting subcomponents but also top-down by selecting already defined components in the system worksheet as shown in Figure 2.4. Every row in the worksheet is a complete system and all systems shown in the figure are used in chapter 3. Pull-down lists are available for the first 2 systems to enable fast top-down selection of components. In Figure 2.3 only one sensor is shown, the model is actually prepared to use different sensors, as depicted in Figure 2.4 with sensor1, sensor2 and sensor3. The model is made to be easily extended to multiple sensors (>3). Using these parameter together with the application specific parameters will enable teh model to predict the power usage.

In the coming sections the input parameters stated in Figure 2.3 will be explained in detail and the separate components in Formula 2.1 will be decomposed to parameters that are used in the model.

## 2.2.1 Processor

In this section it is first explained from what parts the processor is composed and which options exist to change the power behavior of the processor. With this basic knowledge the formula for the power consumption of the processor will be explained.

The processor is the main computing part of the system and can be used to fulfill many different tasks in the system. It can, for instance, copy data from a sensor or compute features from the already gathered (sensor) information.

The core will be specified by the average energy used per instruction, the leakage power and the cycles per instructions (CPI). The CPI specifies the average amount of clock cycles needed for a core to execute an instruction.

| Т | U | / | е |

|---|---|---|---|

|   |   |   |   |

| NAME                       | Core                        | L1 inst name                     | L1 data name                  | L2 name                | speed | L2 speed Save L1inst to |

|----------------------------|-----------------------------|----------------------------------|-------------------------------|------------------------|-------|-------------------------|

| CC decomposed              | CC decomposed, PM2          | 8192x8_180nm_SRAM_L1instr_Chipci | 8192x8_180nm_SRAM_Chipcon     | 8192x128_180nm_FLASH   | 32    | 32 Keep in L1inst       |

| 8051 Handshake instruction | 8051 Handshake              | CC verification2                 | CC verification2 data         | 8192x128_180nm_FLASH   | 9.2   | 32 Keep in L1inst       |

| Async ARM 180nm            | ARM996HS acynchr RISC 180nm | 4096x32 180nm SRAM               | 1024x32 180nm SRAM            | 8192x128 180nm FLASH   | 66.7  | 32 Keep in L1inst       |

| Pearl                      | Pearl optimized 180nm       | 2048x64_180nm_SRAM_PEARL         | 1024x16_180nm_SRAM_PEARL      | 8192x128_180nm_FLASH   | 32    | 32 Keep in L1inst       |

| Pearl + L2                 | Pearl optimized 180nm       | 2048x64 180nm SRAM PEARL slee    | 1024x16 180nm SRAM PEARL      | 8192x128 180nm FLASH   | 32    | 32 Keep in L1inst       |

| Pearl + L2 + ROM +reduce   | Pearl optimized 180nm       | 128x32_180nm_SRAM_sleep=no_leak  | 1024x16_180nm_SRAM_PEARL      | 4096x64_180nm_ROM      | 32    | 32 Keep in L1inst       |

| Async ARM ROM 180nm        | ARM996HS acynchr RISC 180nm | 128x32 180nm SRAM                | 1024x32 180nm SRAM            | no mem                 | 66.7  | 32 Keep in L1inst       |

| CC verification2           | CC verification2            | CC verification2                 | CC verification2 data         | 8192x128_180nm_FLASH v | e 32  | 32 Keep in L1inst       |

| CC start                   | CC start antimization       | CC worification?                 | CC varification? data no look | 9192v129_190nm_ELASH   | - 32  | 22 Keen in L1inct       |

Figure 2.5: Snapshot of the input processor worksheet

The CPI can be below 1, meaning that more than a single instruction can be executed within one clock cycle. This is possible if the core has multiple issue slots i.e.: a Very Long Instruction Word (VLIW) processor. The model is also able to work with asynchronous processors, these processors do not have a clock and therefore a CPI can not be specified. These processors commonly use a handshake protocol to synchronize for internal communication and may use a clock to communicate with external devices. To indicate the usage of an asynchronous processor in the model, the CPI must be set to zero and the frequency of the core must be set to the average amount of executed instructions per second (IPS).

The core alone, as already explained, is not enough to create a complete working processor. To create a processor the core has to be selected together with memories, as shown in Figure 2.5. The memories connected directly to the processor are called level 1 memories (L1) and there is also a possibility to connect a second level (L2) memory.

The L2 is optional and existence mainly depends on the size of the L1 or the power saving properties of a second level cache when used correctly. The memories can be selected from a pull down list, which refers to memories in the "Memory" worksheet, which is filled with embedded memory information from NXP [2]. The memories are characterized in the model by the energy needed for an access and by leakage power.

Next to the core and the memories some other options can be set for the processor: the frequency of the core (at this speed the L1 memories will also run), the frequency of the L2 memory and some state saving options, as depicted in Figure 2.5. When the processor is power gated, the core and/or memories are disconnected from the supply voltage, as explained in 1.4.2. No leakage of the core will be added to the power when the core is disconnected from the supply voltage. SRAM looses it content when it is disconnected from the power rail. To enable power gating for the memories the model is able to calculate the power associated with saving the contents of the L1 memories to the L2 memory when they are disconnected from the supply voltage. This saving can be set independently for instruction and data memory. The instruction memory could be erased if the data is still present in another memory, the complete memory must be saved if this is not the case. The L1 data memory holds the state of the processor, this does not need to be the complete size of the L1 data memory. The state size is given as an input and only this size needs to be saved to L2 before the memory is disconnected from the supply voltage.

A processor will use energy when switched from sleep mode to active mode, this can be specified as start-up energy of the processor.

The last option to set for the processor is the possibility to reduce the amount of active L2 in sleep mode. There are 2 possible options: the original memory is completely powered up, or only the part what is actually needed to store the data is powered up. No change is done to the memory when the original memory is used. Power gating on parts of the memory, as explained 1.4.1 will be applied when memory size needs to be reduced. The size of the memory that needs to be active to store the data is determined by if the L1instr needs to be saved and the amount in 'state' explained in the previous paragraph. The model itself will try to find a suitable memory size able to store the requested data.

With the basic knowledge of the processor the formulas for the processor can be explained. Formula 2.3 states how the total power of the processor is calculated. The sample frequency is multiplied with the amount of instructions, needed by the processor to acquire a sample, and energy per instruction. The processor needs to switch from a sleep state to the active state if there are any instruction needed by the processor to acquire a sample (N>0), this switching involves energy which is asses to every sample acquired. The extra instructions multiplied with the energy per instruction and the extra startups from the processor are added next. The amount of state saves, depending on the  $f_{\text{sample}} + f_{\text{switching}}^{\text{extra}} + f_{\text{transmit interval}}$ , is multiplied with the power used to save the state which is explained later on in this section. The leakage of the memories need to be split up between the sleep and active time because in the sleep time it could be the case that (a part of the) memories are power gated and thus do not leak. The leakage of the memories when the processor is in the sleep mode is determined by the state saving options  $\alpha$ ,  $\beta$  and  $\delta$  (zero if state saving is applied and one if state saving is not applied) whereas the duration of the sleep mode is the time that the processor is not active. The reduction in size of L2 will determine the  $P_{L2}^{leakage}$  when the processor is in sleep. Note that the power for processing the radio instructions is not in this formula. The power of the

radio processor is incorporated into the radio itself.

$$P_{\text{processor}} = f_{\text{sample}} \cdot \left( N_{\text{instr}}^{\text{sample}} \cdot E_{\text{instr}}^{\text{processor}} + (\text{if } N > 0) \cdot E_{\text{switching}}^{\text{powermodes}} \right) \\ + N_{\text{instr}}^{\text{extra}} \cdot E_{\text{instr}}^{\text{processor}} \\ + f_{\text{switching}}^{\text{extra}} \cdot E_{\text{switching}}^{\text{powermodes}} \\ + (f_{\text{sample}} + f_{\text{switching}}^{\text{extra}} + f_{\text{transmit interval}}) \cdot P_{\text{state save}} \\ + \left(1 - \frac{f_{\text{sample}} \cdot N_{\text{instr}}^{\text{sample}} + N_{\text{instr}}^{\text{extra}}) \cdot CPI}{f_{\text{core}}}\right) \\ \cdot \left(\alpha \cdot P_{\text{leakage}}^{\text{core}} + \beta \cdot P_{\text{L1instr}}^{\text{leakage}} + \delta \cdot P_{\text{L1data}}^{\text{leakage}}) \\ + P_{\text{L2}}^{\text{leakage}}$$

(2.3)

In Formula 2.4 the energy per instruction for the processor when active is stated. This is the summation of the energy per instruction of the core and energy per access on the memories (together with the power used in the bus), where  $\tau_{\text{Llinstr}}$ ,  $\tau_{\text{Lldata}}$  and  $\tau_{\text{L2}}$  determine activity fraction of the memories. The leakage per instruction is determined by the time of an instruction multiplied with the leakage power. The core and L2 can have different frequencies so the leakage of the core, L1instr and L1 data are multiplied with frequency of the core, while the leakage of the L2 is multiplied with it own frequency. The time of one instruction must be compensated in the leakage of the memories, this is done by the CPI.

$$\begin{split} \mathbf{E}_{\text{instr}}^{\text{processor}} &= \mathbf{E}_{\text{core}}^{\text{active}} + \tau_{\text{L1instr}} \cdot (\mathbf{E}_{\text{L1instr}}^{\text{active}} + \mathbf{E}_{\text{L1 instr bus}}^{\text{active}}) \\ &+ \tau_{\text{L1data}} \cdot (\mathbf{E}_{\text{L1data}}^{\text{active}} + \mathbf{E}_{\text{L1data bus}}^{\text{active}}) \\ &+ \tau_{\text{L2}} \cdot (\mathbf{E}_{\text{L2}}^{\text{active}} + \mathbf{E}_{\text{L2 bus}}^{\text{active}}) \\ &+ \frac{\text{CPI}}{f_{\text{core}}} \cdot \left(\mathbf{P}_{\text{core}}^{\text{leak}} + \mathbf{P}_{\text{L1instr}}^{\text{leak}} + \mathbf{P}_{\text{L1data}}^{\text{leak}}\right) + \frac{\text{CPI}}{f_{\text{L2}}} \left(\mathbf{P}_{\text{L2}}^{\text{leak}}\right) \quad (2.4) \end{split}$$

$$P_{\text{state save}} = \beta \cdot \frac{N_{\text{Bytes to save for L1instr}}}{N_{\text{L2 wordsize in bytes}}} \\ \cdot \left( E_{\text{L2}}^{\text{active}} + E_{\text{L1instr}}^{\text{active}} + \frac{f_{\text{processor}}}{f_{\text{L2}}} \cdot \frac{E_{\text{core}}^{\text{active}} + E_{\text{L1instr}}^{\text{active}}}{\text{CPI}} \right) \\ + \delta \cdot \frac{N_{\text{Bytes to save for L1data}}}{N_{\text{L2 wordsize in bytes}}} \\ \cdot \left( E_{\text{L2}}^{\text{active}} + E_{\text{L1data}}^{\text{active}} + \frac{f_{\text{processor}}}{f_{\text{L2}}} \cdot \frac{E_{\text{core}}^{\text{active}} + E_{\text{L1instr}}^{\text{active}}}{\text{CPI}} \right)$$

$$(2.5)$$

The energy spent for saving one state is depicted in Formula 2.5. This formula consists of two parts: one for the energy spent to save L1 instr

and the other for L1data. This division is done because state saving can be selected independent for both memories. The energy usage for state saving the memories is calculated the roughly the same for both memories; first the amount of write cycles to the L2 is calculated by dividing the amount of bytes needed to be saved by the word size of L2. This amount of write cycles is multiplied with the power needed to do one such write cycle: energy for L2 write, energy for reading L1instr or L1data, and the energy spend by the processor while the data is written back. The frequency of the processor and L2 can be different, as a compensation the energy spent by the processor and L1instr must be multiplied by the term  $\frac{f_{\text{processor}}}{f_{\text{L2}}}$ . This can be done because it is assumed that  $f_{\text{processor}} \leq f_{\text{L2}}$ . The amount of instruction needed to save the state is not only dependent on the frequency difference of the processor and the L2 bus also on the CPI. Dividing by the CPI brings the amount instructions back to the real executed instructions in stead of the difference of the frequencies. The processor is assumed to be able to fill the L2 word size every time it is written to L2. For asynchronous processors, having a CPI of zero, the CPI will be set to  $\frac{f_{\text{processor}}}{f_{\text{L2}}}$ , canceling out the earlier frequency term, this can be done due to the previous assumption.

If the model is set to reduce the amount of L2 during state save, the model substitutes the selected L2 by a smaller memory if available. If fore instance only 2kB of data needs to be saved and the memory is larger, a smaller memory is selected automatically from the memory list. The substituted memory must fulfill the next requirements: created in the same technology and having the same data width. This reduction in memory size is in the line of reducing the memories as a optimization stated in Section 1.4.1.

## 2.2.2 Radio

The radio is composed out of the radio technology, protocol and radio processor. The radio technology specifies the sleep, idle, transmit and receive current together with the supply voltage, data rate of the radio and the startup energy. Radios need a high frequency input clock with a specific accuracy. These last two parameters can be put into the radio part of the model but are not used, they only are added for completeness.

$$P_{radio} = f_{packet} \cdot \left( E_{protocol} + E_{payload} + E_{radio}^{processor} + E_{radio}^{startup} \right) + P_{radio}^{sleep}$$

(2.6)

Formula 2.6 is used to determine the power used by the radio; the packet frequency is multiplies with the energy of one packet which in turn is constructed out of the energy for the protocol, payload, radio processor and radio startup. If the radio consumes power while inactive, a sleep power is

added.

$$\begin{split} \mathbf{E}_{\text{protocol}} &= (\mathbf{T}_{\text{protocol}} \cdot \tau_{\text{protocol}}^{\text{RX}} + \frac{\mathbf{N}_{\text{bytes}}^{\text{RX overhead}}}{\text{link speed}}) \cdot \mathbf{P}_{\text{radio}}^{\text{RX}} \\ &+ (\mathbf{T}_{\text{protocol}} \cdot \tau_{\text{protocol}}^{\text{TX}} + \frac{\mathbf{N}_{\text{bytes}}^{\text{TX overhead}}}{\text{link speed}}) \cdot \mathbf{P}_{\text{radio}}^{\text{TX}} \\ &+ \mathbf{T}_{\text{protocol}} \cdot (1 - (\tau_{\text{protocol}}^{\text{TX}} + \tau_{\text{protocol}}^{\text{RX}})) \cdot \mathbf{P}_{\text{radio}}^{\text{tA}} \end{split}$$

(2.7)

Protocols are used to specify how different wireless nodes communicate with each other. All protocols add a specific overhead to the data needed to be send, which is depicted in formula 2.7. The packet overhead is divided into three parts: receive, transmit and idle. The part of the protocol that is independent of the link speed is specified with a total protocol time ( $T_{protocol}$ ) for the tree parts. The time for the tree parts is calculated by multiplying the total protocol time with the fraction of that part. The receive and transmit part of the protocol also have a link speed dependent piece which is specified in amount of bytes per part. The time of every part is calculated before it is multiplied with the power used for that part.

$$E_{payload} = \frac{N_{bytes}^{payload}}{link speed} \cdot P_{radio}^{TX}$$

(2.8)

The power used to transmit the payload is calculated by the number of payload bytes divided by the link speed and multiplied with the transmit power.

$$E_{radio}^{processor} = N_{MAC \ instr}^{processor} \cdot E_{instr}^{processor}$$

(2.9)

For every transmitted packet a certain amount of instructions is needed by the radio processor. The  $E_{instr}^{processor}$  in Formula 2.9 is calculated by Formula 2.4 with the values of the radio processor, except for the power of the L2 memory. If the radio processor is a different processor than the application processor the L2 will be shared between the two processors. The L2 for the radio processor is ignored and the values of the application L2 processor are used for the radio processor.

## 2.2.3 Sensors

To characterize the sensors, active and sleep power, duration per event (in case of an ADC this is the time it takes to acquire one sample) and start-up energy should be given, as depicted in formula 2.10.

$$P_{\text{sensor}} = f_{\text{sensor}} \cdot (T_{\text{sensor}}^{\text{duration}} \cdot P_{\text{sensor}} + E_{\text{sensor}}^{\text{startup}}) + P_{\text{sensor}}^{\text{sleep}}$$

(2.10)

$f_{\text{sensor}}$  in formula 2.10 is an application dependent frequency and is not set in the hardware profile of the sensor. It is possible to enter the minimal required

input clock. If the minimal input clock is set to 0, the high frequency crystal oscillator is not activated for the duration of the event, in all other cases the clock is started and continues to run for the duration of the event.

## 2.2.4 Peripherals

Peripherals in the system are components like timers, data interfaces (UART and IO-pads) or others. The peripherals are a future extension to the model, as depicted in Figure 2.3 in gray.

## 2.2.5 Clock

The clock generation can be specified supply voltage, active-(and) start-up ampere and startup time. The clock drives a clock net that consumes power which is modeled by the frequency of the clock multiplied with energy needed for one complete clock cycle. From these parameters the energy used by the high frequency oscillator can be calculated when the startup frequency and the Duty Cycle (DC,  $\tau_{\rm HF}$ ) is known, as depicted in Formula 2.11. The accuracy is also given as an input for completeness, but not used in the calculations of the model.

$$P_{HF} = f_{\text{startup}} \cdot E_{\text{HF}}^{\text{startup}} + \tau_{\text{HF}} \cdot \left(P_{\text{HF}}^{\text{active}} + f_{\text{clock}} \cdot E_{\text{clock net}}^{\text{switch}}\right) \quad (2.11)$$

The startup frequency is the addition of three components: sensor, radio and extra startups.  $\xi$ ,  $\psi$  and  $\zeta$  for the sensor time are booleans specifying if the high frequency crystal oscillator needs to be active for sensor1, sensor2 or sensor3 respectively.

$$f_{\text{startup}} = (\xi \text{OR}\psi \text{OR}\zeta) \cdot f_{\text{sensor}} + f_{\text{radio}} + f_{\text{extra}}$$

(2.12)

The DC of the high frequency crystal oscillator is an addition of three factors: sensor time, radio time and extra processing time.

$$\tau_{\rm HF} = f_{\rm sensor} \cdot {\rm MAX} \left[ (\xi \cdot {\rm T}_{\rm sensor1}), (\psi \cdot {\rm T}_{\rm sensor2}), (\zeta \cdot {\rm T}_{\rm sensor3}), \left( \frac{{\rm N}_{\rm instr}^{\rm sensor} \cdot {\rm CPI}}{f_{\rm processor}} \right) \right] + f_{\rm packets} \cdot {\rm MAX} \left[ \left( \frac{{\rm N}_{\rm instr}^{\rm radio} \cdot {\rm CPI}}{f_{\rm processor}} \right), ({\rm T}_{\rm protocol} + {\rm N}_{\rm bytes}^{\rm payload} \cdot {\rm linkspeed}) \right] + \frac{{\rm CPI}}{f_{\rm processor}} \cdot {\rm N}_{\rm instr}^{\rm processor}$$

(2.13)

The sensor time is the maximum duration of the different sensors and the processor time. The maximum time of the processor and radio transmission is used to calculate the time that the high frequency crystal oscillator is active for the radio part.  $T_{protocol}$ ,  $T_{packet}^{RX \text{ overhead}}$ ,  $T_{packet}^{TX \text{ overhead}}$ ,  $T_{packet}^{ille \text{ overhead}}$ ,  $N_{bytes}^{ille \text{ overhead}}$ ,  $N_{bytes}^{RX \text{ overhead}}$  and linkspeed depends on the same variables used in Formula 2.6. The last part in Formula 2.13 determines the DC used to execute the extra instructions by multiplying the time for one instruction with the amount of instructions.

## 2.2.6 Power manager

To stabilize and convert the input power supply to the correct voltage a  $DC:DC^1$  converter is used. The efficiency of the converter can be put into the model, which is used to adjust all the power drawn in the system.

The power manager includes a continuously running crystal oscillator, this typically runs at a low frequency to save power and it is used to schedule global events in the system. The used crystal oscillator can be selected from the clock worksheet in the model. Therefore it has the same input parameters specified as in the section 2.2.5, however the startup power is not used because it is continuously running. Formula 2.14 states how to calculate the power for this crystal oscillator.

$$P_{\rm LF} = V_{\rm oscillator} \cdot I_{\rm oscillator} \qquad (2.14)$$

Formula 2.1 on page 15 that states to total power used in the system is changed to Formula 2.15 due to the  $P_{total}$  being influenced by efficiency of the DC:DC converter. Next to the efficiency change,  $P_{PM}$  in Formula 2.1 is changed to LF in the new formula because it is the power drawn by the power manager.

$$P_{total} = \frac{P_{sensor} + P_{radio} + P_{processor} + P_{LF} + P_{HF} + P_{Peripheral}}{efficiency} (2.15)$$

# 2.3 Model calibration on Chipcon 2430 SoC

In this section the instruction count of two applications, executed on the Chipcon, are determined. Next, the hardware parameters of the Chipcon components are calculated.

## 2.3.1 Estimation of instruction count

The first application is the RAW ECG application where two main functions are executed:

- 1. Acquiring ECG samples at 200Hz

- 2. Wireless transmission of groups of 32 sample values

Measurements on the Chipcon are done with an oscilloscope to determine the time needed to handle a job. The time can be determined very accurate because a led on the Chipcon platform can be toggled at the start and end of a function. The led can be monitored with one of the leads of the

$<sup>^{1}\</sup>mathrm{An}$  on-chip DC:DC converter is mostly constructed out of an Low Drop-Out regulator

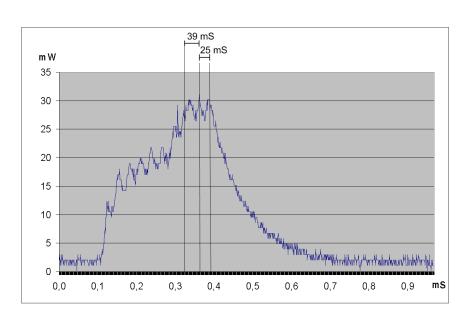

Figure 2.6: Measurement of taking a sample

oscilloscope. The measured time can be converted into instruction count by using the clock frequency and the CPI as illustrated in Formula 2.16.

$$N_{\text{instructions}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

(2.16)

Figure 2.6 shows a measurement when taking a sample. In this figure, the Chipcon first has to wakeup from a low power mode before it can acquire a sample. The processor of the Chipcon is active for the duration of acquiring a sample (39µs), after which it needs 25µs to process the sample. The frequency of the Chipcon processor is 32MHz, and the CPI is 2.82 as determined in Appendix B, the amount of instructions per sample is determined to be 726 by using Formula 2.17. The 726 instructions is listed in the first row of Table 2.1.

$$N_{\text{instructions}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

$$= (39\mu\text{s} + 25\mu\text{s}) \cdot \frac{32\text{MHz}}{2.82} = 726[1/\text{sample}] \qquad (2.17)$$

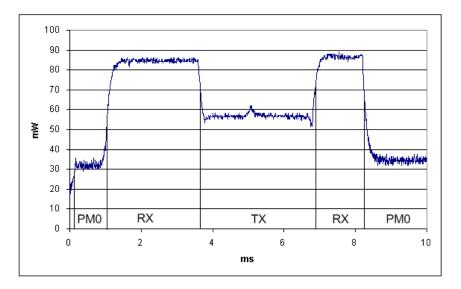

The measurement of a wireless transmission is shown in Figure 2.7. First the Chipcon does a part of the MAC processing in active mode (PM0) and then activates the radio in the receive mode (RX), followed by transmitting data (TX) and receiving the acknowledge (RX). After a packet is transmitted the processor stays in PM0 until the next sample is taken. It is needed to stay in PM0 because when a power down sequence on the Chipcon is activated (after a packet has been completely transmitted) and the wake-up timer is

|         | Sampling     | QRS extract        | MAC                              | Total instructions <sup>a</sup> |

|---------|--------------|--------------------|----------------------------------|---------------------------------|

|         | instr/sample | $\mathrm{instr/s}$ | $\mathrm{instr}/\mathrm{packet}$ | $\mathrm{instr}/\mathrm{s}$     |

| RAW ECG | 726          | -                  | 113475                           | 854419                          |

| QRS ECG | 726          | 930892             | 113475                           | 1200915                         |

Table 2.1: Summary of instruction count per function and second

$^a\mathrm{With}$  a sampling rate of 200Hz and a sampling rate of 6.25Hz for RAW ECG and 1.1Hz for QRS ECG

Figure 2.7: Power usage for transmission of a wireless packet

triggered (to acquire a new sample), the Chipcon goes to an undefined state where it stops responding. This causes the Chipcon to stay active for the wireless transmission in multiples of 5ms (which corresponds to the period of 200Hz sampling rate). The wireless transmission takes roughly 8ms, so the processor is active for 10ms. The amount of instructions used to transmit a single packet, as stated in Table 2.1, is calculated by formula 2.18.

$$N_{\text{instructions}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

$$= 10 \text{ms} \cdot \frac{32 \text{MHz}}{2.82} = 113475 [1/\text{packet}] \qquad (2.18)$$

The total amount of instructions per second for the RAW ECG application is calculated by formula 2.19 and listed in Table 2.1.

$$N_{\text{instructions}}^{\text{per second}} = f_{\text{sample}} \cdot N_{\text{instr}}^{\text{sample}} + f_{\text{packet}} \cdot N_{\text{MAC instr}}^{\text{processor}}$$

(2.19)

$$= 200 \text{Hz} \cdot 726 \text{instr} + 6.25 \text{Hz} \cdot 113475 \text{instr}$$

$$= 854419 [1/\text{second}]$$

Figure 2.8: Power usage for transmission of a wireless packet

A sample frequency of 200Hz and transmitting packets containing 32 samples leads to a transmit interval of 6.25Hz. Since the application adds eight bytes per packet to the payload and every sample is represented in 2 bytes, the total amount of data send per second is: 6.25 packets/s  $\cdot$  (32  $\cdot$  2bytes + 8bytes) = 450 bytes per second which needs to be put in the model at the application worksheet under the name 'Amount of transmitted bytes per second'.

The second application is an ECG parameter extraction algorithm. Calculating the parameters is done by computing the QRS times of a heart beat, more details how the algorithm works can be found in [4]. The input of the algorithm are samples taken from the heart and the output is a 10 byte packet transmitted by the radio for every heart beat. The same amount of instruction are needed for acquiring the samples and transmitting a packet, which can be seen in Table 2.1.

A measurement of calculating the QRS parameters can be seen in Figure 2.8. The calculation of the QRS parameters involves three parts:

- 1. Filter the data at 200Hz

- 2. Beat detection at 4Hz

- 3. Calculate QRS parameters at heartbeat frequency

The measurement indicates that the filter function and beat detection takes 269µs and 2987µs respectively and the amount of instructions is calculated by formula 2.20 and 2.21.

$$N_{\text{instructions}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

$$= 269 \mu \text{s} \cdot \frac{32 \text{MHz}}{2.82} = 3052 [1/\text{sample}] \qquad (2.20)$$

$$N_{\text{instructions}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

$$= 2987 \mu \text{s} \cdot \frac{32 \text{MHz}}{2.82} = 33895 [1/250 \text{ms}] \qquad (2.21)$$

The duration of calculating the QRS parameters takes so long that three new samples are acquired and filtered in the mean time. The duration of acquiring and filtering these samples need to be subtracted from the measured duration of QRS parameter calculation. The measured time of the QRS parameter is 18.8ms, which besides the acquiring and filtering of the samples also includes the beat detection while need to be subtracted. The amount of instructions is for calculating the QRS parameters is stated in Formula 2.22.

$$N_{\text{instructions}}^{\text{QRS extract}} = T_{\text{measured}} \cdot \frac{f_{\text{HFoscillator}}}{\text{CPI}}$$

$$= (18.8\text{ms} - (3 \cdot (39\mu\text{s} + 25\mu\text{s} + 269\mu\text{s}) + 2987\mu\text{s}))$$

$$\cdot \frac{32\text{MHz}}{2.82} = 168102[1/\text{heart beat}] \qquad (2.22)$$

Knowing the average beat per minute, which is assumed to be 66 bpm (=1.1Hz) it is possible to calculate the total executed instructions per second for the QRS parameters, as illustrated by Formula 2.23 and listed in Table 2.1.

$$N_{\text{instructions}}^{\text{QRS total}} = 200 \text{Hz} \cdot 3052 + 4 \text{Hz} \cdot 33895 + 1.1 \text{Hz} \cdot 168102 \quad (2.23)$$

$$= 930892[1/\text{second}]$$

The total amount of instructions per second needed to do the QRS extraction is calculated in Formula 2.24, which is based on Formula 2.19 but an extra term is added for the extra instructions used for the QRS parameter extraction, and is also listed in Table 2.1, in this formula the packet rate is the same as the frequency of the heartbeat.

$$N_{\text{instructions}}^{\text{total}} = f_{\text{sample}} \cdot N_{\text{instr}}^{\text{sample}} + f_{\text{instr}}^{\text{extra}} \cdot N_{\text{instr}}^{\text{QRS total}} + f_{\text{packet}} \cdot N_{\text{instr}}^{\text{MAC}} (2.24)$$

$$= 200 \text{Hz} \cdot 726 + 1 \text{Hz} \cdot 930892 + 1.1 \text{Hz} \cdot 113475$$

$$= 1200915 [1/\text{second}]$$

Ten bytes are transmittes per packet. The frequency of the heartbeat is 1.1Hz and this is therefore also the packet frequency. The amount of bytes transmitted per second is  $1.1\text{Hz} \cdot 10$  bytes = 11 bytes.

## 2.3.2 Estimation of component power

The power consumption of individual Chipcon components is not listed in the Chipcon datasheet[1] and, unfortunately, can not be directly derived from measurements. In this section, literature, measurements and the Chipcon datasheet will be used to estimate the power of all components of the Chipcon. The Chipcon has several Power Modes (PM), where PM0 is the active mode and PM1, PM2 and PM3 are sleep modes, where only parts of the Chipcon are active. PM0 and PM1 are measured to be 27.18mW and 1.05mW respectively. PM1 includes Power on reset (POR), sleep timer (ST), a kHz crystal oscillator, leakage of the digital part of the system including SRAM memories.

$$P_{PM0}^{\text{measured}} \cdot \text{LDO}_{\text{Efficiency}} = P_{PM1}^{\text{measured}} \cdot \text{LDO}_{\text{Efficiency}} + P_{\text{clock net}}^{32\text{MHz}} + P_{32\text{MHz Xosc}} + P_{\text{peripheral}}^{\text{active}} + P_{\text{Leakage}}^{\text{ELASH}} + P_{\text{mem}}^{\text{active}} + P_{\text{core}}^{\text{active}}$$

$$(2.25)$$

PM0 of the Chipcon equals the power drawn in PM1, 32MHz clock, the clock net, peripherals, FLASH leakage, power use in active memory and the power in the core. The measured PM0 and PM1 need to be corrected by the DC:DC efficiency before they can be used in Formula 2.25. The power consumption for all these parts will be determined.

The DC:DC converter, implemented as a Low Drop Out (LDO) regulator, has a conversion efficiency depicted in Formula 2.26, where the input voltage is 3V, the output voltage is 1.8V and the conversion efficiency  $\theta$  is set to 100%.

$$LDO_{Efficiency} = \frac{V_{out}}{V_{in}} \cdot \theta$$

(2.26)

The power of the clock net can be calculated by Formula 2.27.

$$P_{\text{clock net}} = f \cdot C \cdot V^2 \qquad (2.27)$$

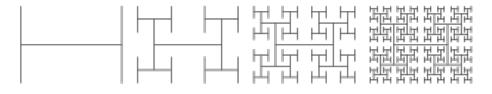

The clock net is commonly constructed out of an H-tree, as illustrated in Figure 2.9, because it ensures an equal propagation delays to each end point of the tree. Every inner buffer in the H-tree powers 4 buffers toward the end of the tree. The total amount of buffers in the H-tree can be calculated by Formula 2.28, where L is the amount of levels in the tree. The amount of

Figure 2.9: H-tree of levels two to five

end buffers in the H-tree is calculated with Formula 2.29.

$$N_{\text{buffers}}^{\text{total}} = \sum_{0}^{L-1} 4^L \qquad (2.28)$$

$$N_{\text{buffers}}^{\text{end}} = 4^{L-1} \tag{2.29}$$

It is assumed that there are 5 levels in the Chipcon clock net, bringing to total buffers in the clock net to 341. Every end buffer is assumed to drive eight Flip-flops and the average wire length per buffer and to the Flip-flops is 0.3mm. A input capacitance of a buffer and Flip-flop in 180nm is 4.7fF and the wire capacitance 100fF/mm, both values come from a NXP library. The total capacitance for the clock net is calculated by Formula 2.30 by multiplying the amount of gates with the capacity per gate.

$$C = (341 + 256 \cdot 8) \cdot (4.7 \text{fF} + 0.3 \text{mm} \cdot 100 \text{fF/mm})$$

(2.30)

= 82.9 pF

The total power of the  $P_{clock net}$  can be calculated with Formula 2.27, which leads to 8.60mW with a clock frequency of 32MHz and a supply voltage of 1.8V.

Power consumed by the 32MHz crystal oscillator can be extracted from the Chipcon datasheet; the processor running with low activity on a 16MHz RC-oscillator consumes 7.74mW. With the same low activity but now on 32MHz it consumes 17.1mW, the frequency is generated with a crystal oscillator. The active part of the processor scales linear with the frequency, so if the static energy (indicated with PM1) is subtracted it is possible to calculate the power consumed by the crystal oscillator because the power used by the RC-oscillator can be neglected, as depicted in Formula 2.31.

$$P_{32MHz \ Xosc} = \left(P_{PM0}^{32MHz} - P_{PM1}\right) \\ - \left(\frac{32MHz}{16MHz} \cdot \left(P_{PM0}^{16MHz} - P_{PM1}\right)\right)$$

(2.31)

$$= \left(17.1 \text{mW} - 342 \mu \text{W}\right) \\ - \left(\frac{32MHz}{16MHz} \cdot \left(7.74 \text{mW} - 342 \mu \text{W}\right)\right) \\ = 1.962 \text{mW}$$

This power consumption is inline with measurement performed in a similar manner that point to 2.5mW. Difference might be due to different devices.

$P_{peripheral}$  in Formula 2.25 is set to zero because it is assumed to be negligible.

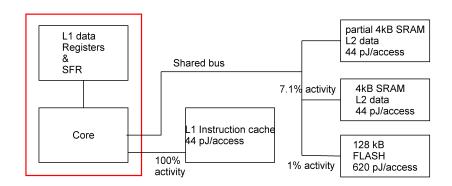

From the Chipcon datasheet it is know that three different memories are used; two 4kB SRAMs, one 128kB FLASH and internal registers of the core, as illustrated in Figure 2.10. One 4kB SRAM is partially used in the register and the SFR register and it is unsure if it is also used for the instruction cache. The Chipcon datasheet states that both SRAM memories are build with high V<sub>t</sub> memory technology. Using the memory estimator from NXP[2] the energy per access and leakage will be approximated for the memories

Figure 2.10: Chipcon core with memories and buses activity

interpreted in the Chipcon. A 4kB ultra low power SRAM uses 44pJ/access and leaks 180nW, embedded FLASH uses 620pJ/access and leaks 405µW. The leakage of both SRAM memories are already included into PM1 and are therefore already subtracted from the Chipcon power, the leakage of the FLASH is not included in PM1 and is directly subtracted in Formula 2.25 from PM0. FLASH is used to store the instruction for the processor, it is stated in the Chipcon datasheet that there is a cache between the FLASH and the processor. The size of this cache is unknown and it is assumed that it is byte addressable because the instruction width of the processor is one byte, further it is assumed that it has the same active power as a 4kB SRAM From [15] it is known that an typical instruction cache has a miss rate of 1%. which in term is used as the activity of the FLASH. The 8051 has internal registers and we assume that the power in these registers are included in the power of the core, as illustrated with a red box in Figure 2.10. The internal registers are L1 data for the core, the L2 data for the core is the 4kB SRAM. Because the registers are included in the core, the name of the L2 data in the model will be L1 data.

The power of the memories is calculated in Formula 2.32, which is partially derived from Formula 2.4: the amount of instructions per second multiplied with the power of the memories used for every instruction.

$$P_{MEM}^{active} = \frac{\text{instruction}}{\text{second}} \cdot \left( \tau_{\text{instr cache}} \cdot \left( E_{\text{instr cache}} / acc + E_{\text{bus}}^{\text{instr cache}} \right) + \tau_{\text{external data}} \cdot \left( E_{\text{external data}} / acc + E_{\text{bus}}^{\text{external data}} \right) + \tau_{\text{FLASH}} \cdot \left( E_{\text{FLASH}} / acc + E_{\text{bus}}^{\text{FLASH}} \right) \right)$$

(2.32)

In most processors the activity of the L1instr is around 100% because every execution of an instruction involves fetching the instruction. One instruction fetch on the 8051 is 1 byte, but because some instructions of the 8051 uses multiple bytes for one instruction the activity will be more than 100 %. In appendix B it is shown that on average 1.46 bytes are used for an instruction,

leading to a 146% activity to the L1instr cache. The data memory activity is determined to be 7.1% by counting the amount of MOVX instructions that refer to external memory divided by the total amount of instructions used for the filter code of the QRS application.

Formula 2.33 calculates the energy per bus transaction, which is the width of the bus multiplied with the capacity and squared voltage. Not all wires in a bus change per transaction, it is assumed that 2/3 of the wires actually changes state and thus consume power.

$$E_{\text{bus}}^{\text{transaction}} = N_{\text{bus width}} \cdot \frac{2}{3} \cdot C_{\text{wire}} \cdot V^2 \qquad (2.33)$$

The capacity of a wire in Formula 2.33 can be calculated by multiplying the amount of gates per wire with the gate capacity and adding the capacity of the wire, as depicted in Formula 2.34.

$$C_{wire} = N_{gates}^{per wire} \cdot C_{gate} + L_{wire} \cdot C_{per L}$$

(2.34)

The bus from the core to the instruction cache has a width of 8 bit and is a dedicated bus, meaning that it only has 2 gates per wire, assuming a bus length of 0.2mm the energy per bus transaction is 508fJ, calculated by using Formula 2.34 and 2.33. The bus to the FLASH and external data memory is shared, meaning that a lot of gates are connected to every wire. The width of the FLASH is 32-bit an therefore the bus has the same width. A bus transaction consumes 7.9pJ assuming a bus length of 0.2mm and 20 gates per wire, calculated by Formula 2.34 and 2.33.

All values are know to fill in Formula 2.32 to calculate the power used by the memories:

$$P_{MEM}^{active} = \frac{32 \text{MHz}}{2.82 cpi} \cdot (1.46 \cdot (44 \text{pJ} + 508 \text{fJ}) + 0.071 \cdot (44 \text{pJ} + 7.9 \text{pJ}) + 0.01 \cdot (620 \text{pJ} + 7.9 \text{pJ})) = 850 \text{uW}$$

$P_{core}$  can be calculated because all other term in Formula 2.25 are known, this leads to a 3.86mW. The power of the core can be converted in to energy per instruction by Formula 2.35.

$$E/\text{instr} = P_{PROC}^{active} \cdot \frac{\text{CPI}}{f_{\text{core}}}$$

$$= 3.86 \text{mW} \cdot \frac{2.82}{32 \text{MHz}}$$

$$= 340 \text{pJ/instr}$$

(2.35)

As a reference, Handshake Solutions uses a reference 8051 consuming 500 pJ/instr<sup>2</sup> which most likely involves a version not fully optimized for ultra low power.

<sup>&</sup>lt;sup>2</sup>Source: Handshake Solutions

The start-up power is measured to be  $6.3\mu$ J. The radio power for both transmit and receive is measured to be 55.32mW, while the sleep power of the radio is zero due to power gating. The measured power should be adjusted with the DC:DC efficiency (Formula 2.26) before they are put in the model. The protocol times are derived from Figure 2.7 which the help of the work in [8], these times include switching between the radio modes and thus the power consumed for switching between the radio modes.

PM1 includes Power on reset (POR), sleep timer (ST), a kHz crystal oscillator, leakage of the digital part of the system and memory leakage due to data retention of both SRAM memories. Power involved in PM1 must be split up before it can be put in the model. The leakage of the SRAM memories is already covered in the memories itself. The kHz clock dissipation can not be measured because the power consumption is so low that is falls below the measure accuracy. It is assumed the the clock uses 396nW which is the power consumed by an EM microelectronic[9] crystal oscillator also running on 32kHz. POR power can be extracted from the Chipcon datasheet: 360nW. ST and peripherals are assumed to consume 500 nW and  $10.5 \mu \text{W}$  respectively. The power of the digital leakage can than be calculated by subtracting all other parts from the PM1 power usage:  $1.05 \text{mW} \cdot \frac{1.8}{3} - (180 \text{nW} + 180 \text{nW} + 396 \text{nW} + 360 \text{nW} + 500 \text{nW} + 10.5 \mu \text{W}) = 0.05 \text{mW} + 10.5 \mu \text{W}$ 617.9mW. Note that the first two terms are the leakage the SRAM memories, which do need to be subtracted from PM1 to come to the leakage of the digital part.

The Chipcon datasheet specifies a consumption of 3.6mW for the ADC, this needs to be corrected with the DC:DC efficiency before it is put in the model.

# 2.4 Model Validation on Chipcon 2430 SoC

In Section 2.3.1 the amount of instructions is determined. The power usage of the Chipcon components is determined in a static way in Section 2.3.2. The model will estimate the dynamic power consumption of the Chipcon with the two above stated inputs.

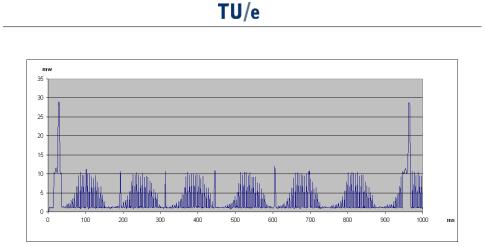

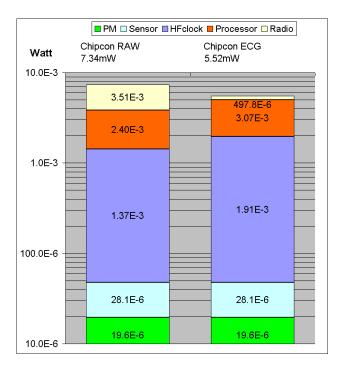

The first application transmits the RAW ECG samples. The model predicts a power usage of 7.34 mW, as illustrated in Figure 2.11. Measurement indicates that the Chipcon uses 7.31 mW, a 0.4% difference to the model.

The second application that calculates the QRS parameters and transmits the QRS parameters wireless is predicted to use 5.52mW by the model, as illustrated in Figure 2.11 and was measured to use 5.60mW, which is a 1.4% difference.

A possible reason for the difference between the model and the measurement is the CCA time of the protocol. The CCA time is determined for every packet by a random variable, causing the measurement of the Chipcon

**Figure 2.11:** Power breakdown of RAW data and QRS parameter extraction. Note the logarithmic axis

to be non deterministic. The result of the random variable can be seen in Figure 2.2 on page 14. Two transmitted packets are illustrated in the figure, the first has a short CCA time, while the second has a long CCA time. The difference between the measurements and predictions of the model is small enough to state that the model works correctly.

From Figure 2.11 it is already possible to see that different applications have different power bottlenecks. This insight is made possible by the model due to dividing the power in components. Most power in the RAW mode is consumed by sending the data wireless By processing the data locally, as in the case of the QRS algorithm, more energy is evidently used for processing but this is compensated by bigger reduction in energy needed to transmit the data wireless. The next chapter will start with optimizing the biggest power consumer: the processor.

# 2.5 Summery