# **MASTER**

The control of a digital copier based on the Intel 80960SA

Manrique Lizarraga, Jose de Jesus

Award date: 1995

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Faculty of Electrical Engineering Section of Digital Information Systems

Master's Thesis:

# The control of a digital copier based on the Intel 80960SA risc processor.

José de Jesús Manrique Lizárraga.

Coach

: Ing. Cees van Tilborg (Océ)

Ir. Hans Wierink (Océ)

Supervisor: Prof. Ir. M.P.J. Stevens

Period

: August 1994 - February 1995

"le coeur a des raisons que la raison ne connaît pas" **Pascal**

#### Abstract.

CISC (Complex Instruction Set Computer) processors have been used in embedded applications since the introduction of the microprocessor, mainly because of its flexibility. Low cost solutions can be achieved when the peripherals are integrated into the microprocessor chip to form a microcontroller. During the last decade another kind of processors has been developed to respond to the increasing demand of performance, from those applications of intensive data manipulation like a workstation: The RISC (Reduced Instruction Set Computer) processor.

There are different implementations of RISC, every producer has its own architecture. The common features are the use of cache memory for those pieces of code and data that are often used by the processor, and the substitution of microcode by hardwired techniques. These characteristics have proven to boost the performance of the conventional processor, but imply a certain degree of uncertainty or non deterministic behaviour which might affect negatively the operation of real time applications.

Certain applications of the embedded sector, that also require high performance for intensive data processing, have taken advantage of the RISC developments, an example is a laser printer. But in real time systems, which are interrupt driven, the context switching can make the effectiveness of the RISC approach less notorious.

Even though, the combination real time and RISC is not an obvious one, those RISC processors that are used in the industrial sector offer other benefits like long term availability and often more performance when compared to the existing CISC processors and microcontrollers.

This work deals with the implementation of the control of a digital copier based on the Intel 80960SA RISC processor, a member of the i960 family of embedded processors. This processor offers the benefits of RISC, but its internal facilities have been simplified (no MMU, no FPU) as well as the external data bus (16 bits multiplexed address/data bus), which makes the processor interesting for low cost applications.

The control of a digital copier is a multitask real time system. Because of its digital character, more functionality is available than with the analog counterpart. Furthermore, the copier can behave like a printer or like a scanner. This makes possible the integration of the copier (or portions of it) in other environments. To cope with all this, there is an increasing performance demand of the control unit of the machine.

Several hardware architectures are considered in order to find a soluition that shortens the time to market. An implementation for the short term start of production is given as well as a development plan for the future versions.

One important engineering trade-off is the integration of the control panel into the control unit. By doing this, the price of the system is maintained low, but this will increase the required processor power, because the control unit will be in charge of generating and manipulating bitmaps for a graphic Liquid Crystal Display.

Because RISC may involve risks in real time applications, an analysis of the extent of these problems is given. An important conclusion is that the contribution of the RISC architecture to the latency time (for asynchronous context switchings) is in average slightly higher than the time required by the scheduler to perform its administration tasks in this application.

# Table of Contents.

| 1     | Introduction4                                                                                    |    |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2     | Control of a digital copier                                                                      | 5  |  |  |  |  |

| 3     | Hardware architectures of a digital copier9                                                      |    |  |  |  |  |

| 4     | Implementation of the engine control, phase 1                                                    |    |  |  |  |  |

| 4.1   | Choice of the Main Processor                                                                     | 14 |  |  |  |  |

| 4.2   | The 80960SA processor                                                                            | 16 |  |  |  |  |

| 4.2.1 | Processor highlights                                                                             | 16 |  |  |  |  |

| 4.2.2 | Execution environment                                                                            | 17 |  |  |  |  |

| 4.2.3 | System Data Structures                                                                           | 19 |  |  |  |  |

| 4.2.4 | Call/Return mechanism                                                                            | 20 |  |  |  |  |

| 4.2.5 | Interrupts                                                                                       | 23 |  |  |  |  |

| 4.2.6 | Signaling interrupts                                                                             | 25 |  |  |  |  |

| 4.2.7 | Internal Structure of the 80960SA processor                                                      | 26 |  |  |  |  |

| 4.3   | The Interprocessor Communication                                                                 | 29 |  |  |  |  |

| 4.4   | The Eprom Interface                                                                              | 33 |  |  |  |  |

| 4.5   | The RAM interface                                                                                | 35 |  |  |  |  |

| 4.6   | The hardware system architecture                                                                 | 36 |  |  |  |  |

| 5     | Implications of using a RISC processor for the control of a digital copier                       | 38 |  |  |  |  |

| 5.1   | Context Switching                                                                                | 38 |  |  |  |  |

| 5.1.1 | Asynchronous context switching                                                                   | 38 |  |  |  |  |

| 5.1.2 | Synchronous context switching                                                                    | 47 |  |  |  |  |

| 5.1.3 | Effects of the CPU to the context switching                                                      | 49 |  |  |  |  |

| 5.2   | Non deterministic behaviour                                                                      | 53 |  |  |  |  |

| 5.3   | Debug facilities                                                                                 | 53 |  |  |  |  |

| 5.4   | Amount of software code                                                                          | 54 |  |  |  |  |

| 6     | Conclusions                                                                                      |    |  |  |  |  |

| 7     | Literature Index                                                                                 | 59 |  |  |  |  |

|       | ENDIX A1 Communication Memory Interface (GAL Listings) A ENDIX A2 EPROM interface (GAL listings) |    |  |  |  |  |

# 1 Introduction.

Analog copiers that are controlled by digital means have been produced by Oce during the past 15 years. The digitalization has gained even more territory influencing also the copier process of the machine. This has created a number of possibilities that has transformed the copier from a "black box" document reproducer into a system that can be integrated in other environments. A digital copier can for instance operate like a printer and the digital image processing functions can service alien devices like an external scanner. This results in an increasing performance demand to the control unit of the copier.

The complex image processing items are available to the user through a control panel with a graphic Liquid Crystal Display. The control unit will be in charge of generating and manipulating the necessary bitmaps

To cope with this functionalities as well as the multitasking real time aspects of the engine control, a high performance hardware architecture is needed.

This work deals with the analysis of different hardware architectures under the following constraints:

- Strategic need to exchange, to remove and to add modules, in order to reduce the time to market.

- Overall price of the system should be as low as possible.

- Reserve processing power for future applications.

- Flexibility items in the design to support the development of functions.

- A solution should be ready for production by the summer of 1995.

Furthermore the implications of using a RISC processor for this real time multitasking system should be identified.

# 2 Control of a digital copier.

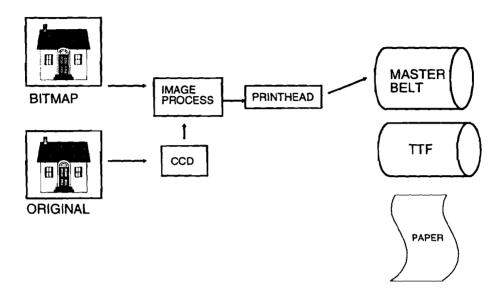

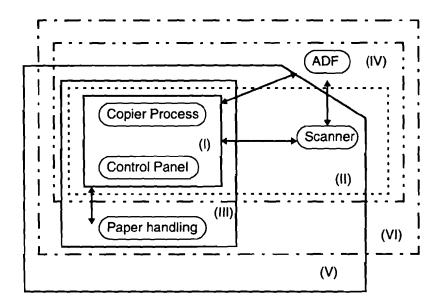

A brief description of the activities of the control of a digital copier are given in this chapter. Some items have already been used for years by the analog copiers, but the digital character of the system gives them an extra dimension: the digital copy process involves an implicit storage of the scanned information, this makes the retrieval of the original information independent of the actual copy process. The following figure depicts the different functions in a digital copier:

Figure 2.1: Digital copier, control functions.

# Copier process.

This function involves a number of actions that constitute the oce technology of analog copiers: A light sensitive master is uniformly moved and passed through a series of stations, at the first one, electrostatic charge is deposited on the master, then the printhead creates an electrostatic image of the document by illuminating and in consequence reducing the impedance of those positions where the charge will flow to ground. The charge image is developed by the accumulation of toner particles at the places where the charge is still present. The toner is transferred to a silicon band, taking advantage of the higher adhesion coefficient of the band to the toner particles than the cohesion coefficient of the particles. Then the particles are pressed and fused into the recipient paper under high temperature.

This is a real time control system that needs a master position reference clock and a real time clock, to perform a number of simultaneous controls. The productivity of the copier (amount of copies per minute: cpm) and the precision of the registration depend on the performance of the processor and its interrupt latency. The last parameter includes the context switching and the scheduling time of the last functional task. For a productivity of 60 cpm and 0.1 mm registration error, the maximum interrupt error may be:

t= .1 mm x 1 sec / 210 mm = 476 microsec.

# Original handling.

The original information is retrieved in two phases: during the first phase, the scanner moves to its start position and delivers rough information to the image processing to determine the background compensation. In case that the Automatic Document Feeder (ADF) is used, both original and scanner move to the start position (the original is transported to the same position it would have if no ADF is used). During the

second phase the actual scanning process is started: the CCD (Charge Coupling Device) is uniformly moved from the start position.

The ADF function consists of the accurate control of motors to separate, transport and eventually to turn a duplex document. The precision of the registration is closely related to the stability and precision of the velocity profile of the scanner motor. The speed of the scanner motor determines also the zoom factor gain in one direction. For reductions the zoom factor is determined by the image processing for both directions.

Because of the fact that the scanning process is independent of the print process, the velocity of the motors does not need to be synchronized to the master motion. Furthermore, the information is stored in a set memory in order to be able to reproduce the original several times (Electronic Recycle Document Feeder): scan one, print many (this improves the reliability of the system).

# Paper Handling.

This function is related to the storage, separation, transport, precise feeding into the (toner) transfer unit and output of the paper. All along the paper trajectory, there are a number of sensors to signal a possible paper-jam.

#### Control Panel.

The functionality of the copier is made available to the user by means of the control panel. The last generation of analog copiers of Oce makes use of dedicated keyboards and standard graphic LCD's. Graphic information is used to warn about possible positions of paper-jams and to generate fancy menus for the different operating modes.

# Service Diagnosis.

This is actually a function that covers the whole machine. It applies hardware feedbacks and software routines to verify the different functions and to monitor the sensors. The installation parameters are also introduced through this function.

## Image Processing.

This function characterizes the digital behaviour of the copier. It consists mainly of the following operations:

Scanner compensation.

Photo quality reproduction algorithms.

Zoom.

Background histogramming.

Conversion of 400 dpi scanned information with gray values into a 600 dpi bitmap.

Rotation (90°, or 180°).

Overlay functions.

Compression.

Storage into a set memory (dram).

Decompression.

Deliver of processed information to the printhead.

The implementation of these operations require sequential manipulation of 34 Mpixels (A4 document), this can only be achieved by the use of dedicated components;

ASICS. A certain degree of flexibility is attained by parameters that are updated by the image processing control.

The image processing control is in charge of the control of the asics and synchronization with the copy and original processes. The retrieval of document information (scan process) is validated by a real time signal generated by the original information control, and the print process is enabled by a real time signal generated by the copy control.

## Open interface

A document can also be a bitmap delivered by an alien scanner or a computer. The copier behaves then as a printer. In case the information comes from a computer, a SCSI interface is used.

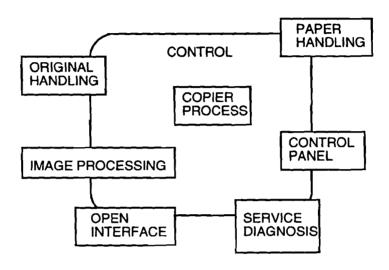

The functions of a digital copier can also be roughly divided into two categories: Data Processing (Image Processing control, and open interface) and Engine control (the rest of the functions).

Figure 2.2: Digital copier, rough division of the control.

The image processing with its dedicated functionality is a stable unit with limited degree of flexibility. Future needs will require a technology migration towards a new generation of DSP's. The Image processing control will keep its present implementation for the years to come and will be used as a black box by the different versions of the basic copier. This functional block will have its own control unit.

The functions related with the analog part of the copier have been controlled during the last decade by CISC processors of the fourth generation: Motorola 68000 or similar.

The engine controller depends in a great extent on the configuration of the machine. There is the need to add, to remove or to exchange modules. The basic machine will have for instance three paper reservoirs and no sorter. Another spin-off product will

require a sorter and a fancy finisher. Other project will require the same ADF/ Scannner but different copy control and paper handling.

One of the subjects of this report is to find the most suitable engine control architecture to satisfy the different configurations of the machine, so that the time to market can be shorten.

By the time this work was started, fundamental development was taken place on the ADF/Scanner and the behaviour of the master during the production process was analysed in order to improve its yield. One important constrain was the fact that a hardware solution should be ready for production by the summer of 1995

# 3 Hardware architectures of a digital copier.

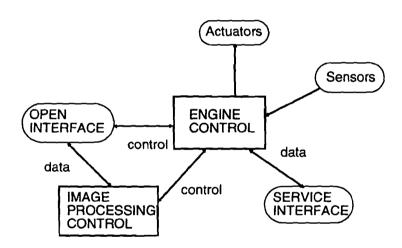

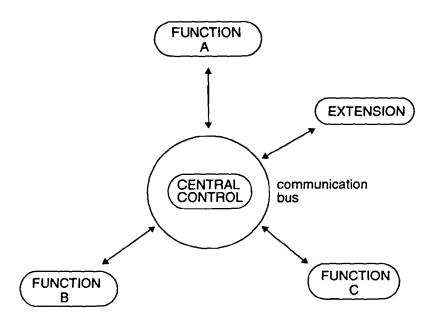

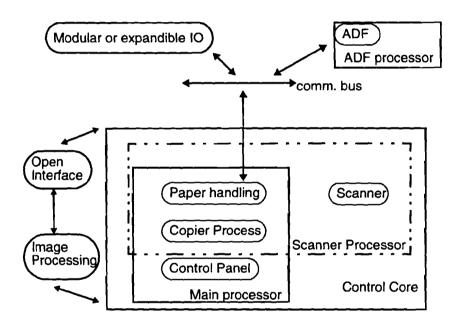

The strategic need to exchange, to add and to remove modules of the machine to shorten the time to market of spin-off projects asks explicitly for a field network. In such a network, the different functions are implemented as individual modules that receive operating instructions from a central control unit. The communication medium is a bus or a ring that gives the possibility to expand or remove functions without considerable deterioration of the quality of the signals.

Figure 3.1: Modular approach for the hardware architecture.

The digital nature of the machine with features that may be used by the outside world demands whether spare processing power or the possibility to add it when necessary.

A modular approach implies a very flexible solution, and when a serial bus is used, the reliability of the system is increased due to the low amount of wring. However the communication overhead poses limitations to the real time behaviour of the system. Another factor that determines the hardware architecture is the overall price of the system. By choosing a different module per function, a great deal of resource sharing is lost and the price increases. Activities involved in one function can not easily be distributed among the intelligent elements of the network and idle items of the modules are not ready to be used by the others. Furthermore, because of the fact that a design should be flexible enough to support the development of the functions (see chapter 2) a serial bus might introduce limitations. The trade-offs to be taken into account can be summarized as follows:

- Strategic need to exchange and add modules.

- Overall price of the system.

- Reserve processing power for future applications.

- Flexibility items in the design for development support.

- A hardware solution should be ready for production by the summer of 1995.

The need of spare processing power can be satisfied by choosing a processor with more than enough power to control certain functions of the copier. Spare processing power means that the infrastructure of the processor should also be available or expandible in order to cope with the required functionality. The advantages of having spare processing power instead of adding it when necessary, are that the costs of interfacing the processor are spent one time and the communication overhead with the eventual extra processor is avoided. Besides the system remains simple which reduces the chance of failures. The powerful processor will get the role of main or central processor, and its functionality will be referred to in the following paragraphs as the control-core functionality.

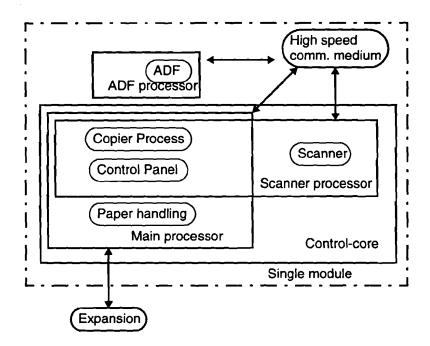

The following figure depicts the possible combinations to form the basic functionality.

Figure 3.2: Basic functionality, possible combinations.

There are three kinds of modules:

#### a) Fixed modules.

These are present in all the different configurations without alterations (copier process, control panel).

## b) Exchangeable modules.

Which can be removed or added to the system (ADF/Scanner).

# c) Configurable modules.

That are built upon submodules whose amount depend on the product (paper handling: amount of paper reservoirs).

It is obvious that the control-core will be at least in charge of the fixed modules: the copier process and the control panel. The interfacing to the control-core should be as simple as possible in order to keep the communication overhead low, and guarantee the real time behaviour of the machine. This can be implemented by four intelligent modules: The control-core, the ADF, the Scanner and the paper handling. The com-

plexity of the paper handling is low and its actual control functionality can be added to the control-core without significant performance deterioration, the modular behaviour can still be kept by using remote i/o submodules for this configurable function. This leads to combination III.

Modules D and C have a high influence on the real time behaviour of the machine, both need the accurate control of motors, a close synchronization with each other and the Image Processing control, and fast detection of errors to prevent damage of documents and mechanic elements. The use of microcontrollers (embedded controllers) for these functions is the most practical choice. The fact that the scanner only controls one motor, the processor capacity and the integrated i/o peripherals of the eventual scanner microcontroller may be available to the control-core (combination V). This introduces a great amount of resource sharing that allows the main processor to reserve even more performance for future applications and reduces the overall price of the system. A fast communication medium for both processors is required in order to optimize the resource sharing and comply with the real time requirements of the system.

Figure 3.3: Modular solution with a certain amount of resource sharing.

The combination of the original retrieval functions (ADF and Scanner) might be an interesting alternative. Both functions could be implemented by one processor, but the lost of modularity does not render the advantages of the solution depicted above.

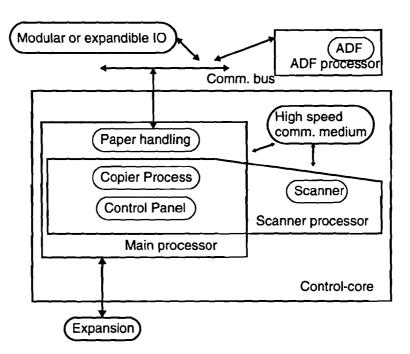

The introduction of a bus between the control-core, the ADF and the paper handling submodules, makes automatically possible the expansion of the system.

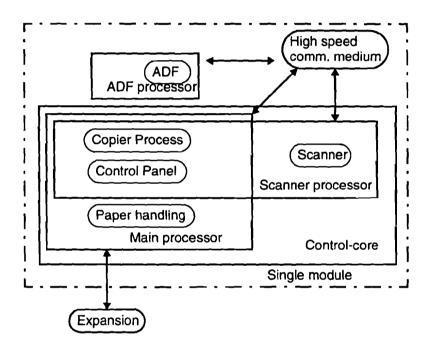

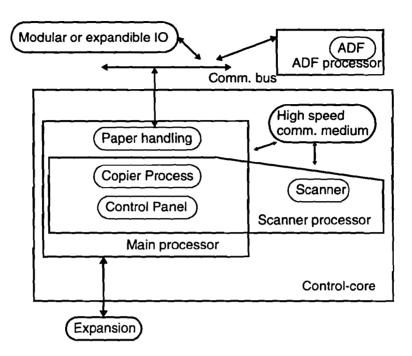

A problem needs still to be solved: how can the development of the functions be supported by means of a hardware implementation ready for production? The functions that might require expansions or modifications are spread among three different processors. The kind of modifications can be as simple as the addition of control lines or more complex electronics that need to be accessed by one of the functions at high speed. Flexibility items at the different processor buses might be an alternative, but it would increase the cost and the complexity of the system. A more adequate solution is the addition of one expansion I/O bus to the processor with the highest performance, and let also the ADF processor share the high speed communication

medium of the control-control, this way all the functions would access directly or indirectly (through the main processor) the needed hardware functionality. The physical modular approach is lost but the start of production would not be in danger. Furthermore the real time risks of a serial bus are avoided. In order to regain modularity at a later stadium, the following development phases are proposed:

#### Phase 1.

A Flexible solution with three processors that communicate with each other by means of a high speed communication medium. The main processor will have an i/o expansion channel for extra hardware functionality for any function.

Figure 3.4: Flexible solution.

## Phase 2.

A value engineering step to decide whether or not to separate the ADF processor, and investigate the real time implications of a serial bus.

Figure 3.5: Modular solution.

This report will deal with the further realization of phase 1, and in particular with the performance issues of the main processor and its real time behaviour.

# 4 Implementation of the engine control, phase 1.

This chapter deals with the implementation of a flexible solution for the engine control of the digital copier. As stated in the previous chapter, the control-core will be based on a high performance processor, which is tight coupled to the scanner embedded controller. The ADF controller will be so far also coupled to the internal high speed communication medium of the control-core so that it can take advantage of the extension i/o bus of the main processor.

We are going to concentrate our attention to the performance items of the main processor: the clock frequency, the eprom interface, the high speed communication medium and the context switching during interrupts. A brief discussion of the considerations that led to the choice of the Intel 80960 SA-processor follows first:

## 4.1 Choice of the Main Processor.

The factors that contribute to the choice of the 80960 SA were:

Compatibility with the ADF/Scanner-processors.

The 80196KC microcontroller was chosen for the ADF/Scanner functions, a member of the MCS-96 family. This embedded controller will operate at 16 MHz and zero wait states for eprom accesses. It contains a number of analog functions (ADC's and PWM's) which can be used for the implementation of the temperature and motor controls of the machine. Besides, it has normal and high speed i/o lines (HSI/O) that operate in combination with the 2 internal 16 bits timers for accurate i/o control. A serial channel is available. Furthermore a Peripheral Transaction Server (PTS) provides DMA-like response to an interrupt with few CPU-overhead. Single and block transfers are supported, as well as special modes to service the AD-converter and the HSIO.

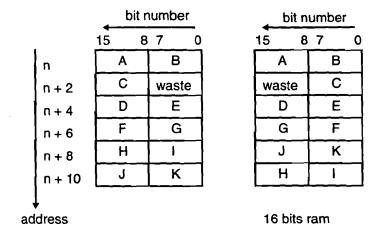

By choosing Intel microcontrollers and the fact that a high speed communication medium is needed, a compatible main processor is required to guarantee the simplicity and the transparency of the hardware: the data should be interpreted the same way by all the participants of the communication medium. To illustrate this, consider the following 16 bits aligned structure:

```

struct {

short a;

char c;

short d;

char f,g;

long h;

};

struct {

short a;

/* 16 bits a = AB */

/* 8 bits c = C */

short d;

/* d = DE */

/* f = F, g = G */

/* h= HIJK

A through K are bytes*/

```

The data is stored into memory by a little endian machine (Intel processors) in a different way than a big endian processor (e.g. Motorola):

Figure 4.1: Little endian vs. big endian; memory allocation.

Byte swapping takes place at addresses n+2 and n+6 and word swapping at n+8 and n+10. A detection and eventually a correction of this situation need that the sequential accesses of one data type occur within the same machine cycle. The Motorola processors that comply with this requirement are the MC68020 and its successors, because they feature a dynamic data bus sizing. In order to keep low the complexity and cost of the system a little endian processor is chosen.

# Availability.

The general purpose market has been dominated by Intel with its 80x86 line. Intel has been able to confirm its position by introducing every couple of years more powerful processors maintaining their instruction set compatibility. The kind of applications of the personal computer area demands increasing of performance, which limits the life cycle of the processors (about 3 years). Embedded controllers on the other hand, are intended for a complete different market segment, where price is mostly the steering factor. Extra performance does not always results in attractive items for the end user (e.g. washing machine). The life time of this kind of processor is often longer: about 7 years. An indication that the embedded controller market is a different area is illustrated by the fact that 60% of the applications is still implemented by 4-bits processors, 30% by 8-bits processors, 9% by 16 bits processors and 0.8% by 32 bits processor (according to the Intel representantion in the Netherlands). Taking this into consideration it is recommended to make use of an embedded processor for this kind of application.

#### Performance.

Taking into account that a MC68000 has already proven to control an analog copier with similar requirements, a processor with a comparable performance to that of the MC68020 is needed, which has more than two times processor power. This way, capacity would be available for future applications. The nature of this application: control and a certain degree of bit manipulation for the graphic display, makes a MMU and a floating point processor unnecessary. Possible embedded candidates are the AMD29K, the i960 family or one 80386-based microcontroller. The 80376 was about to be discontinued by Intel because of the planned introduction of the i386EX microcontroller. A choice had to be made between a low end processor of the I960 family of one of the AMD29K. A benchmark report [1] indicates that the 80960SA performs almost two times better than the AMD29200 using the Standford benchmark and

about 30% better when the Dhrystone is used. This figures give only an indication of the possible performance of the processors, because they do not reflect the demands of the actual application. These benchmarks do not include operating system calls and i/o control. However they suggest that the 80960SA might be a better choice.

Cost, support and development equipment.

Even though these are engineering aspects, these factors are also mentioned to give a complete picture of the items that are taken into account during the development of a system in the industry. The cost of the 80960SA at 16 MHz is about USD 20.00 when quantities of 5 000 pieces/year are purchased. The cost of the AMD29200 is slightly higher. There are cross language systems for both processors and in circuit emulators are available.

Because of the fact that the 80960SA is an Intel processor, which guarantees compatibility with the other processors, and that the price and the performance are better, this Intel embedded processor has been chosen. A clock frequency of 16 MHz has been selected in order to accommodate standard memory components with low amount of wait states. The inherent characteristics of this risk processor and its implications to the real time behaviour of the system need to be analysed.

# 4.2 The 80960SA processor.

A brief description of the 80960 processor follows. We are going to concentrate our attention on the features of the processor that might affect the real time behaviour of the system: call/return mechanism and interrupt mechanism. The interprocessor communication, and the memory interfaces are considered later on, these items are tightly related to the performance of the processor.

# 4.2.1 Processor highlights.

- Load and store model: most of the operations are performed in registers rather than in memory. The architecture provides an amount of general purpose registers: For each procedure, 16 global- and 16 local-registers are available. The global-registers maintain their contents across procedure boundaries, whereas the processor allocates a new set of local registers each time a new procedure is called. There are four local register-sets on chip. The processor can perform burst transfers of 1, 2, 4, 8, 12, or 16 bytes of information between memory and registers during one machine cycle.

- On-chip caching of code and data: the size of the instruction cache is 512 bytes. Data caching is provided by means of the general purpose registers.

- Overlapped Instruction execution: This is accomplished through register score-boarding, which permits instruction execution to continue while data is being fetched from memory. When a load instruction is executed, the processor sets one or more scoreboard bits to indicate the target registers to be loaded. While the target registers are being loaded, the processor is allowed to execute other instructions that do not use these registers. The processor uses the scoreboard bits to ensure that target registers are not used until the loads are complete.

- Single-clock instructions: The processor is able to execute commonly used instructions such as move, add, substract, logical operations compare and branch in a minimum number of clock cycles. All the instructions are 32 bits or 64 bits long and aligned on 32-bit boundaries, this feature allows instructions to be decoded in one

clock cycle. It also eliminates the need for an instruction-alignment stage in the pipeline. About 50 instructions are one-clock-cycle-executable.

- Procedure Call Mechanism: Each time a call instruction is issued, the processor automatically saves the current set of local registers and allocates a new set of local registers for the called procedure. Likewise, on a return from a procedure, the current set of local registers is deallocated and the local registers for the procedure being returned to are restored. On a procedure call, the program thus never has to explicitly save and restore local variables that are stored in local registers.

- 4-gigabyte address space.

- On chip trace facilities to ease debugging.

#### 4.2.2 Execution environment.

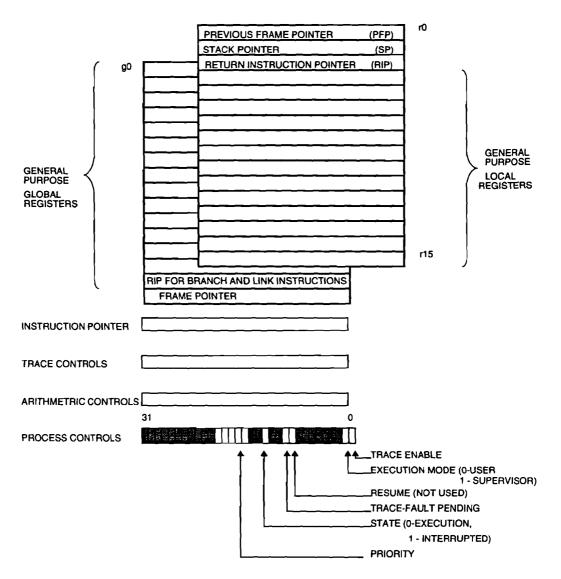

The execution environment of the processor consists of a set of general purpose registers, an arithmetic control register, Instruction Pointer (IP), Processor Controls register, Trace Control register and an address space of 4 gigabyte. The process controls register shows the current execution state of the processor. The trace facilities of the processor are controlled through the trace controls register.

# Register Model.

The 80960SA provides two types of data registers: global and local. The 16 global registers constitute a set of general purpose 32-bits registers, the contents of which are preserved across procedure boundaries. The 16 32-bits local registers are provided to hold parameters specific to a procedure. For each procedure that is called, the processor allocates a separate set of 16 local registers; there are four available sets. The general purpose global registers g0 through g14 are general purpose; g15 is reserved for the current frame pointer (FP), that contains the address of the first byte in the current stack frame. The local registers r3 through r15 are general purpose registers; register r0 contains the previous frame pointer (PFP), r1 contains the stack pointer (SP), and r2 contains the Return Instruction Pointer (RIP; for branch and link instructions g14 contains the RIP). The following figure shows the register organization. A description of the pointers is given in the next paragraphs.

Figure 4.2: 80960SA, Register model.

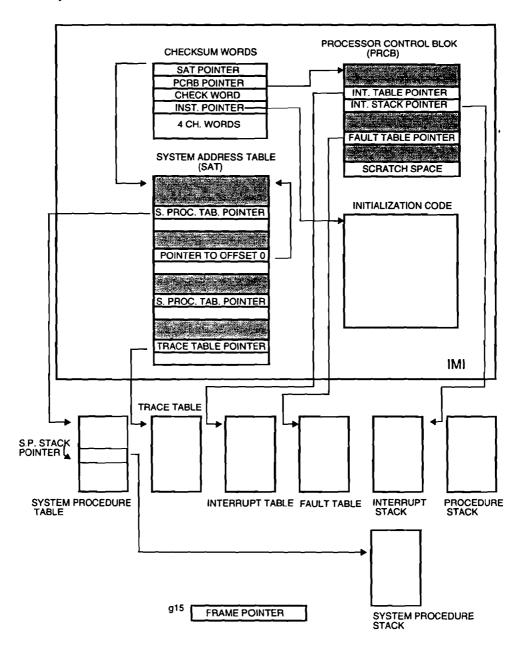

# 4.2.3 System Data Structures.

The data structure offers a means to configure the processor to operate in a specific way

Figure 4.3: System data structures.

The IMI (Initial Memory Image) contains the minimum data structures required for the processor to initialize itself and begin executing code. It contains pointers to the other data structures. It is a common practice to copy a portion of the IMI into RAM during initialization. This can be necessary because of the dynamic character of the pointers as well as the processor scratch space. If the interrupt posting mechanism is used, the interrupt table must also be copied into RAM for the processor to operate properly because it contains the interrupt pending fields, which the processor must be able to write to. After the copy process, the processor is reinitialized with the new addresses

of the System Address Table and the Processor Control Block. (This reinitialization is performed through an IAC, Intra-Agent Communication, message. The primary function of the IAC mechanism is to provide an alternative to the external interrupt facilities to communicate with the processor, without the need of context switching. The processor handles an IAC in much the same way as it handles an instruction. All IACs have the highest priority level. The IAC messages are used for setting breakpoint registers, purging the instruction cache, or sending software initiated interrupts).

Upon power up the processor is in the interrupted state. It is a common practice to take the processor out of the interrupted state through the execution of a call statement, then the frame is fixed up to cause a return from interrupt. Before calling the application software, the frame pointer and the stack pointer should be initialized with the corresponding addresses at the user stack.

#### 4.2.4 Call/Return mechanism.

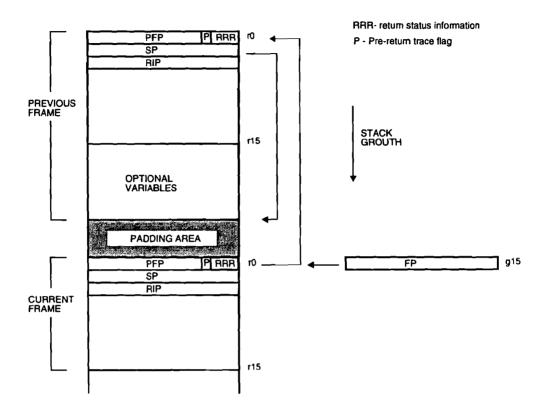

The processor has two structures to support this mechanism: the local registers (on the processor chip) and the procedure stack (in memory). The stack consists of contiguous frames, one frame for each active procedure. For each procedure, the processor allocates a set of local registers and a frame on the procedure stack. If additional space for local variables is required, it can be allocated in the stack frame.

When a procedure call is made, the processor automatically saves (if necessary) the contents of the local registers on the stack frame for the calling procedure and sets up a new set of local registers and a new frame for the called procedure. When the number of nested procedure calls exceeds the number of registers sets (= 4), the processor automatically stores the contents of the oldest set of local registers on the stack to free up a set of local registers for the most recently called procedure.

The processor aligns each stack frame on a 64-byte boundary. Each frame provides besides a space for the local registers an optional area for additional variables; when the processor creates a new frame on a procedure call, it will if necessary, add a padding area to the stack so that the new frame starts on a 64 byte boundary.

Global register g15, and local registers r0-r2 contain information to link procedures together and to link the local registers to the procedure stack. The frame pointer (g15) is the address of the first byte of the current stack frame; the stack pointer (r1) is the address of the next available byte of the stack frame; the previous frame pointer (r0) is the address of the first byte of the previous stack frame; the return instruction pointer (r2) is the address of the instruction that the processor is to execute after returning from a procedure call. The following figure depicts the use of the pointers:

Figure 4.4: Procedure stack structure.

Occasionally, it is necessary to have the contents of all local registers sets match the contents of the register save areas in their associated stack pointer. The processor provides the *flushreg* instruction to allow voluntary flushing of the local registers.

There are three different kinds of procedure calls: local call, system call and branch & link.

Local Call.

During a local call, the processor performs the following operations:

- 1. Stores the RIP in r2 (of the calling procedure).

- 2. Allocates a new set of local registers for the called procedure.

- 3. Allocates a new frame on the procedure stack (RIP is invalid).

- 4. Changes the instruction pointer to point to the first instruction in the called procedure.

- 5. Stores the FP for the calling procedure in new local register r0 (PFP).

- 6. Stores the FP of the new frame in global register g15.

- 7. Allocates a save area for the new local registers in the new stack frame.

- 8. Stores the SP in the new local register r1.

On a return the processor performs the following operations:

- Sets the FP in global register g15 to the value of the PFP in current local register r0.

- 2. Deallocates the current local registers for the procedure that initiated the return and switches to the local registers assigned for the procedure being returned to

- 3. Deallocates the stack frame for the procedure that initiated the return.

- 4. Sets the IP to the value of the RIP in new local register r2.

#### System Call.

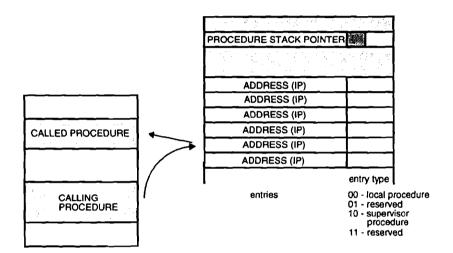

The system call is similar to the local call, except that the processor gets the IP for the called procedure from a data structure called the system procedure table

Figure 4.5: System call mechanism.

The System Procedure table contains a list of Instruction Pointers (IPs) which can be accessed through the system call mechanism. IP's for fault handlers may be stored. (The fault table contains a pointer to a specific entry of the System Procedure Table).

If the entry type specifies a supervisor call the processor switches to Supervisor execution mode and the Supervisor Stack becomes active. The processor gets a pointer to this stack from entry 12 of the System Procedure Table. When the supervisor mode is invoked, the field RRR of the local register r0 of the calling user procedure is set to 01X to indicate that mode and stack switch has taken place.

The processor provides a mode and stack switching mechanism called the user-supervisor protection model. This protection model allows a system to be designed in which kernel code and data reside in the same address space as user code and data, but access to the kernel procedures (called supervisor procedures) is only allowed through a system call.

The processor remains in the supervisor mode until a return is performed from the procedure that caused the original mode switch. When using the user-supervisor mode mechanism, the processor maintains two separate stacks in the address space, one for the procedures executed in the user mode (local procedures) and another for procedures executed in the supervisor mode (supervisor or system procedures). Both stacks are identical, except that the processor obtains the stack pointer for the supervisor stack from the system procedure table.

In the supervisor mode the Process Controls register can be modified through the modpc instruction. An application may be a modification of the processor priority.

#### Branch and Link.

A branch and link instruction save the address of the next instruction (RIP-return instruction pointer) in a specified location, then branches to a target instruction. A return instruction specifies the RIP. The state of the local registers and the stack remains unchanged.

For the bal (branch and link) instruction the RIP is stored in g14; for the balx (branch and link extended), the RIP is specified with one of the instruction operands.

This kind of procedure call does not cause context switching. It is commonly used for the so called leave-procedures.

# 4.2.5 Interrupts.

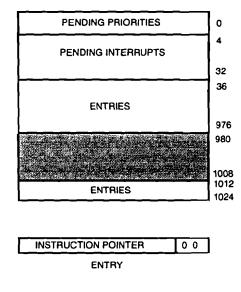

The 80960SA supports a vector interrupt mechanism. An interrupt vector is 8 bits in length and has a predefined priority (= vector/8). At each priority there are 8 possible vectors. An incoming interrupt is serviced if the current priority is lower than the requested interrupt. A priority 31 is always serviced immediately (if the processor priority < 31; priority level 0 is not supported, because the memory locations that would be required for the interrupt vectors, are use by the interrupt table header).

Figure 4.6: Interrupt Table.

A vector number specifies an entry to the Interrupt Table. The first 36 bits of the interrupt table are used to record pending interrupts. This section is divided into two fields: pending interrupt priorities and pending interrupts. When a pending interrupt is logged, its corresponding interrupt pending bit and interrupt pending priority are set.

The processor execution mode is set to supervisor while an interrupt is being handled. When an interrupt service routine is called, the states of the process controls

and arithmetic controls for the interrupted program are saved. The interrupt handler shares the global registers with the user/system procedures.

Except from the interrupt record, the interrupt stack has the same structure as the local procedure stack.

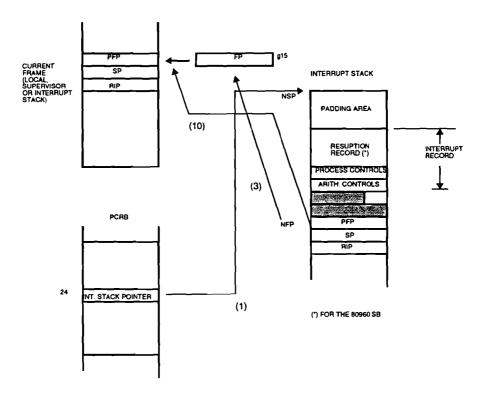

The method that the processor uses to service an interrupt depends on the state the processor is when it receives the interrupt: execute or interrupted. In the first case the processor switches to the interrupt stack. In both cases an interrupt record is also stored on the top of the stack prior to the new frame that is created for use in servicing the new interrupt.

Figure 4.7: Framing manipulation during interrupts.

The following events take place:

- 1. If necessary, the processor switches to the interrupt stack. The interrupt stack pointer becomes the new stack pointer (NSP) for the processor.

- 2. The processor saves the current state of process controls and arithmetic controls in an interrupt record on the interrupt stack.

- 3. The processor allocates a new frame on the interrupt stack and loads the new frame pointer in register q15.

- 4. If necessary, the processor switches to interrupted state.

- 5. The processor, sets the state flag in its internal process controls to interrupted, its execution mode to supervisor, and its priority to the priority of the interrupt.

- 6. The processor sets the frame return status field (associated with the PFP in register 0) to 111 (interrupt return).

- 7. The processor performs an implicit call-extended operation. The address for the procedure call is that specified in the interrupt table by the corresponding interrupt vector.

- 10. The frame is linked to the previous frame through the address of the previous frame being written into r0 of the new created frame.

Once the processor has completed the interrupt procedure, it performs the following:

- 1. The interrupt record is restored.

- 2. The processor deallocates the current stack frame and if necessary switches to the user or system stack.

- 3. The processor checks the interrupt table for pending interrupts that are higher than the priority of the program being returned to. If a higher interrupt pending interrupt is found, it is handled as if the interrupt occurred at this point.

# 4.2.6 Signaling interrupts.

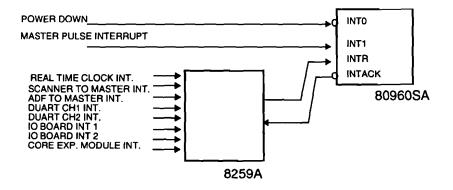

The 80960SA can be interrupted by: signals on its interrupt pins, signals on the interrupt pins of an external interrupt controller, an IAC message from a program or a pending interrupt. The processor has four interrupt pins, two of which can be configured for handshaking with an interrupt controller such as the 8559A programmable interrupt controller.

In this application more than 4 interrupt lines will be needed, the following figure shows the how these lines are going to be used:

Figure 4.8: Interrupt signals.

The interrupt control register is memory mapped at address 0ff000004. Only the processor can access this register through two instruction (synld, synmov), which prevents the register from being modified by another external agent. The interrupt vector for INT0 is specified at the first byte of the interrupt register, that for INT1 should be specified in the next byte.

Important to know now is that both the real time clock and master pulse interrupts are used by the executive. The first one provides the time reference, the other one the position reference with respect to the master belt. The frequency of the master pulse

is 300 Hz and that of the real time clock is 200 Hz. The resolution of the events is determined by these figures. Some precise actions need to be activated through hardware timers.

# 4.2.7 Internal Structure of the 80960SA processor.

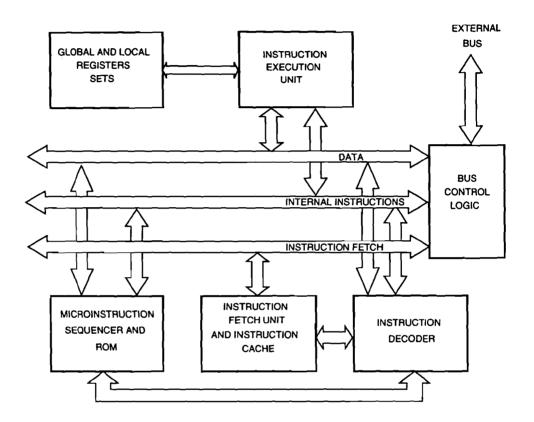

Figure 5.9: 80960SA, block diagram.

The i960 architecture defines several mechanisms for increasing performance through the use of pipelining and parallel execution of instructions. The 80960SA processor is composed by five major functional units. These units are described below:

Bus Control Logic (BCL).

The Bus Control logic provides the interface between the processor and the external world. It accepts requests from other units. It attempts to maximize bus access efficiency through buffering ad burst accesses.

It provides a queuing mechanism that can buffer up to three outstanding requests at any given time. This allows other internal units to continue operation without waiting for bus requests to be completed. As a result, the execution of most memory reference instructions require little delay in the instruction execution pipeline.

The BCL generates burst cycles on the external bus, which allow 1-, 2-, 4-, 8-, 12-, or 16-bytes of read or written in a single operation. Instructions can be fetch in 16-byte bursts.

Instruction Fetch Unit (IFU) and Instruction Cache.

The IFU acts as an intelligent buffer for the Instruction Decoder. The IFU contains a 512 byte, direct mapped instruction cache. While the other units in the processor are executing instructions, the IFU looks ahead in the flow of instructions stored in the

instruction cache, if a cache miss is detected, the IFU issues a prefetch to the BCL. Upon receiving the requested instruction, the IFU updates the instruction cache. The fetch and load might take place before the ID requires the instruction cache. The major exception to this rule happens on branch conditions.

The ID informs the IFU of any branch operations that are about to take place; the IFU checks for a cache hit, if the instruction is not present, the IFU begins fetching instructions for the new control path. To further minimize delays in the instruction pipeline, the ID sends a special signal to the IFU whenever instructions are required immediately. The IFU then passes the fetched instruction directly, rather than writing them back to the cache and reading them back again (instruction-cache bypassing).

The Instruction Pointer (IP) register in the processor and the IFU maintain several instruction pointers. These pointers point to instructions at various stages of the fetch-decode-execute pipeline.

#### Instruction Decoder (ID).

The ID decodes the instructions it receives from the IFU and routes them to the appropriate execution units

The ID decodes the so called simple instructions (shift; integer add and substract; ordinal add and substract), and passes them to the Instruction Execution Unit (IEU), where they are executed, usually in a single clock period.

The ID executes branch instructions directly. If the branches are unconditional, no interaction with the other execution units is required. On conditional branches, the ID uses a condition code <u>scoreboard</u> (various mechanisms within the processor can be marked as in use). When the ID prepares to execute a conditional branch, it checks the condition code scoreboard, if it is clear, the ID signals the IFU immediately if a change in program is about to happen.

The complex instructions (those that are executed using one or more microcode instructions: flushreg (flush local registers), mark and fmark, are decoded by the ID and forwarded to the Micro-Instruction Sequencer (MIS). The MIS sends the equivalent microcode to the IEU.

Load and store instructions are sent directly to the BCL, the ID is responsible for converting the address information encoded in load, store, branch and call instructions into effective memory addresses. These instructions are executed by the ID or the BCL; this preserves the pipeline.

# Micro-Instruction Sequencer (MIS) and ROM.

When the ID receives a complex instruction, the MIS supplies the microcode to the execution unit for that instruction, which can be the IEU or BCL. The MIS also supplies microcode for the power-up and self-test sequences, which are performed during processor initialization.

## Instruction Execution Unit (IEU).

It contains the ALU and the mechanism for register and condition code scoreboarding. It also manages the 16 global registers and the 4 sets of 16 local registers.

The IEU handles the reading and writing of global and local registers. It also handles the allocation of local register sets on procedure calls. The EIU allocates a new set of local registers on each procedure call. If all register sets become allocated, the IEU automatically flushes the oldest frame to the stack on the next procedure call. The IEU retrieves automatically any local register frame from the stack when required by a return operation.

The <u>register scoreboard</u> provides scoreboarding for the local and global registers: when one or more registers are being used in an operation, they are marked in use. The register scoreboard allows the processor to continue executing subsequent in-

structions, as long as those instructions do not require the contents of the scoreboarded registers.

One feature of the IEU that enhances instruction-execution performance is <u>register bypassing</u>. This is a mechanism that allows an instruction that would ordinarily require source operands to be placed in registers to be executed without accessing one or both of the source registers. This can be achieved in two situations: When the IEU executes an instruction with two source operands and one or both of the operands are literals (5 bits). Register bypassing will also occur when the second of two source operands is the result of the previous instruction. The net result of register bypassing is the saving of one clock cycle. Most instructions that the IEU executes can be executed in a single cycle when register bypassing occurs.

# 4.3 The Interprocessor Communication.

A communication medium for the three processors, which operates at a high transmission rate should be defined. An important condition is the fact that the performance of the processors should not suffer a considerable deterioration. A balanced communication medium is therefore one which is isolated from the buses of the different processors and is fairly granted to any of them. A communication ram, whose bus is independent to the local buses satisfies this requirement. The communication memory arbiter needs to comply with another requirement:

Data present in memory should be unambiguously interpreted by the processors at any time. In order words, the validity of the messages or data types that involve more than one memory access should be protected.

One way to solve this problem is by the use of semaphores. This mechanism involves read modify write accesses to control and set a flag. The 80196KC processor do not support this kind of operations, and in consequence a hardware solution would be necessary.

The best way to satisfy this requirement is that the processors agree upon the maximum size of the data types and implement an arbitration mechanism that grants the bus until the maximum amount of bytes has been transferred. In order to calculate the effect of the maximum data size to the transfer rate and the stall time of the processors, the following arbitration mechanism is assumed:

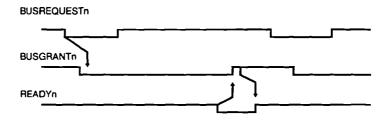

Figure 4.10: Arbitration Mechanism.

- 1) When a processor wants to access the communication memory, it will request it by activating BUSREQUESTn.

- 2. If no other device is performing an access, the communication bus is granted (BUSGRANTn active).

- 3. The processor will relinquish the bus and activate READYn. This will allow another device to perform an access.

The data bus width of the 80960SA is 16 bits. This processor does not have a dynamic bus sizing mechanism, which implies that the communication memory should also be 16 bits. The 80196KC can operate with a data bus of 8- or 16-bits. The 80960SA can access 8 consecutive memory locations within the same machine cycle in the so called burst mode, while the 80196KC can only access one location per machine cycle.

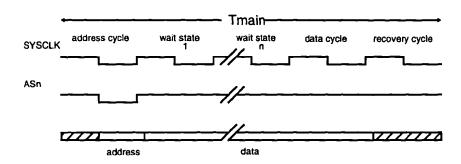

The machine cycle time of the main processor as a function of the amount of wait states and the number of consecutive accesses is [13]:

Figure 4.11: 80960SA, machine cycle.

Tmain(M) = (NxM + M + 2) x Tclk

N = amount of wait states to accommodate standard rams = 2 (if Tclk = 62.5 ns).

M = amount of consecutive accesses during one machine cycle

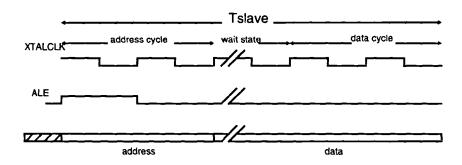

The machine cycle time of the 80196KC as a function of the amount of wait states is [14]:

Figure 4.12: 80196, machine cycle.

tslave = (2xN + 4) x Tclk

N = amount of wait states to accommodate standard rams = 1 (if Tclk = 62.5 ns).

Synchronization of ready signal

Assuming that the arbiter clock has the same frequency as the reference clock of the processors, the arbitration and synchronization introduce the following amount of wait states:

Synchronization of request signal - 1 cycle

Arbiter change of state - 1 cycle

Synchronization of grant signal - 1 cycle (80960SA))

- 2 cycles (80196KC)

(Tclk = 2 x Txtalclk)

- 1 cycle

Toverhead\_main = 4 Tclk

Toverhead\_slave = 5 Tclk

The stall time as a function of the amount of allowed accesses is:

Tstall main(M) = (2xToverhead slave + 2x Tslave) x M;

Tstall\_slave(M) = (Toverhead\_slave + Tslave) x M + Tmain(M)

+ Toverhead\_main;

The access time as a function of the amount of allowed accesses is:

Tacc\_main(M) = Tstall\_main(M) + Tmain(M);

Tacc\_slave(M)= Tstall\_slave(M) + MxTslave;

The effect of the amount of allowed states is summarized in the following table:

| M | MxTslave                                   | Tmain(M) | Tstall_<br>slave(M) | Tstall_<br>main(M) | Tacc_<br>slave(M)                    | Tacc_<br>main(M) |

|---|--------------------------------------------|----------|---------------------|--------------------|--------------------------------------|------------------|

|   | expressed in amount of clock periods #Tclk |          |                     |                    | #Tclk - Mbyte/sec<br>(fclk = 16 MHz) |                  |

| 1 | 6                                          | 5        | 16                  | 22                 | 22-1.45                              | 27-1.18          |

| 2 | 12                                         | 8        | 30                  | 44                 | 42-1.52                              | 52-1.23          |

| 4 | 24                                         | 14       | 58                  | 88                 | 82-1.56                              | 102-1.25         |

| 8 | 48                                         | 26       | 114                 | 176                | 162-1.58                             | 202-1.26         |

Table 1: Effect of amount of accesses

The transfer rate (access time) remains almost constant and the stall time increases linearly, its effect per byte is slightly less notorious for the slave processors at high values of M. Increasing M does not contribute in a big extent to the transfer rate. By choosing M = 2 almost all the data types may be supported (max. 4 bytes). Furthermore by choosing M low, the complexity and price of the arbiter will be kept low.

A problem remains to be solved: the fairness of the arbitration. None of the participants of the communication memory should get priority over the others, in order to prevent high stagnation of one of the low priority processors. In a VME solution for instance, fair bus requesters are implemented, that do not request the bus after an own transaction has taken place and other requests are pending. A VME configuration has a daisy chain grant mechanism, that even if a single priority is used, the boards located far from the arbiter have an intrinsic low priority. This justifies the fairness to be implemented on the requester. As far as this application is concern, all the processors will generate its own request signal, this way, the arbiter can decide whether or not to grant the bus to a device. An arbiter that polls the requests of the processors has the properties we are looking for.

The arbiter should have the following characteristics:

- The arbiter should allow the slave processors to execute two consecutive accesses.

- The main processor may acquire the bus only for one machine cycle.

- Because of the fact that the amount of software code of the slave processors will be low (less than 64 KByte) compared to that of the main processor (more than 3 MByte if all the different languages for the messages of the user interface are supported), the software code of the Scanner and ADF controllers may be stored in the main processor eproms. During initialization, the code could be down loaded. This approach eases the replacement of the eprom modules and makes down load of different kinds of software possible for service diagnosis and testing. This operation can take place while the controllers are in the reset situation, because the buses float or have a high impedance. A dma access during the normal operation of the processors

will not be implemented because it does not have practical applications and in case of a dma access is requested while the slave processor tries to communicate via the share memory, the dma request would have to be postponed until the slave processor access has taken place. This would increase the complexity of the hardware.

The architecture of the shared memory looks as follows:

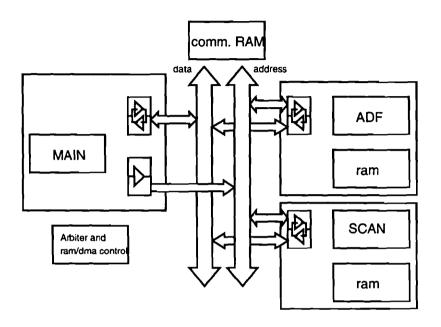

Figure 4.12: The communication memory interface.

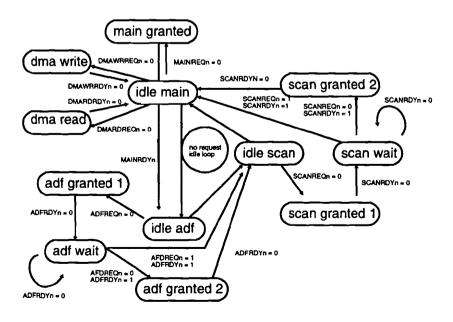

The state diagram of the arbiter is depicted below:

Figure 4.13: The communication memory arbiter (state diagram).

The implementation of the arbiter and communication memory/dma controller has been realized by means of Generic Array Logic (GAL) components, the hardware description listings are shown in appendix A1.

# 4.4 The Eprom Interface.

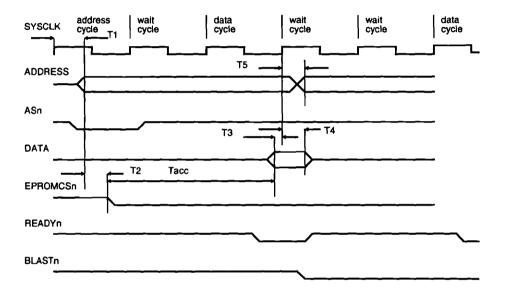

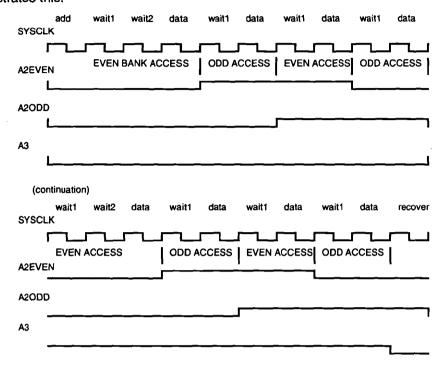

The 80960SA provides a 512-byte cache for instructions. When the processor fetches an instruction or group of instructions from memory, they are stored in this cache before being fed into the instruction execution pipeline. In order to load the cache at a high rate, the processor can access 8 consecutive memory locations within one machine cycle (burst mode). If we want to take advantage of this feature of the processor, a mechanism should be found to be able to perform high speed accesses even in combination with standard commercial eproms. The 80960SA operating at 16 MHz has the following timing for a burst cycle of two accesses:

Figure 4.14: Eprom access.

During the first cycle, the access is determined by the last generated signal among EPROMCSn and the less significant address lines that are latched from the multiplexed data/address bus. If the chip select is generated by means of a 15 ns GAL, and a commercial 120 ns eprom is used, the amount of wait states during the first cycle is calculated below (the timing parameters of the processor can be found in ref. [13]):

```

T1 = T5 = 25 ns.

T2 = 15 ns.

T3 = 10 ns.

Tacc = 120 ns.

Tclk = 62.5 ns.

Wait_states1 = (T1 + T2 + T3 + Tacc)/Tclk -2

= 170ns/62.5ns - 2= 0.72 wait states

1 wait states is necessary.

```

The amount of wait states during the following accesses is determined by the low address lines that specify the memory location during the burst cycle [A1,A3]:

$Wait_states2 = (T5 + Tacc + T3)/Tclk -1 = 1.48$  wait states.

2 wait states are necessary.

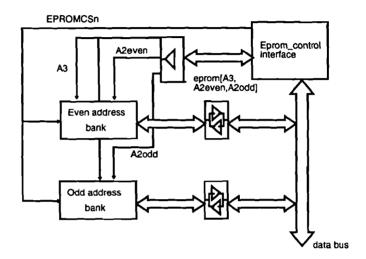

The amount of wait states can be reduced by defining an eprom array of 32 bits and making use of two interleaved banks. While the processor is accessing one bank, the access of the other bank is started by an eprom\_control interface.

Figure 4.15: Interleaved eprom interface.

The eprom\_controller interface generates the two least significant address lines and enables the buffers of the proper bank at the correct moment. The following figure illustrates this:

Figure 4.16: Interleaved eprom access.

The state machines were implemented also in GAL's, see appendix A2.

Note that transceivers were used in order to be able to make use of Flash Eproms in the future. This has influenced the amount of wait states, along with the fact that the state machine that produces the RDYn signal to the processor is also used for the other memory components. The average amount of states is 1.25 wait\_states/access. Without this configuration, the amount of wait states would have been 1.875 wait\_states/access.

# 4.5 The RAM interface.

Standard static ram devices are used in this application. This avoids the use of refresh circuitries that are required by dynamic rams. Furthermore, the low power requirements for battery back up are met. The amount of wait states is 2, this is necessary to compensate the propagation delay introduced by the protection circuit (which prevents accesses to take place during power down). The accesses to ram are controlled by means of the same state machine of the rom interface.

An interleaved configuration makes the hardware very complex and expensive, due to the selection of the proper byte during write cycles.

This choice might have strong implications on the behaviour of the processor during context switching. The amount of clock cycles as a function of the amount of accesses (M) during one machine cycle is given by:

$$Tmain(M) = (3xM + 2) \times Tclk$$

# 4.6 The hardware system architecture.

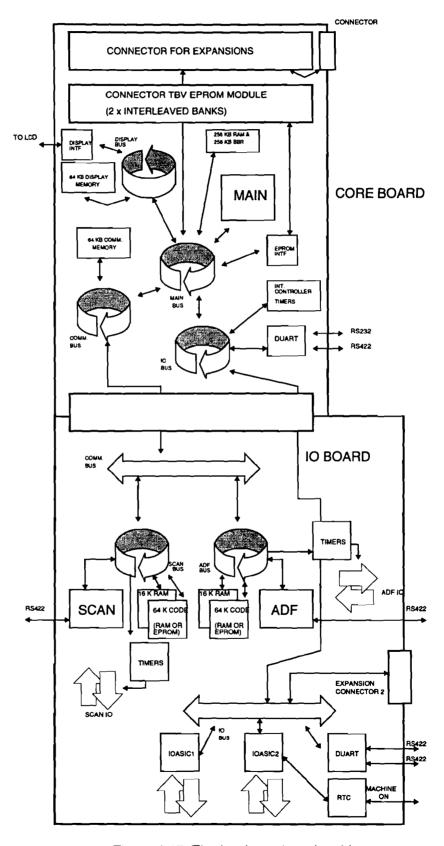

Figure 4.17: The hardware board architecture.

The previous figure shows the final implementation of the hardware. Note that two boards are used:

#### The Core Board.

It contains the main processor, the communication memory, the display interface and the peripherals of the processor. By separating this board from the i/o functions (including the ADF/Scanner processors) a possible migration to other main processor can take place. At the core board an i/o bus is implemented to access the i/o devices located on the i/o board as well as the extension connector which has, besides an 8-bits i/o-data bus, a couple of chip select lines, an interrupt line and the four least significant address lines. This way, devices of low complexity can be added. The amount of wait states for this eventual devices can be programmed in one GAL located at the core board. There is also a connector available for expansions that would require a large amount of address lines (memory components).

#### The I/O board.

This board contains the i/o devices. The Scanner and the ADF processors are tightly coupled to the main processor by means of the communication bus. One can decide whether to make use of EPROM's or to let the main processor down load the program code at dma basis through the communication bus.

This solution has so far proven to comply the requirements of the copier and the flexibility items in the design (expansion connectors) have been used to adapt some functions; one example: The control of one motor of the ADF function needed a 16 bits up/down counter as well as its related logic that generates the control signals from the phase of the rotary encoder that is coupled to the motor. The temporary solution was a module with such a counter that has been installed at the expansion connector of the i/o board; the value of the counter was retrieved by the main processor and stored in the communication memory. The ADF processor could access later on the communication memory and get the value of the counter.

# 5 Implications of using a RISC processor for the control of a digital copier.

RISC processors were intended to be used in applications where a great deal of data processing takes place. In this kind of applications, the processor remains in a certain routine for a long period of time until the necessary result is found. Some embedded applications show this behaviour, e.g. the description language interpreter of a laser printer. The RISC architecture becomes more and more popular due to its attractive features such as high speed.

The architecture of the processor can affect the behaviour of the software as well as its development. In the following paragraphs an investigation is done of the possible problems that the 80960 RISC processor introduces in this real time application.

#### 5.1 Context Switching.

One of the factors which makes the RISC fast is the large number of internal registers. They enable the RISC processor to perform many operations internally, hence reduce the access time to the external memory. However, the Berkeley-RISC (sparc) and Standford-RISC (MIPS) architectures for instance, do not provide enough support for task switching. This is also the case for the 80960SA processor. The window structure of the Berkeley-RISC as well as the register organization of the 80960 makes them suitable for procedure handling, but if a context switch takes place, a great number of register contents should be moved to/from the processor. These processors make in general use of standard cisc techniques in saving/loading the task state.

In real time applications there are a lot of interactions with the external agents. Furthermore, in multitasking solutions, several tasks require processor services at the same time; for every task a stack is needed. The task state is stored in the stack when the task relinquishes the processor to other task.

Context switches can take two forms: synchronous and asynchronous. The first one occurs when the task voluntarily gives up the cpu for another task to run. An asynchronous context switch occurs when the task has to unexpectedly give up its cpu time, this usually happens as a result of an interrupt. In the last case the running task may or not get continued during interrupt, depending on its priority. Preemption takes place if a task is temporary suspended, for a higher priority task.

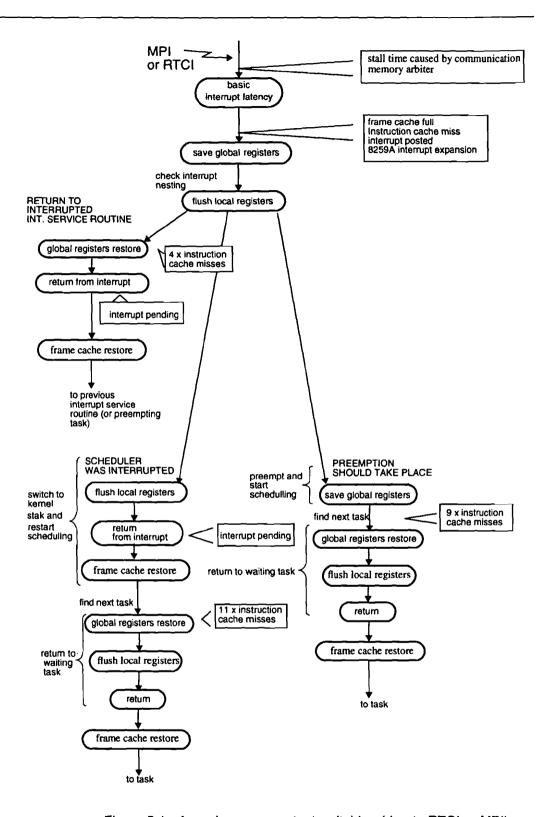

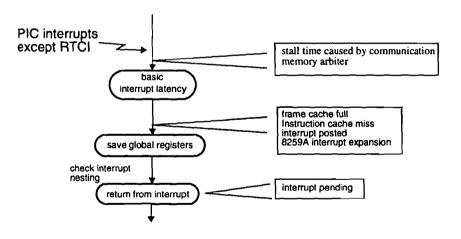

#### 5.1.1 Asynchronous context switching.

We are going to examine the different asynchronous control transitions that take place upon receiving an interrupt. For this purpose, the first version of a real time multitasking kernel is going to be used. This kernel has been ported from an existing one and even though it needs to be optimized, it constitutes a valuable tool that allows us to analyse the behaviour of the processor. The kernel has, as far as the hardware related items are concerned, the following characteristics:

- a) The time reference interrupt (or real time clock interrupt-RTCI) and master belt position interrupt (or master pulse interrupt-MPI) force the running task to relinquish the cpu to the scheduler, if preemption should take place, otherwise the interrupted task is resumed. If a higher priority task gets the cpu, it might be also preempted or it finishes its operation and gives up voluntarily the cpu. The scheduler will then reactivate the preempted task.

- b) The other interrupts produce signals to the scheduler. The scheduler makes use of this information in order to activate the relevant tasks later on. The scheduler gets control of the cpu after the interrupted task completes operation.

- c) The kernel has its own stack. However, this stack will only be used if the scheduler happens to be interrupted. For the other control transitions, the stack of the previous activated task is used. This approach limits the number of stack switchings and avoids eventual problems that might occur if the processor resumes its operation with invalid stacks.

d) The processor will operate constantly in the interrupt mode. This will ensure the robustness of the kernel.

The <u>latency time</u> is defined here as the time that elapses from the moment that one interrupt arrives until one task becomes operative. This definition covers the case that one task is preempted for the sake of a higher priority one, as well as the case that the scheduler is interrupted, and because of the interrupt, one task acquires a higher priority and is scheduled.

The latency time increases when a higher priority interrupt arrives than the one being serviced or by posting an equal or lower priority interrupt during an interrupt service routine.

In case a RTCI is being serviced and a MPI is requested, this last one will be immediately nested but no preemption takes place. The program will return to the RTCI service routine, which will eventually cause preemption, if the scheduler was not interrupted. In this particular case of preemption, the scheduler has the information of both interrupts in order to activate the proper task.

If the program is executing a MPI service routine and a TRCI arrives, this last one will be posted. The program will execute the TRCI service routine as soon as the scheduler performs a return from interrupt. The cpu handles the pending interrupt as if it has just arrived, however, the "latency" will be slightly lower. Note that the actual latency time with respect to the moment that the interrupt arrived may vary considerably due to preemption.

It is not allowed that a RTCI is posted if the cpu is processing a RTCI service routine (the same applies for the MPI) because it would mean that the time (or position) reference has been lost.

Multilple Peripheral Interrupt Controller (PIC) interrupts will cause naturally one interrupt being posted per interrupt service routine.

All the processor activity that is not related to the application software is called <u>overhead</u>. The software administration (the kernel), and the hardware characteristics (cpu-architecture, amount of wait states for external accesses, clock frequency) are responsible for both latency an overhead.

A calculation of the cpu contribution to the latency time follows. We are going to use these results to make later an estimation of the right balance between the task processing time and the overhead.

When a RTCI or a MPI arrives, three different situations can occur:

- 1) The scheduler is interrupted. This will only cause a restart of the scheduling mechanism in order to reinitiate the cpu-granting priorities. Then a waiting task can be activated.

- 2) A task was running when the interrupt arrived. The interrupt service routine gives the cpu to the scheduler, which may decide that the interrupted task should be preempted for the sake of a task with higher priority.

- 3) A RTCI service routine was running (or because of a RTCI-preemption one task was running) when a MPI arrives. The MPI service routine is nested. After the service routine notifies that a MPI has taken place to the scheduler (through increasing the MPI-counter), the program returns to the preempting task or to the RTCI service routine, in which case it will then call the scheduler for an eventual preemption. Nesting of RTCIs or MPIs within the other Peripheral Interrupt Controller interrupts result in immediate return to the previous interrupt routine.

These cases are depicted in the following figure:

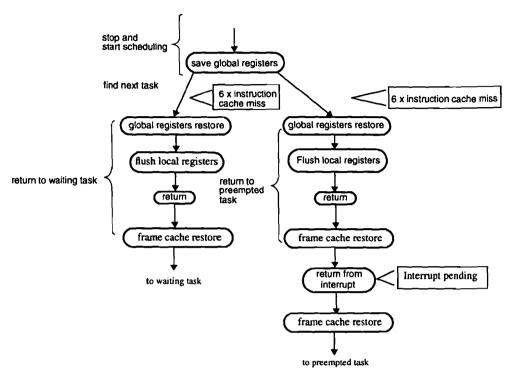

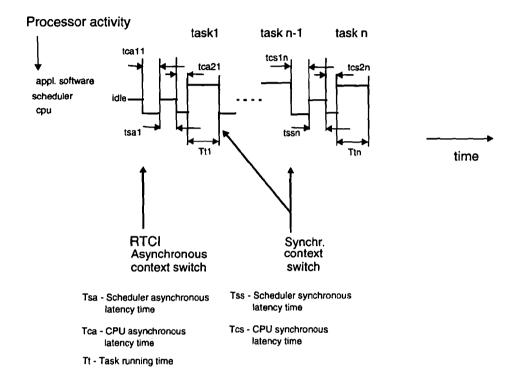

Figure 5.1: Asynchronous context switching (due to RTCI or MPI).

Possible expansions to the latency time are indicated by square blocks. The amount of cache misses, that is indicated in the figure gives an indication of the procedure nesting.

The timing calculations that follow are approximations, because of the internal parallelism of the processor; the introduced fault is marginal if we take into consideration that the timing is mainly determined by the external accesses. The ram accesses are performed with 2 wait states, and those to the eprom in a sequence of 2-1-1-2-1-1-1 wait states. The access times can be expressed as follows:

Access\_time\_ram =  $2 + 3 \times M$ ; M = amount of accesses = [1,8] Access\_time\_eprom =  $2 + 3 \times M1 + 2 \times M2 + 3 \times M3 + 2 \times M4$

M = M1 + M2 + M3 + M4 = amount of access = [1,8]

M1 = 1

M2 = [1,3] if M>1

M3 = 1 if M>4

M4 = [1,3] if M>5

Basic latency: Interrupt service routine in cache, Master pulse interrupt.

Hardware recognition: 4 cycles

Stop current instruction flow assuming a RISC instruction: 4 cycles

Determine next iP and save:

This value is taken from the instruction cache, afterwards 2 external accesses (M=2) are necessary to store this value onto the stack (at the location that corresponds to local register r2. The reference manual specifies 8 cycles for zero wait states. In case of 2 wait states:  $t = 8 + 2 \times M = 12$  cycles.

Read interrupt vector number: 18 cycles.

Check interrupt priority: 8 cycles.

Read Interrupt table pointer (2 external accesses M = 2): 15 cycles are specified in the reference manual [2] for zero wait states. In case of 2 wait states  $t = 15 + 2 \times M = 19$  cycles

Check if processor already interrupted: 6 cycles.

Current process in interrupt:

The reference manual specifies 14 cycles. We can assume that no external accesses are performed. The processor might need this time to re-establish the local register allocation mechanism.

Save process control and write interrupt record (M = 5 external accesses). 14 cycles are specified [2] for zero wait states. In case of 2 wait states  $t = 14 + 2 \times M = 24$  cycles

Compute interrupt record address of new local register set: 10 cycles.

Allocate new local register set: 3 cycles.

Fetch new instruction and start decoding: 2 cycles.

124 cycles

- Check if processor in interrupt mode: 6 cycles

- Save global registers:

To save the global registers the following sequence of instructions is assumed:

t = eff. add. calculation + external access + internal working

| lda | 64(sp),sp   | M = 2; $t = 2 + 8 + 1 = 12$ cycles.  |

|-----|-------------|--------------------------------------|

| stq | g0,64(fp)   | M = 8; $t = 2 + 26 + 1 = 29$ cycles. |

| stq | g4,80(fp)   | M = 8; $t = 2 + 26 + 1 = 29$ cycles. |

| stq | g8,96(fp)   | M = 8; $t = 2 + 26 + 1 = 29$ cycles. |

| stt | g12,112(fp) | M = 6; $t = 2 + 20 + 1 = 23$ cycles. |

|     |             |                                      |

123 cycles

#### Return from interrupt: