| MASTER                                                 |

|--------------------------------------------------------|

| Definition of a description language for IDDQ monitors |

|                                                        |

|                                                        |

| Waayers, T.F.                                          |

| Award date:<br>1995                                    |

|                                                        |

| Link to publication                                    |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

#

by

T.F. Waayers

June 1995

supervisor: Prof. ir. M.T.M. Segers

mentor: M. Sc. K. Baker advisor: Ir. F.G.M. Bouwman

© Philips Electronics N.V. 1995 All rights reserved. Reproduction in whole or in part is prohibited without written consent of the copyright owner.

# Definition of a description language for $I_{DDO}$ monitors

#### **Abstract**

This report describes the development of a language based on VHDL intended to simplify the use of  $I_{DDQ}$  instrumentation in production testing. This language called 'Monitor Description Format' or MDF, is part of the development by QTAG (Quality Test Action Group) of an infrastructure for quiescent current testing. The MDF can be used with commercial supported QTAG monitors ( $I_{DDQ}$  measurement equipment) to create a 'Plug & Play' environment for  $I_{DDQ}$  testing. Prior to the definition of MDF, first all known available  $I_{DDQ}$  monitors and QTAG proposals are discussed since developments in monitor design have a great deal of impact on the semantics and syntax of MDF. Furthermore, MDF integration in the Philips Test-development flow is discussed. This integration reveals some interesting shortcomings of to-days Test-development tools with respect to  $I_{DDQ}$  testing.

#### Keywords

CMOS testing, quiescent current,  $I_{DDQ}$  monitoring, Automatic Test Equipment, QTAG

#### **Preface**

This work was performed in partial fulfilment of the requirements to become Master of Electrical Engineering at the Eindhoven University of Technology. It was performed in the group 'VLSI Design Automation and Test' at Philips Research Laboratories during the period from October 1994 up to June 1995.

# Acknowledgements

I would like to thank a number of people in supporting me in this project. My mentor Keith Baker for his excellent guidance and advice. Frank Bouwman for his advice on software development, his punctual report reviewing and his overall support. Math Verstraelen for his support on testing in general. Furthermore, I would like to thank my supervisor Prof. ir. Rene Segers and Eric van Utteren for giving me the opportunity to carry out this project at Philips Research. I would also like to thank my roommates and fellow students who made my stay at the Philips Research Laboratories very pleasant.

#### Note

Section 2.2 of this report has been taken from [Bouwman, 95]. Section 6.8 of this report has been taken from [Baker, 95].

Philips Research Laboratories,

Eindhoven, June 1995

# **Contents**

| 1 Introdu | action                                        | 1  |

|-----------|-----------------------------------------------|----|

| 2 IC Desi | sign and Testing                              | 3  |

| 2.1       | Introduction                                  | 3  |

| 2.2       | The IC development flow                       |    |

| 2.3       | Structural test                               | 6  |

| 3 IDDQ t  | testing                                       | 9  |

| 3.1       | Introduction                                  | 9  |

| 3.2       | Basic concept of IDDQ testing                 | 9  |

| 3.3       | Advantages of current testing                 | 9  |

| 3.4       | Limitations of current testing                | 12 |

| 4 Automa  | atic Test Equipment                           | 15 |

| 4.1       | Introduction                                  | 15 |

| 4.2       | What ATE is                                   |    |

| 4.3       | Testing overview                              | 17 |

| 4.4       | Functional testing                            | 18 |

| 5 Quality | y Test Action Group (QTAG)                    | 23 |

| 5.1       | Introduction                                  | 23 |

| 5.2       | Goals of QTAG                                 | 23 |

| 5.3       | QTAG monitor classes                          | 25 |

| 5.4       | QTAG monitor types                            | 27 |

| 5.5       | QTAG monitor pins                             | 28 |

| 5.6       | Monitor Description Format (MDF) requirements | 28 |

| 6 IDDQ 1  |                                               | 31 |

| 6.1       | Introduction                                  | 31 |

| 6.2       | Monitor principles                            |    |

| 6.3       | QuiC-Mon v3.2                                 | 33 |

| 6.4       | QuiC-Mon v5.0                                 |    |

| 6.5       | OCIMU                                         | 37 |

| 6.6       | IDUNA-2                                       | 39 |

| 6.7       | LTX IDDQ monitor                              |    |

| 6.8       | The Fully Digital Interface                   | 43 |

| 7 MDF d   | · · · · · · · · · · · · · · · · · · ·         | 47 |

| 7.1       | Introduction                                  | 47 |

| 7.2       | QTAG pin classes                              | 47 |

| 7.3       | The entity description                        |    |

| 8 Using N | MDF in Philips CAD-Test flow                  | 57 |

| 8.1       | Introduction                                  | 57 |

| 8.2       | Computer Aided Test (CAT) system              |    |

| 8.3       | TASS                                          |    |

| 8.4       | Philips IDDQ Test-development flow            |    |

| 8.5       | MDF2TASS                                      |    |

| 8.6       | MDF2TASS example                              |    |

| 9 Conclu  | •                                             | 71 |

|           | e development                                 | 73 |

| Appendi     | x A BNF conventions                    | 75 |

|-------------|----------------------------------------|----|

| Appendi     | x B MDF entity description in BNF      | 77 |

| Appendi     | x C MDF standard package               | 81 |

| Appendi     | x D Lexical elements of MDF (and BSDL) | 83 |

| Appendi     | x E Files MDF2TASS example             | 85 |

| E.1         | PAT file: 'testdut.pat'                | 85 |

| E.2         | CTR file: 'testdut.tass'               | 85 |

| E.3         | ATF file: 'testdut.atf'                | 86 |

| E.4         | CTR file: 'mdf2tass.tass'              | 86 |

| E.5         | TDL file: 'mdf2tass.tdl'               | 87 |

| E.6         | ATF file: 'mdf2tass.atf'               | 88 |

| Appendi     | x F Examples MDF                       | 91 |

| <b>F.</b> 1 | MDF: IDUNA-2                           | 91 |

| F.2         | MDF: QUICKMON V5.0a                    | 92 |

| F.3         | MDF: LTX_IDDQ                          | 93 |

|             |                                        |    |

# 1 Introduction

Testing of Integrated Circuits (ICs) has become a major issue in research and development of Very Large Scale Integration (VLSI). ICs have been growing continuously in number of transistors and complexity. This has caused an increase in the probability of design errors. To prevent design errors, the design must be checked at several stages of the design. It is not possible to prevent manufacturing faults. Because the market asks for reliable, zero defect ICs every single IC produced must pass several tests. One of these tests is the *structural test*. The idea of structural test is that all structures, created on the silicon surface, must be tested for correctness against known models for failing the process. The problem of structural testing of ICs is complicated by the enormous amount of possible faults, and the limited accessibility of parts of the ICs via the IC pins.

To detect as much faults as possible during structural test, it is generally believed that already during the design phase of the IC, testability has to be taken into account. This is referred to as Design for Testability (DfT). In DfT, methods are developed which give greater controllability and observability to VLSI circuits under test. In case of combinatorial logic, this can be achieved by automatic test pattern generation tools, using algorithms based upon fault models. The complexity of getting high controllability and observability within sequential circuits demands for extra precautions during the design trajectory of an IC. The sequential controllability and observability is achieved by memory elements which can be used in two modes, called a scannable memory element. In normal mode, it acts as a conventional memory element. In test mode, the input of the memory element is directly under control of the vector generation by test software. All scannable memory elements in test mode form a shift register, called a scan path, which can be filled with stimuli data. After a period in normal mode, in which the device acts according its specification, the contents of all scanable memory elements can be shifted out in test mode.

When the scan test DfT technique is used during the design phase the testability of the design improves drastically, resulting in high fault coverage within relative short test times. This is very important because structural test should be performed on every individual IC produced.

While testing, stimuli are applied to the IC bringing it into a predefined state. After a 'normal' period, resulting values are captured and compared with known responses. ICs failing this comparison intend to be defect. The generation of test stimuli and related expected data is done according to fault models, for example the stuck-at model in which every fault on the input or output of a gate is assumed to behave as if it is shorted to fixed logic values. In the case of CMOS, many defects do not cause stuck-at behaviour. Other models like 'bridging and open fault model' are needed to generate tests with high fault coverage.

Conventional testing is done by so called *voltage testing*. During this type of testing responses of the device under test (DUT) are captured and compared with expected data, as mentioned above. To achieve higher fault coverage with CMOS VLSI ICs, another test method called *current testing* is used. This method is based on the fact that CMOS ICs cause very low power supply current during the logic quiescent period. This current, I<sub>DDO</sub>, can be nanoam-

peres for VLSI circuits and much less for smaller scale ICs. In CMOS ICs, stuck-at faults and most other types of defects cause state-dependent elevated  $I_{DDQ}$ . Consequently,  $I_{DDQ}$  measurement is a very efficient test technique for CMOS ICs. To achieve highly reliable ICs,  $I_{DDQ}$  should be measured at each test vector in a test set that achieves 100% node toggling [Rajsuman, 95]. Despite its effectiveness, CMOS IC test methods at most companies usually measure  $I_{DDQ}$  at only a few test vectors or not at all. This is partially due to the lack of commercial instrumentation for high-speed  $I_{DDQ}$  measurements (current monitors) and partially due to the difficult technique: "Hearing a pin fall after a cannon shot!".

At the present time, development of a current monitor is an open problem. A number of companies are developing current monitors independently to match with their existing test equipment and production lines. Considering the present difficulties in current-monitoring systems and the mismatch in various equipment, the IEEE technical committee on test technology has initiated the development of a standard for current monitors. The proposed name for this standard is QTAG (Quality Test Action Group). One issue of this standard is the so called 'Monitor Description Format' (MDF), a description language that uses the syntax of VHDL, IEEE Std 1076, in the way BSDL (Boundary Scan Description Language) does [Parker, 90] to describe the functionality of the  $I_{DDQ}$  monitoring hardware. MDF is needed to allow the monitor to be described in a machine and human readable format, so that different monitors could be used with different test systems, and would allow the test engineer to efficiently and effectively utilize the monitor in the application.

This report deals with the definition of the MDF and the use of MDF in the  $I_{DDQ}$  test development flow to create a 'Plug&Play' environment for  $I_{DDQ}$  monitors. To show the possibilities of MDF, a compiler has been written using LEX and YACC. This compiler has been integrated in the Philips test-development flow by the developed MDF2TASS software, using the possibilities of the Philips test assembler software TASS [CAT team, 94].

In the first three chapters of this report an introduction to testing and testing hardware is given for those who are not familiar with testing. In the next chapter QTAG and its proposals are introduced. After these introductory chapters a start for the development of the 'Plug&Play' environment is made in chapter 6 by mapping the currently available monitors. In chapter 7 the definition of MDF is described. The following chapters describe the  $I_{DDQ}$  test-development flow and the development of the MDF2TASS software used in the Philips test-development flow. Also results of an example are given. In the last chapters conclusions are drawn from the MDF2TASS results and subjects for further research are mentioned.

# 2 IC Design and Testing

# 2.1 Introduction

Before an IC can be delivered to a customer, its correctness must be determined. This implies that each individual IC must operate conform to its specifications. Since the design of ICs is done in a number of phases, it must be checked that no errors are introduced (an error meaning a difference between implementation and specification). After manufacturing the IC must be tested to assure its functionality conform its specification. The term *defect* is used to mean those physical occurrences which give rise to some circuit malfunction. A *fault* is the logical manifestation of a defect. In this chapter we will first discuss the IC design process in more detail. Secondly, we will take a look at the IC testing process, which is closely related to the design process and *verification* as opposed to *production testing* will be explained.

# 2.2 The IC development flow

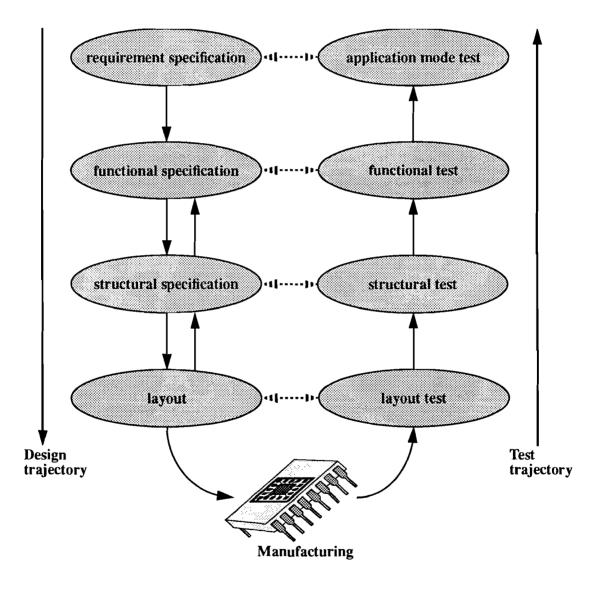

The implementation of a concept at system level into one or more ICs consists of many small steps [Claassen, 89][Bruls, 94]. One way of representing this development is illustrated in Figure 2-1. The figure shows the flow from high-level to low-level specifications, the manufacturing, and the various levels of testing.

# 2.2.1 Design

Developments start with a concept for a system. Once the partitioning of the system in the various ICs is done, a requirements specification can be written for each IC. This is often not a formal description using a specific hardware description or programming language, but a plain textual description of the high-level behaviour of the complete IC.

The second step is to translate this requirements specification into a formal functional description. On this level, the functionality of the complete IC is described on a level of, for example, adders, multipliers, and registers. For this purpose, formal hardware description languages, such as VHDL, or other programming languages (Pascal, C) are used. The functional specification can be simulated to verify the correctness. However, the step between requirement and functional specification is a weak point in the flow and remains a source of concern because formal verification of this step is impossible due to a lacking formal requirements specification.

The formal description at the functional level can be used to generate the structural specification (gate-level description) and finally a layout. It is common practice to apply commercially available synthesis tools for these last translation steps. Verification of the correctness of these steps is possible as a result of the formal approach.

# 2.2.2 Manufacturing

The resulting layout specification has to be implemented on silicon. For this purpose each layer of the layout is handled separately and several processing steps are required for each of them. It is important to notice here that, due to the complexity and sensitivity to disturbances of various processing steps, it is possible for an IC to contain a defect causing it to fail one or more specifications [Maly, 88a]. Depending on the size of the chip and the stage of development of the IC as well as the process, the percentage of fault-free processed VLSI circuits, i.e. the production yield, can virtually have any value. For complex innovative ICs and immature processes it may be low, 10% or even less, while for mass-produced ICs in a mature process the production yield may be as high as 95% or even more.

Figure 2-1: The IC design and test flow

# 2.2.3 Testing

To assure that the manufactured ICs perform the specified tasks, various tests are applied. Depending on the product development stage (e.g. prototype or mass-production), this test can be very extensive or just minimal to check the correctness of the production process. The three types of tests which can be distinguished are:

- Validation test: This test checks whether the device actually implements the specified

functionality and can be applied in the complete system. Once the device has been

shown to be functionally correct, it does not need to be validated again. The horizontal

arrows in Figure 2-1 represent the validation processes.

- Characterization test: This test checks under which conditions the IC is able to perform

according to the requirements. It includes checks on process variability, temperature

variations, and power supply changes. This test is performed on a small sample size

and only needs to be carried out once for a design and a given process.

- Production test: This test checks that no abnormal processing conditions or local disturbances occurred during the manufacturing process, causing a particular IC to malfunction. Because such a defect can occur on any device, each IC has to be tested for its correctness with respect to the processing.

Validation and characterization tests both are part of what is called *verification*. Production tests are not part of the verification trajectory!

Each of these three tests can be performed at various levels of abstraction, which are indicated in Figure 2-1. At the lowest level of abstraction, one should test whether the layout as specified by the designer is actually realized on silicon, bearing in mind certain process margins. Despite the direct relationship between a layout test and the detection of defects, this level of testing is only starting to be applied because of the relatively computation-intensive technique of fault list generation and test vector generation.

For production testing, the structural level is used in most situations. Because of the available fault models, which are an abstraction of the electrical impact of the defects on the corresponding level of design description, and corresponding efficient algorithms for test vector generation and evaluation, structural tests offer an excellent opportunity to derive a metric for the effectiveness of a test set (fault coverage). For the application of these structural tests, the scan technique often is used as simple controllability and observability improvement for the sequential circuit elements.

During the 80s and begin 90s, the stuck-at fault model has been the de-facto standard for a large part of the industry in classifying the test effectiveness. However, it should be remarked that the limited accuracy of the available fault models, especially the stuck-at fault model, in representing the behaviour of actual defects and the limitations of the static behaviour of a scan based test are becoming more evident and it is becoming more and more difficult to

meet the ever-increasing quality requirements. Additional and alternative test methods are considered to overcome these problems. These vary from voltage stress measurements to supply current measurements in the quiescent mode of a circuit ( $I_{DDO}$  or  $I_{SSO}$ ).

Structural tests concentrate on finding spot defects and not on parametric defects. For example, as a result of a local processing disturbance, the signal propagation delay between two points on an IC might be increased, causing the IC to fail the functional specification, although the structure of the connections is not changed. Therefore, some tests also need to be carried out at the functional level.

On top of this level, it might be necessary to test the operation of the device in the way it is supposed to function in the system it is designed for. This is known as application mode test. Here the issue to be checked is not whether the IC implements a certain algorithm, but whether the implementation of that algorithm in combination with the other part of the system performs the expected tasks. In order to obtain enough controllability over the various conditions which might need to be varied also an application mode test is preferably applied on an automatic test equipment (ATE) instead of a bench implementing the application. However, this implies some requirements with respect to the availability of the right input signals and processing of the output signals [Bouwman, 95]. Application mode testing is generally only applied for validation and characterization purposes. For production testing this approach is too costly and will only be used if the quality demands of the customer are high.

The area of interest to us in this thesis is structural testing. Therefore, we look at this kind of testing more closely in the following section.

# 2.3 Structural test

The higher density of modern circuits results in an enormous set of possible fault cases. The main problem in structural testing is how to detect such faults, given the limited accessibility via the IC pins.

The requirements for a structural test are strict. The test should be fast because it is performed on every individual IC, and it must still have a high fault coverage since customers do not accept faulty ICs. Furthermore, it is important to be able to generate this test in a relative short time in order to prevent lengthy design times. It is generally believed that these requirements can only be met if already during the design phase the IC testability is taken into account. This is referred to as design for testability.

# 2.3.1 Design for Testability

Testability can be defined as follows [Bennetts, 84]: "An electronic circuit is testable if test-patterns can be generated, evaluated, and applied in such a way as to satisfy pre-defined levels of performance (v.g. detection, location, application) within a pre-defined cost budget and time scale".

Using this definition Design for Testability (DfT) can then be defined as the design effort that is specifically employed to ensure that a device is testable.

There are two important attributes related to testability, namely *controllability* and *observability*. Controllability is the ability to establish a specific signal value at each node in a circuit by setting values on the circuit's inputs. Observability is the ability to determine the signal value at any node in a circuit by observing its outputs.

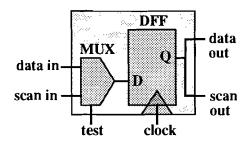

Figure 2-2: Scannable D-flipflop

When the scan test DfT technique is used during the design phase the testability of the design improves drastically by creating an extra test mode for the design. In normal mode, the design operates just as it is supposed to, according to its specification. In test mode, the memory elements will be connected into one or more scan paths. To achieve this, the memory elements must be replaced by versions that are equipped with such a test mode (this version is called scannable variant). In Figure 2-2 a scannable D-flipflop (DFF) is shown. The multiplexer (MUX) directs data either from data-in or scan-in to the D-input of the flipflop depending on the logic state of the test signal, which denotes if the scannable flipflop is used in test mode or in normal mode. In test mode the input of the DFF is directed from scan-in.

Figure 2-3: Scan path during test mode

When connecting scan-in and scan-out of different scannable flipflops, a potential scan path arises. A scan path is a shift register that only exists during test mode. Test patterns can be shifted in this register and applied to the rest of the circuit (controllability), which now only contains combinatorial logic, see Figure 2-3. After applying the test patterns during normal

mode, responses can be captured at the primary outputs of the circuit and the inputs of the memory elements. Switched back in test mode, captured responses in the memory elements can be shifted out of the scan path and gathered by the tester (observability). In this way, test pattern generation has only to be done for the combinatorial part of the circuit, this eases the process of structural testing.

### 2.3.2 Increasing fault coverage

The conventional methodology for testing digital CMOS circuits is the execution of a test sequence which exercises as many of the internal nodes and transistors as possible. A test pattern sequence should be able to detect, as a minimum, any stuck at 1 or stuck at 0 fault. On very complex VLSI devices, the development of the test pattern to achieve 100% fault coverage can be very tedious and extensive, resulting in many millions of vectors being generated. Even then, the level of fault coverage may not be sufficient to provide the degree of quality desired.

Quality level is a function of *total* fault coverage, of which the single stuck-at is simply an estimator. To maintain a given quality level, fault coverage must increase with increasing chip size (assuming the defect density of the fabrication process remains constant) [Maxwall, 92]. Since stuck-at tests by themselves are inadequate, the detection of other fault types needs to be quantified in order to obtain a good estimate of total fault coverage.

One method of getting higher total fault coverage is by adding functional test vectors to the structural test. As mentioned before signal propagation delay between two points on an IC might be increased, causing the IC to fail the functional specification, although the structure of the connections is not corrupted. In chapter 4, in which automatic test equipment is described, the term functional testing is used for both structural and functional test. From a tester point of view there is no difference.

Another method to obtain higher fault coverage is a test method based upon power supply current measurement. This method, also known as  $I_{DDQ}$  testing, is capable of detecting physical defects such as bridging, gate-oxide shorts, and spot defects in CMOS circuits. It is important to realize that at present time  $I_{DDQ}$  testing is supplemental to voltage testing. To verify functionality, voltage testing is still required. However, reliability can be significantly improved by  $I_{DDQ}$  testing.

# $I_{DDQ}$ testing

# 3.1 Introduction

Current testing is a method for enhancing the quality of IC tests by monitoring the level of power supply current. It is primarily applied to CMOS circuits where the quiescent power supply current,  $I_{DDQ}$ , in a defect-free device is very low. In the presence of a defect ,  $I_{DDQ}$  can be orders of magnitude higher. Thus by monitoring the power supply current, it is possible to detect defects and achieve a higher device quality.

# 3.2 Basic concept of $I_{DDQ}$ testing

A CMOS gate consists of an NMOS pulldown network and a complementary PMOS pullup network. In a fault-free situation for any given inputs, only one part conducts, connecting the output node to either the  $V_{DD}$  or the  $V_{SS}$  node. The gate output voltage is well defined at either logic level 1 or 0, and the circuit does not provide a conducting path from  $V_{DD}$  to  $V_{SS}$ . Thus in the fault-free situation, steady-state current in the circuit is negligible. The circuit contains only some junction leakage current. The magnitude of this leakage current is in the order of nA for VLSI and for all practical purposes it can be neglected.

In the presence of various physical defects, the steady-state current in a CMOS circuit no longer remains negligible. The magnitude of the power supply current increases in the presence of a fault. Thus, by monitoring the power supply current it may be determined whether or not a circuit contains a fault.

# 3.3 Advantages of current testing

IC manufacturing involves many critical steps such as metal depositions of a few thousand angstroms thick, sub-micron photolithography, and etching contact holes a few tenths of a micrometer wide. Small imperfections during these steps can cause randomly distributed defects in the IC such as shorts between metal lines or open contacts between the input signal and the polysilicon gate control.  $I_{DDQ}$  can be used to detect these defects using test vectors based upon other fault models than the stuck-at fault model.

#### 3.3.1 Total observability

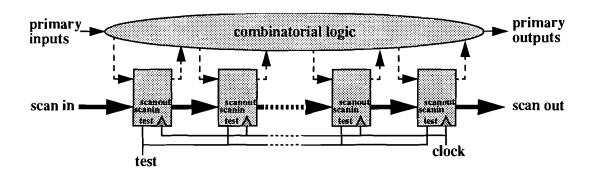

$I_{DDQ}$  can also be used to detect faults that can be found with voltage testing, using shorter test vectors. This is a result of the *total observability*  $I_{DDQ}$  offers. The benefit of  $I_{DDQ}$  total observability above voltage testing will be shown by example.

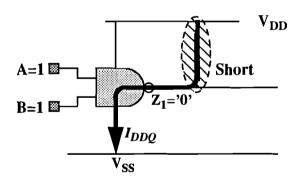

In Figure 3-1 a test pattern 'A=1, B=1, C=0, D=1' is necessary to detect a short between output  $Z_1$  and the power supply. The first two bits (A=1, B=1) of the test pattern are necessary to activate the defect so that a faulty behaviour is produced. In this example the test pattern is designed to produce a "0" on a non-defective  $Z_1$  and power will force the output value to be a "1". A "1" in place of the expected "0" identifies a defect.

Figure 3-1: Test circuit with output  $Z_1$  shorted to power

The remaining part of the test pattern (C=0, D=1) is necessary to propagate the defective behaviour to the primary output M, where a tester can observe the signal and compare it to the expected value. In the case of a sequential circuit, a sequence of test patterns is necessary to sensitize and propagate the defect.

Figure 3-2: Fault detection with current testing

In current testing, the defective behaviour of a circuit is observed by measuring its power supply current rather than by propagating the fault to the primary output. In this case, a shorter test pattern (A=1, B=1) is required to detect the short shown in Figure 3-1. This is illustrated in Figure 3-2. A "0" on output  $Z_1$  causes elevated quiescent current to flow from the power supply to ground in the presence of a short.

The faulty behaviour need not be propagated to an output since the power supply acts as an observation point on all gates simultaneously. This makes the test program generation task much simpler: only fault activation patterns need to be generated. It is found that fault activation is very similar to logic verification and that the simulation patterns used for verification are very effective at achieving high fault coverage with current testing.

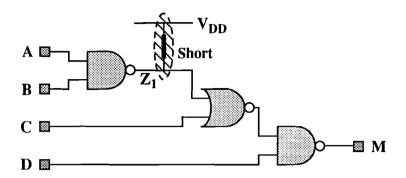

#### 3.3.2 Enhanced defect detection

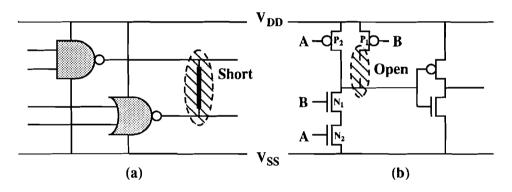

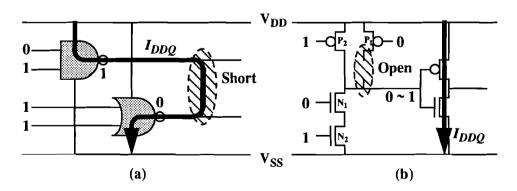

Another advantage of current testing is its ability to detect defects that are not detected by the voltage detection technique that rely on stuck-at fault models. In stuck-at fault models, it is assumed that every defect causes the input or output of a gate to behave as if it is shorted to power or to ground. In the case of CMOS, many defects do not cause stuck-at behaviour. Figure 3-3 shows two examples of defects that are not characterized by stuck-at behaviour. i) short between two signal lines, and ii) an open contact on a FET.

Figure 3-3: Examples of defects not covered by stuck-at testing

With current testing it is possible to detect many of the defects that escape stuck-at testing. In Figure 3-4 the tests for detecting the defects in Figure 3-3 are shown. In order to detect a short, complementary signal values are generated at the two ends of the suspected short. An elevated quiescent current will then flow through the power supply if a short exists.

Figure 3-4: Detection of non-stuck-at defects with current testing

The detection of opens is more complicated. In this case a test pattern is applied that causes a net to float. In Figure 3-4 (b) this is achieved by applying a test pattern (A=1, B=0) that turns off the transistors P2 and N1. If transistor P1 is open due to a defect, the output floats. Initially the voltage on the output stays at a 1 or a 0 depending upon the charge stored on the output capacitance. However, if enough time elapses, leakage currents in reverse biased FET junctions cause the output voltage to drift to an intermediate value between logic 1 and 0. When that happens the logic gates controlled by the floating signal start to conduct D.C. current, causing an  $I_{DDQ}$  test failure. How much time should be allowed for sufficient  $I_{DDQ}$  to develop depends upon the capacitance on the node, the leakage current, and the size and threshold voltages of the FETs being driven by the floating node.

In addition to detecting shorts and opens, current test can also detect small leakage currents which may indicate long term reliability problems. For example, excessive gate leakage (current flowing through the gate oxide to substrate) may not cause an immediate fault, but it can lead to long term failure.

# 3.4 Limitations of current testing

Current testing is an 'inexpensive' and effective way to enhance the quality of CMOS ICs. However, it has several limitations that must be kept in mind. Two most important limitations are the signal to noise ratio and the test time.

To avoid failing good devices it is necessary to have a good signal to noise ratio. The signal is the D.C. current flow caused by a defect. If the defect is a short to power supply or a short between two nets, the signal would be of the order of several hundred microamperes or even a few milliamperes. However, some of the defects create a much smaller signal. The noise current is caused by the valid leakage current through the reverse biased junctions in each transistor on the IC. In addition, current transients caused by switching can have very long time constants, approaching several milliseconds. Any noise on the power supply or input signals can also cause current to flow through the device. For example, a 50 mV noise on the ground can cause 5 to 10 microamperes of noise in moderately dense ICs. As the number of transistors and wires on a chip increase, the noise continues to grow; at very high gate counts, the noise level is so high that it often masks defects.

The other limitation of current testing is the long measure time. Enough time should be allowed for i) the power supply transient currents to die down; and ii) the floating nodes to drift sufficiently to cause a current flow. For example, a floating node with 1 pF capacitance could take over 50 milliseconds to change its value from 5 to 3 Volts. Test economics limits the amount of time that can be spent on the number of measurements that can be made.

Selecting which vectors to perform  $I_{DDQ}$  testing has been a problem until recently.  $I_{DDQ}$  testing detects many common classes of process defects, such as bridges and opens, in a much more direct fashion than functional or scan test. However, the industry is accustomed to measuring fault coverage via the stuck-at fault. If  $I_{DDQ}$  testing is not based on a fault model then testing many tens of thousands of vectors with a functional test maybe the only alterna-

tive. If the industry could agree to measure fault coverage for  $I_{DDQ}$  on the basis of a common model, it would be possibly to reduce the number of  $I_{DDQ}$  vectors for VLSI ICs to a few thousand possible a few hundred.

How many vectors are necessary for efficient  $I_{DDQ}$  testing is a serious question. However, it is a problem surrounded by controversy. One fact that is widely accepted is that current Automatic Test Equipment (ATE) systems are too slow, and that ten to twenty  $I_{DDQ}$  vectors are the limit without adaptations. So  $I_{DDQ}$  can only be used as a supplementary test with today's instrumentation. If the industry had an accepted fault model, it is possible that  $I_{DDQ}$  vector selection could be minimized to a few hundred vectors. In combination with faster measurement hardware this could lead to acceptance of  $I_{DDQ}$  as a general test method.

# 4 Automatic Test Equipment

# 4.1 Introduction

While testing, stimuli data has to be applied to the Device Under Test (DUT) and resulting responses have to be captured and compared with expected data. The equipment that translates the stimuli data into voltages that are set on the right times on the right pins and that observes output pins to compare with expected data is called Automatic Test Equipment (ATE).

# 4.2 What ATE is

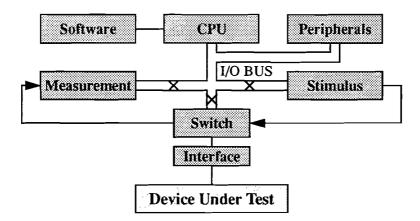

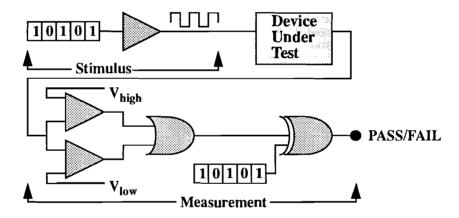

ATE is computer-controlled equipment that is used to verify certain parameters of a DUT and to identify defects that may be present in the DUT. It may, in its most general form, be block diagrammed as shown in Figure 4-1.

Figure 4-1: Block diagram of generic ATE system

At the heart of the system is the "control section". The control section consists of the computer (CPU), its peripherals, and its software. The computer executes application-specific software that directs the stimulus, measurement, and switching resources of the system in a manner that will yield the desired test results and data.

The stimulus section provides vectors to the DUT. The measurement section evaluates the DUT's response to the vectors from the stimulus section. The switching section may be thought of as the programmable path network between the stimulus and the measurement section. The control part then operates upon the information obtained from the measurement section to determine the next course of action (e.g., abort the test, issue a failure message, or issue a "test pass" message).

The ATE system is interfaced to the DUT via an interface adapter which is often DUT-specific. This interface adapter may be as simple as wires between the ATE system and the DUT, or it may contain extensive electronics for level shifting, signal translation, and special signal conditioning.

Typical stimulus devices for electronics ATE for large-scale integration (LSI) and very-large-scale integration (VLSI) integrated circuits and the printed circuit board assemblies (PCBAs) include programmable power supply units (PSUs), signal generators, and data driver pins. Typical measurement devices include parametric measuring units (PMUs), digital multimeters, timer-counters, and data receiver pins. Typical switching systems may be constructed of either relays or solid-state logic circuits, depending on the levels and types of signals to be routed. The stimulus, measurement, and switching devices and circuitry may be configured as individual items interfaced to the control section central processor unit, or may be designed as integrated, multifunction electronic assemblies.

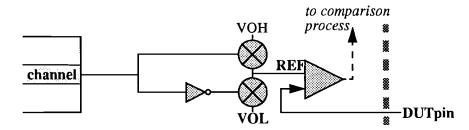

Pass/fail parameters are typically programmed into the system when the application test program is written. This situation is illustrated in Figure 4-2. Immediately prior to test program execution, digital drive levels are set on the stimulus pins and digital receive thresholds are set on the measurement pins. Then the specific functional "1"s and "0"s are driven into the DUT and sensed from the DUT by the tester electronics. On the measurement side, if a signal exceeds the logic "1" threshold, it is assumed to be valid logic "1". If it is below the set logic "0" threshold, it is assumed to be logic "0". If the signal is between the two thresholds, it is deemed to be a defective level and indicates that the DUT is not functioning correctly.

Figure 4-2: Schematic diagram of digital pin electronics

The only other indication of non functionality is if a "1" is received when a "0" was expected, or vica versa. Some testers allow for the programming of a time limit by which the response must be received, and others allow for the sensing of driver pins to ensure that the stimulus signal was actually able to drive the DUT. Regardless of the level of sophistication of the electronics and the software, if the tester does not provide specific parametric values as part of the test results, it is considered a functional tester.

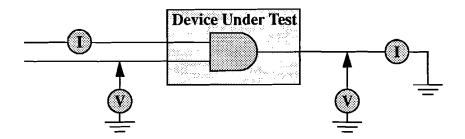

Figure 4-3: Circuit diagram of DC parametric measurement

Adding parametrics involves adding enough hardware and software to provide actual measurements in engineering units (e.g. volts, amps, and seconds). The term DC parametrics (see Figure 4-3) refers to such parameters as input current, output voltage, and supply current. The term AC parametrics refers to such parameters as rise time, fall time and propagation delay (e.g. time between input stimulus and output response). It is possible for a functional ATE to provide go/no-go (pass/fail) indication of parameters without providing actual measurements in parametric units. For DC parametric approximations, one way that this is accomplished is by running the ATE with drive levels, thresholds, and loading conditions set as close as possible to the parametric limits of the DUT.

# 4.3 Testing overview

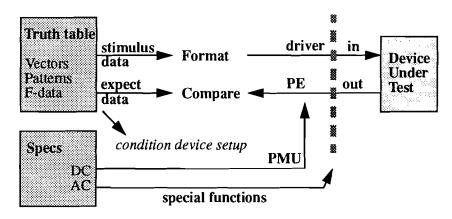

First goal with testing is to insure that the DUT operates according to its truth table. Figure 4-4 shows the general structure for testing logic devices.

Figure 4-4: Block diagram of testing process

The truth table is loaded into the tester in the form of patterns (vectors or F-data). To get the data to the device, stimulus data is output from the pattern memory. It is passed through the formatter, which combines the data with timing edges to form a waveform. The waveform is passed to a driver, which converts the data levels to programmed voltage values. The voltage values called "input references", are supplied by the test engineer in the test program. The total waveform is passed to the device through the interface. The interface consists of a load-

board, which connects to the tester head, and a socket which is wired to the loadboard. The device respond with an output, which is passed through the loadboard to a comparator in the testhead. Expected data is converted by output voltage references and compared with device output. Naturally there is a driver and comparator for each pin. The pattern memory is also used to pass a sequence of patterns to condition the device to a state where the DC parametric measuring unit can be connected, under software control, to various pins for making voltage and current measurements.

# 4.4 Functional testing

Functional testing refers to the process of accessing the normal input/output (I/O) interface of the DUT (its package pins) and providing stimulus patterns and measurement verifications that the DUT is functioning. Functional testing relies on the assumption that if the DUT functions, no process-induced problems exist.

#### 4.4.1 Truth table

Logic devices are tested by two types of testers, Golden Device and truth table (stored response). Golden Device testers compare the DUT with a known good device. They are only used during production or incoming inspection. The most common tester is the stored response or truth table tester. It stores the truth table for a device in its memory, formats the data, and applies the data to the device. One line of a truth table is called pattern or vector, they are applied to the device one at a time. Each vector or pattern consists of stimuli and expect data. Vectors are stored in the high-speed pattern memory of the tester.

The test program loads vectors into the pattern memory and applies its pattern data to the device. Each test program will call several vector loads to test the different functions of the DUT. The pattern data must be formatted before it is passed on to the DUT. This means that it must have timing and voltages assigned to it.

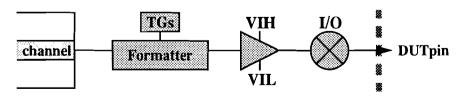

# 4.4.2 Creating stimuli data

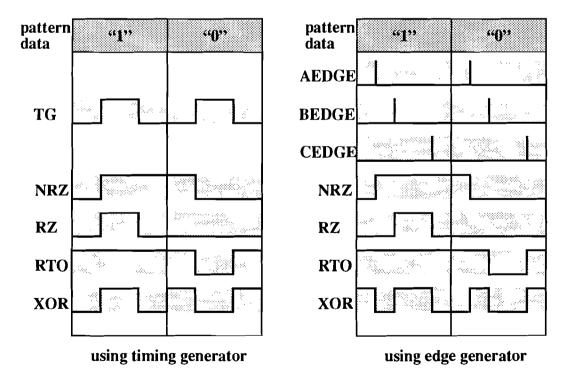

Truth table / pattern data alone is a poor method to stimulate the device, because of the weak control of timing. The pattern data must be formatted and passed to the device through the tester driver. This is illustrated in Figure 4-5. The formatter couples the pattern data with timing generators (TGs) or timing edges. At the device, data appears as a timing diagram.

Figure 4-5: Schematic of tester hardware which creates input waveforms

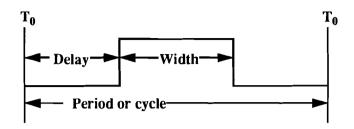

Each cycle begins at time zero,  $T_0$ , with respect to the device, and lasts for a certain length of time specified in the test program. Most testers have a number of timing generators or clocks that are shared by all the pins. Figure 4-6 illustrates the timing parameters used in testing.

Figure 4-6: Timing parameters used in testing

A waveform is the output of the formatter. Waveforms are individually specified for each pin. The common waveforms are shown in Figure 4-7. Some testers define timing with edges (or phases).

Common edge definitions would be:

AEDGE: Data transition edge BEDGE: Leading edge of pulse CEDGE: Trailing edge of pulse

The formatter couples the edges with the pattern data to form the standard waveforms.

Figure 4-7: Common input waveforms created by formatter

Depending on the tester, the flexibility of its timing generators to create waveforms will vary. The common waveforms illustrated in Figure 4-7 have the following properties:

- NRZ: Nonreturn to zero or straight data. When coupled with a TG, the data transition is delayed from  $T_0$ , but the data level remains for the length of a complete period.

- **RZ**: Return to zero. When pattern data is "1", a pulse equal to the assigned TG is created. The level remains low for pattern data "0".

- RTO: Return to one. When pattern data is "0", a negative pulse equal to the assigned TG is created. The level remains high for pattern data "1".

- **XOR**:Exclusive OR (surrounded by complement). Positive pulse on pattern data "1". Negative pulse on pattern data "0".

Although the above four waveforms are used in the majority of applications, the possible waveforms available on modern VLSI testers will not be limited to them. The formatter creates the waveform and passes it to the driver, which converts the logical levels to voltages.

# 4.4.3 Comparing DUT output against expected data

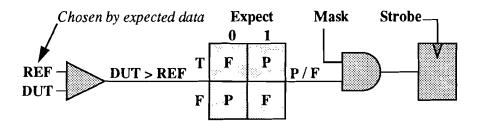

A comparator is used to compare the output of the DUT with the expected pattern data. A schematic of the comparator is given in Figure 4-8. The DUT output is passed to the comparator through the loadboard connector. The pattern data (expected data) selects the high or low level of the output reference assigned to that pin. There is a choice of at least two output reference pairs that can be assigned to each comparator. The level is compared with the DUT output and the result is passed to the next stage of the pin electronics for pass/fail determination.

Figure 4-8: Schematic of tester comparator hardware

A failure is recorded only if the comparison is incorrect at a specified time as determined by a strobe. There are two types of strobes, edge and window. With edge strobe an instantaneous latch of comparison results occurs. Failure is recorded only at a specified instant in the cycle. Using window strobe, the comparator result is observed during an interval. Any failure of the comparison during the interval is a failure; i.e., the DUT output must be at the correct level during the entire interval.

For various reasons it may be desirable to mask the failure results for certain cycles or pins. Although the comparator is always attached to the pin, the comparator results are not monitored for input pins. Also during input cycles of I/O pins the comparator is disabled. The user must be given the option of masking the failure results for any cycle, known as a "don't care" cycle. Thus, to have complete control, the following has to be possible on a cycle-by-cycle basis:

- 1. Switch driver from driving to Hi-Z.

- 2. Enable and disable comparator results.

This is accomplished on modern testers by embedding the I/O control and masking within the pattern data. The pattern data for each pin will have a minimum of five states as shown in Table 4-1.

| Pattern<br>data | Driver<br>state | Comparator state           |  |

|-----------------|-----------------|----------------------------|--|

| 1               | drive one       | disabled                   |  |

| 0               | drive zero      | disabled                   |  |

| Н               | Hi-Z            | compare against high level |  |

| L               | Hi-Z            | compare against low level  |  |

| X               | Hi-Z            | disabled                   |  |

Table 4-1: Minimum tester states

The results of the comparator can be masked for an input-only pin by not assigning a strobe to that pin. This is obvious from the complete diagram of the comparison process, given in Figure 4-9.

Figure 4-9: Diagram of output to expected data comparison process

The expect data selects an output reference level, which is compared with the DUT output. The comparison results are passed through some logic for decoding, as represented by the truth table after the comparator. Depending on the expect data, a pass or fail is passed on as a

"0" or "1". The failure can be masked by the pattern data. The pass, "0" or fail, "1" is latched into the results register by the strobe. Notice that the default condition in the results register is a "0"; i.e., a pass is assumed unless otherwise shown.

Finally a mechanical relay must be closed to connect the pin electronics to the device. Different methods are used to close the relay in different testers. Some require at least one driver register to have a "1" in it for that pin; some require a direct closing statement; and others close it whenever a pin is defined. The point is that it can be controlled.

# **5** Quality Test Action Group (QTAG)

# 5.1 Introduction

QTAG was proposed at a public meeting of the IC test engineering community at the International Test Conference in 1993 (ITC 93). The need for QTAG has arisen from the rapidly rising quality demands that the cutsomers of CMOS ICs are making on IC vendors. In general, the experience of the IC vendors has been that significant improvements in overall realistic fault coverage, using the classical stuck-at fault model, cannot be expected. Adopting more advanced fault models based on realistic defect probabilities leads the test engineering department to adopting  $I_{DDO}$  based test methods for advanced CMOS devices [Baker, 90].

Experience over a number of years with  $I_{DDQ}$  testing within Philips Semiconductors and reports from development centres in the industry indicate that  $I_{DDQ}$  testing has its drawbacks. Measurement of a significant number of  $I_{DDQ}$  vectors is excessively time consuming with conventional automatic test equipment (ATE) systems. In the past ATE vendors have been pressed to improve the performance of the ATE based  $I_{DDQ}$  facilities, but in general the facilities provided have not been widely used. For some CMOS products Philips has developed and maintained special test systems for  $I_{DDQ}$  testing. Such a discrepancy between the needs for  $I_{DDQ}$  testing and the capabilities of the ATE systems is heading for a "finger-pointing" crisis between the test engineering departments and the ATE vendors. Action is needed to avoid this crisis. QTAG's aim is to develop a de-facto standard for test fixture based  $I_{DDQ}$  monitors. The standard should allow the monitor vendors to develop innovative products with the functionality that will create a small, but active market-place for their monitors.

# 5.2 Goals of QTAG

The original proposals for QTAG made at ITC 93, had the aim of focusing the attention of the industry on the problem of  $I_{DDQ}$  production testing. The proposal was made to the industry that the solution was to be found in the so called "Little-Foot" monitors.

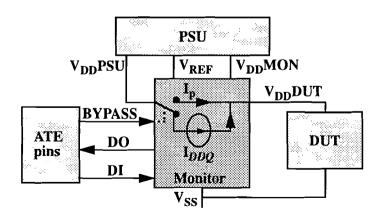

Figure 5-1: QTAG  $I_{DDO}$  monitor with bypass option

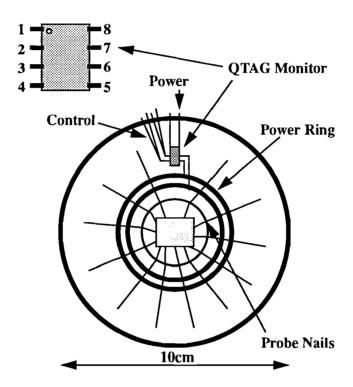

These monitors are based on the technology developed for Built-In Current (BIC) sensors, see Figure 5-1, but packaged in such a manner as to be used on any test fixture. Two major modes are provided, the normal  $I_{DDQ}$  current monitor mode and the bypass mode. If bypass mode is activated a short circuit resistance is provided between  $V_{DD}PSU$  and  $V_{DD}DUT$ . Measurement during this period is not possible. In monitor mode measurements are made. The idea of the *Little-Foot* was that the physical foot-print on the test fixture was so small that it could even be used on probe-cards, see Figure 5-2. This requirement for small physical size, demands that the pin count be small (< 10 pins). An acceptable package is the SO-8, demanding less than  $0.5 \text{cm}^2$  with SMD decoupling capacitors.

Figure 5-2: OTAG monitor on a probe card

Given that the monitor is to be driven by an ATE system virtually any digital interface based on three or four pins can be created. Originally, a simple two mode interface was proposed at ITC 93. However, it is better to allow a more complex interface to be defined which gives the capability to control more monitors with the same pins and permits much more functionality to be built in to future monitors [Hales, 94a]. At the same time the standard has to be realistic about the capabilities of monitors that could be designed in a reasonable timescale.

After ITC 93 a second class of monitor was defined. These are the so-called *Big-Foot* monitors. This class of monitor, probably not based on BIC sensor technology, requires a significantly larger area on the test fixture, so would not be as useful in production testing. However, given the known performance of such monitors, and the need to provide a measurement capability for engineering applications it was decided to cover them within the standard as a separate class. The idea being that such monitors could also be driven by the same ATE driver software.

A set of goals of QTAG was defined by Keith Baker of Philips Research and Chuck Hawkins of the University of New Mexico. These goals were re-stated in the Philips proposals for QTAG [Baker, 93] and have been reproduced below:

- 1. A definition of a "minimal-pin" configuration package for a monitor whose specific design may differ for any manufacturer. That such a monitor allows any digital test system to drive and receive information appropriate for I<sub>DDQ</sub>/ I<sub>SSQ</sub> testing.

- 2. A defined pin configuration that demands packaging in a minimal number of package types to cover most applications needs.

- 3. A standard ATE interface definition and physical form that allows all common test fixtures to be used: DUT board, probe-card and contactors.

- 4. A standard that defines both VDD and VSS line monitor configurations.

- 5. A standard that would recommend or define multiple monitors and multiple power pin configurations.

- 6. Definition of a Monitor Description Format (MDF) that would allow different monitor implementations to be easily driven by ATE hardware and software.

- 7. A standard that allows tester selection of a variable  $I_{DDO}/I_{SSO}$  threshold.

- 8. A standard that allows robust physical construction and reliable operation in a stressful Electro Static Discharge (ESD) environment.

# 5.3 QTAG monitor classes

In its proposal, Philips developed the original goals of QTAG into a structure with three classes of monitor. Details of the three classes are given in Table 5-1. Class 1 would be the original Little-Foot monitors. These would be tightly standardized monitors which would be the central thrust of the QTAG activity. From the specification of Class 1 the MDF would be created. The other two classes form the Big-Foot monitor types.

Progress during the Monitor Standard Definition phase of QTAG has been very uneven for the two different types of monitors. For the Little-Foot monitors, the semiconductor vendors have produced a very clear definition of the function and physical format of the monitor. For the Big-Foot monitors, the progress has been less rapid because of the lack of a clear champion for the concept among the semiconductor vendors.

Table 5-1: Overview of QTAG Monitor Classes

| Class | Template<br>cm | Function    | Pins | Packages<br>type |

|-------|----------------|-------------|------|------------------|

| 1     | 0.8 x 1        | production  | 8    | SO-8             |

|       |                |             |      | SO-8L            |

|       |                |             |      | SO-14            |

| 2     | 2 x 2          | production  | 24   | any              |

|       |                | engineering |      |                  |

| 3     | 4 x 4          | engineering | 24   | any              |

### 5.3.1 Proposals for Little-Foot monitors: Class 1

Texas instruments (TI) also made a proposal to QTAG in a much more detailed form than Philips. This developed the concept of the class 1 monitor in a definitive architecture. The TI proposal built on the original *Little-Foot* concept addressing many of its shortcomings. Main issues are using multiple monitors, providing a truly digital interface, giving a measurement option etc. [Hales, 94a]. These issues were originally not addressed by Philips [Baker, 93].

After the completion of the Monitor Standard Definition phase it is clear that the semiconductor vendors proposals for class 1 monitors give this class a leading role in development of the standard.

After bi-lateral discussions between Philips and TI, a common proposal based on the umbrella format from Philips and the class 1 specific proposal from TI has been put forward [Hales, 94b]. Philips would then develop a prototype QTAG class 1 monitor on the basis of this specification. This prototype would be a proof of concept study for QTAG [Baker, 94b].

A second European group, Alcatel Bell-Telephone, Technical Highschool of Ostend and the University of Hull, have also supported the development of the class-1 monitor by the development of a  $I_{DDQ}$  monitor based on discrete components. However, the pinning and functionality would be compatible with the general proposal for the class-1 [Manhoeve, 94].

#### 5.3.2 Proposals for Big-Foot monitors: Class 2/3

None of the major semi-conductor vendors has made more detailed proposals for class 2 or 3 monitors. Given the lack of interest in these classes from those parts of the industry that could create a demand for a marketable product, the most direct solution would be to scrap them from the standard. Further enquiries reveal that there are groups developing such monitors, however, they have not found the time to fully participate in QTAG.

The Quic-Mon circuit, originally developed by Sandia Labs but further developed by one of the original authors with Philips Semiconductors, falls very clearly into the *Big-Foot* category. This monitor is without doubt the most popular type published todate and QTAG must ensure that users of this monitor are not excluded from support on ATE systems [Wallquist, 93].

# 5.4 QTAG monitor types

The QTAG monitor classes are based on pin count, function and physical size. The monitors can also be distinguished in capability. This is done by the QTAG monitor type definitions. In the next subsections the two basic types of monitor are discussed:

- Threshold: return a simple pass-fail, or analog value

- · Measurement: returns a digital value

Current monitors can be divided in semi-digital and fully-digital versions. Semi-digital monitors are controlled by a mixture of digital and analog pins. These monitors are the majority of QTAG monitors in development at this time. Fully digital monitors are much simpler to interface to a digital tester because they have only digital control pins. Moreover, the binary control codes for digital monitors must be inserted in the test vectors of the DUT, which is an extra step. Semi-digital monitors do not need those codes in the test vectors. Digital monitors have an internal architecture that must either be standardized or defined within the MDF to allow the ATE to control the monitor. Also a distinction can be made in  $I_{DDQ}$  and  $I_{SSQ}$  monitors. The difference between these two types is the current observation point. In case of  $I_{DDQ}$  the measure pin will be connected to the DUTs  $V_{DD}$  pins, whereas with  $I_{SSQ}$  the measure pin will be connected to the DUTs  $V_{SS}$  pins.

## 5.4.1 Threshold monitors

The threshold monitor is the simplest of the QTAG monitors. In case of a digital output, it simply tests if the quiescent current  $(I_{DDQ}/I_{SSQ})$  value is above or below a user-specified or fixed threshold value. The result of this comparison is returned to the tester as a binary pass/fail value (DO output). When multiple monitors are chained this signal will be forwarded by a chain of DI and DO pins. In case of an analog output value, this will be directed to the pin electronics comparator, which requires the digital tester to determine the pass or fail by comparing the input voltage to a known reference voltage set on the pin electronics comparator.

#### 5.4.2 Measurement monitors

Measurement monitors provide either a parallel or serial digital word to one or more test system pin electronics comparators. In case of serial data, timing of the data is determined via a separate digital clock pin on the monitor driven by a pin electronics driver. With analogue testers or by using an ADC on the test fixture it is possible to create a measurement capability on threshold monitors with an analog output. When using an analog threshold monitor in this way it is called a measurement monitor.

# 5.5 QTAG monitor pins

DO

The standard pins of a QTAG  $I_{DDQ}$  monitor are listed below in Table 5-2. The first three pins are power supply connections to the tester's power supply, and the fourth pin is the VDD supply to the DUT. The other four pins form the interface which the tester uses to communicate with the QTAG monitor. The MODE, CLK and DI pins are outputs from the tester to the QTAG monitor, and the DO pin is an output from the monitor back to the tester. Multiple monitors can be connected by chaining together their DI and DO pins and connecting the MODE and CLK outputs from the tester to the MODE and CLK input pins of all of the QTAG monitors.

Pin Description VDD\_MON VDD supply for the QTAG monitor **VSS** VSS supply for the QTAG monitor VDD PSU VDD supply for the DUT from the tester VDD\_DUT VDD output from the QTAG monitor to the DUT **MODE** Mode select **CLK** Clock DΙ Data input

Table 5-2: QTAG  $I_{DDO}$  monitor pins

# 5.6 Monitor Description Format (MDF) requirements

Data output

One of the QTAG goals is definition of a Monitor Description Format. At the initial meeting of QTAG the concept of the MDF was outlined. MDF was needed to allow the monitor to be described in a machine and human readable format, so that different monitors could be used with different test systems, and would allow the test engineer to efficiently utilize the monitor in the application.

It was a stated goal that the MDF should be so broadly formulated as to allow monitors not fully compliant with the QTAG standard to be used. This may seem strange at first. However, the QTAG document [Baker, 94a] makes it clear that this is essential. For example, the QTAG monitor proposal will allow monitors to be daisy-chained to allow two or more monitors to be used in conjunction. However, this demands that a pin is available as digital input pin, DI, but for so-called semi-digital monitors in stand-alone applications this would waste a valuable monitor pin. So flexibility is needed to provide a standard that maximizes the potential of the individual monitors.

The semantics of the MDF language are based on the resources provided by a simple digital tester, i.e. pin memories, pin driver, pin comparators, PSU, PMU, and a test program executed on a computer. Each of these resources is assumed to be under control of the test program. A test program is a computer program executed by the control computer of the test system. It is assumed that the test program has access to a set of standard routines to control the monitor. Furthermore it is assumed the files of test vectors loaded by the test program into the pin memories and pin timing generators have been so modified by an external program that all the control, triggering and timing of the monitor and DUT are correct.

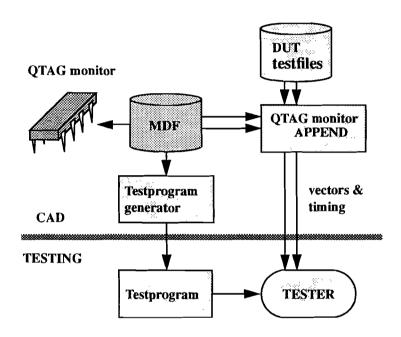

Figure 5-3: QTAG Design-test flow

Using the semantic model described above, the MDF has to contain the information for two functions, as shown in Figure 5-3. First the MDF must contain the information needed to allow a filter function called Append, to modify the Computer Aided Design (CAD) generated test data to include the monitor timing and vectors. Second, the MDF must provide input to an automatic test program generator to create the correct test programs to control the tester resources.

MDF is not a general purpose hardware description language. It is intended solely as a means of describing the key aspects of the implementation of  $I_{DDQ}/I_{SSQ}$  monitors used in conjunction with ATE systems. MDF is not a simulation model.

# Features Described by MDF:

- Pin declarations and pin definitions for monitors

- Definition of architecture of digital monitors

- · Definitions of monitor actions

- View of monitor for test fixture

# Features not described by MDF:

- How chains of monitors are linked on a test fixture

- Test programming or test functions

- Input format from CAD tools for ATE

The MDF is best served by a simple format specifically created for the application. So that the general behaviour of the implementation is defined in the standard and only the device specifics are provided in MDF. In this the role model of BSDL used by IEEE std 1149.1, which specifically excludes extraneous details is followed.

In chapter 7 MDF is defined according to the requirements stated in this chapter and the needs that followed from the stock taking of present available  $I_{DDQ}$  monitors and detailed proposals for future development in chapter 6. The architecture of digital monitors has not been defined in MDF so far, due to the lack of a standard digital interface. This part of MDF will be future work. The MDF defined yet covers all QTAG monitors known and expected in the future, including the digital monitors without specific interface information needed to control this type of monitor.

# 6 $I_{DDQ}$ monitors

# 6.1 Introduction

Developments in monitor design have a great deal of impact on the semantics and syntax of MDF. At this time, the only monitors actually in development are simple types that use only a semi-digital interface. This requires that the ATE system must be able to supply analogue signals or accept analog input signals. In this chapter first two measurement principles are described in section 6.2. In the following sections an overview is given of the current monitors developed and published in the literature. Each monitor will be described, mentioning details that are used while defining MDF. This implies that the controlling part of the monitors will be main issue. In section 6.8 a fully digital interface that was proposed to the QTAG-group is discussed. Below is a short summary of the monitors presently available:

#### QuiC-Mon v3.2

Developed by the university of New Mexico and Sandia Labs, this is one of the best defined  $I_{DDQ}$  monitors so far published in the literature. It is a complex monitor that provides a digital measurement capability to the test system. It is suited to the task of device characterization and analysis.

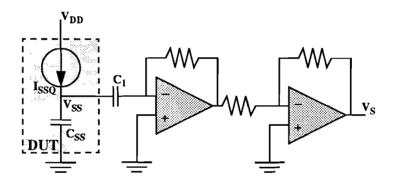

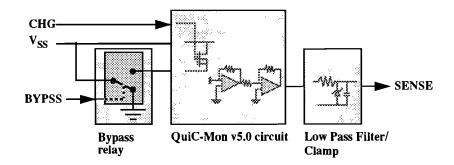

# • QuiC-Mon v5.0

A new version of the original QuiC-Mon monitor, further developed by one of the original authors with Philips Semiconductors. This is a simpler monitor, that can be used for both  $I_{DDO}/I_{SSO}$ , but provides an analogue value to evaluate as pass/fail.

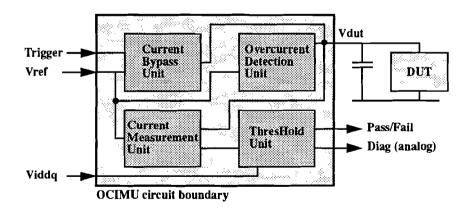

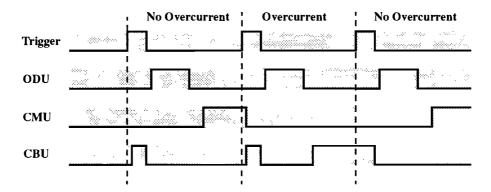

#### OCIMU

Developed by Alcatel-Bell and Technical School Ostende to demonstrate the feasibility of QTAG monitors for  $I_{DDQ}$  testing. It is capable of performing a relatively high speed (measurement time can be less than 30  $\mu$ s for a  $2\mu$ F load) current measurement especially when driving a high capacitive load (several  $\mu$ F). It provides a digital pass/fail to the test system.

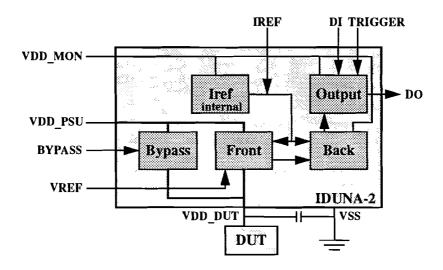

#### • IDUNA-2

A demonstration QTAG class 1 monitor developed by Philips Research and Lancaster University in Application Specific Integrated Circuit (ASIC) form. It provides a digital pass/fail to the tester based on a fixed internal threshold current, that can be altered through a analog pin.

# LTX I<sub>DDQ</sub> monitor

This monitor is a stand alone option of a LTX test system. It has been designed to integrate into the current test systems. The LTX trillium test head is modified to accept the  $I_{DDQ}$  monitor. It provides a digital measurement capability to the test system. Internal threshold can be set by a binary value on four digital pins.

## 6.2 Monitor principles

The problem of measuring  $I_{DDQ}$  current is basically measuring the current flowing into the DUT after all transients have settled to a steady state. It is important that the monitoring device should not influence the DUT. This implies that the  $I_{DDQ}$  monitor should be transparent at the moment the logic state of the circuit changes. Finally the monitor should be placed as close as physically possible to the DUT (actually on the loadboard) to minimize environmental influences. Especially since during the test of an IC a lot of signal activity takes place in the testhead to which the loadboard is attached. Test signals with rising and falling times less than 1 ns are not uncommon, this generates a lot of high frequency switching noise which can disturb other signals and thus create a hostile signal environment. As a result and because of the noise accurate measurements of voltage levels below 1 mV are not feasible, connection wires are to be kept as short as possible.

To measure DC currents two basic principles can be used. The first one is based on a current to voltage conversion by placing a resistive sensing element in the current path and applying Ohm's law. The second principle is based upon a voltage to time conversion by measuring the time needed to let the voltage across a given capacitor drop by a predefined amount. This method is based upon the discharging of the capacitor over a load resistance when it is disconnected from the supply voltage, this is known as Keating-Meyer principle [Keating;Meyer,87].

The main drawback of the first method is that the introduction of a resistive element in the current path of the DUT inevitably causes a voltage drop across it. To be of any use, the voltage drop caused by the sensing element should be either negligible (even for large currents) or be made invisible to the DUT. The DUT will always see a well/stabilised supply voltage. Ensuring that the voltage drop is negligible, even for large currents, implies that a low ohmic sensing element should be used. This implies also that the voltage drop caused by small currents will also be very small. To measure this very accurate low voltage measuring techniques are required. Application of such techniques may either not be feasible due to a hostile signal environment or take too much time. The second drawback is that the sensing element also needs to pass the switching transients. To avoid a large voltage drop during the transients, the measuring device should be bypassed during the transients.

The advantage of the Keating-Meyer principle is that no special action needs to be taken in relation to transients, as the principle is relying on the parasitic capacitance of the DUTs supply pin and (if present) on the decoupling capacitance connected to the supply pin. The main drawback of the Keating-Meyer principle is that the supply of the DUT is left floating during the measurement phase. This would not cause any problem if it could be guaranteed that the voltage drop during the measurement phase is in all cases negligible. A negligible voltage drop once again requires very accurate very low voltage measurements. If the overcurrent is too high then it is possible that the supply voltage drops too much, leaving the circuit in an unknown state. Another drawback is that the measuring speed is function of the total capacitance.

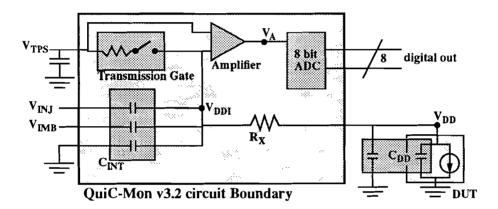

# 6.3 QuiC-Mon v3.2

In this section a printed wiring bord called QuiC-Mon (Quiescent Current Monitor) version 3.2 is described. QuiC-Mon, developed by the university of New Mexico and Sandia Labs, reports an eight-bit value that may be converted into an absolute current measurement. It uses the Keating-Meyer method of  $I_{DDQ}$  measurement. This technique requires knowledge of the DUT  $V_{DD}$  pin capacitance ( $C_{DD}$ ), see Figure 6-1; QuiC-Mon makes independent  $C_{DD}$  measurements up to 4 nF in the same vector as the  $I_{DDQ}$  measurement. The  $I_{DDQ}$  range is programmable, but typically up to 25  $\mu$ A may be measured with the onboard Analog-to-Digital Converter (ADC) for a target  $I_{DDQ}$  resolution of 100 nA.  $I_{DDQ}$  values that fall outside the measurement range are signalled by a overrange output from the ADC. Range can be doubled through ADC cascading.

Figure 6-1: Block diagram of QuiC-Mon v3.2

Maximum test frequencies depend upon several factors, a primary one being the DUT power supply current ( $I_{DD}$ ) transient settling time. Measurement rate also depends heavily on capacitance contributed by the DUT and load board. QuiC-Mon switches out most of the loadboard capacitance. Higher capacitance environments in the  $\mu F$  range slow  $I_{DD}$  measurements considerably, primarily because of RC time constants on the  $V_{DD}$  node introduced by QuiC-Mon. Despite these degradations, vector rates of over 250 kHz have been achieved on smaller VLSI devices with QuiC-Mon [Wallquist et-al, 93].

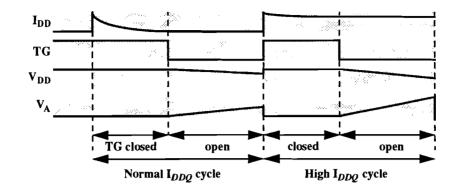

If the Transmission Gate switch is closed, the DUT draws current from the Tester Power Supply ( $V_{TPS}$  in Figure 6-1). If the Transmission Gate switch is opened, the DUT draws current from its own capacitance ( $C_{DD}$ ). As a result, voltage on  $V_{DD}$  (and  $V_{DDI}$ ) drops causing  $V_A$  to increase linearly. For typical  $I_{DDQ}$  measurements, the voltage drop in  $V_{DD}$  is on the order of 10 mV; in this range, it is assumed that even resistive defect loads will be linear. After a predefined discharge time has elapsed, the amplifier output is converted to a digital value representing measured  $I_{DDQ}$ .

Figure 6-2: Typical Keating-Meyer Waveforms

Figure 6-3: Typical QuiC-Mon v3.2 timing waveforms

- QTAG class & type: The QuiC-Mon v3.2 monitor clearly belongs to class 2 or 3, because

of using a wiring board, limiting its physical size. It is a semi-digital measurement type

monitor, because of its analog pins and external measurement equipment used for CDD

measurement.

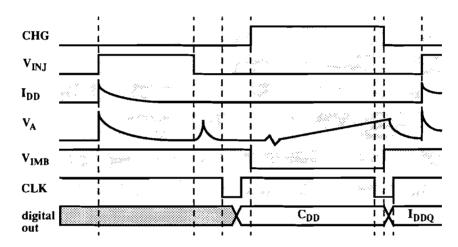

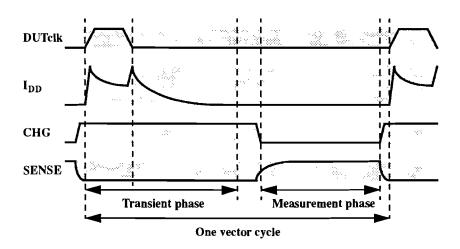

- Monitor control: In literature describing QuiC-Mon v3.2 the typical Keating Meyer Waveforms (see Figure 6-2) are used to explain the measurement part [Wallquist et-al, 93]. In this figure the relation of I<sub>DD</sub> and V<sub>A</sub> is shown. In Figure 6-3 typical QuiC-Mon timing waveforms are shown. The CLK signal is used to latch the ADC output. The CHG input is a inverted version of TG described above. CHG is used in the final hardware version of QuiC-Mon. Note that the digital output is used for both I<sub>DDQ</sub> measurement and C<sub>DD</sub> measurement. Controlling this type of monitor fully automated is difficult. This is caused by the critical timing (floating V<sub>DD</sub>) and continuous C<sub>DD</sub> measurements needed for accurate I<sub>DDQ</sub> measurements.

# 6.4 QuiC-Mon v5.0

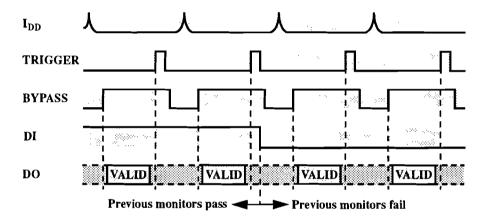

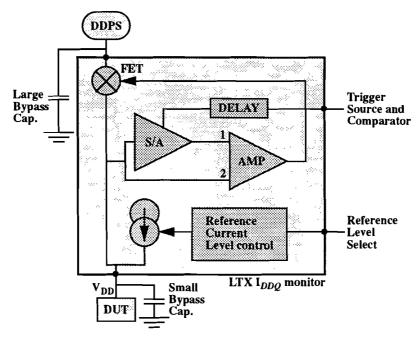

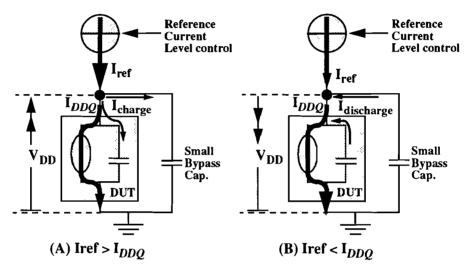

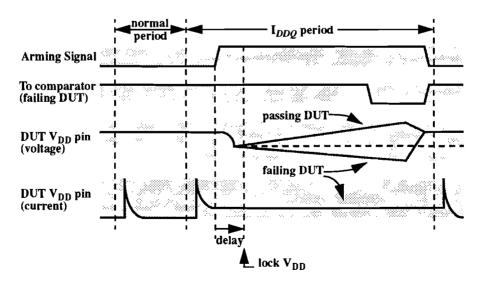

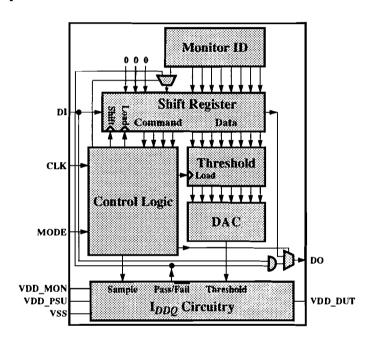

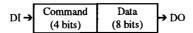

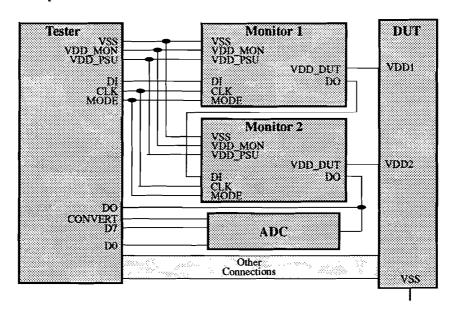

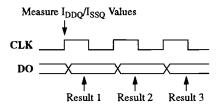

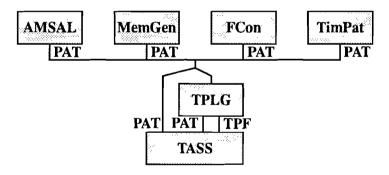

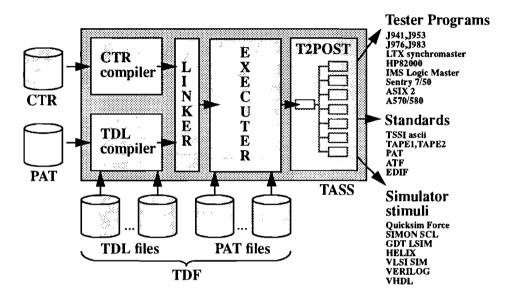

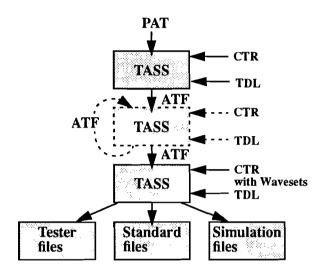

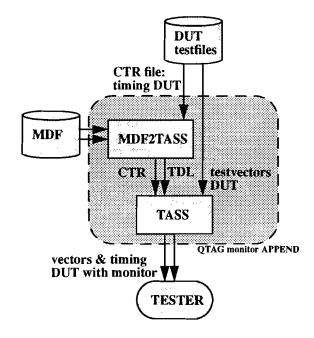

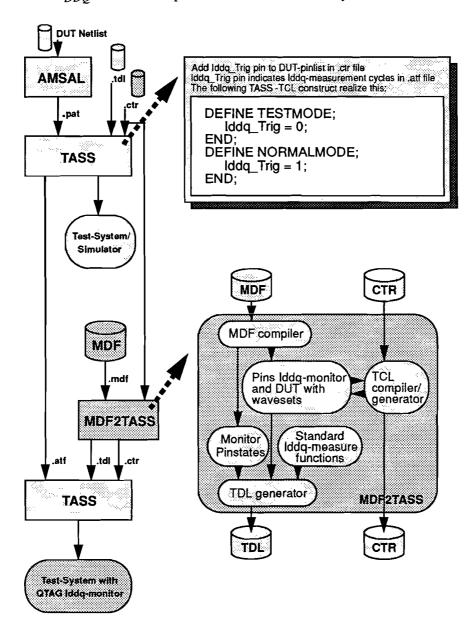

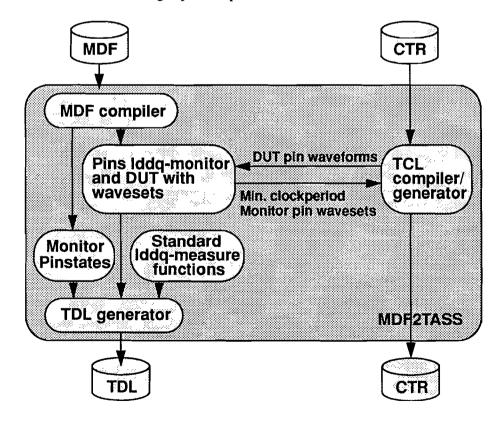

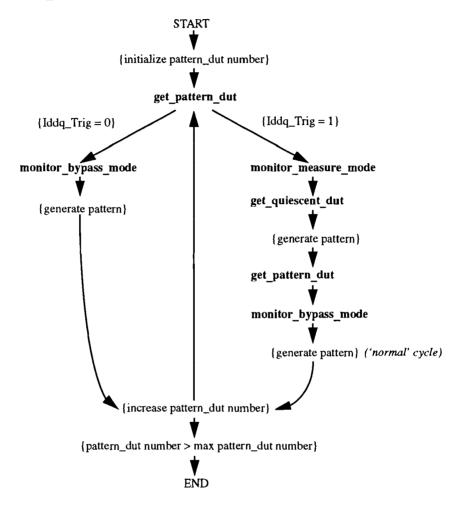

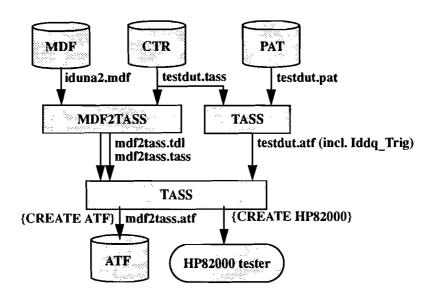

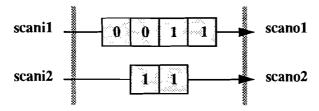

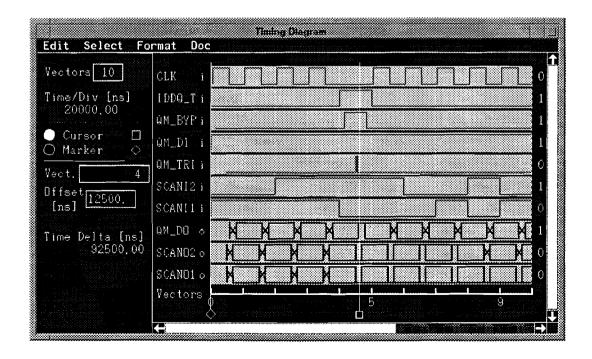

This section decribes a new version of QuiC-Mon, further developed by one of the original authors with Philips Semiconductors. This monitor can be used for both  $I_{DDQ}/I_{SSQ}$ . Version 5.0 of QuiC-Mon takes the Keating-Meyer concept one step farther then version 3.2. The QuiC-Mon v3.2 allowed a simple calculation of the quiescent current (For a constant  $I_{DDQ}$ , the slope of the voltage drop at the node is constant) by measuring the amount of voltage drop after a predefined period of time, if  $C_{DD}$  was known. However, measuring current in this way has its drawbacks. The most obvious being a reliance on timing accuracy, as strobing at different times results in what can be considered different current gains. Longer wait times result in higher current resolution. Unless timing is guaranteed accurate, incorrect  $I_{DDQ}$  readings can result.