#### MASTER

An optimizing C-compiler for the PMS500 processor using the Lcc front end

van Loon, M.R.

Award date: 1995

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Technische Universiteit **tu**? Eindhoven

Faculty of Electrical Engineering Section of Digital Information Systems

Master's Thesis:

# An optimizing C-compiler for the PMS500 processor using the Lcc front end

M.R. van Loon

Coach : Ir. A.G.M. Geurts, Drs. C.M. Moerman, H.J.M. Joosten

- Supervisor : Prof. Ir. M.P.J. Stevens

- Period : July 1994 February 1995

The Faculty of Electrical Engineering of Eindhoven University of Technology does not accept any responsibility regarding the contents of Master's Theses.

# **Table of Contents**

| 1  | Abstra                          | Act                                                                          |  |

|----|---------------------------------|------------------------------------------------------------------------------|--|

| 2  | Introd                          | uction                                                                       |  |

| 3  | Survey                          | of compiler generating utilities                                             |  |

| 4  | Descr                           | ption of the target processor                                                |  |

|    | 4.1                             | The CONTEXT switching scheme 10                                              |  |

|    | 4.2                             | The SP, DP and EP pointers 10                                                |  |

|    | 4.3                             | The status register                                                          |  |

|    | 4.4                             | The mode register and I/O                                                    |  |

|    | 4.5                             | IRQ registers and Interrupts                                                 |  |

|    | 4.6                             | The PC register                                                              |  |

|    | 4.7                             | The PMS500 instruction set                                                   |  |

| 5  | Buildi                          | ng a dumb compiler with Lcc                                                  |  |

|    | 5.1                             | A brief description of the Lcc code generation interface                     |  |

|    | 5.2                             | Description of the dumb compiler 13                                          |  |

|    |                                 | 5.2.1 Assumptions                                                            |  |

|    |                                 | 5.2.2 Problems, possible solutions and useful information provided by Lcc 13 |  |

|    |                                 | 5.2.3 Possible optimizations                                                 |  |

|    |                                 | 5.2.4 Summary                                                                |  |

|    |                                 | •                                                                            |  |

| 6  | Invest                          | igation for useful additions to the PMS500 instruction set                   |  |

| 7  | Structure of the final compiler |                                                                              |  |

|    | 7.1                             | Possible optimizations                                                       |  |

|    | 7.2                             | Data flow analysis                                                           |  |

|    | 7.3                             | Loop optimization                                                            |  |

|    | 7.4                             | Code elimination and code substitution                                       |  |

| 8  | Data                            | Flow Analysis                                                                |  |

|    | 8.1                             | Collecting reference- and definition information                             |  |

|    | 8.2                             | Determining usage- and definition points                                     |  |

|    | 8.3                             | Data Flow Graph Construction                                                 |  |

|    | 8.4                             | Alias analysis                                                               |  |

|    | 8.5                             | Reaching definitions                                                         |  |

|    | 8.6                             | Finding cycles in the DFG                                                    |  |

|    | 8.7                             | Making use of the calculated data flow information                           |  |

|    | 8.8                             | Forward data flow analysis based on divergence                               |  |

|    | 8.9                             | Backward data flow analysis based on divergence                              |  |

| 9  | Regist                          | er allocation                                                                |  |

| ,  | 9.1                             | Defining live variables for register allocation                              |  |

|    | 9.1<br>9.2                      | Graph Colouring                                                              |  |

|    | 9.2<br>9.3                      | Simulated execution                                                          |  |

| 10 | Imple                           | nentation                                                                    |  |

| 10 | 10.1                            | Data structures                                                              |  |

|    | 10.1                            | 10.1.1 Reference-definition information                                      |  |

|    |                                 |                                                                              |  |

|    |                                 |                                                                              |  |

|    |                                 | 10.1.3 Extensions to codenodes                                               |  |

|       | 10.1.4 Extensions to symbol table entries                                     |                |

|-------|-------------------------------------------------------------------------------|----------------|

|       | 10.1.5 Lists for aliases                                                      |                |

|       | 10.1.6 Bitfields for data flow analysis                                       |                |

|       | 10.2 Algorithm complexity                                                     |                |

|       | 10.2.1 Building the DFG                                                       |                |

|       | 10.2.2 Alias analysis                                                         |                |

|       | 10.2.3 Reaching definitions                                                   |                |

|       | 10.2.4 Live variable analysis                                                 |                |

|       | 10.3 Using the data flow information and implementing optimization algorithms |                |

|       | 10.4 Calling trees                                                            |                |

|       | 10.5 Modifications to the front end                                           |                |

|       | 10.6 Validation and libraries                                                 | 51             |

| 11    | Conclusions                                                                   | 53             |

| 12    | Bibliography                                                                  | 51             |

| 12    |                                                                               | J <del>4</del> |

| I.    | List of criteria                                                              | 56             |

| П.    | List of compiler generating utilities                                         | 57             |

|       | A. Compiler Tool Kits                                                         |                |

|       | 1. Amsterdam Compiler Kit (ACK)                                               | 57             |

|       | 2. ELI                                                                        | 58             |

|       | 3. The GMD Tool Box (Cocktail)                                                | 59             |

|       | 4. Purdue Compiler Construction Tool Set (PCCTS)                              |                |

|       | B. Retargetable compilers                                                     | 61             |

|       | 1. Lcc                                                                        | 61             |

|       | 2. GCC                                                                        | 63             |

|       | 3. Archelon User Retargetable Development Tools II                            | 64             |

| ш.    | Summary of discarded tools                                                    | 66             |

| IV.   | List of Lcc opcodes                                                           | 67             |

| V.    | The PMS500 instruction set                                                    | 68             |

| VI.   | Function declarations                                                         | 70             |

| VII.  | Global variables and definitions                                              | 74             |

| VIII. | Index                                                                         | 75             |

•

## List of Tables

| Table | 1 Available registers                          | 9  |

|-------|------------------------------------------------|----|

| Table | 2 Usage statistics of MOV Ax, Ay+c instruction | 16 |

| Table | 3 List of Lcc opcodes                          | 67 |

| Table | 4 List of PMS500 opcodes                       | 69 |

# List of Figures

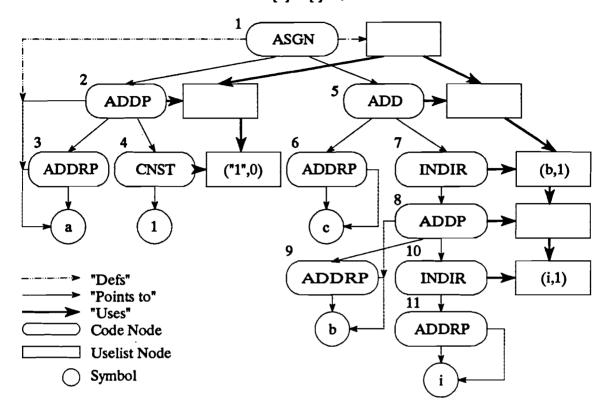

| Figure | 1 PMS500 processor architecture         2 Context switching         3 Stack frame layout of the dumb compiler | 10 |

|--------|---------------------------------------------------------------------------------------------------------------|----|

|        | 4 A code tree and its corresponding ref-def information.                                                      |    |

|        | 5 Example of a data flow graph                                                                                |    |

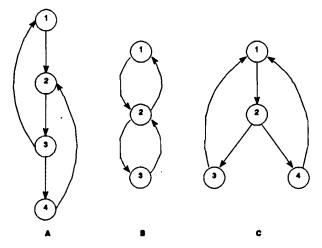

| Figure | 6 Example of complex loops                                                                                    | 35 |

| Figure | 7 The Xnode structure                                                                                         | 13 |

| Figure | 8 The Xsymbol structure                                                                                       | 4  |

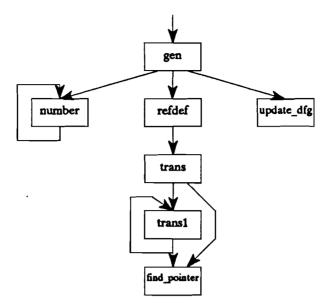

| Figure | 9 Calling tree for collecting reference-definition information and data flow graph construction               |    |

|        |                                                                                                               |    |

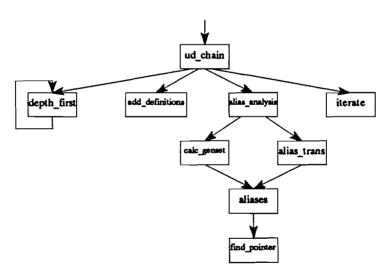

|        | 10 Calling tree for reaching definitions                                                                      |    |

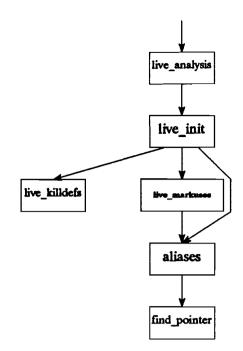

| Figure | 11 Calling tree for live analysis                                                                             | 51 |

# List of Algorithms

| Algorithm | 1 Construction of the Data Flow Graph           | 27 |

|-----------|-------------------------------------------------|----|

| Algorithm | 2 Calculating the set of aliases                | 28 |

| Algorithm | 3 Solving the general forward dataflow problems | 30 |

| Algorithm | 4 The TRANS function                            | 31 |

| Algorithm | 5 Calculating the GEN- and KILL sets            | 32 |

.

•

.

# 1 Abstract

To be able to build a complete, optimizing, C-compiler for the PMS500 microprocessor core, a project was started to gather the information and knowledge necessary to build such a compiler and to implement a base from which the compiler could be completed without too much difficulty, i.e. in just a few man-months. An investigation has been held to select a tool to simplify this task. A large number of compiler building toolkits and retargetable compilers have been examined and compared to select the most appropriate candidate. This investigation resulted in the selection of the Lcc retargetable C-compiler to be used as C-front end from which the final compiler could be developed. After thorough examination of the limitations and features of both the target processor and Lcc, a number of optimizations, promising the largest gain in the areas of code elimination and execution time minimalization, were selected. The selected optimizations include loopoptimizations (loop-invariant code detection, induction variable detection), optimizations to eliminate code (dead code elimination through copy- and constant propagation and folding, common subexpression elimination), improving register allocation and, providing they don't interfere with the previously mentioned optimizations, code substitution for faster execution (reduction in strength). The currently selected optimizations are basically target-processor independent (and are strictly speaking part of the front end), but since optimizations that have no effect on code size or execution speed of programs running on the PMS500 are left out, the choice of optimization algorithms can be said to be 'target-processor dependent'. Subsequently, preparations were made to implement these optimizations. The need for different types of data flow analysis have been investigated and methods and algorithms to implement these types of analysis have been provided to deal with the different aspects of the C-language and the Lcc toolkit. These algorithms include a number of data flow analysis types as well as algorithms to build a data flow graph or to handle the effect of pointers in C. Most algorithms have been implemented yielding a base from which most of the selected optimizations can be implemented within the timespan mentioned above. The optimizations for which it is currently possible to write an implementation include induction variable detection, detection of loop-invariant code and the resulting code hoisting, constant -propagation and -folding and dead code elimination, and sufficient information is available from data flow analysis to perform reasonable register allocation by simulated execution. Loop detection, register allocation and code selection as well as the actual implementation of the different optimizations must be done to complete the compiler.

# 2 Introduction

This is a report on a project performed at Pijnenburg micro-electronics & software b.v. in Vught, in order to acquire the degree of Master of Science from the Eindhoven University of Technology. Pijnenburg has developed a microprocessor core, the PMS500, for which a C-compiler was to be developed. Particularly, since building a complete C-compiler from scratch was recognized to be too large a task to finish in a reasonable amount of time for a graduate project, the objective was to establish a firm base, in the form of documentation and implementation, from which an optimizing C compiler could be built. The largest part of the work consist of providing a basis for optimization.

Modern compilers can be divided into two main parts, the front end and the back end. The front end embodies the source-language dependent actions, while the back end takes care of target language specifics. In most cases the back end also provides solutions for target system requirements and/or optimizations. For higher level programming language compilers, the front end accepts source language programs and translates them into a machine-independent form like intermediate code (IR) or abstract syntax trees (AST's). Subsequently, the back end takes this intermediate representation and adds the machine dependent information to generate the assembly. In most practical compilers, both intermediate code and final assembly are subject to optimization phases.

The front end itself comprises three blocks:

- The scanner, converting source code to tokens

- The parser, combining sequences of tokens to find the syntactic structure of sentences in the source language, often resulting in an AST or a preliminary IR

- The constrainer, doing semantic analysis such as storing symbols and ensuring their correct use, resulting in a decorated AST or final IR.

Machine-independent optimizations, such as common subexpression elimination and copy propagation are also considered part of the front end.

The back end comprises of the code generator and the machine dependent optimization. The code generator performs tasks like outputting the actual assembly instructions, and assigning storage space for symbols (memory or registers). Optimizing can include instruction scheduling (to take advantage of some processor's pipeline), register reallocation (to reduce memory access) or peephole optimization (replacing sequences of instructions with specialised or more suitable instruction sequences).

Existing code generators show two ways to translate the IR or AST to assembly. The first approach is to have the front end generate intermediate code for a virtual machine that resembles the target machine in architecture and instruction set. The back end then translates this intermediate code by means of a simple mapping to the target assembly. This is the simplest way to generate code but this approach usually results in inefficient assembly.

Another way to generate code is to have the front end generate an AST or some IR that is largely independent of the source- and target language or target machine. Assembly instructions are represented by short sequences of intermediate code or AST subtrees. The code generator then substitutes parts of the AST or IR with matching instructions. The generator is also able to translate sequences of IR instructions or subtrees of the AST into semantically identical sequences to match assembly instruction sequences. There are generally two ways to do this substitution:

- Using 'Attribute Grammars (AG's)': The code generator parses the IR in the same way as the front end parses the original source, using abstract grammars. Production rules in this grammar can be attributed with actions to output pieces of assembly, assign values to symbols and so on.

- With 'Tree Pattern Matching' or 'Tree rewriting': Tree pattern matchers try to cover the original AST with subtrees corresponding to assembly instructions, until an assembly instruction sequence is found covering the complete AST. Register allocation is usually delayed until a full match is found and is then done by means of a graph colouring algorithm. 'Tree rewriters' substitute subtrees of the original intermediate tree with nodes representing machine instructions, rather than match them against subtrees.

# 3 Survey of compiler generating utilities

A sensible way to build a compiler nowadays is to generate it, at least partially, automatically. Much research effort has been put into creating all kinds of compilers from standard descriptions of source- and destination languages. As a result of this, many ready-made compiler generating utilities exist. Because of the popularity of the C language, the possibility exists that some of these utilities can be used or are intended to be used specifically as C-compiler generators. The front end of the compiler, comprising scanning, lexical analysis and syntactic analysis is practically the same for every C-compiler (due to the presence of an ANSI/ISO standard for the C-language). Using existing utilities can therefore keep us from reinventing the wheel, thus saving time and hopefully providing an amount of code that has already been debugged.

A survey of existing compiler generating utilities was made to find the most suitable 'starter kit'. A query was started at the USENET 'comp.compilers' newsgroup, yielding a list of publicly available utilities. Checking references to articles using the 'Science Citation Index' did not result in any utilities besides those already known from the USENET query, but it did bring up a large number of related articles, some of which are ([6, 9]). Simultaneously Paul Jansen at Philips Eindhoven conducted a query for compiler compilers [2], also using USENET, showing that Yacc, Flex, ELI, Cocktail and PCCTS were the most frequently used compiler compilers. Retargetable compilers such as Lcc or Gcc were not included in this query, however. Finally, the Eindhoven University libraries provided interesting reading material ([14, 25]), including an earlier conducted survey on attribute grammars listing over 33 compiler compilers using attribute grammars [13].

Following the survey, some of the most promising options were tried (when available) to verify the different qualities found in the survey. Inspected utilities were ELI, Cocktail, Lcc and Gcc. ELI proved to be a large system but thoroughly documented. A C scanner/parser was included with the package. Cocktail was dropped when it became known that BEG would not be available. Lcc had the smallest size of all packages, and it was not very difficult to see that simple compilers could easily be built using the Lcc front end. Documentation of the Lcc package was limited. However, the new version of Lcc (due September 1994) would be followed by the release of a book about Lcc, expected to come out near the end of 1994. Finally, inspection of existing Gcc compilers showed them to be high quality compilers, using a large amount of resources. Documentation was present in on-line form but was not as complete as the ELI documentation. The front end- back end interface, using Gnu's Register Transfer Language (RTL) was more complex than the Lcc interface (using a tightly coupled system in which the front end and the back end make use of each other's functions), but would be more flexible to use.

To choose the best possible utility, a list of criteria was made. Every utility was checked against this list to decide to which level it was fit to be used. Appendix I shows the list of criteria. These criteria cannot, however, be used to compare utilities point-by-point because of the different nature of some utilities. There are generally three ways to generate a compiler, each resulting in a different type of utility:

- Using a compiler construction toolkit

- Using a retargetable compiler

- Writing it completely from scratch

In case of a compiler toolkit, programs to deal with reside on three levels:

- The toolkit level: the actual utilities. These programs are finished and will only have to be compiled into executables for the machine the compiler will be developed on. System requirements (memory usage, original platform the code was written for), documentation, ease of use have to be considered.

- The compiler level: the resulting compiler or the programs comprising the compiler. These programs have to be compiled into executables for the user platform, which is DOS in our case. Important factors are size of the compiler, compiling speed, debugging capabilities, ANSI conformance and the possibility to generate code for machines with varying register size.

- The target code level: These are the programs written for the PMS500 that are to be compiled by the new compiler. Code size and code speed have to be considered.

When using a retargetable compiler, two levels of code exist:

- The compiler level: Programs that comprise the compiler front end, and that implement an interface to the machine-dependent back end. The previously mentioned considerations still hold, in addition to the documentation of the interface, complexity of said interface, portability of the front end code (what platform was the original front end developed for and how much time does it take to translate it to the DOS platform?)

- The target code level.

Writing a completely new compiler means scanning, lexical-syntactic- and semantical analysis and -checking must be implemented from scratch. As this task was estimated to take up approximately three man-years of time, it was decided not to take this approach.

Appendix II lists compiler toolkits and retargetable compilers considered. Possible advantages, disadvantages and expected problems are also included.

Practical considerations influencing the decision process were cost of a package, availability, copyright restrictions and support. Looking only at the compiler tool kits, Cocktail, PQCC and ACK seemed the most promising as these where the only toolkits with a specific code generator generator. Most toolkits provided similar utilities and only differed in ease of use or completeness, with ELI being the most complete and general, and PCCTS being a very user-friendly but less sophisticated package. Toolkits mentioned in [13] range from 'simpler than PCCTS' to 'comparable with ELI or Cocktail' (including Cocktail itself), but since these toolkits were not reported to be in use and were older than the above toolkits, they where not pursued any further. Further investigation showed that the PQCC project had been abandoned some time ago and satisfying results were never reached.

From the retargetable compilers, Lcc and Gcc seemed the most promising. Lcc for it's ease of use, Gcc for its wide support and the fact that it was known to have been ported to many systems and applications. Archelon would be very well suited to our needs but the copyright restrictions and price prohibited its use. Information on ACC never arrived (Only one reference to its use was found. The information promised never arrived and as it took too much time to get other information, ACC was dropped.). CCG was not to be sold.

Considering the fact that the target processor has a fairly straightforward instruction set and (from a compiler's point of view) a relatively simple architecture (No pipeline, almost every instruction takes one clock cycle), Lcc seemed the best alternative. Compiler generating toolkits would generate front ends that would be larger and slower than the Lcc front end, and Lcc offered an easy way to generate debuggable output. Other points were the fact that ACK was quite expensive, whereas Lcc was free, and the fact that the latest version of Cocktail no longer incorporated its code generator generator (BEG). BEG was at that time in use for an Esprit project and the policy towards selling BEG was not yet clear. The author offered to speed up the decision process, but even then this would take too long so Cocktail lost its main advantage. Another problem was the fact that the C front end, which was reported as written for Cocktail, would not come with the package. This meant either writing a new C description or using a publicly available but incomplete description.

Gcc was (and still is) on of the best optimizing compilers available, and is also able to generate debuggable code. Taking the above points into consideration, the difference between Lcc's (less optimized) and GCC's code would be marginal. GCC, however, is much more difficult to retarget than Lcc, and would also result in a larger, slower compiler due to the built-in options and functionality that would never be used. However, a version of GCC ported to DOS (called DJGPP, from DJ Delorie's DOS port of GPP, the GCC compiler including C++) was initially used as development compiler to build the Lcc compiler.

# 4 Description of the target processor

This chapter is an extract of [17].

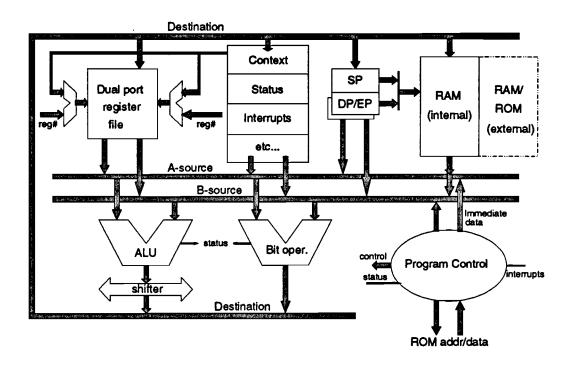

The PMS500 processor contains a 16-bit RISC processor core centered around a dual-ported windowed register file. It uses separate program and data memory spaces. The system architecture of the core is shown in figure 1. The controller is register based. Registers are divided in two groups; the general purpose working registers organised in a register file, and the device registers. Table 1 shows the available registers.

Figure 1 PMS500 processor architecture

The PMS500 is intended for integration with custom specific circuits. It can easily be extended with off-chip customized I/O and other devices, such as A/D and D/A converters, external memory controllers or parallel/serial ports using UARTs.

Program space, data space and I/O space are strictly separated. These three area's can be accessed simultanuously so execution speed is increased.

| Name                                                                                                                                                                          | Access                                                                | Description                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                               |                                                                       | General purpose registers                                                                                     |  |  |

| A0A7 R/W General purpose arithmetic registers. These registers are a subset complete register file, as selected by the current position of the slid context window (See 4.1). |                                                                       |                                                                                                               |  |  |

|                                                                                                                                                                               |                                                                       | Device registers                                                                                              |  |  |

| MODE R/W Mode and I/O register bank select.                                                                                                                                   |                                                                       |                                                                                                               |  |  |

| STAT                                                                                                                                                                          | R/W                                                                   | X/W Arithmetic condition codes.                                                                               |  |  |

| IRQE                                                                                                                                                                          | IRQE R/W Interrupt enable bits.                                       |                                                                                                               |  |  |

| IRQS                                                                                                                                                                          | RQS R Interrupt status bits. Indicates pending interrupts.            |                                                                                                               |  |  |

| CNTX                                                                                                                                                                          | R/W                                                                   | Context register. Determines which register window of the general purpose register bank is visible. (See 4.1) |  |  |

| PC                                                                                                                                                                            | R/W                                                                   | Program counter. Accessible for e.g. indirect or calculated jumps and for creating relocateable code.         |  |  |

| MULDIV R/W Intermediate register used for multiply and division steps.                                                                                                        |                                                                       |                                                                                                               |  |  |

|                                                                                                                                                                               |                                                                       | Data pointers                                                                                                 |  |  |

| SP                                                                                                                                                                            | R/W                                                                   | RAM stack pointer. Used to select a specific RAM location, and to stack PC for subroutines/IRQ's.             |  |  |

| [SP]                                                                                                                                                                          | R/W                                                                   | The RAM contents as selected by the stack pointer.                                                            |  |  |

| [SP++]                                                                                                                                                                        | R/W                                                                   |                                                                                                               |  |  |

| [SP]                                                                                                                                                                          | R/W                                                                   |                                                                                                               |  |  |

| DP                                                                                                                                                                            | R/W                                                                   | RAM stack pointer. Used to select a specific RAM location.                                                    |  |  |

| [DP]                                                                                                                                                                          | R/W                                                                   | The RAM contents as selected by the DP data pointer.                                                          |  |  |

| [DP++]                                                                                                                                                                        | R/W The data pointer can be post-incremented or                       |                                                                                                               |  |  |

| [DP]                                                                                                                                                                          | [DP] R/W pre-decremented automatically.                               |                                                                                                               |  |  |

| EP                                                                                                                                                                            | R/W                                                                   | RAM stack pointer. Used to select a specific RAM location.                                                    |  |  |

| [EP]                                                                                                                                                                          | R/W                                                                   | The RAM contents as selected by the EP data pointer.                                                          |  |  |

| [EP++]                                                                                                                                                                        | R/W                                                                   | /W The extra pointer can be post-incremented or                                                               |  |  |

| [EP]                                                                                                                                                                          | [EP] R/W pre-decremented automatically.                               |                                                                                                               |  |  |

| I/O Registers                                                                                                                                                                 |                                                                       |                                                                                                               |  |  |

| IO0IO3                                                                                                                                                                        | IO0IO3         R/W         Defined by I/O of specific implementation. |                                                                                                               |  |  |

Table 1 Available registers

.

# 4.1 The CONTEXT switching scheme

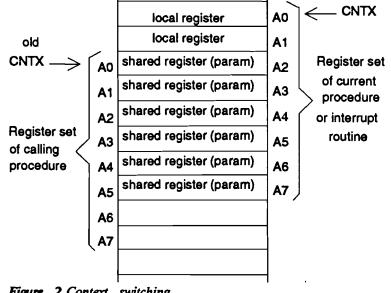

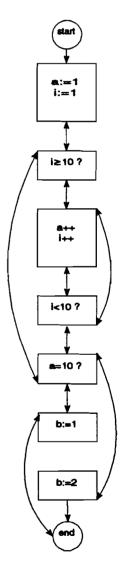

The general purpose registers are treated as a window on some sort of stack, the base address of which is contained in the CNTX register. The context space contains a total of 64 registers, of which 8 can be accessed directly. One of the intended usages of this register file by the designers was as follows: Each routine can reserve its own local register set by decrementing the number of words it needs. Any general register above the created local ones is shared with its thus calling routine. enabling parameter passing between them (see figure 2).

Figure 2 Context switching

The processor automatically generates an interrupt (number 4) when CNTX becomes less than 0 (overflow) or if it reaches value 57 or higher (underflow). For a more specific description of the register file and the interrupt routines, the reader is referred to [17].

# 4.2 The SP, DP and EP pointers

The stack pointer SP, data pointer DP and extra pointer EP are the only ways in which data in the data space RAM and program space ROM can be accessed. The addressing scheme provides indexed and auto in/decrement modes for all pointers. The SP is used as hardware stack for pushing the program counter PC and STAT register, when a subroutine or interrupt is activated.

Depending on the actual external RAM, only one read or write access may be done in a single instruction. This means read/modify/write instructions such as add (ADD [SP], #1) and bit set are not allowed for this type of RAM. Due to the single RAM address bus, instructions like MOV [DP++], [EP++] are never allowed. The internal RAM does allow a single cycle read/modify/write operation on a single location.

## 4.3 The status register

The status register reflects the status from the last arithmetic/logic instruction. MOVes and control flow instructions do not alter the status register bits. The status register is automatically saved when entering an interrupt routine and stored on return from interrupt. When STAT is used as destination register, the actual value written is the result of the ALU operation, not the value of the flags.

# 4.4 The mode register and I/O

In the PMS500 instruction encoding, 4 I/O addresses are direct accessible. The MODE register is intended as a 'bank' register for the I/O address space. By (externally) implementing this mode register, extra address bits can be added to extend the I/O address range.

# 4.5 IRQ registers and Interrupts

The PMS500 has 7 interrupt inputs: IRQ0..IRQ3 and IRQ6 are external interrupts. IRQ4 is activated when the CNTX space overflows or underflows. IRQ5 is reserved for a built-in trace mode, which enables single

step execution for easy debugging.

Two registers control the IRQ response of the PMS500:

- The IRQS (status) register shows a status bit for all currently active interrupts. Up to five external events may cause interruption. Only bit 0..6 are used, bit 7 is always cleared. Bit 5 (trace interrupt) is always set.

- The IRQE (enable) register contains individual interrupt enable bits for each interrupt. Clearing these bits disables the corresponding interrupts. Only bit 0..6 are used, bit 7 is always cleared.

Once an interrupt is detected, the processor will:

- stack the status register on [--SP]

- stack the program counter on [--SP], i.e. stack the address of the instruction to be executed after RETI.

- adjust the status register to reflect the current interrupt level, thereby disabling all interrupts of the same or lower priority

- decrement CNTX by 2 (freeing 2 local registers)

- jump to an address, specified by the interrupt number.

Return from interrupt is as follows:

- increment CNTX by 2

- restore PC from [SP++]

- restore status from [SP++]

- enable interrupts of same or lower priority

# 4.6 The PC register

Data can be moved into the Program Counter to enable calculated jumps (via the JMP <reg> instruction or other instructions using the PC as destination) or to use jump tables located in ROM (via the JMPC instruction). Using PC as an explicit destination (as in ADD PC, #1) will take one extra instruction cycle.

## 4.7 The PMS500 instruction set

The PMS500 instruction set contains three mayor instruction groups:

- Control flow instructions

- Data transfer instructions

- Arithmetic/Logic instructions.

Appendix V list the instruction set. Note the following points:

- An assembler is present that selects the appropriate MOV combination when moving immediate data into a register (i.e. the data5 or data8 and possibly an extra move to HIGH)

- Instructions for moving to and from ROM take extra cycles, and writing to ROM takes extra (external) hardware

- Pushing the stack pointer on stack will first decrement SP and then push the decremented value

- Arithmetic and logic instructions operating on immediate data can include only 5 bits of data. However the assembler can generate code to take into account larger data constants.

- Multiply- and divide instructions perform only part of the calculation. A full multiplication (or division) takes 16 steps to complete (see [17] for a full explanation).

# 5 Building a dumb compiler with Lcc

To get acquainted with the Lcc package and code generation interface, a dumb compiler was built. No assumptions were made with respect to the way in which 'good' code could be generated or what 'good code' should look like. This approach was chosen to gain a better insight in Lcc's code generation interface and the assumptions Lcc makes about the target processor. The design of the real compiler would be based on information found during this recognition phase, thus making it less likely that design decisions would collide with Lcc's assumptions or requirements in a later stage. A better understanding of the code generation interface would also make it easier to take advantage of Lcc's features to simplify 'good' code generation.

## 5.1 A brief description of the Lcc code generation interface

For better understanding of the following chapters, a brief description of the Lcc code generation interface is added. For a full description, the reader is referred to [1].

The Lcc front end and back end are closely coupled. This means that the front end calls functions from the back end, and vice versa. Both ends share two datastructures: the symbol table and the directed acyclic graph nodes (DAG nodes). The symbol table stores information on name and place of variables, constants and labels. DAG nodes store information on the program flow and program semantics.

The front end provides the following information using the symbol table entries:

- The front end's name for the symbol

- Scope level of the symbol (Global, local, label, constant etc.)

- Storage class of the symbol (Static, register, auto etc.)

- Its type

- In case of a constant symbol, its value or location

- In case of a label, its number

- Additional information, such as whether the symbol is defined, generated, or addressed, or if it's a temporary or a structure parameter.

The back end can annotate these symbol table entries to its own liking with information such as offset from stack, heap address or back end name.

The dag nodes provide the following information:

- The Lcc-opcode for this node (appendix IV lists all available opcodes)

- Number of references to this node's result

- Links to symbols used by this node and/or the kids of this node (nodes that compute values needed by this node's computation)

The back end can annotate these nodes with information like register number or symbol to store the result of the node's computation, or the back end can do the first optimization phase on the DAG. The front end passes DAGs in execution order, sometimes bundling various DAGs in case they share common subexpressions, and forests containing DAGs to set up and execute jump- and switch statements.

The front end manages four logical segments being the code segment, the bss segment (uninitialized variables), the data segments (initialized variables) and the lit segment, containing constants. Code- and literal segments can be mapped onto read-only memory, data and bss segments must be mapped on readand writable memory. These segments can be declared to the back end in random order, so it may be possible that references to (for instance) labels in a segment occur before they have actually been declared.

When compiling a source program, the front end first announces global symbols and symbols to be exported or imported, such as function names and externally defined variables. The front end will switch to the appropriate segment before announcing symbols belonging to that particular segment. If no global symbols are announced in one segment this segment may be declared after the code segment.

Generating program code is done in the following way:

The front end first completely consumes a function before calling the back end. The back end then gets the opportunity to initialize the annotation phase. Control is then returned to the front end that in its turn repeatedly calls the back end for every DAG forest in the function, so the back end can annotate the DAG. After that, the front end returns control to the back end to initialize the code generating phase. Control is passed back again to the front end that passes the annotated forests in sequence to the back end to emit the final code. Finally, the back end may round up the code generation phase and the front end continues to read the next function from the source file.

# 5.2 Description of the dumb compiler

#### 5.2.1 Assumptions

Because the sole purpose of building the compiler was to determine Lcc's assumptions, features and shortcomings, the following (simplifying) assumptions were made:

- No effort was put into correct representation of different variable types. The front end provides ample opportunity to correctly implement this functionality as can be seen from the table in appendix IV For the dumb compiler, it is assumed that the value of a basic variable type fits into one PMS500 word.

- No effort was put into dynamic memory allocation. Locals and function parameters reside on the stack, which is assumed to be infinitely large. Globals and statics are assumed to be initialized by a (nonexistent) linker.

- Possible optimization of the DAGs was not investigated.

- A0, A1 and A2 are reserved for use by the compiler to pass function return values and copy blocks to stack (A0), hold the base address of the current stack frame (A1) or to hold the address of temporaries to which register values are spilled (A2).

- To free registers at function entry, 8 is added to CNTX. CNTX is restored at function exit. The register file is also assumed to be infinite.

- Certain functions (multiply, divide and modulus) that take a sequence of assembly instructions are not expanded.

- Functions returning structures are not supported

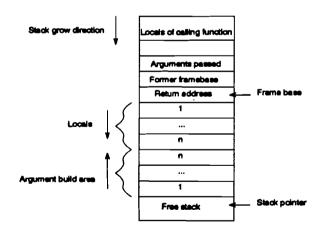

Figure 3 shows the layout of the stack frame used. During the first code generation phase, maximum local offset and maximum argument offset are calculated. At function entry, the stack pointer is decreased according to the sum of these values to declare the necessary stack space. This approach enables the use of the PUSH and POP commands without having to keep track of the location of locals or arguments relative to the stack pointer.

Register allocation was taken from the example VAX code generator that came with Lcc. Only small changes were necessary to make it suitable for the PMS500 code generator. Registers are allocated on the fly, and the register allocation algorithm does not keep track of values of symbols already present in a register; All symbols are fetched from memory the moment their values are needed, except values used more than

Figure 3 Stack frame layout of the dumb compiler

once per DAG forest. Register variables are not supported by the register allocator.

#### 5.2.2 Problems, possible solutions and useful information provided by Lcc

Problems or possible problems were encountered in the following area's:

#### Segment management:

Lcc manages four logical segments, including a read only and a read/write data segment. String literals, for instance, might be declared inside the read-only segment. It cannot, however, be computed at compile time whether a pointer dereference accesses read only or read/write space. String literals can therefore not be mapped onto PMS500 codespace since the compiler is unable to determine if it should use the MOV or the MOVC instruction. Besides that, Lcc generates the code to initialize variables inside the data- and literal segments. Strictly speaking this means that this is code that will not be executed by the PMS500 processor but should be interpreted by the PMS500 assembler and linker. One or both modules should therefore be able to initialize memory for the compiler, for example by generating initialization routines in the startup code. If the compiled program is to be able to initialize all variables by itself, then the linker should first call the module's initialization routines before calling 'main'.

#### Register allocation:

Because the front end passes the DAGs to the back end in execution order and at most one forest at a time, it is difficult to allocate registers on a more global level. If this is to be implemented, extra information containing symbol lifetime and storage location must be added during the first phase of code generation. This information can be used to choose which variables should be allocated to registers rather than to memory. It will also be necessary to combine forests into basic blocks and basic blocks with each other in the back end to get a complete view of variable lifetime and usage. Chapter 8.3 explains the concept of basic blocks.

#### Instruction layout:

Lcc assumes for arithmetic instructions the presence of three operands for diadic, and two operands for monadic instructions. An ADD instruction, for instance, adds the values of two registers and stores the result in a third, whereas the PMS500 ADD instruction adds the values of two registers and stores the result in one of the original registers. It might therefore take one extra cycle for the PMS500 processor to move the value of one of the original registers into the third, assigned by the front end, for every arithmetic instruction.

Overhead caused by calculating the address of locals and arguments:

The dumb code generator has to calculate the address of locals and arguments every time the value of such a variable is used. This results in nearly 20% of the generated code consisting of address calculations. This is partly a result of the choice to store every local variable or argument on stack and the percentage might be lowered by choosing another storage method. However, the addition of an instruction to calculate this address in one instruction could achieve an easy gain in speed and code size. To find out if such an instruction would indeed cause a fundamental improvement in code size and execution time, a small investigation was held (chapter 6).

Lcc provides information on the number of times the result of a node is used after it has been calculated, and whether its address is taken. This is useful when deciding if a symbol can be assigned to a register rather than to a memory location. A relation between the symbol (in the symbol table) and the node (in a DAG forest) has to be calculated and stored for this purpose.

#### 5.2.3 Possible optimizations

Building the dumb compiler, several points were found on which the generated code could be improved without too much trouble. At this point, optimization means those transformations on the assembly code that result in less and/or faster executing code. Lcc does some local optimizations such as constant folding and eliminating conditional jumps with a constant condition. The code that cannot be reached via these eliminated jumps is still generated, though.

Optimizations than can easily be implemented:

- Every node for which the value can be calculated at compile time need not be emitted but can be substituted directly wherever the value is used (this equals tree pattern matching, in which subtrees of the AST are matched against subtrees representing instructions). This goes for:

- Addresses of labels,

- Constant values or expressions,

- Offsets to locals and arguments.

- Keeping track of values in registers, value lifetime and distance to next use can aid in:

- Assigning frequently used symbols to registers,

- Minimizing references to memory,

- Generating better spill code.

Optimizations that will need a more fundamental change in approach:

- Building and linking of basic blocks. This will make it possible to:

- Allocate registers globally,

- Eliminate dead code,

- and perform many other types of global optimizations.

- Changing the way locals and arguments are stored and passed. This could mean, for instance, that addresses of symbols no longer have to be calculated as an offset from stack but can be accessed directly in memory. To enable this approach, dynamic memory allocation has to be provided by the startup code or host operating system (if available), or a protocol has to be invented so the compiler can allocate memory by itself. Argument passing could make use of the context register file that could speed up the process, but would introduce the problem of reindexing all registers in use.

- Loop optimizations, such as invariant code movement, can be implemented.

#### 5.2.4 Summary

Lcc does not make assumptions about the type of processor it will generate assembly for, nor about the kind of environment in which it will run, that provide any real problems concerning the PMS500 processor. The way in which symbols are declared implicitly assumes the presence of an assembler, for instance because the generation of code for variable initialization is left to the assembler. Since the existing PMS500 assembler did not recognize multiple data segments, a solution had to be found to initialize data in other than the code segment. But the PMS500, being an embedded processor, allowes for multiple types of external ram, so the use of segments or other ways to discriminate between these memory areas had to be added to the assembler. If these different types of external memory are to be discriminated by means of different assembly instructions, however, then the properties of the C-language make it impossible to effectively use these different kinds of memory. Discrimination between segments using different address ranges in the same numbering space, can be supported by the compiler (to the extend of the four segments managed by Lcc), but the assembler must make sure that labels declared in one of the segments indeed refer to addresses inside the correct address range. All address ranges must then be accessible through one machine instruction (instead of using either MOV or MOVC)

Various types of code improvements can be added without fundamentally changing the structure of the dumb compiler but to be able to add global optimizations, the DAG forests Lcc sends to the back end have to be rejoined, meaning that some of the work done by Lcc has to be undone.

# 6 Investigation for useful additions to the PMS500 instruction set

To be able to make suggestions about extensions to the PMS500 instruction set, a small investigation was held to determine the effect of some extensions on code size and program execution time. Investigated additions were the possibility to add a constant to a register before moving its value into another register (like MOV A0, A1+3), and to access the value of a memory location addressed by an address pointer plus a constant offset (such as MOV A0, [DP+2], which moves the value at the memory address designated by DP added with two into A0). These instructions were considered because it is inevitable that a C compiler uses offsets from a known address to designate local variables; the addresses of these locals have to be calculated at run time while the compiler needs to have a scheme to designate these locals as well (compile time). Optimization can focus on minimizing these address calculations, but since values have to be assigned to variables at ANSI C's agreement points, a substantial amount of code will be dedicated to calculating the addresses of locals. (Agreement points are points in the source code at which the values of variables as stored in the real machine have to be identical to the values of variables as if the code was run on the abstract machine defined by ANSI C).

| Source module | # of lines | # of usages | % of usage |

|---------------|------------|-------------|------------|

| dag           | 10,127     | 1,243       | 12.27%     |

| decl          | 15,159     | 1,761       | 11.62%     |

| enode         | 8,915      | 1,246       | 13.98%     |

| error         | 1,054      | 112         | 10.63%     |

| expr          | 16,735     | 2,040       | 12.19%     |

| init          | 6,267      | 792         | 12.64%     |

| input         | 1,239      | 46          | 3.71%      |

| lex           | 7,477      | 402         | 5.38%      |

| main          | 928        | 85          | 9.16%      |

| output        | 1,494      | 132         | 8.84%      |

| profio        | 2,917      | 344         | 11.79%     |

| simp          | 13,883     | 1,850       | 13.33%     |

| stmt          | 9,033      | 1,129       | 12.50%     |

| string        | 1,668      | 138         | 8.27%      |

| sym           | 3,634      | 404         | 11.12%     |

| tree          | 3,347      | 359         | 10.73%     |

| types         | 11,536     | 1,431       | 12.40%     |

Table 2 Usage statistics of MOV Ax, Ay+c instruction

To gain insight in the amount of space and time the addition of one of the above instructions would save. the dumb compiler was modified to assume the presence of a type MOV A0, A1+x instruction. The number of times the instruction was used was counted and compared to the total number of code lines in the module. Table 2 shows the results for the modules comprising the Lcc front end. On the average, 10% of the code consist of this new instruction. This means that program code will larger without be 10% this instruction as it expands to a MOV and an ADD instruction in the current instruction set. Execution time will increase by about 10%, as the effect of loading the HIGH register when dealing with large constants has to be taken into account.

Checking the usage of the MOV AO, [DP+x]-type instruction was not possible in this way due to the structure of the dumb compiler. A similar usage count was performed on code for the INTEL 386 processor, that possesses this instruction type. This showed that an

average of 20% of the code consisted of indirections on a register value plus an offset, for the same set of modules. The modules were compiled both optimized and non-optimized. This can be seen as an indication that if the processor provides the instruction, it will be used a lot. It does not indicate, however, the gain in code size or execution time compared to code lacking this instruction type, although every time a local variable has to be referenced, this instruction can save up to two 'ordinary' instructions.

Considerations whether these types of instructions belong in the instruction set of a RISC processor or if these instructions impose problems on the processor design (data path length etc.) were left to the designers of the processor (of course). It is not possible to form a reliable conclusion based on the results acquired by using the dumb compiler and an Intel 386 compiler, besides the fact that the extension would be easy to have in the eyes of a compiler writer. It may well be possible that a compiler designed to minimize these types of calculations could do perfectly well without the extra instructions. Further investigation into this subject was not considered to be an objective for this project and the investigation was abandoned.

#### 7 Structure of the final compiler

Based on the information gathered while building the dumb compiler, a number of decisions were made concerning the implementation of the real compiler. These decisions affect the function call interface, register usage and allocation, stack frame layout and memory usage. Below is the list of points the compiler will have to conform to:

- The compiler assumes library functions or assembler macro's for the following actions:

- Multiply, divide and modulus. These operations take a large number of instructions to implement, and inline expansion is not always desirable.

- Dynamic memory allocation. This was not primarily found to be a compiler problem and leaving this functionality to library routines enables multiple allocation schemes for different memory types. The decision to use stack as dynamic storage however makes this assumption redundant.

- Floating point operations. These functions also take more than one PMS500 instruction to be implemented. It also enables the programmer to choose different floating point libraries (if provided).

- Shift and rotate over multiple bits. As the PMS500 isn't equipped with a barrel shifter, these functions also take a number of instructions to implement.

- The compiler will calculate an upper bound for relative jump distances and decide accordingly which jump construct will be used. Peephole optimization can then be used to collapse long jumps to relative jumps if possible. Calculating this upper bound is an easier task for the compiler than for the assembler.

- The compiler will not recognize different memory types the user might add to the PMS500 core besides the code- and data memory. This effectively means that all datapointers used by the compiler are assumed to address the dataspace in which the stack resides (or to which SP points). DP will be used as framepointer (see below), EP will be used for block copy/move instructions.

- DP will be used as framepointer. Addresses of locals and argument will be calculated this way:

- ADD DP, offset

- MOV Ax, [DP] SUB DP, offset

This approach enables merging of successive SUB- and ADD instructions when calculating multiple addresses and keeps the general purpose registers free for other uses.

- The context-stack will not be used by the compiler. CNTX is reserved for use by interrupt routines. This leaves eight available registers: A0-A7.

- Locals and arguments will be allocated on the stack. Globals and static variables will be declared to the assembler which will concern itself with the actual storage allocation.

- The callee (in stead of the caller) saves and restores the registers it uses; it also saves and restores the caller's framepointer. This choice enables assembly writers to interface with the compiler-generated code and save/restore only the necessary number of registers.

- A stack frame will be similar to the stack frame used by the dumb compiler, with the exception of the argument build area. The dumb compiler reserved enough stack space at function entry to be able to handle all function calls from this function, which means declaring enough stack space to handle the function with the largest number of arguments. The real compiler will push arguments on stack and pop them again at function exit, thus making more efficient use of stack space.

- The caller removes arguments from stack. In case of library functions with a variable list of arguments, the callee doesn't even know how much of the stack should be freed.

- ANSI dictates the following lower bounds for type sizes (in bits): CHAR: 8; INT: 16; LONG: 32; FLOAT: 32. Lcc assumes INT and LONG types of equal length. This would mean that INT = LONG = 32 bits, even for the 16 bit PMS500. This poses a serious problem. Separating INT's and LONG's, aliasing LONG's and DOUBLE's or replacing SHORT's for LONG's will take a considerable amount of redesign of the Lcc front end. For now, INT=LONG=16 bits is assumed for the 16 bit PMS, invalidating the compiler as ANSI conforming. The 32-bits PMS500 compiler can safely assume INT=LONG=32 bits.

- Registers will be allocated with 'Function scope'. Allocation schemes will be investigated starting with graph colouring.

- The compiler will perform global (function level) optimization, optimizing primarily for program size.

Most decisions only affect the last steps of the code generation process, when the code is actually emitted.

Register allocation and global optimization, however, induce a number of analysis steps preliminary to the emitting stage. Both register allocation and optimization require data flow analysis to decide which values to store in registers, which variables can be substituted by constants and so forth. The compiler back end will therefore perform the following operations:

- Data flow graph construction. Necessary to perform data flow analysis.

- Data flow analysis.

- Global (function level) and local (basic block level) optimization using the results of data flow analysis.

- Global register allocation.

- Code selection and emitting.

- Peephole optimization.

To some extent, local optimizations such as strength reduction and common subexpression elimination are performed by the front end (always concerning a few code-trees at a time but not complete basic blocks) but might be extended to cover complete basic blocks or even functions. The compiler parts will be constructed in the following order: first data flow graph construction and data flow analysis, because this step is obligatory for both register allocation and optimization. At that point a number of optimizations should be investigated for implementation cost, computation cost and optimizing effect. After the desired optimizations have been chosen, the methods for implementing these optimization have to be put on paper to make it possible for other programmers to implement the desired algorithms. Subsequently the register allocation algorithm will be chosen and implemented. Finally the emitting stage of the compiler will be constructed. This completes the first version of the compiler and marks the first point in time on which correct machine code can be generated by the compiler. It is at that point possible to add local, global and peephole optimization to the compiler.

## 7.1 Possible optimizations

[18, 5, 12, 14, 15, 23 and 25] list a number of optimizations and data flow analysis techniques to aid in optimization that can be performed during or after code generation. These optimizations generally aim to reduce the amount of machine code produced by the compiler and at the same time minimize the execution time of the produced program. Often these aims interfere with each other. Most of the optimizing techniques only work or work best if the data flow graph of the program is reducible (See [7] for information on reducible flow graphs). It is easily seen, however, that data flow graphs derived from C programs need not be reducible per se, so a number of techniques cannot be implemented or will have greater complexity when implemented for a C compiler. The following paragraphs list the optimizations that are considered useful for the PMS500 compiler and are therefore candidates for implementation.

Because the PMS500 was intended to be used as a processor core that could easily be embedded in specific applications, and the amount of memory in these systems is generally fairly small, it was decided that optimization of program size would prevail over minimizing the execution time of target programs. Based on this decision, the most important optimization techniques are:

- Loop optimizations

- Code elimination

- Code substitution

Other optimizations such as instruction scheduling or code selection using tree rewriting yield a relatively low optimizing performance because the PMS500 has no visible pipeline, executes every instruction in one clock cycle (apart from a few instructions that need the HIGH register such as load immediate with large constants) and has a fairly orthogonal instruction set (i.e. functionality of instructions doesn't overlap making it unlikely that a sequence of instructions can be substituted for one, more complex, instruction).

Local optimizations affect only basic blocks. Even when Lcc performs a number of optimizations on code trees, local optimization can find a number of optimizations that can be performed parallel to global optimization, such as (local) common subexpression elimination, strength reduction or copy propagations. Local optimizations are easier to perform since it is not necessary to do data flow analysis.

Loop optimization algorithms try to reduce the number of instructions contained in the body of the loop, or the number of times the loop body is executed. Since most programs spent 90% of their execution time inside loops, these optimizations provide a large gain in execution time minimalization while at the same time decreasing the program size (excluding the loop unrolling algorithm).

Code that will never be executed (dead code) can be eliminated and calculations occurring more than once and yielding the same result (common subexpressions) can be substituted with a temporary so the expression needs to be evaluated only once, its result can be used many times and every other occurrence of the subexpression can be eliminated. These optimization techniques can be used to reduce the size of the target program and, to a lesser amount, decrease the execution time of the program.

# 7.2 Data flow analysis

Most optimization problems require data flow analysis, so let us first, for a better understanding, establish what data flow analysis means. The different types of data flow analysis must also be identified. [18] defines data flow analysis as "the transmission of useful relationships from all parts of the program to the places where the information can be of use". These 'useful relationships' include relations between the occurrence and the usage of a variable definition or the availability of (sub)expressions at any point in the program.

Data flow analysis can be done in two directions. Forward data flow analysis takes information from certain points in the program and tries to propagate the information through the program to points were it might be used. Backward analysis does the exact opposite; it recognizes points that use some kind of information and tries to trace points in the program where the information might have been generated. The information propagation for both types of analysis can be done based on confluence or divergence. For instance, analysis based on confluence initially assumes that nothing is valid, but if, at some point in the program, the possibility exists that information may become valid, it is propagated until it is absolutely sure it becomes invalid. Analysis based on divergence initially assumes that anything is valid but if at some point in the program the chance exists that the information might become invalid, propagation of this information beyond that point is stopped and is only started again if it is absolutely sure the information becomes valid again.

An example of forward flow analysis based on confluence is the analysis of 'reaching definitions'. The aim of this analysis is to establish which definitions of variables reach uses of certain variables (e.g. in the expression x-a+b, x is defined and a and b are used). This type of analysis is can be used to decide wether a used variable can be substituted for a constant value (constant propagation). Such a substitution can only be made if it is absolutely sure the variable can only have one particular value at that point in the program. So if there exist different paths from the start of the program to the point in question, and each path contains a different definition of the variable, the variable cannot be substituted. If no definitions occur on both paths, the variable can also not be substituted (note that this generally means a programming error). So it is clear that the initial condition is 'no variable is defined', and every point y in the program that might define a variable x adds a 'x is defined at y' to the information heap. Only if it is absolutely certain that a variable is defined at some point, all other definitions of the same variable prior to this point are removed from the heap.

# 7.3 Loop optimization

As stated, loop optimizations provide an easy way to speed up the program with relatively little effort. To be able to perform loop optimizations, the following information has to be gathered from the source program:

- The Data Flow Graph (DFG) of the program has to be constructed. (See chapter 8.3 for more information on DFG's)

- Loops in the DFG must be discovered. A loop is a collection of nodes that are connected in such a way that from every node in the loop, walking the connections, any other node (including itself) can be reached. To make optimization possible, a loop must also have one entry node, the only node through

which any node inside the loop can be reached from outside the loop.

• The flow of information through the program must be analysed. (Data Flow Analysis or DFA). DFA makes it possible to detect computations that yield the same result every time the body of the loop is executed, regardless of the conditions changed by multiple execution of the loop body. These computations can be moved out of the loop. It can also provide information about the number of times a loop will be executed.

Detecting loop invariant expressions makes use of usage-definition information, derived from the 'reaching definitions' information described in the previous chapter, and can be implemented using an algorithm that iterates over the loop. Detection of loops can be done using an iterative algorithm for data flow graphs in general and using depth-first ordering or dominance relations if the flow graph is reducible. In C, however, the possibility exists that flow graphs are not reducible.

Loops provide a number of sources for optimizations. Summarizing the possibilities, we have (from [18, 14] and [25]):