### MASTER

The design of a microprocessor with an object oriented architecture

van Hamersveld, F.P.

Award date: 1992

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

The Design of a Microprocessor with an **Object Oriented Architecture**

ED 367 5494

F.P. van Hamersveld

Faculty of Electrical Engineering Digital Systems Group Eindhoven University of Technology

Eindhoven, february 1992

Supervisor: Prof. Ir. M.P.J. Stevens Coach: Ir. A.C. Verschueren

٠

The Department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of student project- and graduation reports.

#### Abstract

# <u>Abstract</u>

Object oriented programming is being used more often. A disadvantage however is that the implementation of such languages is far more complex than procedure oriented languages. If a system can be build that supports object oriented languages, then it will become even more powerful. Therefore a microprocessor will be designed with an object oriented architecture.

A frequently used object oriented language is Smalltalk-80. This language compiles its source code to bytecodes, that are executed by the interpreter.

In the literature a microprocessor is described that supports object oriented programming. This processor, called the Rekursiv, can be programmed to run Smalltalk. Hereto the Smalltalk-interpreter is implemented in microcode.

The Rekursiv consists of three processes. The Logik contains the sequencer for the microprogram and the stack addressing unit. The Numerik contains the data manipulator (32-bit alu, barrel shifter and multiplier). The Objekt contains the object oriented memory management unit.

The Rekursiv can be improved when a few mechanisms are implemented in hardware. Instead of an on-line garbage collection routine in the microprogram, a parallel garbage collector in hardware should be used. Furthermore the dynamic binding mechanism should be implemented in hardware.

To design a comparable microprocessor, the micro-instructions have to be defined, together with the hardware that implements them. Hereto a model is defined, using the modelling tool Promod. When this model is satisfactory, an architectural model can be set up using the design and simulation tool IDaSS.

The author of this master's thesis had the assignment to design a microprocessor with an object oriented architecture. Until now, the model Objekt and the model of the garbage collection have been defined. The garbage collector uses a generation scavenging algorithm that is adjusted to run in parallel with the main processor.

Due to the fact that Promod is not ideally suited to define a hardware model, there are a few errors in the Promod report that gives the model.

Before the hardware can be designed, the entire model of the processor, including the Logik, Numerik, and dynamic binding mechanism, has to be defined.

# **Contents**

| Contents |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| 1.       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                        |  |  |

| 2.       | 2.1. Some Terminology         2.1.1. Objects                                                                                                                                                                                                                                                                                                                                                                                                      | 4<br>4<br>4<br>5<br>5                                    |  |  |

| 3.       | The Smalltalk-80 Virtual Machine         3.1. The Syntax of Messages in Smalltalk-80         3.2. An overview of the virtual machine         3.2.1. The compiler         3.2.2. The interpreter                                                                                                                                                                                                                                                   | 7<br>7<br>8<br>8<br>8<br>9                               |  |  |

| 4.       | 4.1. The Principles behind Rekursiv       1         4.1.1. Object Representation       1         4.1.2. Persistent Storage       1         4.1.3. Object Swapping       1         4.1.4. Access Checking       1         4.1.5. High-Level Instructions       1         4.2.1 The Object Oriented Memory Management Unit (Objekt)       1         4.2.2. The Microsequencer (Logik)       1         4.2.3. The Data Manipulator (Numerik)       1 | 11<br>12<br>12<br>12<br>13<br>13<br>15<br>17<br>18       |  |  |

| 5.       | 5.1. Garbage Collection       2         5.2. The Disk Processor       2         5.3. Dynamic Binding       2                                                                                                                                                                                                                                                                                                                                      | 20<br>21<br>21<br>22<br>22                               |  |  |

| 6.       | 6.1. Garbage Collection Algorithms       2         6.1.1. Reference Counting       2         6.1.2. Mark and Sweep       2         6.1.3. Baker's Semispace Algorithm       2         6.1.4. Generation Garbage Collection       2         6.1.5. Generation Scavenging       2         6.1.6. The choice of an algorithm       2         6.2. Parallel Generation Scavenging       2         6.2.1. Memory Usage       2                         | 23<br>24<br>25<br>25<br>25<br>26<br>27<br>28<br>28<br>29 |  |  |

| 6.2.3. Protection of Shared Resources                         | 30 |  |  |  |

|---------------------------------------------------------------|----|--|--|--|

| 6.2.4. The First Solution                                     | 31 |  |  |  |

| 6.2.5. The Second Solution                                    | 31 |  |  |  |

| 6.3. The Implementation of Generation Scavenging              | 32 |  |  |  |

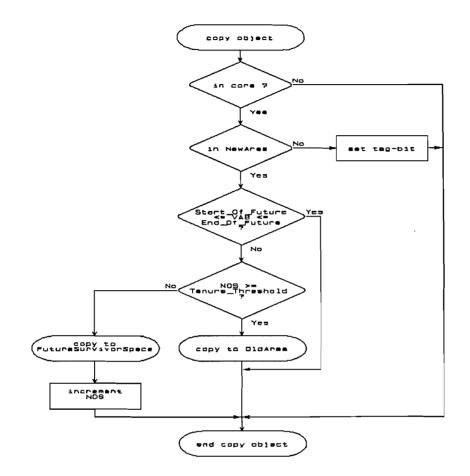

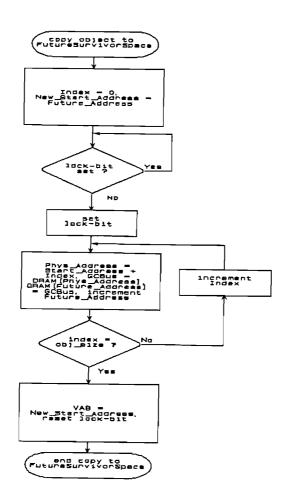

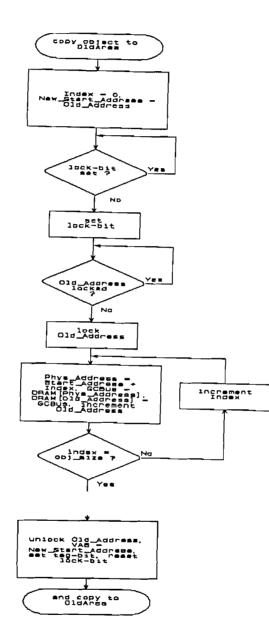

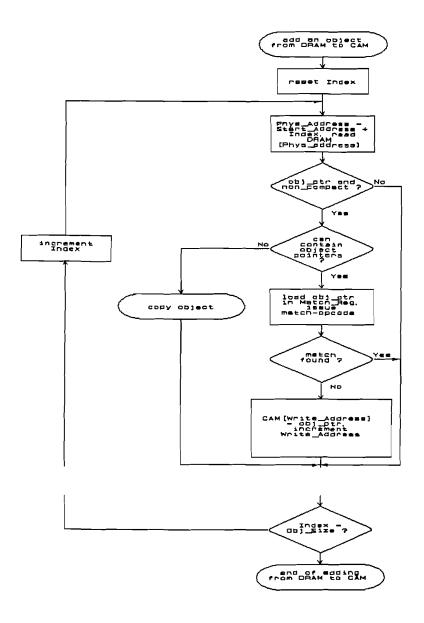

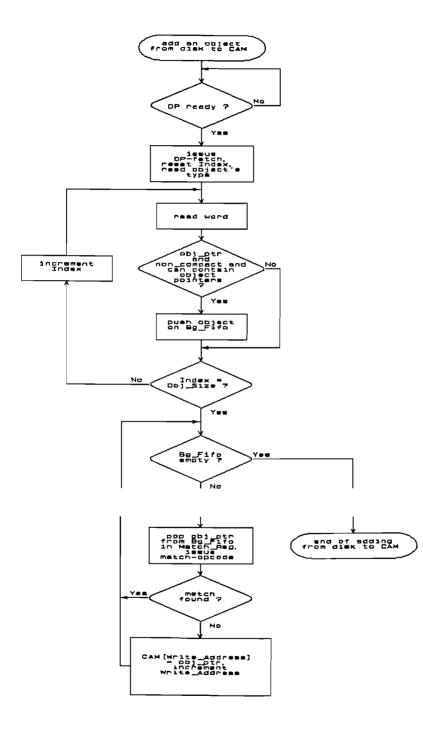

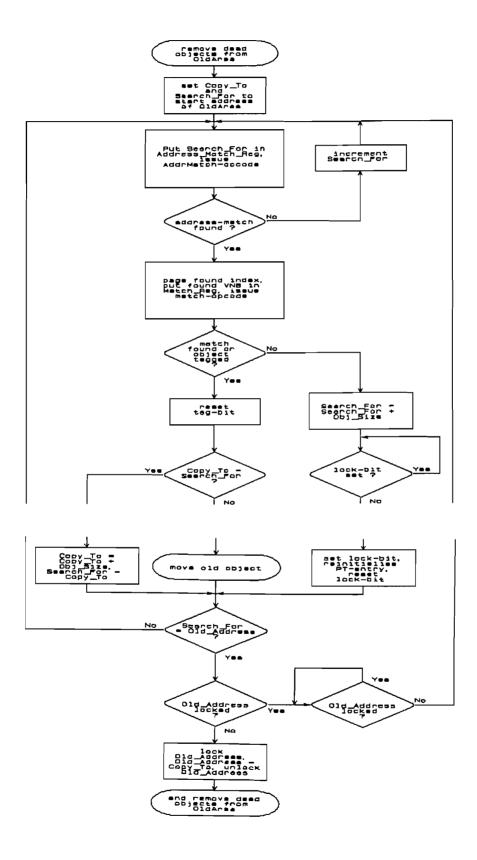

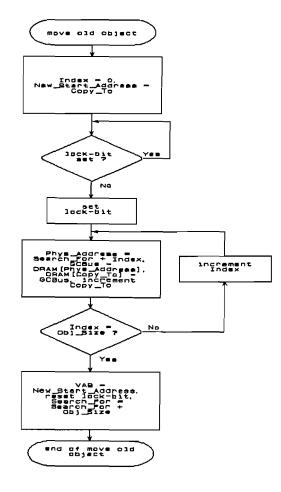

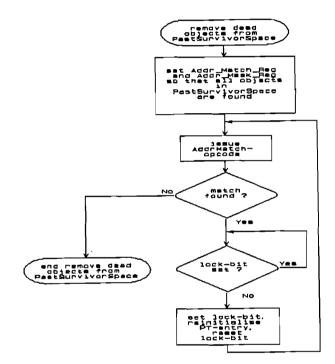

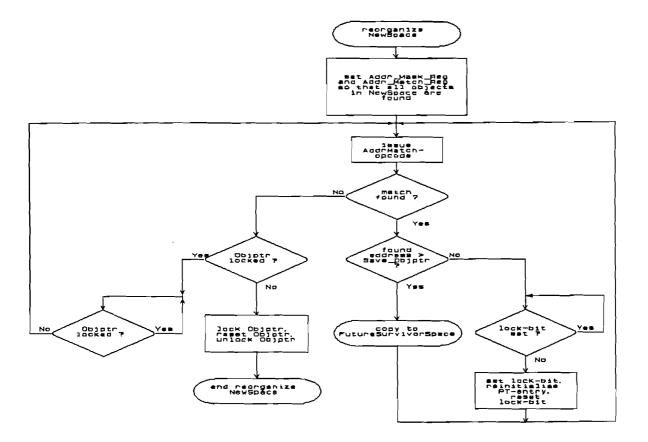

| 6.3.1. The Flowcharts                                         | 33 |  |  |  |

| 6.3.2. The Instruction Set                                    | 35 |  |  |  |

| 7. The Model of the Microprocessor                            | 40 |  |  |  |

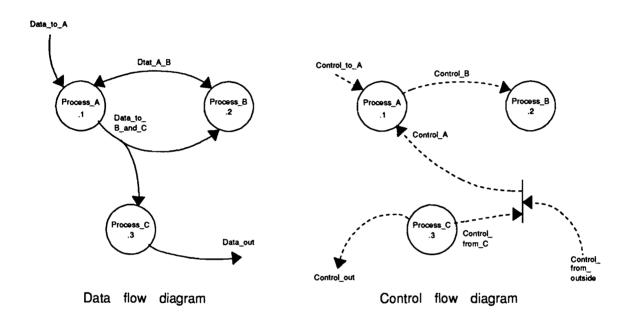

| 7.1. Structured Analysis According to Hatley and Pirbhai      | 40 |  |  |  |

| 7.2. The Model of the Processor                               | 42 |  |  |  |

| 7.2.1. The Context Diagram                                    | 42 |  |  |  |

| 7.2.2. The Processor                                          | 43 |  |  |  |

| 7.3. The Objekt                                               | 44 |  |  |  |

| 7.3.1. The Address Generation and Range Checking Process      | 45 |  |  |  |

| 7.3.2. The Pager                                              | 48 |  |  |  |

| 7.4. The GC                                                   | 50 |  |  |  |

| 7.4.1. The PT_and_DRAM Process                                | 51 |  |  |  |

| 7.4.2. CAM_Processes                                          | 52 |  |  |  |

| 7.5. Review                                                   | 53 |  |  |  |

|                                                               |    |  |  |  |

| 8. Conclusions and Recommendations                            | 55 |  |  |  |

| 8.1. Conclusions                                              | 55 |  |  |  |

| 8.2. Recommendations                                          | 56 |  |  |  |

| References                                                    | 57 |  |  |  |

| List of Figures                                               |    |  |  |  |

| Appendix A. Flowcharts of the Generation Scavenging Algorithm | 60 |  |  |  |

| Appendix B. The GC's Control Word                             | 72 |  |  |  |

| Appendix C. The Processor's Control Word                      | 76 |  |  |  |

| Appendix D. The Promod Report                                 | 79 |  |  |  |

# **<u>1. Introduction</u>**

Object oriented programming is being used quite widely in the fields of both software engineering and artificial intelligence. Like structured programming, object oriented programming is mainly a technique of programming.

Although the object oriented point of view is not new, it is more frequently used lately. Major advantages over the more traditional high-level languages, such as Pascal, is that it reduces the complexity of large software systems, and makes these systems easier to maintain.

A great disadvantage however is that the implementation of such object oriented languages is far more complex than comparable procedure oriented languages. The high-level instructions can not be implemented as efficiently on conventional hardware, as for example Pascal-instructions can: the semantic gap between these languages and typical hardware is greater.

At the Digital Systems Group (EB) of the Faculty of Electrical Engineering of the Eindhoven University of Technology, the Interactive Design and Simulation System (IDaSS) has been developed. This design and simulation environment for digital circuits has been implemented using the object oriented language Smalltalk.

To be able to run object oriented systems efficiently in the future, research is done to architectures that support these systems better. As his master's project the author was given the assignment to design a microprocessor with an object oriented architecture.

This master thesis will start in chapter 2 by giving a short introduction into object oriented programming. In chapter 3 Smalltalk-80 and the Smalltalk-80 virtual machine are explained briefly. Chapter 4 shows the Rekursiv architecture, which forms the basis of the master project. In chapter 5 the Rekursiv is discussed and improvements made to the Rekursiv are explained. The model of the Rekursiv is given in chapter 6. Finally, conclusions and recommendations are given in chapter 7.

# 2. Object Oriented Programming

Object oriented programming systems are built on the model of communicating objects. Large applications are viewed in the same way as the fundamental units from which the system is built. The interaction between the most primitive objects is viewed in the same way as the high-level interaction between the computer and the user. Objects support modularity. The functioning of any object does not depend on the internal details of other objects.

# 2.1. Some Terminology

### 2.1.1. Objects

An object represents a component of the object oriented system. For example, objects can represent numbers, characters, strings, queues, rectangles, text editors, programs, compilers, etc. An object consists of some private memory and a set of operations. The nature of the operations depends on the type of data it represents.

A message is a request for an object to carry out one of its operations. A message specifies which operation is desired, but not how that operation should be carried out. The receiver, the object to which the message was sent, determines how to carry out the requested operation.

The set of messages to which an object can respond is called its interface with the rest of the system. The only way to interact with an object is through its interface. A crucial property of an object is that its private memory can only be manipulated by its own operations. A crucial property of messages is that they are the only way to invoke an object's operations. These properties ensure that the implementation of one object cannot depend on the internal details of other objects, only on the messages to which they respond.

This principle is called information hiding. Information hiding is important for ensuring reliability and modifiability of software systems by reducing interdependencies between software components.

### 2.1.2. Classes and Instances

A class describes the implementation of a set of objects that all represent the same kind of system component. The individual objects described by a class are called its instances. Each object, each instance has one class, a class may have multiple instances.

A class describes the form of its instances' private memories and how they carry out their operations. The object's private properties are a set of instance variables that make up its private memory, and a set of methods that describe how to carry out its operations. The instances of a class all use the same set of methods. Each instance has its own set of instance variables, but they generally all have the same number of instance variables.

Typically, a method sends messages to other objects, which invoke other methods, until you reach the point where a primitive method is invoked. The primitive methods are built into the virtual machine and cannot be changed by the programmer.

Each message-send eventually returns a result to the sender.

# 2.2. Features of Object Oriented Programming

To be object oriented, a programming language must provide four major facilities, namely:

#### **Information Hiding**

Information hiding is important for ensuring reliability and modifiability of software systems by reducing interdependencies between software components.

#### **Data Abstraction**

Data abstraction is a way of using information hiding to mask the precise way in which data is represented, so that it is accessible only through an abstract procedural interface and is easily maintainable.

#### **Dynamic Binding**

Dynamic binding encourages uniform programming conventions by providing polymorphism. Polymorphism allows equal naming of messages in different classes. Comparable methods of different kind of objects can have different implementations and still wear the same name. Many highly dynamic systems would be impracticable without this capability.

#### Inheritance

Inheritance enables programmers to create classes and, therefore, objects that are specializations of other objects. Creating a specialization of an existing class is called subclassing. The new class is a subclass of the existing class. The existing class is called the superclass of the new class. The subclass inherits instance variables, class variables, and methods from its superclass. The subclass may add instance and class variables and methods that are appropriate to more specialized objects. In addition, a subclass may override or provide additional behaviour to methods of a superclass. A large amount of code can be reused this way.

These features make that object oriented programming systems provide major advantages in the production and maintenance of software: shorter development times, a high degree of code sharing, and flexibility. This makes object oriented programming an important tool for building complex software systems.

Of course, object oriented programming has a few drawbacks too. Probably the most restricting disadvantage is that the implementation of object oriented languages is more complex than comparable procedure oriented languages, since the semantic gap between these languages and typical hardware machines is greater. This is also the reason why object oriented programming systems, implemented on conventional hardware, are often insecure. Using for example a simple debugger, individual datawords can be changed, that are not to be changed in the original object oriented environment.

Another disadvantage is the run-time cost of the dynamic binding mechanism. A message-send takes more time than a straight function call in conventional machines.

If hardware can be built that supports object oriented programming better than the traditional architectures, it would result in a faster and more secure system.

This chapter only gives a very short overview of object oriented programming. For more information on this subject, the articles [Pas86], [Pok89], [RaK90], and [Rob81] are recommended.

# 3. The Smalltalk-80 Virtual Machine

Smalltalk-80 is a frequently used object oriented programming system. Two major components of the Smalltalk-80 system are the virtual image and the virtual machine.

The virtual image consists of all the objects in the system. The virtual machine consists of the hardware devices and machine language (or microcode) routines that give dynamics to the objects of the virtual image.

The system implementer's task is to create a virtual machine. A virtual image can then be loaded in the machine.

This chapter will give an overview of the Smalltalk-80 virtual machine.

# 3.1. The Syntax of Messages in Smalltalk-80

Messages are described by expressions. A message-sending expression describes the receiver, selector and arguments of the message. When an expression is evaluated, the message it describes is transmitted to its receiver. Here are several examples of message-describing expressions:

- 1. frame center

- 2. origin + offset

- 3. frame moveTo:newLocation

- 4. list at:index put:element

Each expression begins with a description of the receiver of the message. The receivers in the examples are described by variable names: frame, origin, frame, and list, respectively. The selectors represent the actions that are desired. The selectors in the examples are: center, +, moveTo: and at:put: respectively.

Messages without arguments are called unary messages. A unary message consists of a single identifier called a unary selector. The first example is a unary message.

A binary message has a single argument and a selector that is one of a set of special single or double characters called binary selectors. The second example is a binary message.

A keyword message has one or more arguments and a selector that is made up of a series of keywords, one preceding each element. A keyword is an identifier with a trailing colon. The third and fourth example are keyword messages.

For more information on Smalltalk-80, see [Xer81] and [GoR83].

# 3.2. An overview of the virtual machine

The source methods, written by programmers, are translated by a compiler into sequences of eightbit instructions called bytecodes. The bytecodes are instructions for an interpreter. Below the interpreter in the implementation is an object memory, that stores the objects that make up the virtual image.

# 3.2.1. The compiler

A programmer doesn't interact directly with the compiler. When a new source method is added to a class, the class asks the compiler to translate the source methods in a sequence of bytecodes. These bytecodes are held in an instance of the class CompiledMethod.

In addition to the bytecodes, a CompiledMethod contains a set of objects called its literal frame. The literal frame contains any object that could not be referred to directly by the bytecodes.

The categories of objects that can be referred to directly by bytecodes are:

- the receiver and arguments of the invoking message,

- the values of the receiver's instance variables,

- the values of any temporary variables required by the method,

- seven special constants (true, false, nil, -1, 0, 1, and 2),

- 32 special message selectors.

The objects ordinarily contained in a literal frame are:

- shared variables (global, class, and pool variables),

- most literal constants (numbers, characters, strings, arrays, and symbols),

- most message selectors (those that are not special).

## 3.2.2. The interpreter

The Smalltalk-80 interpreter executes the bytecode instructions found in CompiledMethods. The state of the interpreter consists of five pieces of information:

- 1. The CompiledMethod whose bytecodes are being executed,

- 2. The location of the next bytecode to be executed. This is the interpreter's instruction pointer,

- 3. The receiver and arguments of the message that invoked the CompiledMethod.

- 4. Any temporary variables needed by the CompiledMethod,

5. A stack.

The interpreter repeatedly performs a three-step cycle:

- 1. Fetch the bytecode from the CompiledMethod indicated by the instruction pointer,

- 2. Increment the instruction pointer,

- 3. Perform the function specified by the bytecode.

When a message is sent, all five parts of the interpreter's state may have to be changed in order to execute a different CompiledMethod in response to this new message. The interpreter saves its old state in objects called contexts. The context that represents the current state of the interpreter is called the active context. When a send-bytecode requires a new CompiledMethod to be executed, the active context becomes suspended, and a new context is created and made active. The suspended context is called the new context's sender. Contexts are represented by instances of class MethodContext.

Another type of context is represented by instances of class BlockContext. A BlockContext represents a block in a source method that is not part of an optimized control structure. Blocks are sequences of instructions, which will be evaluated when they receive the message value. For example:

incrementBlock  $\leftarrow$  [index  $\leftarrow$  index + 1]

will only be executed when the message value is sent to incrementBlock:

incrementBlock value.

In this case index is incremented.

A BlockContext responds to the message value: by becoming the active context.

When a send-bytecode is encountered, the interpreter finds the CompiledMethod indicated by the message as follows.

- 1. Find the message receiver. The message receiver is found on the stack.

- 2. Access a message dictionary. The original message dictionary is found in the receiver's class.

- 3. Look up the message selector in the message dictionary. The selector is indicated in the send-bytecode.

- 4. If the selector is found, the associated CompiledMethod describes the response to the message.

- 5. If the selector is not found, a new message dictionary must be searched (returning to step 3). The new message dictionary will be found in the superclass of the last class whose message dictionary was searched.

An exception to the way the CompiledMethod is found, is used when a super-send is encountered. the original message dictionary for step 2 is now found in the superclass of the class in which the currently executing CompiledMethod was found.

The bytecodes used by Smalltalk-80 are enumerated in [GoR83].

# 3.2.3. The object memory

Each object is associated with a unique identifier which is called its object pointer. The object memory and the interpreter communicate about objects with object pointers. The object memory

associates each object pointer with a set of other object pointers. Every object pointer is associated with the object pointer of a class. If an object has instance variables, the object pointer is also associated with the object pointers of instance variable values.

In Smalltalk-80, instances of class SmallInteger represent the integers -16384 through 16383. Each of these instances is assigned a 1 in the low-order bit position of their object pointer, and the two's complement representation of their value in the high-order 15 bits. An instance of SmallInteger needs no instance storage since both its class and its value can be determined from its object pointer.

The object memory provides the following five fundamental functions to the interpreter.

- 1. Access the value of an object's instance variable.

- 2. Change the value of an object's instance variable.

- 3. Access an object's class.

- 4. Create a new object.

- 5. Find the number of instance variables a class has.

More information on Smalltalk-80 and its virtual machine can be found in [GoR83].

# 4. The Rekursiv Architecture

Ivor Tiefenbrun is the founder of Linn Products, a firm with a worldwide reputation in the audio marketplace.

In the early 1980's, Tiefenbrun was convinced that an object oriented programming system would allow Linn Products to integrate all the factory's functions with flexibility. Since only few of such systems were commercially available, Tiefenbrun decided to have such a system designed. As a result, an object oriented programming system called LINGO, with many features of Smalltalk, was written.

However, the performance of LINGO on Linn's VAX-minicomputers proved far from adequate for the task of automating the whole factory. Therefore, Tiefenbrun decided to finance the development of a new processor architecture optimized to run object oriented languages orders of magnitude faster than conventional hardware can. Thus was born the Rekursiv project.

# 4.1. The Principles behind Rekursiv

On conventional computers, the high-level primitive instructions of an object oriented programming system are implemented in machine-coded programs. Apart from the fact that these machines execute very slowly, they are insecure because of the semantic gap between the language and the machine. Objects generated by the object oriented system can easily be changed by a program written in some other language, like assembler. Therefore, what is needed is a machine which provides an object oriented store, full persistence for all types of data, and a high-level instruction set which eliminates the semantic gap entirely by directly implementing the primitive operations.

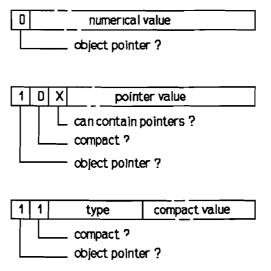

## 4.1.1. Object Representation

Objects should be stored in a form which directly reflects their structure, their type and their relationship to one another:

- 1. an object should be stored and moved as a unit,

- 2. objects should be created by system primitives only, so that they cannot be forged. The system should be the sole creator of references to objects,

- 3. objects should refer to one another in some non-positional manner, so that they can be moved about within memory and migrate to or from backing store without having to perform address translation,

- 4. the type of an object should be inseparable from it, so that it can always be identified, and made immutable so that it cannot be altered,

- 5. the operations available for each class of objects should be accessible from the type, so that operators can be checked when applied, to prevent data being misinterpreted.

## 4.1.2. Persistent Storage

To create a single level store, main memory should be integrated with backing store. This requires that both media employ the same storage format for objects so that objects don't have to be transformed in order to be moved to or from disk.

Such a system provides a natural form of object persistence. This property should be independent of the data type. Just as all data can be passed between processes, all data is treated equally.

### 4.1.3. Object Swapping

In an object-based system, data can be loaded into memory simply by referring to it. There is no need to read data from disk explicitly. Similarly, it will move back to disk automatically, should references to it cease to be frequent. Furthermore, there is no need to transform any data that need to be moved.

This leads to a paging strategy which swaps individual objects as and when necessary, rather than swapping in large pages of memory around the address of the desired location.

## 4.1.4. Access Checking

When highly dynamic systems are used, run-time activities must be provided, which less powerful systems don't need to support. Typically, this might involve searching symbolic namespaces during execution and dynamic type and range checking. There is a requirement for appropriate hardware support for these activities. The reasonable thing is to carry out such checks if necessary in parallel with the limitation of the access.

If object access is to be secure, it will be necessary to determine dynamically that the types of indices are appropriate to the types of the structures into which they are indexed.

## 4.1.5. High-Level Instructions

Object oriented programming systems are often, as is the case for Smalltalk, implemented by way of an interpreter which executes a machine code routine for every instruction. It would seem only logical to try to make a machine which provides such operations as proper

instructions, so that, at least the interpretational overheads can be eliminated from the implementation.

A large part of the interpreter is usually devoted to storage management. What must be designed therefore, is a machine architecture in which storage is managed below the level of the instruction set, or within the instructions, so that from the viewpoint of a running program it is automatic. This makes a hardware object store far more secure than one simulated on a conventional virtual memory system.

Since all access to the fields of an object is through a set of self-contained instructions, the individual high-level instructions can perform type and range checking to guarantee that the right type of indexing is performed and that the index only addresses valid components. Another aspect to data security, is polymorphism. Taking an operator in addition to data, they work out dynamically what the operator means to that data. The system will detect and reject requests to perform semantically senseless operations.

# 4.2. The Architecture

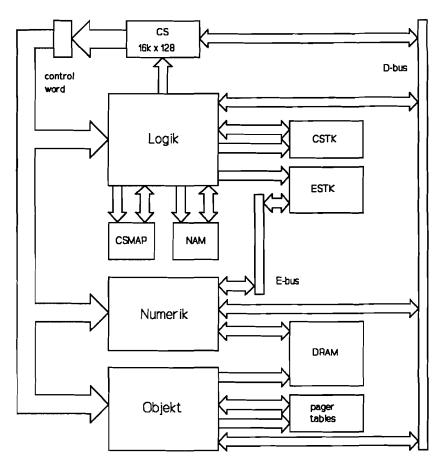

The Rekursiv architecture consists of three processors, each designed for a specific task, and a couple of distinct banks of memory (see fig. 4.1).

The basic processor architecture, as outlined in fig. 4.1, is built around the socalled Objective chipset comprising three gate arrays.

- 1. Objekt: object oriented memory management unit,

- 2. Logik: microsequencer and stack addressing unit,

- 3. Numerik: data manipulator.

Furthermore, the Rekursiv architecture contains six memory blocks that are implemented in static RAM (SRAM) and one large bank of dynamic RAM (DRAM). This DRAM is the main object store memory. The six SRAM blocks are:

CSTK: control stack, ESTK: evaluation stack, CS: control store, CSMAP: control store map, NAM: new language abstract memory, pager tables.

The microcode is stored in the control store which has its own 16-bits address-bus. This control store can contain up to 16,384 (in Rekursiv) control words of 128 bits each. The control store map

Fig. 4.1: The Rekursiv architecture

holds a table of 2048 microcode start addresses, and maps 10-bit opcodes onto the microcode that implements them. The control store and the control store map can be thought of as a Smalltalk-style bytecode interpreter implemented in hardware.

The NAM can store up to 524,288 words of 10-bit opcodes and their 30-bit arguments that form abstract or high-level instructions. The NAM behaves like a fast instruction cache. In a Smalltalk implementation, the abstract code in the NAM would be the methods of the most important system classes.

Usually, a major disadvantage of employing a tightly coupled cluster of processors is the overhead of communications between the processors. This disadvantage is overcome in the rekursiv by using a single control word to synchronise all the elements. This has resulted in a 128-bit wide control word, that permits many separate activities to be specified in parallel.

Such a wide control word is not effective, if contention can occur for some vital component in the system, which can only be allocated to one of the activities on a given clock cycle. If for example a variety of registers could be loaded at the same time except for the fact that all have to use the same data path to acquire their information, then that data path is a bottleneck which must be remedied if parallelism is to be realised.

This and the fact that a memory chip can be accessed only once a clock cycle, is the reason why the Rekursiv processor is heavily fragmented into many distinct banks of memory, for stacks, code and data. Each memory should be directly accessible and manipulable by the associated processing elements, independently of the main system bus. In addition, each memory should have an appropriate system of control registers and sufficient local arithmetic logic to support the address calculation, thereby further reducing the bus traffic.

Each stack is therefore controlled by a separate addressing system. Each control register can be controlled individually, and offset addresses can be computed independently of the ALU.

In most general purpose machines, when a page fault occurs during the address translation phase of an instruction, it must back up the instruction to a point at which it can be re-entered, saving the microstate, and then invoke a system call to handle the fault. Then when the fault is fixed, the microstate must be restored and the instruction must be restarted from the middle. Clearly for an instruction which implements a high level algorithm during which memory is accessed frequently, the microstate may become very complex and the recovery process quite costly.

The Logik sequencer overcomes this limitation, because page faults are handled below the processor by the interface to the object oriented store. When a page fault (DPFLT) occurs, the Rekursiv is halted while the storage system fixes the fault by loading in the desired item from disk, updating the page tables and then restarting the Rekursiv.

Conventional microcodable machines so far have not been able to provide high-level instruction sets, simply because they don't provide nested or even recursive algorithms. To achieve this a different kind of architecture had to be developed.

The Rekursiv attaches a fixed size header to each object's storage image, thereby giving direct support to a very large number of types. This header contains an object's size and type, so they can be directly accessed.

Because backing store and main memory have to form a single object store, the storage format has to be the same in each case. The Rekursiv maps position-independent object numbers into the current physical address of objects, and will page them in if necessary.

In the memory management system are tables to hold an object's size, an object's type or class, an object's current address in memory, and the first word of the object. Each table element is indexed by the object number, modulo the table size. Each table is accessed at the same time, to fill individual output registers at the end of the paging cycle. These can be fed into range checking logic, so that checks can rapidly be carried out when the components of an object are accessed.

## 4.2.1. The Object Oriented Memory Management Unit (Objekt)

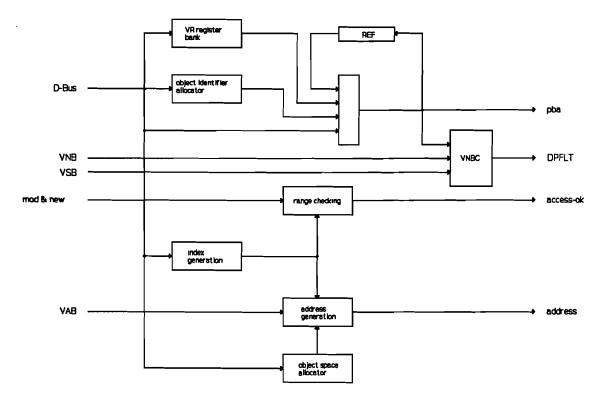

The major sub-units are shown in fig. 4.2.

The principal routes in Objekt are the VSB, VAB and VNB which are 24-bit data buses from the pager tables and represent an object's size, address, and number respectively. The 40-bit system D-bus forms a bidirectional path. PBA, a 40-bit quantity of which the low-order bits are stripped off to form an address, runs out to the pager tables, and a 24-bit address is sent out to main memory. Other inputs comprise the clock, reset signals and controlling opcodes. Other outputs are the condition code, an access validation signal, and a data page fault signal.

The object-identifier allocator is a 38-bit counter which increments to yield the object number of the next object to be allocated. The other two bits of an object number are flag-bits.

VR is a bank of eight 40-bit registers loadable from the system bus, able to source the object pager.

VNBC compares the identifier of the newly-paged object with the contents of the VNB slot addressed by that identifier. If these two quantities differ, it means that the desired object is not in memory, so that it must be fetched from backing store.

The index generator incorporates special hardware which can be microcoded to scan efficiently over the elements of objects.

The object space allocator, upon being presented with the desired size on the system bus, produces the base address that each newly created object will have.

Fig. 4.2: The internal architecture of Objekt

Rekursiv has been designed with a brutal, but fast garbage collection strategy. The DRAM object store is divided into two halves, only one of which is used at any time. When objects have to be created that exceed the last address of the active half, more memory is required and Objekt invokes hardware garbage collection.

The garbage collector then identifies all the objects to be kept, and copies them into the free semispace, updating the entries in the address tables in the paging system. If this process still doesn't free enough memory, a second level of garbage collection is used to squeeze out infrequently accessed objects to disk. If even this fails then all persistent objects are squeezed back to disk.

These fallback strategies ensure that garbage collector performance degrades gracefully rather than failing with a bang. The sweeping of unwanted objects from disk is a software housekeeping problem that should take place off-line.

#### 4.2.2. The Microsequencer (Logik)

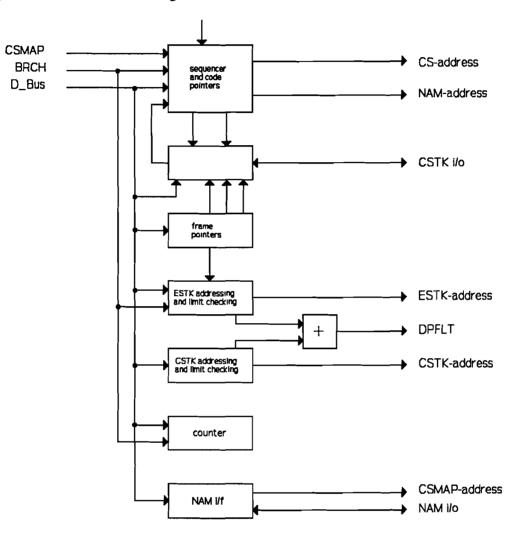

The major sub-units are shown in fig. 4.3.

Fig. 4.3: The internal architecture of Logik

The microsequencer issues successive 128-bit control words.

Various addresses are produced by the Logik, including addresses for both stacks, the NAM kernel program code store and the microcode control store. The sequencer may select the next microaddress from one of its inputs or from an internal source. External sources are the control store map's microcode address register, the BRCH (a 16-bit field in the control word), the D-bus, or the top of the control stack.

A large multiplexer can be enabled to present data to the bidirectional control stack data lines, or these lines can carry the top of the control stack into the sequencer. Data that can be carried onto the control stack includes the code pointer of the microcode and the abstract codestream, three frame pointers (base of current microframe, argument pointer of the current abstract frame, or the current stackpointer), or the system bus. More information on the operations that can be performed using the fields of the Rekursiv's control word, can be found in [Har88].

### 4.2.3. The Data Manipulator (Numerik)

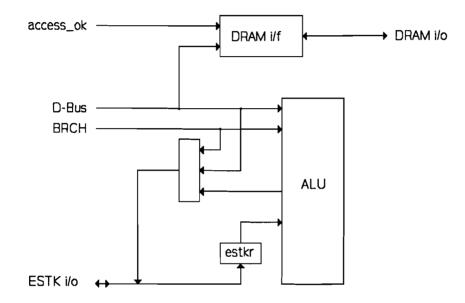

As can be seen from figure 4.4, in addition to the main memory interface, the Numerik holds the 32-bit ALU, multiplier and barrel shifter. The results from the elements can be pushed out onto the evaluation stack either in 32-bit format or first be combined with an 8-bit extension specifying the type to form a compact object.

Fig. 4.4: The internal architecture of the Numerik

## 4.2.4. The Pipeline

An instruction takes four cycles in the pipeline, two of which are overlapped with the previous instruction. The basic sequence is:

| inc apc :                              | increment the abstract program counter (apc),             |

|----------------------------------------|-----------------------------------------------------------|

| read nam[apc] $\rightarrow$ mapar :    | load the opcode in the abstract code stream (nam) at the  |

|                                        | point addressed by the apc into the map address register  |

|                                        | (mapar),                                                  |

| read csmap[mapar] $\rightarrow$ ucar : | read out the control store map into the microcode address |

|                                        | register (ucar),                                          |

| jv :                                   | jump to the microaddress specified by ucar.               |

The two and two overlap will give:

inc apc read nam[apc]  $\rightarrow$  mapar read csmap[mapar]  $\rightarrow$  ucar jv

inc apc read nam[apc]  $\rightarrow$  mapar read csmap[mapar]  $\rightarrow$  ucar jv

so the shortest instruction can be reduced to two cycles.

For more information on the Rekursiv architecture, see [Har88] and [Pou88]. [HaB86-1] Describes the Objekt shortly. [Har86] and [HaB86-2] give more information on microcoding the architecture.

# 5. Evaluating the Rekursiv

This chapter gives the author's opinion on the architecture of the Rekursiv and how it could be modified in order to implement the Smalltalk-80 virtual machine efficiently.

An important principle behind the Rekursiv's architecture is that it has a writable instruction set. This means that a user can write his own instruction set, one that is best suited for his applications. Then he can load his instruction set in the control store to run his applications.

The Rekursiv does not necessarily have to run object oriented languages. For example, a C-instruction-set can be implemented as well. A C-instruction-set however will not make use of all unique features of the Rekursiv.

Because the processor is developed to run object oriented languages, and because it is easier to build, it is advisable not to give the processor a writable instruction set. This means that the microcode must be known to be correct when the processor will be produced.

As is already stated, the microcode that implements the instruction set, is stored in the CS (see fig. 4.1). The CSMAP holds a table with the microcode start addresses and maps 10-bit opcodes onto the microcode that implements them. In a Smalltalk-80 implementation, the CSMAP can use the number of the bytecode as an index, returning the start address of the microcode routine that implements the bytecode. In this way the CSMAP together with the CS act as a hardware bytecode interpreter.

Frequently performed operations can use the NAM as a fast instruction cache. For example the NAM could contain the methods of the most important system classes. Methods for user-defined classes would be stored in the main DRAM memory.

Because the microcode can use its own control stack (the CSTK), it can implement very high-level instructions, since it is now possible to use recursion and subroutine calling. This makes it possible to implement complex algorithms in microcode.

What still has to be done is to define the different fields of the control word and to provide the logic that implements these instructions.

In [Har88] nothing is said about any I/O-function. If one looks at the microcode instructions, no instructions are provided for basic I/O-operations. Since these instructions might be needed they have to be implemented.

This can be done by providing the Objekt with an outputline \*IO/MEM. This line indicates whether the source or the target of a read- or write-operation is an I/O-register or the main memory. When the I/O-registers are accessed, the low-order bits of the address-bus indicate which I/O-register is accessed.

The instruction set has to be extended with two instructions, ioput and ioget. Ioput puts the value of the D-bus in the I/O-register indicated by the address. Ioget reads the desired register and puts its value on the D-bus.

# 5.1. Garbage Collection

The Rekursiv's main memory is divided into two semispaces. Only one of the semispaces is used at a time. In the active half, space is allocated to objects sequentially. When the active half overflows, garbage collection is invoked. The garbage collection process, as it is implemented in the Rekursiv, traces all objects that are reachable from the processor. These objects are copied to the inactive half, leaving behind all the dead ones. Finally it interchanges the two semispaces.

This garbage collection has the advantage that it is very simple. However the algorithm implies that the memory usage of the Rekursiv is very inefficient. Only 50 % of the total DRAM memory is used at a time.

Furthermore, when garbage collection is invoked, the process that was running is suspended. It is restarted after the garbage collection process has finished. These pauses are not always acceptable. When, for example, the microprocessor is a part of the controller for a complex chemical process, and garbage collection forces the processor to suspend its controlling function, strange things might happen.

Because the garbage collection process, as it is implemented in the Rekursiv, causes unwanted pauses in the execution of the application program, the decision was made to develop a garbage collector that performs its function in parallel with the main processes. It takes care of the removal of dead objects, and of the compaction of the main memory.

# 5.2. The Disk Processor

The disk processor (DP) is the interface between the Rekursiv and the background memory. Together with the DRAM memory and the disk it forms the one level memory.

When an instruction is encountered to page an object that is not yet in main memory, a datapagefault (DPFLT) occurs. The disk processor now has to make sure that all the proper actions are performed to load the required object into main memory. If the pager tables entry of the wanted object is already occupied by another object, the disk processor must first store the associated object on background memory, if it is modified or new. This process is performed without the user explicitly having to instruct it.

The disk processor takes care of all stores on and fetches from disk. Furthermore, it has to perform the housekeeping of the disk. Dead objects must not be allowed to fill up the disk. These objects must be removed, and thus compaction of the disk is one of the tasks too.

The disk processor has an interface to the Objekt and an interface to the garbage collector for reasons that will be explained in the next chapter. This means that there is a lot of communication between the disk processor and the Rekursiv. This communication is made more difficult by the fact that a harddisk is an asynchronous resource.

# 5.3. Dynamic Binding

One of the time consuming mechanisms of an object oriented environment is the dynamic binding mechanism. When a non-primitive message is sent, the dynamic binding algorithm is used to find the corresponding method that handles the message.

Usually, the dynamic binding mechanism starts by looking in the so-called method dictionary of the class of the object to which the message was sent. When the method is not found here, the search continues in the superclass of the last-searched class until the method is found. In large systems, it may take a long time before the method is found. Because a message-send is one of the most frequent operations in an object oriented programming system, a lot of time is spent looking for methods. When an algorithm can be found that implements the dynamic binding mechanism as fast as possible, it will save a lot of time. Unfortunately, the dynamic binding mechanism is beyond the scope of this thesis.

# 5.4. The Strategy

This paragraph gives the strategy that is used to come to the result of this master thesis. Now the decision is made to design an object oriented microprocessor with a microcoded instruction set, it can be divided in distinct parts. The microprocessor is divided into four parts:

- the memory management unit Objekt,

- the garbage collector,

- the sequencer and stack-addressing unit Logik,

- the data manipulator Numerik.

The memory management unit and the garbage collector heavily depend on eachother since they both employ the same memory. The structure of the memory is defined by these processes. The Logik and the Numerik can be developed independently.

The choice is made to design the memory management unit and the garbage collector first, because it is vital for the speed and efficiency of the total processor.

In accordance with the book in which the Rekursiv is described, [Har88], first the instruction set is defined, then the hardware that implements the instruction set is developed. The function of the hardware is defined in a model. Finally the model can be implemented using IDaSS.

# 6. Garbage Collection

Whenever the processor needs an object that is not already paged in, it instructs the disk processor to fetch the object from disk, and to store it in main memory. This works well, but when a large application is in progress, the memory will fill up, until it can not contain more objects. At this point the memory has to be re-arranged. All the space that is occupied by objects that are not needed any longer, can be freed. This process is called garbage collection.

Garbage collection usually takes place on-line. When memory overflows, the program that is currently being executed is suspended, and garbage collection is invoked. When this process terminates, the suspended program is started again.

As is already said in chapter 5, the object oriented processor is given a parallel garbage collector. This process frees the space occupied by 'dead' objects in parallel with the execution of the application program. The purpose is to perform garbage collection on all objects in the DRAM memory. The application should at all times have enough space to perform its task. It should be interrupted as little as possible. The garbage collection process should put as little overhead on the processor's execution as possible.

# 6.1. Garbage Collection Algorithms

The garbage collector must decide which objects can be removed and which objects must stay in main memory. Objects that are dead can be removed in any case. An object is said to be dead when no other object in the system contains an object pointer that points to it. It is dead because it can not be reached through any of the objects. Objects that can be reached from the processor's sources without going through an object on background memory, are said to be reachable. A strategy that can be used is to dispose of all objects that are not reachable. These objects are not necessarily dead, because they might be reached via an object on background memory.

Various algorithms for garbage collection have been developed through the years. Some of them will be explained in this paragraph. After this, an algorithm will be chosen that can be implemented as a parallel process.

## 6.1.1. Reference Counting

The reference counting algorithm ([GoR83], [Ung84], [Ung86]) keeps track of the number of objects that refer to a certain object, by associating a reference count with this object. When the reference count drops to zero, the object is no longer needed, and the memory it occupied can be freed.

Whenever an object pointer is stored in an object, the reference count of the former object to which was pointed must be decremented, and the reference count of the object to which the new pointer points must be incremented. When an object's reference count becomes zero, all the reference counts of the objects to which it refers must be decremented. This can initiate a chain of objects that must be deleted. It is apparent that an object is deleted as soon as it becomes obsolete.

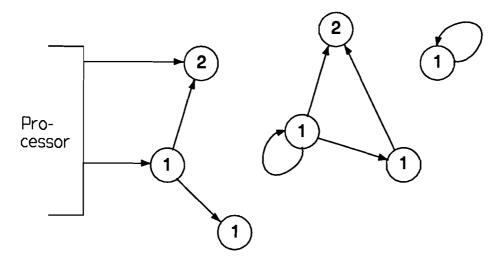

The reference counting algorithm usually does not free all space occupied by non-reachable objects. Objects that refer to themselves or a group of objects that forms a cyclic structure are not deleted by this algorithm. The different kind of object chains are shown in fig. 6.1.

Fig. 6.1: Object structures

Objects are represented by circles. The numbers in the circles is the reference count. The three objects on the left are still reachable. Their reference count is greater than zero, and hence they are not removed. The next three objects form a cyclic structure. The respective reference counts of the objects is not equal to zero, but still they can not be reached. The object on the right has a reference to itself and is not removed.

When circular structures are not removed, it is just a question of time before memory overflows. This is the reason why this algorithm needs another garbage collection mechanism too at fixed times.

Another disadvantage of the reference counting algorithm is the overhead the algorithm puts on each store instruction. Furthermore pauses in the execution of the user program will occur when one or more objects are de-allocated. Each page table entry needs a field to count the references.

# 6.1.2. Mark and Sweep

The mark and sweep algorithm ([Ung84], [Ung86]) consists of two phases. The first phase, the mark phase, searches all objects that are alive (reachable), and marks these. The second phase, called the sweep phase, scans the memory for dead (not reachable) objects (which are not marked), and frees the space they occupy.

The algorithm needs only one bit extra per page table entry. The largest drawback is the time that is needed to perform garbage collection. This causes disturbing pauses in the execution of the user program.

The algorithm is split in two phases. When a parallel garbage collector employs the mark and sweep algorithm, the complete object structure can be changed in the time needed for the mark-phase. When the sweep-phase starts, many objects are kept that are actually dead.

# 6.1.3. Baker's Semispace Algorithm

Baker's semispace algorithm ([LiH83]) divides memory into two spaces, tospace and fromspace. New objects are created in tospace. When garbage collecting, live objects are copied from fromspace to tospace (called scavenging). When this process is finished the memory in fromspace can be reused. The algorithm finishes by interchanging the two semispaces, called flipping. Baker does not use an object table. Instead he uses forwarding pointers in the location where the copied object's object pointer was. An object that accesses this copied object follows the forwarding pointer to the new location, and simultaneously updates its pointers to the copied object. A disadvantage is the inefficient memory usage, because only one semispace is used at a time.

The Rekursiv as described by Harland uses a slightly different version of Baker's algorithm. The Rekursiv does use an object table. This makes the idea of forwarding pointers redundant. Once an object is copied to tospace, the physical address of the object in the object table is changed. This makes the algorithm faster, but the inefficient use of the DRAM memory stays.

# 6.1.4. Generation Garbage Collection

An improvement to Baker's algorithm is described in [LiH83] (and [WiM89]). They use the fact that most young objects die young, and that old objects usually continue to live. They realised that a lot of time is wasted by repeatedly copying old objects.

With generation garbage collection, memory is divided into regions. These regions are organized into generations. The current generation number is periodically incremented. In this way newer generations (which contain a high percentage of garbage) can be garbage collected more often, than older generations (which contain a low percentage of garbage).

The process of garbage collecting a particular region, is initiated by condemning the region. When a region is condemned, new regions are created to hold the objects evacuated out of a condemned region. Each of the evacuation regions will inherit the same generation number as the condemned

region, but is assigned a version number one higher. The version number of a region counts how many times that generation has been condemned.

There is a chance that fragmentation of the memory occurs, as is the case in paged memory systems. Fragmentation can be diminished by making the regions larger.

To make the scavenging-process faster, pointers that point forward in time are restricted. Pointers that point backward in time are directed through an entry table. This means that when a region is condemned, only the regions of that generation and of younger generations (plus the entry table) have to be scavenged.

The disadvantage of the generation garbage collection algorithm is its complexity. The DRAM memory is divided into regions. Each region has its own generation and version number. This memory structure implies extra paging-tables. Furthermore the algorithm is difficult to implement.

## 6.1.5. Generation Scavenging

Generation scavenging ([Ung84], [Ung86], [Jac90]) also uses the fact that young objects tend to die young, and older objects are likely to remain.

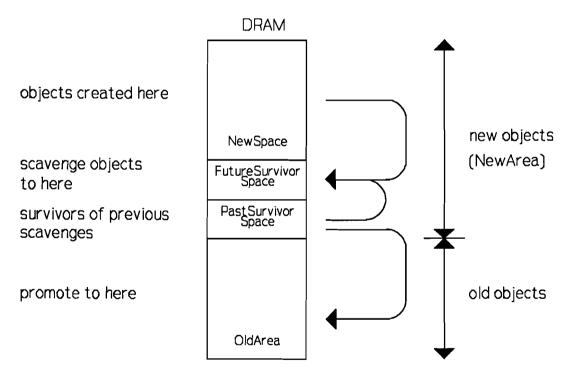

Fig. 6.2: The memory structure as used with generation scavenging

With generation scavenging memory is divided into two areas, OldArea and NewArea (see fig. 6.2). OldArea contains objects that have survived a certain number of scavenges, and hence are likely to stay. NewArea consists of three spaces, NewSpace, FutureSurvivorSpace, and PastSurvivorSpace. New objects are created in NewSpace. When this space fills up, all the live objects from NewSpace and PastSurvivorSpace are copied to FutureSurvivorSpace. When this has finished, Future- and PastSurvivorSpace are interchanged.

If an object survives a certain number of scavenges, it is promoted to the OldArea. This is called tenuring. The tenuring threshold can be determined dynamically. Once in a while the OldArea should be subjected to garbage collection too. This can be done by an off-line mark and sweep algorithm.

The search for live objects starts at the remembered set. This set consists of all "old "objects that contain pointers to 'new' objects. Objects are added to this set as a side effect of store-instructions.

The main idea behind the division in an OldArea and a NewArea, is that objects in OldArea are not copied over and over anymore. The only overhead that is put on the processor-instructions is related to the remembered set.

## 6.1.6. The choice of an algorithm

Which strategy is to be used depends on a couple of factors. First, the processor must be interrupted as little as possible. Second, the garbage collector should work correctly. Third the garbage collector should not need too much extra hardware (the processor is large enough as it is).

A major disadvantage of reference counting is that it does not free circular structures that are not reachable. The individual objects in such a structure all have a reference count that is not equal to zero, but still they can not be reached. Furthermore the reference counting algorithm puts additional overhead on the store-instructions.

Because the mark and sweep algorithm works in two phases it is unreliable. When the mark-phase is in progress, the application program can alter the object structure in memory. When the sweep phase starts, the object structure might not match the way it is marked. This does not lead to errors, because when an object dies after it is marked, it will be deleted in the following garbage collection cycle. The amount of marked dead objects should be as little as possible, since the purpose of garbage collection is to remove space occupied by dead objects for objects that are alive.

The reference counting algorithm and the mark and sweep algorithm will not be used for apparent reasons.

It must not take too long to perform an entire garbage collection cycle. The processor should be given as little time as possible to alter the object structure. To make the time needed for garbage collection shorter, the older objects that contain a low percentage of garbage, should not be subject to garbage collection as often as the newer objects. This eliminates Baker's algorithm as a possibility, which does not make a distinction between new and old objects. Only two algorithms are left, generation garbage collection, and generation scavenging.

A disadvantage of generation garbage collection is the use of regions. This makes the algorithm far more complex then generation scavenging, and it needs a lot more hardware (generation number, version number, and an entry table per object containing region, plus the indirection table). The extra hardware needed by generation scavenging is a field in the pager tables that reflects the number of scavenges (NOS) an object has survived. This field does not need any additional memory. It can be put in the VNB slot of a non-compact object. The lower 16 bits of this slot are not used (they are given by the index in the pager tables), and hence can be used to store the NOS-field.

Because compared to generation garbage collection, generation scavenging needs less extra hardware, and is easier to implement, generation scavenging will be the algorithm used for garbage collection.

# 6.2. Parallel Generation Scavenging

This chapter gives a couple of observations on generation scavenging. A few adjustments are made in order to be able to implement the algorithm in parallel.

### 6.2.1. Memory Usage

As is said earlier, generation scavenging uses a memory configuration in which memory is divided into two parts, called NewArea and OldArea. NewArea is subdivided into three spaces, NewSpace, FutureSurvivorSpace, and PastSurvivorSpace. New objects are created in NewSpace. When NewSpace fills up, the scavenging process is activated. All live objects from NewSpace and PastSurvivorSpace are copied to FutureSurvivorSpace, leaving behind the dead objects. When the copying is done, Future- and PastSurvivorSpace are interchanged ('flipped'). NewSpace now can be reused. When an object has survived a certain number of scavenges, it is promoted to OldArea. This process is called tenuring. The tenured object is no longer subject to on-line garbage collection.

The OldArea can probably not be loaded into the DRAM entirely. The main part of the OldArea will be on background memory. When an object is requested that must be fetched from background memory by the DP, it is loaded into the OldArea directly. Space in the NewSpace is only allocated to newly created objects. In summary the NewArea is entirely in the DRAM, a part of the OldArea is spread over a part of the DRAM and the background memory.

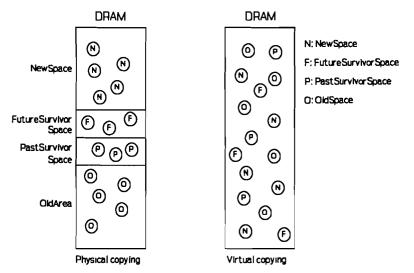

There are two possible solutions to realise the copying of objects from one space to another space. When the objects are copied physically, memory is divided into four distinct banks of memory. The process actually copies an object from one part of the memory to another part. The second solution does not really copy the objects. To each page tables entry a couple of bits are added, at least two, that reflect the virtual memory space in which an object resides. The virtual copying process consists of changing the space-bits of that object. The two methods are shown in fig. 6.3.

The benefit of virtual copying is the time is saves. Copying objects physically takes time. All virtual copying needs is two bits extra per pager tables entry.

However, the author thinks the whole idea of generation scavenging is abandoned, when virtual copying is applied. Dividing memory into different parts has become useless. The OldArea was added for older objets that ware likely to stay. These objects are not copied anymore. When virtual copying is applied, copying does nearly take any time, so why use an OldArea. An advantage of generation scavenging is that it has a built-in compaction mechanism. When a scavenge starts the objects are copied to the FutureSurvivorSpace, starting at word zero. FutureSurvivorSpace is filled sequentially. When a scavenge ends (at least in the on-line case) NewSpace is empty and can be reused. When virtual copying is applied, the memory is not divided into distinct banks. This means that when an object is dead, it leaves an empty space and the

Fig. 6.3: Two possible copying strategies

memory gets fragmented. When the fragmentation becomes too heavy, a compaction mechanism must be applied. Furthermore the allocation of memory is more complex in a fragmented memory, since the space must be large enough to accommodate an object of specific size. The allocation of space is done by the main processor, so the execution speed decreases.

Virtual copying may decrease the duration of a garbage collection cycle, but this is only relative. The execution speed of the processor is decreased, and every now and then a compaction mechanism must be invoked. This is the reason why the physical copying is used.

### 6.2.2. Scanning the Objects

The purpose of garbage collection is to remove all dead objects from memory, so that memory space is obtained for live objects. There are different ways to find all live objects.

Generation scavenging as described in [Ung84] and [Ung86] starts searching for live objects at the remembered set. The remembered set consists of all the objects in OldArea that contain pointers to objects in NewArea. Objects are added and removed from the remembered set as a side-effect of store-instructions. This puts an extra overhead on the store-instructions, which of course, is not wanted.

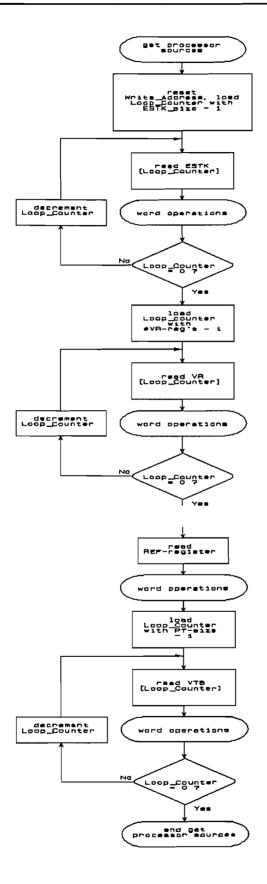

This overhead can be eliminated, if one uses another point of view. Instead of starting scavenging at the remembered set, scavenging is started from the processor sources that can contain object pointers. When the search continues through all objects in the system, all live objects are reached.

The sources in the Rekursiv that can contain object pointers are the evaluation stack (ESTK), the eight VR-registers, and the REF-register. These sources have to be presented to the garbage collector.

In the Rekursiv the ESTK is implemented as a segmented stack, of which only one segment at a time is in the RAM-area. The other segments are stored on disk until they are needed. When a stack position must be accessed that currently is not in the ESTK-RAM, a page fault is issued and the DP loads the required stack-segment in the SRAM. Because each class in the object oriented

system has its own logical stack, the ESTK will be heavily fragmented into many distinct smaller stacks. Because these logical stacks are not necessarily ordered sequentially, the entire SRAM has to be searched for object pointers.

The problem that arises is that when we want to make a sequential scan of the ESTK in its configuration used in the Rekursiv, the DP will be called upon frequently, halting the processor accordingly. There are two possible solutions to this problem. The first solution is to give the garbage collector its own stack-segment. This however must be done very carefully to prevent that the processor alters a stack segment that is also loaded in the garbage collector. The second solution is to present the processor with the entire ESTK in SRAM (the Rekursiv uses a 256 kB ESTK). This also speeds up the processor because it does not have to store and load stack segments anymore on-line. Despite of the large SRAM the second solution is chosen.

## 6.2.3. Protection of Shared Resources

There are a couple of resources that are used by the main processor and the garbage collector. When these resources must be accessed by one of the processes, this must be done very carefully. When both processes want to write into a register simultaneously, the result can not be predicted. The processes that can be accessed by both processes are:

- every object in main memory,

- the register that points to the next location to be written in NewSpace (Objptr),

- the register that points to the next location to be written in OldArea (Old\_Address),

- the ESTK,

- the VR-registers,

- the REF-register.

The last three resources only have to be read by the garbage collector. This can be done without errors when an extra read-port per resource is added. Then the main processor and the garbage collector can access the resources simultaneously.

The DRAM is provided with an extra input/output-port for the same reason.

When the main processor wants to modify a location of an object, it must first be sure that the garbage collector is not moving that object to another area in main memory. In the same way the garbage collector must be sure that the main processor is not writing into an object, before it starts moving that object. This can be done easily when one bit is added to each page table entry. Before a process wants to perform a critical action on an object, it first checks the lock-bit of that object. If the lock-bit is not set, the process sets the bit and performs its operation. It ends the operation by resetting the lock-bit. When the lock is set, the process has to wait until the lock-bit is reset by the other process, before it can perform the operation.

The two registers Objptr and Old\_Address are provided with a lock-bit too. When a critical action has to be performed on one of these registers, it is done in the same way as described above.

## 6.2.4. The First Solution

The search for reachable objects can be done by traversing the objects in the order in which they are encountered. The search starts with an object pointer from a processor source. The object associated with the pointer is scanned for object pointers. When a pointer is encountered its object is accessed. This sequence is continued until all objects that can be reached from one processor source are found. Now the next processor source is read and the search is initiated again. When an object pointer is encountered, the part of memory in which the object resides, determines where the object is copied to (if it needs to be copied).

The implementation of this search needs a stack-mechanism. When an object is reached, the algorithm decides whether the object is in the NewSpace, in the PastSurvivorSpace or in the OldArea. In the former two cases, the object has to be copied to FutureSurvivorSpace before scanning the object. In the latter case the object can be scanned immediately after setting the tagbit. The tag-bit tells whether an object is already scanned or not. In this way the algorithm makes sure that each object is scanned only once.

The object is scanned by testing each object location for being a non-compact object pointer, whose object has not been copied and scanned before (the tag-bit is not set). When such a pointer is found, and the corresponding object must be moved to another part of the memory, it is copied. Then the object number of the object in which the pointer was found and the index of the location at which it was found, are pushed onto the stack, and the found object pointer is loaded as the new object number. Scanning continues with this object after it is copied (if necessary).

When the end of an object is reached, the object number and the index are popped from the stack and scanning continues from this location. When the stack is empty, the next processor-source is read.

This generation scavenging implementation stops the scanning of a chain of objects when an object pointer whose object is on background is encountered. In this way the objects are found that are reachable without having to activate the DP. However not all live objects are found. This implementation works well for the NewArea. However dead objects from OldArea are not removed. The motivation for this was that the relative number of dead objects in the OldArea is smaller than the relative number of dead objects in the NewArea. The OldArea should be subjected to off-line garbage collection. This does not have to be done very often. This could for example be done at night, when no application program is running on the processor.

The reason why the choice is not fallen on this implementation of the generation scavenging algorithm is that the entire DRAM should be cleaned in parallel with the execution of the main processor. When for example the microprocessor is controlling a industrial process, there may not be time to perform off-line garbage collection of the OldArea. When the main memory is cleaned by the build-in garbage collector, the background memory can be kept clean by the disk processor, if necessary in co-operation with the garbage collector.

## 6.2.5. The Second Solution

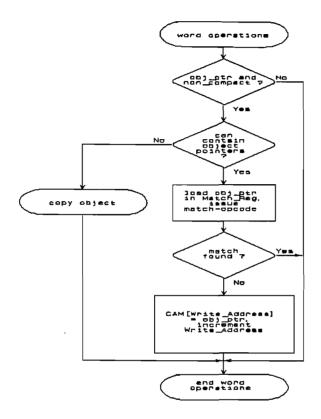

This implementation of the garbage collection algorithm takes advantage of the fact that not all objects can contain object pointers. In order to find all live objects, only the objects that can contain object pointers have to be scanned. For example instances of the class String can not

contain object pointers, they only contain numerical values. This selective search saves a considerable amount of time. To implement the selective search, one bit of the object pointer has to be dedicated to indicate whether the object can contain object pointers or not.

The generation scavenging algorithm consists of two main parts. The first part searches for live objects from the processor sources that can contain object pointers.

If a live object is found that can not contain object pointers, and if that object resides in NewSpace or PastSurvivorSpace, that object is copied to either FutureSurvivorSpace or OldArea (depending on the number of scavenges (NOS) it has survived).

When a live object is found that can contain object pointers, its object pointer is stored in a content addressable memory (CAM). A CAM is a combination of RAM and logic that is able to address a location on the basis of its content very fast (ideally one clock cycle).

The second part makes a sequential scan of the CAM, and performs the following operations on the associated objects. Note that all objects whose objects pointers are stored in the CAM, can contain object pointers and hence must be scanned.

The garbage collector reads in a word from the CAM. When the object is not in main memory, it has to be fetched from disk. Because it is not the purpose to increase the amount of objects in DRAM, the object may not be loaded. Every incoming word from the disk processor is checked to see if it is a non-compact object pointer of an object that can contain object pointers. If so it is stored in a fifo for later use. When all incoming words are checked, the garbage collector checks whether the words stored in the fifo, are in the CAM yet. If this is not the case the object pointer is added to the CAM. The intermediate fifo has to be used because the rate of incoming words is one per clock cycle.

When the object is in main memory, it is copied if necessary. Now the object is searched for other object pointers. Again object pointers of live objects that can contain other object pointers, and that are not already in the CAM are added to the CAM. Live objects that can not contain object pointers are copied immediately.

When all live objects are found and, if necessary, copied, the algorithm first cleans NewSpace, then PastSurvivorSpace, and finally it reorganizes OldArea.

At the end of a garbage collection cycle, all live objects are found. All dead objects are removed from main memory. The pager table-entries of all dead objects are re-initialised and the OldArea contains a contiguous chain of live objects.

What still has to be done is the garbage collection of the external (disk) memory. This part has to be done by the disk processor, which is beyond the scope of this thesis. A solution could be: The disk processor can administrate which objects are alive. This would only need a small extension to the generation scavenging algorithm. When a garbage collection cycle has finished, the disk processor knows which objects are alive and which are dead. It then can reorganize the disk.

# **6.3.** The Implementation of Generation Scavenging

The way the implementation of the garbage collector is obtained is as follows. First the algorithm is defined using flowcharts. This algorithm must be converted to hardware. The author has chosen to do this the same way as it is done in [Har88]. In this way a uniform description is obtained for both processes described in this thesis. An instruction set is made that can implement the

flowcharts. Each field of the control word controls a special piece of hardware. The hardware is developed to run the generation scavenging algorithm efficiently. Finally, the model of the garbage collector is developed. The model is described in chapter 7, together with the model of the object oriented memory manager.

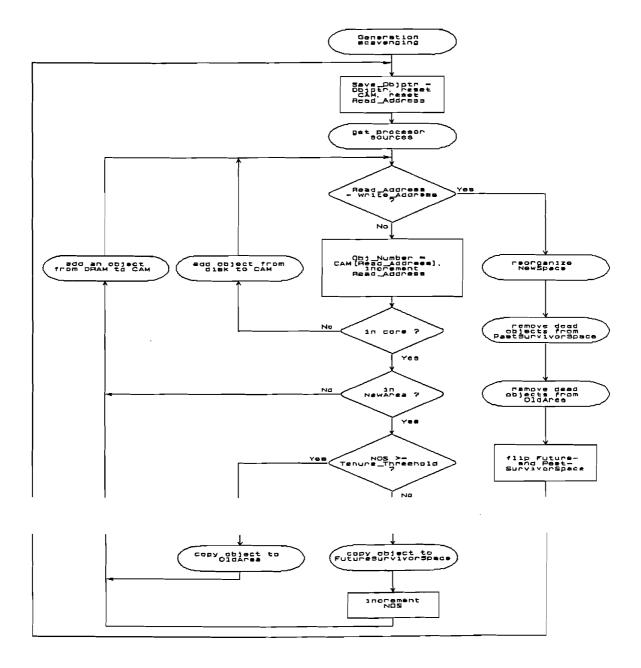

## 6.3.1. The Flowcharts