MASTER

Data structures and VLSI

Bink, J.M.

Award date: 1991

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

EB321 5864

Eindhoven University of Technology Department of Electrical Engeneering Digital Systems Group (EB)

## DATA STRUCTURES and VLSI

by J.M. Bink

Master Thesis Report Supervision: Prof. Ir. M.P.J. Stevens. Ir. L.P.M. Benders.

Eindhoven, August 1991

The Department of Electrical Engineering of Eindhoven University of Technology does not accept any responsibility regarding the contents of student project and graduation reports.

## <u>Summary</u>

For the description of problems, many high level description languages are known. Most of these languages are software languages. An easy way to describe problems is to use abstract data types, but then the translation to hardware is difficult. If we could find a hardware implementation for often used data types, it would become much easier to translate the problem description to hardware implementation.

I have searched in literature for data structures, which are often used for the description of problems. These data structures are described just like abstract data types. Research is done to software structures, used for the implementation of these given data structures. I have also studied algorithms which are used with the data structures (e.g. a search algorithm for trees). If we implement algorithms along with the data structures, faster implementations can be found.

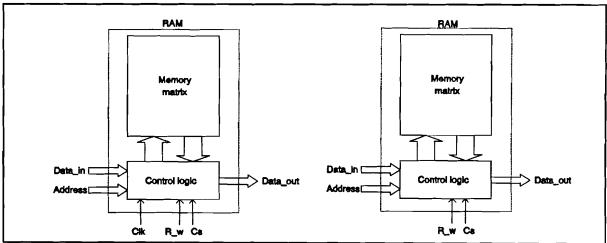

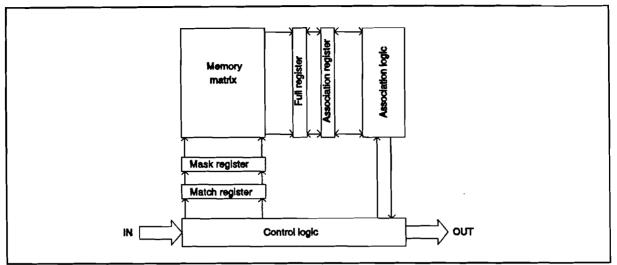

Then, two hardware memories (RAM and CAM) are described, which can be used for the implementation of the data structures in hardware. The CAM can besides storing information, also compare applied information with stored information. For some structures, like the table, the set and some graphs, the CAM gives a faster implementation than the RAM. There are also many CAM algorithms known for searching, sorting etc. The CAM however, is much more complex (size CAM is 3 to 4 times the size of the RAM).

Finally I have started with the hardware description of the data structures. This is done with the hardware description language VHDL. Because of the complexity and variety of the subject, I have not yet finished this.

For each data structure, several implementations are possible. Which implementation we should use depends on the use of the structure. Adding algorithms to the data structures improves the performance.

## Table of contents

|                                                  | . 1 |

|--------------------------------------------------|-----|

| 2. Data Structures                               |     |

| 2.1. Arrays                                      |     |

| 2.2. Records                                     |     |

| 2.3. Linked lists                                | . 3 |

| 2.4. Lists                                       | . 4 |

| 2.4.1. Stacks                                    |     |

| 2.4.2. Queues                                    |     |

| 2.5. Tables                                      |     |

| 2.6. Trees                                       |     |

| 2.7. Sets                                        |     |

| 2.8. Graphs                                      |     |

|                                                  | . J |

| 3. Software implementations and their complexity | 11  |

| 3.1. Arrays                                      | 11  |

| 3.2. Records                                     | 12  |

| 3.4. Lists                                       | 13  |

| 3.4.1. Implementations                           | 13  |

| 3.4.2. Algorithms                                | 15  |

| 3.4.3. Stacks                                    | 17  |

| 3.4.4. Queues                                    | 18  |

| 3.5. Tables                                      | 20  |

|                                                  | 20  |

|                                                  | -   |

|                                                  | 22  |

|                                                  | 23  |

| 3.7. Sets                                        | 26  |

| 3.7.1. Simple implementations                    | 26  |

| 3.7.2. Advanced implementations                  | 27  |

| 3.8. Graphs                                      | 32  |

| 3.8.1. Implementations                           | 32  |

| 3.8.2. Algorithms                                | 34  |

| 1 Desig hardware huilding blacks                 | ~-  |

| 4. Basic hardware building blocks                | 37  |

| 4.1. RAM                                         | 37  |

| 4.2. CAM                                         | 38  |

| 4.2.1. CAM applications                          | 44  |

| 5. Hardware implementations        | 45  |

|------------------------------------|-----|

|                                    | . – |

|                                    | 45  |

|                                    | 47  |

| 5.3. Record                        | 47  |

| 5.4. Linked list                   | 48  |

|                                    | 48  |

|                                    | 49  |

|                                    |     |

|                                    | 50  |

| 5.6. Table                         | 50  |

| 5.7. Tree                          | 51  |

|                                    | 52  |

|                                    | 52  |

| <b>5.5.</b> Graph                  | 52  |

| 6. Conclusions and recommendations | 54  |

| References                         | 55  |

| Appendix A                         | 57  |

# 1. Introduction

At the Digital Systems Group, Department of Electrical Engineering, Eindhoven University of Technology, research is done to the traject of developing digital systems. This is the traject of high level problem description to hardware implementation. If possible, this traject has to be automated. One of the topics is the high level description language, used for describing problems.

There are many ways to describe a problem, and there are many ways to implement the solution. An easy way to describe problems is to use software data structures. The main disadvantage of this solution is that these data structures are usually not known in hardware implementations. So if we could find a hardware implementation of often used data structures, it would become much easier to translate the problem description to hardware implementation.

My task was, under supervision of prof.ir. M.P.J. Stevens and ir. L.P.M. Benders, to inventorise the most commonly used data structures, and then I should try to find a good hardware implementation.

First, I have studied the most commonly used data structures, and described these like abstract data types.

Secondly I have studied software structures, used for the implementation of these data structures. Using these software implementations, we can construct abstract data types, which can be used for the description of problems. I have also looked for each data structure for algorithms, which are often used with that data structure.

I have studied some hardware memories, like a RAM and a CAM, which can be used for the implementation of the data structures in hardware.

Finally I have started with the hardware description of the data structures. Because of the complexity and variety of the subject, I haven't finished this. There is for every data structure a behavioral description. A structural description still have to be made. This should be done by someone else.

## 2. Data Structures

When we want to solute a problem, it is useful to have some predefined data structures, which makes it easy to describe the problem. This chapter is an overview of the most fundamental data structures, with a set of operations, used for the description of problems.

We study the elementary data structures array, record and linked list. We consider lists, which are sequences of elements, and two special cases of lists: stacks, where elements are inserted and deleted at one end only, and queues, where elements are inserted at on end and deleted at the other. Then we study tables, which is often used for the conversion of types. We study trees, which is a collection of elements with a hierarchical structure. We also study sets, which is closely related to the mathematical notion of a set. Finally we study graphs, which are often used for problems arising in computer science, mathematics, engineering, etcetera. We can use graphs to represent arbitrary relationships among data objects. We consider the basic data types (boolean, char, integer and real) known.

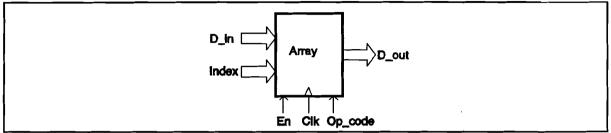

#### <u>2.1. Arrays</u>

An array is a collection of objects, all of the same type - called *elementtype* - and indexed by a *linear ordered* set of values - called the *index set*. The members of the index set are all of the same type, called the *index type*. There is a one-to-one correspondence between the value of the index type and the object of each array element. An array is often denoted as

A:  $array[i_1, \ldots, i_n]$  of elementtype;.

An array is a linear store, which has a finite number (n) of places with indexes i, with in each array element A[i] an object of the type elementtype. Elementtype can be of any type. The following operations are defined:

RETRIEVE(A,*i*,*c*): This operation reads element *i* of array A and assigns it to value *c*. This is often denoted as c := A[i]. This operation is not defined if  $i \le i_1$  or if  $i \ge i_n$ .

UPDATE(A,*i*,*c*): This operation assigns the value *c* to element *i* of array *A*. This often denoted as A[i] := c. This operation is not defined if  $i \le i_1$  or if  $i \ge i_n$ .

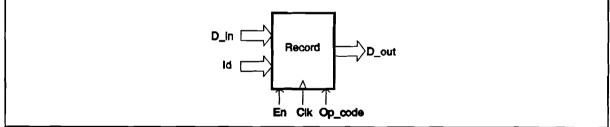

#### 2.2. Records

A record is a collection of objects, which may be of a different type, with for each object an identifier. There is a one-to-one correspondence between the record identifiers and the record elements. A record is often denote as

Each record has a finite number of identifiers  $id_n$ , with each identifier connected to an object of any type. We can define the following operations on the data structure record.

- RETRIEVE(R,id,v): This operation assigns to v the value of the component of R, which is identified by id. This is often denoted as v := R.id. This operation is not defined if the type of v is not equal to the type of R.id, or if id is not in R.

- UPDATE(R,id,v): This operation assigns the value v to component id of record R. This is often denoted as R.id := v. This operation is not defined if the type of v is not equal to the type of R.id, or if id is not in R.

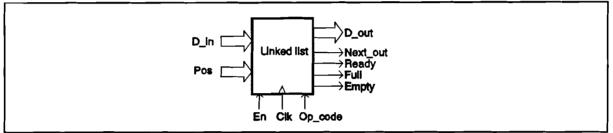

#### 2.3. Linked lists

In computer science, there are many applications in which the number of objects is changing dynamically. If we use for these applications static data structures, such as arrays or records, it would lead to inefficient use of memory space, and bad operations. So, it is useful to have a dynamic data structure.

Linked lists are the simplest form of dynamic data structures. A linked list is a list of pairs, each consisting of an element and a pointer, such that each pointer contains the address of the next pair. A pointer is simply a variable that holds as its value an address of another element. Each such pair is represented by a record. The following operations are defined:

CLEAR(LL): This operation makes the linked list LL to be an empty list.

- INSERT(LL, p, x): This operation creates a new record, fills it with data x, and links it on position p in linked list LL. If position p does not exist, this operation is not defined.

- DELETE(LL,p): This operation relinks linked list LL in such a way, that the record on position p in the list is no longer a member of list LL. If position p does not exist, this operation is not defined.

RETRIEVE(LL, p, x): Gives variable x the value of the data stored on position p of linked list LL. If position p does not exist, this operation is not defined.

NEXT(LL,p): This function returns the boolean true if there exist an element p + 1 of linked list LL, otherwise it returns false.

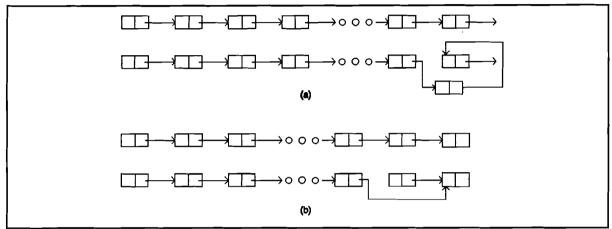

In figure 2.1. we see that the operations INSERT and DELETE are just a relinking of the pointers.

Figure 2.1. (a)Insert and (b) delete operation on linked list.

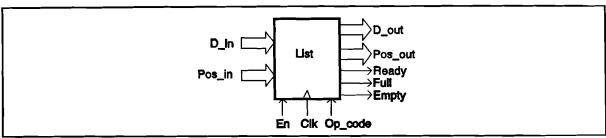

#### <u>2.4. Lists</u>

Mathematically, a list is a sequence of zero or more elements of a given type (which we generally call the elementtype). We often represent such a list by a comma-separated sequence of elements

a<sub>1</sub>,a<sub>2</sub>, . . . ,a<sub>n</sub>

where  $n \ge 0$ , and each  $a_i$  is of type elementtype. The number n of elements is said to be the length of the list. Assuming  $n \ge 1$ , we say that  $a_i$  is the first element and  $a_n$  is the last element. If n = 0, we have an empty list, one that has no elements. An important property of a list is that its elements have an ordering according to their position on the list. We say  $a_i$  precedes  $a_{i+1}$  for i = 1, 2, ..., n-1, and  $a_i$  follows  $a_{i+1}$  for i = 2, 3, ..., n. We say that the element  $a_i$  is at position i.

There is another ordering, which is often used. That is an ordering on the 'magnitude' of the elements. Then,  $|a_i| \le |a_{i+1}|$ . A list ordered by position we call 'unordered' and a list ordered by magnitude we call 'ordered'. On the data structure 'unordered' list we can define a set of operations. This is not a unique set of operations, but we try to give a complete set.

- CLEAR(L): This function causes L to become an empty list.

- END(L,p): The function END(L) will assign to p the position following position n in a *n*-element list L. Note that the position END(L) has a distance from the beginning of the list that varies as the list grows or shrinks, while other positions have a fixed distance from the beginning of the list.

- INSERT(L, p, x): Insert x at position p, moving elements at p and following positions to the next higher position. That is, if L is  $a_1, a_2, \ldots, a_n$  then L becomes  $a_1, a_2, \ldots, a_{p-1}, x, a_p, \ldots, a_n$ . If p is END(L), then L becomes  $a_1, a_2, \ldots, a_n, x$ . If list L has no position p, the result is undefined.

- LOCATE(L,p,x): This functions returns the position of x on list L. If x appears more than once, then the position of the first occurrence is returned. If x does not appear at all, then END(L) is returned.

- RETRIEVE(L,p,x): This function returns to x the element at position p on list L. The result is undefined if p = END(L) or if L has no position p.

- DELETE(*L*,*p*): Delete the element at position *p* of list *L*. If *L* is  $a_1, a_2, \ldots, a_n$ , then *L* becomes  $a_1, a_2, \ldots, a_{p-1}, a_{p+1}, \ldots, a_n$ . The result is undefined if *L* has no position *p* or if p = END(L).

- FIRST(L,p): This function returns to p the first position on list L. If L is empty, the position returned is END(L).

- EMPTY(L): Return true if list L is empty, return false otherwise.

- FULL(*L*): Return true if list *L* is full, return false otherwise.

With this set of operations it is possible to describe all possible manipulations on 'unordered' lists. If we want to define an 'ordered' list, we have to replace INSERT(L,p,x) by INSERT(L,x). Element x is inserted 'in order' and not on position p.

#### 2.4.1. Stacks

A stack is a special list in which all insertions and deletions take place at one end, called the *top*. Other names for a stack are "pushdown list", and "LIFO" or "last-in-first-out" list. The intuitive model of a stack is a pile of poker chips on a table, books on a floor, or dishes on a shelf, where it is only convenient to remove the top object on the pile or add a new one above the top. We can define here a set of basic operations.

- CLEAR(S): This function causes S to become an empty stack. This operation is the same as for general lists.

- TOP(S,x): Return to x the element at the top of stack S. If, as is normal, we identify the top of a stack with position 1, then TOP(S,x) can be written in terms of list operations as RETRIEVE(S,FIRST(S),x).

- POP(S,x): Delete the top element of the stack, that is, DELETE(S,FIRST(S)). Sometimes it is convenient to implement POP as a function that returns the element it has just popped. Then, we don't need the function TOP(S).

- Data structures -

- PUSH(S,x): Insert the element x at the top of stack S. The old top element becomes next-to-top, and so on. In terms of list operations this operation is INSERT(S,FIRST(S),x).

- EMPTY(S): Return true if S is an empty stack; return false otherwise.

- FULL(S): Return true if S is a full stack; return false otherwise.

#### 2.4.2. Queues

A queue is an other special list, where items are inserted at one end (the rear) and deleted at the other end (the front). Another name for a queue is a "FIFO" or "first-in-first-out" list. The operations for a queue are similar to those for a stack, the substantial differences being that insertions go at the end of the list, rather than the beginning, and that the traditional terminology for stacks and queues is different. We shall use the following basic operations on queues.

CLEAR(Q): Makes queue Q an empty list.

- FRONT(Q,x): This is a function that returns the first element on queue Q. FRONT(Q,x) can be written in terms of list operations as RETRIEVE(Q,FIRST(Q),x).

- ENQUEUE(Q,x): This function inserts element x at the end of queue Q. In terms of list operations, ENQUEUE(Q,x) is INSERT(Q,END(Q),x).

- DEQUEUE(Q,x): This function deletes the first element of Q; that is, DEQUEUE(Q,x) is DELETE(Q,FIRST(Q)). It is also possible to combine FRONT and DEQUEUE in a single operation. Then, we don't need the operation FRONT.

- EMPTY(Q): Returns true if and only if Q is an empty queue.

- FULL(Q): Returns true if and only if Q is a full queue.

#### 2.5. Tables

A table is a collection of *keyed* records, with for every record a *unique* key. When we want to retrieve a record, we look in the table for the key. If the key is found, that record is retrieved. Sometimes there is used a translation mechanism on the key for computing the address of the record. The following operations are defined:

CLEAR(T): Makes table T to be an empty table.

INSERT(T, id, x): Inserts data x with identifier *id* in table T. If *id* already exist in table T, the data connected with *id* is replaced by x.

- DELETE(*T*,*id*): Deletes the record with key *id* from table *T*. If *id* is not a MEMBER of table *T*, nothing happens.

- RETRIEVE(T, id, x): Returns the data to x from the record with key id, from table T. If id is not a MEMBER of table T, nothing happens.

- MEMBER(*T*,*id*): Returns TRUE if the record with key *id* is in hash table *T*.

- FULL(*T*): Returns true if table *T* is full; returns false otherwise.

EMPTY(T): Returns true if table T is empty; returns false otherwise.

## 2.6. Trees

A tree imposes a hierarchical structure on a collection of items. A tree is a collection of elements called *nodes*, one of which is distinguished as a *root*, along with a relation ("parenthood") that places a hierarchical structure on the nodes. A node, like an element of a list, can be of whatever type we wish. We often depict a node as a character, a string or a number with a circle around it. Formally a *tree* can be defined recursively in the following manner.

- 1. A single node by itself is a tree. This node is also the root of the tree.

- 2. Suppose *n* is a node and  $T_1, T_2, \ldots, T_k$  are trees with roots  $n_1, n_2, \ldots, n_k$ , respectively. We can construct a new tree by making *n* be the parent of nodes  $n_1, n_2, \ldots, n_k$ . In this tree *n* is the root and  $T_1, T_2, \ldots, T_k$  are sub-trees of the root. Nodes  $n_1, n_2, \ldots, n_k$  are called the *children* of node *n*.

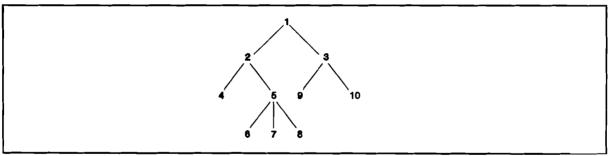

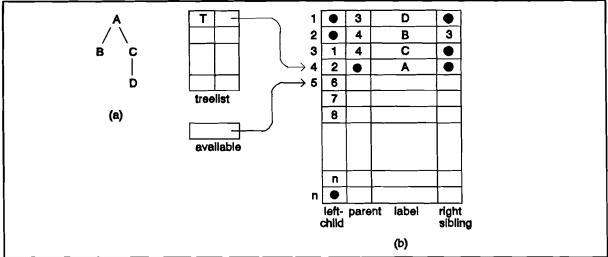

Sometimes it is convenient to include among trees the *null tree*, a "tree" with no nodes, which we shall represent by  $\bullet$ . It is possible to define an order on the nodes of a tree. Then, all the children of a node are assigned a different order. This depends on the implementation of a tree. In a graphic representation of a tree, the children of a node are usually ordered from left to right (see figure 2.2.).

Figure 2.2. Graphic representation of a tree.

The ancestors of node n are defined as following: If node n is the root of a tree, then it has no ancestors. Else, the parent of n and all the ancestors of the parent of n are ancestors of n. The descendants of node n are: If node n is a leaf of a tree, it has no descendants. Else, the children of node n and all the descendants of the children of n are descendants of n.

We can associate a *label*, or value, with each node of a tree, in the same way as we associated a value with a list element. That is, the label of a node is not the name of the node, but an object that is "stored" at the node. Now we shall present several useful operations on trees. As with lists, there are a great variety of operations that can be performed on trees. Here, we shall consider the following operations:

CLEAR(T): Makes T the null tree.

- PARENT(T,n,x): This function returns to x the parent of node n in tree T. If n is the root, which has no parent,  $\bullet$  is returned. In this context,  $\bullet$  is a "null node", which is used as a sign that we have navigated off the tree.

- LEFT\_CHILD(T,n,x): Returns to x the child of node n in tree T with the lowest order, and returns • if n is a leaf, which has no children.

- RIGHT\_SIBLING(T,n,x): Returns to x the right sibling of node n in tree T, defined to be that node m with the same parent p as n such that m has the lowest ordering, following n in the ordering of the children of p.

- LABEL(*T*,*n*,*I*): This function returns to *I* the label of node *n* in tree *T*. We do not, however, require labels to be defined for every tree.

- CREATE( $T_i, T_1, T_2, \ldots, T_i, I$ ): This is an infinite family of functions, one for each value of  $i = 0, 1, 2, \ldots$  CREATE makes a new node r with label I and give it i children, which are the roots of trees  $T_1, T_2, \ldots, T_i$ , in order from the left. The tree T with root r is returned. Note that if i = 0, then r is both a leaf and the root.

- ROOT(T,x): This function returns to x the node that is the root of tree T, or  $\bullet$  if T is the null tree.

There are special trees, such as binary trees, AVL trees, B-trees and tries, which often have a special set of operations. See also [AHO83], [COR90], [MAN89] and [WAR90]. These operations are usually combinations of operations described above. However, it can be useful to define for each data structure its own operation set.

#### 2.7. Sets

As we said before, the set is the basic structure underlying all mathematics. A set is a collection of *members* (or *elements*); each member of a set either is itself a set or is a primitive element called an *atom*. All members of a set are different, which means no set can contain two copies of the same subset. We can denote a set of atoms by putting curly brackets around its members. A set with only the members 1, 3 and 4 is denoted as:

$\{1,3,4\}$  or  $\{1,4,3\}$  or  $\{4,3,1\}$  etc.

Sometimes, atoms are linearly ordered by a relation, usually denoted by "<". In that case, a *linear order* < on a set S satisfies two properties:

- 1. For any *a* and *b* in *S*, exactly one of a < b, or b < a is true.

- 2. For all a, b, and c in S, if a < b and b < c, then a < c (transitivity).

We can give a set of operations on the data structure set, but this is not a unique set.

Data structures

- UNION(A,B,C): This operation takes the set-valued arguments A and B, and assign the result A U B to the set variable C.

- INTERSECTION(A, B, C): This operation takes the set-valued arguments A and B, and assign the result  $A \cap B$  to the set variable C.

- DIFFERENCE(A,B,C): This operation takes the set-valued arguments A and B, and assign the result A B to the set variable C.

CLEAR(A): Makes the null set to be the value for set variable A.

- MEMBÈR(A,x): Takes set A and object x, whose type is the type of elements of A, and returns a boolean value true if  $x \in A$  and false if  $x \notin A$ .

- INSERT(A,x): Makes element x a member of set A. That is, the new value of A is  $A \cup \{x\}$ . Note that if x is already a member of A, INSERT(x,A) does not change A.

- DELETE(A,x): Removes element x from set A, i.e., A is replaced by A {x}. If x is not in A originally, DELETE(x,A) does not change A.

- ASSIGN(A,B): Sets the set value of set variable A to be equal to the value of set variable B.

- EQUAL(*A*,*B*): This function returns the value true if and only if sets *A* and *B* consist of the same elements.

- MIN(A): This function returns the smallest element in set A. This operation may only be applied when the members of the parameter set are linearly ordered.

- MAX(A): This function returns the greatest element in set A. This operation may only be applied when the members of the parameter set are linearly ordered.

#### <u>2.8. Graphs</u>

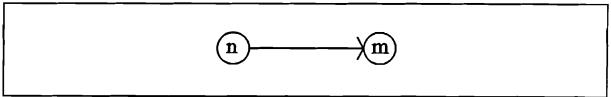

Directed and undirected graphs are models for representing arbitrary relationships among data objects. A *directed graph* (*digraph* for short) *G* consists of a set of nodes *N* and a set of edges *E*. The nodes are also called *vertices* or *points*; the directed edges could be called *arcs* or *directed lines*. A directed edge is an ordered pair of nodes (n,m); *n* is called the *tail* and *m* the *head* of the edge. The directed edge (n,m) is expressed by  $n \rightarrow m$  (figure 2.3).

Figure 2.3. A directed graph.

The nodes of graph G are used to represent objects, and the arcs or directed edges are used to represent relationships between objects. Common operations on this data structure are:

- INSERT\_NODE(G,n,I): Makes a new node *n* with label *I* in graph *G*. This node is not connected to graph *G*.

- INSERT\_EDGE(G,n,m,I): Creates in graph G a directed edge from node n to node m which has the label I. This operation is undefined if n or m are no nodes of graph G.

- DELETE\_NODE(G,n): Deletes node *n* from graph G. There are no edges between node *n* and the rest of graph G.

- DELETE\_EDGE(G,n,m): Deletes in graph G the directed edge between node n and node m. Both n and m are elements of the set nodes of graph G, else this operation has no effect.

- RETRIEVE\_EDGE(G, n, m, l): This function returns to l the label of the directed edge between node n and node m in graph G. If there is no edge between nand m or these nodes are not in G, this function returns the null label  $\bullet$ .

- RETRIEVE\_NODE(G,n,l): This function returns to l the label of node n in graph G. If node n is not in G, then the null label  $\bullet$  is returned.

- CLEAR(G): Makes G to be a graph with no nodes and no edges (null graph).

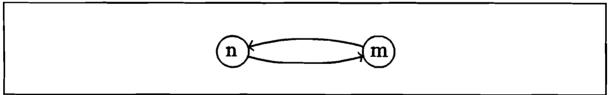

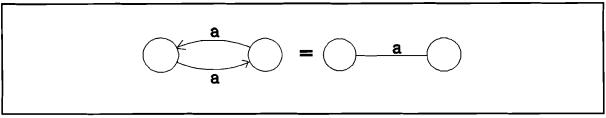

We represented only the directed graphs, because the undirected graphs can be implemented as directed graphs. An undirected edge can be represented as two directed edges in the opposite direction. See figure 2.4.

Figure 2.4. Undirected graph.

In this chapter we gave a definition of the data structure, and an overview of the (basic) operations on that data structure. It isn't always possible to define a 'best' set of operations for a data structure, but we tried to give a complete set of operations. It is possible that an other set of operations gives an easier or faster implementation. It is also known that a set of operations can be optimal for one problem, but not for another problem. For more information about data structures and algorithms see [AHO83], [COR90], [MAN89], [SED88], [STU85], [WAR90] and [WUL81]. In the next chapter, we will give some commonly used software implementation, and some algorithms used on these data structures.

# 3. Software implementations and their complexity

If we look at the most commonly used software languages, we see that only a few data structures are available (e.g. array, record, pointer). The other structures have to be implemented with these available structures. If all discussed data structures would be available for the programmer, it would be much easier to implement solution for a problem. For that reason, many languages support *abstract data types*. This are modules, which contain a data structure with its predefined operations. Then, if they use these modules, they have all data structures available.

This chapter gives an overview of the software implementation of the data structures. With every data structure we have given its characteristics and possible mappings to elementary structures (arrays, records and linked-lists). For every mapping, we discuss the complexity of the predefined operations, and we examine algorithms, which are often used with the data structure.

#### <u>3.1. Arrays</u>

An array is a row of elements of the same type. The size of the array is the number of elements in the array. This size must be fixed. The array is a storage type that is direct accessible, i.e. we can retrieve or update every single element of the array in a fixed time. In almost every software-language the array is a predefined data type. For the implementation of the array no extra memory space is necessary, but the size and type of the array should be defined before use. Because the array is a direct accessible storage type, the predefined operations 'RETRIEVE' and 'UPDATE' have a complexity O(c) (table 1).

| Table | 1: | Array | characteristics |

|-------|----|-------|-----------------|

|-------|----|-------|-----------------|

| ARRAY      |            |  |

|------------|------------|--|

| Operations | Complexity |  |

| UPDATE     | O(c)       |  |

| RETRIEVE   | O(c)       |  |

| Access     | Direct     |  |

| Size       | Fixed      |  |

Arrays cannot be used to store elements of different types (or sizes), and the size of an array cannot be changed dynamically.

#### 3.2. Records

A record is a list of elements of different types. The exact combination of types has to be defined before use. The storage size of a record is known in advance. Records are a predefined type in many programming languages. Each element of a record can be accessed in a fixed time. This is often done using an indirection. The names of the record elements are stored in a table with the same number of elements, such that for each element the table contains its starting location. This table is automatically created by the compiler. The characteristics of an array are listed in table 2.

| Re         | ecord      |

|------------|------------|

| Operations | Complexity |

| UPDATE     | O(c)       |

| RETRIEVE   | O(c)       |

| Access     | Direct     |

| Size       | Fixed      |

Table 2: Record characteristics

Like an array, the size of a record cannot be changed dynamically, but we can store elements of a different type in it.

#### 3.3. Linked lists

Linked lists are the simplest form of dynamic data structures. Each element is represented separately, and all elements are connected by pointers (see figure 2.1). A pointer is a variable that holds as its value the address of another element.

There are two major drawbacks to the linked list representation. First it requires more memory space. There is one additional pointer per element. Secondly, if we want to look at the, for example, 30th element, we start at the beginning and look at 29 pointers, one at a time. With arrays, we make a simple calculation and find the 30th element quickly. The characteristics of the linked list are listed in table 3.

| Linked list           |            |  |  |

|-----------------------|------------|--|--|

| Operations Complexity |            |  |  |

| CLEAR                 | O(c)       |  |  |

| INSERT                | O(n)       |  |  |

| DELETE                | O(n)       |  |  |

| RETRIEVE              | O(n)       |  |  |

| NEXT                  | O(c)       |  |  |

| Access                | Sequential |  |  |

| Size                  | Dynamic    |  |  |

| Table 3. | Linked | list | characteristics |

|----------|--------|------|-----------------|

|----------|--------|------|-----------------|

c = constant, n = number of elements in linked-list.

The data structures array, record and linked list and pointer are the basic data structures, and are predefined in many programming languages. They are used in a wide range of applications. The following data structures are more complex can be created by a mapping to the basic data structures.

#### <u>3.4. Lists</u>

A list is a sequence of elements with a certain ordering. Lists are a particularly flexible structure because they can grow and shrink on demand, and elements can be accessed, inserted, or deleted at any position within a list. Lists arise in applications such as information retrieval, programming language translation, and simulation.

Lists have a certain ordering. The ordering defined in chapter 2 was an ordering by position. In algorithms however, there is often an ordering by 'magnitude'. Then, the insertion of an element is not on a fixed position, but on a place where it fits by its magnitude. The first, we will call an 'unordered' list (The list is ordered by position, but the 'magnitude' of the elements is unordered), and the second an 'ordered' list.

#### 3.4.1. implementations

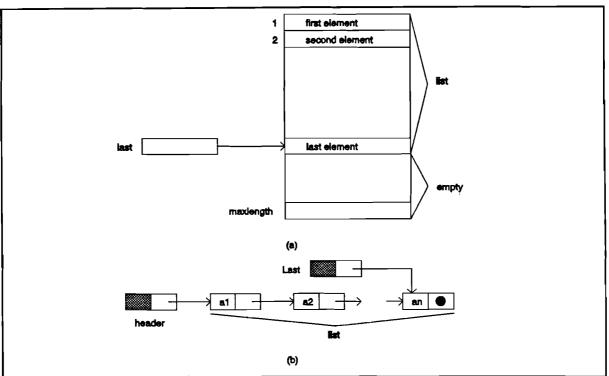

For the implementation of lists, there are two methods commonly used. That is, the list is mapped on an array, or the list is mapped on a linked list (see figure 3.1). The advantage of the first method is that all elements are direct accessible, but the size of the list has a fixed upper bound. The advantage of the second method is that the size of the list has no upper-bound, but the access to the list is sequential.

Figure 3.1. (a) Array and (b) linked list implementation of a list.

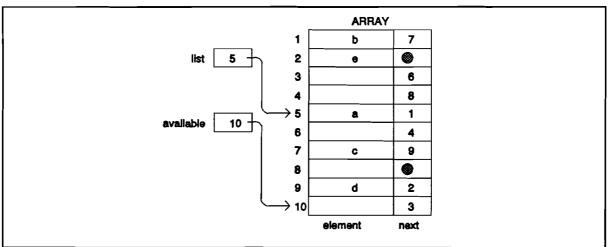

A third mapping, which is used very little, is interesting for a mapping to hardware. This method is called a cursor implementation, and simulates the linked list implementation (see figure 3.2). The list is mapped on an array, which contains record elements. The first record entry contains the data, while the second entry contains an index (cursor) to the next array entry of the list. The head of the list is stored in a separate variable, while a second list contains the available array elements.

Figure 3.2. Cursor implementation of a list.

All three representations make it possible to implement the operations. The characteristics are given in table 4.

#### Table 4: List characteristics

|            | List        |             |             |            |  |

|------------|-------------|-------------|-------------|------------|--|

|            |             | Complexity  |             |            |  |

| Implement. | An          | ray         | Linked list |            |  |

| Operation  | Ordered     | Unordered   | Ordered     | Unordered  |  |

| CLEAR      | O(c)        | O(c)        | O(c)        | O(c)       |  |

| INSERT     | O(n)        | O(n)        | O(n)        | O(n)       |  |

| LOCATE     | O(log n)    | O(n)        | O(n)        | O(n)       |  |

| RETRIEVE   | O(log n)    | O(c)        | O(n)        | O(n)       |  |

| DELETE     | O(n)        | O(n)        | O(n)        | O(n)       |  |

| FIRST      | O(c)        | O(c)        | O(c)        | O(c)       |  |

| END        | O(c)        | O(c)        | O(c)        | O(c)       |  |

| EMPTY      | O(c)        | O(c)        | O(c)        | O(c)       |  |

| FULL       | O(c)        | O(c)        |             |            |  |

| Access     | Direct/Seq. | Direct/Seq. | Sequential  | Sequential |  |

| Size       | Fixed       | Fixed       | Dynamic     | Dynamic    |  |

c = constant, n = number of elements in list.

For the LOCATE and RETRIEVE operation of the sorted array implementation, a search algorithm (binary search) is used.

#### 3.4.2 Algorithms

The two major problems for lists are -- search an element and -- sort the list. Several algorithms have been developed for these problems, which will not be discussed, but the use and complexity will be given.

For 'unsorted' lists or lists implemented by a linked list, searching for an element is only possible by a linear search.

For an 'ordered' list implemented by an array, there are several algorithms known for searching. Often used algorithms are:

- Linear search: The algorithm inspects all elements of the list, one by one, for a searched element and decides whether the element is found. The complexity is O(n). This algorithm is used when the list contains few elements (n is small).

- Binary search: The algorithm looks at the element in the middle position of the list. If the searched element is smaller than the middle element, than it is positioned in the first half of the list, else in the second half. Then we repeat this search with the half (sub)list that contains the element etc. The complexity of this algorithm is O(log n). This algorithm is used when the list contains much elements (n is big).

- Interpolation search: This algorithm guesses by interpolation the position of the searched element. If the searched element is smaller than the element on the guessed position (pivot), the operation is repeated on the first part of the list, else on the second part. This operation is repeated until the search is successful, or the element is not in the list. The complexity of this algorithm is O(log log n). This algorithm is only this good if the elements are uniformly distributed (i.e. equally distributed). Otherwise, the binary search is just as good or even better than interpolation search.

Several algorithms are known for the sorting of an 'unordered' list, which is implemented by an array. Often used algorithms are:

- Radix sort: (Bucket sort) The elements of a list are retrieved and then sorted in a number of buckets, depending on a part of the element. For example, if we want to sort numbers from 100 to 999, we can sort first on the first digit and put the resulting lists in buckets. Then we know that the first bucket contains a list with the elements form 100 to 199. We continue the sorting by looking to the next digit, etc. The complexity of this method is O(nk), where n is the number of elements and k is the number of search iterations. This method is not 'in place' i.e., there is extra storage necessary.

- Insertion sort: This algorithm divides the list in two parts, a sorted part and an unsorted part. Then it takes the first element of the unsorted and inserts it on it's correct position in the sorted part. This algorithm has the complexity O(n<sup>2</sup>) and is 'in place'.

- Selection sort: This algorithm divides the list also in two parts. It takes the maximum unsorted element and adds it to the beginning of the sorted list. The algorithm is 'in place' and the complexity is O(n<sup>2</sup>).

- Merge sort: This algorithm splits the list into two equal or close-to-equal parts. Then, each part is sorted recursively. Finally, the two sorted parts are merged (sorting by picking each time the smallest element of both lists, i.e. the first element of one of the lists) into one sorted list. The complexity of this 'divide and conquer' algorithm is O(n log n). This is good, but the algorithm is not 'in place', and it is difficult to implement.

- Quicksort: This algorithm is also a 'divide and conquer' algorithm. We do not divide the list in two equal parts, but we choose element value (pivot). The elements of the list are swapped, so that all elements smaller than the pivot are in the first part of the list and elements larger than the pivot are in the second part of the list. Then the algorithm is applied to both subparts. Finally all element will be sorted. If we choose the pivot well (the parts should be equal) than we have an algorithm of complexity O(n log n). If we choose the pivot bad, it goes to O(n<sup>2</sup>).

We should keep in mind, that we can use these algorithms for all data structures thatwhich use a list, implemented by an array. For an exact description of these algorithms, you should see [AHO83], [SED83], [MAN89] and [WAR90].

#### 3.4.3. Stacks

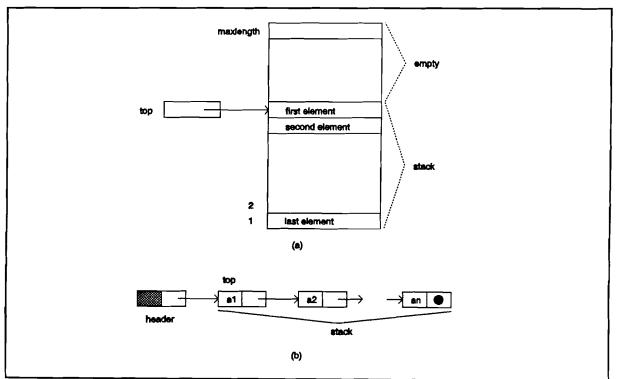

The stack is a special list in which all insertions and deletions take place at one end, called the top. Because the stack is a list, any list implementation can be used for a stack. The restrictions of the stack make it much easier to implement a stack in software. The stack is usually mapped on an array, with an extra variable to hold the end of the list. It is also possible to map a stack on a linked list, with a cursor to the top element, but this encounters less frequently (see figure 3.3.).

Figure 3.3. (a) Array and (b) linked list implementation of a stack.

The characteristics of the stack are presented in table 5. Normally spoken, the access to a linked list structure is sequential, but we only insert and retrieve elements at the front of the list, and so we need only one access to insert or retrieve an element. That's why the access to the linked list in this case is called direct. The linked list implementation is more difficult to implement, and it uses per element additional storage space.

|           | Stack<br>Complexity |             |  |

|-----------|---------------------|-------------|--|

|           |                     |             |  |

| Operation | Аггау               | Linked list |  |

| CLEAR     | O(c)                | O(c)        |  |

| ТОР       | O(c)                | O(c)        |  |

| POP       | O(c)                | O(c)        |  |

| PUSH      | O(c)                | O(c)        |  |

| EMPTY     | O(c)                | O(c)        |  |

| FULL      | O(c)                |             |  |

| Access    | Direct              | Direct      |  |

| Size      | Fixed               | Dynamic     |  |

#### Table 5: Stack characteristics

Stacks are used for controlling the recursive procedures in programming languages. Stacks are automatically created and destroyed by the host of the process, store state data and other data temporarily, while another (or the same) process is called. After finishing the called process, the stopped process can continue in its old state by retrieving it's state data from the stack. Stacks are also often used in language compilers implementations.

#### 3.4.4. Queues

A queue is another special list, where the items are inserted at one end of the list( the rear) and deleted at the other end of the list (the front). As for stacks, any list implementation is possible for queues, but we can take advantage of the fact that insertions are only done at the rear and deletions are only done at the front. We can keep a pointer (or cursor) to the first and last element of the list. This makes it possible to implement the operations on the queue much more effective.

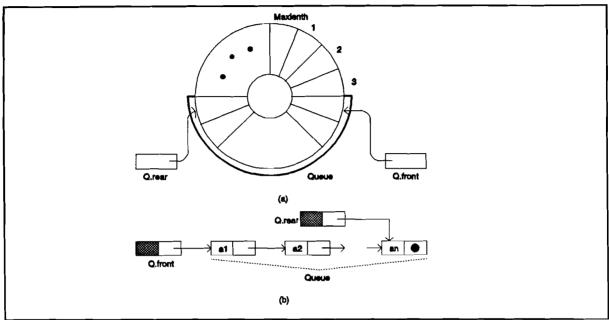

We can implement the queue with an array and a linked list. We use a circular array, to make optimal use of the memory space. Both implementations are shown in figure 3.4. The characteristics of the queue are found in table 6.

Figure 3.4. (a) Circular array and (b) linked list implementation of a queue.

|            | Queue      |             |  |

|------------|------------|-------------|--|

|            | Complexity |             |  |

| Operations | Array      | Linked list |  |

| CLEAR      | O(c)       | O(c)        |  |

| FRONT      | O(c)       | O(c)        |  |

| ENQUEUE    | O(c)       | O(c)        |  |

| DEQUEUE    | O(c)       | O(c)        |  |

| EMPTY      | O(c)       | O(c)        |  |

| FULL       | O(c)       | -           |  |

| Access     | Direct     | Direct      |  |

| Size       | Fixed      | Dynamic     |  |

<u>c = constant.</u>

Queues are mostly used as buffer between two processes, which communicate with each other.

## <u>3.5. Tables</u>

A table is a list of records with two different fields, i.e. the key field and the data field. Tables are mostly used for converting data of one type to another type. For example, we can think of a video memory, with for every pixel (=position) an intensity and a colour. The key is the pixel position and the data is the colour and intensity. The key of every record is unique, which makes it possible to identify every record of the table. The table is addressed by the key of a record, so if we want to retrieve a record with key K, then we have to look in the table for the record with key K.

#### 3.5.1 Implementations

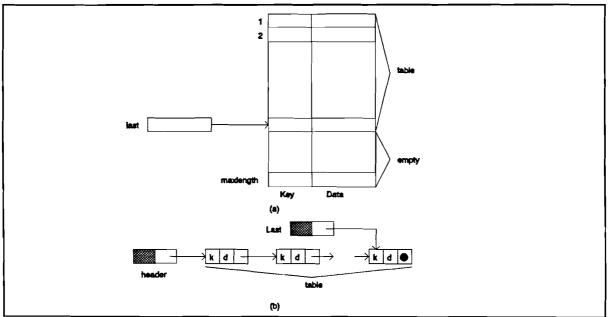

There are several software implementations for a table. The first one is a mapping to an array of records. It is also possible to map the table to a linked list of records. Both implementations are shown in figure 3.5.

Figure 3.5. (a) Array and (b) linked list implementation table.

For every INSERT, DELETE, RETRIEVE and MEMBER operation we have to search the whole list, so the complexity of most of the operations is O(n), which is not good for a table (tables are often used for fast reference). But there is an other implementation technique, called *hashing*. Then, the key is translated by a translation function to an address. We call such a translation function a *hash function*. It can occur that the computed address does not contain the record being sought, but an other record with a different key. When this happens, a search of other addresses is required, and this is known as *rehashing*. It is important that the hash function satisfies the following properties:

- 1. They compute rapidly.

- 2. They produce a random distribution of index values.

It is difficult to find a *perfect hashing function*. To find a good hashing function, it is necessary to know all possible keys and the available memory space in advance. With a hash table it is possible to retrieve and insert records in a fast way.

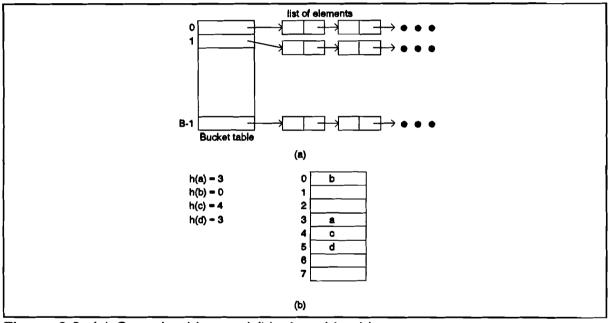

There are two implementations of hashing, open or external hashing and closed or internal hashing. In figure 3.6.(a). we see the basic structure for open hashing.

Figure 3.6. (a) Open hashing and (b) closed hashing.

The input set (keys) is divided in a finite number of classes. The partitioning is done by a hash function h(x), which computes the bucket number 0..B-1 where the record is stored. Each bucket contains a pointer to a linked list, containing records. We need a constant amount of time to find the bucket, and a small amount of time to find the record in the linked list. For a good performance, we have to choose a hash function that gives a random distribution of elements over the buckets, and the number of buckets *B* has to be greater than n/2.

The closed hashing structure is simpler (figure 3.6.(b)), but the hashing strategy is more complicated. Now if we want to insert an element and we have computed the address of a record, it is possible that this address is occupied by an other record.

Then we have to *rehash* and find an other place where we can store the record. We can use a *rehash function* or use a simple strategy by picking the first free place. This last strategy is used in the example of figure 3.6.(b).

If next an element is not on its computed address, we have to look at the addresses, until an empty place is reached. If in the meanwhile an element is deleted, it is possible that we reach an empty place, before we reach the searched element. That is why we have to mark places of deleted elements. For a good performance, we have to choose a good hash function, and the size of the table should be greater than 1.1\*B. See also [AHO83], [KOH87]. The characteristics of each implementation, and the complexity of the operations is given in table 7.

|                | Table      |                             |                              |                   |  |  |

|----------------|------------|-----------------------------|------------------------------|-------------------|--|--|

|                |            | Complexity / representation |                              |                   |  |  |

| Implementation | Array      | Linked<br>list              | Open<br>hashing <sup>*</sup> | Closed<br>hashing |  |  |

| CLEAR          | O(c)       | O(c)                        | O(B)                         | O(B)              |  |  |

| INSERT         | O(n)       | O(n)                        | O(c+n/B)                     | O(c+1/(1-n/B)     |  |  |

| DELETE         | O(n)       | O(n)                        | O(c+n/B)                     | O(c+1/(1-n/B)     |  |  |

| RETRIEVE       | O(n)       | O(n)                        | O(c+n/B)                     | O(c+1/(1-n/B)     |  |  |

| MEMBER         | O(n)       | O(n)                        | O(c+n/B)                     | O(c+1/(1-n/B)     |  |  |

| FULL           | O(c)       |                             | _                            | O(c)              |  |  |

| EMPTY          | O(c)       | O(c)                        | O(c)                         | O(c)              |  |  |

| Access         | Sequential | Sequential                  | Direct/Seq.                  | Direct/Seq.       |  |  |

| Size           | Fixed      | Dynamic                     | Dynamic                      | Fixed             |  |  |

#### Table 7: Table characteristics

c = constant, n = number of elements in table.

\* B = number of buckets (open) c.q. size of hash table (closed).

#### <u>3.6. Trees</u>

A tree imposes a hierarchical structure on a collection of items. Familiar examples of trees are organization charts. Trees are used to analyze electrical circuits and to represent the structure of mathematical formulas. Trees also arise naturally in many different areas of computer science. For example, trees are used to organize information in database systems and to represent the syntactic structure of source programs for compilers.

#### 3.6.1 Implementations

There are many different variants of trees, and each tree has its own optimized set of operations. But first of all, we'll discuss some implementations of the tree defined in chapter 2. These implementations are mostly a mix of an array and a linked list implementation, to make the operations as effective as possible.

We suppose that the nodes are named 1,2,3,..,n. This numbering can be random, but we suppose that we start numbering with number 1 and stop with number n for a tree with n nodes.

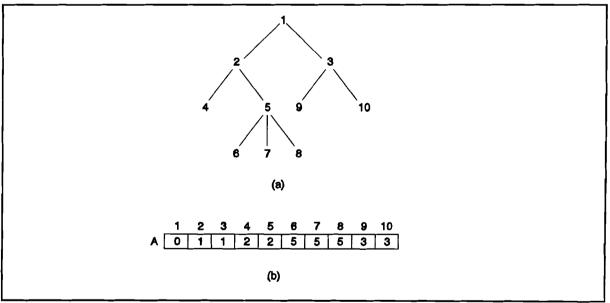

The array implementation of a tree uses the property that each node has a unique parent. The parent of every node is stored in an array. The root, which lacks a parent, will point to a null node. With this representation the operation PARENT, which looks for the parent of a node, can be executed in fixed time. A path going up the tree, that is, from node to parent to parent, and so on, can be traversed in a time proportional to the number of nodes on the path. We support the LABEL operator by adding another array L, such that L[i] is the label of node i, or by defining the elements of array A to be records consisting of an integer (cursor) and a label. An example of such an implementation is given in figure 3.7.

Figure 3.7. (a) A tree and its (b) parent pointer representation.

Such a parent representation does not facilitate operations that require child-of information. Given a node n, it is expensive to determine the children of n, and the implementation does not specify the order of the children of the node. Thus, operations like LEFT\_CHILD and RIGHT\_SIBLING are not well defined. We could impose an artificial order, for example, by numbering the children of each node after

numbering the parent, and numbering the children in increasing order from left to right. Then the operations LEFT\_CHILD and RIGHT\_SIBLING are defined. The operations PARENT, LABEL, ROOT and CLEAR are also defined, but the operation CREATE can not be implemented with this structure. This implementation can't represent multiple trees, which is necessary for the operation CREATE.

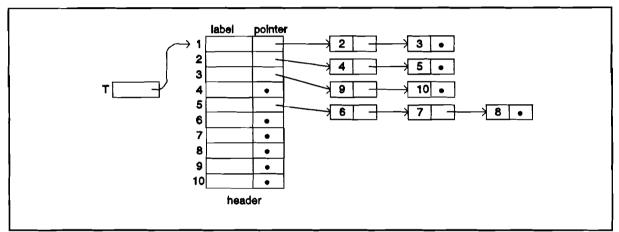

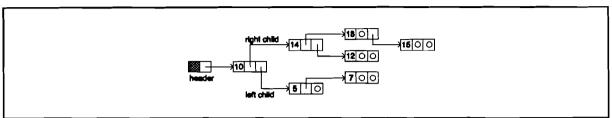

An important and useful representation of trees is to form for each node a list of its children. The list can be represented by any of the methods suggested in paragraph 3.4., but because the number of children of each node can vary, the linked-list representations are often more appropriate. Figure 3.8. suggests how the tree of figure 3.7.(a) might be represented.

Figure 3.8. Linked-list representation of a tree.

An array of header cells is indexed by the nodes, and each cell contains the label of that node and a pointer to a linked list of child nodes. If a node has no children, then a nil pointer is used. The root is stored in a separate root field. With this representation it is easy to implement the operations LEFT\_CHILD, LABEL, ROOT and CLEAR. The operations RIGHT\_SIBLING and PARENT are more difficult to implement, and the operation CREATE can not be implemented. An extra operation should be defined to build the tree.

The data structure described above can't create large trees from smaller ones, using the CREATE operator. The reason is that all trees have a separate array of headers for their nodes. For example, to implement CREATE(T,2,I, $T_2$ , $T_2$ ) we would have to copy  $T_1$  and  $T_2$  into a third tree T and add a new node with label I and two children - the roots of  $T_1$  and  $T_2$ .

If we wish to build trees from smaller ones, the representation of nodes from all trees should share one area. This can be done by adding an array with pointers to the root of every tree. If we want to implement the RIGHT\_SIBLING operation effectively, we have to add pointers to the right\_sibling element in the tree. This representation is given in figure 3.9.

Figure 3.9. (a) A tree and its (b) left-child, right sibling implementation.

With this representation it is easy to implement all defined operations. There are many special trees, each for a special purpose, and all with its own operation set. Usually, trees are used to store information, which has to be searched for certain elements. They are also used for the implementation of other data structures, like sets. The characteristics of the implementations and the complexity of the operations are given in table 8.

|               | Tree                        |             |                              |  |  |  |

|---------------|-----------------------------|-------------|------------------------------|--|--|--|

|               | Complexity / representation |             |                              |  |  |  |

| Operations    | Parent pointer              | Linked list | Left_child-<br>Right_sibling |  |  |  |

| CLEAR         | O(n)                        | O(n)        | O(c)                         |  |  |  |

| PARENT        | O(c)                        | O(n²)       | O(c)                         |  |  |  |

| LEFT_CHILD    |                             | O(c)        | O(c)                         |  |  |  |

| RIGHT_SIBLING |                             |             | O(c)                         |  |  |  |

| LABEL         | O(c)                        | O(c)        | O(c)                         |  |  |  |

| CREATE        | —                           | (           | O(c)                         |  |  |  |

| ROOT          | O(log n)                    | O(c)        | O(c)                         |  |  |  |

| Access        | Direct                      | Direct/seq. | Direct                       |  |  |  |

| Size          | Fixed                       | Dynamic     | Fixed/Dynamic                |  |  |  |

Table 8: Tree characteristics

c = constant, n = number of nodes in tree.

Software implementations and their complexity ----

There are some well known algorithms for trees. The depth-first search (dfs) and the breadth-first search (bfs) are some often used search algorithms. These algorithms are also used with graphs (a tree is a very special kind of graph), and are discussed in section 3.8. See also [AHO83], [COR90], [MAN89] and [SED88].

#### <u>3.7. Sets</u>

The set is a very often used data structure, often with only a subset of operations. Using this knowledge, we can define several representations for a set.

#### 3.7.1. Simple implementations

The best implementation of a set structure depends on the operations to be performed and on the size of the set. When the set consists of a small 'universal set' whose elements are the integers 1,..,N for some fixed N, then we can use a *bit-vector* (boolean array) implementation. The set is represented by a bit vector in which the  $1^{th}$ bit is true if *i* is an element of the set. The major advantage is that MEMBER, INSERT, and DELETE operations are performed in fixed time by directly addressing the appropriate bit. UNION, INTERSECTION, and DIFFERENCE can be performed in a time proportional to the size of the universal set. Also the other operations can be executed in a constant amount of time. The main disadvantage of this implementation is that all elements must be in a small, predefined universal set.

It should be evident that sets can be represented by lists, where the items in the list are the elements of the set. If we use a linked list, it uses, unlike the bit-vector representation, space proportional to the size of the set represented, not the size of a universal set. Moreover, the list representation is more general since it can handle sets that need not be subsets of some finite universal set.

When we have operations like INTERSECTION on sets  $L_1$  and  $L_2$  represented by lists, we have several options. If the universal set is linearly ordered, then we can represent a set by a sorted list. With unsorted lists we must match each element on  $L_1$  with each element on  $L_2$ , a process that takes  $O(n^2)$  steps on lists of length *n*. But if we use sorted lists, this operation takes only O(n) steps. On the other hand an insertion in an unsorted list takes O(n) steps (if we insert at end of list), while an insertion in a sorted list takes O(n) steps.

Another representation is the hash table. The set-element is stored in the key field, and the data field will be empty. The operations INSERT, DELETE, and MEMBER will be executed in a constant amount of time, but other operations can not be implemented. The characteristics of the implementations discussed above are given in table 9.

|              | Set                         |           |                    |                    |                    |              |               |  |

|--------------|-----------------------------|-----------|--------------------|--------------------|--------------------|--------------|---------------|--|

|              | Complexity / representation |           |                    |                    |                    |              |               |  |

| Implement.   | Bit-                        | List      | - Array            | List - Linked list |                    | Hash table** |               |  |

| Operation    | vector*                     | Ordered   | Unordered          | Ordered            | Unordered          | Open         | Closed        |  |

| UNION        | O(N)                        | O(n)      | O(n <sup>2</sup> ) | O(n)               | O(n <sup>2</sup> ) |              |               |  |

| INTERSECTION | O(N)                        | O(n)      | O(n <sup>2</sup> ) | O(n)               | O(n <sup>2</sup> ) |              |               |  |

| DIFFERENCE   | O(N)                        | O(n)      | O(n²)              | O(n)               | O(n <sup>2</sup> ) | . —          |               |  |

| CLEAR        | O(n)                        | O(c)      | O(c)               | O(c)               | O(c)               | O(B)         | O(B)          |  |

| MEMBER       | O(c)                        | O(log n)  | O(n)               | O(n)               | O(n)               | O(c+n/B)     | O(c+1/(1-n/B) |  |

| INSERT       | O(c)                        | O(n)      | O(n)               | O(n)               | O(n)               | O(c+n/B)     | O(c+1/(1-n/B) |  |

| DELETE       | O(c)                        | O(n)      | O(n)               | O(n)               | O(n)               | O(c+n/B)     | O(c+1/(1-n/B) |  |

| ASSIGN       | O(N)                        | O(n)      | O(n)               | O(n)               | O(n)               | _            |               |  |

| EQUAL        | O(N)                        | O(n)      | O(n <sup>2</sup> ) | O(n)               | O(n <sup>w</sup> ) | —            | - 1           |  |

| MIN          | O(N/n)                      | O(c)      | O(n)               | O(c)               | O(n)               | _            | _             |  |

| MAX          | O(N/n)                      | O(c)      | O(n)               | O(c)               | O(n)               |              | -             |  |

| Access       | Direct                      | Dir./Seq. | Dir./Seq.          | Sequent.           | Sequent.           | Dir./Seq.    | Dir./Seq.     |  |

| Size         | Fixed                       | Fixed     | Fixed              | Dynamic            | Dynamic            | Fixed        | Dynamic       |  |

#### Table 9. Set characteristics (1)

\* N = maximal set size, n = number of set elements

\*\* see note table 7.

#### 3.7.2 Advanced implementations

We will now introduce some data structures for sets that permit a more efficient implementation of common collections of set operations. These structures however, are often more complex and are often only appropriate for large sets. All are based on various kinds of trees, such as binary search trees and balanced trees.

#### Binary search tree implementation of sets

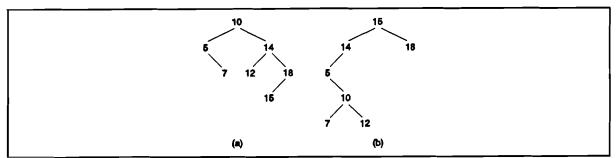

A representation of a set can be given by a binary search tree, a basic data structure for representing sets whose elements are ordered by some linear order (denoted by '<'). This structure is useful when we have a set of elements from a universe so large that it is impractical to use the elements of the set themselves as indices into arrays. A binary search tree can support the set of operations INSERT, DELETE, MEMBER and MIN, taking on the average O(log n) steps per operation for a set of n elements.

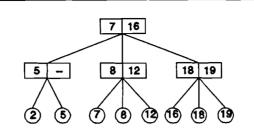

A binary search tree is a tree in which the nodes are labelled with elements of a set. The important property is that all elements stored in the left subtree of any node x are all less than the element stored at x, and all elements stored in the right subtree of xare greater than the element stored at x. This condition, called the *binary search tree*  *property*, holds for every node of a binary search tree, including the root. Figure 3.10 shows two binary search trees representing the same set of integers.

Figure 3.10. Two binary search trees.

Suppose a binary search tree is used to represent a set. The tree property makes testing for membership in the set simple. To determine whether x is a member of the set, first compare x with element r at the root of the tree. If x = r, we are done, the element is found. If x < r, then x can only be in the left subtree of r, if x > r, then x can only be in the right subtree of r. Then we repeat this operation on the left, c.q. right subtree.

The operation INSERT is easy. We have to compare the element x with a node element. If the node element equals x, then x is already in the set. If x is smaller than the node element, then we have to repeat this comparison with the element of the left child. If there is no left child, then that is the position, where x has to be inserted. This is also true for the right child.

MIN is also easy to implement. We only have to search in the tree for the first left child node that has no left child. Using this, the operation DELETEMIN is also easy. We replace the element found with MIN, by its right child.

The operation DELETE is implemented by using DELETEMIN. When we want to delete element x, we have to locate this element. If it is found, we delete it and replace it by the minimal element of its right sub tree (if exist). In figure 3.11 we see an insertion of 6 and a deletion of 10 in the tree of figure 3.10.(a).

Figure 3.11. Tree 3.10(a) after insertion of 6 (a) and after deletion of 10 (b).

A binary search tree is mostly implemented by linked records. The implementation of the tree of figure 3.10.(a) is given in figure 3.12.

Figure 3.12. Binary search tree implementation.

If we insert a sorted list into a set, we don't get a balanced binary tree, but a chain of nodes, so the complexity of the operations would be O(n). If we assume a random input sequence, we have a complexity  $O(\log n)$ .

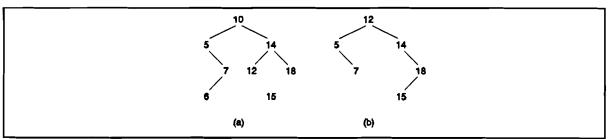

#### Balanced tree implementation of sets

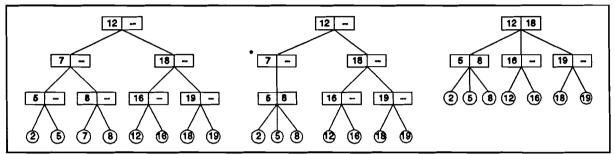

Another implementation is the balanced tree. This representation has as advantage that the execution of the operations has a time of O(log n) worst case. There are many implementations of balanced trees, such as the 2-3 tree, the AVL-tree, the B-tree etc. One of the balanced tree implementations is the '2-3 tree'. A 2-3 tree is a tree with the following two properties.

- 1. Each interior node has two or three children.

- 2. Each path from the root to a leaf has the same length

We shall consider a tree with zero nodes or one node as special cases of a 2-3 tree.

We represent sets of elements that are ordered by some linear order <, as follows. Elements are placed at the leaves; if element *a* is to the left of element *b*, then a < b must hold. We shall assume that the ordering of elements is based on one field of a record that forms the element type; this field is called the *key*. For example, elements might represent information about students, and the key field might be 'id-number'.

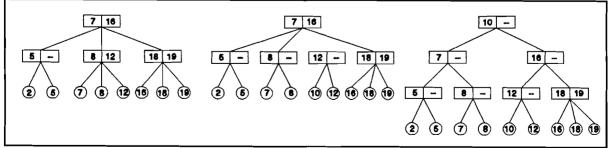

At each interior node we record the key of the smallest element that is a descendant of the second child. If there is a third child, we record the key of the smallest element descending from that child as well. Figure 3.13. is an example of a 2-3 tree.

Figure 3.13. A 2-3 tree.

Observe that a 2-3 tree representing a set of *n* elements requires at least  $1 + \log_3 n$  levels and no more than  $1 + \log_2 n$  levels. Thus, path lengths in the tree are O(log n).

To test membership of a record with key x, we just have to move down the tree and compare x with the keys stored at the internal nodes. If x < first key, then we go to the first sub tree. If there is a second node key and if first key  $\leq x <$  second key, then we search the second subtree. If second key  $\leq x$ , then we search the third tree. When x equals one of the node keys, we know that x is a member of the set, and we don't have to search further. So testing membership takes O(log n).

To insert elements, we proceed at first if we were testing membership of x in the set. However, at the level just above the leaves, node's children do not include x. If that node has only two children, we simply make x the third child of that node, placing the children in proper order, and adjusting the keys of the node.

Suppose, however, that *x* is the fourth child of the node. We cannot have a node with four children, so we split the node in two nodes, giving the first new node the two smallest elements and the second new node the other two. Now we have to insert an extra node among the parent of the node, just as the insertion at the leaf level. One special case occurs when we wind up splitting the root. Then we create a new root, whose children are the two nodes into which the old root was split. This is how the number of levels increase. In figure 3.14. an example is given of an insertion.

Figure 3.14. Insertion of 10 in 2-3 tree.

When we delete a leaf, we may leave its parent node n with only one child. If that node n is the root, delete the node and lets its lone child be the new root. Otherwise, if the parent p of node n has another child, adjacent to n on either the right or left, and that child of p has three children, we can transfer the proper one of those three to n. Then, n has two children and we are done. If that adjacent node has only two children, transfer the lone child of n to that adjacent node and delete node n. Should parent p now have only one child, repeat all the above recursively. An example of a deletion is given in figure 3.15.

Figure 3.15. Deletion of 7 in a 2-3 tree.

This 2-3- tree is one of the many implementations of balanced trees. This tree can easily be extended to, for example, 2-3-4 trees. They all have in common that the maximal time needed for execution of the operations is O(log n). In table 10 an overview of the characteristics is given.

|           | Set                         |               |  |  |  |

|-----------|-----------------------------|---------------|--|--|--|

|           | Complexity / representation |               |  |  |  |

| Operation | Binary search tree          | Balanced tree |  |  |  |

| CLEAR     | O(c)                        | O(c)          |  |  |  |

| INSERT    | O(log n) - O(n)             | O(log n)      |  |  |  |

| DELETE    | O(log n) - O(n)             | O(log n)      |  |  |  |

| MEMBER    | O(log n) - O(n)             | O(log n)      |  |  |  |

| DELETEMIN | O(log n) - O(n)             | O(log n)      |  |  |  |

| MIN       | O(log n) - O(n)             | O(log n)      |  |  |  |

| Access    | Sequential                  | Sequential    |  |  |  |

| Size      | Dynamic                     | Dynamic       |  |  |  |

Table 10. Set characteristics (2)

c = constant, n = number of elements in set.

For more information about set representations, trees etc. see [AHO83], [COR90], [MAN 89], [SED88] and [WAR90].

### 3.8. Graphs

Graphs, representing relationships among data objects, are used for problems arising in computer science, mathematics, engineering etc. This paragraph presents the basic structures that can be used to represent graphs. Also some algorithms are given, which are often used on graphs.

#### 3.8.1 Implementations

When we look at a graph, we should see a difference between a directed and an undirected graph. However, an undirected graph can be represented by a directed graph (figure 3.16), so the representation can be the same. This makes the graph structure more general.

Figure 3.16. Directed and undirected graph.

#### Adjacency matrix implementation of graphs

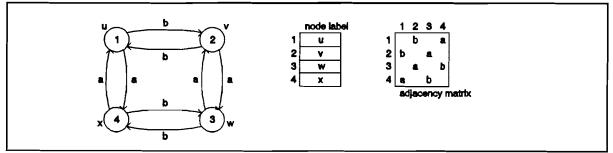

The appropriate choice of data structure depends on the operations that will be applied to the edges and nodes of the digraph. One common representation for a digraph is the *adjacency matrix*. Suppose the nodes are in  $\{1,2,..,n\}$ . The adjacency matrix is an  $n \times n$  matrix of edge labels, where A[i,j] is the label of the edge from node *i* to node *j*. If there is no edge between two nodes, there should be a special nil-value in the matrix. There should also be a list with the nodes that are present at that moment (with their node labels). Figure 3.17 shows such an implementation.

Figure 3.17. Digraph with adjacency matrix representation.

In the adjacency matrix representation the time required to access an element of an adjacency matrix is independent of the number of nodes and the number of edges. This representation is useful in those graph algorithms in which we frequently need to know whether a given edge is present and what's its label is. The main disadvantage of using an adjacency matrix is that the matrix requires  $n^2$  storage even if the digraph has less than  $n^2$  edges. So if we have a sparse adjacency matrix, we can better use another representation.

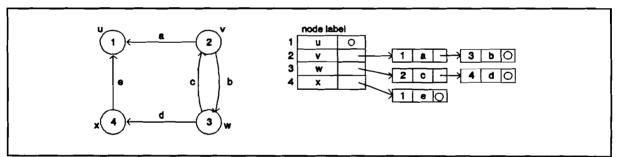

#### Adjacency list implementation of graphs

Another common representation for a digraph is called the *adjacency list* representation. The adjacency list for node *i* is a list, in some order, of all edges adjacent to *i*. We can represent the graph by an array with all nodes and their labels (if the node exists), with a pointer from every node to the adjacency list for that node *i*. The adjacency list representation of a digraph requires a storage proportional to the sum of the number of nodes and the number of edges (n + e). This representation is often used when the number of edges is less than  $n^2$ . However, a potential disadvantage of the adjacency list representation is that it may take O(n) time to determine whether there is an edge from node *i* to node *j*, since there can be O(n) edges on the adjacency list for nodes *i*. Figure 3.18 shows such an implementation.

Figure 3.18. Graph with adjacency list representation.

In table 11 are given some characteristics of the two implementations.

|               | Graph<br>Complexity / representation |                |  |

|---------------|--------------------------------------|----------------|--|

|               |                                      |                |  |

| Operations    | Adjacency matrix                     | Adjacency list |  |

| CLEAR         | O(n <sup>2</sup> )                   | O(c)           |  |

| INSERT_NODE   | O(c)                                 | O(c)           |  |

| INSERT_EDGE   | O(c)                                 | O(n)           |  |

| DELETE_NODE   | O(n)                                 | O(n²)          |  |

| DELETE_EDGE   | O(c)                                 | O(n)           |  |

| RETRIEVE_NODE | O(c)                                 | O(c)           |  |

| RETRIEVE_EDGE | O(c)                                 | O(n)           |  |

| Access        | Direct                               | Direct/Seq.    |  |

| Size          | Fixed                                | Dynamic        |  |

#### Table 11. Graph characteristics

#### 3.8.2 Algorithms

There are many algorithms that are used on graphs. We make a difference between algorithms for directed and undirected graphs, because each of these two types of graphs has its own use. First we give some algorithms for directed graphs. We won't explain the algorithms in detail, we will just explain the problem, give the name of an often use algorithm, and give the complexity of that algorithm.

- Single source shortest path problem: Consider a directed graph in which each edge has a non negative label, and one node is specified as the source. When there is no edge between two nodes, the label is ∞. Our problem is to determine the cost of the shortest path from the source to every other node, where the length of the path is the sum of the costs of the arcs on the graph. To solve this problem we use a greedy technique, often known as Dijkstra's algorithm [AHO83], [MAN89], [SED88]. The algorithm works by maintaining a set S of nodes whose shortest distance from the source is known. At each step we add to S a remaining node *n* whose distance to *S* is as short as possible. When S includes all nodes, then the solution is known. If we use an adjacency matrix representation for the graph, the running time is  $O(n^2)$ , but if the number of edges e is much smaller than  $n^2$ , we might better use an adjacency list representation for the digraph, and a priority queue representation for the nodes not yet selected in S. This gives a running time of O(e log n).

- All-pairs shortest paths problem: Find the shortest distance from any node to every other node. We could solve this with *Dijkstra's* algorithm, taking every node once as the source. This would take a running time of O(n<sup>3</sup>), or if e is much smaller than n<sup>2</sup>, then it would take O(ne log n) time. There is for this problem an other algorithm known, i.e. *Floyd's algorithm* [AHO83], [MAN89], [SED88]. This takes also O(n<sup>3</sup>) time.

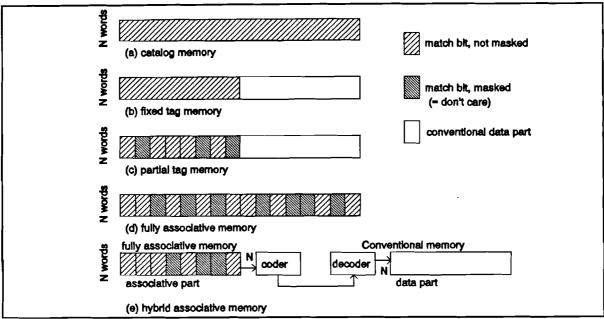

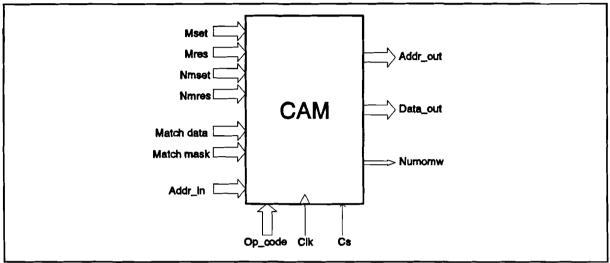

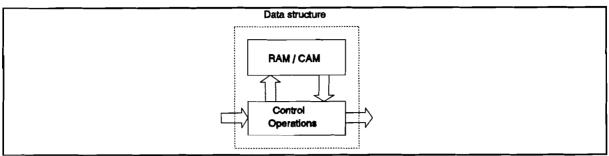

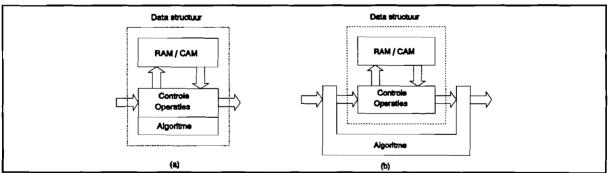

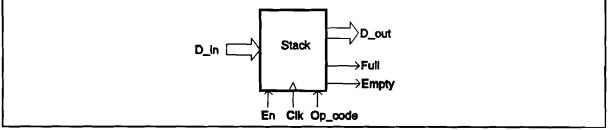

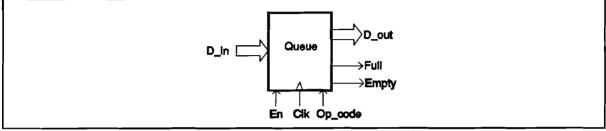

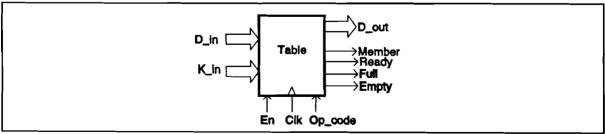

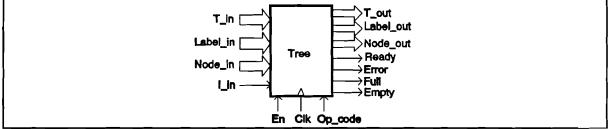

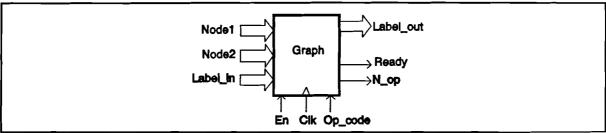

- Transitive closure: Given a graph G = (V,E), the transitive closure C = (V,F) of G is a directed graph such that there is an edge (v,w) in C if and only if there is a directed path from v to w in G. For this problem is developed an algorithm by Warshall, called *Warshall's algorithm* [AHO83], [MAN89], [SED88] that is based on Floyd's algorithm. This algorithm has also complexity O(n<sup>3</sup>).