| MASTER                        |

|-------------------------------|

| Integrated cooling in silicon |

|                               |

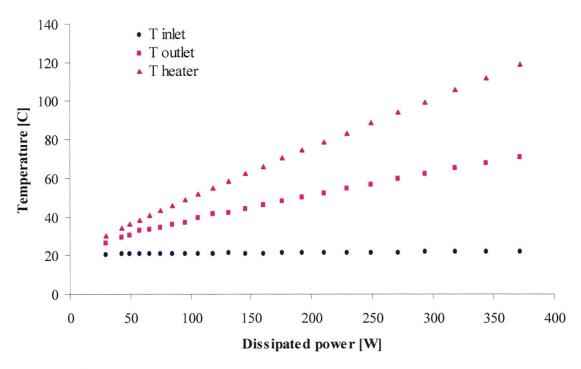

| Pijnenburg, R.H.W.            |

| Award date: 2004              |

|                               |

| Link to publication           |

|                               |

|                               |

|                               |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

## Integrated cooling in silicon

## Remco Pijnenburg

May 14, 2004

Philips Research Eindhoven

Technische Universiteit Eindhoven (TU/e)

Supervisors: Ronald Dekker and Leo van IJzendoorn

#### **Abstract**

In this report two different types of integrated cooling mechanisms will be investigated. The first one is cooling by combined thermo tunneling and thermionic emission in vacuum. The second method is cooling by forced water convection through micro-channels.

The feasibility of the concept for cooling by combined thermionic emission and thermo tunneling to vacuum will be reviewed. In theory, a combination of a strong electric field (>10<sup>6</sup> V/cm) and an image charge potential can significantly lower the work function, which may open the possibility for cooling at room temperature by combined thermionic emission and thermo tunneling. However, due to numerous practical problems, such a cooling device is not possible within the present experimental tolerances.

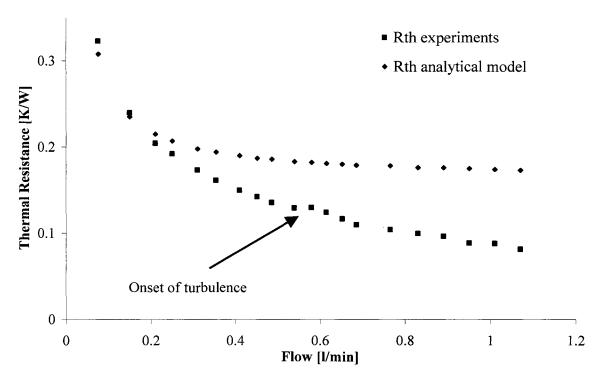

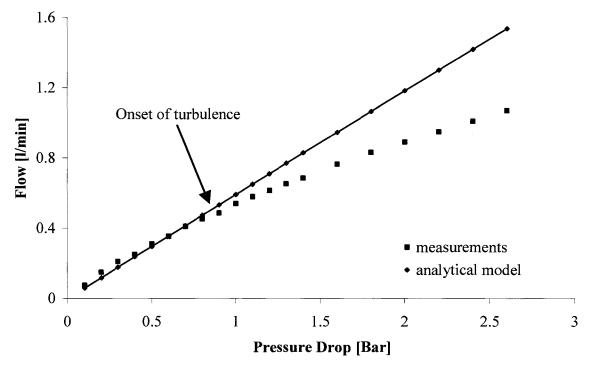

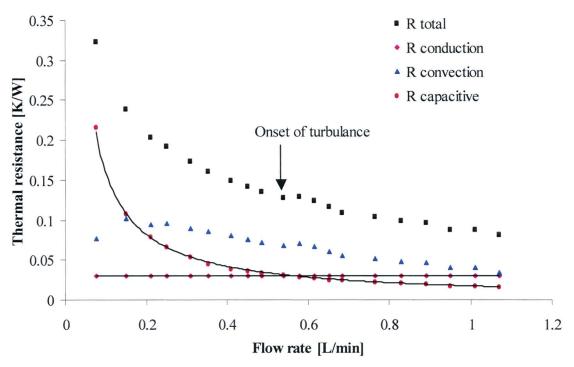

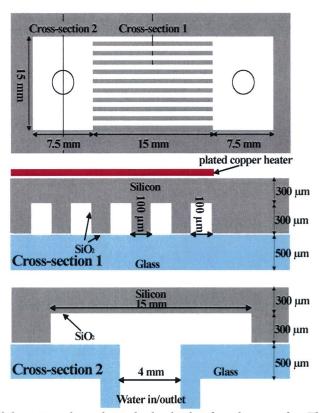

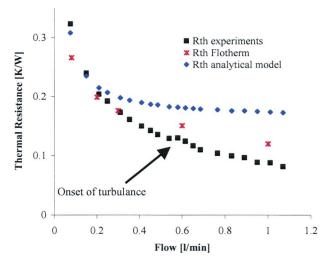

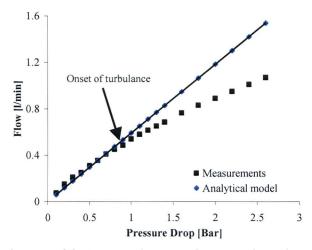

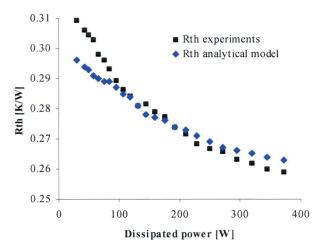

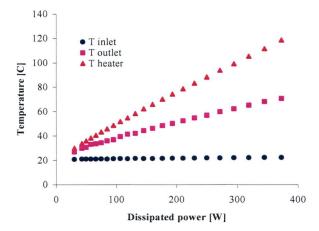

Integrated micro-channels, processed in silicon, directly underneath an electronic circuit for on-chip cooling with forced water convection has been investigated both theoretically and experimentally. In a 1-cm² experimental device 370 W was dissipated without exceeding the critical junction temperature of 120 °C at a flow rate of only 0.1 l/min and a pressure drop of 0.15 bar. The minimum thermal resistance, which is measured, is 0.08 K/W for a power dissipation of 428 W at a flow rate of 1.1 l/min. This more than satisfies the requirements for cooling of next generation CPUs. The experimental results are compared to numerical calculations. For low flow rates there is a very good agreement. For higher rates, the flow is not fully developed and becomes turbulent, which results in an even better performance as predicted by the numerical calculations. There are several opportunities available to improve the cooling performance.

#### **Technology assessment**

As integrated circuits become faster and more densely packed with transistors, the power density increases and the heat generated, due to the electrical resistance of the large number of interconnects, becomes a problem. In addition, the area available for heat removal decreases. As a result, thermal management becomes increasingly critical to the electronics industry.

The reliability of semiconductor devices depends on the temperature reached during operation. This interrelation between reliability and temperature is the result of both direct and induced mechanisms. Direct mechanisms are caused by the relationship between the temperature and the rate of diffusion or chemical reactions, which frequently lead to chip failure. These mechanisms are exponentially dependent on the operating temperature and hence, the package reliability. The induced mechanisms are directly related to thermal stresses inherent within the chip and typically result in failure caused by fatigue of the mechanical devices or connections. In addition, many of the physical and chemical processes that can cause chip failure are accelerated by elevated temperature. This all is why heat buildup is becoming one of the major limitations to creating tomorrows more compact and complex microelectronics devices. The increasing integration of electronic systems is leading to challenges for the thermal design of an integrated cooling device directly underneath the electronic circuit, to remove the heat from the circuit and transport it to other places. By separating the heat source from the area where the heat is released to the ambient, the area available for heat removal can be increased, and hot spots in the electrical devices can be prevented.

The possible methods to cool an electronic system vary widely [1]. Because in most systems the space available for the cooling device is limited, not all methods are possible. Consequently, research on cooling concepts is focused on integrated micro cooling devices.

In this report two different types of integrated cooling mechanisms will be investigated. The first one is cooling by combined thermo tunneling and thermionic emission in vacuum. The second method is cooling by forced water convection through micro-channels.

<sup>[1]</sup> C.S. Nicole, "Alternative cooling techniques," Nat.Lab. Technical Note 2002/224, July 2002.

## **Contents**

| Abstract                                                                        | •••••••••••••••••••••••••••••••••••••••                       | 1       |  |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------|---------|--|--|

| Technolog                                                                       | gy assessment                                                 | 2       |  |  |

| Contents.                                                                       |                                                               | 3       |  |  |

| PART I Cooling by combined thermo tunneling and thermionic emission in vacuum 5 |                                                               |         |  |  |

| Chapter 1                                                                       | Introduction                                                  | 6       |  |  |

| Chapter 2                                                                       | Theory                                                        | 9       |  |  |

| 2.1                                                                             | Theory of thermionic emission                                 |         |  |  |

| 2.2                                                                             | Theory of thermo tunneling                                    |         |  |  |

| Chapter 3                                                                       | Calculation of expected cooling power by combined thermio     | nic     |  |  |

| •                                                                               | emission and thermo tunneling                                 |         |  |  |

| 3.1                                                                             | Electron energy distribution                                  |         |  |  |

| 3.2                                                                             | Current and cooling power densities                           |         |  |  |

| 3.3                                                                             | Conclusion                                                    |         |  |  |

| Chapter 4                                                                       | Practical implementation: the fabrication of an integrated co | oler in |  |  |

|                                                                                 | silicon                                                       | 23      |  |  |

| Chapter 5                                                                       | Discussion                                                    | 27      |  |  |

| Chapter 6                                                                       | Conclusion                                                    | 31      |  |  |

| Chapter 7                                                                       | Reference                                                     | 32      |  |  |

| PART I                                                                          | II nvection through micro-channels                            | 33      |  |  |

| Chapter 1                                                                       | Introduction                                                  | 34      |  |  |

| Chapter 2                                                                       | Theory                                                        | 36      |  |  |

| 2.1                                                                             | Heat transfer basics                                          |         |  |  |

|                                                                                 | 2.1.1 Conduction                                              | 36      |  |  |

|                                                                                 | 2.1.2 Convection                                              | 37      |  |  |

| ,                                                                               | 2.1.3 Radiation                                               |         |  |  |

| 2.2     |              | d fluidic laws for single phase forced convection through |    |

|---------|--------------|-----------------------------------------------------------|----|

|         | micro-chanr  | nels                                                      | 38 |

|         | 2.2.1 There  | mal resistances                                           |    |

|         | 2.2.1.1      | Conduction thermal resistance, <i>R<sub>cond</sub></i>    | 39 |

|         | 2.2.1.2      | Convection thermal resistance, <i>R<sub>conv</sub></i>    | 39 |

|         | 2.2.1.3      | Capacitive thermal resistance, <i>R<sub>cap</sub></i>     | 39 |

|         | 2.2.1.4      | Overall thermal resistance, <i>R<sub>th</sub></i>         | 40 |

|         | 2.2.2 Conv   | rective exchange laws from a thermal and hydraulic point  |    |

|         | of vie       | ew                                                        | 40 |

|         | 2.2.2.1      | Reynolds number                                           | 40 |

|         | 2.2.2.2      | Prandtl number                                            | 41 |

|         | 2.2.2.3      | Friction coefficient and pressure losses                  | 41 |

|         | 2.2.2.4      | Nusselt number                                            | 42 |

| 2.3     | Analytical n | nodel                                                     | 42 |

|         | 2.3.1 Fluid  | velocity profile                                          | 43 |

|         |              | perature field                                            |    |

|         |              | ion procedure                                             |    |

|         |              | •                                                         |    |

| Chapter | 3 Practical  | implementation                                            | 51 |

| 3.1     |              | of micro-channels in Silicon                              |    |

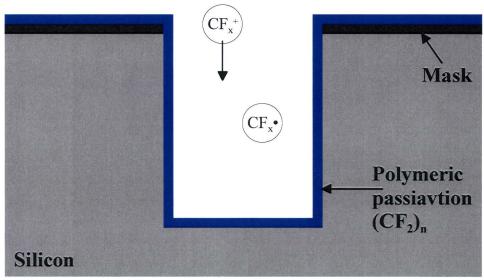

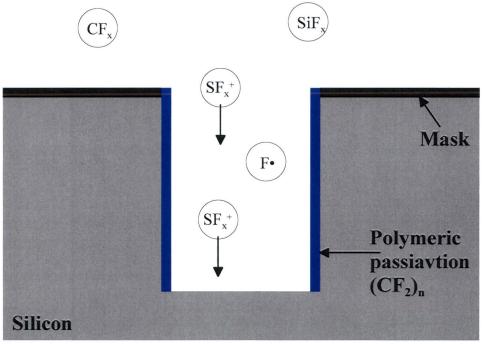

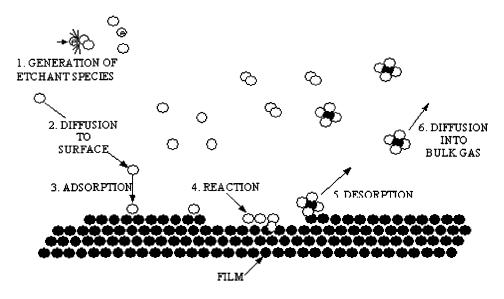

| 3.2     |              | dry etching of silicon                                    |    |

|         |              | osition step                                              |    |

|         |              | step                                                      |    |

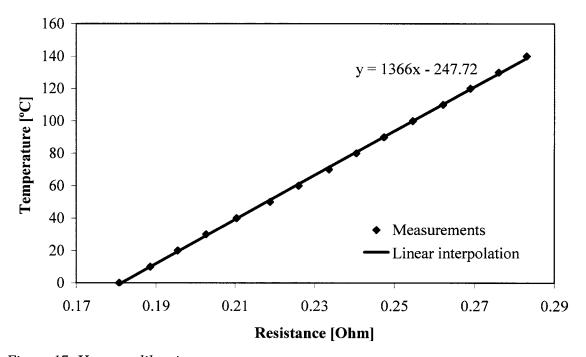

| 3.3     |              | ealibration                                               |    |

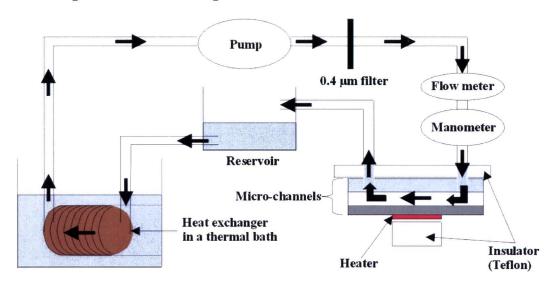

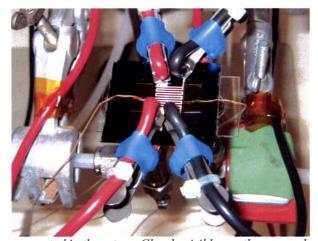

| 3.4     |              | al setup                                                  |    |

|         | <b>—</b>     | <b>-</b>                                                  |    |

| Chapter | 4 Experime   | ental results and comparison with calculations            | 60 |

|         |              |                                                           |    |

| Chapter | 5 Discussio  | on                                                        | 66 |

| •       |              |                                                           |    |

| Chapter | 6 Conclusio  | on                                                        | 69 |

| •       |              |                                                           |    |

| Chapter | 7 Referenc   | e                                                         | 70 |

|         |              |                                                           |    |

| Chapter | 8 Appendix   | x B: Matlab program                                       | 71 |

| L       | 11           |                                                           |    |

| Chapter | 9 Appendix   | x B: Publication                                          | 79 |

| . 1     | rr           |                                                           |    |

| Acknowl | edgements    |                                                           | 86 |

|         |              |                                                           |    |

#### **PART I**

Cooling by combined thermo tunneling and thermionic emission in vacuum

#### Introduction

Solid-state coolers, like thermoelectric coolers have many advantages over conventional refrigerators. They have the advantage of not having moving parts, nor any type of fluid. Therefore, they produce minimum of noise and can be made very compact. Furthermore, thermoelectric refrigeration avoids the use of environmentally hazardous chlorofluorocarbons (CFC's) used in most compressor-based refrigeration. However, it has a small efficiency and only a small temperature difference can be maintained in a single stage thermoelectric cooler.

In thermoelectric refrigerators or generators [1], electrons serve as both entropy and charge carriers in solids. In linear approximation, the effectiveness of heat and electric power conversion depends only on a single dimensionless material parameter ZT:

$$ZT = \frac{\Pi^2}{\rho \kappa T},\tag{1.1}$$

where  $\Pi$  [WA<sup>-1</sup>] is the Peltier coefficient which is equal to the entropy flow divided by the charge flow carried by the electric current,  $\rho$  [ $\Omega$ m] the electrical resistivity and  $\kappa$  [WK<sup>-1</sup>m<sup>-1</sup>] the thermal conductivity. It is important to reduce the thermal conductivity and electrical resistivity as much as possible in order to have a better thermoelectric material, as can be seen from equation 1.1. Since electrons serve as both heat and charge carriers in solids, it has been a difficult task to find a good thermoelectric material.

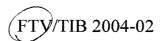

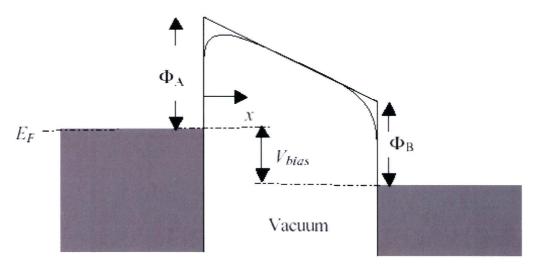

An alternative cooling mechanism is thermionic refrigeration, which is based on the principle of thermionic emission. In thermionic emission, two electrodes are used, an emitter and a collector (or cathode and anode), separated by vacuum with a bias potential applied (Fig. 1). On the emitter side, a heat source is attached, which results in an increased electron temperature. Those electrons that are thermally excited and have enough energy to surmount the barrier (called work function, denoted by  $\Phi$ , this is the minimum amount of energy an individual electron has to gain to escape from a particular surface) will escape into the vacuum. The emitted electrons travel ballistically toward the anode, arrive at the anode, and give off their heat. On the emitter side, an electron is replaced at the Fermi level to maintain charge neutrality. Thus there is a net transport of heat equivalent to the work function per emitted electron, and the emitter is cooled.

Figure 1. Thermionic emission of electrons.

Thermionic emission across a vacuum gap promises to have a much higher figure of merit (ZT, equation 1.1) than a solid thermoelectric because there is no lattice thermal conductivity, there is no ohmic resistivity due to the absence of electron scattering in the vacuum, because they travel ballistically. A result of the absence of heat dissipation in the vacuum is that all the heat is pumped to the hot side of the cooling device (collector). The effective Peltier coefficient is also greater than that of thermoelectric materials. Other advantages of thermionic emission are that the only possible heat backflow through the vacuum is by radiation, which is  $\sim 0.1~\rm W/cm^2$  for black body radiation at room temperature.

Mahan theoretically studied the possibility of vacuum thermionic refrigeration [2]. To make a thermionic cooling device, which can operate at room temperature, an anode with a work function of 0.4 eV is needed. However, it seems unlikely that such low values of work function will be found. As a result of this, room temperature cooling with use of only thermionic emission seems to be not possible. The lowest work functions for materials at room temperature are around 0.7-0.8 eV. This value of work function permits a thermionic refrigerator whose cold temperature is 500 K, but this temperature is too high for most electronic devices. So additional reduction of the barrier of 0.4 eV is necessary for thermionic emission at room temperature.

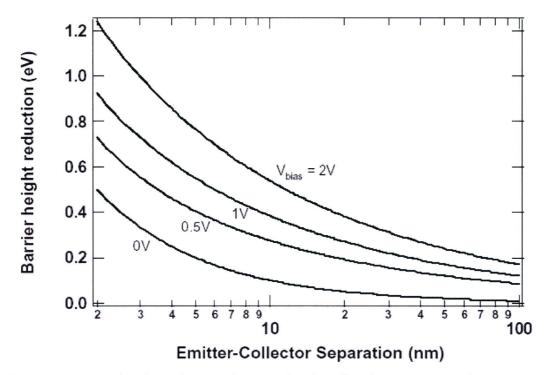

It is known that the energy barrier near a surface is significantly distorted by a strong applied electric field and by the image charge of the emitting electron itself. The distortion causes the barrier height reduction, which is generally known as the Schottky effect. The Schottky effect reduces the effective barrier height by few tenths of an eV when an electric field in order of  $10^6$  V/cm is applied. In order to produce such a strong field, a high potential usually needs to be applied between the emitter and the collector. For example, if the emitter-collector separation is  $10~\mu m$ , the required potential is over 1000~V, which makes the thermionic cooling very inefficient and impractical. In order to make thermionic cooling efficient and competitive, at room temperature, with other cooling methods, the emitter-collector gap must be reduces to 1-10 nm. Such a narrow gap and a

strong electric field also make it possible for electrons to tunnel through the barrier to the collector.

So by combining low work function materials and making controlled nanometer gaps, with vacuum between the emitter and collector and an applied bias voltage, there seems to be a window of opportunity for achieving the low barrier potential condition necessary for room temperature thermionic emission.

#### **Theory**

#### 2.1 Theory of thermionic emission

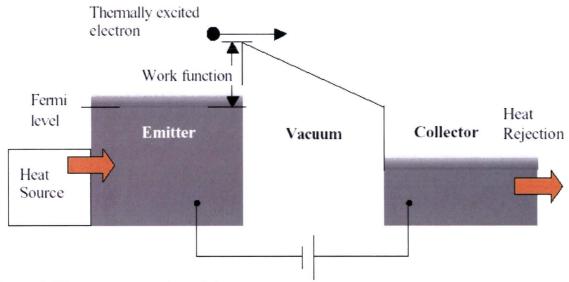

In a metal or semiconductor at non-zero temperature, free electrons move around in a random manner whose velocity distribution it determined by the temperature. Some electrons have enough kinetic energy to escape from the surface of the solid. The energy necessary for an electron to escape from the surface of solid into the vacuum is called the work function of a material and is denoted by  $\Phi$ . More electrons are emitted into the vacuum as temperature is increased or the work function is decreased.

Figure 2. Potential barrier at the metal/semiconductor-vacuum boundary.

The probability that an electron energy level E will be occupied in an ideal electron gas in thermal equilibrium is given by the Fermi-Dirac distribution:

$$f(E) = \frac{1}{1 + \exp\left[\frac{(E - E_F)}{k_B T}\right]},$$

(1.2)

where  $E_F$  [J] the Fermi energy level,  $k_B$  [JK<sup>-1</sup>] the Boltzmann constant and T [K] the temperature. When the Fermi energy level is set to zero by definition, than the number of electrons incident on unit area in unit time with kinetic energy in x direction in the range  $E_x$ ,  $E_x+dE_x$  is given by:

$$N(E_x) = \frac{mk_B T}{2\pi^2 \hbar^3} \ln \left[ 1 + \exp\left(-\frac{E_x}{k_B T}\right) \right], \tag{1.3}$$

where m the mass of an electron and  $\hbar$  [Js] the constant of Planck divided by  $2\pi$ . Electrons whose  $E_x$  is greater than the work function of the material will escape into vacuum, so the

total thermionic emission current density is obtained by integrating all electrons having  $E_x > q\Phi$ :

$$J_R(T) = \frac{mqk_B^2 T^2}{2\pi\hbar^3} \exp\left(-\frac{q\Phi}{k_B T}\right),\tag{1.4}$$

with q the charge of the electron.

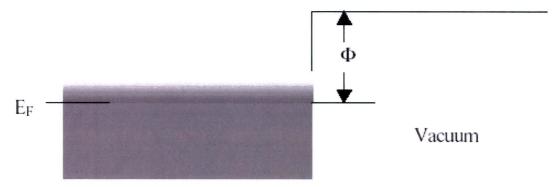

This well-known result is called the Richardson equation. As seen in this equation, a small variation in work function caused by a change in surface conditions produces a significant change in amount of electron emission. To obtain a reasonable amount of thermionic current (~1 A/cm² [2]) at room temperature, a work function of 0.4 eV or less is necessary. However, the work function of clean silicon is 4.7 eV. It is possible to lower the work function by evaporating alkali metals onto the surface. Alkali metal sub-monolayer coverage onto a surface is known to produce work functions lower than that of bulk values of alkali metals (Fig. 3).

Figure 3. Schematic of work function vs. alkali metal coverage.

Oxygen additives can achieve further lowering of the work function. It is possible to create work functions around the 1 eV [3]. This is already a good start to get a low barrier needed for thermionic emission.

The amount of energy carried by thermionically emitted electrons can be found similarly. The mean kinetic energy of electrons in the transverse directions is  $\frac{1}{2} k_B T$  each according to the equipartition theorem. Therefore, the thermal flow density is given by:

$$Q_R(T) = \int_{q\Phi}^{+\infty} (E_x + k_B T) N(E_x) dE_x = J_R(T) \left(\Phi + \frac{2k_B T}{q}\right). \tag{2.5}$$

To collect the thermionically emitted electrons, an electric field is applied between an emitter and a collector. In addition to this linear field, an electron also experiences a force due to its image charge. Accordingly to this image charge, the potential profile of an electron is modified as seen in Fig. 4.

Figure 4. Potential barrier between two electrodes modified by image charges.

The potential of an electron between two conductors is given by [3]:

$$V(x) = \frac{\Phi_A}{q} - \frac{V_{bias} + \Phi_A - \Phi_B}{d} x - \frac{q}{4\pi\varepsilon_0} \left[ \frac{1}{4x} + \frac{1}{2} \sum_{n=1}^{\infty} \left( \frac{nd}{n^2 d^2 - x^2} - \frac{1}{nd} \right) \right], \tag{1.6}$$

where d is the gap between the electrodes and  $V_{bias}$  is the applied bias voltage. The last summation terms are included to account for an infinite number of the image charges reflected on both emitter and collector surfaces. The maximum of the potential barrier is no longer located at x=0, but is located at some distance away from the emitter surface. The maximum height of the barrier is also reduced, which lowers the effective work function and increases the amount of thermionic emission. This increase in current is called the Schottky effect, and is appreciable with fields in order of  $10^4$  V/cm or greater. Figure 5 shows barrier height reduction due to the Schottky effect as function of emitter-collector separation for various applied bias voltages. The emitter and collector are assumed to have the same work functions in this calculation. As seen from this graph, the barrier height decreases by several tenth eV when the field strength is on the order of  $10^6$  V/cm range. This electric field corresponds to gaps of a few nanometers to a few tens of nanometer when the applied bias voltage is a few volts.

Figure 5. Barrier height reduction due to Schottky effect for various applied voltages, both electrodes are assumed to have the same work function.

With the barrier height reduction as result of the Schottky effect and the work function lowering by covering the surface with a sub-monolayer of an alkali metal with oxygen additives is it possible to create barrier heights around the 0.4 eV, or even lower. With such a lower barrier it is theoretically possible to make a thermionic refrigerator working at room temperature.

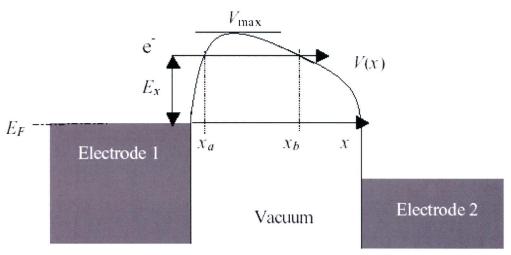

#### 2.2 Theory of thermo tunneling

Field emission is another mechanism for extracting electrons from the surface. Such emission occurs when a very strong electric field is applied, reducing the potential barrier width and making it permeable for electrons to tunnel.

The probability that an electron will penetrate a potential barrier of height V(x) (assuming the barrier to be in the x-direction) can be found by the Wentzel-Kramer-Brillouin (WKB) approximation:

$$D(E_x) = \exp\left[-\frac{2}{\hbar} \int_{x_b}^{x_a} \sqrt{2m(V(x)q - E_x)} dx\right],$$

(1.7)

where  $x_a$  and  $x_b$  are the roots of V(x)q- $E_x$ =0 (Fig. 6), V(x) defined by equation 1.6 and  $E_x$ = $\frac{1}{2}m_e v_x^2$ .

Figure 6. Potential barrier between two electrodes with an electron tunneling through the vacuum.

Assuming that the electrons are at thermal equilibrium, the tunneling current is obtained by:

$$J_{tun} = q \int_{-\infty}^{qV_{max}} D(E_x) N(E_x) dE_x, \qquad (1.8)$$

where  $N(E_x)$  is the number of electrons incident on unit area in unit time with kinetic energy in x direction in the range  $E_x$ ,  $E_x+dE_x$ , as given by expression 1.3. The amount of energy carried by the tunneling electrons is similarly obtained by:

$$Q_{tun}(T) = \int_{\infty}^{qV_{max}} (E_x + k_B T) D(E_x) N(E_x) dE_x, \qquad (1.9)$$

$k_BT$  is included to account for kinetic energy in transverse directions.

To maintain the charge neutrality of the emitter electrode, the emitted electrons are replaced by electrons at the Fermi level. This is why it is important to prevent that also a lot of electrons below the Fermi level will tunnel. Because when there is a significant amount of emission originating below the Fermi level, the emitter will become hot instead of cold. For this reason, the potential barrier cannot be to low.

# Calculation of expected cooling power by combined thermionic emission and thermo tunneling.

As discussed in the two previous sections, work functions around 1 eV can be obtained by forming sub-monolayer coverage of alkali metals with oxygen additives. Further reduction in the barrier height is possible by application of a strong electric field and because of image charges of emitting electrons as already mentioned. A work function reduction of 0.3 - 0.5 eV is expected for  $E = 1 \sim 2 \cdot 10^6$  V/cm or bias voltage of  $1 \sim 2$  V across a 10 nm gap. This chapter illustrates calculations performed to estimate current and cooling power densities for emitters with work functions of  $0.8 \sim 1.2$  eV.

#### 3.1 Electron energy distribution

At thermal equilibrium, the electrons in a metal or semiconductor have an energy distribution given by the Fermi-Dirac distribution function. The electrons, which have enough energy to surmount or penetrate the potential barrier at the surface, will escape into the vacuum and travel to the collector. The electrons emitted from the surface form a new energy distribution after being filtered by the potential barrier. Therefore, it is important to keep track of the energy distribution of the electrons in order to calculate the energy carried by the electrons.

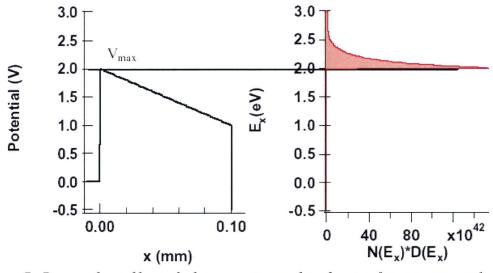

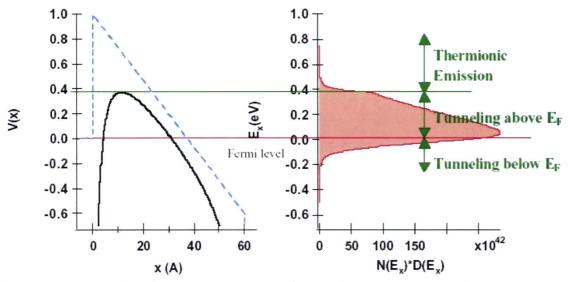

An example of an electron energy distribution for a conventional thermionic device is shown in Fig. 7. The work function is 2.0 eV, the applied bias is 1.0 V, the distance between electrodes is 0.1 mm and the temperature is 1500 K.

Figure 7. Potential profile and electron energy distribution for conventional thermionic emission.  $\Phi = 2.0 \text{ eV}$ , the applied bias is 1.0 V, the distance between electrodes is 0.1 mm and the temperature is 1500 K.

In this example, the vast majority of the electrons that escape into the vacuum have energies greater than the potential barrier height, because the tunneling current is negligible due to the relatively small electric field and large vacuum gap. Because of the high temperature, there are a significant number of electrons populating the high-energy states. For this nearly pure thermionic emission case, the Richardson equation (1.4) can be employed to find the current density. When the temperature is around 300 K (room temperature), almost no electrons populate the high-energy states. This implies that at room temperature there are almost no electrons that are able to escape into the vacuum and there is almost no thermionic current. Consequently the thermionic cooler will not work at a room temperature, when the work function is 2.0 eV.

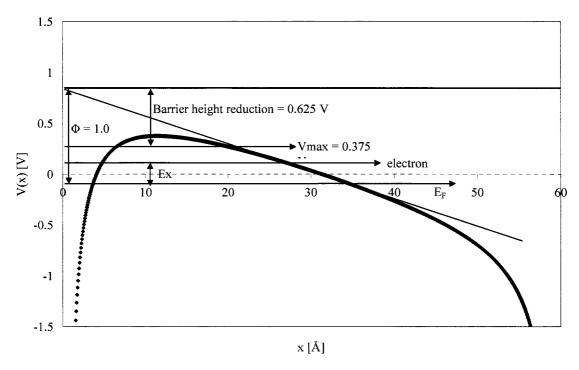

Figure 8 shows an electron energy distribution for a much smaller gap as proposed for the integrated cooling of IC's. In this example, the gap between emitter and collector is only 60 Å, the bias voltage is 1.6 V, the temperature is 300 K and both electrodes have a work function of 1.0 eV.

Figure 8. Potential profile and electron distribution for a very narrow electrode separation at 300 K. The applied bias voltage is 1.6 V, the emitter-collector distance is 60 Å and the work function is 1.0 eV for both electrodes. The dominant emission comes from tunneling above the Fermi level. The dashed line is the potential profile without distortion due to the image charge effect.

The barrier height, as calculated with equation 1.6, is significantly reduced, from  $\Phi = 1.0 \text{ eV}$  to 0.375 eV, a reduction of 0.625 eV, due to a distortion of the potential profile by a combination of the strong electric field and the image charge effect. The emitted electrons consist of those with enough energy to surmount the barrier and those tunneling through the barrier. In the case of conventional field emission electrons are originating in the neighborhood of the Fermi level. If electrons are origination below the Fermi level. They would cause the emitter heat-up, because they will be replaced by electrons at the Fermi level. In the case of Fig. 8, a large number of tunneling electrons originate above the Fermi level, taking heat away from the emitter. In fact, these hot tunneling electrons constitute the majority of the emission and energy transport in this case.

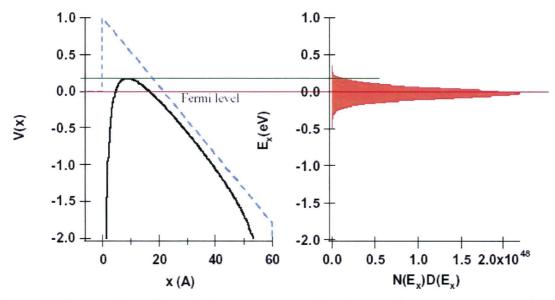

Figure 9 shows the electron energy distribution with the same conditions as the previous case except with a larger bias voltage (2.8 V). In this case, electrons originating below the Fermi level are dominant, consequently heating up the emitter instead of cooling it.

Figure 9. Potential profile and electron energy distribution for a very narrow electrode separation at 300K. The applied bias voltage is 2.8 V, the emitter-collector distance is 60 Å and the work function is 1.0 eV for both electrodes. The dominant emission comes from tunneling below the Fermi level, thus heating the emitter. The dashed line is the potential profile without distortion due to the image charge effect.

There is a range of electric field strength in which electrons originating above the Fermi level are dominant and thereby cool the emitter at room temperature even if the emitter has a work function as high as 1.0 eV. The strength of the electric field is therefore critical, as the emission goes into the heating regime when an excessively strong field is applied.

#### 3.2 Current and cooling power densities

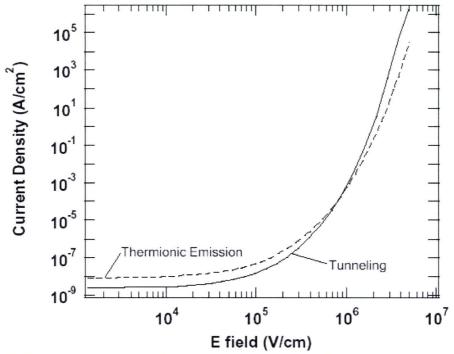

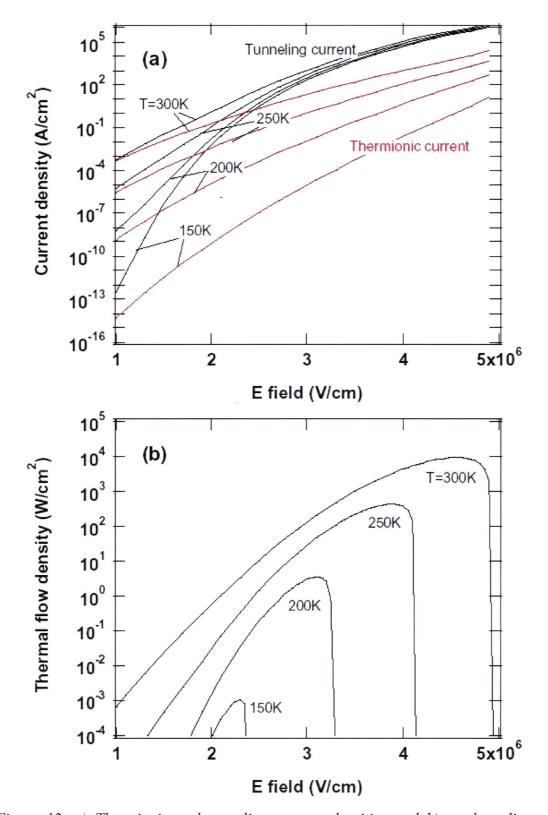

Once the electron energy distribution is obtained, it can be integrated to find the current density across the gap. Integrating the distribution from the barrier maximum to infinity with respect to  $E_x$  gives thermionic emission current. Integration below the barrier height gives the tunneling current. Figure 10 shows both types of current as a function of electric field for the case of a narrow electrode gap (100 Å) at room temperature (300K).

Figure 10. Thermionic and tunneling current density as a function of electric field at 300K. For a work function of  $\Phi = 1.0 \text{ eV}$  and the gap between the electrodes is 100 Å.

When the electric field strength is less than  $10^5$  V/cm, the current is negligible for the purpose of cooling. The tunneling current is smaller than the thermionic current in this range. When the electric field is larger than  $10^5$  V/cm, both currents start to increase rapidly, and reach a useful level (>1 A/cm² [2]) above ~  $2 \cdot 10^6$  V/cm. In this range of electric field, the tunneling current constitutes the major part of the total current. Therefore, it is necessary to calculate not only the thermionic emission density but also tunneling current density and their energy distributions in order to accurately calculate the thermal flow when the electrode gap is in nanometer range.

As can be seen in Fig. 10, the applied electric field is an important parameter for the current and thus also for the cooling power. Figure 11 shows a) current and b) cooling power densities as a function of the electric field strength for various gaps between emitter and collector with  $\Phi=1.0$  eV and T=300K. The cooling power is calculated by summing the contributions from thermionic and tunneling emission, as calculated with equations 1.5 and 1.9. For  $E>2\cdot10^6$  V/cm, the tunneling current density is one or two orders of magnitude larger than thermionic current density. This situation resembles the normal field emission case. However, as stated previously, tunneling electrons could become a dominant cooling component if they originate above the Fermi level. If the electric field becomes too high  $(E>5\cdot10^6$  V/cm), a significant part of the tunneling electrons originates below the Fermi level, which results in heating instead of cooling. This can be seen by the fast decreasing thermal flow density in Fig. 11b.

Figure 11. a) Thermionic and tunneling current densities and b) total cooling power densities as a function of electric field for various emitter-collector gaps at 300 K,  $\Phi = 1.0$  eV for both electrodes.

Both tunneling and thermionic current densities strongly depend on the electric field and have a weak dependence on the emitter-collector gap above 50 Å. However, below a gap of  $\sim$ 30 Å, a large tunneling current originating around the Fermi level begins to flow, which is detrimental to cooling. Therefore, for the purpose of cooling the emitter-collector gap must be kept above  $\sim$ 40 Å. Cooling power for the case of 30 Å is negative (heating the emitter) throughout this field range, and cannot be shown in this semi-log graph. Maybe the most important thing, which can be seen from Fig. 11b is that a cooling power of almost  $10^4$  W/cm<sup>2</sup> can be reached at room temperature.

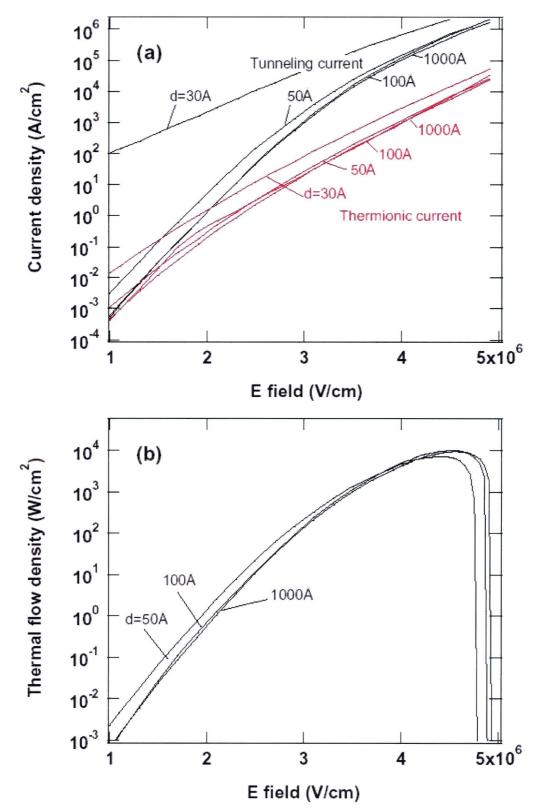

Figure 12 shows current densities and cooling power densities as a function of electric field at different temperatures for the case of emitter-collector gap of 100 Å and  $\Phi = 1.0$  eV. Thermionic current has a strong dependence on temperature since the electron population at high energy levels rapidly changes with temperature, whereas the tunneling current has a weaker dependence especially for  $E > 2.5 \cdot 10^6$  V/cm.

Cooling power on the order of a few W/cm<sup>2</sup> is expected even at temperatures as low as 200 K. In thermionic cooling, thermal conduction is absent (limited only by radiation), this implies that thermionic/tunneling cooling is capable of sustaining a large temperature difference between the cathode and the collector, because there is vacuum between them.

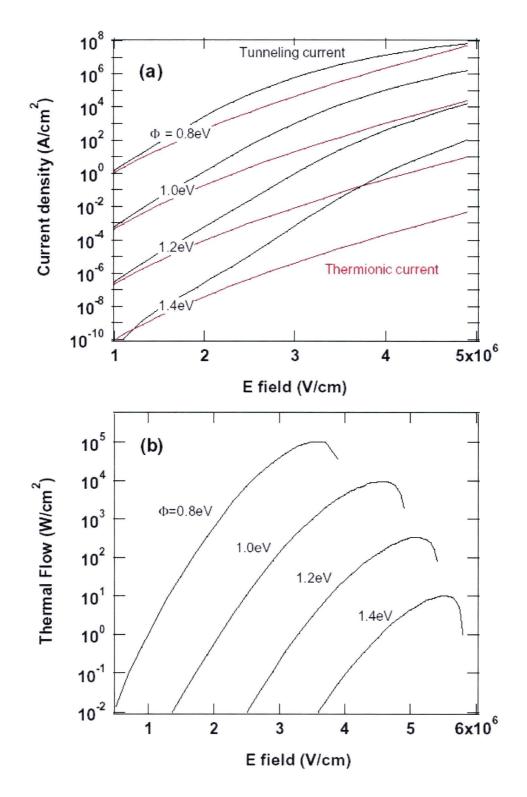

Figure 12. a) Thermionic and tunneling current densities and b) total cooling power densities as a function of electric field for different temperatures. The emitter-collector gap is 100 Å and  $\Phi = 1.0 \text{ eV}$  for both electrodes.

Figure 13 shows a) thermionic and tunneling current densities and b) cooling power density as a function of electric field at 300 K with an emitter-collector gap of 100 Å for work functions of 0.8, 1.0, 1.2 and 1.4 eV. Figure 13 shows that for a low work function, a small difference between thermionic and tunneling current densities occurs. Consequently, for emitters with small work functions, emission currents become more thermionic-like and result in more energy carried per electron (larger Peltier coefficient).

As expected, the smaller the work function, the more cooling power is obtained and the smaller the electric field requires to reach the maximum cooling power which improves cooling efficiency. With use of nanometer gap ( $\sim$ 6 nm) between emitter and collector, a work function as large as 1.4 eV is expected to produce a cooling power of few tens of W/cm<sup>2</sup> at room temperature.

#### 3.3 Conclusion

In summary, dependences of thermionic and tunneling currents on electric field, emitter-collector vacuum gap, temperature and work function are explored. It is found that for a range of electric field ( $1 \sim 5 \cdot 10^6 \text{ V/cm}$ ), tunneling current becomes the dominant component of electron emission and provides the major contribution to the thermal flow density. In theory, a combination of a strong electric field (> $10^6 \text{ V/cm}$ ) and an image charge potential can significantly lower the work function, which may open a window of possibility for cooling at room temperature by combined thermionic emission and thermo tunneling. It is found from the calculations that an emitter with a work function as large as 1.0 eV is capable of producing a cooling power on the order of  $1000 \text{ W/cm}^2$  at room temperature, when an electric field of  $3 \sim 4 \cdot 10^6 \text{ V/cm}$  is applied. In addition, refrigeration down to 200 K is possible. However, making such a cooling device is not obvious, this is why the next chapter discusses a practical implementation.

Figure 13. a) Thermionic and tunneling current densities an b) cooling power density as a function of electric field for various work functions at T = 300K.

# Practical implementation: the fabrication of an integrated cooler in silicon

To make an efficient cooling device, based on combined thermionic cooling and thermo tunneling, an emitter and collector separated by several nanometers are needed. The distance between the emitter and collector must be constant within a tolerance of 5 % of the separation [4], over a surface as big as the device that is cooled. The local electric field can become too high if the separation is not constant within the tolerance, which results in heating instead of cooling. This means that the surface roughness may not be more than a few Angstroms. Furthermore, the spacing between the emitter and collector must be vacuum, to prevent a thermal leak over the gap in reverse direction by conduction and convection. An additional complication is that the emitter and collector will bend to each other as a result of the pressure difference between the nanometer gap and the surrounding of the device. To prevent the bending, small spacers between the emitter and collector are necessary. The spacers have to be both a thermal and electrical insulator to prevent heat and current flowing through the spacers. The most efficient way to cool electronics is to integrate the cooling device directly underneath the electric circuit. Silicon is an attractive material for the fabrication of such a cooling device because:

- Electric circuits are most of the time made in silicon.

- Silicon wafers have an extremely flat surface.

- Nanometer lithography is possible on silicon.

- It is possible to grow a layer of several nanometers SiO<sub>2</sub> on top of a wafer to make the spacers. SiO<sub>2</sub> is an electrical and thermal insulator.

Consequently, it is interesting to investigate the possibility to integrate a cooling device in silicon.

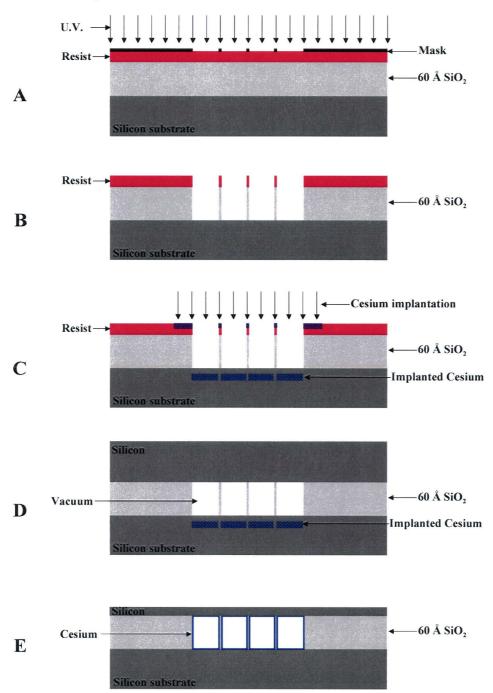

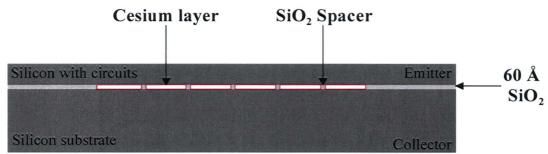

The basic technology required for the fabrication of the cooling device is wafer bonding. A cooler can be constructed when two flat silicon wafers with a very thin patterned oxide layer acting as a spacer are wafer-bonded. To lower the work function of the silicon surface half a monolayer of cesium on the surface is required. However, this cannot be deposited prior to vacuum wafer bonding, because of two reasons. For fusion bonding two very clean and hydrophilic surfaces are necessary, so when there is some cesium on the silicon or SiO<sub>2</sub> surface, fusion bonding is hampered. The second reason is that cesium is reactive with oxygen gas in the atmosphere. Consequently it is important that the spacing between the emitter and collector is vacuum before the cesium will be applied on the surface. A suitable technology to apply the Cs might be ion implantation. Cs can be implanted underneath the silicon surface and subsequently to diffuse it to the surface after fusion bonding in vacuum.

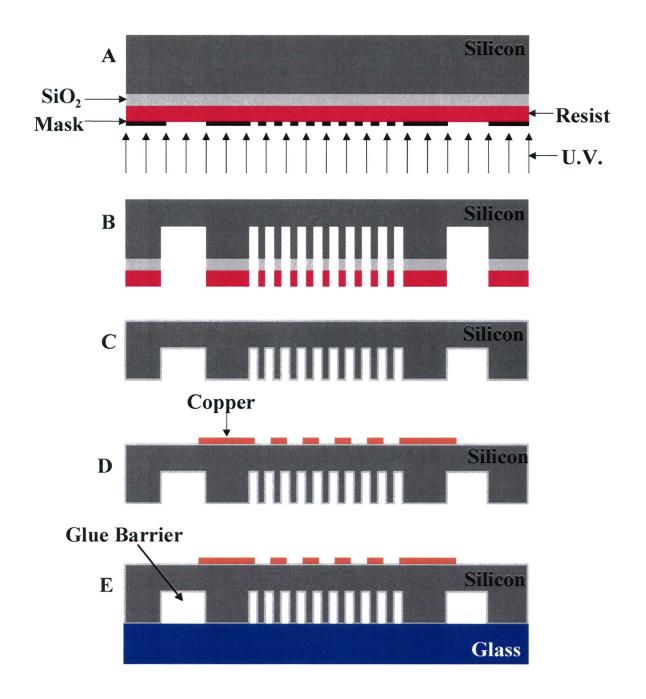

The following procedure is proposed to fabricate a device for combined thermionic cooling and thermo tunneling. The most important process steps are shown in Fig. 14. The silicon wafers are heavily doped, to decrease the electrical resistance (lowest resistance:  $n^{++}$  3-6 m $\Omega$ cm), and are polished to obtain a very flat surface to create a constant emitter-

collector separation. The organic contamination layer on top of the wafer needs to be removed. This is done by cleaning the wafer, for 10 minutes, in concentrated sulphuric acid (H<sub>2</sub>SO<sub>4</sub>, 96 %) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, 31 %) mixture at 90 °C (Piranha clean). After the wafer is cleaned a layer of 60 Å SiO<sub>2</sub> is grown by dry oxidation. The wafer is cleaned again with Piranha, to supply the surface with OH-groups. Before the resist is spincoated, the wafer is HMDS (HexaMethylDiSilazane) primered to improve the adhesion between the SiO<sub>2</sub> layer and the resist. On top of this SiO<sub>2</sub> layer a layer of resist (AZ111XF, Micro Chemicals) is spincoated, with a thickness of 1 µm (4000 rpm). After the resist is applied by spin coating, the wafer is put on a hotplate (90 °C, 1 minute) to bake the resist. To pattern the spacers in the resist, the wafer is exposed to ultraviolet light using I-line stepper lithography (Fig. 14 A). Because the ultraviolet light changes the chemical properties of the positive resist, it is possible to remove the resist only on the positions where it was exposed by developing the wafer for 1 minute in developer AZ303 1:4 (Micro Chemicals). Wet etching with buffered HF (20:1, 32.5 nm/min) is used to remove the SiO<sub>2</sub> at the positions where the resist was exposed and developed. Wet etching is proposed since it will not affect the silicon surface (Fig. 14 B). The next step is implanting the cesium underneath the silicon surface. The resist is again used as a mask to prevent the cesium going into the SiO<sub>2</sub> (Fig. 14 C). To be sure the cesium is implanted underneath the silicon surface, an implantation energy of 200 keV is used. After the cesium has been implanted, the resist needs to be removed. This is done by a resist strip in a IPC Barrel (Branson) (60 Minutes of plasma-oxide (800W, 130°C)). Both surfaces have to be clean and hydrophilic before they can be bonded, this is why the wafers first get a Piranha clean. Another heavily doped silicon wafer is bonded on top of the SiO<sub>2</sub> layer using fusion bonding. The bonding is done in vacuum, to be sure the spacing between the emitter and collector is vacuum (Fig. 14 D). After the fusion bonding the two wafers get an anneal at 1000 °C in N<sub>2</sub> to make the binding between the new silicon wafer and the SiO<sub>2</sub> layer stronger and to diffuse the cesium to the surface between the two wafers. The last process step is to grind and polish the upper wafer to a thin layer of silicon. This layer cannot be too thin, because it has to handle a pressure drop of 1 bar.

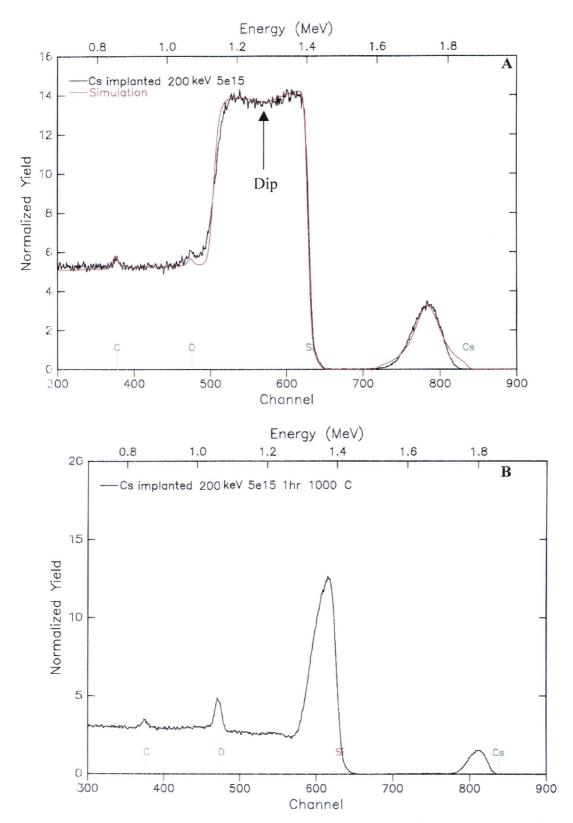

The critical step in the proposed fabrication procedure is the Cs migration towards the silicon surface after ion implantation and wafer bonding. Some research has been carried out to investigate the feasibility of this concept. To investigate whether if the implanted cesium will diffuse to the surface during annealing, some Rutherford Backscattering Spectrometry (RBS) measurements have been done on silicon wafers implanted with Cs (a 2 MeV He<sup>+</sup> ion beam is used, the detection angle is 77.2° and the sample is channeled). For this purpose, 5•10<sup>15</sup> cesium atoms/cm<sup>2</sup> have been implanted with an energy of 200 keV in a silicon wafer. The RBS spectrum direct after implantation is shown in Fig. 15 A. The mean implantation depth of the cesium is 800 Å and the FWHM is 700 Å. The thickness of the amorphous silicon layer formed during ion implantation is 1760 Å. The oxygen signal is a result of a native silicon oxide layer on top of the silicon wafer. The carbon signal is a result of the carbon contamination layer, which is deposited on top of the wafer during the measurement. The dip in the amorphous silicon signal is because of the presence of the cesium at that depth. In order to investigate the Cs migration process towards the surface another part of the implanted wafer is first annealed for one hour at a temperature of 1000 °C before it is measured with RBS. The RBS spectrum of this measurement is shown in Fig. 15 B. The cesium signal is now much smaller (1.5•10<sup>15</sup> cesium atoms/cm<sup>2</sup>) and the signal is also shifted to a higher channel. This implies that the

cesium is diffused in the direction of the surface and already 70% of the cesium atoms have reached the surface and have evaporated. The amorphous silicon signal is also much smaller. This is a result of re-crystallization of the silicon atoms during the temperature anneal. The amorphous layer thickness is now 540 Å. Another result of the annealing is the increase of the  $SiO_2$  layer thickness.

Figure 14. Most important process steps to make an integrated cooling device in silicon, based on thermionic emission and thermo tunneling.

Figure 15. RBS spectra of a silicon wafer implanted with  $5 \cdot 10^{15}$  cesium atoms/cm<sup>2</sup> with an energy of 200 keV, before A) and after B) a 1 hour temperature anneal at 1000 °C.

#### **Discussion**

In this section the operation of a practical device based on realistic dimensions and process parameters is discussed. At first we assume that it is possible to lower the work function of silicon from 4.7 eV to 1.0 eV, by covering the surface with half a monolayer of cesium (with oxygen additives) as discussed before. Based on the design rules required for cooling and following the fabrication process described in chapter 4, the spacing between emitter and collector is chosen as d = 60 Å and the bias voltage over the gap  $V_{Bias} = 1.6$  V (Fig. 16)

Figure 16. Vacuum gap of 60 Å, made by silicon processing and wafer bonding as discussed before.

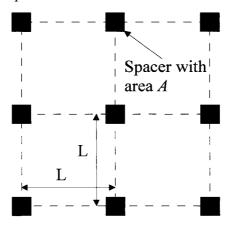

Furthermore, it is assumed that the silicon top layer has a thickness of  $10~\mu m$ , the silicon substrate a thickness of  $500~\mu m$  and the  $SiO_2$  layer (and also the spacing between emitter and collector) a thickness of 60~Å. The spacers between the emitter and collector are needed to prevent bending of the wafers, because of the vacuum in between. The spacer density can be determined by calculation the deformations due to the applied pressure [5]. There are three deformations due to this pressure:

- 1. The silicon top layer and substrate bends due to the pressure difference.

- 2. The spacer height d changes an amount  $\Delta d$  due to the applied pressure.

- 3. The spacer deforms the silicon top layer and substrate locally  $(u_0)$ . This deformation will be ignored in the calculation of the spacer density.

The total deformation must be smaller than the tolerance.

The deflection due to bending can be calculated with:

$$\delta = C_{\delta} p L^4 D^{-1} \quad , \tag{1.10}$$

where  $C_{\delta}$  a constant, dependent on the geometry,  $C_{\delta}$  =0.00581 in the case of an array of spacers [5], with a distance L between the centers of the spacers (Fig. 17). D is the flexural rigidity of the plate give by:

$$D = \frac{Eh^3}{12(1-v^2)},\tag{1.11}$$

where E is Young's modulus ( $E_{Si}$  = 170 Gpa and  $E_{Siliconoxide}$  = 72 Gpa) and v the Poisson ratio ( $v_{Si}$  = 0.3 and  $v_{Siliconoxide}$  = 0.2), h is the thickness of the silicon layer.

The change in spacer height  $(\Delta d)$  can be calculated with:

$$\Delta d = \frac{d}{A} \frac{F}{E},\tag{1.12}$$

where d the spacer height, A the contact area between the silicon and the spacer and F the force acting on an individual spacer.

Figure 17: Array of spacers, with contact area A and a distance L between the centers of the spacers.

To estimate the distance between the spacers (L) it will be assumed that deformation due to bending must be smaller than 2 Å. This implies that the distance between the spacers must be smaller than 10  $\mu$ m (equation 1.10 and 1.11). To estimate the size of the spacers it will be assumed that the change in spacer height  $(\Delta d)$  must be smaller than 1 Å. This results in  $A \approx 8 \ \mu\text{m}^2$  (equation 1.12). The spacer density must be larger than 8 % of the total surface to prevent exceeding the tolerance due to mechanical deformation.

For the calculation of the cooling power using the theory described in chapter 2, we take a spacer density of 8 % of the total surface, and a working temperature of 300 K. The potential barrier for this situation calculated with formula 1.6 is given in Fig. 18, the work function reduction by a combination of the strong electric field and the image charge effect is 0.625 eV.

The applied voltage over the vacuum gap is 1.6 V. In first approximation it is assumed that the resistance of the silicon emitter and collector can be neglected because heavily doped silicon is used. Consequently it is assumed that the voltage over the total device (emitter vacuum and collector) is also 1.6 V by approximation. The thermal cooling power of the device described above can be calculated using the thermionic current (equation 1.4) and the thermo tunneling current (equation 1.8) The sum of the thermionic and tunneling current is  $2.25 \cdot 10^2$  A/cm<sup>2</sup> and the cooling power is 35.3 W/cm<sup>2</sup> (equation 1.5 and 1.9). When the resistance of the silicon is assumed to be 3 m $\Omega$ cm and the total silicon thickness is 510 µm, the voltage drop over the silicon substrate is  $V = R \cdot I = 3 \cdot 10^{-3} \cdot 510 \cdot 10^{-4} \cdot 2.25 \cdot 10^2 = 0.03$  V. If we assume that there is also a heat dissipation of 35.3 W/cm<sup>2</sup> in the electric circuit on top of the emitter we obtain stationary situation. As result of the bias voltage and the thermionic and tunneling current, a power of  $3.60 \cdot 10^2$  W/cm<sup>2</sup> ( $P = I \cdot V$ ) will be dissipated in the top layer of the silicon substrate, because there is no dissipation in the

vacuum gap. The electrons, which reach the collector, are decelerated in the top layer of the silicon substrate by collisions and will give their energy to the silicon atoms. Consequently, the total heat flux in the silicon substrate is the sum of the cooling power and the joule heating in the top layer of the silicon substrate.

Figure 18. The potential barrier profile V(x) versus x, for  $\Phi = 1.0$  eV, emitter-collector separation of 60 Å,  $V_{Bias} = 1.6$  V. The Barrier height reduction is 0.625 eV.

This heat is transported to the bottom of the substrate by conduction. The temperature difference between the top layer and the bottom of the silicon substrate can be calculated with Fourier's law:

$$\vec{q} = -k\vec{\nabla}T, \tag{1.13}$$

with q the heat flux, k [Wm<sup>-1</sup>K<sup>-1</sup>] the thermal conductivity of the material. The top layer of the silicon substrate will reach a temperature of 320 K when the bottom of the substrate is kept at room temperature (300 K). This is no problem, when there is vacuum between the emitter and collector. But because spacers are needed to maintain the gap, a heat leak through the spacers will be present. This heat leak is always in the direction of the emitter, because the principal of the cooling mechanism implies that the temperature of the top layer of the substrate always is higher than the emitter temperature. When the temperature difference over the spacer is 20 K, the spacer thickness is assumed to be 60 Å and the spacer density is 8 % of the total surface, the heat leak through the spacers is  $3.77 \cdot 10^6$  W/cm<sup>2</sup>. This implies that the heat flow through the spacers is much higher than the cooling power.

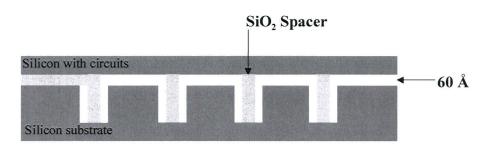

It is possible to decrease this heat leak by decreasing the spacer density. The problem is then that the bending of the silicon and the deformation of the spacers will exceed the tolerance. The heat leak through the spacers is still  $4.66 \cdot 10^3$  W/cm<sup>2</sup> when the spacer density is only 0.01 %. A solution is to use thicker oxide spacers located in recesses in the wafer surface as shown in Fig. 19. However, this is quite complicated to make and it is much more difficult to create a gap with a constant distance between emitter and collector. The difference in the expansion coefficient between silicon and SiO<sub>2</sub> makes it more difficult to maintain a constant gap.

Figure 19. New design for a vacuum gap of 60 Å, now with longer spacers to reduce the heat leak through the spacers.

#### **Conclusion**

In this chapter, the feasibility of the concept for cooling by combined thermionic emission and thermo tunneling to vacuum will be reviewed. In theory, a combination of a strong electric field (>10<sup>6</sup> V/cm) and an image charge potential can significantly lower the work function, which may open a window of possibility for cooling at room temperature by combined thermionic emission and thermo tunneling. The theory described in chapter 2 shows that a material having a work function of 1.0 eV is capable of producing a cooling power in order of 100-1000 W/cm<sup>2</sup> at room temperature. However, making such a cooling device is not obvious and there are some practical problems. The first problem is that the spacing between the emitter and collector must be constant within 5 % of the spacing length. This implies that the roughness of the emitter and collector must be less than a few Angstroms given a required vacuum gap of approximately 60 Å. The surface roughness of most materials is already much larger. However, silicon has one of the flattest surfaces (in the order of some Angstrom), which maybe provides the opportunity to integrate cooling devices in silicon, closely situated to the heat producing electrical circuits. But even if the roughness of silicon is small enough, the constant spacing is still a problem. This is because the spacing between emitter and collector must be vacuum. This results in a pressure drop over the silicon and the result of this pressure drop is bending of the silicon. To prevent this bending, spacers between emitter and collector are needed. These spacers must be electrical and thermal insulators to prevent the electrons going through the spacers instead of going through the vacuum and to prevent a heat leak back to the emitter. Fortunately, SiO<sub>2</sub> is a good electrical and thermal insulator. Its compatibility with IC technology allows to grow a layer of several nanometers SiO2 on top of a silicon wafer and to make the spacers really small. A spacer density of 8 % of the total surface is needed to prevent the deformations exceeding the tolerance. This density results in a heat leak much larger than the cooling power. Because of this heat leak, the cooling device cannot work at room temperature.

Another topic that has to be addressed is the lowering of the work function. The work function of the silicon surface needs to be decreased to a value around 1 eV. In principle, this can be achieved by covering the surface with cesium as discussed in chapter 2. A number of potential problems have to be investigated: the resulting roughness of the surface, possibly the diffusion of cesium into the SiO<sub>2</sub>, or the formation of a conductive layer of cesium on the spacer sidewalls. Because of all these practical problems, a cooling device based on thermo tunneling and thermionic emission is not possible within the present experimental tolerances.

#### Reference

- [1] D.M.Rowe, "CRC Handbook of Thermoelectrics," CRC Press LLC, 1995.

- [2] G.D. Mahan, "Thermionic refrigeration," J. Appl. Phys., vol. 76 (7), pp. 4362-4366, October 1994.

- [3] Y. Hishinuma, "Refrigeration by combined tunneling and thermionic emission in vacuum: Use of nanometer scale design," *Appl. Phys. Lett.*, vol. 78 (17), pp. 2572-2574, 23 April 2001.

- [4] Y. Hishinuma, "Refrigeration by combined tunneling and thermionic emission in vacuum: Use of nanometer scale design," Dissertation thesis, November 2002.

- [5] P.C.P. Bouten, "On the Deformation of Flexible Displays," Nat.Lab. Technical Note 2000/237, October 2000.

# PART II Forced convection through micro-channels

#### Introduction

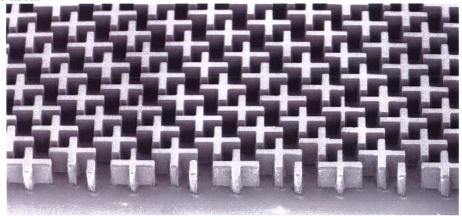

One of the most commonly applied cooling principles is forced convection. In the second part of this thesis, integrated cooling of electronic circuits by a single-phase flow through rectangular micro-channels machined in the backside of a silicon wafer will be discussed.

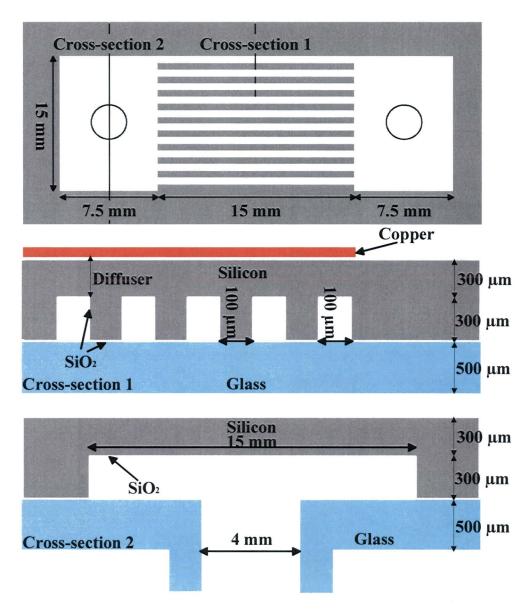

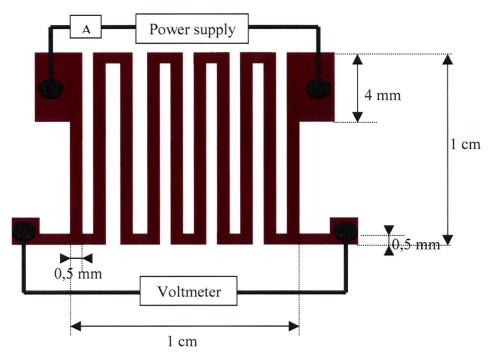

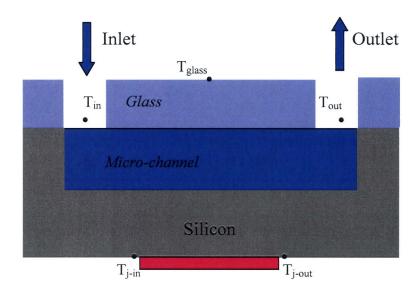

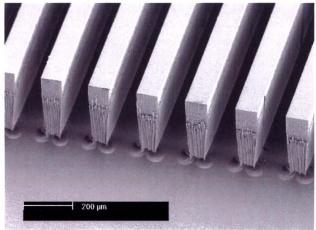

Figure 1. The geometry of the micro-channels in the backside of a silicon wafer. The final device has a total number of 75 channels.

By integration into the silicon wafer, space can be saved and intermediate layers between the integrated circuit (IC) and the micro-channels, which may act as thermal barriers, are eliminated.

The geometry of the fabricated and used micro-channels is shown in Fig 1. Water is selected, as working fluid, because of its good thermal and hydraulic properties. Especially the high heat capacity and relative low viscosity, makes water a suitable cooling medium.

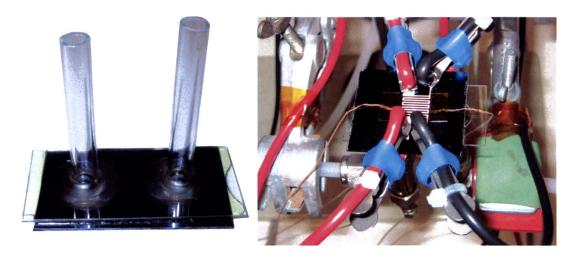

First of all, the theory about active cooling with use of an active flow through micro-channels will be reviewed. With use of this theory the proposed micro-channels are analysed by solving (numerically) the heat transfer problem consisting of a simultaneous determination of the temperature field both in the solid substrate and in the flowing liquid. After the theory is reviewed, the fabrication of integrated micro-channels in silicon will be discussed, together with the sealing steps. Subsequently an experimental setup will be described which was build to measure the cooling capacity of a micro-channel cooling device. The results of the measurements will be discussed and compared with the calculations, followed by a general evaluation and the conclusions.

## Chapter 2

## **Theory**

#### 2.1 Heat transfer basics

Heat transfer is energy in transit due to a temperature difference. Whenever a temperature difference exists in a medium or between media, heat transfer will occur. Different modes for heat transfer processes exist. The term conduction is used when a temperature gradient exists in a stationary medium. In this situation, the heat transfer will occur across the medium by atomic or molecular collisions or by collective vibrations such as phonons. The term convection refers to heat transfer in a moving fluid or gas by the collective movement of molecules or diffusion. The third mode of heat transfer is by emission of electromagnetic waves, called radiation. All surfaces of finite temperature emit electromagnetic waves, with an energy depending a.o. on the surface temperature. Hence, in the absence of an intervening medium, there is still heat transfer by radiation between two surfaces at different temperatures.

In order to characterize heat transfer between two objects/places A and B in contact, thermal resistance is introduced as an analogy with electric resistance. It links the temperature difference between A and B with the heat flux P[W]. The thermal resistance  $[KW^{-1}]$  can be expressed as:

$$R_{th} = \frac{T_A - T_B}{P} \,, \tag{2.1}$$

where  $T_A > T_B$ .

#### 2.1.1 Conduction

Conduction can be seen as the transfer of energy from the more energetic to the less energetic particles of a material due to interactions between the particles. The heat flux vector  $\vec{q}$  [Wm<sup>-2</sup>] is the heat transfer rate per unit area perpendicular to the direction of heat transfer, and is proportional to the temperature gradient:

$$\vec{q} = -k\vec{\nabla}T, \qquad (2.2)$$

with k [Wm<sup>-1</sup>K<sup>-1</sup>] the thermal conductivity of the material. This equation is known as Fourier's law. The minus sign is a consequence of the fact that heat is transferred in the direction of decreasing temperature. The power flux P [W] is defined as:

$$P = \frac{dQ}{dt} = \iint_{S} \vec{q} \cdot \vec{n} \cdot dS \,, \tag{2.3}$$

dQ [J] represents the elementary quantity of energy handed over by an arbitrary surface S characterized by the local vector  $\vec{n}$  perpendicular to the elementary surface dS.

#### 2.1.2 Convection

The convection heat transfer mode is comprised of two mechanisms. In addition to energy transfer due to diffusion, there is also energy being transferred by the bulk, or macroscopic, motion of the fluid (or gas). The fluid motion is associated with the fact that, at any instant, large numbers of molecules are moving collectively. Such motion, in the presence of a temperature gradient, will give rise to heat transfer. The molecules retain also their random motion, which leads to diffusion in presence of a temperature gradient. The total heat transfer is the superposition of energy transport by the random motion of the molecules and by the bulk motion of the fluid. It is customary to use the term convection when refereeing to this cumulative transport and the term advection when referring to transport due to bulk motion only.

For micro-channel cooling, heat transfer due to convection between a fluid in motion and a boundary surface has to be considered. A consequence of fluid flow is the development of a region in the fluid through which the velocity varies from zero to a finite value  $u_{\infty}$ , associated with the bulk flow. This region is known as the hydrodynamic boundary layer. Moreover, if the surface and fluid differ in temperature, there will be also a region of the fluid through which temperature varies from  $T_S$ , the temperature of the surface, to  $T_{\infty}$  in the outer flow. This region, called the thermal boundary layer, may be smaller, larger or the same size as the hydrodynamic boundary layer. If  $T_S > T_{\infty}$ , convection heat transfer will occur between the surface and the outer flow. The diffusion dominates near the surface, where the fluid velocity is low. In fact, at the interface between the fluid and the surface, the fluid velocity is zero and heat is transferred only by this mechanism. The contribution due to bulk fluid motion originates from the fact that the thermal boundary layer grows as the flow progresses. In effect, the heat that is transported into this layer is swept downstream and is eventually transferred to the fluid outside the boundary layer.

Convection flow can be classified according to the nature of the flow. It is called forced convection when the flow is caused by an external force. In contrast, for free (or natural) convection, the flow is induced by forces, which arise from density differences caused by temperature variations in the fluid. The heat flux due to convection [Wm<sup>-2</sup>], regardless of the particular nature of the convection, is given by:

$$q = h.(T_s - T_{\infty}), \tag{2.4}$$

where *h* [Wm<sup>-2</sup>K<sup>-1</sup>] the convection heat transfer coefficient. It encompasses all the parameters that influence convection heat transfer. In particular, it depends on conditions in the boundary layer, which are influenced by surface geometry, the nature of the fluid motion and an assortment of fluid thermodynamic and transport properties. Equation 2.4 is known as Newton's law of cooling.

#### 2.1.3 Radiation

Unlike conduction and convection, which requires a medium, radiation is an electromagnetic phenomenon and travels easily through vacuum with the speed of light. All surfaces emit thermal radiation and absorb or reflect incident radiation. The net rate of heat flux from a surface equals the total energy emitted minus the total energy absorbed from the surroundings. A "black" surface (emission at a maximal rate and, correspondingly, absorption of all incident radiation) emits energy at a rate proportional to the fourth power of the absolute temperature of the surface. If a black surface has area A and temperature T, its radiant emission is given by:

$$E_{h} = \sigma A T^{4}, \qquad (2.5)$$

where  $\sigma$  [Wm<sup>-2</sup>K<sup>-4</sup>] the Stephan-Boltzmann constant. Real surfaces are non-black and emit radiation at a rate less than maximum. A convenient way to express this is to say that they emit at a fraction  $\varepsilon$  of the black body rate:

$$E = \varepsilon \sigma A T^4. \tag{2.6}$$

The dimensionless parameter  $\varepsilon$  is called the emissivity of the surface and varies between zero and unity. Experiments show that  $\varepsilon$  varies with the temperature and also with surface parameters, texture, colour, degree of oxidation and the presence of coatings. The analysis of radiant interchange between two or more surfaces can be a complex algebraic procedure. A common special case is when body 1 has a temperature  $T_1$  and constant emissivity  $\varepsilon_1$ , and is completely enclosed by a large surface area,  $A_2 >> A_1$ , with temperature  $T_2$  and constant emissivity  $\varepsilon_2$ . The net radiant heat transfer from the small body to the large enclosure is:

$$q_{1\to 2} = \varepsilon_1 \sigma A_1 (T_1^4 - T_2^4),$$

(2.7)

which is independent of the size and the emissivity of the enclosure.

# 2.2 Thermal and fluidic laws for single phase forced convection through micro-channels

#### 2.2.1 Thermal resistances

The maximum temperature allowed in an IC is around 120 °C. Because of this maximum temperature, the heat transfer by radiation to the surrounding can be neglected. This means that the heat generated in the IC is most efficiently transported by conduction and convection. For a micro-channel cooler, in the backside of a silicon wafer, the thermal resistance can be seen as the sum of three terms:

- 1. The thermal resistance due to conduction through the diffuser,  $R_{cond}$ . The diffuser contains silicon and a thin layer of silicon oxide (Fig. 1).

- 2. The convection resistance, which represents the heat exchange between the micro-channel walls and the fluid,  $R_{conv}$ .

- 3. The capacitive resistance, which represents the increase of the fluid temperature between the channel inlet and outlet,  $R_{cap}$ .

#### 2.2.1.1 Conduction thermal resistance, R<sub>cond</sub>

Two cases have to be distinguished about diffusion resistance:

1. The heat flux is unidirectional. The heat flux is only unidirectional when the heat dissipation in the IC is uniform, and the IC has the same size as the micro-cooler. In the simple case of a single layer diffuser, the conduction resistance can be expressed as:

$$R_{cond} = \frac{d}{kA},\tag{2.8}$$

where d the diffuser layer thickness, k the thermal conductivity and A the diffuser area through which the heat flux goes. It is easy to minimize the importance of this resistance by decreasing the diffuser thickness, only limited by the mechanical constraints of our system. When the diffuser contains several layers, the thermal resistance can be calculated with:

$$R_{cond} = \sum_{i=1}^{n} R_{cond,i} = \sum_{i=1}^{n} \frac{d_{i}}{k_{i} A}.$$

(2.9)

2. The heat flux is 2-Dimendional. This case appears when the IC is smaller than the cooler or when the heat dissipation in the IC is not uniform, and is amplified when the diffuser contains a thermal barrier. In the micro-channel design shown in Fig. 1 the silicon is covered with a thin layer of SiO<sub>2</sub> (100 nm), to make the surface hydrophilic and the prevent the copper diffusing into the silicon. SiO<sub>2</sub> is an insulator, but because this layer is only 100 nm, it is not a big thermal barrier. When the heat dissipation in the IC is not uniform, the presence of the SiO<sub>2</sub> even decreases the maximum temperature. This is because heat is spread in SiO<sub>2</sub> layer, and the heat flows through a larger area than in the one-dimensional case. This is why it is important to make the diffuser layer not to thin when the heat flux is not uniform. By using an optimal diffuser layer hot spots can be prevented.

#### 2.2.1.2 Convection thermal resistance, R<sub>conv</sub>

Convection represents heat exchange between the channel walls and the fluid. Convection thermal resistance can be expressed as:

$$R_{conv} = \frac{1}{hA_{\mu-ch}},\tag{2.10}$$

where h [Wm<sup>-2</sup>K<sup>-1</sup>] the heat transfer coefficient for convection and  $A_{\mu\text{-}ch}$  the surface of the micro-channels. The heat transfer coefficient for convection depends on numerous parameters such as convection mode (forced or free), cooler geometry, flow characteristics (laminar or turbulent), thermal and hydraulic transient properties etc.

## 2.2.1.3 Capacitive thermal resistance, $R_{\text{cap}}$

Contrary to the former thermal resistances, which care about temperature differences parallel to the heat flux, this resistance describes the fluid temperature increase between the channel inlet and outlet perpendicular to the heat flux. This

temperature rise is due to the heat quantity absorbed by the fluid while it is flowing through the micro-channels. The capacitive thermal resistance can be calculated with:

$$R_{cap} = \frac{1}{\rho \dot{V}C_p},\tag{2.11}$$

where  $\rho$  [kg m<sup>-3</sup>] the density of the fluid, V [m<sup>3</sup>s<sup>-1</sup>] the volumetric flow rate and  $C_p$  [J kg<sup>-1</sup>K<sup>-1</sup>] the specific heat.

#### 2.2.1.4 Overall thermal resistance, $R_{th}$

By applying equation 2.1 to micro-channel cooling, the overall thermal resistance can be calculated with:

$$R_{th} = \frac{T_j - T_{in}}{P}, (2.12)$$

where  $T_j$  the junction temperature in the IC,  $T_{in}$  the fluid inlet temperature and P the dissipated power. Because the micro-channels are made in the backside of a silicon wafer, there is no intermediate layer between the IC and the micro-channels. When the micro-channels are not fabricated in the silicon, there is an extra thermal resistance due to the presence of the intermediate layer.

## 2.2.2 Convective exchange laws from a thermal and hydraulic point of view

In this part, the flow through the micro-channels will be characterized with use of four dimensionless numbers:

- 1. The Reynolds number

- 2. The Prandtl number

- 3. The Friction coefficient

- 4. The Nusselt number

#### 2.2.2.1 Reynolds number

The Reynolds number describes the relation between the convective forces and the friction forces in the fluid and is given by:

$$Re = \frac{\rho v D_h}{\mu}, \qquad (2.13)$$

with v the speed of the fluid,  $\mu$  [Pa s] the dynamic viscosity and  $D_h$  the hydraulic diameter of the micro-channel. The hydraulic diameter can be calculated with:

$$D_h = \frac{4s}{p},\tag{2.14}$$

with s and p respectively the area and the perimeter of the channel.

The Reynolds number defines the transition between laminar and turbulent flows. The transition value is well known for channels and mini-channels ( $D_h > 1$  mm), the flow is laminar for Re < 2300 and becomes turbulent for Reynolds numbers above this value. However, in the case of micro-channels, the Reynolds number for the transition is not well known. Wang and Peng [1] studied the forced convection of liquid in micro-channels ( $D_h \sim 0.3$  mm) experimentally and found that fully developed turbulent convection was initiated at Re = 1000-1500 and the conversion from laminar to turbulent occurred at approximately Re = 300-800.

#### 2.2.2.2 Prandtl number

Flow can be fully developed either thermally and hydraulically. A flow is fully developed thermally (or hydraulically), when the fluid temperature (or velocity) profile, in a channel, no longer depends on its position along the channel. The Prandtl number, Pr, gives information about the thermal and hydraulic development of the flow. This dimensionless number only depends on fluid properties and not on the channel geometry.

$$\Pr = \frac{\mu C_p}{k} \,. \tag{2.15}$$

This number represents the relative importance between the thermal and viscous effects. For instance, consider a fluid element with a characteristic size of 1, then the viscous diffusion time  $\tau_v$  and the thermal diffusion time  $\tau_\kappa$  can be expressed as:

$$\tau_{\nu} = \frac{1^2}{D},$$

(2.16)

$$\tau_{\kappa} = \frac{1^2}{\kappa},\tag{2.17}$$

where v [m<sup>2</sup>s<sup>-1</sup>] the fluid kinematic viscosity and  $\kappa$  [m<sup>2</sup>s<sup>-1</sup>] the thermal diffusivity of the fluid. Now follows for the Prandtl number:

$$\Pr = \frac{\mu C_p}{k} = \frac{\rho C_p \upsilon}{\rho C_p \kappa} = \frac{\upsilon}{\kappa} = \frac{\tau_{\kappa}}{\tau_{\upsilon}}.$$

(2.18)

So, for fluids with a high Prandtl number (Pr >> 1), the time to reach thermal equilibrium is longer than the time to reach viscous flow equilibrium, consequently heat diffusion processes initially determine the fluid motion. On the contrary, for low Prandtl numbers (Pr << 1), thermal effects decrease and hydrodynamic laws lead the fluid motion. The Prandtl number for water is around 7. This implies that the viscous diffusion time and thermal diffusion time have the same order of magnitude.

#### 2.2.2.3 Friction coefficient and pressure losses

Pressure losses between channels input and output can be calculated with:

$$\Delta P = \frac{4\rho C_f L v^2}{2D_h},\tag{2.19}$$

where  $C_f$  the friction coefficient, v the speed in the channel and L the channel length.

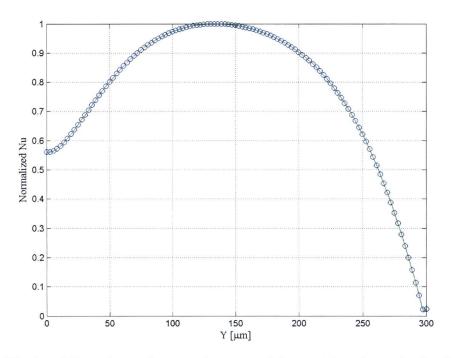

#### 2.2.2.4 Nusselt number

The Nusselt number describes the heat transfer between the solid and the fluid and is given by:

$$Nu = \frac{hD_h}{k} \,. \tag{2.20}$$

For a laminar flow, which is fully developed, both thermally and hydraulically, it is possible to calculate the Nusselt number analytically, if the velocity profile is known and when it is known how to solve the heat equation.

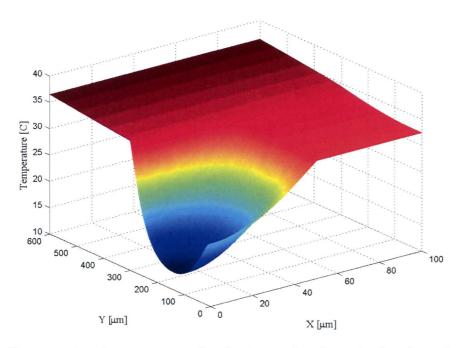

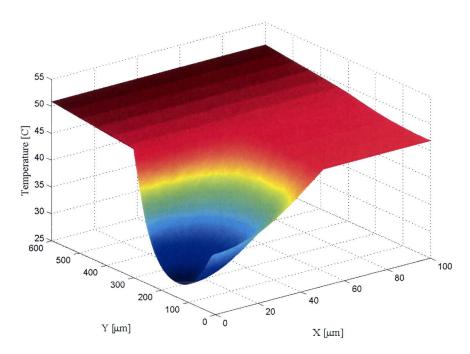

#### 2.3 Analytical model

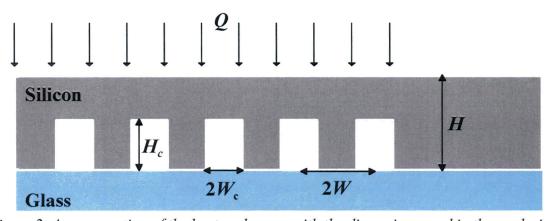

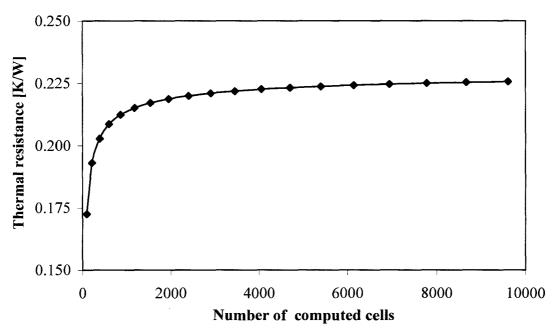

To compare the results of our experiments with theory, the thermal resistance of the micro-channels is calculated by solving numerically a conjugate heat transfer problem consisting of the simultaneous determination of the temperature fields, in both the substrate and the liquid [2]. For the purpose of this calculation, it is assumed that all the channels have a uniform, rectangular cross-section of width  $2W_c$ , height  $H_c$ , hydraulic diameter  $D_h$  and length L. The distance between the centers of adjacent channels is 2W and the thickness of the wafer is H(Fig. 2)

Figure 2. A cross section of the heat exchanger with the dimensions used in the analysis.

Since the cover plate is made out of glass, which thermal conductivity is about two orders of magnitude lower than that of silicon ( $k_{glass} \approx 1$ ,  $k_{silicon} \approx 100$ ), it is assumed that this boundary is thermally insulated. This is a conservative assumption, which will lead to a slight overestimation of the overall thermal resistance. A more precise analysis would require information about the thermal interaction between the glass plate and its environment. The exact nature of this interaction depends on the packaging of the electronic circuits and is not likely to be generic. Further, it is assumed that the channels surfaces are smooth, and that the heat flux Q is uniform. The thermal conductivities of the solid and the fluid are  $k_s$  and  $k_f$ , respectively.

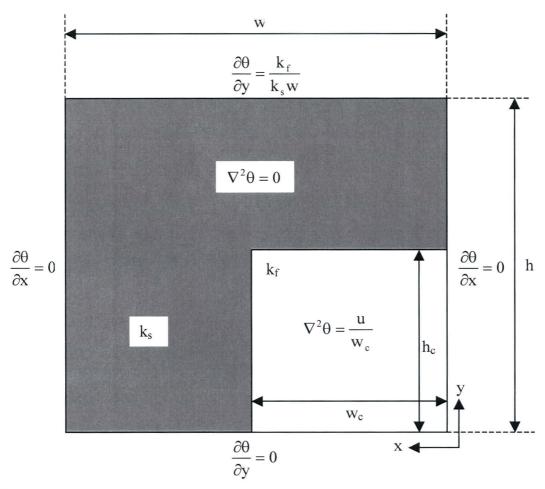

Taking advantage of symmetry, the computations are based on a unit cell consisting of half a channel and the surrounding silicon. Figure 3 depicts the computational domain, the governing equations, and the boundary conditions. The channels height,  $H_c$ , is used as a unit of length and the average fluid velocity,  $\bar{U}$ , is taken as the unit for the velocity. The convention is adopted that uppercase and lowercase represent, dimensional and non-dimensional quantities, respectively. For this model, the flow is assumed laminar and fully developed (both thermally and hydraulically). In situations in which entrance effects may be important, this model would overestimate the thermal resistance.

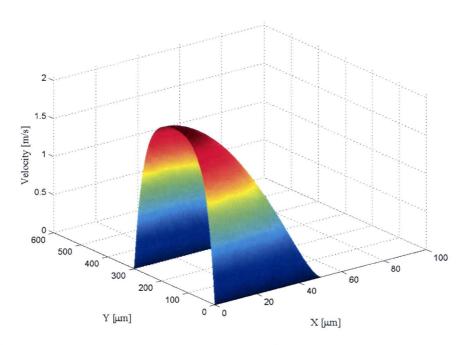

#### 2.3.1 Fluid velocity profile

The dimensional average velocity,  $\bar{U}$ , and the non-dimensional velocity field, u(x,y) are obtained from the classical expressions for fully developed, laminar flow in a rectangular duct with aspect ratio  $A = H_c/2W_c = 1/w_c > 1$  [2]:

$$\overline{U} = \frac{H_c^2}{12\mu} \left( -\frac{dP}{dZ} \right) \left[ 1 - \frac{192A}{\pi^5} \sum_{i=1,3,5...}^{\infty} \frac{\tanh\left(\frac{i\pi}{2A}\right)}{i^5} \right], \tag{2.21}$$

and

$$u(x,y) = \frac{\frac{48}{\pi^3} \sum_{i=1,3,5,\dots}^{\infty} (-1)^{\frac{i-1}{2}} \left[ 1 - \frac{\cosh(i\pi x)}{\cosh(i\pi w_c)} \right] \frac{\cos(i\pi (y - 0.5))}{i^3}}{1 - \frac{96}{\pi^5 w_c} \sum_{i=1,3,5,\dots}^{\infty} \frac{\tanh(i\pi w_c)}{i^5}}.$$

(2.22)

In the above, P is the pressure,  $\mu$  the dynamic viscosity, and (x,y,z) are Cartesian coordinates. The coordinates (x,y) are depicted in Fig. 3. The coordinate z is aligned in the streamwise direction.

Figure 3. A computational cell obtained utilizing symmetry is shown together with the governing equations and boundary conditions.  $\theta$  is the non-dimensional temperature, which will be defined further on.

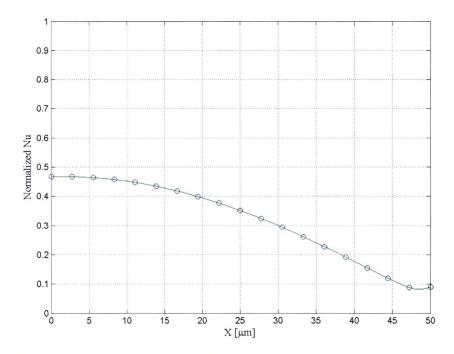

#### 2.3.2 Temperature field