#### MASTER

Design of a low power 100MHz, 8-bit, bipolar, folding Analog-to-Digital Converter

Compiet, J.P.R.

Award date: 1997

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

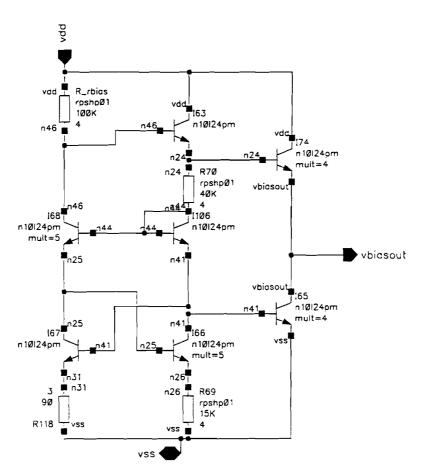

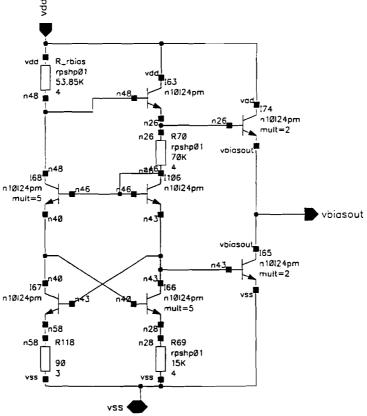

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Eindhoven University of Technology Faculty of Electrical Engineering Signal Processing and Electronic Systems (SES)

"Design of a low power

### 100MHz, 8-bit, bipolar, folding

## Analog-to-Digital Converter"

by *J.P.R. Compiet* Eindhoven, June 1997

Report of graduation work, performed from November 1996 - June 1997 at the Eindhoven University of Technology and the Philips Research Laboratories, Eindhoven

Professor Supervisors prof. dr. ir. R.J. van de Plassche

dr. ir. D.M.W. Leenaerts

ir. G.G. Persoon

#### ABSTRACT

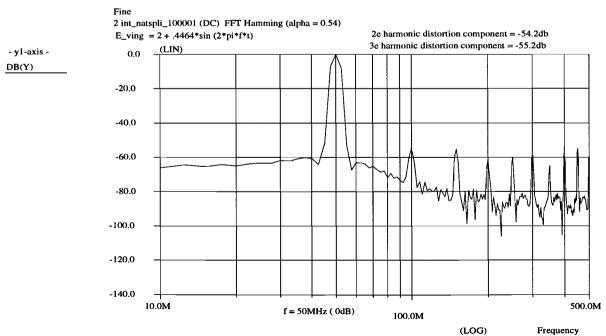

The architecture of this 8-bit ADC is based on a three-stage conversion, using Cascaded Folding & Interpolating techniques. Compared to the other multi-stage ADC architectures, Folding & Interpolating ADCs are based on non-linear analog preprocessing the input signal. This architecture is an attractive solution for ADCs, as extremely linear circuit topologies are not required. In order to raise the resolution of Folding & Interpolating ADCs, without rising the number of parallel input stages or the number of comparators in the fine-comparator, a Cascaded Folding & Interpolating architecture is used. The ADC preprocessing part achieves a 55 dB Spurious-Free Dynamic Range (SFDR), while quantizing a 50 MHz full-scale input signal at 100 MSample/s. The ADC will be fabricated in an advanced bipolar IC process and the preprocessing part only dissipates 6 mW from a single 3.0 V supply. The preprocessing part consists of the fine folding circuit with input gain stages, reference ladder and bias circuits and the total coarse signal generation. This report is based on simulation results. Additional the layout of the preprocessing part has been extracted. For further research, the implementation of the folding ADC offers possibilities to scale down the power consumption when the bipolar process is better stabilized. The 'Nat. Lab.' transistors parameters, used in the first simulations, should be better implemented in the IC-lab in Hamburg. The total ADC power can be scaled down a factor 3. Also a two metal layer (or more) bipolar process, with small interconnect via's, reduces the total wirering capacitance and saves more power.

# **TABLE OF CONTENTS**

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2. INITIAL DESIGN SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                         | 4              |

| 3. FOLDING AND INTERPOLATING PRINCIPLE                                                                                                                                                                                                                                                                                                                                                                                                                   | 5              |

| <ul> <li>3.1 INTRODUCTION</li> <li>3.2 FOLDING PRINCIPLE USED IN LOW-POWER A / D CONVERTER</li> <li>3.3 FINE FOLDING SIGNAL GENERATION</li></ul>                                                                                                                                                                                                                                                                                                         | 7<br>10        |

| 3.5 OVERVIEW OF THE USED PREPROCESSING TECHNIQUE                                                                                                                                                                                                                                                                                                                                                                                                         | 13             |

| 4. BLOCK DIAGRAM FOLDING A / D CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| 5. BIPOLAR TECHNOLOGY : SPIRIT                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| <ul> <li>5.1 INTRODUCTION</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 6. REFERENCE LADDER WITH INPUT GAIN STAGES                                                                                                                                                                                                                                                                                                                                                                                                               | 21             |

| <ul> <li>6.1 INTRODUCTION</li> <li>6.2 BANDWIDTH VERSUS INPUT FREQUENCY RATIO OF THE ADC</li> <li>6.3 INPUT GAIN STAGES</li> <li>6.3.1 Standard implementation of a differential input amplifier</li> <li>6.4 REFERENCE LADDER NETWORK</li> <li>6.4.1 Influence of noise on the ladder network</li> <li>6.4.2 Definition maximum ladder resistor value</li> <li>6.5 NONLINEARITY OF THE INPUT STAGE</li> <li>6.6 DC SETTINGS INPUT GAIN STAGE</li> </ul> |                |

| 7. FINE FOLDING CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| <ul> <li>7.1 INTRODUCTION</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                      | 36<br>39<br>40 |

| 7.5.1 Simulation with input signal as ramp between 1.5V and 2.V                                                                                                                                                                                                                                                                                                                                                                                          | 42<br>42       |

| <ul> <li>7.5.3 DC - simulation for measuring interpolation errors</li> <li>7.5.4 Conclusions of the performance preprocessing part</li> <li>7.6 DYNAMIC PERFORMANCE OF THE PRE-PROCESSING BLOCK</li></ul>                                                                                                                                                                                                                                                | 45<br>45       |

| 7.6.2 Dynamic performance at low frequencies                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| 7.6.3 Dynamic performance at high frequencies      |    |

|----------------------------------------------------|----|

| 7.7 NOISE ANALYSIS OF THE ANALOG PREPROCESSING     |    |

| 7.8 OVERALL PERFORMANCE OF THE PREPROCESSING BLOCK | 52 |

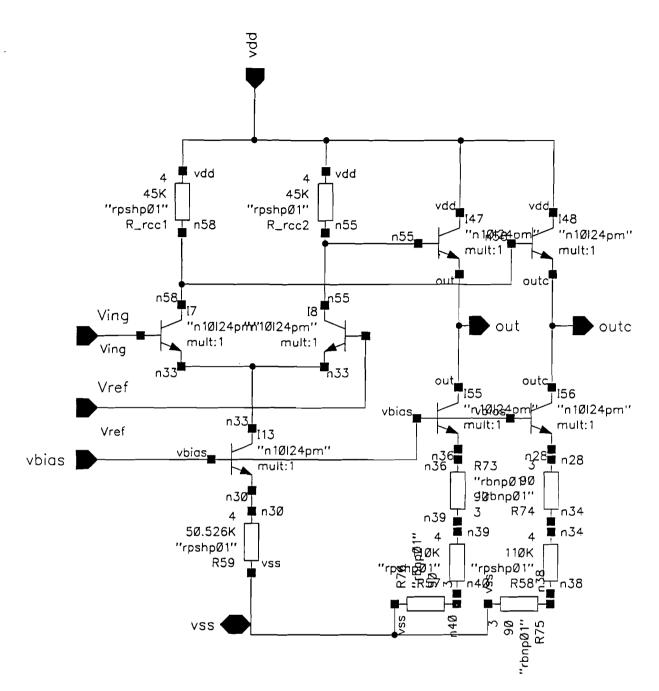

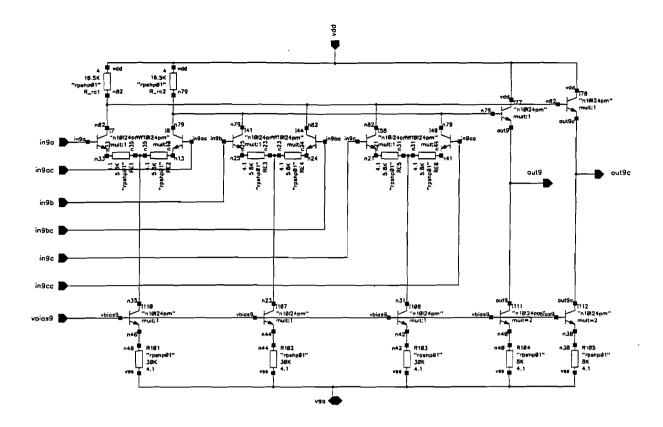

| 8. COARSE FOLDING CIRCUITS                         | 53 |

| 8.1 INTRODUCTION                                   | 53 |

| 8.2 DEFINITION OF THE COARSE FOLDING SIGNALS       | 54 |

| 8.3 DESIGN COARSE FOLDING BLOCK                    |    |

| 8.4 SIMULATION RESULTS OF THE COARSE FOLDING BLOCK | 58 |

| 9. PREPROCESSING BIAS CIRCUITS                     | 60 |

| 9.1 INTRODUCTION                                   | 60 |

| 9.2 PARTITION FOR SEPARATE BIAS CIRCUITS           |    |

| 9.3 IMPLEMENTATION OF THE BIASING CIRCUITS         |    |

| 9.4 POWER CONSUMPTION TOTAL PREPROCESSING PART     | 64 |

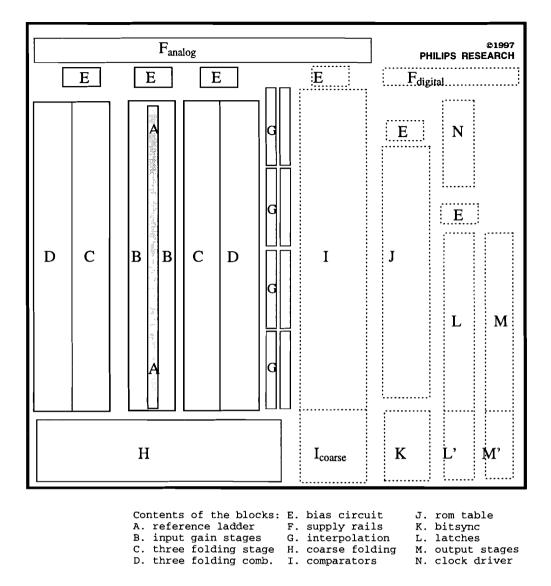

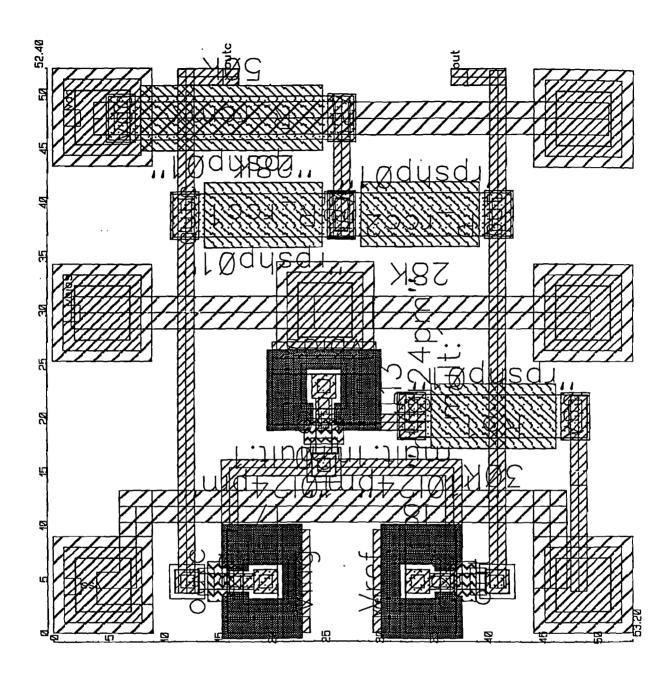

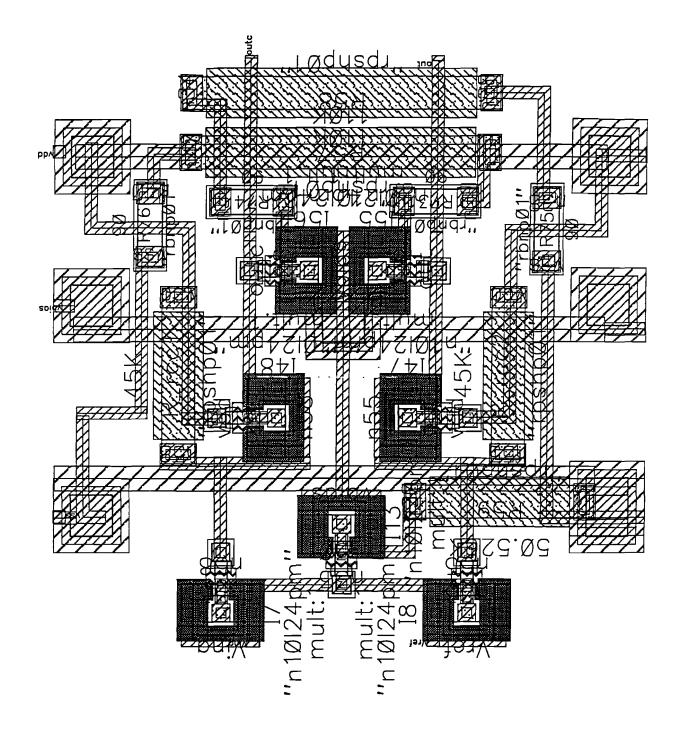

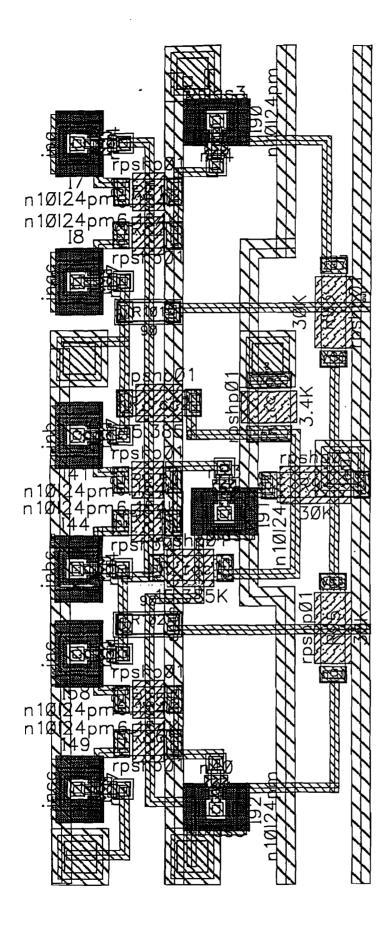

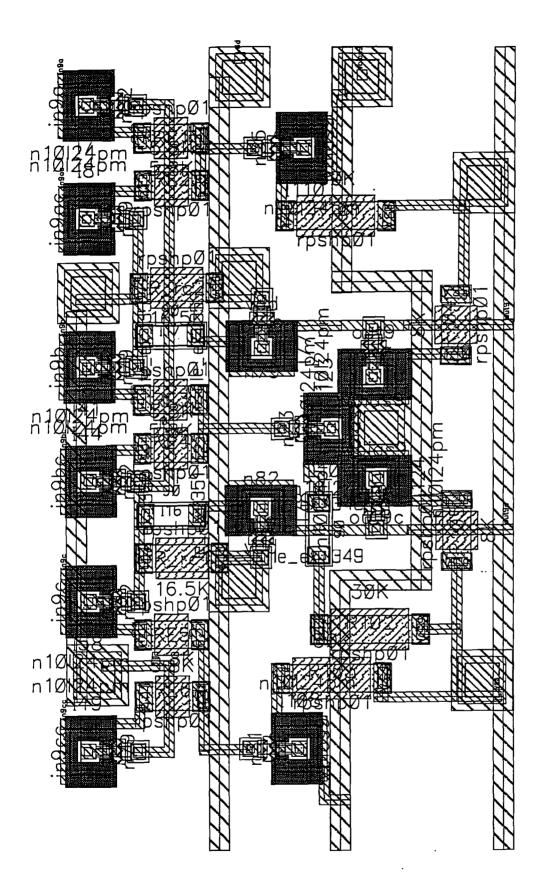

| 10. LAYOUT DESIGN OF PREPROCESSING BLOCK           | 65 |

| 10.1 placement considerations                      | 65 |

| 10.2 FLOORPLAN TOTAL ANALOG-TO-DIGITAL CONVERTER   | 65 |

| 10.3 LAYOUT DESIGN OF THE PREPROCESSING CIRCUITS   | 66 |

| 11. CONCLUSIONS AND RECOMMENDATIONS                | 68 |

| 12. ACKNOWLEDGE                                    | 70 |

| 13. REFERENCES                                     | 71 |

### **LIST OF FIGURES**

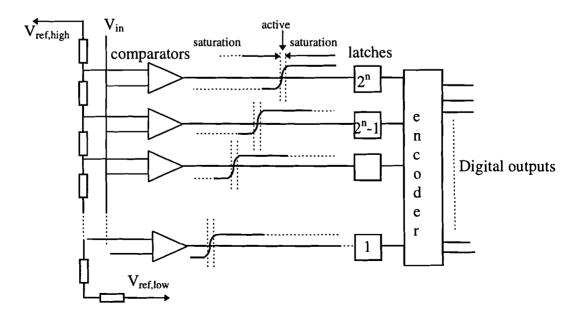

- Figure 1.1: Full-flash A/D converter structure

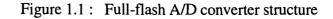

- 1.2: Two-step A/D converter structure

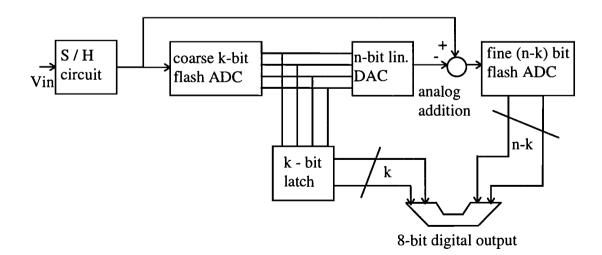

- Figure 3.1: Folding A/D converter architecture

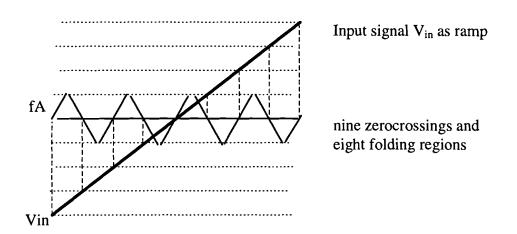

- 3.2: The folding process, input and output voltages V versus time t

- 3.3: High frequency rounding of the folding signal

- 3.4: Double folding technique for the fine selection

- 3.5: Generation of the 3 coarse bits and 5 fine bits in folding architecture

- 3.6: Nine zerocrossings in 'fA' due to marking both min. and max. input signal

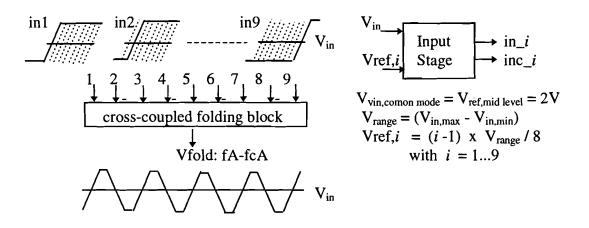

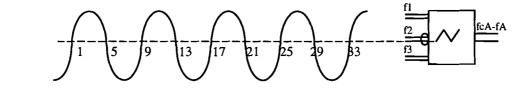

- 3.7: Combination of input signals *in1* to *in9* into a single nine folding signal

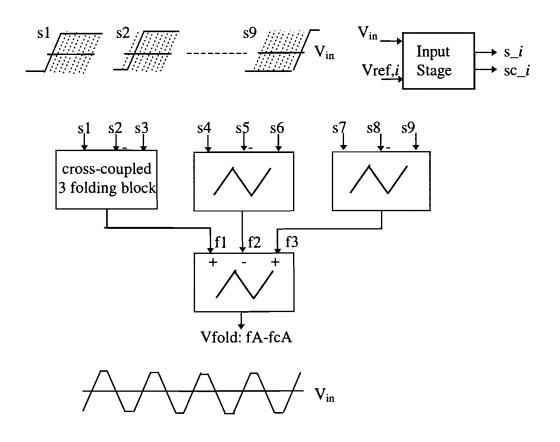

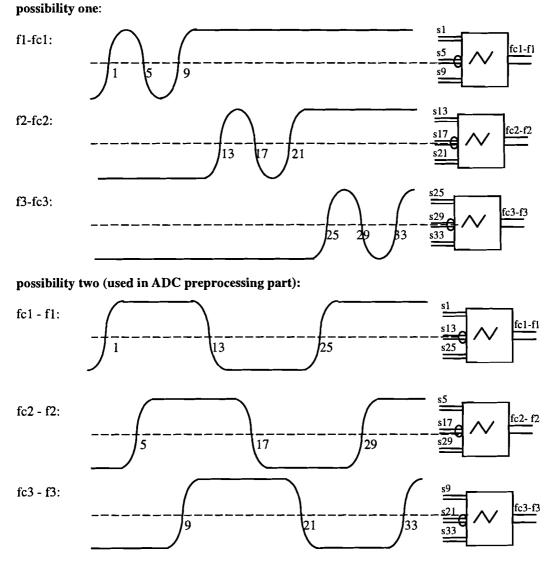

- 3.8: Cascaded folding of input signals s1 to s9 into a nine folding signal

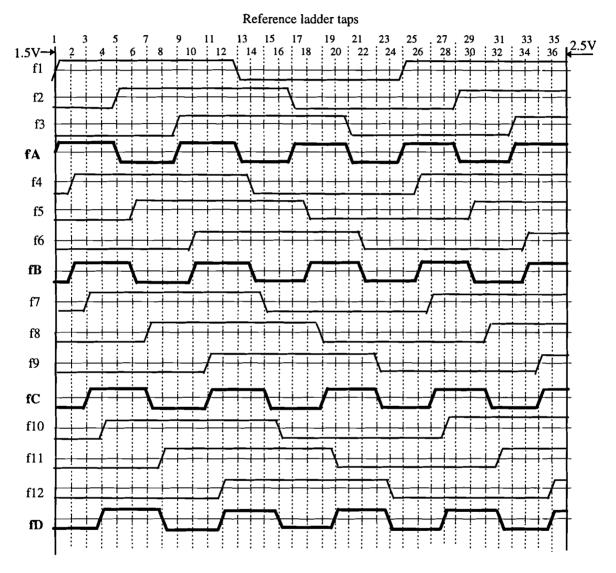

- 3.9: Overview of the '3'- and '9' times folding signals as function of the input

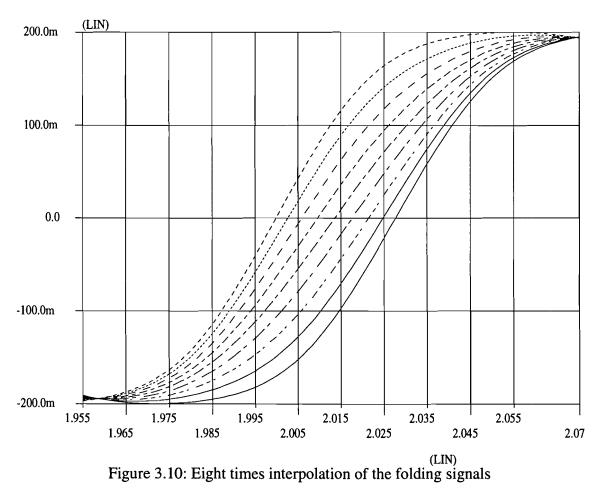

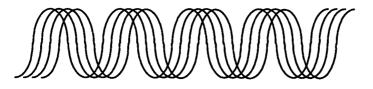

- 3.10: Eight times interpolation of the folding signals

- 3.11: Circular interpolation circuit

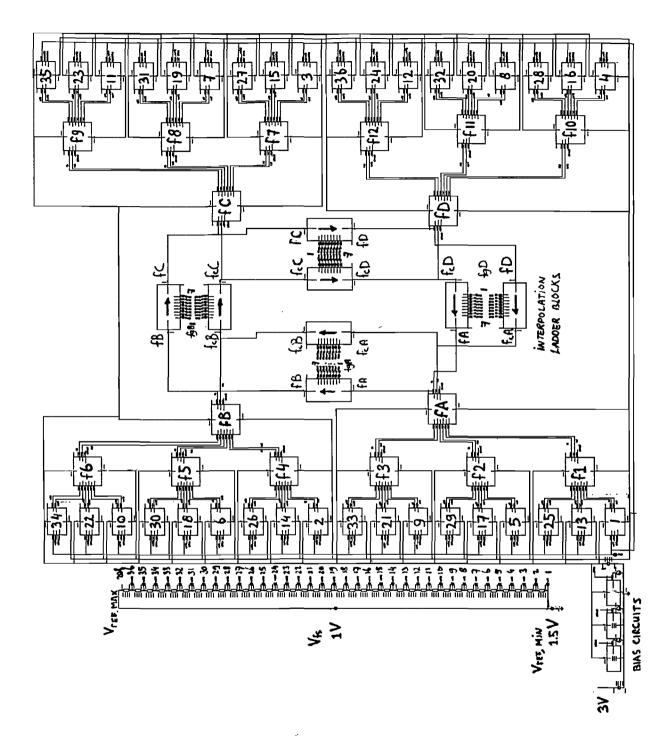

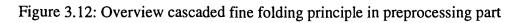

- 3.12: Overview fine folding principle

- Figure 4.1: Structure of the folding Analog-to-Digital converter

- 4.2: Output code comparators including EXOR-operation

- 4.3: Exor function

- Figure 5.1a: NPN transistor with additional parasitic capacitors

- 5.1b: Simplified small signal equivalent circuit for vertical NPN transistor

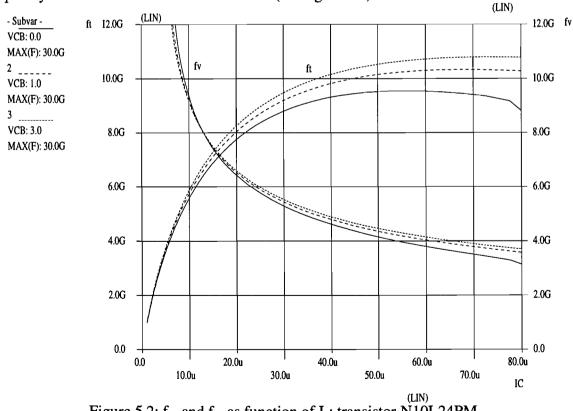

- 5.2:  $f_T$  and  $f_V$  as function of the collector current in SPIRIT technology

- Figure 6.1: Simple differential pair with reference ladder tap connection

- 6.2: Input gain stage, differential output voltage as function of the input voltage

- 6.3: Current source using a single transistor

- 6.4: Current source using a transistor with emitter resistor

- 6.5: Levelshift in the input gain stage with R<sub>cm</sub>

- 6.6: Reference ladder feedthrough of input signal via series capacitive combination in the differential pairs of the input stages

- 6.7: Calculation model to derive the maximum feedthrough on the reference ladder

- 6.8: Simulation setup for measuring the coupling capacitance of one input stage

- 6.9: Interpolation errors due to nonlinearities of the input stage

- 6.10: The 7 interpolation signals with linear transfer curve:  $V_{out} i*\delta V_y/8$

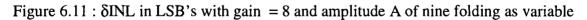

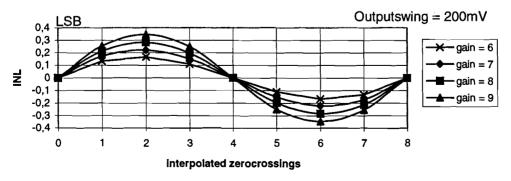

- 6.11:  $\delta_{INL}$  in LSB's with gain = 8 and the amplitude A of nine folding as variable

- 6.12:  $\delta_{INL}$  in LSB's with amplitude = 200mV and gain<sub>tot</sub> nine folding as variable

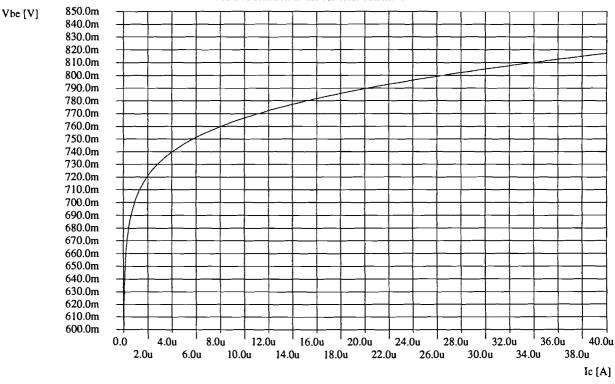

- 6.13: Vbias as function of the collector current Ic

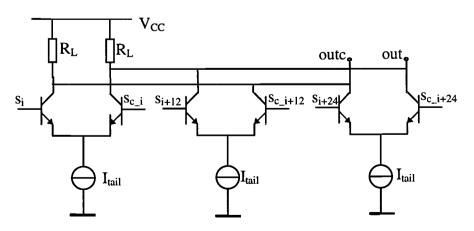

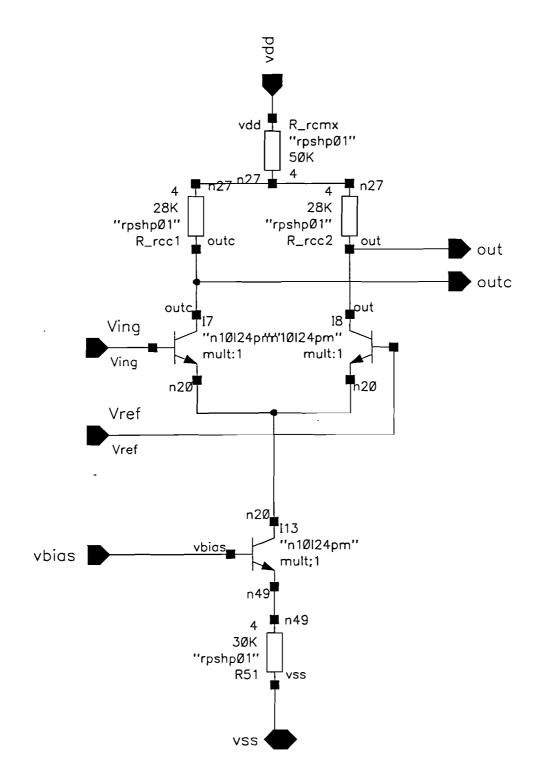

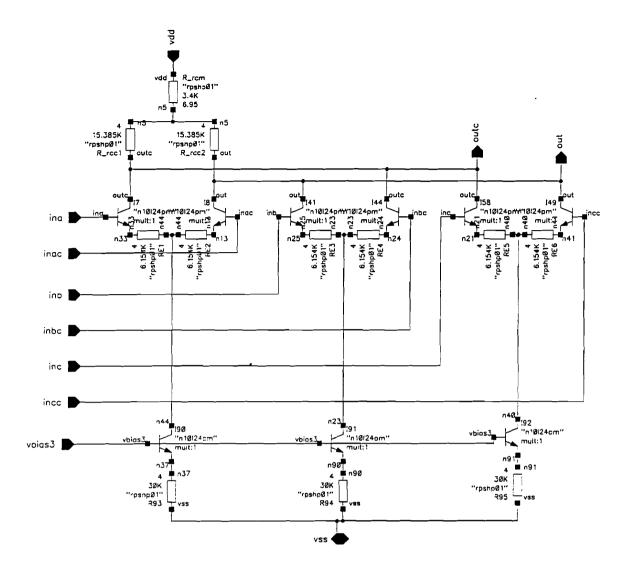

- Figure 7.1: Implementation of standard 'three' folding block

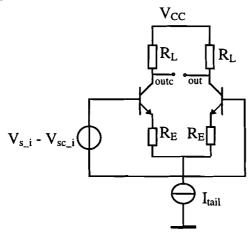

- 7.2: Differential pair with local serie feedback

- 7.3: Implementation of 'three' folding bock in ADC

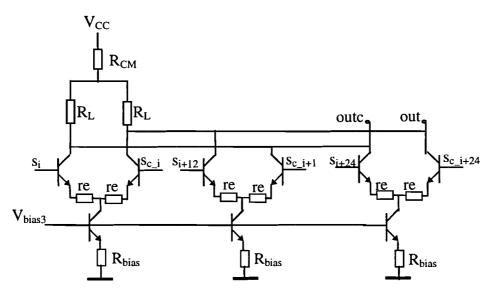

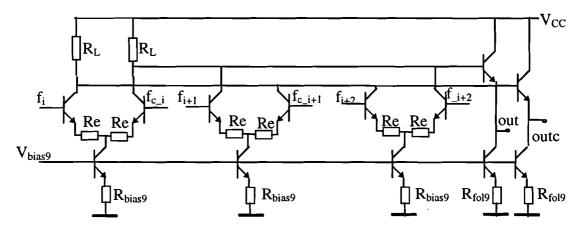

- 7.4: Implementation of 'three' folding combination block in ADC

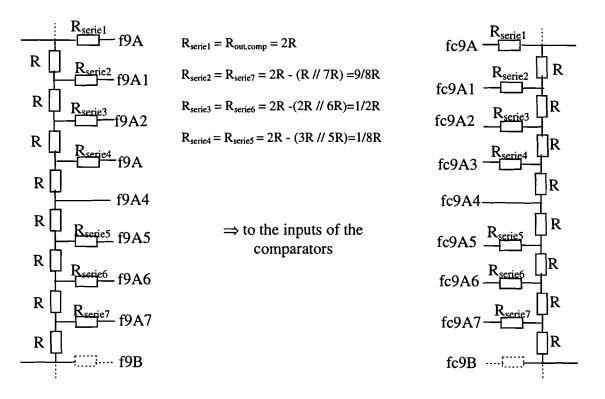

- 7.5: Interpolation ladder with serie resistors for delay compensation

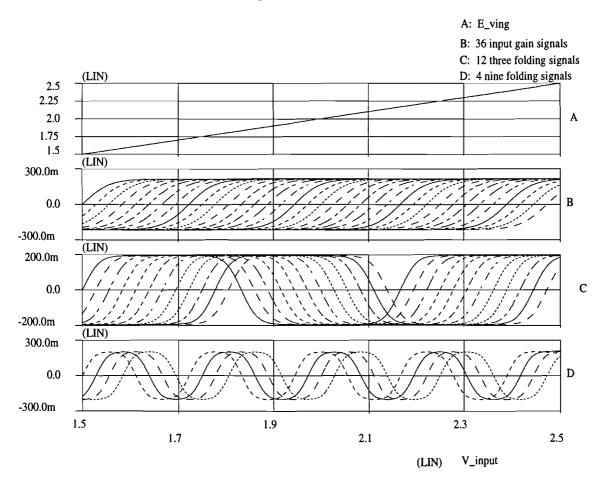

- 7.6: Overview fine folding signals as function of the input voltage

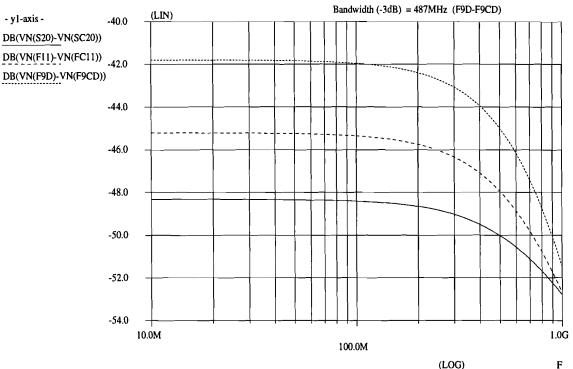

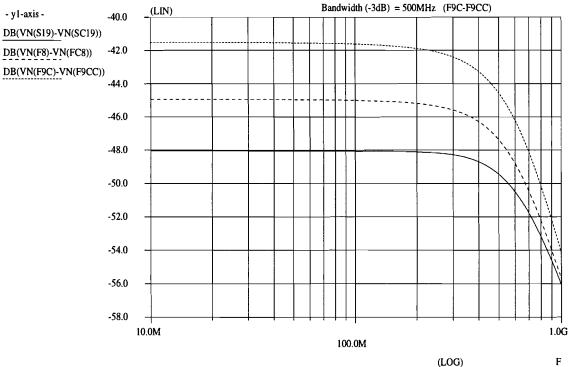

- 7.7: Small signal bandwidth on ref<sub>20</sub> of the preprocessing part

- 7.8: Small signal bandwidth on  $ref_{19}$  of the preprocessing part

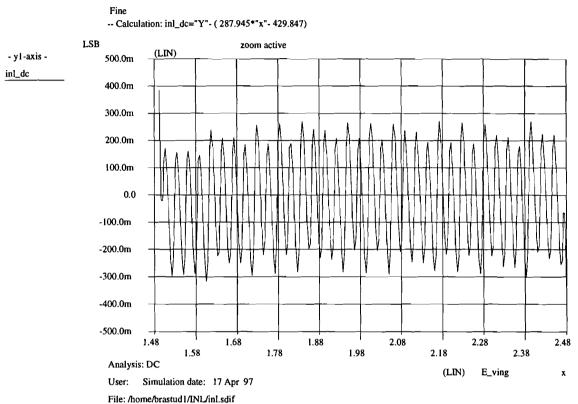

- 7.9: INL in LSB's of the preprocessing part with as input an DC-ramp

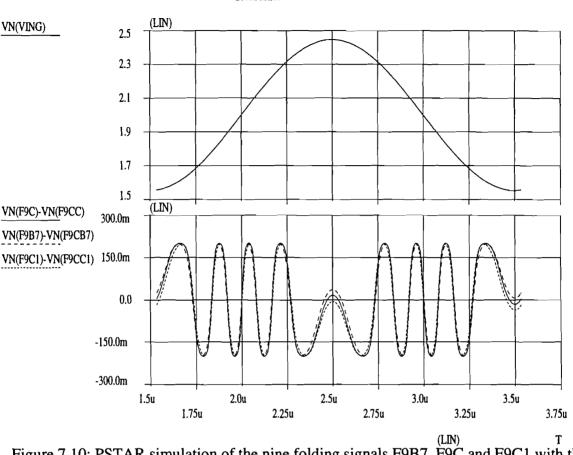

- 7.10: PSTAR simulation of the nine folding signals F9B7, F9C and F9C1 with the input signal frequency of 500kHz

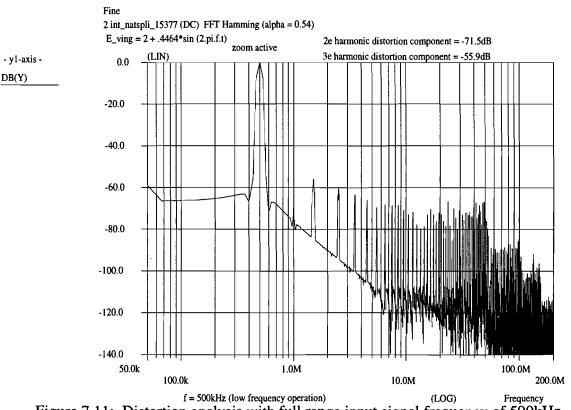

- 7.11: Distortion analysis with full range input signal frequency of 500kHz

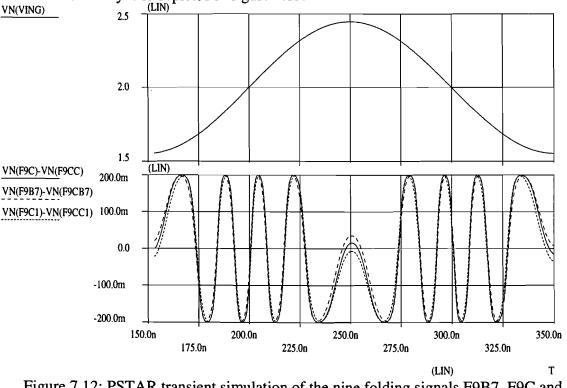

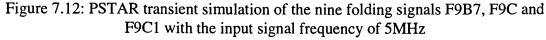

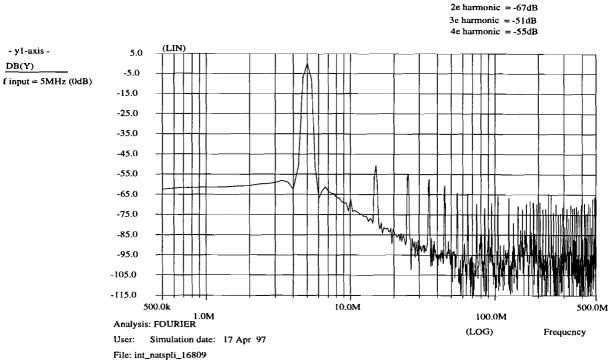

- 7.12: PSTAR simulation of the nine folding signals F9B7, F9C and F9C1 with the input signal frequency of 5MHz

- 7.13: Distortion analysis with full range input signal frequency of 5MHz

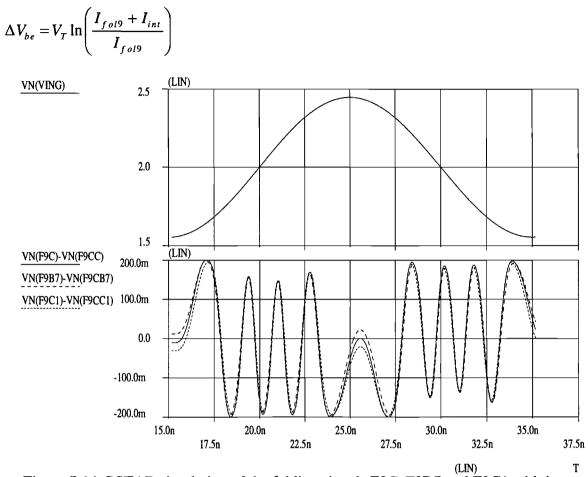

- 7.14: PSTAR simulation of the nine folding signals F9B7, F9C and F9C1 with the input signal frequency of 50MHz

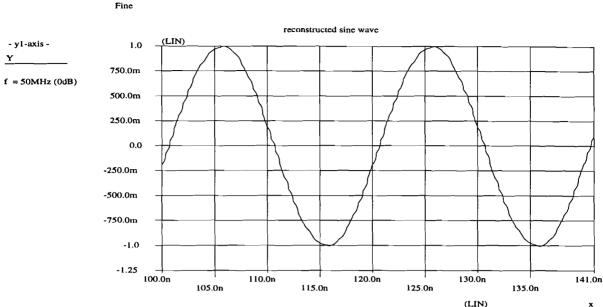

- 7.15: Distortion analysis of reconstructed sine wave with  $f_{in} = 50MHz$

- 7.16: Reconstructed sine wave with  $f_{in} = 50 MHz$

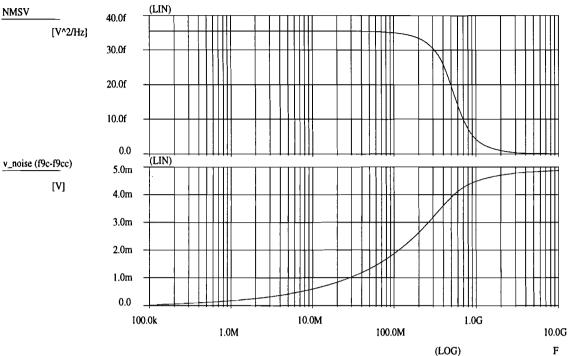

- 7.17: Noise power spectrum and rms noise voltage of the preprocessing block

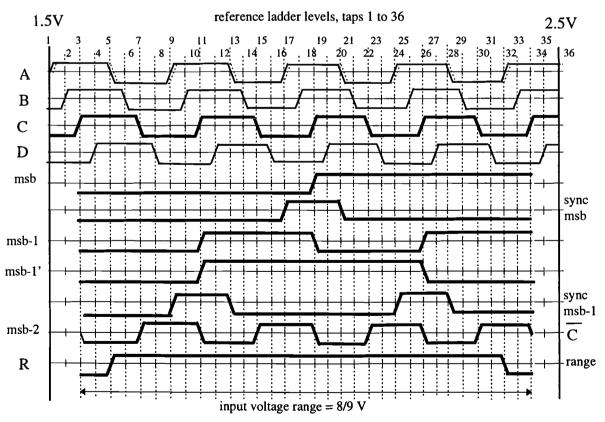

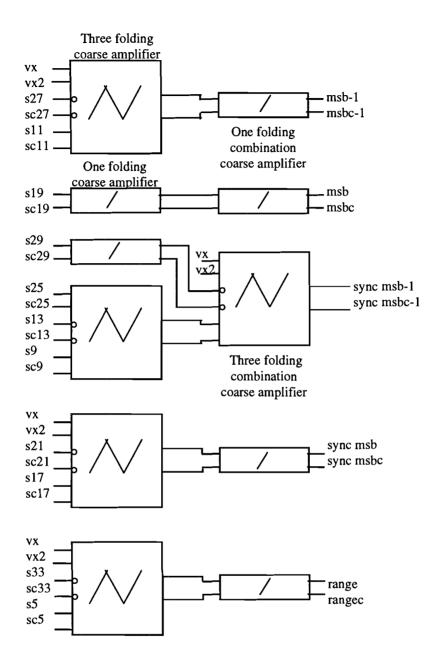

- Figure 8.1: Definition of the coarse folding signals

- 8.2: 'Transformation' of a three folding block to an 'one' folding circuit

- 8.3: Coarse folding implementation

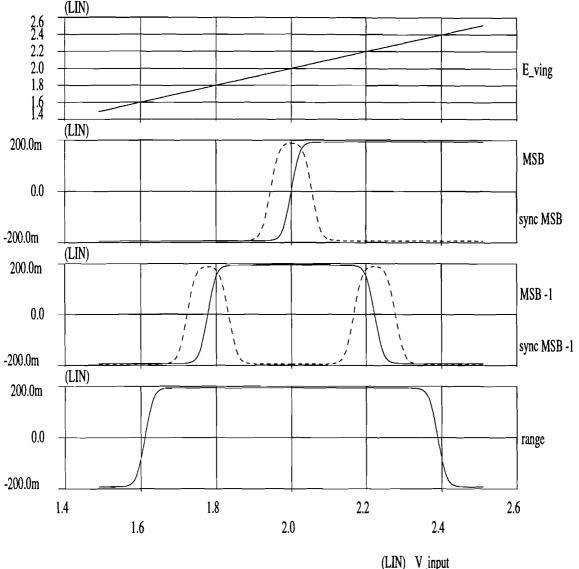

- 8.4: Coarse folding signals as function of the input signal

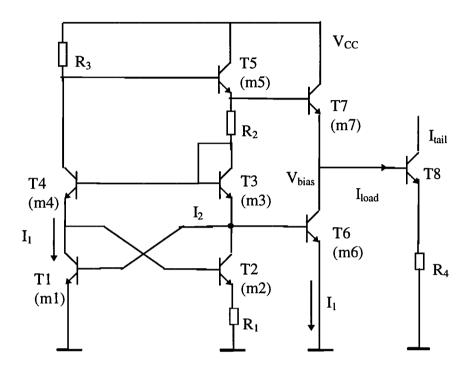

- Figure 9.1: Voltage reference voltage source for biasing the preprocessing block

- Figure 10.1: Floorplan of the folding ADC

# LIST OF SYMBOLS

| ADC                              |           | : Analog-to-Digital Converter                                                              |

|----------------------------------|-----------|--------------------------------------------------------------------------------------------|

| А                                |           | : amplitude of output voltage input stage amplifier                                        |

| b                                |           | : gain at zerocrossing                                                                     |

| с                                |           | : voltage step between two non-interpolated nine folding signals                           |

| DAC                              |           | : Digital-to-Analog Converter                                                              |

| DNL                              |           | : Differential Non Linearity [LSB]                                                         |

| F9.                              | (A to D)  | : nine folding signal at the output of the interpolation ladder                            |

| g                                | (/        | : normalized delay variation                                                               |

| INL                              |           | : Integral Non Linearity [LSB]                                                             |

| δ <sub>INL</sub>                 |           | : interpolated zerocrossing - ideal zerocrossing [LSB]                                     |

| ipf                              |           | : interpolation factor                                                                     |

| LSB                              |           | : Least Significant Bit Value defined as $V_{range}$ / (ipf * $N_{ref}$ )                  |

| N <sub>ref</sub>                 |           | : number of voltage levels in the reference ladder                                         |

| SFDR                             |           | : Spurious-Free Dynamic Range                                                              |

| S/H                              |           | : Sample and Hold                                                                          |

| SNR                              |           | : Signal to Noise Ratio                                                                    |

| t <sub>d</sub>                   |           | : delay time                                                                               |

| δt <sub>d</sub>                  |           | : delay time difference                                                                    |

| VCC                              |           | : voltage supply of 3V                                                                     |

| V <sub>ref (high, i,</sub>       | low)      | : voltage reference source ( high =2.5V, $i \in [1,36]$ , low = 1.5V)                      |

| Vin                              | ,         | : input voltage (maximum voltage range = 1V)                                               |

| Vinp                             |           | : differential input voltage of the input gain stage                                       |

| V <sub>tt</sub>                  |           | : output voltage swing of differential output of amplifiers                                |

| $V_{lr}$                         |           | : linear range of the input gain stage                                                     |

| V <sub>range</sub>               |           | : maximum input voltage range defined as V <sub>ref,max</sub> - V <sub>ref,min</sub> - 4*c |

| V <sub>s</sub>                   | (1 to 36) | : output signals of the input gain stages                                                  |

| V <sub>sc</sub>                  | (1 to 36) | : complementary output signals of the input gain stages                                    |

| V <sub>s</sub> - V <sub>sc</sub> | (1 to 36) | : differential output signals of the input gain stages                                     |

| $V_{f}$                          | (1 to 12) | : output signals of the three folding blocks                                               |

| V <sub>fc</sub>                  | (1 to 12) | : complementary output signals of the three folding blocks                                 |

| $V_{f.}$                         |           | : output signals of the three folding comb. blocks                                         |

| $V_{fc.}$ - $V_{f.}$             | ( A to D) | : differential output signals of the three folding comb. blocks                            |

| $\delta V_y$                     |           | : difference between two folding signals                                                   |

| х                                |           | : V <sub>in</sub>                                                                          |

#### PREFACE

This master thesis is performed at the Philips Research Laboratories and the Eindhoven Technical University. The simulations, in the beginning of the assignment, are performed at the University with the circuit-simulator HSPICE. The final part of the assignment is performed at the Philips Research Laboratories. Here, linearity and distortion measurements on the Analog-to-Digital Converter are performed, and the layout of the chip is developed. The total design of the Analog-to-Digital Converter (ADC) is split up into two parts. The analog preprocessing part of the ADC is described in this report. The 'digital' part is designed by Roland van Wegberg and will be described in his report. The workgroup, where these simulations are performed, is called "Integrated Transceivers". The aim of this group is to do research into signal processing and electronics design for integrated circuits and electronic equipment and terminals. Nearly all the expertise's of the group are essential to personal communication products. The application field for the Analog-to-Digital Converter is the digital cellular mobile telephone market.

# 1. INTRODUCTION

Advances in consumer electronics are creating new requirements for high speed data converters: Personal (portable) communication products requires all 6-12 bit converters with power dissipation as important key parameter. The demand for low power consumption with fewer batteries in applications such as wireless and personal communications have motivated engineers scaling down the supply voltage and to develop new IC processes. The availability of high speed analog-to-digital converters gives in digital receivers the opportunity to realize some of the base-band and intermediate frequency processing to be done in the digital domain. The advantage of digital receivers is that they can be made programmable to comply with different standards and that they can be integrated into IC's in order to get very compact (receiver) circuits. At this moment the disadvantage of fully integrated digital receiver circuits is that they consume relative high power. Therefore, the introduction of digital receivers will be done first in base stations, car systems and television receivers. With the use of new IC process techniques, the introduction of more digital signal processing circuits in a receiver will be inevitable in the future. The A/D converter, as described in this report, is making use of a new advanced bipolar IC technology, which can be useful in designing low power integrated circuits.

At first in this report, there will be a short introduction about A/D converter architectures where the folding A/D converter is derived from. The converter is a combination of the well known flash A/D converter [6,7,15] and the two-step A/D converter [20,21]. A short overview of these two types ADC's is described below.

The most straightforward technique to convert an analog signal into an 8-bit output code is the so called 'full-flash structure' (see Figure 1.1). The full-flash architecture requires  $(2^{n}-1)$ comparators, with n the number of bits. The power, die-area and the input capacitance are proportional to (2<sup>n</sup>-1). An 8-bit flash structure requires 255 comparators, together with a set of 255 reference voltages to define all quantisation levels of the ADC. In practice, there is a limit to the power dissipation that can be handled in IC packages. Therefore, the power-dissipation in the comparators stage must be reduced drastically to keep the over-all power dissipation as low as possible. The bandwidth of the system is related mostly to biasing currents, which in turn results in power dissipation. Because of increase of the die size, it is difficult to distribute the clock and input signal lines, and to match all the properties of all these comparators within the same specification. The large numbers of comparators also makes it difficult to make a clockdriver, which can drive the heavy (capacitive) loading. Small rise and fall times are difficult to obtain for these clockdrivers. When a ramp is applied at the input, S-shaped curves will be generated at the output of the comparators. It also can be seen from figure 1.1 that over the entire full-scale input range a sample latch in a full parallel implementation only makes one decision that results in a change of the output code. The use of the latches is not efficient. The comparator outputs yield a thermometer-like code and only the position in the array of the transition between ONE's and ZERO's contains relevant information concerning the immediate level of the analog signal. When the output of, for instance, comparator k is "high", all comparator outputs below k are known to be "high". Although this is common practice in full-flash converters, there is no need to retain the output levels of the comparators that are known anyway during the sample process. Therefore, full-parallel systems retain information that is redundant.

To avoid some problems encountered with the full-flash converter, the two-step architecture was developed. This structure reduces the amount of comparators drastically. The two-step architecture uses a coarse and a fine quantisation to increase the resolution of the converter. At first, a coarse decision is made, using a *k*-bit flash ADC.

Figure 1.2 : Two-step A/D converter structure

This decision is converted back into an analog value using a digital-to-analog converter (DAC) and is subtracted from the original applied input signal. The residual signal is then converted into a  $2^{n-k}$  quantisation levels using (n-k)-bit fine flash ADC. In this system an ideal coarse-fine matching is required. The succeeding conversion steps takes time. The analog signal, to be converted, is held at a constant value by a S/H amplifier. During this hold time, the conversion takes place making it virtually "timeless". In practical applications, timing and accuracy limitations can result in conversion problems resulting in "missing" codes. The number of comparators is now reduced from  $2^n$  comparators to  $(2^{k}-1) + (2^{n-k}-1)$ , which reduces the power dissipation as well as the die area. The DAC must have a resolution of at least n-bit to avoid limiting the performance of the converter. A good balance between circuit complexity, power consumption and die size is obtained in this type of converter. The final dynamic performance however depends on the quality of the S/H amplifier. The structure of the *n*-bits two-step principle is shown in figure 1.2.

The advantages of this structure in comparison with the flash structure are:

- smaller die size

- less hardware then flash structure

- moderate power

The disadvantages are:

- (n-k) DAC needs n-bit linearity

- substractor difficult to implement

- hardware increases exponential with resolution

In a folding analog-to-digital converter the problems discussed above, can be avoided. Therefore this type analog-to-digital converter will be explained in the following chapters. The design parameters of the ADC based on the first transistor models will be shown in the next chapter. Special attention will be given in the following chapters of the design of the preprocessing part of the ADC. Each subcircuit of the preprocessing part will be described thoroughly. Measurements incorporating gain, bandwidth, power dissipation, noise and linearity will be presented from each subcircuit of the preprocessing block. From the finally design a layout is drawn and the floorplan of the preprocessing part will be shown. Finally, conclusions and recommendations on this design will be shown in chapter 11. For the total design of the ADC, with digital part as comparators, rom table, latches and output drivers, will be referred to the graduation report of Roland van Wegberg. In this thesis the final specifications of the total ADC are presented.

# 2. INITIAL DESIGN SPECIFICATIONS

The goal of this project was to design and implement an 8-bit folding ADC with all the necessary subcircuits. The specifications of the ADC, how they are specified at the beginning of the assignment, are shown in table 1. The specifications are based on the first parameters of the IC process.

| radie 1. Design constraint        | is of the Analog-to-Digital Converter         |

|-----------------------------------|-----------------------------------------------|

| Technology                        | bipolar: SPIRIT                               |

| Principle                         | folding and interpolation architecture        |

| Resolution                        | 8-bit + overflow/underflow outputs            |

| Signal to Noise Ratio (SNR)       | > 50 dB                                       |

| Maximum analog bandwidth          | 50 MHz                                        |

| Conversion rate                   | 100 MHz                                       |

| Power consumption                 | $6-9 \text{ mW} \rightarrow 25-30 \text{ mW}$ |

| Analog input signal voltage range | 1 V <sub>pp</sub>                             |

| Supply voltage, V <sub>CC</sub>   | 3 V                                           |

Table 1 : Design constraints of the Analog-to-Digital Converter

These specifications are an estimation of the performances of a low power A/D converter built in this new IC technology. The technology SPIRIT is an advanced bipolar IC process, which produces very small diffusion capacitors in the transistor. The inevitable process parasitic capacitors, later measured in the process, introduces a heavy load for the small transistors. The specifications shown above are too stringent for the new process parameters. The power dissipation shall increase from 6-9mW to approximately 25-30mW due to these additional parasitic capacitors. The transistor model with parasitics is shown in chapter 5. In that way the other specifications, as shown in table 1, remain the same. These specifications show that the folding ADCs are favorable comparing to the original flash converters. The final specifications of the ADC determined by simulation are shown in this thesis later. From the preprocessing block a layout will be drawn. From this layout, an estimation will be done, incorporating the additional wirering capacitance and dummy resistors and shall all be added in the final circuit of the preprocessing part.

# 3. FOLDING AND INTERPOLATING PRINCIPLE

### **3.1** INTRODUCTION

The systems presented here consists only black boxes at this moment. In further chapters, the total implementation of the preprocessing part is discussed. In a folding ADC, the advantages of digital sampling of signals used in a full-flash system are combined with the component saving architecture of the two-step system. No S/H amplifier is required for this system [1,2,3,5,8,9]. The architecture uses an analog preprocessing block to transform the input signal into a repetitive set of output signals to be applied to the fine (flash) converter (see Figure 3.1).

Figure 3.1 : Folding A/D converter architecture

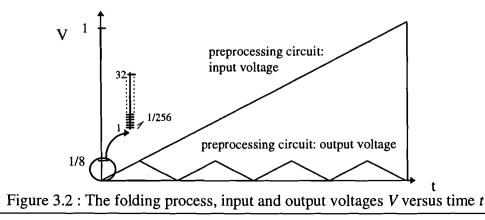

In this system the most significant bits k are determined by the coarse quantizer, which determines the number of times ( $k = \lfloor \log_2(\# \text{foldings}) \rfloor$  bit) a signal is folded. The fine bits (n-k) are determined by the fine quantizer which converts the preprocessed "folded" signal into LSB bits. The preprocessing part is a time continuous circuit which contributes a small amount of propagation delay. As example the principle of an 8 times folding process is shown in figure 3.2.

Note that for the folded signal a triangular signal is used instead of a sawtooth signal. The discontinuities of a sawtooth signal contain very high frequency components, which are difficult to realize in the circuit. Therefore a triangular signal is being used, containing the same information differently coded.

The input signal is applied to a folding circuit. The folded signal at the output of this circuit is applied to a flash converter. Because the folded signal has a smaller range than the input signal, this flash converter can be small. For example, if the input signal is folded 8 times (see figure 3.2) then the folded signal has only 1/8 of the range of the input signal. To get an 8-bit resolution with the folding A/D converter, the folded signal uses 5 bits or 31 comparators. These 5 bits will indicate the value of the input signal within the eight subranges of the input signal is located. Because there are eight subranges the coarse quantisation requires 3-bit or 7 comparators. The number of comparators of the folding A/D converter brings it back from 255 to 38 comparators. The folding structure is different from the two-step principle in that it performs the conversion of the input signal into fine and coarse quantisation in the *analog* domain. This makes it possible to operate the ADC without S/H circuit.

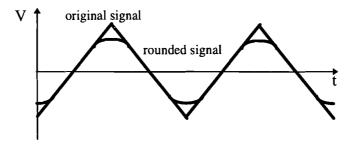

If the frequency of the input signal is increased, the edges of the folding signal will tend to round off, because the bandwidth of the folding circuit is limited. The edges contain the highest frequency components (figure 3.3).

Figure 3.3 : High frequency rounding of the folding signal

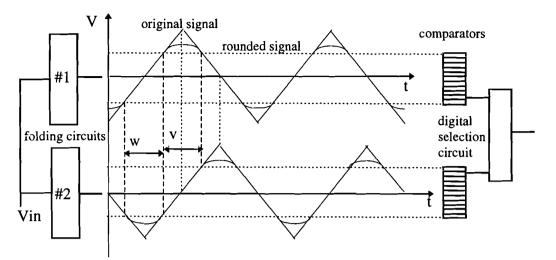

This problem of frequency rounding can be avoided by using two folding signals with a 90°degree phase shift. If one signal is near the edge, the other signal will be around a zero crossing which is his most accurate region. This double folding technique is shown in figure 3.4. The information around the tops can be discarded. For any input signal, one of the two folding signals will be in its linear region.

Figure 3.4 : Double folding technique for the fine selection

For still higher frequencies, even the double folding technique may not be sufficient. By increasing the number of folding circuits, only a decreasing part (W from folding signal #1 cq. V from folding signal #2 in figure 3.4) of the folded signal around zero is used. Although folding saves a lot of comparators, extra circuitry is used to perform the folding operations. The use of folding techniques is only attractive if the die size of the ADC is smaller than the flash-ADC. Fortunately, it is possible to make small size folding circuits. With the folding technique the input signal frequency is multiplied by the number of foldings. So the bandwidth of the preprocessing circuit ( $B = f_{max} * #foldings$ ) is the limiting factor for high frequency input signals.

It is important to see, that the sensitivity for rounding the triangular waveform at high frequencies can be avoided by not quantizing the waveform in amplitude, but quantizing it in the *zerocrossings*. In a differential folding signal, the only information to be gathered is whether it is positive or negative. So, only the zerocrossings in the folding signals are important. Zerocrossings are not affected by the bandwidth of the preprocessing part, so each zerocrossing can represent an input reference level.

By transforming each input reference level into a zerocrossing, the area, input capacitance and power consumption of the ADC would be the same as a flash ADC. By interpolating between two folding signals extra zerocrossings can be defined without folding circuitry. This interpolation is implemented by a resistor network. Moreover the interpolation method will be discussed in the following chapter. At first shall be described how the folding structure of the designed ADC will be implemented.

### 3.2 FOLDING PRINCIPLE USED IN LOW-POWER A / D CONVERTER

As stated before, the actual shape of the folding signal is not important anymore. As long as a folding signal is not affected around the region of the zerocrossing the performance of the ADC will not be influenced. For an 8 bit resolution, the next partitions can be made between the fine and coarse folding circuits. In table 2 an overview of the possible partitions is depicted.

| k -bit coarse | (n-k)-bit fine | # comparators                           | folding factor |

|---------------|----------------|-----------------------------------------|----------------|

| 1             | 7              | $128_{\text{fine}} + 2_{\text{coarse}}$ | 1              |

| 2             | 6              | $64_{\text{fine}} + 4_{\text{coarse}}$  | 4              |

| 3             | 5              | $32_{\text{fine}} + 8_{\text{coarse}}$  | 8              |

| 4             | 4              | $16_{\text{fine}} + 16_{\text{coarse}}$ | 16             |

| 5             | 3              | $8_{\text{fine}} + 32_{\text{coarse}}$  | 32             |

| 6             | 2              | $4_{\text{fine}} + 64_{\text{coarse}}$  | 64             |

| 7             | 1              | $2_{\text{fine}} + 128_{\text{coarse}}$ | 128            |

Table 2 : Partitions between the fine - and the coarse part

When all the characteristics as power consumption, chip area and bandwidth of the subcircuits are defined the best partition can be made. These characteristic are not available at the beginning of the design, but it can be stated that a partition of 128 times folding will not gain the best partition. This configuration leads to very high internal frequencies (128 \* maximum input frequency) which is very difficult to design for the specifications given. Also a partition of 2 times folding will not give the best balance between power and die area of the total ADC. Practical solutions of the partition will be in 4,8 or 16 times folding.

In the process, where the ADC is designed in, it should be possible to fold the input signal 8 times. Chapter 5 makes clear that with a folding rate of eight the bandwidth required for the preprocessing part is available in the implemented process. This will result as denoted in table 2, in a partition of 3-bit coarse and 5-bit fine quantisation. This partition shall be worked out during this design. The number of comparators (NC) in the fine folding part can be directly derived from the folding rate (FR): NC<sub>fine</sub> =  $2^n$  / FR.

Figure 3.5: Generation of the 3 coarse bits and 5 fine bits in folding architecture

One folding signal contains  $2^3$  zerocrossings. With a number of  $2^5$  folding signals 8 x 32 = 256 zerocrossings are incorporated, resulting in an eight bit resolution. Actually, the folding signal incorporates nine zerocrossings in the preprocessing design. This is a result that the

first folding signal both marks the minimum input signal and the maximum input signal! Consider figure 3.6 in this case:

Figure 3.6: Nine zerocrossings in 'fA' due to marking both min. and max. input signal

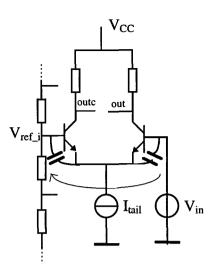

Extra circuitry shall be added for signaling overflow and underflow of the input signal and synchronization of the coarse - part with the fine folding part. A 9 times folding signal can be generated by making use of nine differential pairs with the collectors of the even and odd differential pairs cross coupled and connected to two identical load resistors, and whose inputs are connected to appropriately defined reference voltage levels [9,14] (see figure. 3.7). A disadvantage of this approach is that the output capacitance ( nine base-collector capacitance for one single output) of the nine folding block will be to large. The bandwidth of the folding block is limited too much by this approach. Implementing 9 folding blocks. The input gain amplifiers, coupled on the one side to the reference voltage and on the other side to the input signal transforms the input signal into 36 'one' folding signals. Moreover, these input gain stages will be explained in the chapter 6. Another preprocessing implementation shall be used in this design, namely *Cascaded folding*.

Figure 3.7 : Combination of input signals in1 to in9 into a single nine folding signal

A nine folding block composed of nine cross-coupled differential pairs can be split up into 3 times 3 folding blocks of each three cross-coupled differential pairs [23](see figure 3.8). The

output signals of the input gain blocks are now folded three times and for the combination of the three folding signals another three times folding block should be used (from now on called three folding combination block). This split up relaxes the restrains of transistor matching in the three folding block.

Figure 3.8: Cascaded folding of the input signals s1 to s9 into a nine folding signal

In an actually implementation, the shape of the nine folding signal is as a 'sine' wave. But as stated before, the shape of the folding signal does not matter. The information is contained in the position of the zerocrossing!

### **3.3** FINE FOLDING SIGNAL GENERATION

The implementation of the folding blocks is discussed for the generating the fine folding signals. From the nine times folding signal five 'fine' bits should be generated. Due to this 32 folding signals should be generated within the fine folding circuit. These 32 folding signals can be made by 4 nine folding signals (fA,fB,fC,fD) with between each two folding signals an 8 times interpolation. The number of interpolations (ipf) multiplied by the number of folding signals must be equal to 32 folding signals. The 4 nine folding signals are generated parallel by four identically blocks. When using 4 nine times folding signals at least 36 reference voltage levels (N<sub>ref</sub>) should be needed for the definition of the quantisation levels. The zerocrossings of the folding signal fB is shifted along the V<sub>in</sub> -axes  $-1/32*V_{range}$

with respect to the fA zerocrossings. Generation of the fC zero crossings have been shifted -  $2/32*V_{range}$  and fD zerocrossings  $-3/32*V_{range}$ .

The generation of the missing 28 folding signals will be performed by resistive interpolation. Moreover, this interpolation is discussed in the next chapter. A schematic overview of the generation of the fine folding signals with the *cascaded folding principle* is given in figure 3.9. The 36 reference voltages are generated by a ladder of 36 resistors. The top level of the ladder is connected to  $V_{ref,max}$  and the minimum level is connected to  $V_{ref,min}$ .

Figure 3.9 : Overview of the '3' - and '9' folding signals as function of the input voltage

In appendix A an other '3' folding implementation is shown. This technique has the only advantage of the short routing between the three folding block to the three folding combination block. The three folding method, as discussed above, gives a better spreading of the '3' folding signal over the input range. The voltage distance between the three 'one' folding signals in the three folding block is less: (4/36V) instead of 12/36V in the principle used above in figure 3.9. At high frequency operation of the ADC, the slope of the folding signals is smaller. When the distance between the zerocrossings is small, the folding signal does not reaches his output swing as in total saturation.

### **3.4** INTERPOLATING PRINCIPLE USED IN LOW-POWER A/D CONVERTER

As stated before, the generation of the missing 28 folding signals should be generated by interpolation. Interpolation is a convenient way to generate the missing folding signals. Interpolation can be performed with a few different methods [11,12,13,18]:

- current interpolation

- voltage interpolation

The method current interpolation, is not compatible with the low power specification of the ADC. Voltage interpolation is the most popular way for interpolation in bipolar technologies. It does not results in additional power dissipation and it occupies a relative small die area on the chip.

The output voltages of two neighboring nine folding signals are applied to a resistive network of eight resistors. This network performs a resistive division and generates the signals equivalent to the nine folding signals. In figure 3.10 a division by eight is implemented. With the interpolation circuit the seven extra folding signals are generated. Between the four non-interpolated folding signals the missing 28 signals are generated and forms a total of 32 folding signals. Other practical realizations of voltage interpolation circuits have been published in [9,12,13]. As depicted in figure 3.10, interpolated folding signals does not affect the performance of the ADC. Nonlinearities in the folding signals causes

shifts in the zerocrossings of the interpolated signals with respect to the desired equidistant zerocrossings. Therefore, this phenomenon is discussed in the next chapters as the INL (Integral Non Linearity) of the folding circuit.

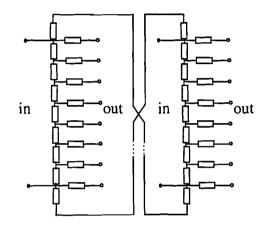

Because of the symmetry of the folding encoder outputs, the interpolation circuit has a circular symmetry. This means that each folding signal has two neighboring folding signals. Care has been taken to compensate of the delay difference introduced by the different output impedance's of the taps of the interpolation circuit. The form of the implemented interpolation circuit is depicted in figure 3.11.

Figure 3.11 : Circular interpolation circuit

The zerocrossings of the 32 folded signals, coming out of the interpolation circuit, are detected by 32 comparators. These comparators are of the master/slave type to increase their sensitivity. The folding signals are made 'digital' in the slave comparator. With the 32-bit circular code the actually fine bits are generated.

#### 3.5 OVERVIEW OF THE USED PREPROCESSING TECHNIQUE

This section deals with the total fine signal processing part in block diagram of the ADC. The generation of the folding signals, discussed in the previous chapter, is given in a schematic overview of folding block with the input gain stage connected to the folding blocks. In this figure the circular symmetry of the interpolation structure is seen. The symbols of the biasing circuits, discussed later, also are depicted in figure 3.12.

reference ladder taps:ref1 to ref36input gain stages:1 to 36three folding blocks:f1 to f12three folding combination blocks:fA to fDoutput signals interpolation ladder:f9., f9.1 to f9.7 with . = A, B, C, D

# 4. BLOCK DIAGRAM FOLDING A / D CONVERTER

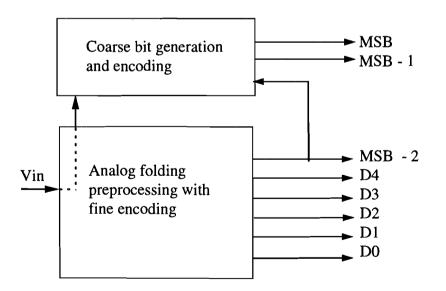

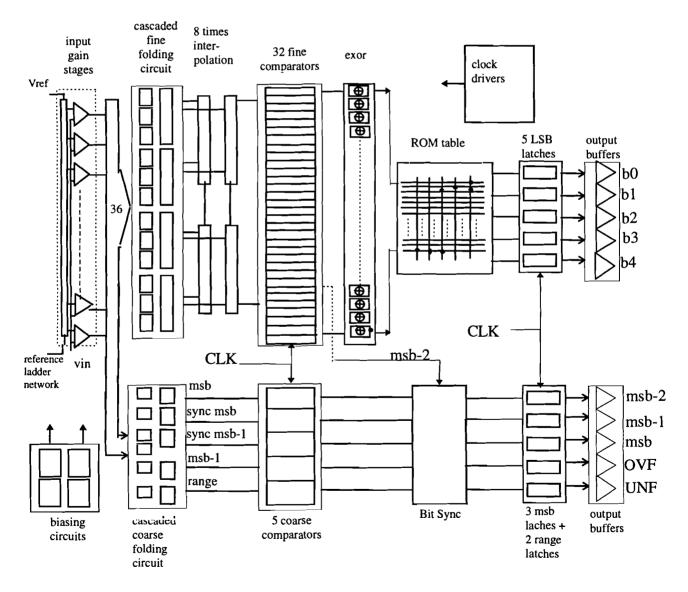

A short explanation of the rest of the ADC after the analog signal processing part is discussed in this chapter. The structure of the total folding A/D converter is depicted in figure 4.1. The preprocessing part consists of the input gain stages with reference ladder, cascaded fine folding circuits with interpolation ladder and coarse folding part. The digital transformation of the analog folding signals converter begins with the comparators. From the 32 fine folding signals a circular thermometer-like output code will be generated.

Figure 4.1 : Structure of the folding Analog-to-Digital Converter

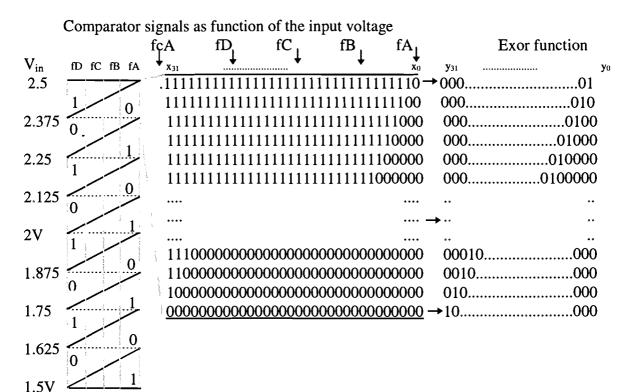

In the comparators, an error correction circuit is built in to ensure that their outputs are consistent which each order [4,23]. The first encoding step is the isolation of the 0 to 1 transition in the circular 32 bit code. This is performed by the application of an EXOR operation directly behind the comparators (see figure 4.2).

Figure 4.2: Output code comparators including EXOR-operation

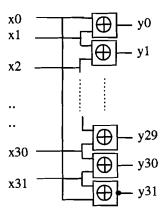

The output code of the EXOR-operation (figure 4.3) is a so called *one high* code. This type of code can easily be decoded into a five bit binary code. A ROM structure for encoding is used. The functions implemented in the ROM table can be derived. For example the function for the LSB bit is:  $D_0 = \sum_{i=1}^{16} y_{2i-1}$ , this summation means a normally digital

OR function. The other functions for the fine bits can also be derived from table 3.

| Table 3:         5-bit Fine Encoder |                |             |

|-------------------------------------|----------------|-------------|

| Fine comp. levels                   | EXOR code yi   | Binary code |

| 0                                   | -              | 00000       |

| 1                                   | У1             | 00001       |

| 2                                   | y <sub>2</sub> | 00010       |

| 3                                   | y <sub>3</sub> | 00011       |

| 4                                   | y4             | 00100       |

| ••                                  | • •            | ••          |

| ••                                  | ••             | ••          |

| 28                                  | <b>y</b> 28    | 11100       |

| 29                                  | <b>y</b> 29    | 11101       |

| 30                                  | <b>Y</b> 30    | 11110       |

| 31                                  | <b>y</b> 31    | 11111       |

Figure 4.3: Exor function

The generation of the coarse signals will be discussed in chapter 8. These signals cannot be generated by a flash A/D converter because there is a delay in the preprocessing block. The coarse folding signals should be derived from the fine folding signals. There is one of the four non interpolated fine folding signals which is equal to the MSB-2 bit. From this MSB-2 signal, the other coarse bits can be generated and synchronized. Digital logic should extracts and synchronizes the desired coarse bits in the Bitsync block. Signals for overflow (OVL) or underflow (UVL) are also generated by this block. Overflow forces all outputs to logical "1", and underflow forces all the outputs to logical "0". What remains of the ADC are auxiliary circuits: clock drivers, bandgap reference circuits, output latches and output buffers. The bandgap reference circuits will be discussed in chapter 9. All the other remaining circuits shall be discussed in the master thesis of Roland van Wegberg.

To conclude the discussed block diagram of the ADC some remarks can be summarized:

- Analog preprocessing in the folding and interpolation A/D architecture reduces the number of comparators significantly compared to flash converter architectures. The architecture presented in this thesis needs 32 comparators for the fine encoding and 5 comparators for the coarse encoding. This reduction of comparators is also a reduction in power dissipation and chip area.

- By incorporating the folding technique there also is a noise reduction. The noise generated in the digital part of the ADC is less, because less encoding circuitry is required in this type of converter.

- The bandwidth of the circuit depends on the folding factor, input frequency and the maximum allowable distortion components (mostly third-order components). Therefore, the relation bandwidth/input frequency of the system is discussed in chapter 6.

- The eight times interpolation circuit is an easy way to generate the missing folding signals at the costs of relative small die area and power consumption.

The preprocessing part and the generation of the coarse folding signals on transistor level are discussed in the chapter 6,7 and 8. In chapter 5 the implementation of the architecture into bipolar transistor logic is discussed.

# 5. BIPOLAR TECHNOLOGY : SPIRIT

## 5.1 INTRODUCTION

The A/D converter will be implemented in the SPIRIT process. SPIRIT is an advanced new bipolar process developed by Philips Research. In this new process low power circuits can be realised due to the small process parasitics. There is no coupling between substrate and the active region. In the ADC design there is only made use of vertical integrated NPN transistors. Normally, for low power designs CMOS circuits are used. The advantage of CMOS technology over bipolar is that the A/D converter can be integrated on the same die as the digital signal processing part. This new technology however, has very small parasitic capacitance and is developed especially for RF circuits. During the assignment the parameters of the bipolar transistors has changed several times. At this moment, the process is not clearly defined, which is a great disadvantage of this process. The transistor parameter settings of the IC process Lab. in Hamburg has been taken for the final realisation of the A/D converter. These parameter settings are worse than the parameter settings from the process at the Nat.Lab. The geometry of the 'Hamburg' transistor is much larger, so the junction capacitance and the maximum  $f_t$  is higher than was assumed first. In the beginning of the assignment, the maximum power dissipation of the total A/D converter was set on 6-9mW. With the transistors of the NatLab, this could be possible with a few additional mWatts. With the 'HamburgLab' parameters the specification of 6-9mW is not realistic anymore. In the design specifications, the power dissipation should be a factor 3 to 4 times higher ( about 25-30mW), for a realistic specification with the same full-scale analog input signal bandwidth.

# 5.2 RESISTORS

There are three types of resistors used in the ADC. A summarize of the resistors with sheetresistance and sort of material is given below:

1. Epi resistors: sheetresistance of  $20k\Omega$ /square

This is a high resistivity resistor made in mono crystalline silicon.

2. "PSS" resistors: sheetresistance of  $115\Omega$ /square

A medium resistivity resistor made in the emitter poly-silicon layer.

3. "BN" resistor: sheetresistance of  $22\Omega$ /square

A low resistivity resistor made from the collector contact layer. This layer is used as local interconnect layer. Due to the one metal layer technology there are no crossings possible. Crossings are made with these resistors. Also the reference ladder is implemented with this

type of resistor. The "BN" resistor has better matching properties than the medium ohmic "PSS" resistor.

### 5.3 NPN TRANSISTORS

The type of transistor used in the preprocessing part is the vertical N10L24PM transistor. This type is derived from the earlier 'D-25' NatLab. transistor. A full parameter list of transistor N10L24PM is given in appendix B. The most important design parameters are summarized and listed in table 4.

```

Table 4: Important design parameters of NPN TYPE: 'N10L24PM'

```

| IS     | = 1.6000E - 18: | collector emitter saturation current,           |

|--------|-----------------|-------------------------------------------------|

| BF     | •               | ideal forward current gain,                     |

| QBO    | = 6.5100E-15;   | base charge at zero bias,                       |

| RCC    | = 66.6500;      | constant part of the collector resistance,      |

| RCV    | = 5.4880E+03;   | resistance of the unmodulated epilayer,         |

| RBC    |                 | constant part of the base resistance,           |

| RBV    | •               | variable part of base resistance at zero bias,  |

| RE     |                 | emitter serie resistance,                       |

| CJE    |                 | zero bias emitter-base depletion capacitance,   |

| XCJE   |                 | fraction CJE that belongs to the side wall,     |

| CJC    |                 | zero bias collector-base depletion capacitance, |

|        |                 | fraction CJC under the emitter area,            |

| Additi | onal parasitic  | s in the transistor model:                      |

| CBC    |                 | CBE = 1.3000E-15, CBG = 1.0700E-15,             |

| CCE    | = 4.8700E-16,   | CCG = 4.7000E-16, $CEG = 5.6000E-16$ ;          |

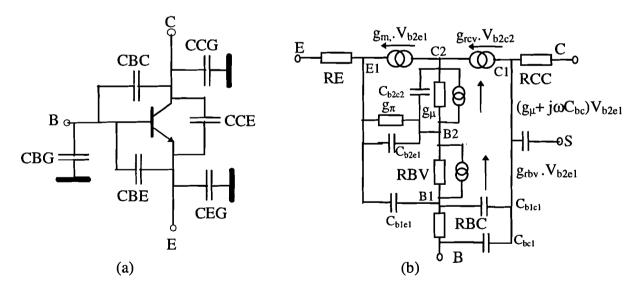

These PSTAR parameters are used in the level 503 bipolar NPN transistor TNS model. The model with parasitic capacitors is depicted in figure 5.1a.

Figure 5.1: (a) NPN transistor with additional parasitic capacitors (b) Simplified small signal equivalent circuit for vertical NPN transistor

The small signal AC model is simplified represented in figure 5.1b. The values of the capacitors in the small signal model are defined as follows:

$C_{b1c1} = (1 - XEXT)^*(1 - XCJC)^*CJC = 2.46E-16$  F (XEXT = 0.05, see appendix B)  $C_{bc1} = XEXT^*(1 - XCJC)^*CJC = 1.29E-17$  F

$C_{blel} = XCJE*CJE$ 0.00 F  $C_{b2e1} = (1 - XCJE)*CJE$ 9.87E-16 F  $C_{h2c2} = XCJC*CJC$ 6.63E-17 F 0.00 F (no coupling between the substrate!!) Cis

The base-emitter capacitance is the sum of the junction and diffusion capacitance and is supply dependent. The dependent current sources  $g_m * V_{b2e1}$ , is the collector current in the transistor which is controlled by the internal base-emitter voltage. The parameter g<sub>m</sub> is called the transconductance of the transistor;  $g_m = Ic / V_T = q^*Ic / kT$  only when  $V_{be} >> V_T$ .

It is directly proportional to the current itself. The input conductance  $g_{\pi}$  is derived from the large signal Ebers-Moll equations:  $g_{\pi} = 1/r_{\pi} = g_m / \beta_F$ .

Now some parameters of the transistor are calculated needed in the design of the circuits:

Now some parameters of the transistor are calculated ... The effective base resistance near peak  $f_T$ :  $R_b = RBC + \frac{RBC}{1 + \frac{V_{de}C_{je}}{OBO}} \approx 4333 \Omega$

according the PSTAR parameters. The base-emitter diffusion capacitance can be calculated  $C_d = \frac{g_m}{2\pi f_r}$ . The extrinsic input bandwidth  $f_V$  as function of the bias current is with:

shown in figure 5.2 and can be written as:  $f_V = \frac{1}{2\pi R_b \left( 2C_{jc} + C_{je} + C_d \right)}$ .

Also an important characteristic for the design of high speed low power circuits is the cutoff frequency as function of the collector current (see figure 5.2).

Figure 5.2:  $f_T$  and  $f_v$  as function of  $I_c$ : transistor N10L24PM

In the following chapters, the design of the preprocessing part on transistor level is discussed. In all the circuits, the used transistors are implemented as transistor N10L24PM.

# 6. REFERENCE LADDER WITH INPUT GAIN STAGES

#### **6.1** INTRODUCTION

Differential pairs are perhaps the most widely used two-transistor sub-circuits in the monolithic analog circuits. The usefulness of this circuit comes from the fact that the emitter coupled pairs can be directly coupled to one another without interstage of coupling capacitors. In this chapter, the function of the differential pair in the folding A/D is discussed. The dc and frequency properties will be considered of the simplest circuit, a common-emitter amplifier. Because of the low power dissipation of the ADC the input gain stages are implemented as simple as possible. So, no emitter followers are used, where possible, and the tail current is kept as low as possible. The biasing circuit is implemented as a current mirror and the amplifier is restively loaded. One side of the differential pair is coupled to one tap of the resistor reference ladder. The reference ladder consisting of 36 resistors forms the quantisation levels for the input signal. Also the influence of the performance of the input gain stages will be analysed with respect to the reference ladder in this chapter. An input gain stage with a part of the reference ladder is given below in figure 6.1.

Figure 6.1 : Simple differential pair with reference ladder tap connection

First, the range of the input signal  $V_{in}$  will be discussed. For this moment assume that the  $V_{be}$  of the transistor is approximately 0.8V. The current source of the differential pair needs at least a minimum voltage on the common emitters of 0.6V. A minimum input voltage of 1.4V is proposed. The base collector diode in the current source transistor is now 200mV forwarded. For safe operation of the current source, the minimum input voltage is adjusted

to 1.5V. The circuits should operate at a power supply of  $V_{CC} = 3V$ . The maximum amplitude of the input signal is  $1V_{pp}$ . The range of the input signal lies between the ranges:

$$V_{ref,min} \le V_{in} \le V_{ref,high}$$

$1.5V \le V_{in} \le 2.5V$

#### 6.2 BANDWIDTH VERSUS INPUT FREQUENCY RATIO OF THE ADC

-

In a folding ADC the amplitude of the input signal ( $V_{fs}$ ) is much larger than the linear range of the input gain stages ( $V_{lr}$ ). The input gain stages are overdriven by the input signal, and the zerocrossings at the output of the amplifier are delayed in time. The input signal is compared with 36 voltage reference levels. A zerocrossing occurs when the input signal equals the reference voltage level. The delay of the zerocrossing can simply be calculated by modeling the amplifier stage as an amplitude limiting circuit and a bandwidth ( $f_b$ ) limiting circuit. The result of the normalized delay variation  $g = \delta t_d/RC$  after simplification becomes [20,21]:

$g \approx e^{-2b_n \frac{V_{l_r} \cdot f_h}{V_{f_s} \cdot f_{l_n}} - 1}$ , where  $b_n$  is the relative output voltage at which the signal delay is determined. In the situation of the ADC we have a value of  $b_n = 0.5$ . From this equation the following can be concluded for a minimum delay variation:

- The linear range  $V_{ir}$  of the input gain amplifier must be large

- A large amplifier bandwidth f<sub>b</sub>

- A small full scale range V<sub>fs</sub> of the converter

In the bipolar technology a linear range of the input gain stage of about 120 to 180mV can be obtained, depending of the gain and the amplitude of the output signal. The bandwidth of the system is mostly related to the dc bias conditions of the amplifier stages. A large bias current results in a large power dissipation, so there must be a compromise in choosing the bias current in relation with bandwidth. These results can be used in the distortion calculations in relation with the bandwidth/input frequency ratio. A good approximation ( $\delta t$ ) of the delay difference  $\delta t_d$  as a function of the input frequency is :

$$\delta t = -\delta t_d |\cos \omega t|$$

This delay function is normalized for zero variations at the tops of the input signals. The distortion can now be calculated by inserting this equation in the function:

$$V_{out} = \sin(\omega(t+\delta t)) = \sin(\omega t)\cos(\omega \delta t_d | \cos \omega t |) - \cos(\omega t)\sin(\omega \delta t_d | \cos \omega t |)$$

assume that  $\delta t_d \ll t$  and  $|\cos \omega t| \approx 2/\pi + 4/(3\pi) \cos(2 \omega t)$  results in:

$V_{out} = \sin \omega t + 8 / (3\pi) \omega \delta t_d \cos \omega t + 2/(3\pi) \omega \delta t_d \cos 3\omega t$

From this equation it is shown that signal-dependent delay results in third harmonic distortion of the input signal after conversion takes place in a linear ADC.

For a third harmonic distortion of at least -50dB with a full scale input range of 1V the bandwidth/input frequency ratio should at least be 10 [20,21]. This results in a bandwidth of the preprocessing block of the folding A/D converter of minimal 500MHz. In this calculation other distortion products due to ladder non-linearity, comparator offset voltages and so on do not occur. The actual input range is smaller than 1V. Of the 36 reference levels are only 32 levels needed for an eight bit resolution. The input range becomes now 1V - 4/36V = 8/9V. The bandwidth/input frequency ratio of 10 is high enough for this input range.

#### 6.3 INPUT GAIN STAGES

#### 6.3.1 Standard implementation of a differential input amplifier

We assume that the base of the transistor is driven by a voltage source of value  $V_{in}$ . The large-signal behaviour of the differential pair is important because it illustrates the limited range of the input voltages over which the circuit behave linearly. For the simplicity the output resistance of the current source is infinity, and the base resistance of the transistor are neglected. These assumptions do not affect the large signal behaviour and the low frequency aspect of the circuit. In the bipolar differential pair of the A/D converter only the zerocrossing is important, so both transistors are conducting and not saturated. We first sum the voltages around the loop of the two voltage sources and the two base-emitter junctions:

$$V_{ref_i} - V_{bel} + V_{be2} - V_{in} = 0$$

From the Ebers-Moll equations, assuming that  $V_{be1}$ ,  $V_{be2} >> V_T = kT/q$ , (Thermal voltage)

$$V_{be1} = V_T \ln \frac{I_{c1}}{I_{s1}}$$

$$V_{be2} = V_T \ln \frac{I_{c2}}{I_{s2}}$$

Combining these two relations and assuming that  $I_{s1} = I_{s2}$ , and  $-(I_{e1} + I_{e2}) = 1/\alpha_F(I_{c1} + I_{c2})$  we will find :

$$\frac{I_{c1}}{I_{c2}} = e^{\left(\frac{V_{in}}{V_T}\right)}$$

$$V_{out\_dif} = V_{outc} - V_{out} = \alpha_F I_{bias} R_{load} \cdot tanh\left(\frac{V_{in} - V_{ref\_i}}{2 * V_T}\right)$$

The output voltage swing:  $A_{tt} = 2 * A = 2* I_{bias} * R_{load}$ .

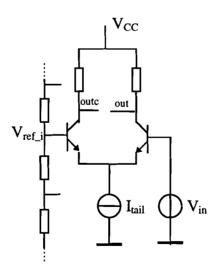

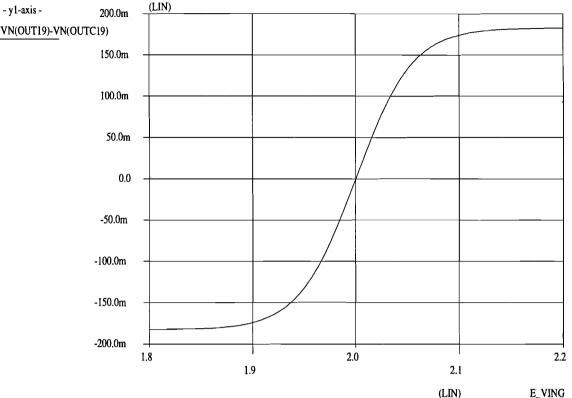

Figure 6.2 : Input gain stage, differential output voltage as function of the input voltage

This output voltage function is plotted in figure 6.2. Here, a significant advantage of the differential pair is apparent: When  $V_{in} = V_{ref_i}$  the output voltage is zero, which allows direct coupling of cascaded stages without introducing dc offsets.

Note that for input voltages of several hundred millivolts, the collector current Ic becomes independent if the input signal, since all current flow through one of the two transistors. Only for differential voltage less than approximately 50mV does the circuit behave like a linear circuit. In the folding A/D converter 36 input amplifiers are used, connected with the reference ladder and the input signal. The voltage step between two successive taps is 1 V /  $36 \approx 27.8 \text{mV}$ , so the circuit behaves in linear fashion round  $V_{\text{ref_i}}$ . The gain of the input stage can be derived as follows; the differential mode gain  $A_{dm}$ , is the change in the differential output  $V_{\text{out}}$  per unit change in the differential input  $V_{\text{inp}} = V_{\text{ref_i}} - V_{\text{in}}$ .

$$A_{dm} = \frac{dV_{out}}{dV_{inp}}\Big|_{V_{ref_{-}i} = V_{ing}} = \frac{I_{bias} * R_{load}}{2 * V_{T}} = g_{m} * R_{load}$$

The common mode gain  $A_{cm}$ , is the change in the common-mode output voltage  $(V_{out}+V_{outc})/2$  per unit change in the common-mode input:

$$A_{cm} = \frac{g_m * R_{load}}{1 + 2 g_m R_o \left(1 + \frac{1}{\beta}\right)},$$

with R<sub>o</sub> the output impedance of the current source for biasing the differential pair.

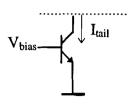

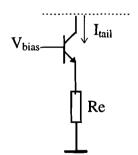

The current source can be a single bipolar transistor as depicted in figure 6.3.

Figure 6.3 : Current source using a single transistor

With the approximation that  $\alpha_F = 1$  and assuming  $V_{bias} >> V_{T}$ , the tail current follows out:

$$I_{tail} = I_s e^{\frac{V_{bias}}{V_T}}$$

A feature of the current source is the sensitivity for variations in  $V_{bias}$ . The sensitivity is defined as:

$$S_{v} = \frac{\partial I_{tail}}{\partial V_{bias}} = \frac{I_{s}}{V_{T}} e^{\frac{V_{bias}}{V_{T}}} = \frac{I_{tail}}{V_{T}} = g_{m}$$

The high sensitivity to voltage variations is a great disadvantage of this approach biasing a differential pair. The tail current must be as stable as possible. The sensitivity of the current source can be decreased by using an emitter resistor (see figure 6.4).

Figure 6.4 : Current source using a transistor with emitter resistor

Now the variation of the output current with the  $V_{\text{bias}}$  can be written as:

$$S_{V} = \frac{\partial I_{tail}}{\partial V_{bias}} = \frac{I_{s}}{V_{T} + Re \cdot I_{tail}} e^{\frac{V_{bias}}{V_{T}}} = \frac{I_{tail}}{V_{T} + Re \cdot I_{tail}} = \frac{g_{m}}{1 + Re \cdot g_{m}}$$

The output current variation of the current source is now decreased a factor  $1 / (1+\text{Re}*g_m)$ . The maximum voltage on the emitters of the input gain stage is 750mV. The V<sub>bias</sub> cannot be chosen to high, because the maximum allowable forward voltage of the base-collector voltage is 200mV. For an insensitive current source to voltage variations, the voltage over

the emitter resistor Re must be approximately 200 - 300 mV. The V<sub>bias</sub> must be generated with additional circuits discussed in chapter 9.

One of the most important aspects of the current source performance is the variation of the current source with changes in the voltage at the output (common emitter point) terminal. This is characterised by the small-signal output resistance of the current source. The common mode rejection ratio depends directly on this resistance. Mostly it is assumed that the collector current is independent of their collector-emitter voltages. Actually, the collector current slowly increases with the increasing collector-emitter voltage, due to the base-width modulation effect. The output impedance of the current source can be defined as:

$$R_o = \frac{\partial V_c}{\partial I_{tail}} = ro\left(1 + \frac{I_{tail}Re}{V_T}\right)$$

, with ro =  $V_{early}/I_{tail}$

Thus, the  $R_o$  depends on  $I_{tail} R_e$ , which is the dc voltage across  $R_e$ . A large  $R_o$  results in improvement of the common-mode-rejection-ratio (CMMR). For a conventional differential pair used as in the input gain stage, the CMMR can be defined as [22]:

$$CMMR = \frac{A_{dm}}{A_{cm}} = 1 + 2g_m R_o \left(1 + \frac{1}{\beta}\right) \approx \frac{I_{tail} \cdot R_o}{V_T}$$

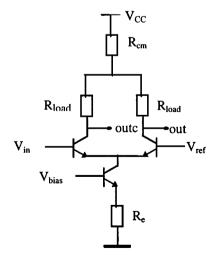

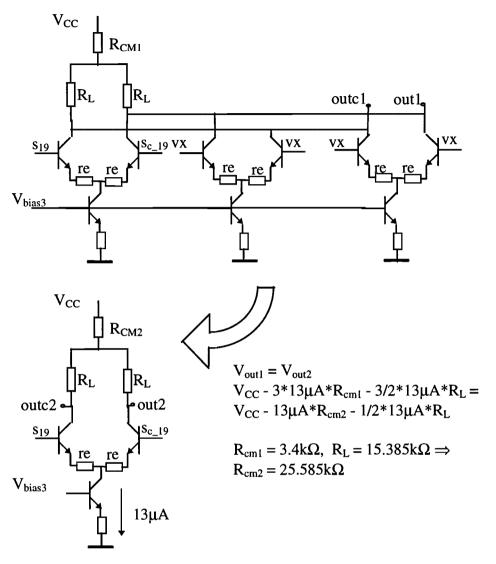

Because of the low power constraint, the use of emitter followers in each input gain stage is not useful. The advantage of emitter followers is the low output impedance for driving the wirering capacitive load and the dc-shift of 'one' Vbe. The total bias current through each input gain stage would be too high, so other possibilities should be investigated. Without emitter followers, problems occurs by coupling the input stage to the inputs of the three folding block. The minimum voltage at the bases of the three folding block is to high for direct coupling of the input gain stage with the three folding block. In order to establish the needed level shift in the differential pair, a resistor  $R_{cm}$  is used as shown in figure 6.5.

Figure 6.5: Levelshift in input gain stage with R<sub>cm</sub>

For the finally dc settings will be referred to the chapter 6.6. First the ideal output swing,  $I_{bias}$  and gain should be extracted. These factors also depend on the AC behavior and the Integral Non Linearity (INL) of the converter.

In the dc behaviour described above, the effects of parasitic capacitance and charge storage in transistors were not considered. However, as the frequency of the signal being increased, the capacitive elements in the circuit eventually dominated the behaviour of the circuit. AC-analysis on the input gain stages and other fine folding circuits are performed in chapter 7.5.2.

### 6.4 REFERENCE LADDER NETWORK

#### 6.4.1 Influence of noise on the ladder network

In a folding A/D converter the step size of the reference ladder is larger than in a flash converter. The reference levels are generated with a resister ladder network. Noise sources can result in inaccurate decisions of the comparator. The zerocrossing detoriates by influence of noise (1/f noise is not included). The maximum rms noise voltage for one side of the input of the differential pair can be calculated as follows:

$$e_{rms} = \sqrt{\left(4kT\left(R_{bb'} + \frac{1}{2g_m}\right)\Delta f\right)} = \sqrt{\left(4kT\left(4445 + \frac{25\cdot10^{-3}}{8\cdot10^{-6}}\right)500\cdot10^6\right)} = 0.25mV$$

This formula includes the independent noise sources: thermal noise and shot noise. The base resistance Rbb' exists out a constant and a variable part. In the formula is assumed that the bandwidth is 500MHz and the bias 'tail' current through the differential pair 8uA. The base resistance according the MEXTRAM transistor model transformed to the HSPICE model in a transistor can be calculated as:

$$R_{bb} = RBC + \frac{3RBV}{q1+q2} \approx RBC + RBV = 1112 + 3333 = 4445\Omega$$

These assumption is based on the translating of the Mextram models parameters to the Spice models for performing the analysis on a HSPICE circuit simulator.

The noise voltage of 0.25mV corresponds with an error of 0.072LSB and hence the noise plays no important role here.

### 6.4.2 Definition maximum ladder resistor value

The definition of the maximum ladder resistance comes from the fact that there is a capacitive coupling between the input signal and the reference ladder. The standard implementation discussed in chapter 6.3.1 is depicted with base-emitter capacitance in figure 6.6.

Figure 6.6 : Reference ladder feedthrough of input signal via series capacitive combination in the differential pairs of the input stages

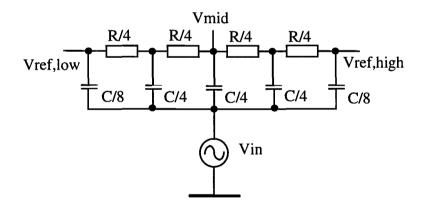

These capacitive coupling detoriates the reference voltage  $V_{ref_i}$ . This voltage determines the position of the zero crossing and variation in this zerocrossing will result in distortion of the ADC. A simple model can be given [14] to calculate the maximum allowed reference ladder resistance. In figure 6.7 this model is shown. The maximum feedthrough will occur at the middle tap of the reference ladder.

Figure 6.7 : Calculation model to derive the maximum feedthrough on the reference ladder

The total reference ladder resistance R is divided into four equal sections R/4, and the total coupling capacitance C of all the input stages has been divided into five capacitors. The model shown in figure 6.7 is symmetrical, so only one half of this model has to be used to calculate the feedthrough on the middle tap of the reference ladder. The transfer function  $V_{mid}/V_{in}$  is calculated in [14] with  $V_{in}$  the input voltage and  $f_{in}$  the input frequency given by:

$$\frac{V_{mid}}{V_{in}} = \frac{\alpha(\alpha + 32)}{\alpha^2 + 32\alpha + 128} , \text{ with } \alpha = \pi f_{in} RC.$$

When it is assumed that  $\alpha \ll 1$  then the equation can be simplified to

$$\frac{V_{mid}}{V_{in}} = \frac{\pi}{4} f_{in} RC.$$

The maximum reference ladder resistance for a given feedthrough is now defined by:

$$R_{ladder,max} = \frac{4 \frac{V_{mid}}{V_{in}}}{\pi f_{in}C} = \frac{4\theta}{\pi 2^n f_{in}C} \,.$$

In this equation  $\theta$  represents the feedthrough in LSB and is *n* the resolution of the ADC in number of bits. The total coupling capacitance of one input gain stage consisting of two base-emitter capacitors and two parasitic process base-emitter capacitance in serie.

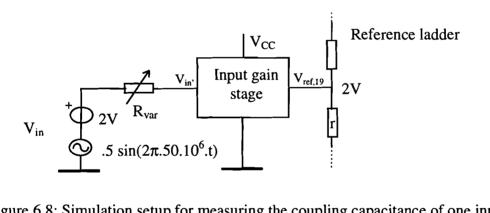

Simulation results show that for the DC operation point ( Ibias = 8uA ) the total base-emitter capacitance of one transistor is 4.78fF. Two of these capacitors in serie give a total coupling capacitance of approximately 2.4fF. Other parasitic capacitance are not included with this simulation result. For an 'exact' value of the total coupling capacitance a simulation is done by assuming the differential pair as a black box. The simulation setup is shown in figure 6.8.

Figure 6.8: Simulation setup for measuring the coupling capacitance of one input gain stage

The input of the input gain stage is connected to a sine wave of 50MHz with amplitude of 500mV. The black box is in balance. With the variable resistor  $R_{var}$ , the input signal  $v_{in'}$  is adjusted to exactly  $\frac{1}{2}\sqrt{2^*V_{in}}$  after a few periods. The resistor value where this  $V_{in'}$  level is achieved is  $1.6M\Omega$ . The coupling capacitance can now be derived as follows:

$$C_{coupling} = \frac{1}{2\pi \ 50 \cdot 10^6 \ 1.6 \ M\Omega} = 2 \ f \ F$$

The total coupling capacitance for 36 input gain stages become:

$$36 * C_{coupling} = 72 fF.$$

The maximum ladder resistor value becomes now:

$$R_{ladder,max} = \frac{4\theta}{\pi 2^{n} f_{in} C} = \frac{4}{\pi \cdot 256 \cdot 50 \cdot 10^{6} \cdot 72 \cdot 10^{-15}} = 1440\Omega$$

$$r_{max} = \frac{1440}{36} = 40\Omega$$

$$P_{refladder,max} = 694\,\mu\,W$$

The power dissipation is calculated with a input range of 1V. It is possible to the reduce the feedthrough by external decoupling the middle tap of the ladder. A disadvantage of this external decoupling is the inductance of the bondwire, reducing the decoupling at higher frequencies.

## 6.5 NONLINEARITY OF THE INPUT STAGE

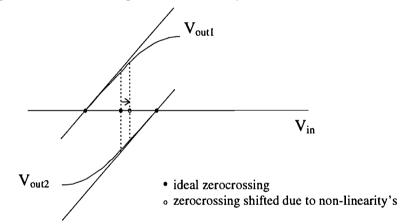

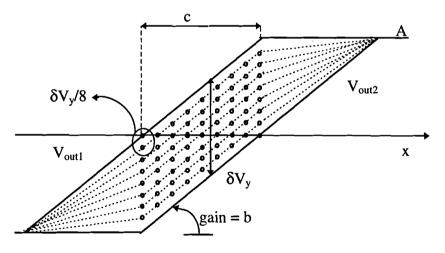

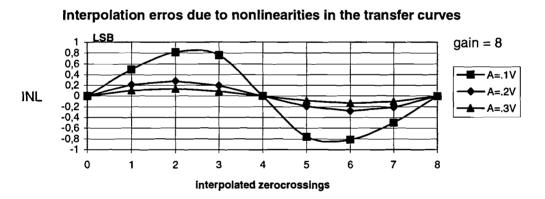

In this chapter, the influence of the nonlinearities of the input curves is discussed. A formula is derived for the position of the interpolated zerocrossings. The non-linear output curves causes the main part of the total Integral Non Linearity of the ADC.

Figure 6.9: Interpolation errors due to nonlinearities of the input stage

The position of the interpolated zerocrossings is depended of the gain, the distance between two folding signals and the amplitude of the fine folding signals. A definition of the used symbols in the following derivation is depicted in figure 6.10. The nonlinear output curve of the input gain stage is defined as:

$$V_{out1} = \alpha_F I_{bias} R_{load} \cdot tanh\left(\frac{V_{in} - V_{ref_{-1}}}{2 * V_T}\right)$$

$$V_{out2} = \alpha_F I_{bias} R_{load} \cdot tanh\left(\frac{V_{in} - V_{ref_{-2}}}{2 * V_T}\right),$$

with  $V_{ref,2} - V_{ref,1} = c = (V_{range})/32 = (8/9)/32 = 1/36$  V as the distance between two nine folding signals. The output swing is defined as  $A = \alpha_F I_{bias} R_{load}$  and the gain b can be

defined as:

$$b = g_m R_{load} = \frac{I_{bias}}{2V_T} R_{load} = \frac{I_c}{V_T} R_{load}$$

.

The non-linear output curves can be rewritten now to the function: