#### MASTER

The real-time EMPS kernel : memory management and suitability for EPEP/PhyDAS

Marissen, R.J.

Award date: 1994

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

## The real-time EMPS kernel: Memory Management and suitability for EPEP/PhyDAS

Rob Marissen

September 14, 1994 N

**NF/FTL 9404**

Technische Universiteit Eindhoven Faculteit Technische Natuurkunde Vakgroep Fysische Informatica

Afstudeerdocent: prof. dr. ir. K.Kopinga Technische begeleiding: ing. L.A.H.M. van Houten

#### Abstract

The EMPS system is a multi-processor system designed for two different application areas, namely (i) real-time data processing and control of physics experiments, and (ii) dependable distributed computing. The hardware of the EMPS system is built around a VME/VSB computer bus and computer modules based on the MC68030 processor. A short description of the EMPS hardware can be found in chapter 1. The emphasis of the rest of the chapters is on the software of the system, which is called the EMPS kernel.

Multi-processor systems require another approach to writing system software than single processor systems do. Chapter 2 deals with the particular multi-processor related parts of the kernel. Also, some more practical problems associated with the multi-tasking properties of the kernel are addressed.

In a system that serves multiple purposes, the system software must be flexible in order to accommodate different needs. One of the parts of the kernel in which this flexibility is expressed, is the handling of memory resources, often referred to as memory management. The MC68030 processor, which is used in the EMPS system, offers hardware support for memory management in the form of a Memory Management Unit (MMU). Extensions that have been added to the memory management in the EMPS kernel, and the use of the MMU are discussed in chapter 3.

The performance and real-time behavior of kernel services is important when the EMPS system is used to control physics experiments. In chapter 4, the results of performance tests are presented. The performance degradation caused by the particular way interrupts are handled in the EMPS kernel, as well as some suggestions for improvements, are also discussed.

In chapter 5, the results of the previous chapters are discussed.

In the appendixes, the kernel functions that can be called from application programs are described. Information about the most important data structures inside the kernel, as well as other relevant data, is also given.

# Contents

| 1 | Int | roduction                                                                  | 4 |

|---|-----|----------------------------------------------------------------------------|---|

|   | 1.1 | EMPS hardware                                                              | 4 |

|   |     | 1.1.1 The VME/VSB bus                                                      | 5 |

|   |     | 1.1.2 The processor module                                                 | 6 |

|   |     | 1.1.3 The memory module                                                    | 8 |

|   |     | 1.1.4 The PhyLAN module                                                    | 8 |

|   |     | 1.1.5 The VME-PhyBUS converter                                             | 9 |

|   | 1.2 | EMPS software                                                              | 9 |

|   | 1.3 | Data processing and experiment control                                     | 9 |

|   |     | 1.3.1 $PhyDAS$                                                             | 9 |

|   |     | <b>1.3.2</b> EPEP                                                          | 0 |

|   | 1.4 | <b>Overview</b>                                                            | 1 |

| 2 | Mu  | lti-processor and multi-tasking aspects 12                                 | 2 |

|   | 2.1 |                                                                            | 2 |

|   |     | 2.1.1 Mailbox communication                                                | 2 |

|   |     | 2.1.2 Process migration                                                    | 3 |

|   | 2.2 | Multi-tasking facilities                                                   | 4 |

|   |     | 2.2.1 Tasks and processes                                                  | 4 |

|   |     | 2.2.2 Supervisor/user mode                                                 | 5 |

|   |     | 2.2.3 Interrupt handling                                                   | 5 |

| 3 | Me  | mory Management 20                                                         | 0 |

|   | 3.1 | Memory allocation                                                          | 0 |

|   |     | 3.1.1 Implementation of memory allocation                                  | 2 |

|   | 3.2 | MMU                                                                        | 3 |

|   |     | 3.2.1 Address translation with the MMU                                     | 3 |

|   |     | 3.2.2 Use of the MMU in the kernel $\ldots \ldots \ldots \ldots \ldots 24$ | 1 |

|   |     | 3.2.3 Process migration and memory management 20                           | 3 |

|   | 3.3 | The MMU of the MC68030                                                     | 3 |

|   |     | <b>3.3.1</b> Table index limits                                            | 3 |

|   |     | <b>3.3.2</b> Descriptor type                                               | 3 |

|   |     | 3.3.3 Supervisor only/Read only protection                                 | ) |

|   | 3.4 | The old memory management                                                  |   |

|   |     | implementation                                                             | ) |

|          | <b>3.5</b>                               | The new memory management                                   |                                        |

|----------|------------------------------------------|-------------------------------------------------------------|----------------------------------------|

|          |                                          | implementation                                              | 31                                     |

|          |                                          | 1                                                           | 31                                     |

|          |                                          | 3.5.2 Dynamic allocation of memory for translation tables . | 33                                     |

|          |                                          | 3.5.3 Early termination page descriptors                    | 33                                     |

|          |                                          | 3.5.4 Protection of memory areas                            | 33                                     |

|          | 3.6                                      | Use of the MMU to divert VME                                | ~ 4                                    |

|          |                                          | memory access to the VSB bus                                | 34                                     |

| 4        | Per                                      | formance tests                                              | 37                                     |

| -        | 4.1                                      |                                                             | 37                                     |

|          | 4.2                                      |                                                             | 38                                     |

|          |                                          |                                                             | 40                                     |

|          | 4.3                                      |                                                             | 41                                     |

|          |                                          |                                                             | 41                                     |

|          |                                          |                                                             | 42                                     |

|          | 4.4                                      | •                                                           | 43                                     |

|          |                                          |                                                             |                                        |

| 5        | Cor                                      | iclusions and suggestions                                   | 45                                     |

| A        | Con                                      | nmand interpreter                                           | 48                                     |

| в        | Мо                                       | mory maps                                                   | 51                                     |

| D        | INTER                                    | nory maps                                                   | 01                                     |

| С        | Init                                     | ialization                                                  | 54                                     |

| D        | Ker                                      | nel services for application programs                       | 56                                     |

|          | D.1                                      | Calling of kernel functions by                              |                                        |

|          |                                          | applications                                                | 56                                     |

|          | D.2                                      |                                                             | 57                                     |

|          | D.3                                      | Mailbox functions                                           | 59                                     |

|          | D.4                                      | Location independent process                                |                                        |

|          |                                          | management routines                                         | 61                                     |

|          |                                          | 6                                                           |                                        |

|          | D.5                                      | Other process related functions                             | 63                                     |

|          | D.5<br>D.6                               | Other process related functions                             | 63<br>63                               |

|          |                                          | Other process related functions                             | 63<br>63<br>65                         |

|          | D.6<br>D.7<br>D.8                        | Other process related functions                             | 63<br>63<br>65<br>67                   |

|          | D.6<br>D.7<br>D.8<br>D.9                 | Other process related functions                             | 63<br>63<br>65<br>67<br>68             |

|          | D.6<br>D.7<br>D.8<br>D.9<br>D.10         | Other process related functions                             | 63<br>63<br>65<br>67<br>68<br>69       |

|          | D.6<br>D.7<br>D.8<br>D.9<br>D.10         | Other process related functions                             | 63<br>63<br>65<br>67<br>68             |

| <b>.</b> | D.6<br>D.7<br>D.8<br>D.9<br>D.10<br>D.11 | Other process related functions                             | 63<br>63<br>65<br>67<br>68<br>69<br>71 |

| E        | D.6<br>D.7<br>D.8<br>D.9<br>D.10<br>D.11 | Other process related functions                             | 63<br>63<br>65<br>67<br>68<br>69       |

| F | Process queues                                     |    |  |  |  |

|---|----------------------------------------------------|----|--|--|--|

| G | Interrupt Service Processes                        | 78 |  |  |  |

|   | G.1 Process priorities                             | 79 |  |  |  |

| Н | Data structures                                    | 80 |  |  |  |

|   | H.1 Process descriptor                             | 80 |  |  |  |

|   | H.2 Task descriptor                                | 83 |  |  |  |

|   | H.3 Common memory vector table                     | 83 |  |  |  |

|   | H.4 Program file header                            |    |  |  |  |

| Ι | Improvements and extensions of the original kernel | 87 |  |  |  |

.

# Chapter 1

## Introduction

The Eindhoven Multi Processor System (EMPS) has been designed at the Eindhoven University of Technology for two different application areas, namely data processing and control of physics experiments, and dependable distributed computing. The EMPS comprises both the hardware and the software of this multi-processor system.

In this chapter, an overview of the EMPS hardware is given, followed by some characteristics of the EMPS software and a section that focuses on the use of the EMPS for control of physics experiments. The development status of the software is also dealt with.

## 1.1 EMPS hardware

Multi-processor systems can be classified by the way information is exchanged between processors. Two types of communication can be distinguished:

- A system in which processors communicate via shared memory: a tightly coupled system.

- A system in which processors can only communicate via other means, e.g. a local area network: a loosely coupled system.

In the EMPS system, both types are combined, thus forming a hierarchy of communication channels. The system consists of *nodes*, which contain a number of processor-, memory-, and other modules. Within each node, shared memory can be used for communication. Communication between nodes uses either a local area network or fast (20 Mbits/s) serial transputer links which reside on each processor module.

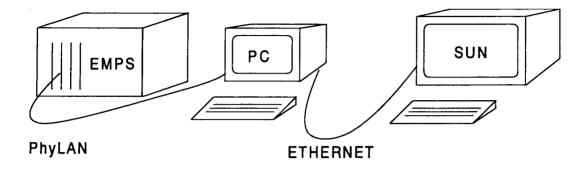

The local area network, which is called PhyLAN, is also used to load the EMPS software when the system is started. The EMPS software and other files are supplied through PhyLAN via a fileserver. In the development stage of the EMPS software the fileserver is a PC, as shown is figure 1.1. Because the actual development of the software is done on a another computer, namely a SUN workstation, the PC in turn is connected to this workstation using

a different local area network, ETHERNET. Hence, the PC is only a link between the SUN workstation and the EMPS system.

Figure 1.1: The EMPS is connected via PhyLAN to its fileserver, a PC. The PC is connected via ETHERNET to a SUN workstation.

#### 1.1.1 The VME/VSB bus

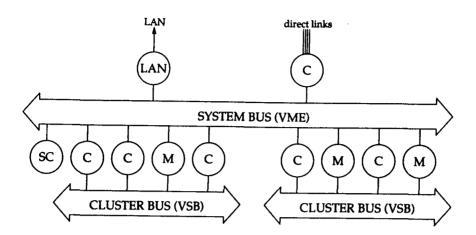

The hardware of the EMPS system is built around a VME/VSB computer bus. The VSB is an extension of the VME bus, but can be considered as an independent bus. Most of the modules that are used in the EMPS system, can be accessed via both the VME bus and the VSB bus. In multi-processor systems the shared bus often forms a bottleneck. The availability of two separate buses helps to avoid this. Processor modules, memory modules, and others are connected to the bus by inserting them in *slots*, of which a maximum of 20 are available in each node.

In figure 1.2 the bus architecture is shown. All modules within one node can be accessed via the VME bus, whereas the VSB bus is split into groups of 5 slots, called *clusters*. The VSB bus can only be used to access modules that belong to the same cluster. The division of a node into clusters further helps to eliminate the occurrence of a communication bottleneck, because access to shared memory within the same cluster using the VSB bus does not occupy the VSB bus of other clusters.

Both the VME and the VSB bus use 32 bits data and addresses. On the VME bus, data and addresses have separate sub-buses, whereas on the VSB bus, data and address lines are time-multiplexed.

Within the bus system, the first slot has a special function: it contains the system controller. The hardware of the system controller is almost the same as that of processor modules, except that it has extra facilities for bus arbitration. The software of the EMPS system is designed in such a way that system bus interrupts are handled exclusively by the system controller.

Figure 1.2: The bus architecture of the EMPS system. The VME bus connects all modules in a node, whereas the VSB bus is split in clusters of 5 slots.

#### 1.1.2 The processor module

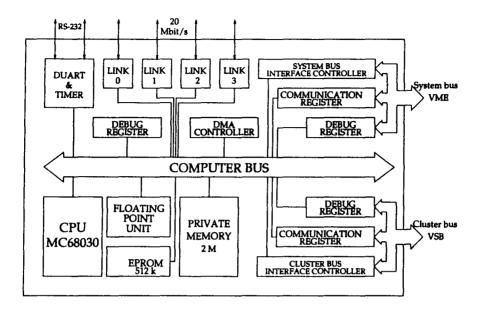

The heart of the processor module on which the EMPS system is based is formed by a Motorola MC68030 processor, that is upward object code compatible with the MC68000. Some of the features of the MC68030 are an on-chip memory management unit, data- and instruction caches, 32 bits data- and address buses, and 16 general purpose registers. The processor is clocked at 33 MHz and can be extended with a MC68882 floating point co-processor. Figure 1.3 shows a block diagram of the computer module.

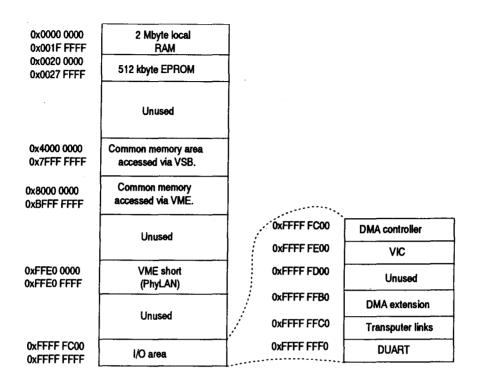

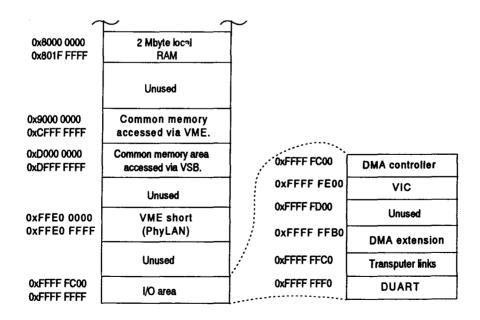

Each processor module is equipped with 2 Mbyte static RAM and 512 kb EPROM. These memories are local to the processor module, and cannot be accessed by other modules. The RAM, also referred to as *private memory*, is used in applications that make extensive use of memory, e.g. program code. A monitor program is stored in the EPROM. At system start up, the monitor program is executed, and copies itself to the local RAM memory for faster access. The monitor program is used to download programs, i.e. the EMPS kernel, via the local area network.

A Dual Universal Asynchronous Receiver/Transmitter (DUART) provides two RS232 serial connections, e.g. for terminals. A programmable timer is also available; it is used to periodically generate interrupts at 20 ms intervals.

Transputer links offer a means for fast communication. Every processor module has four transputer links that transfer data at 20 Mbit/s each. The links can be used for communication between processors in the EMPS system,

Figure 1.3: A block diagram of the processor module.

but are also used for fast transfer of data obtained from physics experiments from a computer module to a PC.

The processor modules in the EMPS system are equipped with a special facility for efficient communication between processors within a node in the form of *communication registers*. Communication in tightly coupled multiprocessor system is often done by writing a message into shared memory, and generating an interrupt at the target processor to attract its attention. The VME bus offers 7 interrupts for all modules together, which is insufficient to use this method efficiently. Communication registers offer a more efficient way of generating an interrupt at another processor, while simultaneously exchanging some information. The communication register of one processor can directly be written by another processor, by writing to a specific memory location. An interrupt is automatically generated at the target processor, which then can read the communication register. Thus, the generation of an interrupt at another processor module has a separate communication register for the VME and the VSB bus, respectively.

The address at which a communication register can be reached, depends on the slot of the processor module. The slot number is derived from the place within a cluster, which is obtained from geographical address signals supplied by the bus, and from the setting of two jumpers on the module, which are set to the number of the cluster. In appendix B, the address of the VME communication register is listed for each slot number.

#### 1.1.3 The memory module

The memory modules used in the EMPS system can contain 4 Mbyte to 64 Mbyte DRAM. Memory can be accessed via both the VME and the VSB bus, with cycle times of 500 ns and 600 ns, respectively. The memory modules can be accessed by all processors within one node and will be used, among others, as the shared memory that is used for communication between processors. It will also be referred to as *common memory*.

Access arbitration is arranged in 3 priorities: refresh cycles, which have the highest priority, VME memory accesses, which are handled when no refresh is pending, and VSB memory accesses, which have the lowest priority. Thus, if a memory module is accessed at the same time via the VME and VSB bus, VME access is handled first. This does not have a serious impact on the speed of VSB accesses, because the access time of the DRAM memory on the module is much smaller than the cycle time of the VME and VSB buses. A VSB memory access may therefore be started before the VME access cycle is completed, so that the accesses overlap.

Both the VME and the VSB buses support uninterrupted read-modifywrite cycles, which are useful for some multi-processor functions, e.g. semaphore handling.

The address space of the memory module is determined by the slot in which the module is placed. The slot number is obtained in the same way as for the processor module. In appendix B the addresses of memory modules as a function of the slot number are listed. Whether a memory module is accessed via the VME bus or via the VSB bus, is determined by the address that is used.

#### 1.1.4 The PhyLAN module

Each node in the EMPS system is equipped with a local area network controller that is used for communication with other computer systems. The local area network, which is called PhyLAN, has a transmission rate of 2.5 Mbit/s. The PhyLAN module has an on-board DMA controller to support fast data transfer to VME/VSB memory modules. Direct data transfer to the local memory of the computer modules is not possible, because this memory cannot be accessed via the VME/VSB bus.

In the future, a different networking capability will be added to the system in the form of an ETHERNET module.

#### 1.1.5 The VME-PhyBUS converter

PhyBUS is the bus system of interface modules that are used to control physics experiments. The VME-PhyBUS converter forms the connection between the VME bus and the PhyBUS. This module contains a DMA controller for fast data transfer between the PhyBUS and the VME bus, and some logic to convert the 32 bit PhyBUS signals to variable size (8/16/32 bit) VME bus signals.

## **1.2** EMPS software

The system software of the EMPS, also called the EMPS kernel [dij 93], was designed to perform the basic functions needed by both the Department of Physics and the Department of Mathematics and Computer Science. These include multi-tasking facilities, interrupt handling, semaphores, and memory management, which are also present in single-processor kernels.

Support for multi-processor applications is given in the form of location transparent exchange of information between processes using mailboxes, and process migration. Facilities offered by the kernel are available uniformly at all processor modules in the EMPS system, since the program code of the kernel is exactly the same at all processors. However, access to specific objects is in some cases limited to one processor module, or to processors within one node (e.g. semaphores, memory).

For efficiency reasons, the EMPS kernel has been implemented in the C programming language. The kernel is developed using an Oasys cross compiler [oas 93] running on a SUN workstation.

## **1.3** Data processing and experiment control

At the time cheap computers first became available, increased use of computers in control of physics experiments resulted in a fast expansion of the different types of interfaces that were being developed for this purpose. It was realized that, in order to limit this growing number of different hardware designs, some form of standardization was required. Within the Department of Physics this has lead to the development of a general purpose Physics Data Acquisition System (PhyDAS).

#### 1.3.1 PhyDAS

PhyDAS is the name of the system that was developed to control physics experiments and to acquire experimental data. It consists of a number of data-acquisition and control interfaces, which are connected with an asynchronous bus system, called the PhyBUS. The PhyBUS is connected to a computer system that controls the interfaces, and that can have a different bus system. Since the life cycle of computers is generally much shorter than the life cycle of the interface modules, separating the interface bus from the computer bus enables cost-efficient upgrading to a new computer generation.

The PhyDAS concept was developed around 1979 and has since been used with three different computer generations: first DEC PDP11, followed by a system based on the Motorola 68000 processor, which is called the Micro-Giant, and more recently, the EMPS system. Currently, only the hardware part of the EMPS system is used to control the PhyDAS hardware. The software of the EMPS is still in development and will later be incorporated in the system. At this moment, the software that is used to control the PhyDAS interfaces is an "all in one" program, called EPEP.

#### 1.3.2 EPEP

The system software that is used for the control of physics experiments, is an interpreter type of programming language, called EPEP (Eindhoven Program Editor and Processor). This language provides special features for process control in the form of a multi-tasking capability with event driven process switching. Furthermore, processes can have different priorities, reflecting the urgency of each process. EPEP has a command interpreter that can be used interactively while processes are being executed, which is useful for accessing data and parameters of an experiment that has already started, i.e. runs under program control.

The version of EPEP that is currently used in the Department of Physics is not only an interpreter, but also comprises the underlying operating system plus a program editor. All these functions are integrated in one program. Because EPEP was developed at a time that efficient use of computer resources was still a factor of primary importance, this program has been written in assembly language.

Because of the ongoing development of micro electronics, efficient use of resources, especially memory, has become less important. Maintainability and portability, on the other hand, are now factors of increased consideration. Therefore, the three functions of EPEP, (interpreter, editor, and operating system) will be split in separate parts, which are implemented in a higher, portable programming language, namely C.

One of main the goals of the EMPS kernel is to provide the basic functionality upon which the EPEP interpreter and editor will be built. This is reflected in the services offered by the kernel, which include the capabilities of the operating system part of EPEP, for instance multi-tasking with event driven process switching, different process priorities, and semaphores.

## 1.4 Overview

Low level multi-tasking facilities form the basis for all other kernel functions, including multi-processor services. Chapter 2 includes a description of multi-tasking concepts which are specific for the EMPS kernel. The multi-processor services that are concerned with handling interrupts are also described.

The original version of the EMPS kernel has a property that limits its usefulness: hard limits are placed on the amount of memory that can be used by application programs, because fixed-size data structures are used in memory management routines. To make memory management more flexible, this part of the kernel has been rewritten. In chapter 3, the memory management of the kernel is described.

The performance and real-time behavior of kernel routines is important when the EMPS system is used to control physics experiments. The results of performance tests are presented in chapter 4. Special attention is given to the performance degradation that is caused by interrupts, which are handled by dedicated Interrupt Service Processes in the EMPS kernel.

The results of the previous chapters are discussed in chapter 5.

Documentation about the original kernel was only available from an object oriented description and from sources code. From these sources, information that is important for extensions of the kernel, plus a description of kernel services that can be used in application programs has been gathered. This information is presented in the appendices.

## Chapter 2

# Multi-processor and multi-tasking aspects

A property of the EMPS system is its non-homogeneous communication topology, which is supported by kernel services. If processors are located in the same node, shared memory is used for communication, otherwise the PhyLAN is used. Which communication path is used, is transparent for application programs that use kernel services developed for this purpose. However, some other kernel services are not available transparently in different nodes, e.g. semaphores, can only be used within the same node. When the kernel is used as a basis for EPEP, it is not expected that more that one node will be needed in the near future. The description of multi-processor functions will therefore be limited to services that work within one node.

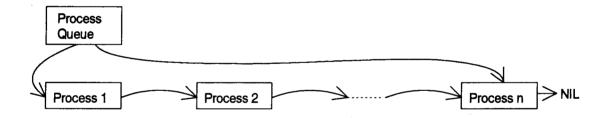

The basis of the EMPS kernel is formed by a set of low level functions that offer multi-tasking facilities. Interrupt driven task switching is one of these facilities. The handling of interrupts, which is done by dedicated processes, is described in section 2.2.

## 2.1 Multi-processor services

Mailbox communication and process migration are the services that make the kernel a multi-processor kernel. Mailbox communication offers communication between processes without the need that processes keep track of each others locations. Process migration provides the possibility to transfer a process between processors in a distributed system. It supports efficient use of computing resources, because the processing load can be balanced evenly over all processors in the system.

#### 2.1.1 Mailbox communication

Location transparent communication is one of the goals of the EMPS kernel. It is achieved by using mailboxes, which allow transparent communication between processes, even if a process has been migrated to another processor. When mailbox communication is used, processes send information to a mailbox instead of to another process. The kernel, which handles the mailbox, routes the information to its destination.

Setting up a communication path between processes using mailboxes consists of 2 steps:

- 1. Creating a mailbox. The mailbox data structure that is created, is used by the kernel to keep track of processes that are communicating. Only one mailbox must be created for all processes that communicate via that mailbox.

- 2. Attaching a process to a mailbox. This is done by connecting a data structure of type *PORT* to the mailbox. *PORT* is used by the process to communicate via the mailbox. Each process that communicates via a mailbox must connect a port to that mailbox.

Processes connected to the same mailbox can communicate by issuing send- or receive commands to the port through which they are attached to that mailbox.

Mailbox communication is location transparent, because processes send and receive information via the mailbox and have no knowledge of the location of the process with which they communicate. The actual process locations are stored in the mailbox data structure, and are updated by the kernel when a process migrates.

Mailboxes provide both a unicast service (send and receive primitives) and a Remote Procedure Call (RPC) service (send request, receive request and send reply primitives). When a process attaches to a mailbox, the port type determines whether the unicast service or the RPC service is provided. Details about the port types are included in appendix D.

The kernel also includes unicast and RPC services that are not location transparent. These services are completely separate from the mailbox services and are used internally in the kernel. They provide the same functionality as the mailbox services, but in a location dependent way.

The mailbox operations are very similar to the file I/O operations in the C language.

#### 2.1.2 Process migration

Processes in the EMPS system can be migrated to another processor transparently, i.e. without any changes to their computation or communication. Process migration can be used to balance the processing load over all processor modules in the system.

Process migration is handled by migration server processes that are present at each processor in the EMPS system. To initiate migration, a message is sent to the migration server process at the processor where the process that must be migrated is present. This message contains an identification of the process that will be migrated, plus the destination of this process. The migration request can be sent by any process on the system.

The migration server at the source processor detaches the process from its environment by removing it from the queue it is in and by locking the mailboxes to which it is connected. Next, it gathers all process information, e.g. process state, processor registers, code-, data-, and stack memory, and sends this to the migration server at the destination processor. The process is then removed from the source processor.

At the destination processor, a new process is created using the process information obtained from the source processor, and mailbox connections are redirected to the new process. The new process is then restarted.

A process can only be migrated if it meets the following demands:

- The process only communicates via mailboxes. Most services of the kernel are provided by server processes which can be reached via a mailbox, and can therefore be used by a process that is migrated.

- No dynamically allocated heap memory is used. Migration of heap memory is not supported.

Use of the EMPS process migration facility is less appropriate for load balancing within the EPEP interpreter. In EPEP, a process consists of EPEP instructions that are interpreted, whereas an EMPS process consists of MC68030 instructions. Some sort of mapping is needed such that a EPEP process corresponds to an EMPS process. In practical terms, this means that the interpreter will be an EMPS process that interprets EPEP instructions. When a new EPEP process is created, this will cause the creation of a new EMPS process, that again interprets EPEP instructions. If an EMPS process is created, only a reference to the program code, data, and heap is made. However, if a process is migrated, a copy of the code and data is made. This is undesirable, because it can cause multiple copies of the same code and data to be present on one processor if the process that has been migrated was part of a task including more processes. Also, within EPEP information is exchanged between processes through the memory they share. When the EMPS process migration facility is used, this is no longer possible.

## 2.2 Multi-tasking facilities

#### 2.2.1 Tasks and processes

Programs that run on top of the kernel, such as EPEP, are called application programs or tasks. Within one task, several related processes can be defined.

The memory space for program code, data and heap are shared between all processes in one task. Each process within a task has its own stack memory.

#### 2.2.2 Supervisor/user mode

The MC68030 processor supports protection of system facilities by offering two modes for program execution: the supervisor mode, which allows access to all facilities, and the user mode, which limits access. Each mode has its own stack pointer. In user mode, execution of certain instructions is prohibited and memory access can be limited to specific areas by using the MMU (chapter 3).

For some kernel functions, execution in supervisor mode is required. Switching between user mode and supervisor mode is a time consuming operation, because of the rather complicated passing of parameters between user mode and supervisor mode routines. Therefore, the whole kernel, including all system processes, execute in supervisor mode.

Application programs should not access privileged facilities, and execute in user mode. A switch from user mode to supervisor mode is made when a kernel routine is called. Parameters for this routine are put on the user stack, and must be copied to the supervisor stack before the kernel routine is invoked. The way a kernel function is called from an application program is described in appendix D.

#### 2.2.3 Interrupt handling

Interrupts are generated by hardware devices to indicate that an event has occurred, e.g. a character was received from the terminal. For some hardware devices, the interrupt can have multiple causes. The DUART for example, contains a clock, 2 serial outputs, and 2 serial inputs, each of which can cause an interrupt. One physical interrupt source may thus be associated with several logical interrupts, each of which is associated with a logical device.

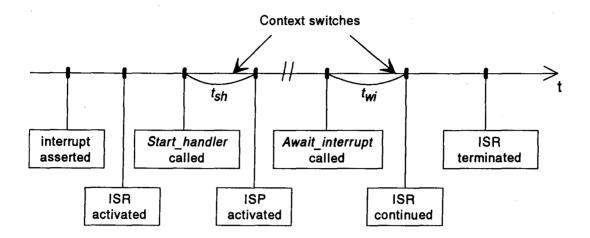

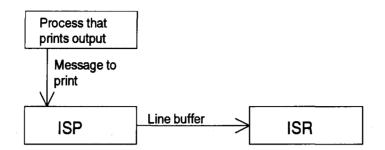

When an interrupt is activated, this leads to the starting of an Interrupt Service Routine (ISR). Each physical interrupt source has its own ISR. In the EMPS kernel, the ISR does not handle the interrupt itself. Instead, logical interrupts are handled by dedicated processes, called Interrupt Service Processes (ISPs). The ISR determines which logical device is the cause of the interrupt, and unblocks the ISP that corresponds to it.

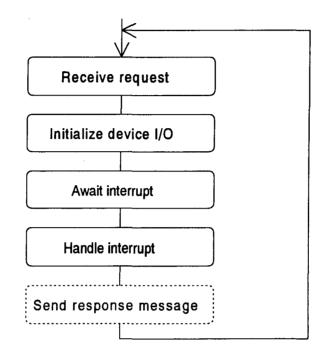

The main reason for using ISPs to handle interrupts is that this offers location independent access to devices. A process that wants to perform an I/O operation sends a request message to the ISP that handles the device. Because messages can be sent to processes at any location in the system, location independence is achieved. A typical ISP consists of an infinite loop, in which it waits for a request message, initializes the I/O device, waits for the interrupt that signals I/O completion, and handles the interrupts. When the ISP is associated with an input device, it sends a response message. An example of such an ISP is shown in figure 2.1.

Figure 2.1: A typical ISP consists of an infinite loop in which I/O related actions are performed.

Apart from location independent device access, handling of interrupts by ISPs has the following advantages:

- Mutual exclusion: Mutual exclusion between processes that perform I/O operations on the same device is achieved automatically, because there is only one ISP that physically accesses the device.

- Minimal stack use for handling interrupts: Interrupts are handled on the supervisor stack of the currently executing process. When an ISR would handle device interrupts, sufficient stack memory would have to be allocated to each process to handle nested interrupts from all devices. Interrupt handling can involve calling of other routines which use the stack to store local variables. By using ISPs that handle interrupts, these routines use the stack memory of an ISP, so that stack use by ISRs is minimized.

We like to note that for the MC68030 processor, this argument is not completely valid, because it has the possibility of using a separate stack pointer for interrupt processing. By using this interrupt stack pointer, reserving extra stack memory in all processes is not necessary.

• Buffered interrupts: Access to some internal data structures in the kernel must not be shared by processes. Shielding these data structures with semaphores is not always possible (e.g. semaphore data structures cannot be shielded by semaphores). Therefore, interrupt driven task switching must be disabled during access to these data structures. If this is done by disabling interrupts completely, interrupts may be lost. With ISPs, activation of the ISP is postponed until access to the data structure is permitted. If an interrupt occurs while activation of the ISP is postponed, the I/O registers of the device that corresponds to the interrupt are stored in a buffer.

There are also some disadvantages in using ISPs:

- Performance loss: For every interrupt, a context switch is needed to activate the ISP. When the interrupt handling is completed, another context switch is needed to continue execution of a regular process. Some overhead is also created by the kernel routine that unblocks the ISP after an interrupt has occurred, and by the routine that blocks the ISP when interrupt handling is completed. In chapter 4, the performance loss is discussed.

- Increased interrupt latency: The context switch and other processing that occurs before the ISP is activated, increase the time between assertion of the interrupt and handling of the device.

Interrupt service processes always have a higher priority than other processes, and therefore they should only be used to perform actions that are directly related to the interrupt. Any subsequent actions, e.g. the numerical processing of data from the device, must be done by activating another process (e.g. by sending a message to a process or by signaling a semaphore).

Each logical device is associated with a data structure of type *DEVICE*, which contains information concerning the device, i.e. which ISP handles the device interrupts, an optional timeout routine, and the number of times that the device interrupt has occurred.

The following logical devices are connected with an interrupt service process:

• Clock: the clock ISP is activated at 20 ms intervals, and is used to start timeout routines and to restart processes that are waiting for a specified amount of time. The clock can also be used to divide the processor time over the processes which are ready to execute, by rotating the queue of these processes. This is called time slicing. Time slicing may not always be desirable, and therefore the corresponding program code for time slicing is compiled conditionally. Compilation of the program code for time slicing is enabled with a **#define TIME\_SLICE** statement.

- **Terminal input:** the terminal input ISP is activated when a character is received from the terminal.

- Terminal output: the terminal output ISP is only activated when two conditions are met: the DUART must be ready to send a character, and output must be available.

- Communication register: the communication register ISP is activated when another processor has written a message into the communication register of the processor module. It is used in communication between processors.

- PhyLAN I/O: the PhyLAN ISP is used to service the PhyLAN module. This interrupt is handled by the system controller (processor in slot 0).

- Link input: the link input ISP is activated when data was received via a transputer link on the processor module.

- Link output: the link output ISP is activated when sending data via a transputer link is completed.

- **PhyBUS interrupt:** contrary to the other interrupts, the PhyBUS interrupt cannot be handled completely within the kernel.

The PhyBUS interrupt is a VME bus interrupt, which is generated by the VME-PhyBUS converter when one of the interfaces connected to the PhyBUS signals an interrupt. There can be a maximum of 16 interfaces acting as an interrupt source on the PhyBUS. Which interface caused the interrupt, is determined by the ISP that handles the PhyBUS interrupt.

The configuration of the PhyBUS interfaces depends on the experiment for which they are used, and therefore the PhyBUS interrupt cannot be handled any further inside the kernel. This PhyBUS interrupt must somehow be handled by the software which controls the experiment, which will be an EPEP program. To activate a process that handles the PhyBUS interface which caused the interrupt, semaphores are used. For each of the 16 possible PhyBUS interrupt sources, a separate semaphore exists. When a PhyBUS interrupt occurs, the ISP performs a signal operation on the semaphore that corresponds to the so-called interrupt bit of the interface from which the interrupt originates. The 16 PhyBUS semaphores are named PhyBUS 0 through PhyBUS 15.

Because the PhyBUS related program code is only needed when the EMPS system is used to control the PhyBUS, it has been made optional. At compile time of the kernel, generation of the extra code for the PhyBUS can be enabled with a **#define** PHYBUS statement.

# Chapter 3

## Memory Management

One of the primary functions of every operating system is handling memory resources, which is called memory management. In the EMPS system this consists of two parts:

- Maintaining a list of memory locations that are occupied.

- Protection of memory areas, and separation of (logical) addresses used in programs from the (physical) addresses that are used to access hardware. This is done by using the MMU (Memory Management Unit) of the MC68030 processor.

These two parts are largely independent.

In many operating systems, memory management allows programs to access more memory than is physically available. This can be achieved on computer systems that contain an MMU, by mapping memory areas to secondary (disk) storage, and is completely transparent for application programs. In the EMPS kernel this technique is not used, because the delay caused by swapping memory areas to secondary storage is not compatible with the real-time requirements of the kernel.

### **3.1** Memory allocation

In any computer system that can have more than one program in memory simultaneously, the use of memory by each program must somehow be administered to avoid that different programs use the same memory area. This administration is one of the tasks of the kernel. To this end, it must keep information about occupied and free memory areas, which is only possible if a program invokes a kernel routine when it needs memory.

When a program needs a specified amount of memory, it issues a call to the kernel (e.g. in the C language the function *malloc* is used). The kernel then checks whether the required amount of memory is available and, if so, it registers the memory area as occupied and returns the start address of the area. If there is not sufficient free memory, some sort of error condition is signaled. When the program no longer needs the memory, it issues another kernel call (in C, the function *free* is called) so that the memory can be added to the free area.

In the EMPS system, memory is divided into blocks of a fixed size, called the pagesize. The size of a memory area that is allocated is always an integer multiple of the pagesize. The reason for splitting memory into pages originates from the hardware of the MMU, which will be discussed in the following sections. In the current kernel version, the pagesize is 1 kbyte.

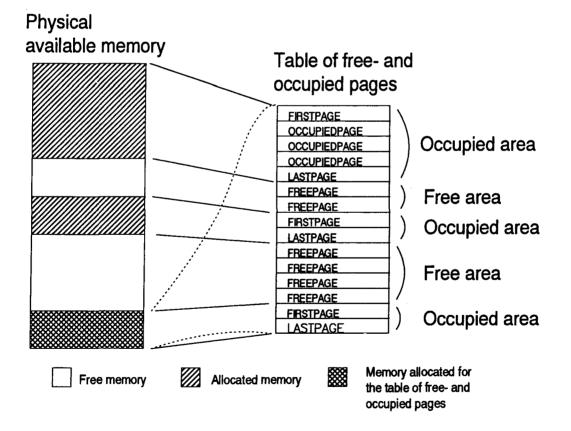

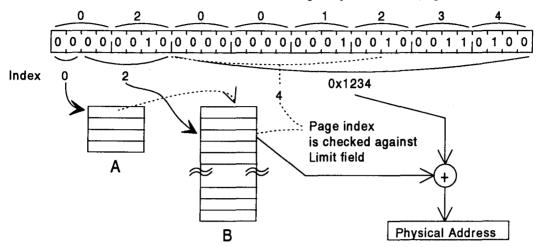

To register free and occupied pages, the EMPS kernel uses an array of bytes, which will be referred to as the allocation table. The index of an element of this array is equal to the number of the memory page that corresponds to it. A byte in the allocation table contains the value FREEPAGE if the corresponding page is free. If a page is occupied, it contains the value OCCUPIEDPAGE, FIRSTPAGE or LASTPAGE. An example of the allocation table is shown in figure 3.1.

Figure 3.1: A list of free- and occupied pages is used for memory allocation. The list is located at the end of the memory area to which it belongs.

The lowest level memory allocation routine takes a parameter which contains the number of contiguous pages that is required. When memory must be allocated, the allocation table is searched for the requested number of contiguous free pages. The array is then modified to indicate that memory is occupied.

The method of memory allocation that is employed in the EMPS system is not used in most other systems, because searching an array for a number of contiguous pages is a slow operation. Several other ways of keeping track of memory use are described in [tan 87]. The most commonly used algorithms maintain a linked list of allocated and free memory areas, respectively. An advantage of such a method is that searching for a free memory area is faster. A drawback is that the size of the linked lists changes when memory is allocated, whereas the size of the allocation table always remains the same. A variable list size is more difficult to implement. When the EMPS system is used in control of physics experiments, the speed of memory allocation operations is not an important factor, because memory allocation will not be performed in time-critical program sections.

We like to note that other methods of memory allocation can be implemented in the EMPS kernel relatively easy, since the allocation part of the kernel is completely separated from the other memory management functions.

#### **3.1.1** Implementation of memory allocation

The basic routines that the kernel has to supply are the allocation of a memory area, and the release of a previously allocated area. In the EMPS kernel, this is done by the low level functions reserve\_contiguous\_pages and release\_contiguous\_pages.

The memory space in the EMPS system consists of different areas: private memory, which is the on board memory of the processor module, and one or more common memory areas from memory modules. In general, memory areas from different memory modules are not contiguous; a gap of unused addresses exists between these areas.

For each contiguous memory area, a separate allocation table is maintained. The position of the table is always at the end of the memory area to which it belongs, as can be seen in figure 3.1.

Because multiple processes may be allocating or releasing memory, mutual exclusion is required. This would suggest using semaphores to shield access to the allocation table. However, memory used to store semaphore data structures is allocated dynamically in the initialization phase of the kernel, which means that the allocation table is accessed before semaphores can be used. To avoid the circular problem that results from this, the allocation algorithm should be made such that semaphores are only used for shielding of the table after the initialization of the semaphores. In the EMPS kernel, no semaphores are used, but instead context switching is disabled when the allocation table is accessed. This is done by disabling the context switch for interrupt handling by ISPs, as explained in section 2.2.3. When the allocation table for common memory is accessed, disabling interrupts is not sufficient, because the table is shared between all processors. In this case the TAS (Test And Set) instruction of the MC68030 is used to test a busy flag: a processor that wants to access the table performs TAS instructions on the flag until the allocation table is available. When the allocation table becomes available, the flag is cleared. The TAS instruction cannot be interrupted by another processor.

## **3.2** MMU

Most modern microprocessors, including the MC68030, provide an MMU that can be used to support multi-tasking facilities and to make the software independent of the memory locations in hardware. The MMU translates a virtual (also called logical) address used by the software into a physical address which is used to access the hardware. In this section, the function of an MMU in general is described. Details of the MMU in the MC68030 processor and the way it is used in the kernel can be found in the subsequent sections.

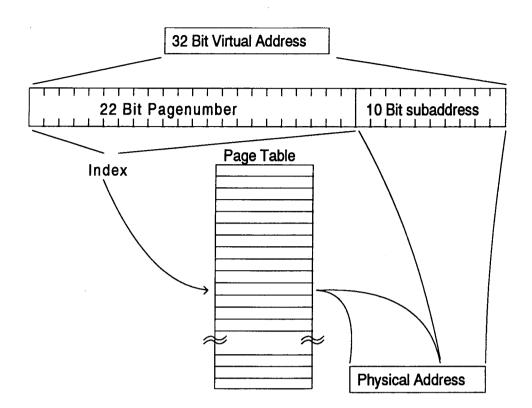

#### **3.2.1** Address translation with the MMU

Translation of a virtual address into a physical address is the most basic function of an MMU. In the translation process, not all bits of the virtual address are used. Instead, the memory space is divided into pages, as is shown in figure 3.2. A page is the smallest block of memory for which a translation can be made. An address is split in a page number plus a subaddress within the page. The page number is translated through the MMU page table, whereas the subaddress within the page is the same for the virtual- and the physical address.

In the example of figure 3.2, the pagesize is 1 kbyte, so 10 bits are used as a subaddress within the page. There are 32 address bits, so 22 bits are used to define the page number, giving  $2^{22} = 4194304$  possible page numbers. If this example would represent reality, a table would be needed with a size equal to the number of pages. Clearly, such a large table is not economical. Therefore, MMUs always have a way to limit the translation table size that is required.

The translation table can be built in such a way that more than one virtual address translates to the same physical address, because different table entries can point to the same physical page.

Figure 3.2: The MMU uses a table to translate virtual addresses into physical addresses.

Apart from translating addresses, an MMU can be used to protect memory areas from illegal access. For instance, it is possible to define a page to be read only, so that a write operation to a address within that page produces an exception which can be handled by the system software.

#### **3.2.2** Use of the MMU in the kernel

The reasons for using the MMU in the EMPS system are:

- Efficiency of application programs. Every time an application program is loaded, it has the same virtual memory map, so absolute addressing can be used in the program code of the application. This is more efficient than position independent program code.

- Protection. The MMU can be used to prevent application programs from overwriting the address space of other programs.

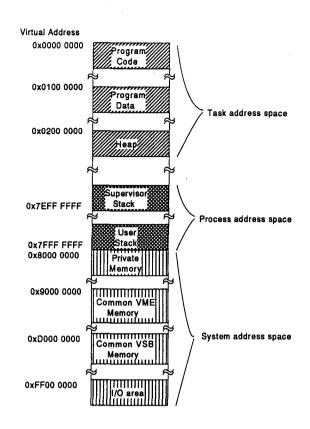

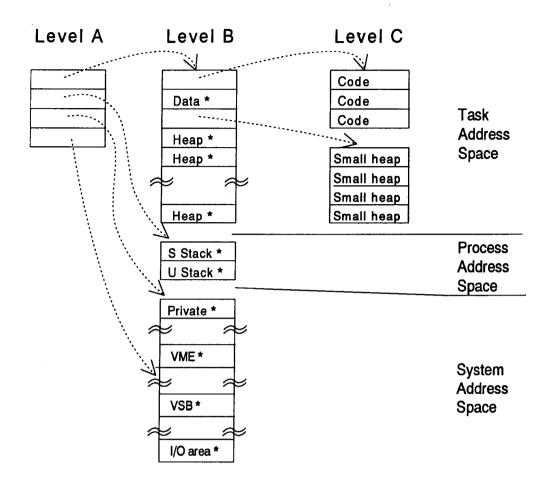

In the EMPS system, a virtual memory map is created for each process. The memory map, which is shown in figure 3.3, consists of three parts:

Figure 3.3: A virtual memory map is created for each process. The process address space is owned by the process, whereas the task address space is shared by all processes in a task, and the system address space is shared by all processes on a processor.

1. The system address space. This is the part of the memory that is shared between all processes running on one processor. In the system address space, all memory locations, plus all memory mapped I/O locations, can be reached. The program code and the data structures of the kernel are situated in this part of the virtual memory. In the kernel, it is necessary to emulate some MMU actions in software. For efficiency of this emulation, it is essential that a simple relation between a physical memory address and the corresponding system address exists. Therefore, the virtual memory map is created in such a way that the system address and the physical address differ by a constant offset.

In the current kernel version, all processes have full access to most of the system address space. However, shielding of the system address space against write access by application programs is desirable. Protection of memory areas is discussed in section 3.5.4.

- 2. The task address space. A task consists of one or more related processes. The memory areas that are shared between all processes within a task are the code, data, and heap, which together form the task address space.

- 3. The process address space. Each process in a task has its own stack memory. A separate stack exists for user- and supervisor mode.

#### 3.2.3 Process migration and memory management

Multiple processes within one task can use the data area of the task to exchange information. When one process in a task is migrated to another processor, this is no longer possible: the data area of the migrated process has become disjunct from the original data area.

Allowing only migration of processes that do not share the code, data, and heap areas with other processes (i.e. single process tasks) can solve this problem, but this limits migration possibilities. Instead, it is assumed that processes that are migrated only communicate via mailboxes. At the destination processor, a new task is created that contains a copy of the code, data, and stack areas. As mentioned in chapter 2, migration of heap memory is not supported. The migrated process is the only process that exists within the newly created task.

After a process has migrated, the stack memory that was used by the process at the source processor is released. If the migrated process was the only process in the task at the source processor, memory in the task address space (code and data areas) is also released.

### 3.3 The MMU of the MC68030

The MC68030 processor contains a very flexible Memory Management Unit [mot 90], which has many features that are not relevant for the kernel. Only the functional part of the MMU that is used will be described here.

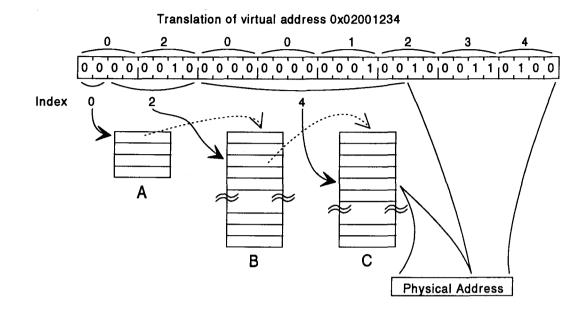

For address translation, the MMU uses a set of tables that are organized in a tree structure: the Translation Table Tree. The tree is stored in the private memory of the processor module. An entry of the table is called a *descriptor*. In the kernel, the tree has 3 levels. The actual address translation can best be explained with an example.

Figure 3.4 shows how the virtual address 0x02001234 is translated using the translation table tree. In each level of the tree, a number of bits of the virtual address is used as an index for a table. In figure 3.4, the 2 most significant bits of the virtual address are used as an index of the table of the first level (A). Since both bits are 0, the first entry of this table is

Figure 3.4: A 3-level translation tree is used for address translation. In the first and second level, the table entries each point to a new table. In the last level, the table entries point to the physical page address.

selected. The descriptor in this table entry contains the start address of the next table. Note that 4 of such tables can be selected. For the index of the selected second table (B), 6 bits (bit 24-29 of the virtual address) are used in this example. This bit field contains the number 2, so the start address of the table of the third level is obtained from entry 2. In principle  $4 \times 64$  of such tables can be selected. The index of the selected table of this (last) level (C) of the translation tree is obtained from 14 address bits (bit 10-23 of the virtual address), which contain a 4. This table contains the physical page addresses, so in this example the address of the page is found in the table at position 4. The remaining address bits (bit 0-9) are the subaddress within the page, and are not used in the address translation. These address bits are the same for the virtual and physical address.

The start address of the first table in the tree is stored in an MMU register. The virtual memory map that is used, can be changed by making this MMU register point to another translation tree. This happens in the kernel when a context switch occurs, so each process has its own virtual memory map.

In the example of figure 3.4, bit fields of sizes 2, 6, and 14 were used to obtain an index of a table of level A, B, and C, respectively. The number of bits that are used for each index can be programmed when the MMU is initialized. When the MMU is initialized by the kernel, the sizes of the bit fields comply with the example.

The address translation process outlined above requires 3 accesses to tables in the translation tree for every address translation. If this tree search would be performed for each memory access, a lot of overhead would be caused by reading the tables. Therefore, the MMU contains an Address Translation Cache (ATC), which keeps the results of the last 22 address translations. When a memory address is used for which the translation is present in the ATC, no tree search is needed.

The descriptors in a translation table not only supply either the address of the next level table or the physical page address, but also contain other information items that are used in the translations process. The items that are used by the kernel are described next.

#### **3.3.1** Table index limits

In section 3.2, it was mentioned that the table used for translation of virtual addresses into physical addresses could become unacceptably large. The fact that a tree of tables is used for address translation does not solve this problem: if the whole tree with all its branches would be present, the total number of table entries in the last level of the tree would be equal to the number of pages.

To reduce the size of each table in the tree, a limit can be placed on the index that is used for accessing the tree. Imposing a limit on the size of a table in the first or the second level of the tree means that the number of tables in the next level is also reduced. For this purpose, a *limit* field is present in every descriptor in the translation table. The limit field contains the extreme value that will be accepted as an index of the next level table in the tree. An index that falls outside the range of allowed values causes an exception which can be handled by the kernel.

The limit that is imposed on the index, can be either a lower limit or an upper limit. If it is a lower limit, the index of the next table level must be greater than or equal to the value in the limit field. If it is an upper limit, the index value must be less than or equal to the limit. Whether the limit is a lower or an upper limit, is determined by the L/U bit in the descriptor.

#### **3.3.2** Descriptor type

From the description of the address translation process, it is clear that not all descriptors are the same: the descriptors in the first two levels of the translation tree contain the start address of the next table, whereas in the last level, the descriptors contain the physical page address which results from the translation. In the kernel, 3 types of descriptors are used:

Translation of virtual address 0x02001234 using early termination page descriptors

Figure 3.5: An example of a translation tree which contains early termination page decriptors. The last level of the tree is omitted.

- 1. INVALID DESCRIPTOR. When an invalid descriptor is encountered in the translation tree, an exception occurs. Invalid descriptors are used if the virtual memory map contains gaps for which no translation is available.

- 2. TABLE DESCRIPTOR. In the first two levels of the translation tree, the descriptors normally contain the address of another table. In that case, the descriptors are called table descriptors.

- 3. PAGE DESCRIPTOR. The last level of the tree contains descriptors that corresponds to the page address which results from the address translation and are called page descriptors.

When a page descriptor is encountered, the physical page address is obtained from the descriptor. The use of the page descriptor type is not restricted to the last level of the translation tree. It can also be used in the first two levels. If a descriptor in the first two levels of the translation tree is marked as a page descriptor, it is called an *early termination page descriptor*, because the tree search is terminated when this descriptor is found.

Early termination page descriptors are used for the translation of a contiguous range of pages. The limit field of an early termination page descriptor is used to check the index of the page, similar to table descriptors. In normal page descriptors, the limit field is ignored. An example of a translation tree in which an early termination page descriptor is used, is shown in figure 3.5. The use of early termination page descriptors reduces the total number of descriptors in the translation tree, because such a descriptor replaces multiple normal page descriptors. Early termination page descriptors can only be used for a range of pages that are physically contiguous. Normal page descriptors provide a separate translation for each page, so that pages that are contiguous in the virtual memory map, do not have to be physically contiguous.

#### 3.3.3 Supervisor only/Read only protection

The MMU offers protection of memory areas against illegal accesses. Memory areas can be protected against access in the user mode of the processor by setting the S bit in the descriptor, and against overwriting by setting the WP bit in a descriptor. If during the table search a descriptor is encountered in which the S bit or the WP bit does not comply with the access mode, an exception occurs.

# 3.4 The old memory management implementation

One of the reasons for using the MMU is to allow application programs to use absolute addressing. Therefore, the MMU address translation must be created in such a way that the virtual memory map of a process is always the same, independent of its physical memory location.

As described in the previous section, the address space of an application process basically consists of five areas: the code area, the static data area, the heap, the user stack and the supervisor stack. Each of these areas has its own MMU tables for address translation.

In the original version of the EMPS kernel, the MMU translation tables are stored in static array variables, and as a result they have the same size for every process. The arrays contain 64 entries for the code, 32 for data, 16 for heap, and 64 for both stack areas. Since the pagesize is 1 kbyte, the maximum size of each area in kbytes is equal to the number of entries. (Note that the number of entries in a table defines the *maximum* size of an area, but that in general a process will occupy less memory. The remaining entries are marked as *INVALID* descriptors by the kernel when a program is loaded.)

When the EMPS kernel is used as a basis for data acquisition in physics experiments, the limitation of the size of memory areas caused by the static size of MMU tables is unacceptable. In particular the heap, which is used to store the data acquired from the experiment, may grow to a size of several megabytes.

Increasing the size of the MMU tables may seem to be a solution. However, the amount of memory required for storing the tables becomes problematic when the table size is increased. In the present version of the EMPS kernel, the maximum number of processes is chosen as 50. Because the MMU translation tables are allocated statically, the total number of MMU descriptors in the last level of the translation tree is 50 \* (64 + 32 + 16 + 64 + 64) = 12000. Each descriptor occupies 8 bytes, so that 96000 bytes are used. If the number of page descriptors would be increased such that megabytes of memory can be accessed, the translation tables would become excessively large.

Another problem with the original implementation is that each process has its own MMU descriptors for code, data, and heap, whereas the memory areas for code, data, and heap are shared between all processes in one task. The descriptors of all these processes must therefore be kept consistent: they all contain a copy of the same information. Every time a new process is created in a task, all descriptors for code, data and heap must be copied, and every time the heap area is expanded, the heap descriptors of all processes in the task must be updated. Apart from the overhead that is created, this implementation also involves a large number of MMU tables.

# 3.5 The new memory management implementation

To avoid the problems of statically declared MMU tables, a new implementation of the memory management routines has been made. In this new implementation, MMU tables are allocated dynamically, and the translation tables of the task address space (the code, data, and heap sections) are shared between all processes in the task. Also, early termination page descriptors are used for address translation of contiguous memory areas.

The translation tree that is built by the new implementation, is presented in figure 3.6.

# 3.5.1 Shared translation tables for processes in one task

As already mentioned above, application processes that belong to the same task share memory areas for program code, static data, and heap. Therefore, the part of the translation tree that is used for these areas can also be shared.

In some cases, memory areas of an application will be accessed by external devices using DMA. In this case, memory accesses do not occur via the MMU, and the physical address of the memory area is used. Because the data that is transferred using DMA will often cross page boundaries, the memory area must be physically contiguous. Therefore, a contiguous range of pages is

Figure 3.6: In the address translation tree created by the new memory management routines, early termination page descriptors are used, and the descriptors for code, data, and heap are shared between all processes in a task. Early termination page descriptors are marked with a \*.

reserved in all cases where DMA is possible. These are the data, heap, and stack sections.

Contiguous memory areas are also needed when data structures of an application process are accessed by a kernel process. The kernel process is not part of the application, and cannot access the data structure at the same virtual address as the application process, because these processes have a different address translation tree. Therefore, the kernel process translates virtual addresses of the application process to virtual addresses in the system address space, through which all memory locations can be reached. Because the data structure may cross page boundaries, the pages of this structure must be physically contiguous.

# 3.5.2 Dynamic allocation of memory for translation tables

The memory that is used to store the task related part of the address translation tree is allocated dynamically when a new task is created on the system. Similarly, the process related part of the tree is allocated when a new process is created in a task. This way, the size of the translation tables can be adjusted to the requirements of the task and the process.

A new task can be created by loading an application program via the LAN. The size of the translation tables is derived from the file header, which contains the size of the code area and the size of the data area. A detailed description of the file header can be found in appendix H.

#### 3.5.3 Early termination page descriptors

Most memory areas of an application program are required to be physically contiguous, as explained above. For these areas, the use of early termination page descriptors is advantageous, because the last level of the translation tree is omitted. Early termination page descriptors are used for the memory areas of data, heap, and stack.

The early termination page descriptors are located in the second level of the translation tree. In this level of the tree, the translation tables contain 64 descriptors (see section 3.3). The code area and data area each use 1 descriptor, so that 62 descriptors remain for the heap area. The heap area contains memory that is allocated dynamically when the application program is executing, and therefore the descriptors for the heap area must be written into the table when the application program allocates memory. If only early termination page descriptors would be used for the heap area, this would limit the number of memory blocks that could be allocated to 62 for each task, because only 62 descriptors are available for the heap area. This can be a problem for programs that allocate many small blocks of memory. To bypass this limitation, the implementation of the memory allocation functions also supports use of normal page descriptors. Normal page descriptors are located in the last level of the tree, in which the translation tables contain 16384 descriptors. The number of normal page descriptors that are required for a task, is a parameter of the kernel function that creates the task related part of the MMU tree.

#### 3.5.4 Protection of memory areas

Restricting access to certain memory areas in application programs can protect programs from the consequences of errors in other programs. The MMU offers read-only and supervisor-only access restrictions for memory areas. Combining these two options gives protection against write access in supervisor mode. It is not possible to protect a memory area against write access in user mode, while allowing write access in supervisor mode, except by prohibiting access of that memory area in user mode completely.

Because all memory locations can be accessed in the system address space, protection of this area against write access by application programs is desired. Application programs execute in the user mode of the processor, and therefore the system address space should be protected against write access in user mode. As explained above, the MMU doesn't offer this protection, but it can prohibit access to the system address space in user mode completely. However, in the current version of the kernel, it is assumed that application programs can read some parts of the system address space (e.g. when a message is sent via a mailbox). Completely prohibiting access to this area for application programs is therefore only possible by making substantial changes to the kernel. Because those parts of the system area which must be accessible to applications are all located in common memory, protection of the private memory part of the system address space is possible.

In the current kernel version, access restrictions have been implemented for the code area of application programs, which has read-only protection, and for the private memory part of the system area, which has supervisoronly protection.

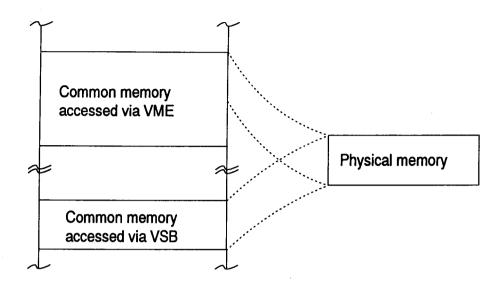

## 3.6 Use of the MMU to divert VME memory access to the VSB bus

Communication between processors within one node uses common memory, as explained in chapter 1. In the EMPS system, processors are connected to common memory with two separate hardware buses, namely the VME bus and the VSB bus. All processors within one node can access common memory via the VME bus, which has 20 slots. Access via the VSB bus is only possible if the processor and the memory module belong to the same cluster, which is a group of 5 slots. Which bus is used, depends on the address that is used to access a location in common memory. Some memory locations in shared memory can thus be accessed at two different addresses, one for access via the VME bus, and the other for access via the VSB bus, as shown in figure 3.7.

The bus system of a multi-processor system often forms a communication bottleneck. The availability of two separate buses for access to common memory can help to avoid this. Access to shared memory should occur via the VSB bus if the processor module and the memory module belong to the same cluster, so that the VME bus is available for communication between

Figure 3.7: Memory that is shared between processors within one cluster can be accessed at two different addresses, corresponding to the VSB and the VME bus, respectively.

modules that do not belong to the same cluster. Even when the EMPS system is equipped with only one processor module (which is a configuration that is likely to be used for the control of many physics experiments), using the VSB bus for memory access by the processor can be advantageous when the VME bus is used for DMA data transfer.

To exploit the access hierarchy formed by the VME/VSB buses in software, additional actions would be required. Each time shared memory is accessed, a program would have to check whether the memory module belongs to the same cluster as the processor module. In that case, it would have to calculate the address at which the memory location can be reached via the VSB bus. This would increase the complexity of the software, and add significant overhead.

Using the MMU, communication via the VSB bus can be made completely transparent. The MMU translation tables can be filled in such a way that when a memory location is accessed with an address that corresponds to the VME bus, but refers to a memory module that belongs to the same cluster, the translation of that address causes the VSB bus to be used instead. Any access to shared memory can therefore be done using the virtual address that belongs to the VME memory area.

Creating MMU translation tables in such a way that a virtual address which normally corresponds to the VME bus translates to a physical address that causes access via the VSB bus is straightforward. At system start up, on every processor a table is generated that contains the VME address areas of memory modules which can also be reached via the VSB bus. When an entry in the MMU translation table is filled, it is checked whether the physical destination address corresponds to a VME area that can also be reached through the VSB bus. If this is so, the corresponding VSB address is substituted.

Because for some applications the automatic use of the VSB bus may be undesirable, it has been made optional. At compile time of the kernel, generation of the extra code for transparent access via the VSB bus can be enabled with a #define TRANSPARENT\_VSB statement.

## Chapter 4

## **Performance tests**