| Eindhoven University of Technology                                            |

|-------------------------------------------------------------------------------|

|                                                                               |

|                                                                               |

|                                                                               |

|                                                                               |

|                                                                               |

| MASTER                                                                        |

| Vectorization of fast Fourier transform and digital audio broadcast reception |

|                                                                               |

|                                                                               |

|                                                                               |

| Gerritsen, D.                                                                 |

| Award date:<br>2004                                                           |

|                                                                               |

|                                                                               |

|                                                                               |

| Link to publication                                                           |

|                                                                               |

|                                                                               |

|                                                                               |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

### TECHNISCHE UNIVERSITEIT EINDHOVEN

Department of Mathematics and Computer Science

### MASTER'S THESIS

Vectorization of Fast Fourier Transform and Digital Audio Broadcast reception

by

D. Gerritsen

Supervisor:

prof. dr. C.H. van Berkel

Advisor:

dr. N. Engin (Philips Research)

Eindhoven, November 2003

### **Preface**

This report is my Master's thesis, resulting from my graduation project for my studies in Computer Science at the Eindhoven University of Technology. The graduation project was performed at the Embedded Systems Architectures on Silicon department of Philips Research Laboratories in Eindhoven.

This report describes the research I have done on mapping Fast Fourier Transform algorithms on a co-vectorprocessor architecture called CVP. Besides a proposal for an implementation of such algorithms on CVP, also suggestions have been made for ISA extensions that would improve FFT performance on CVP.

Furthermore I have looked into relevant applications using FFT, one of which is Digital Audio Broadcasting. For several kernels involved in DAB reception an analysis has been made on the feasibility of mapping those kernels to CVP.

I would like to express my gratitude to Nur Engin for her supervision at Philips Research, Kees van Berkel for his role as my university supervisor, Srinivasan Balakrishnan and Patrick Meuwissen for their help with the CVP compiler and assembler/simulator respectively and finally Albert van der Werf for allowing me to perform my graduation project in his group.

## **Abstract**

CVP (Co-Vector Processor) is a co-processor being developed in the SW-Modem project, combining data and instruction level parallellism in order to obtain a low-cost, power-efficient solution for the signal processing involved in third generation mobile communication.

This document presents a mapping of the Fast Fourier Transform algorithm as well as the kernels involved in baseband processing for Digital Audio Broadcast (DAB) reception to this architecture. Based on schedules for the inner loops of these algorithms cycle count estimates are calculated. Furthermore, bottlenecks in mapping the algorithms to the current architecture are pointed out and possible solutions are suggested. Based on the suggested architectural extensions, estimates are presented for the possible performance on an extended version of CVP.

Finally, a feasibility analysis is presented on the implementation of a DAB receiver on both the current CVP architecture and the extended version, in this document referred to as CVP0 and CVP0x respectively.

# **Contents**

| 1 | Intro | oductio  | n                                     | 1  |

|---|-------|----------|---------------------------------------|----|

|   | 1.1   | Genera   | al introduction                       | 1  |

|   | 1.2   | The Co   | o-Vector Processor                    | 1  |

|   | 1.3   | Fast Fo  | ourier Transform                      | 4  |

|   | 1.4   | Digital  | l Audio Broadcasting                  | 4  |

|   | 1.5   | Proble   | em statement and objectives           | 5  |

| 2 | Fast  | t Fourie | er Transform                          | 7  |

|   | 2.1   | Introdu  | uction                                | 7  |

|   | 2.2   | Overvi   | iew of FFT algorithms                 | 7  |

|   |       | 2.2.1    | Fixed radix                           | 7  |

|   |       | 2.2.2    | Other algorithms                      | 8  |

|   | 2.3   | A naiv   | re implementation                     | 8  |

|   |       | 2.3.1    | Brief description of the algorithm    | 10 |

|   |       | 2.3.2    | The actual algorithm                  | 11 |

|   |       | 2.3.3    | Performance figures and bottlenecks   | 12 |

|   | 2.4   | Improv   | ving FFT performance on CVP           | 15 |

|   |       | 2.4.1    | An alternative implementation         | 15 |

|   |       | 2.4.2    | Bitreversed addressing acu mode       | 16 |

|   |       | 2.4.3    | Scatter-gather memory accessing       | 16 |

|   |       | 2.4.4    | Single cycle full shuffle instruction | 17 |

|   |       | 2.4.5    | Software pipelining                   | 18 |

|   |       | 2.4.6    | Radix 4 FFT                           | 20 |

|   | 2.5   | Conclu   | usions                                | 31 |

| 3 | Dig   | ital Aud | dio Broadcasting                      | 34 |

|   | 3.1   | DAB s    | system description                    | 34 |

|   | 3.2   | DAB r    | reception and CVP                     | 39 |

|   |       | 3.2.1    | Digital filters                       | 41 |

|   |       | 3.2.2    | Cordic                                | 41 |

|   |       | 3.2.3    | FFT                                   | 44 |

|   |       | 324      | Differential demodulation             | 45 |

|           |       | 3.2.5 Quantization                                                                | 15 |

|-----------|-------|-----------------------------------------------------------------------------------|----|

|           |       | 3.2.6 Frequency deinterleaving                                                    | 16 |

|           |       | 3.2.7 Time deinterleaving                                                         | 17 |

|           |       | 3.2.8 Viterbi decoding                                                            | 18 |

|           | 3.3   | Overall DAB performance on CVP                                                    | 18 |

|           |       | 3.3.1 Processing load                                                             | 18 |

|           |       | 3.3.2 Memory usage                                                                | 9  |

| 4         | Cone  | clusions 5                                                                        | 52 |

|           | 4.1   |                                                                                   | 52 |

|           | 4.2   |                                                                                   | 3  |

|           |       |                                                                                   |    |

| T         | ist o | f Figures                                                                         |    |

| <b>I.</b> | ist u | i i gui co                                                                        |    |

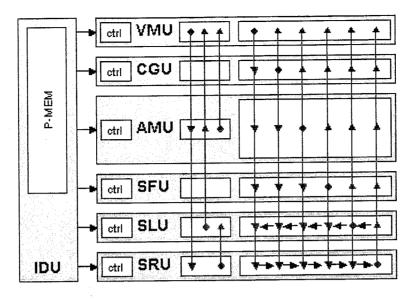

|           | 1     | The CVP framework                                                                 | 2  |

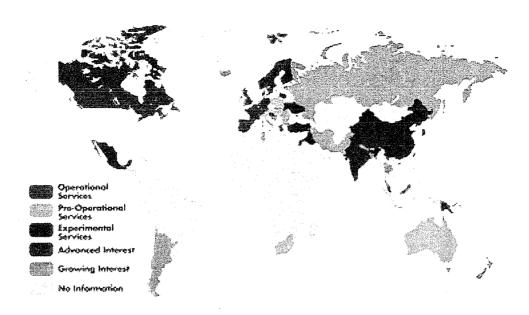

|           | 2     | DAB world coverage map (January 2003)                                             | 5  |

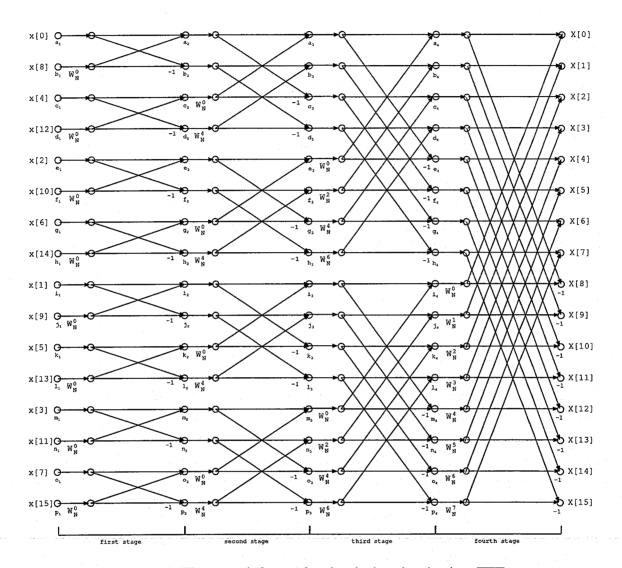

|           | 3     | Flow graph for a 16-point decimation-in-time FFT                                  | 9  |

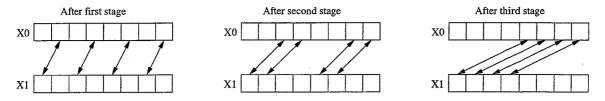

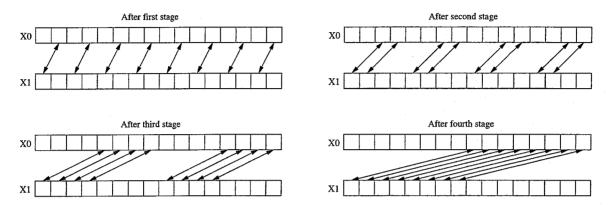

|           | 4     | The shuffle pattern for $N_v = 8$                                                 | 1  |

|           | 5     | The shuffle pattern for $N_v = 16$                                                | 1  |

|           | 6     | Scheduling for the inner loop calculating the actual butterflies                  | 3  |

|           | 7     | Schedule for the radix 2 intra-vector stages                                      | 9  |

|           | 8     | Schedule for the radix 2 inter-vector stages                                      | 0  |

|           | 9     | Flow graph for a 16 point radix 4 FFT algorithm                                   | 1  |

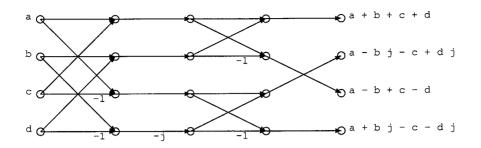

|           | 10    | Butterfly for a 4-point DFT                                                       | 2  |

|           | 11    | The shuffle pattern for radix 4 FFT                                               | 2  |

|           | 12    | Alternative flow graph for the radix 4 butterfly                                  | 5  |

|           | 13    | Schedule for the radix 4 inter-vector stages                                      | 6  |

|           | 14    | Schedule for the first radix 4 intra-vector stage, first intra-vector approach 2  | 7  |

|           | 15    | Schedule for the second radix 4 intra-vector stage, first intra-vector approach 2 | 8  |

|           | 16    | Schedule for the radix 4 intra-vector stages, second intra-vector approach 3      | 0  |

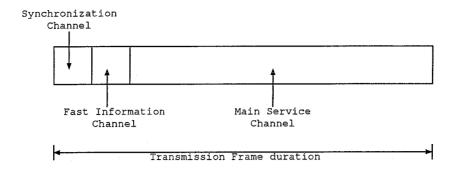

|           | 17    | Structure of the DAB transmission frame                                           | 5  |

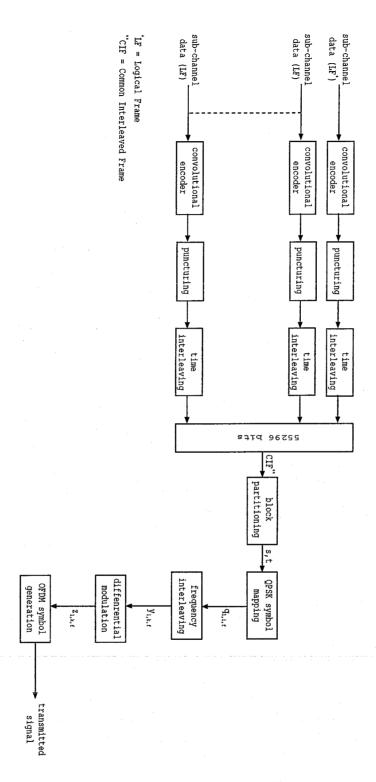

|           | 18    | DAB transmitter block diagram                                                     | 6  |

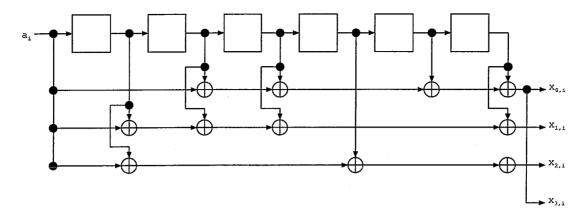

|           | 19    | The convolutional encoder                                                         | 7  |

|           | 20    | Example of a Common Interleaved Frame                                             | 7  |

## Master's Thesis: Vectorization of FFT and DAB reception

|   | 21    | Block partitioning for transmission mode I                                                                                                        | 38 |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

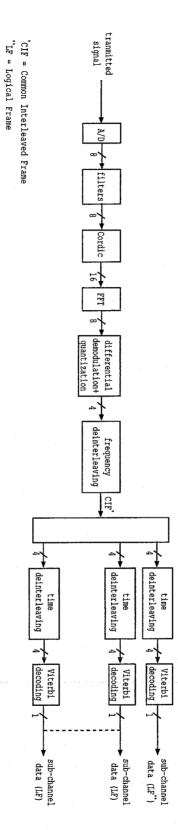

|   | 22    | DAB receiver block diagram                                                                                                                        | 40 |

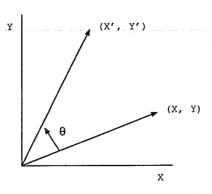

|   | 23    | The rotation performed by the Cordic algorithm                                                                                                    | 41 |

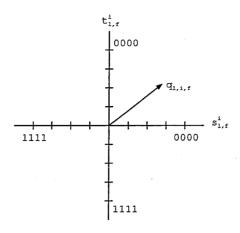

|   | 24    | Quantization of the complex QPSK symbol $q_{l,i,f}$ to two 4-bit symbols $s_{l,f}^i$ and $t_{l,f}^i$                                              | 46 |

| L | ist c | of Tables                                                                                                                                         |    |

|   | 1     | Used CVP assembly instructions                                                                                                                    | 3  |

|   | 2     | Assembly instruction suffixes                                                                                                                     | 4  |

|   | 3     | The required number of full shuffles for bit reversal                                                                                             | 14 |

|   | 4     | Cycle count estimates for FFT, naive implementation                                                                                               | 15 |

|   | 5     | Comparison between the cycle counts for radix 2 and radix 4 on CVP0x, not accounting extra loop initiation and acu configuration overhead cycles. | 31 |

|   | 6     | CVP0x architecture extensions                                                                                                                     | 32 |

|   | 7     | FFT cycle count estimates for CVP0 and CVP0x, 16-bit precison, radix 2 implementation, except those marked with *                                 | 33 |

|   | 8     | Performance figures for a 1024 point 16 bit complex FFT                                                                                           | 33 |

|   | 9     | Parameters for the transmission modes I, II, III and IV                                                                                           | 35 |

|   | 10    | Time interleaving order                                                                                                                           | 38 |

|   | 11    | FFT cycle count estimates for the various DAB transmission modes                                                                                  | 45 |

|   | 12    | FFT processing load for the various DAB transmission modes                                                                                        | 45 |

|   | 13    | Extra CVP0x extensions for DAB reception kernels                                                                                                  | 48 |

|   | 14    | Processing load for the various DAB reception kernels                                                                                             | 49 |

|   | 15    | Memory usage for DAB reception kernels, excluding time deinterleaving                                                                             | 51 |

### Glossary

**ACU** Address Computation Unit Arithmetic Logic Unit **ALU** ALU-MAC Unit **AMU ASIC** Application Specific Integrated Circuit **CDMA** Code Division Multiple Access Common Interleaved Frame **CIF** Coded OFDM COFDM **CVP** Co-Vector Processor DAB Digital Audio Broadcasting Differential Demodulation DD **FFT** Fast Fourier Transform FIC Fast Information Channel FIR Finite Impulse Response Instruction Set Architecture **ISA** Local Area Network LAN LF Logical Frame **MAC** Multiply-Accumulate **MIPS** Mega-Instructions Per Second Moving Pictures Expert Group **MPEG MSC** Main Service Channel Orthogonal Frequency Division Multiplex **OFDM QPSK** Quadrature Phase Shift Keying Shuffle Unit **SFU** Single Instruciton Multiple Data SIMD **SLU** Shift Left Unit Shift Right Unit SRU Vector Memory Unit **VMU** Very Long Instruction Word **VLIW**

### 1 Introduction

### 1.1 General introduction

In the software-modem research project, conducted in the Embedded Systems Architectures on Silicon group at Philips Research, a co-vector processor is being developed, which is intended to serve mainly as a low-cost, low-power, programmable solution for the baseband processing involved in various third generation wireless communication standards, such as UMTS, TD-SCDMA and IS-2000.

In order to meet the computational requirements while at the same time dissipating as little power as possible, a high degree of parallellism is used. This involves data as well as instruction level parallellism.

Since this coprocessor is intended to be used in third generation mobile handsets, it is interesting to explore on other possible mobile aplications, such as wireless LAN, digital audio and video reception, etcetera.

Since fast fourier transforms are used in many of those applications, this will be the first kernel to be discussed. This part is covered in section 2. Section 3 covers one of the applications that involves the use of FFT, namely Digital Audio Broadcasting. It contains a feasibility analysis for implementing various kernels involved in the baseband signal processing for DAB reception. The final section contains the conclusions and suggestions for future study on the subject.

### 1.2 The Co-Vector Processor

To achieve the level of parallellism needed to meet the computational requirements, CVP combines elements of so-called VLIW and SIMD processors. Like a VLIW processor, CVP has multiple different functional units, each of which can typically perform one operation every clock cycle. Furthermore, every sub-instruction processed by a functional unit effects multiple data elements at once, a feature CVP has in common with so-called SIMD processors.

CVP sub-instructions operate on 256 bit vectors, which can be organized in several ways, ranging from 32 8-bit word elements up until 8 32-bit elements. Complex vectors exist in two forms, containing 16 elements of word sized real and imaginary components, or 8 elements of double word sized complex values.

The CVP consists of seven functional units. These are the Instruction Distribution Unit, Vector Memory Unit, Code Generation Unit, ALU-MAC Unit, Shuffle Unit, Shift Left Unit and the Shift Right Unit. Since there is no central register file, these units are connected by a full interconnect network in order to facilitate for communication between functional units. Communication between the functional units is performed by means of send and receive instructions. Every functional unit can send values (either explicit or implicit) that can be received by one or more other units. Every unit can send data to and receive from any other unit during each cycle. The exception to this is the ALU-

Figure 1: The CVP framework

MAC unit, which can receive data from two units every cycle. The CVP framework is graphically depicted in figure 1.

In short, the purpose of the several functional units is as follows.

- The Instruction Distribution Unit (IDU) contains the program memory and handles the distribution of the sub-instructions to the functional units. Allowed control statements involve subroutine calls and zero-overhead looping.

- The Vector Memory Unit (VMU) contains the vector memory and handles all memory read and write accesses. Memory accesses can pertain to vectors as well as scalar values. Indexing the memory locations is done using one of the address computation units (ACUs).

- The Code Generation Unit (CGU) is used to generate CDMA code chip vectors, the code type required for the UMTS/FDD standard. Future extensions could be to include codes for other standards as well.

- The ALU-MAC Unit (AMU) performs all arithmetic and logic functions. These include operations where arithmetic is performed elementwise on multiple vectors, as well as intra-vector operations, where the arithmetic is performed on elements within a single vector.

- The Shuffle Unit (SFU) is used to rearrange elements within a vector. At the moment only half shuffles are supported, which can shuffle only the odd or even indexed half of a vector in a single instruction.

- The Shift Left Unit (SLU) can shift elements in a vector to the left on a word, double word or quad word basis. The value shifted in at the right side of the vector can be either zero or a value presented to the scalar register of the SLU.

| Functional unit | Instruction | Meaning                                                           |  |  |

|-----------------|-------------|-------------------------------------------------------------------|--|--|

| VMU             | SEND        | Send a scalar value                                               |  |  |

|                 | SENDL       | Send a memory line                                                |  |  |

|                 | SENDV       | Send a vector                                                     |  |  |

|                 | RCVL        | Receive a memory line                                             |  |  |

| AMU             | RCV         | Receive a vector                                                  |  |  |

|                 | SND         | Send a vector                                                     |  |  |

|                 | MUL         | Multiplication                                                    |  |  |

|                 | ADD         | Addition                                                          |  |  |

|                 | SUB         | Subtraction                                                       |  |  |

|                 | ASR         | Arithmetic shift right (division by $2^n$ )                       |  |  |

|                 | ASRA        | Arithmetic shift right of an accumulator register                 |  |  |

| SFU             | RCV         | Receive a vector                                                  |  |  |

|                 | CONF        | Receive a configuration vector to one the configuration registers |  |  |

|                 | FULL        | Perform a full shuffle on the vector elements                     |  |  |

Table 1: Used CVP assembly instructions

• The Shift Right Unit (SRU) is similar to the SLU, bit it shifts in the opposite direction. In addition it can merge sparse vectors resulting from consecutive intra-vector operations.

For a more detailed description of the instruction set architecture, see [1, 2].

For the current CVP tools exist for assembly, simulation and debugging. Although pipelining and caching effects inside functional units are hidden from the programmer, assembly level programming is still a complex task, because it involves error-prone tasks such as scheduling of functional unit operations, and register allocation. In order to relieve the programmer of these complex tasks, a higher level programming language called CVP-C exists. It is however still up to the programmer to transform the original algorithm operating on scalar values into a vectorized version. Since the CVP-C compiler became available during the course of this graduate work and is not yet fully reliable, most programming was performed in assembly language.

In this document we shall present schedules for some parts of the algorithms we will look into. These schedules will only include the functional units that are actually used for the particular (part of the) algorithm. In these schedules we use the assembly instruction names to denote the operations. The meaning of these operations can be found in table 1. This table contains the 'basic' instruction names only. In an assembly program the AMU arithmetic instructions are appended with a suffix the denotes the precision to be used. These suffixes and their meaning can be found in table 2.

Besides the current CVP architecture we shall also look into possible architectural extensions that could improve the performance for the algorithms under investigation. In order to distinguish between the current and extended version, we shall refer to these as CVPO and CVPOx.

| Instruction suffix | Short for          | Indicated precision       |

|--------------------|--------------------|---------------------------|

| i                  | int                | 8 bit integer number      |

| di                 | double int         | 16 bit integer number     |

| qi                 | quad int           | 32 bit integer number     |

| ci                 | complex int        | 2 * 8 bit complex number  |

| cdi                | complex double int | 2 * 16 bit complex number |

Table 2: Assembly instruction suffixes

#### 1.3 Fast Fourier Transform

In a wide variety of applications, signal analysis in the frequency domain is performed. A common way to transform a signal from time to frequency domain is by means of the fourier transform. When this transform is is computed over a sampled signal, it is called the discrete fourier transform, in short DFT. The DFT of a finite sequence of N samples is defined by

$$X[k] = \sum_{n=0}^{N-1} x[n]W_N^{kn}, \qquad k = 0, 1, \dots, N-1,$$

where  $W_N = e^{-j(2\pi/N)}$ .

Algorithms that exploit periodicity and symmetry properties of  $W_N^{kn}$  are collectively known as Fast Fourier Transform (FFT) algorithms. Applications involving the use of FFT include spectrum analysis, digital audio and video broadcasting and wireless LAN. Because of the importance of the algorithm many attempts have been undertaken to efficiently implement the algorithm on current Digital Signal Processing (DSP) architectures.

### 1.4 Digital Audio Broadcasting

Digital Audio Broadcasting (DAB) is a system designed to become the successor to the present-day analogue radio. Current AM and FM radio signals are subject to numerous kinds of interference on the way from transmitter to the receiver. These interferences are caused by obstacles such as mountains and high-rise buildings as well as weather conditions. The DAB system is far less sensitive for these kinds of interferences because of the application of forward error correction coding, interleaving, etcetera. This results in a distortion-free reception of CD quality sound. Aside from a higher quality of the received audio, DAB offers further advantages, as it can not only carry radio, but also data such as text, pictures and even video.

In contrast to conventional analogue radio signals carrying one service per frequency, DAB signals can carry multiple services, both audio and data. Such a DAB transmission signal is commonly referred to as a DAB ensemble, and carries a multiplex of audio and/or multimedia services. The number of services, also called sub-channels, depends on the (audio or data) bitrate and the level of error correction coding that is applied.

Figure 2: DAB world coverage map (January 2003)

DAB is currently being implemented in many parts of the world. See figure 2 for the DAB coverage as of January 2003. In the Netherlands, the nation-wide service broadcaster NOS put on air an ensemble containing the radio stations Radio 1, Radio 2, 3FM, Radio 4, 747AM and 'De Concertzender', broadcasted through the transmitter located in Lopik. Nation-wide DAB coverage can be expected within a few years.

### 1.5 Problem statement and objectives

Since the CVP is intended to be used in third generation mobile handsets, it is desirable that it can also be used in other mobile aplications, such as wireless LAN, digital audio and video reception, etcetera. Since FFT is a common kernel in many of those applications, good FFT performance on CVP is required. Furthermore, an analysis of the other kernels involved in those applications is desirable.

The first goal of this graduate project is to study several FFT algorithms and transform these into a vectorized version, intended to be implemented on CVP. Because vector processing in itself is not a new subject, vectorization attempts have been made for other vector processors, such as VIRAM and OnDSP. The novelty lies in the fact that CVP combines this data parallellism with instruction level (VLIW) parallellism. The challenge is therefore to exploit this parallellism in order to make full use of CVP's processing capabilities.

Based on these vectorizations, bottlenecks in both the algorithms itself and the current CVP architecture should be pointed out. A second goal is therefore to come up with possible extensions to the current CVP architecture that would improve the performance for FFT. Estimates on the FFT performance for a hypothetical extended version, which we will call CVP0x, will be made. For both CVP0 and CVP0x the FFT performance will

be compared to that of other DSP architectures.

Besides the mapping of FFT, another goal is to analyse the feasibility of implementing a DAB receiver on CVP. For the various DAB reception kernels too the bottleneck with respect to the current architecture should be pointed out, as well as architectural extensions that would solve these problems.

### 2 Fast Fourier Transform

#### 2.1 Introduction

In order to come up with a good vectorization, we shall first take a look at several existing FFT algorithms. We hope that by implementating a first naive vectorization we will be able to point out the performance bottlenecks. Possible solutions, both algorithmic changes and CVP architecture extensions will then be suggested to address these bottlenecks, as well as the performance gain that could be achieved by these extensions. The resulting performance figures will be compared to benchmarks of existing architectures.

The DFT of a finite sequence of N samples is defined by

$$X[k] = \sum_{n=0}^{N-1} x[n] W_N^{kn}, \qquad k = 0, 1, \dots, N-1,$$

(1)

where  $W_N = e^{-j(2\pi/N)}$ .

Since x[n] may be complex, direct evaluation of the DFT according to Eq. 1 requires N complex multiplications and N-1 complex additions. To compute all N values would therefore require  $N^2$  complex multiplications and N(N-1) complex additions.

By exploiting symmetry and periodicity properties of  $W_N^{kn}$ , computation of a DFT can be done much more efficiently, especially when N is a product of two or more integer numbers. This allows for decomposition of the DFT into successively smaller DFTs, which all together require less computation.

### 2.2 Overview of FFT algorithms

The most commonly known FFT algorithms reduce the required computation by decomposing the DFT into successively smaller DFTs. For this approach to work, the length of the DFT, N, should be a composite number, i.e. a product of two or more integer factors. These algorithms differ in how the decomposition is performed.

#### 2.2.1 Fixed radix

If the decomposition of the DFT is done by using the same factor for every successive decimation, we call the algorithm fixed radix. For the decomposition we have two options. Algorithms that decompose the input sequence x[n] into successively smaller subsequences are called *decimation-in-time algorithms*. Decimation-in-frequency algorithms perform the decomposition on the output sequence X[k].

How this decomposition speeds up computation is most easily illustrated by considering the case that N is a power of 2. The N-point DFT is then split into two (N/2) point DFTs, one consisting of the even numbered points in x[n] and the other one consisting of

the odd numbered points. This way we get

$$X[k] = \sum_{r=0}^{(N/2)-1} x[2r]W_N^{2rk} + \sum_{r=0}^{(N/2)-1} x[2r+1]W_N^{(2r+1)k}$$

(2)

Since  $W_N^2 = W_{(N/2)}$ , Eq. 2 can be rewritten as

$$X[k] = \sum_{r=0}^{(N/2)-1} x[2r]W_{(N/2)}^{rk} + W_N^k \sum_{r=0}^{(N/2)-1} x[2r+1]W_{(N/2)}^{rk}$$

(3)

In Eq. 3, both sums can be seen as an (N/2)-point DFT. We can continue this decompostion until we end up with 2-point DFTs only, which do not involve complex multiplications. Therefore the only remaining complex multiplications are the ones with the factors  $W_N^k$  in Eq. 3, the so-called *twiddle factors*, reducing the computation complexity from  $\mathcal{O}(N^2)$  to  $\mathcal{O}(N \log_2 N)$ .

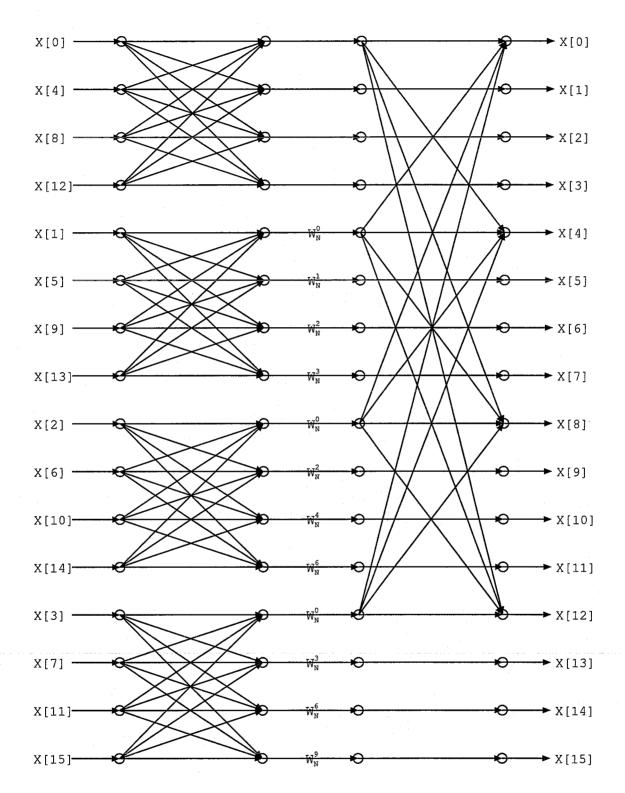

The entire radix 2 decimation-in-time algorithm for a 16-point FFT is graphically depicted in figure 3. In this flow graph, the branch transmittances correspond to multiplication coefficients. The value for a node in the graph is calculated by summing all branches entering the node, multiplied by their branch transmittances. For every branch where the transmittance is omitted, it is assumed to be 1. As can be seen in the flow graph, the input to the algorithm is not in sequential, but in so-called bit-reversed order. For more information and a more detailed derivation of the algorithm, see [3].

Other fixed radix algorithms are similar to the radix 2 algorithm. For instance in a radix 4 algorithm, the input (for decimation-in-time) or the output sequence (decimation-in-frequency) is decomposed iteratively into 4-point DFTs.

### 2.2.2 Other algorithms

In the previous section, we have discussed the case that N is an integer power of some radix r. If we can decompose the DFT using the same factors every decimation step, we get a fixed radix algorithm as discussed in the previous section, but other algorithms exist. We can use different decimation factors during consecutive stages, for instance using as many factors of 4 as possible and finishing with a factor 2. These algorithms are called mixed radix algorithms. Furthermore, FFT algorithms exist which exploit the fact that N is a product of two or more relatively prime factors.

For a more detailed description of these other types of FFT algorithms, see [3].

### 2.3 A naive implementation

This section describes an implementation of a radix 2 decimation-in-time FFT algorithm for CVP. It also contains figures on the performance of this implementation and an analysis of the encountered performance bottlenecks.

Figure 3: Flow graph for a 16-point decimation-in-time FFT

### 2.3.1 Brief description of the algorithm

The implementation is basically a vectorization of the radix 2 decimation-in-time algorithm described in section 2.2.1. According to [1, 2], a vector on the CVP can contain 8 or 16 complex values, depending on the precision. We shall define the vector size as

$$N_v = \frac{128}{P},$$

where  $N_v$  is the number of elements in a vector and P is the precision in bits of the real as well as the imaginary part of a complex vector element.

As can be seen in figure 3, for the first  $\log_2 N_v$  computation stages the values that have to be summed reside in a single vector, whereas for the remaining  $\log_2 N - \log_2 N_v$  stages, these values reside in different vectors. We shall refer to these stages as the *intra-vector* and *inter-vector* stages respectively.

Vectorizing the algorithm is straightforward for the inter-vector stages. If we assume  $N_v = 8$ , all computation for the fourth stage of figure 3 can be done with only a few vector operations. Having a vector  $X_0$  consisting of  $a_4$  through  $h_4$ ,  $X_1$  containing  $i_4$  through  $p_4$  and  $p_4$  and  $p_4$  holding the twiddle factors  $p_N^0$  through  $p_N^0$ , we could compute the new values for  $p_0$  and  $p_1$  as follows

$$tmp := W \times X_1$$

$$; X'_0 := X_0 + tmp$$

$$; X'_1 := X_0 - tmp$$

where  $X \times Y$  is the vector resulting from the element-wise multiplication of the vectors X and Y.

For the intra-vector stages, things are a bit more complicated. Since the values that have to be summed together reside in a single vector, we cannot implement the butterflies in the same manner as we did for the inter-vector stages. In order to be able to use the same basic computation, we will first have to make sure that the values that should be added together are distributed over separate vectors. A means that CVP offers for this is the shuffle unit. It allows us to specify a shuffle pattern, that describes which element of the input vector should end up at which position in the output vector. The current CVP architecture only supports half shuffles, meaning that we can perform a shuffle on only the odd or even indexed vector elements in a single instruction. Since the shuffle result is stored in an implicit target register in the shuffle unit, we can achieve a full shuffle by sequentially performing an odd and even shuffle.

By performing the correct shuffles after each of the intra-vector stages, we can rearrange the vector elements in such a way that we can perform the same basic butterfly operation as we did for the inter-vector stages. For a length N and vector size  $N_v$ , we have a total of  $M = N/N_v$  vectors,  $X_0$  through  $X_{M-1}$ . Shuffling is performed between every two consecutive vectors,  $X_{2i}$  and  $X_{2i+1}$  for  $0 \le i < (M/2) - 1$ . The shuffle pattern to be used

#### Master's Thesis: Vectorization of FFT and DAB reception

Figure 4: The shuffle pattern for  $N_v = 8$

Figure 5: The shuffle pattern for  $N_v = 16$

is depicted in figure 4 for  $N_v = 8$  and figure 5 for  $N_v = 16$ . This shuffling mechanism was suggested in [4].

As can be seen in figure 3, we have to supply the input to the first computation stage in a very specific order, which we will call 'bit-reversed'. This terminology becomes obvious when we look at the indices of the inputs written as binary digits. The order in which we supply the input is regularly increasing, but with the bits reversed. In order to avoid intra-vector operations, we have to interleave these values over two consecutive vectors. As we shall see later, it is this bit-reversed ordering which has to be done in advance that can drastically decrease performance.

#### 2.3.2 The actual algorithm

Following is the pseudo-code for the naive algorithm described in the previous section. We assume that all twiddle values to be used reside in memory, grouped in correctly ordered vectors. This makes computation much more efficient, since we do not have to shuffle the twiddle values in order to get the correct values into a vector, at the expense of some extra memory usage. Furthermore, we assume that the FFT length N is at least twice the vector size  $N_{\nu}$ , so we have at least two vectors of input data.

```

butterfly := 0

;do butterfly <\frac{N}{2N_v} \rightarrow

computeButterly()

; butterfly := butterfly + 1

od

; shuffle()

; stage := stage + 1

;do stage < \log_2 N \rightarrow

butterfly := 1

;do butterfly <\frac{N}{2N_{\rm p}}\rightarrow

computeButterly()

; butterfly := butterfly + 1

od

; stage := stage + 1

od

]

```

The function computeButterfly is given by

M[i] denotes the vector residing in the vector memory at location i. The calculation of the correct memory addresses & $X_0$  and & $X_1$  is done using the address calculation units present in the vector memory unit. The bit-reversed ordering prior to the actual butterfly calculations is performed by means of the shuffle unit. As we shall see later, time tends to grow to a large number of clock cycles for large values of N.

The schedule for the inner loop that performs the actual butterfly computations is illustrated in figure 6.

#### 2.3.3 Performance figures and bottlenecks

As can be seen in figure 6, performing the actual butterfly computations costs five clock cycles per vector pair, per computation stage. This adds up to  $(\log_2 N) * \frac{N}{2N_v} * 5$  cycles.

| cycle  | VMU     | VMU     | AMU      | AMU      | AMU     |

|--------|---------|---------|----------|----------|---------|

| number | vopcode | aopcode | receive1 | receive2 | vopcode |

| n      | RCVL    | INCR    |          |          | MULcdi  |

| n+1    | SENDL   | INCR    |          |          |         |

| n+2    | SENDL   | INCR    | RCV(VMU) |          | ASRAcdi |

| n+3    | SENDL   | INCR    | RCV(VMU) |          | ADDcdi  |

| n+4    | RCVL    | INCR    | RCV(VMU) |          | SUBcdi  |

Figure 6: Scheduling for the inner loop calculating the actual butterflies

In practice, due to overhead for setting up the ACUs, the number of clock cycles will be higher.

Furthermore, we have to add some cycles for the shuffling after each of the intra-vector stages. For every vector pair we have to perform four full shuffles. Since for every two consecutive shuffles, we have to use a different shuffle pattern, this will cost three cycles per full shuffle for the configuration, odd and even shuffle instructions, adding up to a total of  $(\log_2 N_v) * \frac{N}{2N_v} * 12$  clock cycles, only a very small part of which can be executed in parallel with the butterfly computations.

Finally, we have to take into account the clock cycles needed to perform bit reversal prior to the actual computation. Again, like for the shuffles after the intra-vector stages, every full shuffle costs three cycles. So in order to derive the cycle count for the necessary bit reversal, we need to know how many shuffles bit reversal takes for an FFT of length N.

To address this problem, let us define the exact order in which we need to supply the input data. Consider the input data to be an array X of length N. We can divide this array into  $\frac{N}{N_v}$  vectors  $X_i$  of length  $N_v$ , each vector  $X_i$  containing the values  $X[i*N_v]$  through  $X[N_v-1+i*N_v]$ . We define the function b as follows

$$b((i_0, i_1, \ldots, i_{\log_2 N-1})_2) = (i_{\log_2 N-1}, i_{\log_2 N-2}, \ldots, i_0)_2$$

where  $(i_0, i_1, \ldots, i_{\log_2 N - 1})_2$  is the binary representation of the number i, using  $\log_2 N$  bits. Having the input data array X, we will call the array Y its bit-reversed order if

$$Y[b(i)] = X[i]$$

Similarly we could have defined the array Y by

$$Y[i] = X[b(i)].$$

As mentioned before in section 2.3.1, the order we want prior to computation is slightly different than regular bit-reversed. We provide the input to the first computation stage as vectors  $Y_i$ , where every vector  $Y_{(2j)}$  contains the values  $Y[2jN_v]$ ,  $Y[2+2jN_v]$ , ...,  $Y[2N_v-2+2jN_v]$  and every vector  $Y_{(2j+1)}$  contains  $Y[1+2jN_v]$ ,  $Y[3+2jN_v]$ , ...,  $Y[2N_v-1+2jN_v]$ . We now want to derive the number of shuffles needed for this reordering.

| N        | $N_v$ Number of full shuffles |     |  |

|----------|-------------------------------|-----|--|

| 16       | 8                             | 2   |  |

| 32<br>64 | 8                             | 8   |  |

| 64       | 8                             | 32  |  |

| ≥ 128    | 8                             | N   |  |

| 32<br>64 | 16                            | 2   |  |

| 64       | 16                            | 8   |  |

| 128      | 16                            | 32  |  |

| 256      | 16                            | 128 |  |

| ≥ 512    | 16                            | N   |  |

Table 3: The required number of full shuffles for bit reversal

We observe that the indices of the values that initially reside within the same vector  $X_i$ , that is  $iN_v$  through  $N_v - 1 + iN_v$ , written as  $\log_2 N$  bit numbers, share the same  $\log_2 N - \log_2 N_v$  most significant bits. If we now calculate the bit-reversed order, then these values share the same  $\log_2 N - \log_2 N_v$  least significant bits. We can therefore conclude that the corresponding values in array Y will be  $k\frac{N}{N_v}$  apart for  $k \neq 0$ .

In our so-called 'interleaved' bit-reversed order, the values originating from one single vector  $X_i$  will all end up in different vectors  $Y_j$  if the corresponding values in array Y are separated by at least  $2N_v$ . Since we know that the values originating from a single vector  $X_i$  will be multiple of  $\frac{N}{N_v}$  apart in the array Y, we conclude that all elements from one single vector have to end up in all different vectors if  $\frac{N}{N_v} \ge 2N_v$  or  $N \ge 2N_v^2$ . This means that for each of the  $\frac{N}{N_v}$  vectors we have to perform a full shuffle per vector element. In this case, the bit-reversed ordering will take a total of N full shuffles. For smaller values of N the number of required shuffled can easily be deduced as well. The number of shuffles required for bit reversal for different values of N and  $N_v$  can be found in table 3.

Combining the numbers for bit reversal, inter-stage shuffling and the actual butterfly computations, we can derive the estimated cycle counts for computing FFTs for several different sizes. These estimates can be found in table 4. In calculating these numbers, for the inter-vector stages six cycles per vector pair per stage were assumed, whereas this could ideally be five cycles. This was done to compensate for the overhead caused by reconfiguration of the ACUs and loop initiation. Especially for the larger sized FFTs, this gives rise to somewhat pessimistic estimates. For the smaller sized FFTs the estimates are quite accurate. Implementations of 32 and 64 point FFTs have cycle counts within a few percent range of the estimated numbers. These implementations however followed a slightly less naive scheme, hiding the bit reversal behind the actual computations. This has been accounted for by adding three times the required number of shuffles for bit reversal to the cycle count of the simulated cycle counts.

<sup>&</sup>lt;sup>1</sup>As mentioned earlier, we only take into account the cases where  $N \ge 2N_v$ .

| N    | $N_v$ | Estimated cycle count |

|------|-------|-----------------------|

| 16   | 8     | 60                    |

| 32   | 8     | 140                   |

| 64   | 8     | 350                   |

| 128  | 8     | 935                   |

| 256  | 8     | 1955                  |

| 512  | 8     | 4100                  |

| 1024 | 8     | 8580                  |

| 32   | 16    | 75                    |

| 64   | 16    | 165                   |

| 128  | 16    | 400                   |

| 256  | 16    | 1035                  |

| 512  | 16    | 2935                  |

| 1024 | 16    | 6055                  |

Table 4: Cycle count estimates for FFT, naive implementation

### 2.4 Improving FFT performance on CVP

The implementation presented in the previous section is far from optimal. Therfore we will present some measures for enhancing the FFT performance in this section.

#### 2.4.1 An alternative implementation

In the naive implementation of the radix 2 algorithm presented earlier, a disproportionately large part of the total cycle count is consumed by the intra-vector stages. This is due to the necessary bit reversal and the inter-stage shuffles. In this section we will make an effort to come up with a more efficient implementation that reduces the cycle count for those first few computation stages.

Looking at the flowgraph in figure 3, we can see that in order to compute the values resulting after the intra-vector stages for two vectors, we do not need any other values than the ones that reside within these two vectors before the first stage. Therefore we can compute all intra-vector stages for one vector pair before moving on the next pair, thereby eleminating the need to store and load new vectors in between these stages. Another advantage of this approach is that performing these  $\text{Log}_2N_v$  intra-vector stages for a single pair can be combined with the bit-reversed ordering of the next vector pair. That way the bit reversal for all vectors except the first pair can be 'hidden' behind the butterfly computations and inter-stage shuffles during the intra-vector stages.

However, during the intra-vector stages the shuffle unit is already utilized most of the clock cycles. It is therefore not desirable to use the shuffle unit for the reordering of the next vector pair, since it would then become inpossible to hide the bit reversal completely. For the current CVP architecture however, the shuffle unit is the only means available for such reordering. Suggestions for enhancements to the architecture and instruction set in

order to cope with this problem, are given in the next sections.

### 2.4.2 Bitreversed addressing acu mode

A possible solution that would make it possible to perform bit reversal without utilizing the shuffle unit, would be to extend the instruction set architecture to support bitreversed addressing. One could think of an extra 1-bit register per ACU, or probably only for one of them, indicating whether or not to use bitreversed addressing and an extra ACU suboperation to set the value for this register. Another option is to only include an extra ACU suboperation for a bitreversed increment of the offset register of that particular ACU.

In both cases, performing a 'bit-reversed increment' would involve three consecutive steps: bitreversing the current value of the offset register, adding the value of the increment register to the bit-reversed offset value and finally bitreversing the incremented offset value again.

In presence of a bit-reversed addressing mode we can use scalar memory read operations to read the values for the next vector pair to be processed. Using the shift right unit, we can combine these scalar values to form the actual vectors. Since we do not have to use the already heavily utilized shuffle unit, we can perform bit reversal for the next vector pair in parallel with the intra-vector stages for the current pair.

This approach was implemented using the current CVP assembler/simulator toolset. Since the current architecture and toolset do not support this bit-reversed addressing this was simulated by providing the input data in bit-reversed order and reading the inputs on a scalar level using regular ACU addressing. In this implementation the computation of the intra-vector stages for a single vector pair took 57 clock cycles for single precision and 44 cycles for double precision data. For single precision we therefore have 57 clock cycles in which to schedule 32 scalar memory accesses in order to read the values for the next vector pair. For double precision we have to schedule 16 accesses in 44 clock cycles. It turns out that this is indeed possible without having to schedule a scalar and a vector memory access within the cycle, which could cause a memory stall cycle. It is therefore possible to almost completely eliminate the extra clock cycles spent on bit reversal, as we had with the naive algorithm. The only cycles we have to spend on bit reversal are those we need to reorder the first vector pair.

#### 2.4.3 Scatter-gather memory accessing

Another architectural enhancement that is currently under investigation, is to divide the vector memory into sixteen separate memory banks, which can be accessed in parallel. The programmer can specify per bank which element to fetch, thereby making it possible to fetch all desired elements in just one memory access. After the fetch it is still required to reorder the vector elements themselves in the right order, but that will then only take one full shuffle per vector.

<sup>&</sup>lt;sup>2</sup>For single precision data  $N_v = 16$  and we have  $\text{Log}_2$  16 = 4 intra-vector stages, whereas for double precision ( $N_v = 8$ ) the number of intra-vector stages is 3, hence the larger cycle count for single precision.

If we have such a so-called scatter-gather addressing method, we can perform the reordering of a vector pair in parallel with the butterfly computations of the previous pair, thereby eliminating the cycle count for bit reversal except for the cycles needed to reorder the first vector pair. For this to work the programmer has to make sure that the elements to be fetched for each vector all reside in different memory banks, in order to prevent bank conflicts. This requires a little extra effort by the programmer, but greatly reduces the number of cycles needed to reorder a vector of input data. If we can then reorder more than one vector pair during the intra-vector stages of a previous pair, it may even be possible to introduce some extra software pipelining by performing the inter-stage shuffles for one pair in parallel with the butterfly computations of another pair. This will be explored in section 2.4.5.

### 2.4.4 Single cycle full shuffle instruction

Another improvement would be if it were possible to perform a full shuffle in a single cycle instead of having to combine two half shuffles. Because there is large amount of shuffles that has to be performed during the intra-vector stages, this would result in a reasonable reduction of the cycle count for these stages.

We will take the cycle counts for the intra-vector stages given in section 2.4.2 as a starting point. For double precision data, since the intra-vector stages require a total of 12 full shuffles per vector pair, this would reduce the cycle count per vector pair by 12 (one cycle per shuffle), resulting in 32 instead of 44 cycles per pair. Since we have a N/16 of these pairs, this would result in a total saving of  $\frac{3}{4}N$ .

For the 8-bit case, things are somewhat more complicated. In this case the intra-vector stages require 16 full shuffles per vector pair. Therefore one would think that the cycle count for the intra-vector stages per vector pair would be reduced by 16, that is from 57 to 41. Having  $\frac{N}{32}$  vector pairs for a length N FFT, this amounts to a total saving of  $\frac{1}{2}N$  cycles.

However, in this case memory stalls can become the bottleneck. During the intra-vector stages we have to perform some line memory accesses to read the necessary shuffle patterns, as well as some to store the vector pair after having calculated the intra-vector stages. The number of line accesses needed adds up to 18 (16 read accesses for the shuffle patterns and two write accesses for the two resulting vectors after the intra-vector stages). Would we use the bit-reversed addressing method to reorder the next vector pair, this would cost another 32 (scalar) memory accesses. We would therefore have to do 50 memory accesses. Although the current architecture does allow a line and a scalar access to be issued in a single instruction, this would generally cause a stall cycle due to a cache miss. See [1] for more information. This would mean that for the single precision case, the full shuffle would only reduce the cycle count for the intra-vector stages from 57 to 50, which would be a total saving of  $\frac{9}{32}N$  instead of  $\frac{1}{2}N$ .

If we could use the scatter-gather memory accessing discussed in the previous section, we would only need 3 memory accesses in order to read the next vector pair, two for the actual input data and one for the shuffle pattern needed, which happens to be the same for

both input vectors. This would mean that having this banked memory architecture, we can reduce the cycle count for the intra-vector stages to 41 for the single precision case by introducing a full shuffle, because we have fewer memory accesses and therefore do not encounter stall cycles due to cache misses.

#### 2.4.5 Software pipelining

If we assume some of the proposed modifications to exist in the current CVP architecture, such as the scatter-gather addressing or some other efficient means to read input vectors in a bit-reversed manner withouth the use of the shuffle unit, and we also assume the single-cycle full shuffle and a sufficient number of SFU configurations registers, we can improve the FFT performance by introducing software pipelining. Software pipelining is the interleaving of instructions that operate on independant sets of data, so that operations that are dependant for one data set can be scheduled in parallel with those for the other data set, thereby avoiding the data dependencies.

For the intra-vector stages we can pipeline the arithmetic operations on one vector pair with the inter-stage shuffles of another pair, thereby interleaving two vectorized butterflies which together cost less clock cycles than by computing them sequentially. Because we assume an efficient means to read the input in a bit-reversed order, we will not take into account the bit reversal in the schedule. A schedule for this pipeline is depicted in figure 7. In this schedule operations on two independant sets of data are pipelined. For the sake of readability these operations are denoted using different colors. Besides the use of color, also a number is appended to the instruction indicating the data set it operates on.

The inter-vector stages can be optimized further by introducing a pipelined multiply-scale instruction. This instruction would perform a regular multiplication, followed by a scale by the desired amount. It should furthermore offer the possibility to initiate another ALU or MAC instruction in the next cycle. This is currently not allowed, but from a hardware point of view (in particular the number of read and write ports to and from the AMU register file) there is no compelling reason not to allow this. By having such an instruction we could pipeline the butterflies for the inter-vector stages in such a way that an entire vector butterfly (two vectors input, two vectors output) can be performed in only 3 cycles. See figure 8 for the resulting schedule.

However, for larger FFT sizes it is impossible to maintain all intermediate results in the AMU register file. It is therefore necessary to store these intermediate results in the vector memory. This adds up to five memory accesses per vector butterfly (two read accesses for the two input vectors, one for the vector of twiddle factors and two write accesses for the output vectors). This degrades the possible performance from 3 to 5 cycles for a vectorized butterfly. The FFT lengths where this extra pipelining for the inter-vector stages is beneficial is  $N \le 64$  for  $N_v = 8$  and  $N \le 128$  for  $N_v = 16$ .

| VMU          |           | AMU          |         |           | SFU                                           |         |

|--------------|-----------|--------------|---------|-----------|-----------------------------------------------|---------|

| send/receive | receive1  | receive2     | vopcode | receive   | config                                        | shuffle |

|              |           |              |         |           | <u>, , , , , , , , , , , , , , , , , , , </u> |         |

| SENDL1       |           |              |         |           |                                               |         |

| SENDL1       | RCV1(VMU) | )            |         |           |                                               |         |

|              | RCV1(VMU) | )            |         |           |                                               |         |

|              |           | ,            | SUB1    |           |                                               |         |

| SENDL2       |           |              | ADD1    | RCV1(AMU) |                                               |         |

| SENDL2       | RCV2(VMU  | )            | SUB1    | RCV1(AMU) |                                               | FULL1   |

|              | RCV2(VMU  | )            | ADD1    | RCV1(AMU) |                                               | FULL1   |

|              | RCV1(SFU) |              | SUB2    | RCV1(AMU) |                                               | FULL1   |

|              |           |              | ADD2    | RCV2(AMU) |                                               | FULL1   |

|              | RCV1(SFU) |              | SUB2    | RCV2(AMU) |                                               | FULL2   |

|              |           |              | ADD2    | RCV2(AMU) |                                               | FULL2   |

|              | RCV2(SFU) |              | MUL1    | RCV2(AMU) |                                               | FULL2   |

|              |           |              |         |           |                                               | FULL2   |

|              | RCV2(SFU) |              | SUB1    |           |                                               |         |

|              |           |              | ADD1    | RCV1(AMU) |                                               |         |

|              |           |              | SUB1    | RCV1(AMU) |                                               | FULL1   |

|              |           |              | ADD1    | RCV1(AMU) |                                               | FULL1   |

|              | RCV1(SFU) |              | MUL2    | RCV1(AMU) |                                               | FULL1   |

|              |           |              |         |           |                                               | FULL1   |

|              | RCV1(SFU) |              | SUB2    |           |                                               |         |

|              |           |              | ADD2    | RCV2(AMU) |                                               |         |

|              |           |              | SUB2    | RCV2(AMU) |                                               | FULL2   |

|              |           |              | ADD2    | RCV2(AMU) |                                               | FULL2   |

|              | RCV2(SFU) |              | MUL1    | RCV2(AMU) |                                               | FULL2   |

|              |           |              |         |           |                                               | FULL2   |

|              | RCV2(SFU) |              | ASRA1   |           |                                               |         |

|              |           |              | SUB1    |           |                                               |         |

|              |           |              | ADD1    | RCV1(AMU) |                                               |         |

|              |           |              | SUB1    | RCV1(AMU) |                                               | FULL1   |

|              | 1         |              | ADD1    | RCV1(AMU) |                                               | FULL1   |

| RCVL1(SFU)   |           |              | MUL2    | RCV1(AMU) |                                               | FULL1   |

|              |           |              |         | 1         | <del></del>                                   | FULL1   |

| RCVL1(SFU)   |           |              | ASRA2   |           |                                               |         |

|              | 1         |              | SUB2    |           |                                               |         |

|              |           | Sec. 1 (10)  | ADD2    | RCV2(AMU) |                                               |         |

|              |           | ············ | SUB2    | RCV2(AMU) |                                               | FULL2   |

|              |           |              | ADD2    | RCV2(AMU) |                                               | FULL2   |

| RCVL2(SFU)   |           |              | · ·     | RCV2(AMU) |                                               | FULL2   |

| (0, 0)       |           |              |         | 1222      |                                               | FULL2   |

| RCVL2(SFU)   |           |              |         |           |                                               |         |

Figure 7: Schedule for the radix 2 intra-vector stages

| AMU       |         |         |  |  |  |  |

|-----------|---------|---------|--|--|--|--|

| receive   | ALU     | MAC     |  |  |  |  |

|           |         | MULcdi1 |  |  |  |  |

|           |         |         |  |  |  |  |

|           |         | MULcdi2 |  |  |  |  |

| RCV1(AMU) | ADDcdi1 |         |  |  |  |  |

| RCV1(AMU) | SUBcdi1 |         |  |  |  |  |

|           |         | MULcdi3 |  |  |  |  |

| RCV2(AMU) | ADDcdi2 |         |  |  |  |  |

Figure 8: Schedule for the radix 2 inter-vector stages

#### 2.4.6 Radix 4 FFT

As illustrated in the previous section, we can introduce extensive software pipelining, that would allow us for the inter-vector stages to compute an entire vectorized butterfly in only 3 clock cycles, but memory overhead prohibits this for larger FFT sizes. In order to cope with this problem we will look into radix 4 FFT algorithms. In these algorithms the number of butterflies that are computed is less, but the computation of the butterflies themselves is more complex. It is therefore reasonable to assume that the memory accesses will not form the bottleneck and that we might obtain a higher utilization of the available computational power offered by the CVP.

In a radix 4 FFT algorithm the input (for decimation in time algorithms) or output sequence (decimation in frequency) is decomposed into successively smaller sequences by iteratively deviding the sequence into four subsequences until we end up with N/4 four-point DFT. Therefore the length of the input sequence has to be an integer power of four.

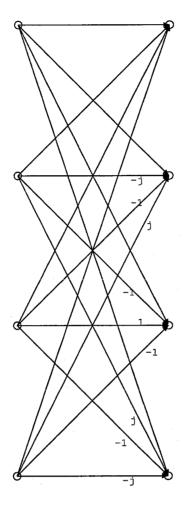

The radix 4 decomposition is discussed in [3], section 9.6. For N=16 the flow graph corresponding to the radix 4 decimation in time algorithm is depicted in figure 9. The branch multipliers within the butterflies have been omitted for the sake of readability. For the same reason, only one butterfly was drawn for the second computation stage. The multipliers for any radix 4 butterfly can be found in figure 10.

A naive vectorization of the Radix 4 algorithm A first vectorization attempt of the radix 4 algorithm is similar to that of the radix 2 version. Since the vectorized algorithm processes butterflies consisting of four vectors at once, we assume  $N \geq 4N_v$ . Since N also has to be a power of 4, N has to be at least 64. As was the case with radix 2 decomposition, we now too distinguish between intra- and inter-vector stages. We will now also have to shuffle the vectors after each of the intra-vector stages before moving on to the next computation stage. The number of intra-vector stages depends on the vector size. For a vector size  $N_v$  the number of intra-vector stages is equal to  $\lceil \text{Log}_4 N_v \rceil$ . For  $N_v = 8$  the shuffle pattern to be used is depicted in figure 11.

Figure 9: Flow graph for a 16 point radix 4 FFT algorithm

Figure 10: Butterfly for a 4-point DFT

Figure 11: The shuffle pattern for radix 4 FFT

Besides the shuffling after each of the intra-vector stages, we also have to shuffle the input data in the correct order prior to computation. For radix 2 implementation, this order was bit-reversed, for radix 4 it is base-four reversed.

For the actual algorithm we make the same assumptions as for the radix 2 implementation with respect to the twiddle values. They are assumed to reside in memory, correctly ordered in vectors, prior to computation. The pseudo-code for the radix 4 algorithm is as follows.

```

I

doBase4Reverse()

; stage := 1

;do stage \leq \lceil \text{Log}_4 N_v \rceil \rightarrow

butterfly := 1

;do butterfly \leq \frac{N}{4N_{v}} \rightarrow

computeButterfly()

; butterfly := butterfly + 1

od

; shuffle()

; stage := stage + 1

od

;do stage \leq \text{Log}_4 N \rightarrow

butterfly := 1

;do butterfly \leq \frac{N}{4N_v} \rightarrow

computeButterfly()

; butterfly := butterfly + 1

od

; stage := stage + 1

od

```

The function computeButterfly is given by

```

;tmp2 := W_2 \times X_2

;tmp3 := W_3 \times X_3

;tmp4 := X_1 \times [j, j, j, j, j, j, j]

;tmp5 := X_3 \times [j, j, j, j, j, j, j, j]

;tmp6 := X_0 + tmp2

;tmp7 := X_0 - tmp2

;M[&X_0] := tmp6 + tmp1 + tmp3

;M[&X_1] := tmp7 - tmp4 + tmp5

;M[&X_2] := tmp6 - tmp1 - tmp3

;M[&X_3] := tmp7 + tmp4 - tmp5

```

The calculation of the memory addresses &  $X_0$  through &  $X_3$  is done using the ACUs.  $W_0$  through  $W_3$  are the vectors containing the correct twiddle values for this stage. If we look at this implementation of the butterfly computations roughly, we see that each vectorized butterfly takes five multiplications, three of which (those with the twiddle factors) need to be scaled afterwards, five additions and five subtractions. The memory accesses (seven read and four write accesses) can be performed in parallel. This amounts to a total of 18 cycles per four-vector butterfly per stage for single precision data and 23 cycles for double precision.<sup>3</sup>

In the radix 2 algorithm, the total number of butterflies to be calculated is four times the number of butterflies for the radix 4 algorithm. Since the number of cycles per vectorized radix 4 butterfly is roughly four times as high as for the radix 2 algorithm, this does not seem to be a big improvement. However, if we implement the computation of the radix 4 butterfly in a different way and introduce some software pipelining, we can improve the radix 4 algorithm such that it outperforms the radix 2 version.

A more efficient implementation The radix 4 butterfly depicted in figure 10 can be computed in a different way, as depicted in figure 12. This reduces the number of multiplications by -j. These multiplications can also be eliminated by using the shuffle unit for this and compensating for the negated imaginary part in a later addition or subtraction.<sup>4</sup>

As mentioned earlier, for the inter-vector stages we will take four input vectors at once to produce four output vectors. We shall call this a vectorized butterfly, so in fact a vectorized butterfly involves  $N_v$  scalar butterflies. The pseudo code for computing a single vectorized butterfly is as follows.

I

<sup>&</sup>lt;sup>3</sup>For the radix 2 case we did not distinguish between single and double precision, because there the memory accesses were the bottleneck in computing a single butterfly.

$<sup>^{4}(</sup>a+bj)*(-j) = b-aj$

Figure 12: Alternative flow graph for the radix 4 butterfly

```

X_0 := M[\&X_0]

;X_1 := M[\&X_1]

; X_2 := M[\&X_2]

;X_3:=M[\&X_3]

;W_1 := M[\&W_1]

;W_2 := M[\&W_2]

; W_3 := M[\&W_3]

;X_1:=X_1\times W_1

; X_2 := X_1 \times W_2

; X_3 := X_1 \times W_3

;tmp0 := X_1 + X_3

;tmp1 := X_1 - X_3

;tmp2 := X_0 + X_2

;tmp3 := X_0 - X_2

;tmp4 := shuffle(tmp1, conf)

;X_0:=tmp2+tmp0

;X_1 := tmp2 - tmp0

; X_2 := MACdi(tmp3, tmp4, sign)

X_3 := MACdi(tmp3, tmp4, -sign)

;M[\&X_0]:=X_0

;M[\&X_1]:=X_1

;M[\&X_2]:=X_2

;M[\&X_3]:=X_3

```

For the scheduling of the code for the inter-vector stages we make the same assumption as in the previous section. We assume that there exists a multiply-scale instruction and that it is allowed to initiate a new ALU or MAC instruction in the next cycle. We again assume the existence of a single-cycle full shuffle, but now the current number of two configuration registers suffices. Based on these assumptions it is possible to schedule butterfly computations for the inter-vector stages such that we can compute an entire vector butterfly (four vectors input, four vectors output) in 14 clock cycles. See figure 13 for the pipelined schedule.

| VMU          |           | AMU       |         |         |           | SFU    | · · · · · · · · · · · · · · · · · · · |

|--------------|-----------|-----------|---------|---------|-----------|--------|---------------------------------------|

| send/receive | receive1  | receive2  | ALU     | MAC     | receive   | config | shuffle                               |

| SENDL1       |           |           |         |         |           |        |                                       |

| SENDL1       | RCV1(VMU) |           |         |         |           |        |                                       |

| SENDL1       | RCV1(VMU) |           |         |         |           |        |                                       |

| SENDL1       | RCV1(VMU) |           |         | MULcdi1 |           |        |                                       |

| SENDL2       | RCV1(VMU) |           |         | MULcdi1 |           |        |                                       |

| SENDL2       |           | RCV2(VMU) |         | MULcdi1 |           |        |                                       |

| SENDL2       | RCV1(AMU) | RCV2(VMU) | ADDcdi1 | ٠       |           |        |                                       |

| SENDL2       | RCV1(AMU) | RCV2(VMU) | SUBcdi1 |         |           |        |                                       |

| SENDL2       | RCV1(AMU) | RCV2(VMU) | SUBcdi1 |         | RCV1(AMU) |        |                                       |

| SENDL2       | RCV1(AMU) | RCV2(VMU) | ADDcdi1 |         |           |        | FULL1                                 |

| SENDL2       | RCV1(SFU) | RCV2(VMU) | ADDcdi1 |         |           |        |                                       |

| RCVL1(AMU)   |           | RCV2(VMU) | SUBcdi1 |         |           |        |                                       |

| RCVL1(AMU)   |           |           |         | MACdi1  |           |        |                                       |

|              |           |           |         | MACdi1  |           |        |                                       |

| RCVL1(AMU)   |           |           |         | MULcdi2 |           |        |                                       |

| RCVL1(AMU)   |           |           |         | MULcdi2 |           |        |                                       |

Figure 13: Schedule for the radix 4 inter-vector stages

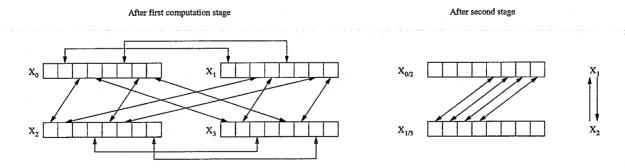

Furthermore we have two options regarding the computation of the intra-vector stages. The first approach is the one also used for the radix 2 algorithm and in the naive radix 4 implementation. In this approach we shuffle the values in such a way that we can use the same computation as for the inter-vector stages in order to compute a vectorized butterfly using four vectors as input and generating four output vectors. If we assume that the shuffling before the first stage is combined with the necessary digitreversal, we only need to perform some additional shuffling after each of the intra-vector stages. The shuffling pattern used is depicted in figure 11.

The schedule for the first stage is depicted in figure 14. From this schedule we can conclude that the first (intra-vector) stage will cost 22 cycles per four vectors. For the second stage, this approach only costs two full shuffles per vector. The schedule for the second stage is depicted in figure 15. From this schedule we can see that the second stage will cost 14 cycles per four vectors. In both schedules for the intra-vector stages, we assume that we have a sufficient number of SFU configuration registers.

We could also use a different shuffling approach for the intra-vector stages in order to reduce the required number of shuffles. For the first stage, assuming  $N_v = 8$ , a single vector contains the values needed to compute 2 (scalar) butterflies. Instead of shuffling values in such a way that we can compute an entire vectorized butterfly using 4 input vectors, we will now shuffle a single vector into two separate vectors in order to compute two scalar butterflies. For the inter-vector stages, we will still compute an entire vectorized butterfly at once, using four input vectors to produce four output vectors.

For this approach the algorithm for the intra-vector stages is as follows. For the first stage this code will compute 2 scalar butterflies at once. We will use the MAC instruction in order to do the necessary additions and subtractions. Since the multiplications involved in the MAC are all by 1 and -1, we can suffice with a real instead of a complex MAC.

| VMU          | AMU       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |        | SFU       |        |                                         |