| MASTER                                   |

|------------------------------------------|

| Vectorization of code generation in CDMA |

|                                          |

|                                          |

| Nas, R.J.M.                              |

| Award date: 2003                         |

|                                          |

|                                          |

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

# EINDHOVEN UNIVERSITY OF TECHNOLOGY Department of Mathematics and Computer Science

# MASTER'S THESIS

# Vectorization of Code Generation in CDMA

by R.J.M. Nas

Supervisor: prof. dr. C. H. van Berkel

Eindhoven, April 2003

# **Abstract**

This master's thesis presents the design of a flexible (i.e. re-configurable) and high throughput Code Generator Unit (CGU). The specific functions we look at are Pseudo Random Noise (PRN) generation, the closely related Hadamard and Orthogonal Variable Spreading Factor codes, and Cyclic Redundancy Check (CRC). The resulting CGU consists of functional units that perform these functions and a unit that combines the output of these functional units in a flexible way. The throughput of the CGU is limited by the throughput of its PRN generator. Our specific PRN generator is implemented by a Linear Feedback Shift Register (LFSR) and its high throughput is achieved by adapting it such that multiple sequence bits are generated in parallel, while keeping the circuits latency relatively low. Conventional parallel implementations of an LFSR have a latency that scales linearly with the amount of parallelism. We use a mathematical model of a parallel LFSR and prove the existence of a factorization of the next-state function for this LFSR. This factorization is the specification of a design with a latency that scales logarithmically with the amount of parallelism in the LFSR. Implementation (down to transistor level) of this specification is straightforward; a specific instance, an LFSR of length 32 generating 16 bits in parallel every clock cycle, was implemented using standard cells and the resulting circuit runs at over 300 Mhz. in 0.18 micron technology. This equates to a throughput of approx. 5 Gb/s. The design is also fully and on-the-fly re-configurable. The CGU's initial target application area is Third Generation Mobile Communications (3G), because of the project context in which this research took place. There are multiple other applications that can benefit from a high throughput LFSR as well, such as the Global Positioning System (GPS), CRC, cryptography (encryption/decryption) and Built-In Self-Test, both test vector generation and signature analysis.

# **Table of contents**

| Pr | eface           |                                                                 | vii      |

|----|-----------------|-----------------------------------------------------------------|----------|

| G: | lossar          | у                                                               | viii     |

| 1  | Intro           | oduction                                                        | 1        |

| -  | 1.1             | Scope                                                           | 1        |

|    | 1.2             | 3G wireless communication                                       |          |

|    | 1.3             | CDMA                                                            |          |

|    | 1.4             | Co-Vector Processor                                             |          |

|    |                 |                                                                 |          |

| 2  |                 | olem Description                                                | 7        |

|    | 2.1             | Assignment                                                      |          |

|    | 2.2             | Previous work                                                   | 7        |

| 3  | CGI             | J Overview                                                      | 9        |

|    | 3.1             | Requirements                                                    | 9        |

|    | 3.2             | Detailed Specification                                          | 10       |

|    | 3.3             | Architecture Overview                                           |          |

|    | <b>X</b> 7 4    | - in the of I in any Feedback Chift Degisters                   | 15       |

| 4  | <b>vect</b> 4.1 | orization of Linear Feedback Shift Registers  LFSR introduction | 15<br>15 |

|    | 4.2             | Fibonacci LFSR Vectorization.                                   |          |

|    | 4.2             | 4.2.1 First solution: Direct implementation                     |          |

|    |                 | 4.2.2 Second solution: Offline $F^{W}$                          | 17       |

|    | •               | 4.2.3 Third solution: Online $F^W$                              | 18       |

|    |                 | 4.2.4 Fourth solution: Factorized $F^W$                         | 10       |

|    |                 | 4.2.5 p <sub>i</sub> expressions                                | 19<br>24 |

|    |                 | 4.2.6 Conclusion                                                | 27<br>25 |

|    | 4.3             | Galois LFSR Vectorization                                       | 26       |

|    |                 |                                                                 |          |

| 5  |                 | Generator                                                       | 29       |

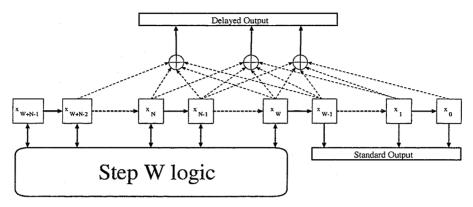

|    | 5.1             | Delayed Sequence Generation                                     | 29       |

|    | 5.2             | LFSR Resizing                                                   | 31       |

|    | 5.3             | CRC and Signature Analysis                                      | 32       |

|    | 5.4             | Sequential Multi-step LFSR                                      |          |

|    | 5.5             | Quaternary Codes                                                | 37       |

| 6  | CGU             | Architecture                                                    | 39       |

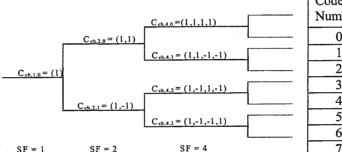

|    | 6.1             | Hadamard/OVSF Code Generator                                    |          |

|    | 6.2             | Table Look-Up functionality                                     |          |

|    | 6.3             | Code Combiner                                                   |          |

|    | 6.4             | Programming Model                                               | 47       |

| 7  | Conc            | clusions                                                        | 49       |

| •  | 7.1             | Accomplishments                                                 | 49       |

|    | 7.2             | Future work                                                     | 49       |

| Bi | ibliog          | raphy                                                           | 51       |

|    |                 |                                                                 |          |

| Aj |                 | lixLemma 4.1                                                    |          |

|    |                 | Lemma 4.1                                                       | 23       |

| Lemma 4.2 | 53 |

|-----------|----|

| Lemma 4.3 | 54 |

| Lemma 5.1 |    |

| Lemma 5.2 |    |

#### **Preface**

This document is my Master's thesis and is the result of a graduation project to obtain the degree of Master of Science in Computer Science with a specialization in Parallel Systems. Most of the work has been performed in de Embedded Systems Architectures on Silicon (ESAS) group at Philips Research in Eindhoven.

This document describes my work on the design of the Code Generation Unit for a programmable, multi standard, Third Generation (3G) wireless communication solution Philips is working on. As such, this documents intended audience has a technical background and is interested in wireless communication.

I would like to thank: Kees van Berkel for his excellent supervision at Philips Research, Rob Takken for his help with several VHDL and synthesis related issues and Daniel Timmermans, Edwin Rijpkema and the members of the ESAS coffee club in general for their help, idea's and interesting discussions that were not necessarily all related to my work. Finally I would like to thank Henk van Tilborg from the Eindhoven University of Technology for his help in understanding, and attempt at dealing with, quaternary Pseudo Random Noise (PRN) sequences.

Rick Nas, Eindhoven, February 2003

# **Glossary**

3G Third Generation

BIST Built-In Self Test

C/A Coarse/Acquisition

CDMA Code Division Multiple Access

CGU Code Generation Unit

CRC Cyclic Redundancy Check

CVP Co-Vector Processor

DS-CDMA Direct Sequence CDMA

DSP Digital Signal Processor

FDMA Frequency Division Multiple Access

GPRS General Packet Radio Service

GSM Global System for Mobile Telecommunications

GPS Global Positioning System

IC Integrated circuit

ISA Instruction Set Architecture LFSR Linear Feedback Shift Register

LUT Look Up Table

Mbps Mega bits per second

MHz Mega hertz

OVSF Orthogonal Variable Spreading Factor

PRN Pseudo Random Noise

SA Signature Analysis

SF Spreading Factor

SIMD Single Instruction Multiple Data

SW-MODEM Software Modem

TD-SCDMA Time Division Synchronous CDMA

TDD-CDMA Time Division Duplex CDMA

TDMA Time Division Multiple Access

TLU Table Look-Up

TU/e Technische Universiteit Eindhoven (Eindhoven University of Technology)

UMTS Universal Mobile Telecommunications System

VLIW Very Long Instruction Word VLSI Very Large-Scale Integration

### 1 Introduction

In this section we introduce several concepts and technologies that are relevant to the context of the assignment discussed in this document. More topics that need to be introduced will follow, but these are quite specific and we will save their introduction until they become relevant.

#### 1.1 Scope

This document is written as a graduation report for the Eindhoven University of Technology (TU/e) and as a research report for Philips Research Laboratories Eindhoven. The context of this assignment is the Software Modem project (SW-MODEM). The aim of the project is to design a low-cost software modem that can support multiple Third Generation (3G) wireless standards as well as the evolution of these standards. More specifically, to design a fully programmable domain-specific co-processor that, together with a conventional "scalar" micro controller or digital signal processor:

- Supports all base-band processing for 3G wireless standards;

- Supports the evolution of these standards by means of software upgrades;

- Is low costs, i.e. has a competitive silicon footprint.

#### 1.2 3G wireless communication

As the successor to Global System for Mobile Telecommunications (GSM, 2G) and General Packet Radio System (GPRS, 2.5G), the third generation mobile radio system is supposed to finally bring broadband Internet access to mobile phones around the world. Broadband, packet-based transmission of text, digitized voice, video, and multimedia at data rates up to and possibly higher than 2 Mbps will be become possible. Different 3G standards have been proposed and several have found acceptance somewhere in the world. The Universal Mobile Telecommunications System (UMTS) is expected to become the prevailing standard in Europe, while the United States seem to be going with CDMA2000 and China is developing Time Division Synchronous Code Division Multiple Access (TD-SCDMA).

While there are certainly differences between these standards, they have at least one important characteristic in common: Wideband Code Division Multiple Access (W-CDMA) has emerged as the mainstream air interface solution for the third generation networks.

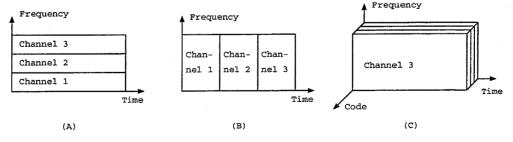

"Multiple Access" indicates that the common transmission medium is shared between users of the system. There are basically three multiple access schemes, which are illustrated in figure 1.1 [1]

Figure 1.1 Multiple Access schemes: (A) FDMA, (B) TDMA and (C) CDMA.

Introduction 1

There are also hybrid schemes, like TD-CDMA, where multiplexing is still achieved with CDMA, but TDMA is used to duplex the uplink and downlink of a signal on the same frequency band.

#### 1.3 CDMA

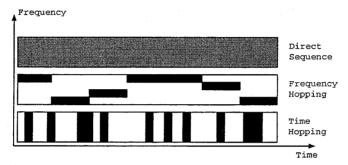

In CDMA multiple access is achieved by assigning each user a pseudo-random sequence (codeword). Pseudo-random indicates that the codes are not truly random, but deterministically generated and reproducible with an algorithm. The pseudo-random sequence is then used to transform the user's signal into a wide band spread spectrum signal. This transformation is usually achieved in one of three different ways. In frequency hopping spread spectrum the codeword defines the transmission frequency. In time hopping spread spectrum the codeword defines the transmission moment. Finally, in Direct Sequence (DS)-CDMA the information signal is multiplied by the codeword, which results in a wideband signal. DS-CDMA is the technique used in 3G. These three different techniques are illustrated in figure 1.2 [1].

Figure 1.2 Direct sequence, frequency hopping and time hopping CDMA.

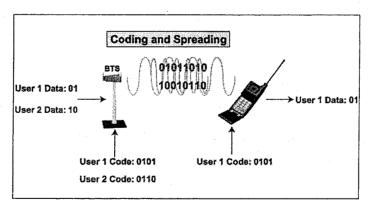

On the receiving side of the transmission the same sequence is generated. The sequence is then used to extract the user's signal from the received signal by either listening (to the right frequency) at the right time, or by correlating the sequence with the received signal and thereby lifting the user's signal above the noise. DS-CDMA is illustrated in figure 1.3 [2]

Figure 1.3 Coding en Spreading in CDMA.

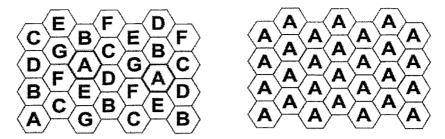

CDMA has several important advantages over T(ime)DMA and F(requency)DMA, the most important of which are universal frequency reuse, power control and rake receiver. Below we give a short description of these three advantages.

In both TDMA and FDMA neighboring cells in the network cannot use the same set of frequencies because otherwise users in different cells would interfere with each other. In

CDMA users are separated by code channels, not frequency channels and therefore each cell in the network has access to the entire frequency band. Universal frequency reuse is illustrated in figure 1.4 [2].

Figure 1.4 Frequency use in TDMA/FDMA versus CDMA.

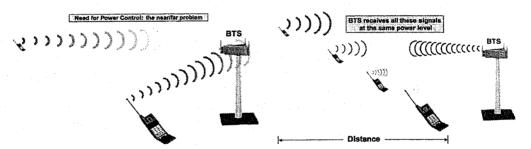

Power control is a feature that enables mobiles to adjust the power at which they transmit. This ensures that the base station receives all signals at an appropriate power. The CDMA network determines, for each mobile individually, the power at which it should transmit its signal. If all mobiles transmitted at the same power level, the base station would receive unnecessarily strong signals from mobiles nearby and extremely weak signals from mobiles that are far away, which is know as the near-far problem. As a result the capacity of the system would be reduced because it is no longer possible to lift weak signals above the strong signals through correlation. Power control is a necessary technique that solves this problem and has the added benefit that a mobile never uses too much power to send a signal, thus reducing power usage. Power control is illustrated in figure 1.5 [2]. It should be noted that Power control is not unique to CDMA; GSM also has power control, but there it is not as crucial to the correctness of the technique.

Figure 1.5 Using power control to solve the near-far problem.

Introduction 3

A rake receiver is a CDMA feature that turns what is a problem in other technologies into an advantage for CDMA. Signals sent over the air can take a direct path to the receiver, or they can bounce off objects and then travel to the receiver. These different paths, called multi-paths, can result in the receiver getting several versions of the same signal but at slightly different times. Multi-paths can cause a loss of signal through cancellation in other multiple access schemes. CDMA's rake receiver implements multiple receivers in one. The rake receiver identifies the strongest multi-path signals and combines them to produce one very strong signal. A rake receiver therefore uses multi-path to reduce the power at which the transmitter must send. A rake receiver is illustrated in figure 1.6 [2].

Figure 1.6 Using a rake receiver to solve the multi-path problem.

Besides these advantages there are a couple of advantages that are inherent to spread spectrum modulation. Because a signal is spread across a wide frequency band it looks like random low energy noise to anyone who is trying to listen but doesn't have the right codewords. This makes it harder for anyone to either eavesdrop on the signal or to scramble it by sending high-powered signals at certain frequencies.

All these benefits do not come for free however. Spreading a signal with DS-CDMA and extracting a specific signal from the ether on the receiving end is no easy task and all in all CDMA-reception is a very computationally intensive technique. On a conventional DSP enhanced with some specific instructions, UMTS would require between 3 and 5 billion operations per second of computing power, an order of magnitude more than any current Digital Signal Processor (DSP) can deliver. Solving this by just harnessing the power of several DSPs is not a very economical solution and using task specific hardware accelerators in combination with a conventional DSP makes for a very standard specific architecture. What we are looking for is an architecture that is both fast and flexible enough to handle several different standards. The SW-MODEM project is developing the Co-Vector Processor (CVP) with that goal in mind.

#### 1.4 Co-Vector Processor

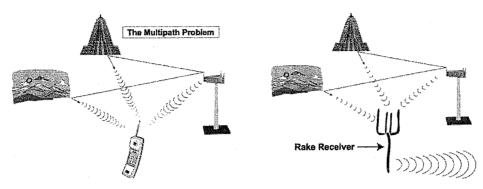

Using the terms loosely, the CVP can be described as a Very Long Instruction Word (VLIW) Single Instruction Multiple Data (SIMD) processor. The SIMD is the most obvious, because as the name says, the CVP is operating on vectors of arguments. VLIW comes from the fact that every instruction for the CVP actually consists of instructions for each of its functional units. Figure 1.7 [3] shows the CVP embedded in the Software Modem (SW-MODEM) architecture. This figure also shows that the CVP is in fact a coprocessor to a conventional DSP or micro-controller.

Figure 1.7 CVP in the SW-MODEM architecture.

The idea behind the SW-MODEM project is that, assuming a high enough clock speed and vector width and the possibility of vectorizing a large percentage of the algorithms that play a role in CDMA, this architecture is capable of delivering the computational power that is required by CDMA.

Inside the CVP we find a vector memory and several functional units. These functional units perform functions like shifting and shuffling vectors and inter- or intra-vector arithmetic. Besides these functional units there is the Code Generation Unit (CGU), which is responsible for generating the pseudo-random sequences we spoke of earlier and several other codes that we will come to speak of. The design of the CGU is the topic of the rest of this document.

Introduction

# 2 Problem Description

# 2.1 Assignment

The initial goal of this project is the design of a high speed, flexible (i.e. multi standard) CDMA code generation unit. This description consists of several sub goals.

First we need to investigate several speed aspects of the CGU. Because of the vector nature of the CVP, the CGU will need to be capable of generating an entire vector full of code-sequence elements (chips) every clock cycle, in order to use the full width of the data path. In the current design of the CVP this means that we need to generate 16 chips every clock cycle. Second, because of the high load some of the CDMA kernels have on the CVP, the clock rate of the chip is ideally around 300 MHz (in 0.12 micron CMOS technology). This speed is most likely unattainable without some clever design decisions. Finally, when specifying an Instruction Set Architecture (ISA) for the CGU, instruction latencies, introduced by for example pipeline stages, should be kept to a minimum, to avoid latency penalties after a state change or re-configuration instruction.

A second, more implicit, sub goal of the project is to list applications and application standards that use the codes like the ones in CDMA and see if the CGU is relevant to them. A subset of these applications is then selected and a specification of the CGU's minimum functionality is then derived from their standards. Of principle interest are the three prevalent 3G standards: UMTS, CDMA2000 and TD-SCDMA. Besides these we will look at the Global Positioning System (GPS) and a seemingly completely unrelated application: Cyclic Redundancy Check (CRC) and Signature Analysis (SA).

Besides being a vector processor, a second important characteristic of the CVP is its programmability. This programmability significantly enlarges the application domain of the CVP. Obviously the programmability of the CVP is limited by the flexibility of its functional units. In the CGU we will try to achieve high flexibility by supporting, in hardware, a set of functions that is more or less shared among the different applications in the target application domain. Some of these functions will be configurable in order to compensate for small differences between applications. The functions we will look at include: Linear Feedback Shift Registers and Hadamard Code generation. With such an architecture we hope to support large parts of different standards and applications in hardware and solve remaining differences in software.

#### 2.2 Previous work

The design described in this document is not the first attempt at designing the CGU. Previously, Tom Geelen, a student from the TU/e, designed a CGU as his internship assignment at Philips Research in 2001 [4,5]. This version of the CGU implemented some of the required features like vector generation of codewords and some of the required configuration possibilities, but it was to slow. Tom Geelen estimated that at a vector width of 8 his design could be made to run at around 100 MHz (in 0.18 micron technology) and this figure would drop dramatically when going to the preferred vector width of 16. Also, the approach he took at vectorizing Pseudo Random Noise (PRN) sequence generation turned out to have been patented by IBM in 1995 [6]. It doesn't lend itself very well for high clock speeds, so it is unlikely that Tom Geelen's design can be easily adapted to run at the required clock speed of 250-300 MHz. Instead, we will have to take an entirely new approach, which is an important topic in this document.

Problem Description 7

### 3 CGU Overview

In this section we present the initial high-level architecture and in subsequent sections we elaborate on the implementation of its various elements. Obviously this initial design has to be based on some requirements, which we define in the next paragraph.

## 3.1 Requirements

We base the functional requirements of the CGU on the specification documents of several 3G standards and other applications that fit well on the CGU.

On of the most important characteristics of the CVP is that it will be programmable for several different 3G standards. However, targeting all of the 3G standards at the first try would be a bit over ambitious, so we decide to focus our main attention on UMTS.

#### **UMTS**

UMTS will initially be the most important application for the CVP and it provides ample opportunities to add and test the flexibility to the design. Code generation for UMTS is specified in [9]. This documents introduces and specifies several different codes and how these are combined with each other and the data signal.

#### Other 3G standards

The 2 other prevailing 3G standards are TD-SCDMA in China and CDMA2000 in the US. Ultimately, the CVP and thus the CGU will be compatible with these standards, but for now this is not a top priority. We occasionally look at parts from their respective specifications [12 and 13] to see where adjustments to the design are needed to accommodate these standards.

#### GPS

The Global Positioning System uses a network of earth orbiting satellites to enable a GPS-receiver to determine its position on earth. The one-way communication between the satellites and the receiver uses CDMA as its multiple access scheme, which makes it a potential target application for the CVP. Consumer electronics use the coarse mode [10,11] (C/A-mode) of GPS, which has an implementation that is almost completely compatible with UMTS.

#### CRC and SA

Signature analysis, as used in CRC and built-in self-tests for integrated circuits (IC) use hardware that is very similar to the hardware that we use to generate some of the codes required for UMTS. A big difference with CMDA is that CRC and SA process an input stream and only occasionally produce output. This requires that the CGU be fitted with a port for this input stream. Requirements for CRC and SA in Very Large-Scale Integration (VLSI) are presented in [7,8].

Besides these functional requirements, there are also some practical requirements that come from the operational context of the CVP. First of all, since we are designing flexible hardware, we will introduce configuration parameters that define the exact operation of a functional unit. These parameters can be used to specify a specific mode of operation or to supply the CGU with rarely changing constants, which would otherwise have to be included in, for example, the instruction-word. The ability to configure these parameters introduces requirements for both the i/o-interface of the CGU and its ISA. The CVP is a VLIW co-processor, which means that the CGU, as a separate functional unit, will have

CGU Overview 9

its own ISA. Furthermore, the CVP uses multitasking to be able to handle several different tasks in parallel. Multi-tasking implies task switching, which requires the ability to save/restore the state of the entire CVP and thus also of the CGU. Saving/restoring the state of the CGU will add a couple of instructions to the ISA and it also imposes some requirements on the i/o-interface.

# 3.2 Detailed Specification

Initially, the CGU will support UMTS, GPS and CRC and SA. All these applications have very detailed specifications [9, 10/11 and 7/8 respectively], but for the CGU only the specifications of the required codes are important. We will now give a list of these codes, with some explanation.

| Name                                             | e Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C <sub>sig,SF,s</sub>                            | This is a Hadamard code. The length of the code, also called the spreading factor (SF) determines how many codewords there are, and the argument s specifies which of these SF codewords is needed. The argument s is part of the configuration for the unit that generates this code. The output of the functional unit should be a vector of elements from the C <sub>sig,SF,s</sub> code.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| C <sub>ch,SF,n</sub>                             | This is an Orthogonal Variable Spreading Factor (OVSF) code. It is very similar to the Hadamard code, and will be generated by the same unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| C <sub>long</sub> ,1,n<br>C <sub>long</sub> ,2,n | $=(x_n(i)+y(i))(0,1:=1,-1)\\ =(x_n(i+16777232)+y(i+16777232))(0,1:=1,-1)\\ x_n: G(x)=X^{25}+X^3+1\\ y: G(x)=X^{25}+X^3+X^2+X+1$ These two are both the sums of two Pseudo Random Noise (PRN) sequences $x_n$ and $y$ , which are generated by a Linear Feedback Shift Register (LFSR). These LFSRs are specified by two generator polynomials $G(x)$ , which are both part of the configuration of the unit that generates them. The code-number $x_n$ specifies the initial state of the generator unit. Notice $x_n$ is a delayed version of $x_n$ . The amount of delay is determined by two more polynomials, which are both also part of the configuration for the unit that generates these codes. The output of the functional unit should be two vectors of elements, one for each of these two codes.                                           |  |  |

| C <sub>short,1,n</sub><br>C <sub>short,2,n</sub> | =(a(i)+2b(i)+2d(i))(0,1,2,3 := 1,-1,-1,1) =(a(i)+2b(i)+2d(i))(0,1,2,3 := 1,1,-1,-1) a: G(x) = X <sup>8</sup> +X <sup>5</sup> +3X <sup>3</sup> +X <sup>2</sup> +2X+1 //Quaternary code b: G(x) = X <sup>8</sup> +X <sup>7</sup> +X <sup>5</sup> +X+1 d: G(x) = X <sup>8</sup> +X <sup>7</sup> +X <sup>5</sup> +X <sup>4</sup> +1  c <sub>short,1,n</sub> and c <sub>short,2,n</sub> are very similar to the two c <sub>long</sub> codes. In this case however, we are summing not two but three PRN codes, one of which, a, is not a binary, but quaternary code. This means that every chip can have four different values instead of two. Again we see some generator polynomials, which will be part of the configuration. The code-number n specifies the initial state of the generator. Again, the output will be two vectors of sequence elements. |  |  |

| $Z_{\mathrm{n}}$                                 | $= (x(i) + y(i))(0,1 := 1,-1)$ $x: G(x) = X^{18} + X^7 + 1$ $y: G(x) = X^{18} + X^{10} + X^7 + X^5 + 1$ $Z_n \text{ is basically the same as the } c_{long} \text{ codes, except for different configuration}$ parameters. Note that we will also need a delayed version of $Z_n$ , just like we saw with $c_{long,2,n}$ , but this is again part of the configuration of the functional unit that will generate this code.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| GPS C/A-<br>code                                 | =G1(t) + G2(t + i)<br>G1: $G(x) = X^{10} + X^3 + 1$<br>G2: $G(x) = X^{10} + X^9 + X^8 + X^6 + X^3 + X^2 + 1$<br>The GPS code that we need to support is the sum of a PRN sequence and a delayed version of a PRN code. We saw this before, only with different configuration parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

Besides these codes, there are several codes that further combine the codes we just introduced into complex valued sequences, which are the final output of the CGU. Note, that in some cases the above codes are not combined any further and become the final output of the CGU themselves.

| Name                                                                                                                                                                                | Specification                                                                                                                                                                                                                                                                                                                       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $S_{dl,n}(k)$                                                                                                                                                                       | $=Z_n(k) + j Z_n(k + 131072)$                                                                                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                     | $S_{dl,n}$ combines a normal and a delayed version of the $Z_n$ code we just saw.                                                                                                                                                                                                                                                   |  |

| $ \begin{vmatrix} C_{\text{pre},n,s}(k) \\ C_{\text{c-acc},n,s}(k) \\ C_{\text{c-cd},n,s}(k) \end{vmatrix} = c_{\text{long},1,n}(k) * C_{\text{sig},s}(k) * e^{j(\pi/4 + k\pi/2)} $ |                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                     | This combination is a bit more complex than the previous one. The multiplication is used is introduced to work more easily with complex values. To facilitate this, the binary sequences that are used are first mapped to the real values $\{-1,1\}$ . The multiplication with the power of $e$ makes the sequence complex valued. |  |

| C <sub>long,n</sub> (k)<br>C <sub>short,n</sub> (k)                                                                                                                                 | $=c_{long,1,n}(k)*(1+j(-1)^{k}*c_{long,2,n}(2*\lfloor k/2 \rfloor))$ $=c_{short,1,n}(k)*(1+j(-1)^{k}*c_{short,2,n}(2*\lfloor (k/2 \rfloor))$ Again a combination that maps binary valued sequences onto the complex domain. Note how not all the elements from the $c_{long,2,n}$ code are actually used.                           |  |

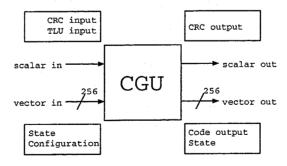

The UMTS standard defines some more codes, but these are only other names for the same codes, to be used in different circumstances. The above codes specify the CGU requirements with respect to UMTS and GPS. The third application that we decided to implement is CRC and SA. This application is different that UMTS and GPS, in that it doesn't generate a code-sequence, but instead consumes one. This requires that the functional unit that implements CRC can receive input. CRC output only occurs after a complete input code-sequence has been consumed. The output of the CRC unit will be a scalar. Internally, a CRC unit is implemented with a LFSR, which is specified by a generator polynomial that will be part of the configuration for the CRC unit.

#### 3.3 Architecture Overview

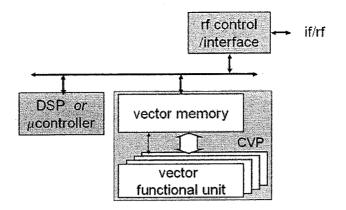

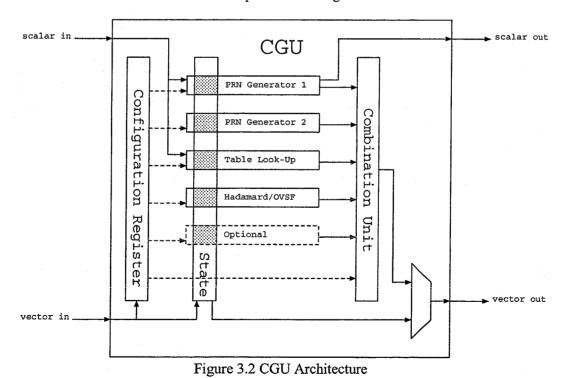

The CGU will be a functional unit of the CVP. The CVP has two different data-paths: a vector data-path and a scalar data-path. Figure 3.1 shows a black-box model of the CGU, with its interfaces, together with an overview of what information uses which data-path.

Figure 3.1 Black-box model of the CGU

The scalar path is used to supply the input sequence of which a CRC signature needs to be calculated. Once this signature is calculated, the CGU outputs it over the scalar path. We could have used the vector port for this output, but that provided no extra value. The vector input is used to read configuration parameters from the vector memory. It is also used to read in a state vector after a context switch. The difference between state and configuration is that configuration vectors are constants that change very rarely and certainly not every context switch, while state vectors are very variable and are

CGU Overview 11

saved/restored every context switch. Since the configuration parameters aren't changed by the CGU, we never need to save them. The state on the other hand does change and therefore we need the vector output to save it when a context switch occurs. The actual output of the CGU, the generated codeword, is also sent over the vector output port. We could have used the scalar in and output ports to load and save state and configuration. However, the scalar path is not wide enough to send all the state or all the configuration data in one packet. So, sending this information over the scalar path would require several clock-cycles, which introduces an unnecessary latency.

The specifications of the codes that we need to support shows that the actual output of the CGU is a combination of several basic codes that may or may not be from the same type.

Looking at the specification, we see that we need a Hadamard/OVSF Code Generator to generate the so-called channelisation and synchronization codes. The detailed design of the Hadamard/OVSF Code Generator is presented in paragraph 6.1.

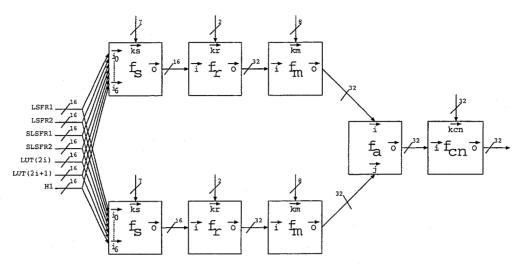

Looking further we see that a very important class of codes in both UMTS and GPS (but also in TD-SCDMA and CDMA2000) is the class of PRN sequences, specifically the ones generated by an LFSR. The design of these PRN Generators turned out to be by far the most challenging topic of this project and we will come to speak of them in detail in chapters 4 and 5. The parallel generation of several PRN sequences requires the inclusion of at least 2 of these PRN Generators.

Finally, for added flexibility we add Table Look-Up (TLU) functionality to the architecture, giving us the possibility to use codes for which we are not prepared to design dedicated hardware. The TLU table will be located in the Vector Memory Unit (VMU), and we decide to use the scalar input to retrieve values from this memory for use in the CGU. TLU-functionality and a situation, occurring in UMTS, that uses it is presented in paragraph 6.2. With this information we can fill in the black-box from Figure 3.1. This more detailed architecture is presented in Figure 3.2.

This architecture clearly shows how the TLU-functionality is implemented over the scalar path. It also shows how one of the PRN Generators can receive input from and generate output for the scalar path; this is used to implement the required CRC/SA functionality.

Both PRN Generators could be extended to provide this functionality, but we choose not to, for sake of simplicity.

All functional units, including the Code Combiner have access the configuration vector. The state vector is distributed over the functional units. Note however that the Code Combiner is stateless. The design of the Code Combiner is discussed in paragraph 6.3.

The modular nature of this design makes it easy to add new or extra code generators to the design. They can simply be added and their output needs to be connected to the Code Combiner in the required way. Looking at for example CDMA2000 it seems likely that another Hadamard Generator is needed to generate some of the required codes. How this extra generator is used in CDMA2000 can then be reflected in changes made to the Code Combiner.

In the next chapter we take a detailed look at Linear Feedback Shift Registers, the basis for the design of the PRN generators.

CGU Overview

# 4 Vectorization of Linear Feedback Shift Registers

#### 4.1 LFSR introduction

In CDMA a specific class of PRN sequences is used, namely the class of sequences generated by the recurrence relation

$$x_{i} = \sum_{j=1}^{N} g_{N-j} x_{i-j}$$

$i = N, N+1, N+2, ...$  (4.1)

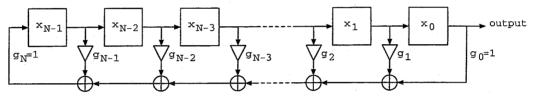

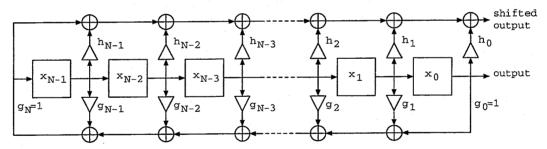

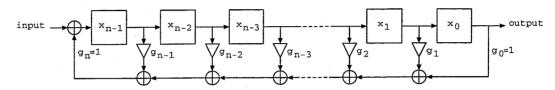

where,  $x_i \in \{0,1\}$  are output sequence digits;  $x_0...x_{N-1}$  represents an "initial state";  $g_0...g_{N-1}$  are given constants and the summation sign represents addition modulo 2. While this form of sequence generation can also be performed in other finite fields, we will assume GF(2) in the rest of this document, unless explicitly stated otherwise. A major advantage of this generation method is the simplicity of its implementation. The hardware of a generator that functions in accordance with expression (4.1) comprises only an N-bit shift register and a set of modulo-2 adders to generate feedback. The resulting circuit is called a Linear Feedback Shift Register (LFSR). There are two basic ways to implement an LFSR. The so-called Fibonacci implementation (Figure 4.1) consists of a simple shift register in which a binary-weighted modulo 2 sum of the register values (taps) is fed back to the input. The register taps are represented with a triangle and the weighing factor; a crossed circle represents addition.

Figure 4.1 Fibonacci LFSR

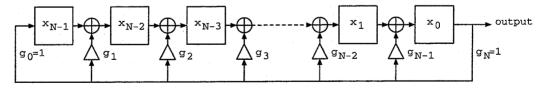

The Galois implementation (Figure 4.2) consists of a shift register, the contents of which are modified at every step by a binary-weighted value of the output stage. A Galois LFSR has a lower latency than an equivalent Fibonacci LFSR because all additions can be performed in parallel, whereas in a Fibonacci LFSR, the additions can merely be balanced, resulting in a logarithmic evaluation time. Galois LFSRs are generally faster than Fibonacci LFSRs and because of this Tom Geelen used them in his design of the CGU [4,5].

Figure 4.2 Galois LFSR

These two implementations will produce the same PRN sequence if configured with the same weights and the appropriate, but different, initial states. Because of this, an LFSR is usually identified by only its weights, as a binary string or in the form of a generator polynomial:

$$G(x) = g_n X^n + g_{n-1} X^{n-1} + g_{n-2} X^{n-2} + \dots + g_2 X^2 + g_1 X + g_0$$

$$(4.2)$$

LFSRs have a firm mathematical basis and one of their properties is that if G(x) is primitive, the produced sequence will have a cycle length of  $2^n - 1$ , which is called an M-

sequence, or Maximum Length Sequence. In CDMA we will mainly be looking at M-sequences. Also note that a sequence generated by an n-bit LFSR will never contain a so-called "run" of n or more zero's in succession. This fact is most easily verified by looking at a Fibonacci LFSR. Because the content of a Fibonacci LFSR equals the next n bits in its output sequence, a run of n zero's implies that the register is filled with all zeros. However, it is easily verified that once the register is filled with all zeros, it can never produce even a single one anymore. There is one exception to this rule and that is when the register is initially filled with zeros, in which case the register produces only zeros. For a more thorough treatment of LFSRs, M-sequences and their properties we refer to the standard works on these subjects [7,8].

Different implementations of an LFSR can be compared on several different criteria. First of all there are two criteria that are important to any hardware design: speed and area.

As for speed, or more precisely, cycle time: the combinatorial logic in an LFSR design consists of mostly AND-gates (which implement binary multiplication) and XOR-gates (which implement binary addition). Therefore, we define the cycle time of a design to be the number of 2-input AND-gate delays measured in  $D_{and}$  and the number of 2-input XOR-gate delays, measured in  $D_{xor}$ . An AND-gate delay is not the same as a XOR-gate delay, so a real comparison can only be made when we assign weights to these two measures. We will do so at the end of paragraph 4.2, when we draw some conclusions. For area we will use the same metric as for speed; we count the number 2-input AND gates and the number of 2 input XOR-gates, measured in  $A_{and}$  and  $A_{xor}$  respectively.

There is a third criterion that is important in a hardware design: power consumption. This criterion is quite difficult to determine at a high level and a good estimate requires careful simulation. For this reason we will mention power consumption only if there is especially striking opportunity to gain an advantage in this area.

A criterion that we will consider is the number of configuration bits required to configure the design. Normally we only have the N configuration bits from the generator polynomial, but we will see an approach that gains an area and speed advantage at the cost of extra configuration bits.

#### 4.2 Fibonacci LFSR Vectorization

As said before, the CGU is designed to operate on vectors of arguments. For this reason the CGU has to generate a vector full of chips every clock cycle. In the remainder of this document we will call the vector width W and the LFSR length N. An LFSR of length N generating W chips (values) every clock cycle will be called an N/W-LFSR.

There are two aspects to generating code words in vectors. First, every clock cycle, W chips have to be derived from the state of the LFSR. Second, every clock cycle, the state has to be advanced by W chips. We will look at both of these aspects.

For a Fibonacci LFSR, the first aspect is almost trivial. At any time, the state of a Fibonacci LFSR consists of the next N output chips. So, as long as  $W \le N$ , we can just take the next W output chips straight from the state of the LFSR. The UMTS standard also uses sequences that are generated with an LFSR that is shorter than the preferred vector width of 16 chips, so W > N. This could present a problem, because in such a case we would like to output more chips than have actually been generated. However, we will deal with this problem and for now we assume that W is always smaller than N (which will turn out to be the case). So, in the case of a Fibonacci LFSR, the output, which we call Z, equals (for now)  $[x_0, ..., x_{P-1}]^T$ .

In the following we look at several methods to advance the state of the register by W. We compare these methods with the criterion introduced in the previous paragraph.

#### 4.2.1 First solution: Direct implementation

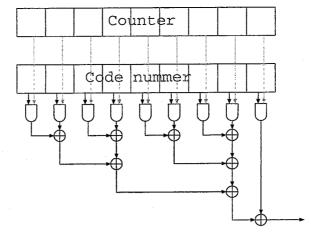

The first method that we look at is the method used by Tom Geelen in his work on the CGU [4,5]. Tom Geelen used the combinatorial logic of multiple (W) cascaded LFSRs to advance the state of one LFSR by W (Figure 4.3).

Figure 4.3 Direct implementation of a Fibonacci LFSR with step-size 3.

The main disadvantage of this solution is the cycle time of the resulting circuit. We highlighted two additions in the figure: one horizontal and one vertical. The values for the horizontal addition are all immediately available, so this addition 'tree' can be rebalanced to get a logarithmic (in N) evaluation-time. However, the vertical addition requires values that are not available yet and this addition has to be evaluated linearly. Because of this the cycle time of the design increases linearly with the step-size W. More precisely, the cycle time of this design equals:  $(\lceil 2 \log N \rceil + W - 1) D_{xor} + (W) D_{and}$ .

The size of the design is easy to determine; it is simple equal to W times the size of a standard LFSR:  $(W * N) A_{and} + (W * (N-1)) A_{xor}$ . Finally, no extra bits are required to configure the design, only the N bits from the generator polynomial.

## 4.2.2 Second solution: Offline $F^{W}$

As the start of our second approach, we first create a mathematical model of an LFSR.

The state of the register at timestamp t is denoted by the vector X(t).

$$X(t) = \begin{pmatrix} x_0 \\ x_1 \\ \vdots \\ x_{N-2} \\ x_{N-1} \end{pmatrix} (t) \tag{4.3}$$

The values  $g_0...g_{n-1}$  determine the feedback pattern of the LFSR and they depend on the generator polynomial. ( $g_0$  is usually equal to 1.) The elements of X(t+1) are all a linear combination of the elements in X(t), therefore, mathematically, shifting the register is equivalent to multiplying the state with a matrix that depends on  $g_0...g_{n-1}$ . This matrix is called the characteristic matrix of the LFSR.

$$F = \begin{pmatrix} 1 & & & \\ & \ddots & & \\ & & 1 \\ g_0 & g_1 & \cdots & g_{N-1} \end{pmatrix}$$

$$\tag{4.4}$$

Because of the sparse nature of the matrices we will be working with, 0-elements are omitted.

With these definitions, making a single step with the LFSR can be expressed as:

$$X(t+1) = F \cdot X(t) \tag{4.5}$$

We can generalize expression (4.5) to advance X(t) by W steps:

$$X(t+W) = F \cdot F \cdot \dots \cdot F \cdot X(t) \tag{4.6}$$

And finally, because matrix multiplication is associative, we also have:

$$X(t+W) = F^{W} \cdot X(t) \tag{4.7}$$

A symbolic evaluation of  $F^W$  in expression (4.7) results in a matrix in which the last W rows contain expressions that depend on  $g_0...g_{n-1}$ . As a second solution to the problem of advancing X(t) by W steps we could choose to introduce a configuration bit for each of these expressions, giving us a matrix filled with  $N^*W$  configuration bits. Advancing the state of the register is now a simple matter of multiplying X(t) by a scalar matrix. To find the required configuration bits, we need to calculate the expressions offline for given  $g_0..g_{N-1}$ . This would result in a very fast solution, because we only have to hardwire a matrix-vector multiplication, which can be implemented as the parallel evaluation of dot-products. A dot product only takes  $1 D_{and} + \lceil 2 \log N \rceil D_{xor}$ , which is a lot less then the previous solution. The solution requires the same amount of hardware; one dot product takes  $(N) A_{and} + (N-1) A_{xor}$ , so W dot products in parallel takes  $(W^*N) A_{and} + (W^*(N-1)) A_{xor}$ .

The problem with this solution is twofold: First of all, the solution is less flexible; on-the-fly re-configuring is only possible for a known set of  $g_0...g_{N-1}$ , for which we can store the configuration bits in a memory. This might not be a problem in practice for current standards, but it might be for future standards. Secondly, the solution requires far more configuration bits than the standard N from the generator polynomial. The required number of bits in this case is  $W^*N$ , making it scale linearly with W, instead of being constant with respect to step-size. These extra bits increase the memory requirement and possibly the time required to configure the design, because retrieving that many bits from a memory probably requires several steps.

#### 4.2.3 Third solution: Online $F^W$

In order to limit the configuration bits to just  $g_0...g_{n-1}$  we have to evaluate the expressions in  $F^W$  on the fly. The symbolic evaluation of  $F^W$  for even a relatively small 8/8-LFSR shows that the expressions in  $F^W$  grow to enormous length as W increases. To illustrate this we look at one column from  $F^W$ , for a LFSR of length 8, as W increases:

$$F^{1}[4] = \begin{pmatrix} 0 \\ 0 \\ 0 \\ 1 \\ 0 \\ 0 \\ 0 \\ g_{4} \end{pmatrix}$$

This clearly shows that the size of the expressions in  $F^W$  grows super linear as W increases. In fact, further practical tests suggest that the size of the expressions in  $F^W$  is  $O(W^2)$ . For UMTS we are looking at 32/16-LFSRs and in large instances like that the size and shear number of these expressions becomes a bottleneck in hardware size. If we assume that the average length of the expressions in  $F^W$  grows quadratically with W then a rough estimate for the hardware required for  $F^W$  is  $O(N^*W^3)$ )  $A_{xor} + O(N^*W^3)$ )  $A_{and}$ . Similarly, an estimate for the latency of this solution is  $O(^2\log{(N^*W^2)}) D_{xor} + O(1) D_{and}$ , which is based on the knowledge that the expressions in  $F^W$  can be evaluated in parallel. Finally, we only need  $g_0...g_{N-1}$  to configure a design based on this solution.

# 4.2.4 Fourth solution: Factorized $F^{W}$

To reduce the hardware requirements of the previous solution we will try to transform the expressions in  $F^W$  into a functionally equivalent form that requires much less hardware and evaluates just as fast. In particular, we would like to identify sub-expressions that occur numerous times in  $F^W X(t)$ . To this end we look at an 8/8-LFSR. The operation of an 8/8-LFSR is modeled by:

$$X(t+8) = F \cdot X(x) \tag{4.8}$$

We can add some parentheses to force a right-to-left evaluation:

We will evaluate expression (4.9) and try to find a pattern as we go along. Starting with:

$$X (t) = \begin{pmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \\ x_6 \\ x_7 \end{pmatrix}$$

we multiply with F and get:

$$X (t+1) = \begin{pmatrix} x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \\ x_6 \\ x_7 \\ g_0 x_0 + g_1 x_1 + g_2 x_2 + g_3 x_3 + g_4 x_4 + g_5 x_5 + g_6 x_6 + g_7 x_7 \end{pmatrix}$$

If we compare X(t+1) with X(t) it is clear that, as expected in a shift register, the elements in X(t) shifted up one location and a new expression is inserted at the bottom. Since the same thing will happen when we multiply X(t+1) by F we substitute the bottom element in X(t+1) with identifier  $s_t$ . We multiply the resulting state by F again and get:

$$X(t+2) = \begin{pmatrix} x_2 \\ x_3 \\ x_4 \\ x_5 \\ x_6 \\ x_7 \\ s_1 \\ q_7 s_1 + q_0 x_1 + q_1 x_2 + q_2 x_3 + q_3 x_4 + q_4 x_5 + q_5 x_6 + q_6 x_7 \end{pmatrix}$$

This time, instead of replacing the entire last element by an identifier, we choose to only replace the part that is similar in form to  $s_1$ . The main reason for this is that replacing the entire first element by  $s_2$  would result in a nested set of identifiers, which would force a more sequential evaluation scheme, i.e. a less balanced addition tree, increasing the evaluation latency. Multiplying the resulting state with F two more times and performing substitutions were appropriate, we get:

$$X (t+4) = \begin{pmatrix} x_4 \\ x_5 \\ x_6 \\ x_7 \\ s_1 \\ g_7 s_1 + s_2 \\ (g_6 + g_7) s_1 + g_7 s_2 + s_3 \\ (g_5 + g_7) s_1 + (g_6 + g_7) s_2 + g_7 s_3 + s_4 \end{pmatrix}$$

The bottom elements in this vector are all a linear combination of s-terms, with repeating coefficients so we can rewrite the above expression into:

And because the identifiers  $s_i$  we introduced are a linear combination of the original state bits and the generator polynomial, we can rewrite this into:

In a similar fashion we can rewrite X(t+5) into:

where we introduced another set of identifiers  $p_i$ , to simplify the result even more.

The simple structure of the two matrices we introduced triggered us to propose the following theorem:

#### Theorem 1

$$F^W = P_W G_W \qquad , W \le N$$

where for given W and N

$$G_{i,j} = \text{if} \qquad (j-i=W) \qquad \Rightarrow \qquad 1$$

$$[] \qquad (i+j\geq N-1) \wedge (i\geq N-W) \qquad \Rightarrow \qquad g_{i+j-N+1}$$

$$[] \qquad \text{else} \qquad \Rightarrow \qquad 0$$

$$p_0 = 1$$

$p_i = \sum_{n=0}^{i-1} p_n g_{N-i+n}$

or, depicted schematically

$$P_{W} = \begin{pmatrix} 1 & & & & & \\ & \ddots & & & & \\ & & 1 & & & & \\ & & & p_{0} & & \\ & & & \ddots & \vdots & & \\ & & p_{0} & \cdots & p_{W-1} \end{pmatrix} \qquad G_{W} = \begin{pmatrix} & & 1 & & & \\ & & & \ddots & & \\ & & & & \ddots & \\ & & g_{0} & g_{1} & \cdots & g_{N-W} \\ & \ddots & \vdots & \vdots & & \vdots \\ g_{0} & \cdots & g_{W-1} & g_{W} & \cdots & g_{N-1} \end{pmatrix}$$

#### Proof of theorem 1

We prove the theorem by induction.

Base case: W = 1

$$F^1 = P_1 G_1$$

Substitution of W = 1 in the definitions of  $P_W$  and  $G_W$  shows that  $P_1$  is the identity matrix and  $G_1$  equals F, so for the base case the theorem holds.

# Induction step: $F^{W+1} = P_{W+1} G_{W+1}$

Using the induction hypothesis  $F^{W} = P_{W} G_{W}$  we try to prove  $F^{W+1} = P_{W+1} G_{W+1}$ .

$$F^{W+1}$$

$$\equiv \{\text{calculus}\}$$

$$FF^{W}$$

$$\equiv \{\text{induction hypothesis}\}$$

$$FP_{W} G_{W}$$

$$\equiv \{\text{lemma 4.1}: FP_{W} = Q_{W+1}\}$$

$$Q_{W+1} G_{W}$$

$$\equiv \{\text{lemma 4.2}: Q_{W+1} = P_{W+1} K_{W}\}$$

$$P_{W+1} K_{W} G_{W}$$

$$\equiv \{\text{lemma 4.3}: K_{W} G_{W} = G_{W+1}\}$$

$$P_{W+1} G_{W+1}$$

where for given W and N

For the proof of lemma's 4.1, 4.2 and 4.3 please see the appendix.

So, what was gained with these transformations? Both the speed and hardware size of this solution are harder to quantify then in the previous solution because of the  $p_i$ -factors. These  $p_i$ -factors are generated by a simple recurrence relation, but because we are working in GF(2), a lot of optimizations can be applied to the expressions afterwards, which makes it hard to find closed formulas for there latency and size. Below we have included the first 8 optimized  $p_i$ -factors.

```

p<sub>0</sub> = 1

p<sub>1</sub> = g<sub>15</sub>

p<sub>2</sub> = g<sub>14</sub> + g<sub>15</sub>

p<sub>3</sub> = g<sub>13</sub> + g<sub>15</sub>

p<sub>4</sub> = g<sub>12</sub> + g<sub>14</sub> + g<sub>15</sub> + g<sub>14</sub> g<sub>15</sub>

p<sub>5</sub> = g<sub>11</sub> + g<sub>15</sub> + g<sub>13</sub> g<sub>15</sub> + g<sub>14</sub> g<sub>15</sub>

p<sub>6</sub> = g<sub>10</sub> + g<sub>13</sub> + g<sub>14</sub> + g<sub>15</sub> + g<sub>12</sub> g<sub>15</sub> + g<sub>14</sub> g<sub>15</sub>

p<sub>7</sub> = g<sub>9</sub> + g<sub>13</sub> g<sub>14</sub> + g<sub>15</sub> + g<sub>11</sub> g<sub>15</sub>

```

Compared to the expressions in  $F^8$  we showed earlier, these expressions are quite simple. These first factors grow approximately linear in W so, if fully balanced, they evaluate in approximately  $\lceil 2 \log W \rceil D_{xor} + O(1) D_{and}$ . The multiplication  $G_W X(t)$  takes  $\lceil 2 \log N \rceil D_{xor} + 1 D_{and}$ , so in practical cases the  $p_i$ -factors can be evaluated in parallel with this first multiplication, which means we can disregard them in our latency evaluation. After the first matrix-multiplication, the multiplication with  $P_W$  takes another  $\lceil 2 \log W \rceil D_{xor} + 1 D_{and}$ , which puts the total for this solution at  $\lceil 2 \log N \rceil + \lceil 2 \log W \rceil D_{xor} + 2 D_{and}$ , which is approximately  $\lceil 2 \log N^*W \rceil D_{xor} + 2 D_{and}$ .

The size of this solution is more difficult to specify, because we can't disregard the  $p_i$  expressions here. The hardware required for the two matrix-multiplications can be easily derived from the definitions of the matrices.

Multiplication with  $P_W$  requires

$$\sum_{i=1}^{W-1} i = W\left(\frac{1}{2}W - \frac{1}{2}\right) \quad A_{and} \text{ and}$$

$$\sum_{i=0}^{W-2} i = W\left(\frac{1}{2}W - 1\frac{1}{2}\right) + 1 \quad A_{xor}$$

Multiplication with  $G_W$  requires:

$$\sum_{i=N-M+1}^{N} i = W\left(N - \frac{1}{2}W + \frac{1}{2}\right) \quad A_{and} \text{ and }$$

$$\sum_{i=N-W}^{N-1} i = W \left(N - \frac{1}{2} W - \frac{1}{2}\right) \quad A_{xor}.$$

This gives a total of  $(W^*N)$   $A_{and}$  +  $(W^*(N-2))$   $A_{xor}$ , exclusive the hardware in the  $p_i$  expressions. If we assume again that for practical cases  $p_i$  expressions grow linearly with W, this adds approximately  $\frac{1}{2}W^2$   $A_{xor}$  and  $A_{and}$  to the hardware requirements.

The number of configuration bits required for this solution equals N.

Finally, this solution has a third advantage that needs mentioning, namely in the area of power consumption. The  $p_i$ -factors that we introduced depend only on the generator polynomial and because this polynomial normally doesn't change during sequence generation, the values of the  $p_i$ -factors don't change either. This means that  $p_i$ -factors only need to be evaluated during the initial configuration of the generator and can then be clock-gated afterwards to save energy. This observation also reinforces our decision to exclude  $p_i$ -factors from the latency of the solution.

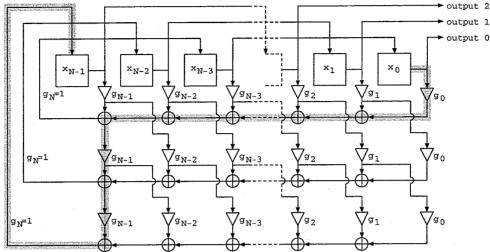

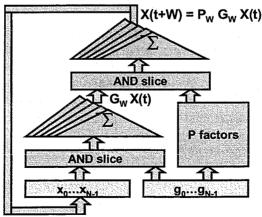

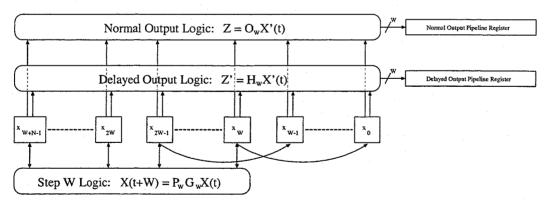

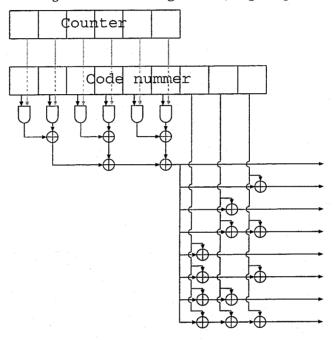

The final result of our transformations is a nice, concise and precise mathematical description of the hardware in an N/W-LFSR, which is both easy to instantiate for arbitrary N and W and easy to implement. A high-level schematic of this design is shown in Figure 4.4.

Figure 4.4. Factorized  $F^{W}$  schematic.

The schematic shows how the p<sub>i</sub> expressions only depend on the generator polynomial. The rest of the circuit consists of parallel, balanced addition trees preceded by a vector AND-operation that implement vector dot-products, which in turn implement matrix multiplication.

#### 4.2.5 $p_i$ expressions

In the previous paragraph we introduced the  $p_i$  expressions that were defined by

$$p_0 = 1$$

$p_i = \sum_{n=0}^{i-1} p_n g_{N-i+n}$

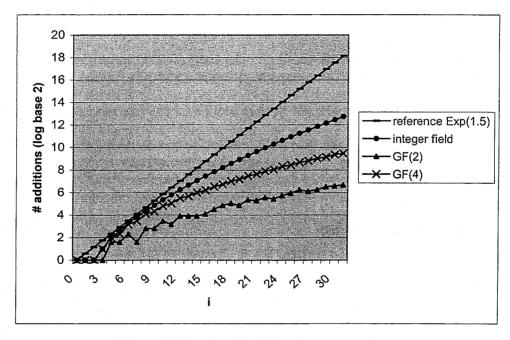

The summation in the definition might suggest that the size of these expressions will grow exponentially as i increases. However, experimental data suggests a linear relation, at least for small (practical) i. Figure 4.5 shows a graphical representation of the number of additions in the  $p_i$  expressions, when calculated in GF(2), GF(4) and the field of integers. As a reference we also added  $(1.5)^i$  to the graph.

Figure 4.5 Number of additions in  $p_i$  expressions

It is difficult to conclude whether or not the size of the expressions grows exponentially, based on such limited data. What we can say is that if it grows exponentially, it does so with a very small base. In the integer field, where very few optimizations are possible, the size grows exponentially in the beginning, but then seems to start flattening out. In both GF(2) and GF(4) the size grows much slower than the reference (1.5). This is because several very systematic optimizations can be performed on the expressions in these cases. Specifically, in GF(2), sub-expressions with an even coefficient can be removed completely, uneven coefficients are taken modulo 2 and exponents can be discarded. These optimizations are also the reason that the size of the expressions is not strictly increasing; some expressions just have more opportunity for optimization than others. There seems to be a pattern in when these decreases occur, but we don't have an explanation for this behavior.

In GF(4) there are similar types of optimizations. For example, sub-expressions with a coefficient that is a multiple of 4 can be discarded. Since completely removing a sub-expression is a very effective optimization, it is clear that binary LFSRs profit the most from these optimizations, at least in absolute terms.

If we look at the size of the expressions in GF(2) again, our assumption that it increases linearly in the beginning seems to be correct; the first 16 expressions range in size from 1

to 18 terms. After that the size starts to grow more quickly, perhaps quadratically, as the size ranges from 24 to 102 in the next 16 expressions. Still, these expressions aren't extremely complex and their latency grows slowly, so an LFSR with step-size 32 is not unthinkable.

As a final remark we can say that the number of multiplications in the  $p_i$  expressions grows approximately as fast the number of additions. However, multiplications are implemented with and-gates, which are a lot smaller than the XOR-gates that implement addition. So, the number of additions dominates the amount of hardware required to implement the expressions. Also, because all terms in a  $p_i$  expression can be evaluated in parallel, the evaluation latency of an expression is also mostly determined by the number of additions.

#### 4.2.6 Conclusion

We have seen four different approaches to advance the state of the LFSR by W bits. But only by factorizing  $F^W$ , were we able to designed a solution that scores well on all three important criteria. The following table gives an overview of the mentioned solutions and their score on the introduced criteria.

|                    | Costs                                                      | Latency                                                                                       | Config size | Remarks                                                            |

|--------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------|

| Direct             | (W*N) A <sub>and</sub><br>W*(N-1) A <sub>xor</sub>         | $(W) \ D_{and}$ $\lceil 2 \log N \rceil + W - 1 \ D_{xor}$                                    | N bits      |                                                                    |

| Offline F          | (W*N) A <sub>and</sub><br>W*(N-1) A <sub>xor</sub>         | $1 \ D_{and} \ \lceil^2 \! \log N \rceil \ D_{xor}$                                           | N*W bits    | <ul><li>high memory requirement</li><li>less flexibility</li></ul> |

| Online $F^W$       | $O(N^*W^3)$ $A_{and}$<br>$O(N^*W^3)$ $A_{xor}$             | O(1) $D_{and}$<br>O( $^2$ log ( $N^*W^2$ )) $D_{xor}$                                         | N bits      | <ul> <li>horrible to<br/>implement</li> </ul>                      |

| Factorized $F^{W}$ | ~W*(N+½W) A <sub>and</sub><br>~W*(N+½W-2) A <sub>xor</sub> | $ \begin{array}{ccc} 2 & D_{and} \\ \sim & \lceil 2 \log N * W \rceil & D_{xor} \end{array} $ | N bits      | <ul><li>vhdl: ~2.6 ns</li><li>clock gating opportunity</li></ul>   |

The last solution is by far the best. It is only marginally more expensive than the cheapest solution, while at the same time being one of the fastest solutions. Determining a good indication of exactly how fast a design is, is best left to a synthesis tool. Assigning weights to the delay of different types of gates is difficult because these values depend greatly on factors such as the drive-strength on the inputs and the required drive-strength on the output. Ballpark figures for a  $D_{xor}$  and a  $D_{and}$  are 0.30 ns and 0.20 ns respectively. Such ballpark figures for the size of these two gates are 40  $\mu^2$  and 20  $\mu^2$  for a  $A_{xor}$  and a  $A_{and}$  respectively. With these figures we can calculate another table, with practical data for a 32/16-LFSR.

|                    | Costs (µ²) | Latency (ns) |

|--------------------|------------|--------------|

| Direct             | 30080      | 9.2          |

| Offline F          | 30080      | 1.7          |

| Online F           | ~125000000 | 4.1 (1.7)    |

| Factorized $F^{W}$ | 37120      | 3.1          |

The "Offline  $F^{W}$ " approach still looks very good. However, it requires so many configuration bits that the design just isn't practical anymore. The fact that all these huge expressions need to be calculated offline isn't very intuitive and it is just a plain ugly solution.

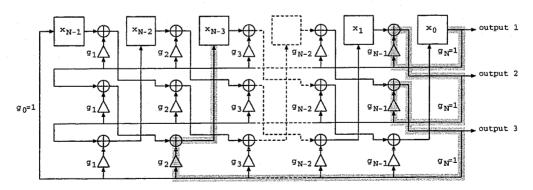

#### 4.3 Galois LFSR Vectorization

In this paragraph we will look at both aspects of vector generation of chips for a Galois LFSR. Unlike with a Fibonacci LFSR, the first aspect, deriving a vector of W chips from the current state of the register is not trivial. Only the very last element in the state occurs in the output sequence unaltered, all other elements change as they shift through the register. Because at every step a state element is only influenced by the elements with a lower index (i.e. closer to the output), we can derive the next W outputs from the last W state bits. We calculated the expressions that transform state bits into output bits and were able to express this transformation in a matrix-vector product again:

$$\begin{pmatrix} Z_0 \\ Z_1 \\ \vdots \\ Z_{W-2} \\ Z_{W-1} \end{pmatrix} = \begin{pmatrix} p_0 \\ p_1 & p_0 \\ \vdots & \vdots & \ddots \\ p_{W-2} & p_{W-3} & \cdots & p_0 \\ p_{W-1} & p_{W-2} & \cdots & p_1 & p_0 \end{pmatrix} \begin{pmatrix} x_0 \\ x_1 \\ \vdots \\ x_{W-2} \\ x_{W-1} \end{pmatrix}$$

That is surprising! The matrix is almost exactly  $P_W$  from the previous paragraph and with a small rewrite we find:

$$\begin{pmatrix} Z_0 \\ Z_1 \\ \vdots \\ Z_{W-2} \\ Z_{W-1} \end{pmatrix} = P_W \begin{pmatrix} x_{W-1} \\ x_{W-2} \\ \vdots \\ x_1 \\ x_0 \end{pmatrix}$$

So, we found a nice, clean way to transform the state bits into output chips. However, the fact that we need to do so might already indicate that Galois LFSRs are less well suited for vector generation of a sequence than Fibonacci LFSRs.

To advance the state of the register by W, we investigate how the solutions for a Fibonacci LFSR translate to a Galois LFSR.

In the first solution we cascaded to logic of several Fibonacci LFSRs. This direct implementation has an equivalent in the case of a Galois LFSR, which is depicted in Figure 4.5.

Figure 4.5 Direct implementation of a 3-step Galois LFSR.

A one-step Galois LFSR has a lower latency then a one-step Fibonacci LFSR and in a direct implementation this advantage translates to a multi-step LFSR. We highlighted the critical path of the circuit and it is clear that going to a multi-step LFSR adds approximately the same latency to a Galois LFSR as it does to a Fibonacci LFSR. This means that the absolute advantage of a Galois LFSR remains, but the relative advantage decreases. The latency of this direct implementation of a multi-step Galois LFSR is (W)

$D_{xor} + (W) D_{and}$ . The size of the LFSR equals that of a Fibonacci LFSR:  $W^*(N-1) A_{xor} + W^*(N-1) A_{and}$ . Configuring the design requires only N bits.

A Galois equivalent for the other three solutions from the previous paragraph requires the characteristic matrix F. In case of a Galois LFSR this matrix has the following form:

$$F = \begin{pmatrix} g_{N-1} & 1 & & \\ g_{N-2} & \ddots & & \\ \vdots & & 1 \\ g_0 & & & \end{pmatrix}$$

(4.10)

Advancing the state by one is again expressed by expression 4.5 from the previous paragraph:

$$X(t+1) = F \cdot X(t)$$

Expression 4.7 again expresses advancing the state by multiple steps.

$$X(t+W) = F^W \cdot X(t)$$

With these definitions there are Galois equivalents for the second and third solutions from the previous paragraph, which differ only in latency from these solutions.

A direct evaluation of  $F^W$  in case of a Galois LFSR results in a matrix in which in every row the first W elements are expressions that depend on  $g_0...g_{n-1}$ . Multiplying X(t) with this matrix results in the parallel evaluation of N expressions each having a time complexity of  $O(\log W)$ . In case of a Fibonacci LFSR multiplying X(t) with  $F^W$  results in the parallel evaluation of W expressions each having a time complexity of  $O(\log N)$ . So, assuming W < N, a Galois LFSR still has the potential of being faster than a Fibonacci LFSR, but this advantage theoretically decreases as W increases. As was the case with a Fibonacci LFSR, an ad hoc evaluation of  $F^W$  results in huge expressions that would require too much hardware to hardwire.

We haven't been able to find a factorization of  $F^W$  equivalent to the one we found in case of a Fibonacci LFSR. There is however a different factorization that wasn't possible for a Fibonacci LFSR because of latency issues. Because the latency of multiplying X(t) with  $F^W$  in the Galois case depends on W instead of N (in the Fibonacci case), we can replace  $F^W$  X(t) by  $F^{V_2W}$   $F^{V_2W}$  X(t), without immediately doubling the latency of the evaluation. This transformation has a very positive effect on the hardware requirements because the expressions in  $F^{V_2W}$  are a lot smaller than in  $F^W$  and they only have to be implemented once. Furthermore, the hardware required for the two smaller multiplications is actually a bit less then what is required for the single big multiplication.

The latency of the operation is affected in conflicting ways by this transformation. On the one hand, the expressions in  $F^{WW}$  are a lot smaller and thus evaluate faster than in  $F^{W}$ . On the other hand, the latency of the actual multiplications rises from  $1 D_{and} + \lceil 2 \log W \rceil D_{xor}$  to  $2 D_{and} + 2 \lceil \lceil 2 \log W \rceil D_{xor}$ . How these two effects interact is not exactly clear. We will assume that splitting  $F^{W}$  increases the latency of the operation, because we are forcing a specific evaluation order that might not be ideal. If the latency increases, then the splitting-transformation is a tradeoff between size and speed, something that is not uncommon in hardware designs. For the CGU, the optimum value in this tradeoff is where the CGU is not a latency bottleneck for the CVP and requires as little hardware as possible. We didn't investigate this tradeoff any further, because the solution doesn't seem to have any advantages over our solution for a Fibonacci LFSR. At the same time it

suffers from several annoying disadvantages, such as difficult instantiation for arbitrary W and N and extremely error prone implementation.

Concluding we can say that we weren't able to find a vectorized solution for a Galois LFSR that is as nice as the one we found for the Fibonacci LFSR. This is unfortunate, because theoretically a Galois LFSR still has a lower latency. In future work it might be a good idea to reinvestigate this issue.

## 5 PRN Generator

Pseudo Random Noise sequences are sequences of values that, for many intents and purposes, appear completely random, but are deterministically generated and reproducible with an algorithm. Two pseudo random sequences have the property that the similarity between them is very low, and not much higher than what would be statistically expected from two completely random sequences. The similarity between two sequences is also called the cross-correlation. Another property of a pseudo random sequence is that two instances of the same sequence are only similar if there is no phase difference between them, as would be expected from a completely random sequence. The similarity of two instances of the same sequence is also called auto-correlation. The good cross- and auto-correlation properties of PRN sequences are what make them well suited for DS-CDMA, because they make it possible to extract a specific user's signal from the received signal, while ignoring the rest.

The LFSR that we designed in the previous chapter forms the basis of our PRN generator. In this chapter we will enhance the functionality of this design so that it is flexible enough to implement all the requirements from paragraph 3.2.

### 5.1 Delayed Sequence Generation