| Eindhoven University of Technology                                                         |

|--------------------------------------------------------------------------------------------|

|                                                                                            |

| MASTER                                                                                     |

| Analysis and design of automatic discrete frequency control for high-frequency oscillators |

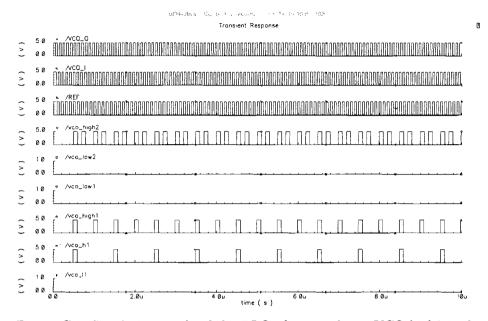

|                                                                                            |

| de Jongh, M.A.                                                                             |

| Award date: 2003                                                                           |

|                                                                                            |

| Link to publication                                                                        |

|                                                                                            |

|                                                                                            |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Eindhoven University of Technology Department of Electrical Engineering Mixed-signal Microelectronics

### Analysis and Design of Automatic Discrete Frequency Control for High-Frequency Oscillators

M.A. de Jongh

November 20, 2003

### Master of Science Thesis

Project period: October 2002 - November 2003 Department: Mixed-signal Microelectronics (MsM)

Supervisors:

dr. ir. J. v.d. Tang

Prof. dr. ir. A.H.M. van Roermund

The Department of Electrical Engineering of the Eindhoven University of Technology accepts no responsibility for the contents of M.Sc. Theses or practical training reports

#### Abstract

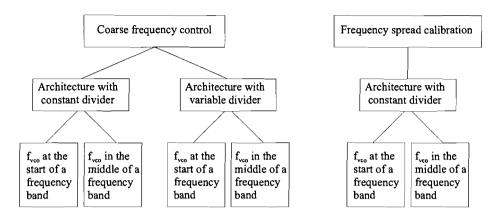

This thesis presents an analysis and design of automatic discrete frequency control systems for band-switched oscillators: An automatic frequency control (AFC) system must select the appropriate frequency band of an oscillator with several frequency bands. Automatic frequency control systems are divided into two types of systems: course frequency control (CFC) and frequency spread calibration (FSC) systems. In brief, CFC systems change frequency bands during operation and FSC systems select the appropriate frequency band at start-up. The main aim of this thesis are systems without any interference on sensitive analog points within the phase-locked loop (PLL).

Literature study has proven that all digital AFC systems, which rely on the reference clock and (digital) feedback signal in the PLL, are the most promising option. Furthermore, most presented systems use an open-loop and closed-loop step of the PLL. Therefore, two additional methods setting the phase-locked loop in an open-loop condition by means of switches in the digital part of the PLL are introduced.

The class of all digital AFC systems is subdivided into architectures using a variable divider ratio and architectures using a constant divider ratio. In addition, two types of digital frequency detectors are discussed: based on a counter or a digital logic quadricorrelator (DLQ). In particular, the DLQ combines minimum complexity with minimized measurement time per frequency measurement cycle.

In order to select the appropriate frequency band, generic frequency band requirements and selection criterions are developed for various detection scenarios. The selection criterions are illustrated with an example of a linear search algorithm, that uses these criterions.

The concept of a reduced division ratio in a variable divider CFC architecture is introduced. In this report, the reduction of the divider ratio decreases the necessary measurement time roughly by a factor of 7. A settling-time of less than  $16\mu$ s can be achieved by combining the reduced division ratio with the digital frequency difference detector based on the DLQ.

Three CFC systems and one FSC system are designed with Verilog behavioral models in Cadence. This work shows that all digital AFC systems, which are not interfering with sensitive points within the PLL can be realized. No major problems are expected by conversion of the simulated AFC systems into actual implementations with digital circuits, as long as the frequency bands of the VCO meet the necessary frequency band requirements.

# Contents

| 1 | Vol | tage co | ntrolled oscillator                                       | 11 |

|---|-----|---------|-----------------------------------------------------------|----|

|   | 1.1 | Oscilla | tor properties                                            | 12 |

|   | 1.2 | Freque  | ncy Bands                                                 | 13 |

|   |     | 1.2.1   | Switch-selected tuning                                    | 13 |

|   |     | 1.2.2   | Band positioning                                          | 14 |

|   | 1.3 | LC osc  |                                                           | 15 |

|   |     | 1.3.1   | Frequency of oscillation                                  | 15 |

|   |     | 1.3.2   | Band-switches                                             | 16 |

|   |     | 1.3.3   | 4.5-7GHz LC oscillator for course frequency control       | 16 |

|   |     | 1.3.4   | 5.1-6.7GHz LC oscillator for frequency spread calibration | 18 |

|   | 1.4 | Summa   | ary                                                       | 19 |

| 2 | Pha | so-lock | ted loop                                                  | 20 |

|   | 2.1 |         | -N PLL architecture                                       | 20 |

|   | 2.2 |         | -pump PLL                                                 | 21 |

|   | 2.2 | 2.2.1   | Phase-frequency detector                                  | 21 |

|   |     | 2.2.2   | Charge-pump                                               | 24 |

|   |     | 2.2.3   | Loop filter                                               | 24 |

|   |     | 2.2.4   | Simulation results                                        | 25 |

|   |     | 2.2.5   | Open-loop condition                                       | 27 |

|   | 2.3 |         | ary                                                       | 30 |

|   |     |         |                                                           |    |

| 3 |     |         | requency control                                          | 31 |

|   | 3.1 |         | frequency control                                         | 31 |

|   | 3.2 |         | ncy spread calibration                                    | 31 |

|   | 3.3 |         | of-the-art                                                | 32 |

|   |     | 3.3.1   | Used architectures                                        | 32 |

|   |     | 3.3.2   | Band search algorithms                                    | 35 |

|   |     | 3.3.3   | Example implementations                                   | 35 |

|   |     | 3.3.4   | Overview                                                  | 38 |

|   | 3.4 | All dig | ital dual-loop topology                                   | 39 |

|   | 3.5 | Freque  | ncy detection                                             | 40 |

|   |     | 3.5.1   | Frequency counter                                         | 40 |

|   |     | 3.5.2   | FDD based on digital logic quadicorrelator                | 46 |

|   | 3.6 | Summa   | arv                                                       | 48 |

| 4                | Free                            | quency band requirements                              | 49 |  |  |  |  |  |

|------------------|---------------------------------|-------------------------------------------------------|----|--|--|--|--|--|

|                  | 4.1                             |                                                       | 49 |  |  |  |  |  |

|                  | 4.2                             | Coarse frequency control                              | 50 |  |  |  |  |  |

|                  |                                 | 4.2.1 Two-band VCO example                            | 51 |  |  |  |  |  |

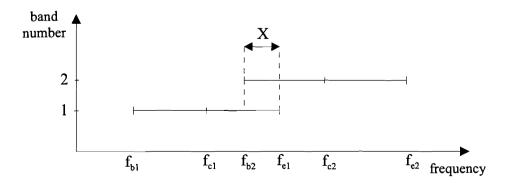

|                  |                                 | 4.2.2 Constant divider detection                      | 52 |  |  |  |  |  |

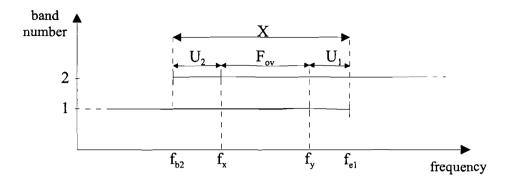

|                  |                                 | 4.2.3 Variable divider detection                      | 55 |  |  |  |  |  |

|                  |                                 |                                                       | 60 |  |  |  |  |  |

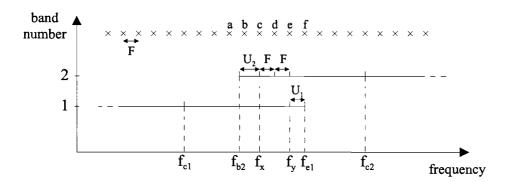

|                  | 4.3                             |                                                       | 61 |  |  |  |  |  |

|                  |                                 | - v -                                                 | 61 |  |  |  |  |  |

|                  |                                 | • •                                                   | 65 |  |  |  |  |  |

|                  |                                 | • • • •                                               | 65 |  |  |  |  |  |

|                  | 4.4                             |                                                       | 66 |  |  |  |  |  |

| 5                | Coa                             | arse frequency control                                | 67 |  |  |  |  |  |

|                  | 5.1                             | - · · · · · · · · · · · · · · · · · · ·               | 68 |  |  |  |  |  |

|                  |                                 |                                                       | 68 |  |  |  |  |  |

|                  |                                 | <u> </u>                                              | 70 |  |  |  |  |  |

|                  | 5.2                             |                                                       | 72 |  |  |  |  |  |

|                  |                                 |                                                       | 72 |  |  |  |  |  |

|                  |                                 | <del>-</del>                                          | 74 |  |  |  |  |  |

|                  |                                 |                                                       | 75 |  |  |  |  |  |

|                  | 5.3                             |                                                       | 78 |  |  |  |  |  |

|                  |                                 |                                                       | 78 |  |  |  |  |  |

|                  | 5.4                             | _                                                     | 84 |  |  |  |  |  |

| 6                | Frequency spread calibration 85 |                                                       |    |  |  |  |  |  |

|                  | 6.1                             | Design                                                | 86 |  |  |  |  |  |

|                  | 6.2                             | Design procedure                                      | 89 |  |  |  |  |  |

| 7                | Cor                             | nclusion                                              | 92 |  |  |  |  |  |

| 8                | Fut                             | ure research                                          | 95 |  |  |  |  |  |

|                  | Rib                             | liography                                             | 96 |  |  |  |  |  |

|                  |                                 | 2                                                     |    |  |  |  |  |  |

| $\mathbf{A}_{]}$ | pper                            | ndices 9                                              | 99 |  |  |  |  |  |

| ${f A}$          | VC                              | 0 10                                                  | 00 |  |  |  |  |  |

|                  | A.1                             | Frequency bands of the first example VCO: 4.5-7 GHz 1 | 00 |  |  |  |  |  |

|                  | A.2                             | Frequency bands of the second example VCO             | 03 |  |  |  |  |  |

| В                | PLI                             | L model 10                                            | 06 |  |  |  |  |  |

|                  | B.1                             | 8 11                                                  | 06 |  |  |  |  |  |

|                  |                                 | B.1.1 Realization in CMOS18                           | 06 |  |  |  |  |  |

|                  |                                 |                                                       | 07 |  |  |  |  |  |

|                  |                                 |                                                       | 07 |  |  |  |  |  |

|                  |                                 | <del>-</del>                                          | 10 |  |  |  |  |  |

|                  | B.3                             | Open-loop simulation results                          | 13 |  |  |  |  |  |

| C            | DLQ                                                                                           | 115 |

|--------------|-----------------------------------------------------------------------------------------------|-----|

| D            | Coarse frequency control  D.1 States of the state-machine in the variable divider system with | 118 |

|              | counter                                                                                       | 119 |

| $\mathbf{E}$ | Frequency spread calibration                                                                  | 120 |

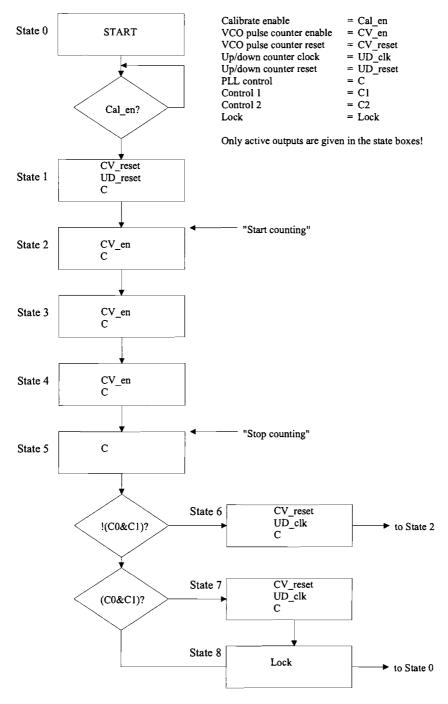

|              | E.1 States of the state-machine in the FSC                                                    | 121 |

| $\mathbf{F}$ | Predecessor FSC system                                                                        | 122 |

|              | F.1 Five Lock methods                                                                         | 122 |

|              | F 2 Design of predecessor FSC system                                                          | 126 |

## Introduction

The frequency range of integrated oscillators is subject to variation. This variation can be caused by temperature variations, power supply variations, aging and, for example, process-spread (in IC-technology the value of devices like capacitors, resistors, transistors vary a certain amount depending on their standard deviation). A standard way of dealing with process spread is increasing the nominal tuning range, such that the required tuning range is covered under worst-case conditions.

Increment of the tuning range of an oscillator to compensate process spread has, without special measures, a number of unwanted effects. A major drawback is an increase of the tuning constant of the oscillator. A high tuning constant means a high sensitivity for noise on the tuning input of the oscillator. Another drawback is that, for LC oscillators it may be impossible to meet the required tuning range with a single varactor.

### Discrete tuning

A method to alleviate some of the problems associated with high tuning constants of oscillators, is adding a discrete tuning input. This added discrete tuning divides the total tuning range into several smaller, but overlapping frequency bands. An automatic frequency control (AFC) system must control this discrete tuning input and must select the appropriate frequency band. In addition to the discrete tuning, the analog fine-tune input is used to cover all the frequencies within one band. Since the tuning range of the analog fine-tune input is reduced significantly, this input is less sensitive for noise. Two types of automatic frequency control systems can be distinguished:

- Coarse frequency control (CFC): This system works together with the phase-locked loop (PLL), which controls the fine-tune input of the voltage controlled oscillator (VCO). Every time a new frequency is selected, this CFC system selects the appropriate frequency band, followed by normal PLL operations which establishes phase-lock at the desired frequency.

- Frequency spread calibration (FSC): This calibration system selects the proper frequency band at start-up and then disables further control of the discrete tuning input of the oscillator. Therefore, the required frequency range must be covered by the selected frequency band, during normal operation, taking into account external variations, like temperature effects and aging.

### Project description

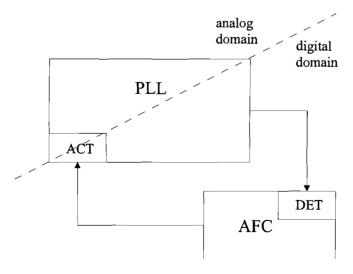

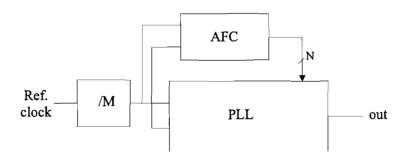

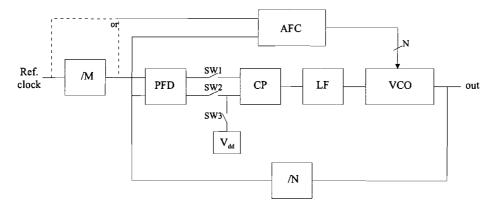

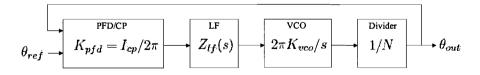

The main aim of this Master Thesis project is to give insight in automatic frequency control (AFC) systems for band-switched oscillators. Especially AFC systems working in the digital domain with minimum interaction with the PLL. And, if possible, no interference with the sensitive analog points within the PLL. The concept of a PLL with automatic frequency control of the VCO is illustrated in figure 1. This figure shows a PLL with an actuator (ACT), partially in the analog domain and partially in the digital domain. Furthermore, the AFC system with detector (DET) is completely in the digital domain.

A 4.5-7GHz LC oscillator with 16 frequency bands [4] will be used to demonstrate the concept of coarse frequency control (CFC). From this oscillator, another oscillator model can be derived, which fits the frequency band requirements for frequency spread calibration systems. This oscillator will be used for verification of the concept of frequency spread calibration (FSC). After that, the differences between CFC and FSC will be discussed.

Figure 1: PLL with automatic frequency control in the digital domain

### Problem definition

The following questions serve as the problem definition

- What are the differences between coarse frequency control (CFC) and the frequency spread calibration (FSC) systems?

- What do automatic frequency control systems assume from the VCO design (exact requirements for frequency bands):

Number of frequency bands?

Amount of span of the frequency bands?

Amount of band overlap?

Amount of variation due to external variables, like process spread?

- What are the actual band selection criterions?

- How is complexity growing with N (number of switches)?

- What kind of interaction with the PLL?

Interaction on sensitive analog VCO control input?

Possible unwanted frequency jumps?

Possibility to shift the actuator and detector (see figure 1) into the digital domain?

### New contributions

This work contributes to the classification of automatic frequency control (AFC) systems for oscillators with discrete tuning inputs. The existing AFC systems are divided into two types of systems: coarse frequency control and frequency spread calibration. After that, the all digital dual-loop architectures are subdivided into systems using a variable or constant division ratio. Furthermore, two (known) conditions of the VCO are introduced, which can be used during selection of the proper frequency band. These conditions, in combination with the type of system and the choice of a variable or constant division ratio, are called detection scenarios.

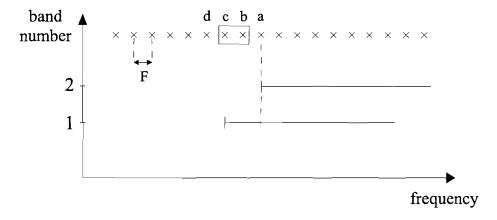

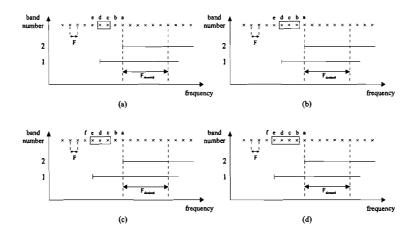

Several detection scenarios are discussed in chapter 4. For each detection scenario, generic frequency band requirements are given, resulting in relationships between necessary detector accuracy and band overlap or band spacing. These requirements are optimized for speed (minimized settling-time) and illustrated by means of examples. Furthermore, necessary band selection criterions are derived from the generic band requirements. Some are illustrated with an example of a linear search algorithm using these selection criterions.

In chapter 3, the basic all-digital AFC system is divided into four functionalities. The relationships between the main parameters of these functionalities are derived. Furthermore, the difference between asymmetric and symmetric detection for the case of a frequency counter is made (for example, asymmetric detection is used in [11]). This work suggests using the

symmetric detection, because the absolute frequency error is less than in the case of using asymmetric detection. The remaining part of this chapter shows the properties of the frequency difference detector based on a digital logic quadricorrelator[9] (DLQ), which is a very good alternative for a frequency counter.

Most AFC systems use an open-loop step, followed by a closed-loop step of the PLL. In chapter 2, two additional methods are presented, setting the PLL in an open-loop condition and the VCO in a known condition (e.g. at the start of each frequency band). These methods use switches in the digital part of the PLL and do not interfere with the sensitive analog part. One of these methods (the fastest), is the preferred method for course frequency control systems.

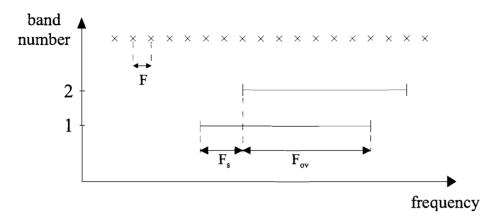

In chapter 5, the concept of reducing the division ratio is introduced: the reduced division ratio decreases the settling-time of the search algorithm. Furthermore, the conversion of the band requirements for a frequency counter to a frequency difference detector based on the DLQ is described.

Chapter 5 and 6 show examples of all-digital AFC systems that are implemented by means of behavioral models in a Verilog/Cadence simulator environment. These simulations verify the theory presented in chapter 3 and 4, by means of testing of worst-case scenarios. Therefore, no major problems are expected by the actual implementation of these AFC systems with digital circuits, as long as the frequency bands of the VCO meet the band requirements that are introduced in chapter 4.

### Answers to the questions

- What are the differences between CFC and FSC systems? Although both systems use the same digital dual-loop topology, the major difference between the CFC and FSC systems is the frequency band parameter to be detected: band overlap and band spacing for CFC and FSC, respectively. Furthermore, the preferred detection scenario (see chapter 4) is different for both systems.

- What do automatic frequency control systems assume from the VCO design (exact requirements for frequency bands)? The requirements for the frequency bands of the oscillator are dependent on the type of system (CFC or FSC) in combination with the used detection scenario; generic requirements are derived in chapter 4 for each discussed detection scenario.

- What are the actual band selection criterions? The band selection criterions are optimized for speed (minimized settling-time) and are derived in chapter 4 for each described detection scenario.

- How is complexity growing with N (number of switches)? In the case that the AFC system uses a separate band selector, without a sophisticated search algorithm (which is not needed due to the application of the digital quadricorrelator), then the amount of hardware will not increase to a great extend for increasing N.

- What kind of interaction with the PLL? Every AFC system must be enabled before it will select a new frequency band. Therefore, no unwanted frequency jumps are possible. Furthermore, the interaction on sensitive analog VCO control input can be minimized by using switches in the digital part of the PLL; two possible methods are introduced in chapter 2.

- Possibility to shift the actuator and detector into the digital domain? This thesis shows that all digital AFC systems can be realized, having the actuator and detector completely in the digital domain.

### Structure of this Thesis

In the first chapter, basic properties of voltage controlled oscillators are described. After that, the concept of frequency bands in an oscillator is introduced. Finally, the chapter is concluded with two examples of band-switched LC oscillators. Both oscillators will be used in a design of an automatic frequency control system.

The second chapter discusses a phase-locked loop, with the emphasis on the commonly used integer-N charge-pump PLL. Each building block is briefly reviewed and behavioral models are developed. The remaining part of this chapter deals with several methods setting the PLL into an open-loop condition, which is used by most automatic discrete frequency control systems.

Then this work proceeds with chapter three about discrete frequency control. First of all, the difference between the two types, coarse frequency control and frequency spread control, is discussed. After that, an overview of state-of-theart systems will be given. The remaining part of this chapter focusses on all digital discrete frequency control systems and a subdivision of these systems is introduced as well as digital frequency detection.

Chapter four deals with requirements for oscillator frequency bands, which are dependent on the type of discrete frequency control system. Throughout this chapter generic band selection criterions are developed, which ensure selection of the appropriate frequency band. In addition, most mentioned band detection scenarios are illustrated by means of an simple example.

The fifth chapter deals with three designs of CFC systems. The main aim of making these designs is to verify the band requirements and selection criterions, introduced in chapter four. Furthermore, the settling-times and complexity of these systems will be compared.

In chapter six, a design of an FSC system is described. This system is used to verify the frequency band and selection criterions for FSC systems. In appendix F, a more complex predecessor of this system is described.

The final chapter summarizes the conclusions that are made throughout this report.

## Chapter 1

## Voltage controlled oscillator

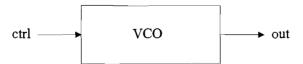

As illustrated in figure 1.1, a voltage-controlled oscillator (VCO) generates an output signal, depending on a control input. The frequency of this output signal is a function of the voltage at the control input. The relationship between the output frequency  $(f_{out})$  and the control voltage  $(V_{ctrl})$  is given by

$$f_{out} = f_0 + K_{vco}(V_{ctrl})V_{ctrl} \tag{1.1}$$

where  $f_0$  is the output frequency when the control voltage is 0V and  $K_{vco}(V_{ctrl})$  is the tuning function [Hz/V] of the VCO.

The output frequency, given in equation 1.1, of integrated oscillators is subject to variation, due to changes in external variables, like: process-spread, supply voltage, temperature and aging. For example, process-spread in IC-technology causes that the value of devices like capacitors, resistors, transistors varies a certain amount depending on their standard deviation. Therefore, the spread in center frequency can easily be as large as 30% for ring oscillators and more than 15% for LC oscillators [1].

This chapter deals with some basic oscillator properties, like center frequency, tuning range, tuning constant and finally phase noise. After that the concept of a VCO with frequency bands will be discussed, for narrow-band and wide-band systems. Subsequently LC oscillators which use band-switching will be considered. Finally, two examples of band-switched VCOs will be presented in combination with an approximation of the process-spread, because behavioral models of these two VCOs will be used in simulations of automatic frequency control systems.

Figure 1.1: The block diagram of a VCO

|                        | Center    | Absolute     | Relative     |

|------------------------|-----------|--------------|--------------|

| Standard               | frequency | tuning range | tuning range |

|                        | [MHz]     | [MHz]        | [%]          |

| FM radio front-end     | 97.75     | 87.5 - 108   | 21           |

| TV receiver            | 500.5     | 41 - 960     | 184          |

| GSM transmitter        | 902.5     | 890 - 915    | 2.8          |

| GSM receiver           | 942.5     | 925 - 960    | 3.7          |

| Satellite TV front-end | 1550      | 950 - 2150   | 77           |

| DECT transceiver       | 1900      | 1880 - 1920  | 2.1          |

| UMTS transmitter (FDD) | 1950      | 1920 - 1980  | 3.1          |

| UMTS receiver (FDD)    | 2140      | 2110 - 2170  | 2.8          |

| Bluetooth              | 2441.5    | 2400 - 2483  | 3.4          |

Table 1.1: Center frequency, absolute tuning range and relative tuning range of several standards [1]

### 1.1 Oscillator properties

Some basic oscillator properties will be discussed in the following paragraphs

#### Center frequency

The center frequency  $(f_c)$ , or mid-range output frequency, is determined by the application in which the VCO is used. Table 1.1 shows the center frequencies of a number of RF standards.

### Absolute tuning range

The absolute tuning range is defined by the minimum and maximum output frequencies  $(f_{min} \text{ and } f_{max})$  that an oscillator can reach. Table 1.1 also gives the minimum absolute tuning range for the given standards.

Especially the specified tuning range must be met under worst-case conditions. Therefore *frequency deviations* due to process-spread, supply voltage variations, temperature changes and aging should be *added* to the actual tuning range of a VCO.

### Relative tuning range

The relative tuning range is defined by  $(f_{max} - f_{min})/f_c * 100\%$  and roughly divides the given systems into two categories: wide-band and narrow-band systems. For example, FM radio, television and satellite TV are wide-band systems and telecom systems like GSM, UMTS, DECT and Bluetooth are narrow-band systems.

### VCO tuning function

The VCO tuning function is dependent of the control voltage at the input of the VCO. It is a non-linear function and the characteristic typically exhibits a high gain region in the middle of the range and a low gain region at the two extremes [3]. Very often this function is approximated by a linear function,

and then this is called a VCO tuning constant  $(K_{vco})$ , which is defined as the ratio of the output frequency over the input control voltage

$$K_{vco} = \frac{f_{max} - f_{min}}{dV_{ctrl}} \tag{1.2}$$

This constant will become larger if the tuning range is increased, to cover process-spread for example. If the supply voltage decreases, in case of a redesign using a newer technology for example, the maximum control voltage swing will also decrease and thus  $K_{vco}$  will increase [1].

#### Phase noise

Phase noise is undesired energy spread continuously in the vicinity of the output frequency, possessing a higher power density at frequencies closer to the fundamental of the output frequency [2]. Furthermore, phase noise is often the most damaging of all noise contributions to the spectral purity of the output signal of an oscillator. A concern in the design of oscillators is the phase noise as a result of the noise on the VCO control input. The noise in the output frequency is proportional to  $K_{vco}$  and the noise voltage on the control input, see equation 1.1. Thus for low noise applications, it is advantageous to implement a VCO with a minimized tuning constant and this can be in conflict with the required tuning range.

### 1.2 Frequency Bands

In general, increasing the nominal tuning range of an oscillator, such that the required tuning range is covered under worst-case conditions, could be used. But, a wider tuning range results in a higher  $K_{vco}$  and therefore a higher noise sensitivity of the VCO control input. A way to achieve a large tuning range and a small  $K_{vco}$  simultaneously, is by breaking a single wide-range tuning curve into several narrower-range sections with some frequency overlap [3]. This leads to the concept of switch-selected tuning elements in a VCO.

#### 1.2.1 Switch-selected tuning

Three types of switch-selected tuning will be discussed in the following paragraphs.

### Switched capacitors

An LC oscillator may be tuned by connecting some combination of MOS capacitors selected from an array. The challenge here is to build a satisfactory RF switch, which will select the capacitors. The switch resistance must be sufficiently low to not degrade the capacitor Q. This implies a MOSFET with a large W/L ratio, whose large junction capacitance will now parasitically load the capacitor array when the MOSFET is turned OFF, and compresses the available spread in capacitance [3].

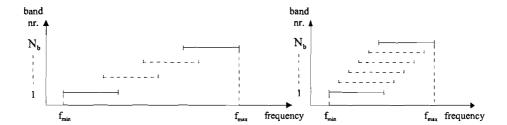

Figure 1.2: Frequency bands in a wide-band and a narrow-band system.

#### Switched inductors / switched oscillators

While a series MOSFET is able to select a capacitor without heavily degrading the resonator Q, when used in series with an inductor it adds a much larger relative loss. However, one of an array of independent oscillators may be selected with a MOSFET switch [3].

#### Switched current sources

One way to change the operating frequency in a ring oscillator is to change the current through an amplifier stage (varying  $g_m$ ). An array of switched current sources can be used to achieve a piecewise frequency-current characteristic.

### 1.2.2 Band positioning

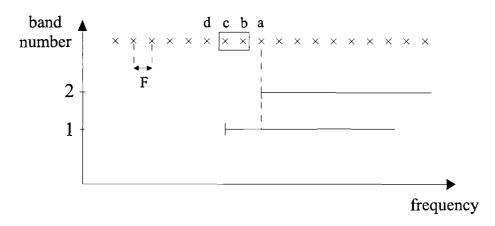

The partially overlapping frequency bands of an oscillator should be positioned differently in narrow-band and wide-band systems. Figure 1.2 shows an example of the frequency bands for a narrow-band system and a wide-band system.

#### Wide-band systems

In wide-band systems the desired frequency range is large. As mentioned earlier, a way to achieve a large tuning range and a small  $K_{\nu co}$  simultaneously, is by using several narrower-range sections with some (small) frequency overlap. Every time a new frequency is selected in the system, an automatic frequency control system must select the appropriate frequency band, after that the PLL locks on the (exact) desired frequency. In this report, this will be called *course frequency control*.

### Narrow-band systems

In narrow-band systems the desired relative tuning range (<5%) is small in comparison with the total relative tuning range ( $\approx30\%$ ), which must be implemented to compensate for external variations. An automatic frequency control loop must select the proper frequency band at startup, this will be referred to as frequency spread calibration. Therefore, the minimum frequency overlap between two adjacent frequency bands is at least the required absolute frequency range of the given standard (see table 1.1). This will guarantee that at least one frequency band can cover the whole required frequency range. Obviously, each frequency band must still be able to compensate for external variations during operation (e.g. temperature changes).

### 1.3 LC oscillator

First of all, the frequency of oscillation of a LC oscillator will be discussed. Then the principle of band-switches is described and finally, two examples of LC oscillators with frequency bands will be given.

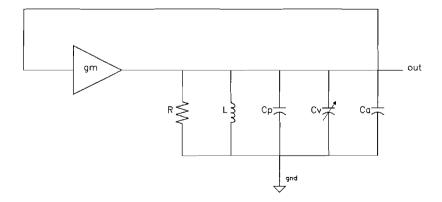

### 1.3.1 Frequency of oscillation

In order to calculate the frequency of oscillation a single-ended linear behavioral model of an ideal LC oscillator is introduced in figure 1.3. The (noiseless) resistor R represents all the losses that are present in the oscillator. These are compensated by the negative resistance amplifier with small-signal gain  $g_m$ . The LC tank inductance has a value L and the capacitance consists of several contributions: a parasitic capacitance  $C_p$ , a varactor capacitance  $C_v$  and a switched-capacitor array capacitance  $C_a$ . Sometimes some extra fixed capacitance  $C_f$  could be added. The frequency of oscillation can be derived easily

$$f_{osc} = \frac{1}{2\pi\sqrt{L(C_p + C_v + C_a)}}$$

(1.3)

The most common method of varying the frequency of oscillation is to vary the total capacitance. Therefore the varactor capacitance is a continuously tunable capacitance which varies from  $C_{v_{min}}$  to  $C_{v_{max}}$ . Furthermore, the switched-capacitor array capacitance is a discretely changeable capacity, which can vary from the minimum array capacitance  $C_{a_{min}}$  to the maximum array capacitance  $C_{a_{max}}$ .

Figure 1.3: Single-ended linear behavioral model of a ideal LC oscillator [1]

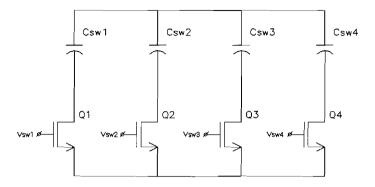

Figure 1.4: A capacitor array implementation

### 1.3.2 Band-switches

As mentioned before, a large tuning range combined with a good phase noise performance can be achieved if band-switching is used. A LC oscillator may be tuned by connecting some combination of capacitors selected from an array [3]. The capacitors can be sized equal, binary-weighted or other weighting schemes are also possible. In the case of equal capacitors, N identical switches and capacitors divide the tuning range in N+1 bands. In case of binary weighted capacitors, N capacitors divide the tuning range into  $2^N$  bands, which is more efficient in terms of the number of required control signals [1].

Simplified models for a MOS-switch  $(Q_1..Q_4)$  in figure 1.4) in ON-state and OFF-state are a resistor  $R_Q$  and a capacitor  $C_Q$ , respectively. The switch ON-resistance must be sufficiently low, otherwise it will degrade the capacitor quality factor. The total capacitance in OFF-state of one branch is:  $C_{off} = (C_{sw}^{-1} + C_Q^{-1})^{-1}$ .

#### 1.3.3 4.5-7GHz LC oscillator for course frequency control

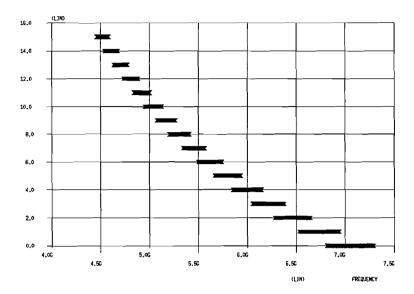

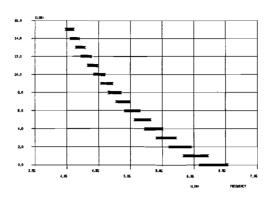

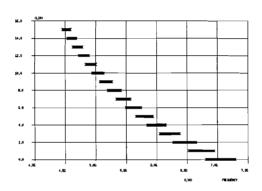

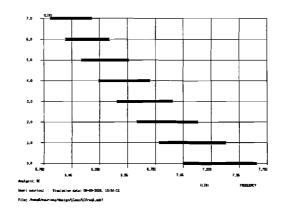

An example of a LC oscillator using band-switching is a 4.5-7 GHz oscillator in CMOS 0.18 $\mu$ m [4]. This VCO will be used in combination with the course frequency control system, as will be discussed in chapter 5. In this oscillator, improved-Q differential switches are applied, but the principle of adding capacity with MOS-switches is the same. The resonator in this oscillator consists of an inductor of approximately 1nH, a paracitic capacitance of around 80fF, varactor with  $\alpha_{varactor}=2$  ( $C_{v_{min}}=125$ fF to  $C_{v_{max}}=250$ fF) and four binary weighted band-switches. The first band-switch represents an on-capacitance of  $C_{on}=64$ fF and an off-capacitance of  $C_{off}=15$ fF. The frequency bands of this VCO are illustrated in figure 1.5.

#### Process-spread simulation

The simulator takes 500 trails with randomly selected values of L and C from the interval  $[-4\sigma, 4\sigma]$  around the nominal value. The first simulation

Figure 1.5: Frequency bands of the 4.5-7GHz LC oscillator

gives the spread of the minimum and maximum frequency of oscillation. The following values:  $\sigma_C$ =5% and  $\sigma_L$ =1% were used (absolute spread). The second effect occurring on a wafer is matching of the (nearby) capacitors. This can be simulated by means of a matching coefficient. These simulations are performed with the following values of  $\sigma_m$ : 0.25%, 0.5% and 1% (relative spread).

Both simulations were done separately. In the case of absolute component spread, the correlation between the (normal distributed) capacitor values is set to 1. In the case of the simulations for mismatch (relative spread), those values are completely uncorrelated.

The absolute spread on values of the inductor and the capacitors results in shifting the frequency bands upwards or downwards. The simulation results can be found in the appendix in table A.2 as well as illustrations of the shifted frequency bands. In brief, absolute spread causes the frequency bands to shift approximately 11% downwards and 14% upwards. If the frequency bands shift downwards, the frequency bands are compressed and if the frequency bands shift upwards, the frequency bands are extended. As a result the overlap between adjacent frequency bands is also approximately 11% less or 14% more in the case of shifting down or up, respectively

The mismatch of the capacitor values results in more or less frequency overlap between two adjacent frequency bands. The simulation results are given in the appendix in table A.3 for  $\sigma_m$  is 0.25%, 0.5% and 1% in the cases that the frequency bands are shifted down, up and in the nominal case. In brief, the frequency band overlap changes approximately 7% due to mismatch of the capacitor values.

# 1.3.4 5.1-6.7GHz LC oscillator for frequency spread calibration

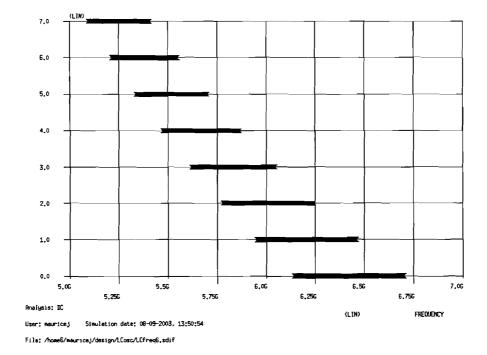

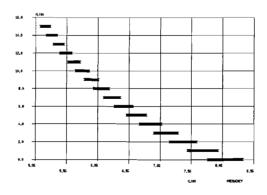

The second example VCO is an oscillator model, which has similarities with the first VCO in inductor, capacitor and varactor values, but has 8 overlapping frequency band and will be used to demonstrate the *frequency* spread calibration system, as will be discussed in chapter 6.

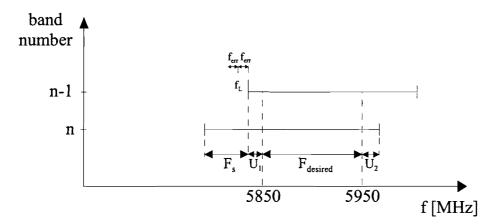

The center frequency of the VCO in the first example will be the starting point for this model:  $f_c=5896 \mathrm{MHz}\approx 5900 \mathrm{MHz}$ . The desired frequency band has a bandwidth of 100MHz and this band will be situated between:  $f_b=5850 \mathrm{MHz}$  and  $f_e=5950 \mathrm{MHz}$ . Process-spread of  $4\sigma_C=20\%$  and  $4\sigma_L=4\%$  will shift the frequency bands to higher or lower frequencies. This sets the minimum and maximum operating frequency for the oscillator:  $f_{min}\approx 5100 \mathrm{MHz}$  and  $f_{max}\approx 6700 \mathrm{MHz}$ . The calculation of the switched capacitor array values can be found in the appendix. Figure 1.6 shows the 8 overlapping frequency bands of this VCO.

Process-spread simulations were done with  $\sigma_m = 1\%$  and the results are given in the appendix in table A.5 and A.6. As a result of the process-spread, the spacing between two adjacent frequency bands changes roughly by 4%.

Figure 1.6: Frequency bands of the VCO for frequency spread calibration

1.4. SUMMARY 19

### 1.4 Summary

Some basic oscillator properties were introduced, like center frequency, tuning range and phase noise. The center frequency of a VCO is the mid-range output frequency and absolute tuning range is defined by the minimum and maximum output frequencies. In general, the output frequency of a VCO is a function of the control voltage at the input and is subject to variation due to external variables (e.g. process-spread). Furthermore, phase noise is proportional to  $K_{vco}$  and the noise voltage on the control input. Thus, low noise applications require a VCO with a minimized tuning constant. However, a low tuning constant can be in conflict with the required tuning range.

A way to achieve a large tuning range and a small  $K_{vco}$  simultaneously, is by breaking a wide frequency band into several smaller, partially overlapping frequency bands. Therefore, switch-selected tuning elements are used in an oscillator. Then, an automatic frequency control system must select the appropriate frequency band.

The tuning range requirement will roughly divide the systems that use an oscillator into two categories: narrow-band and wide-band systems. The frequency bands of an oscillator should be positioned differently in narrow-band and wide-band systems. Therefore two example VCOs are presented in this chapter:

- The first example VCO will be used in a course frequency control system. Process-spread (assuming  $4\sigma_C = 20\%$  and  $4\sigma_L = 4\%$ ) will shift the frequency bands of this oscillator approximately 11% downwards and 14% upwards, this is also affecting the band overlap between two adjacent frequency bands by the same amount. In addition, the frequency band overlap changes approximately 7% due to mismatch ( $\sigma_m = 1\%$ ) of the capacitor values in the capacitor array.

- The second example VCO has 8 overlapping frequency bands and will be used to demonstrate the *frequency spread calibration* system. In addition to the absolute spread, the frequency spacing between two adjacent frequency bands changes roughly by 4%, due to relative spread (mismatch,  $\sigma_m = 1\%$ ).

## Chapter 2

## Phase-locked loop

Nowadays nearly all radio-frequency products rely on digital tuning functionality. The digital tuning systems use a voltage controlled oscillator which is incorporated in a feedback control loop, the phase-locked loop (PLL). This PLL achieves a very high absolute accuracy of the output frequency, which can be varied in small and precise steps.

This chapter deals with a commonly used integer-N architecture, followed by a brief review of the building blocks of a basic charge-pump PLL. After that, simulation results of a charge-pump behavioral model will be given. This model is used for simulations of the automatic frequency control systems. Finally, several methods to set the PLL in an open-loop condition are presented.

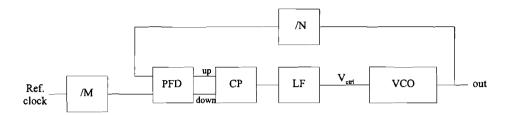

## 2.1 Integer-N PLL architecture

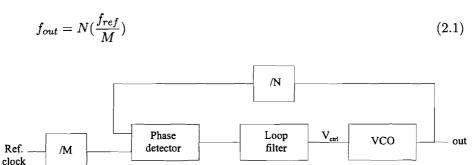

An integer-N PLL is illustrated in figure 2.1 and consists of a VCO, a frequency divider with divider ratio N, a phase detector and a loop filter. In addition, the architecture uses a reference divider with ratio M. The frequency divider (N) in the feedback loop will give a frequency multiplication of the input reference frequency. If the divider has value N, then the output frequency will be N times the input frequency. If the divider value is adjustable, the output frequency of a PLL is programmable. The output frequency produced is a function of the values selected for the input reference divider (M) and the feedback divider (N), such that

Figure 2.1: Standard integer-N architecture

Figure 2.2: Charge-pump PLL

### 2.2 Charge-pump PLL

Figure 2.2 shows a charge-pump PLL, which consists of a phase/frequency Detector (PFD), charge pump (CP), loop filter (LF), voltage controlled oscillator (VCO), a feedback divider N and a reference divider M.

Phase-frequency detector: This part determines the phase difference between the input reference frequency and the output frequency. The two outputs, UP and DOWN drive the charge pump.

Charge-pump: This part sinkes or sources current from or into the loop filter, depending on the up and down input signals.

Loop filter: A low-pass filter is used to attenuate the high-frequency components produced by the PFD/CP combination and for stabilizing the loop.

Voltage controlled oscillator: This device generates a sinusoidal signal at a frequency which is a function of the control voltage. As mentioned earlier, a VCO has the following characteristic:  $f_{out} = f_0 + K_{vco}(V_{ctrl})V_{ctrl}$ . The first integrator in this loop is the VCO, the second integration is the result of the CP/LF combination, which results in a type II PLL.

Frequency dividers: The reference divider divides the reference frequency by M. The feedback divider divides the frequency at the input by a variable factor (N). With this variable N, the PLL is able to generate frequencies that are integer multiples of the (fixed) reference frequency, according to (2.1).

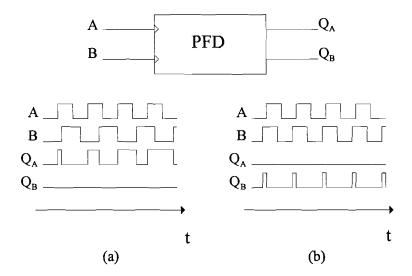

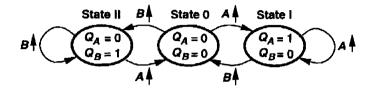

### 2.2.1 Phase-frequency detector

A phase-frequency detector (PFD) circuit can detect both phase and frequency differences, as illustrated in figure 2.3. The  $Q_A$  and  $Q_B$  outputs of the PFD are not complementary and are usually called "UP" and "DOWN" signals. An example of the operation of a PFD: If the frequency of input A is greater than that of input B, than the PFD produces pulses at  $Q_A$ , while  $Q_B$  remains zero. Conversely, if  $\omega_A < \omega_B$ , then positive pulses appear at  $Q_B$  while  $Q_A = 0$ . If  $\omega_A = \omega_B$ , then the circuit generates pulses at either  $Q_A$  or  $Q_B$  with a width equal to the phase difference between the two inputs. Thus, the average value

of  $Q_A - Q_B$  is an indication of the frequency or phase difference between A and B [5].

At least three states are required to create a circuit with the above mentioned behavior:  $Q_A = Q_B = 0$ ;  $Q_A = 0$ ,  $Q_B = 1$ ; and  $Q_A = 1$ ,  $Q_B = 0$ . The circuit could be implemented as an edge-triggered sequential state machine. The states can only change at the rising transitions of A and B. Figure 2.4 shows a state diagram of the operation of this PFD. If the PFD is in state "0", a transition on A will put the PFD in state "I". The circuit remains in this state until a transition occurs on B, then the PFD returns to state 0. The switching sequence between states "0" and "II" works similar [5].

Two extra points will be mentioned:

- If  $\omega_{out}$  is far away from  $\omega_{in}$  the PFD varies the control voltage such that  $\omega_{out}$  approaches  $\omega_{in}$ . When the input and output frequency are sufficiently close, the PFD operates as a phase detector, performing phase lock. In this case a linear model can describe the locking behavior, see appendix B.

- In practice, a PFD will produce narrow reset pulses on the outputs  $Q_A$  and  $Q_B$ , if the PLL is in lock.

### PFD behavioral model

The behavioral model in Verilog is a three-state behavioral model and if the loop is in lock, this model simply produces  $Q_A = Q_B = 0$  instead of the narrow reset pulses on the outputs.

Figure 2.3: PFD response with (a)  $\omega_A > \omega_B$ , (b) A lagging B [5]

Figure 2.4: PFD state diagram [5]

Figure 2.5: CP current sources

Table 2.1: Output table of the Charge-pump

| UP | DOWN | Out                    |

|----|------|------------------------|

| 0  | 0    | high imp.              |

| 0  | 1    | $-I_{cp}$              |

| 1  | 0    | $-I_{cp}$<br>$+I_{cp}$ |

| 1  | 1    | 0                      |

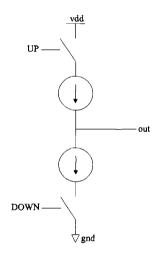

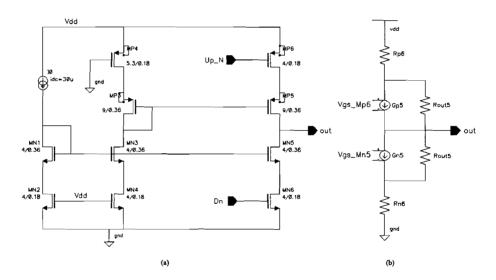

### 2.2.2 Charge-pump

As illustrated in figure 2.5, a charge-pump (CP) consists of two switched current sources and has two inputs. The output of the CP drives the loop filter. The "UP" and "DOWN" inputs can be active or not active. Therefore, the output has four different states, which can be found in table 2.1.

In the case of two ideal switched current sources, the behavior of the CP can be described as follows: If the UP-input is active, the circuit acts as a current source, pumping current into the LF. In the case of an active DOWN-input, the CP circuit is a current sink, and the current flows from the LF into the CP. If both inputs are active, then both current sources are "ON" and this results in zero output current. If both inputs are not active, both current sources are switched "OFF" and therefore the output of the CP is high impedant.

In practice some mismatch will always be present between the UP and DOWN current sources. This will result in a mismatch output current  $(I_{mismatch})$  in the case of two active inputs and in a small leak current  $(I_{leak})$ , if both inputs are not active.

#### Charge-pump behavioral model

Although a simple charge-pump model consists of two ideal switched current sources, this cannot be used in the behavioral model of the PLL. The *integration* of the CP/LF combination, together with ideal current sources, results in unrealistic values of the output voltage of the CP/LF combination. In practice the output voltage of the CP/LF combination is limited (between negative and positive power supply voltage) and therefore output current of the CP is also limited. Thus, the output current of a CP must be a function of the loop-filter voltage. A CP behavioral model has been derived from a charge-pump build with CMOS18 models and the results are given in appendix B.

The advantages of the charge-pump behavioral model are: The output current is easy changeable, the UP and DOWN currents are exactly matched (therefore the mismatch current will be zero), the leak current (when the output is high impedant) is also zero. Further explanation of the behavioral model and simulation results can be found in appendix B.

### 2.2.3 Loop filter

In [8] is shown that the output of the CP vanishes when the phase difference between the input signals of the PFD is zero. This is an ideal locking position for the loop: There is no current injection into the loop filter. Phase lock with zero phase error, for all possible output frequencies requires a loop filter with infinite DC gain. In other words, the loop filter must perform an integration operation on the CP output signal. A simple capacitor suffices to realize the integration function at the loop filter [8].

On the other hand, the loop already contains a perfect integrator: the VCO. So, the addition of another perfect integrator in the loop leads to instability, unless further measures are taken to increase the phase margin. For that reason

a resistor  $(R_1)$  should be added in series with the capacitor  $(C_1)$ , resulting in a first order filter, yielding a second-order PLL system [8].

Every time current is injected into the series combination of the capacitor and resistor, the control voltage makes a voltage step. As a consequence the minimum loop filter configuration found in practice includes an additional capacitor  $(C_2)$  in parallel to the  $R_1C_1$ -section. The purpose of this extra capacitor is to decrease the loop filter trans-impedance for higher frequencies and therefore suppress the (initial) voltage step. The loop filter is now a second order filter and the PLL a third-order system.

#### Second-order filter

A way to calculate a second-order loop filter for an CP-PLL can be found in appendix B. An example of a second-order filter, which gives a PLL loop with a phase margin of  $55^{0}$ , with VCO band number 7 (5393MHz - 5582MHz,  $K_{vco} = 105 \mathrm{MHz/V}$ ), reference frequency  $f_{ref} = 1 \mathrm{MHz}$ , Divider ratio N = 5500 and charge-pump current  $I_{CP} = 200 \mu \mathrm{A}$  results in calculated loop-filter component values of:  $R_{1} = 183 \mathrm{k}\Omega$ ,  $C_{1} = 27.6 \mathrm{pF}$  and  $C_{2} = 3.05 \mathrm{pF}$ .

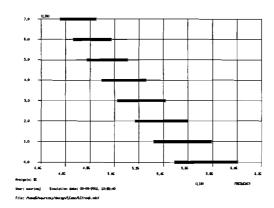

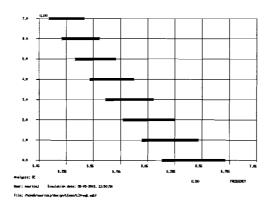

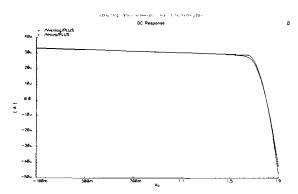

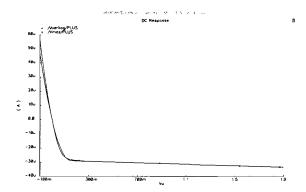

### 2.2.4 Simulation results

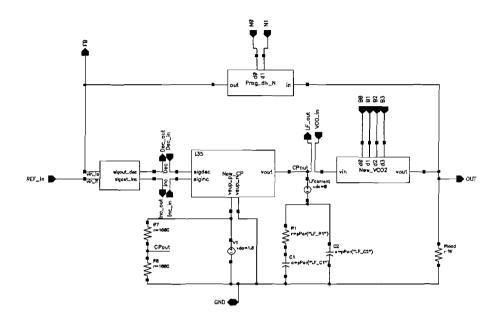

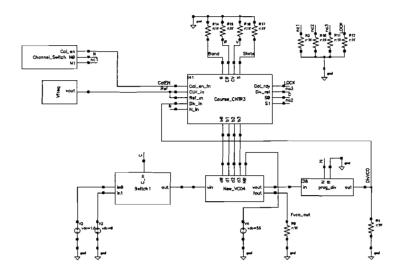

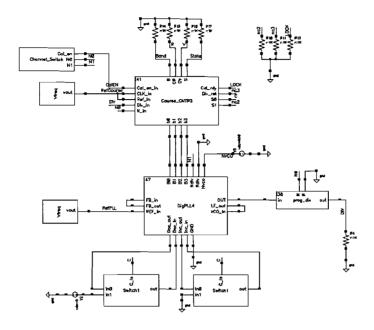

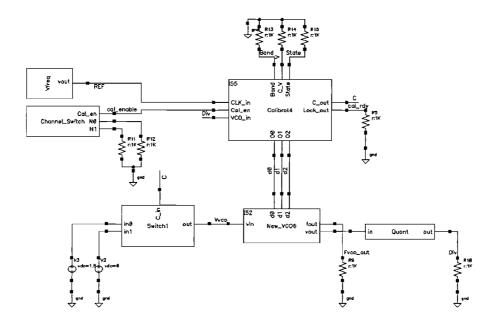

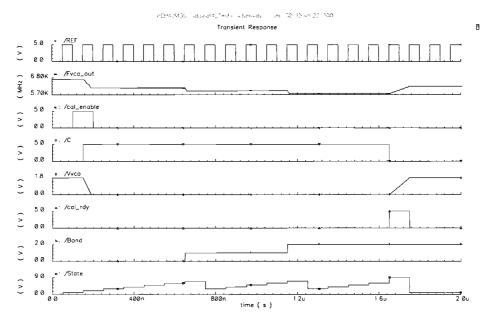

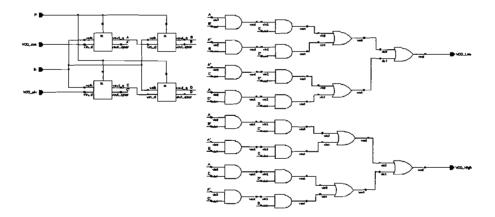

The complete behavioral model of a charge-pump PLL in Cadence is illustrated in figure 2.6. The PFD, CP, VCO and programmable divider N are build with Verilog models. The band-switched VCO has 16 frequency bands and further details about this VCO are given in chapter 1 and in appendix A. Furthermore, the divider ratio N, the charge-pump output current and LF component values can easily be changed.

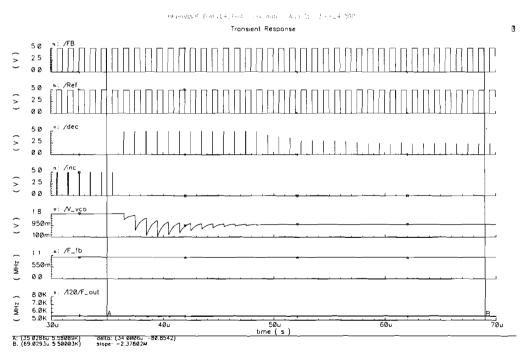

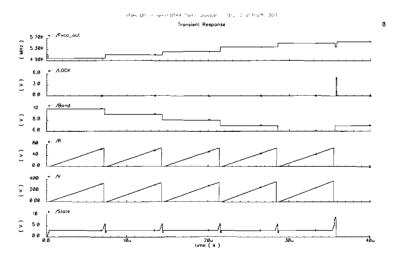

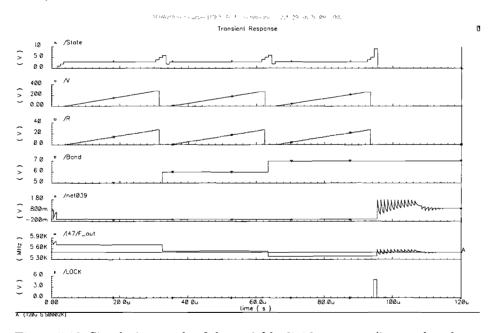

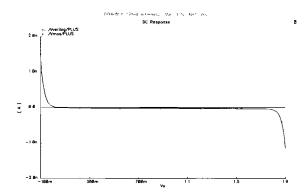

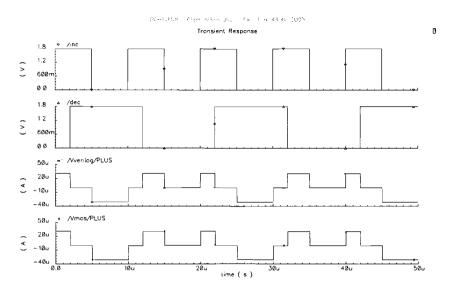

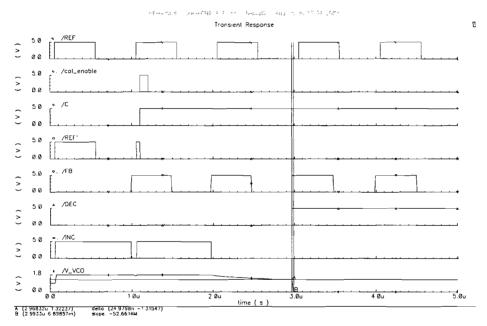

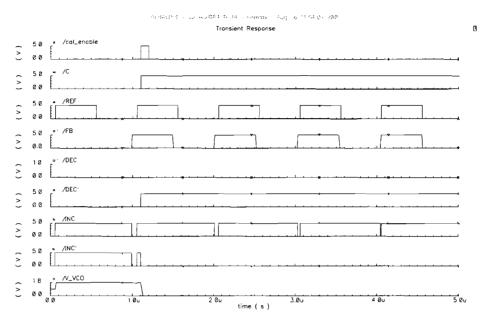

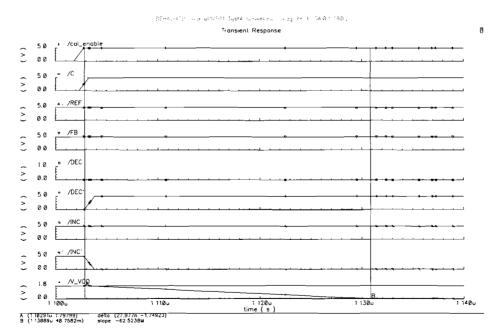

A simulation result of normal locking behavior is given in figure 2.7, which shows that the PLL achieves phase-lock at the desired frequency of 5500 MHz: At marker A the output frequency is 5581 MHz and at marker B the output frequency 5500 MHz. In addition, the phase of the FB and REF signals is the same at marker B.

Figure 2.6: The PLL model in Cadence

Figure 2.7: A simulation result of the PLL:  $f_{REF} = 1 \text{MHz}$ , FB = feedback signal, inc = UP and dec = DOWN output of the PFD, V\_vco = loop filter voltage, F\_out = output frequency.

### 2.2.5 Open-loop condition

A commonly used method, in automatic frequency control systems, is setting the PLL in an open-loop condition, during selection of the appropriate frequency band of the oscillator. After that, the PLL is returned into normal closed-loop operation and the PLL locks on the desired output frequency. This section gives four possibilities to set the phase-locked loop in an open-loop condition.

The first two methods are reported in the literature and use a reference voltage at the input of the VCO, which can be defined at any level between  $V_{ss}$  and  $V_{dd}$ . Therefore, the center frequency of each frequency band can be selected during automatic frequency control. In some cases, which are discussed in chapter 4, the VCO output frequency can be set at the start (or end) of each frequency band. Then, the third or fourth method can be used.

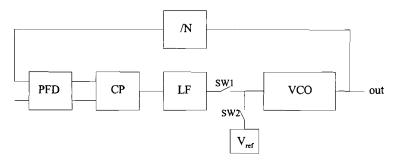

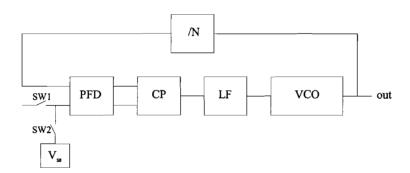

### Switches between LF and VCO (no. 1)

The first method to open the fine-tune loop is illustrated in figure 2.8. To set the PLL in an open-loop condition, switch SW1 is opened and a reference voltage is connected to the VCO control input (by means of switch SW2). For example, this method can be used to set the VCO at the center output frequency, during automatic frequency control. After selection of the desired frequency band of the VCO, the reference voltage is disconnected and the fine-tune loop is closed. In practice, the switches are implemented with (noisy) MOS-switches, therefore a drawback of this method is the interference with the noise sensitive analog control input of the VCO.

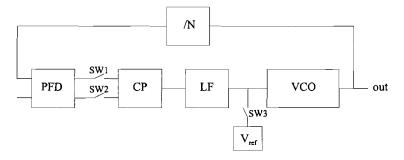

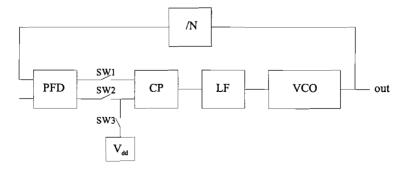

### Switches before CP and between LF and VCO (no. 2)

The second way to open the fine-tune loop is given in figure 2.9. The principle is same as the first method: During open-loop condition, a reference voltage is applied to the control input of the VCO. But, instead of using a switch between the LF and the VCO, the inputs of the CP are disconnected from the PFD. This results in a high impedance output of the CP and therefore the loop-filter voltage can be controlled by the reference voltage source. An advantage in comparison with the first mentioned method is the absence of the MOS-switch between the LF and the VCO input. The switching is partially moved to the digital inputs of the CP, which are less sensitive to noise than analog tuning input of the VCO.

It must be noted that the loop-filter capacitors will be (dis)charged to a level equal to the reference voltage. In the case that the reference voltage is at mid-range voltage, the loop-filter voltage is at mid-range voltage and the initial VCO output frequency will be around the center frequency when the fine-tune loop is closed. Therefore, this method can be used to achieve a fast settling time of the closed-loop step.

Figure 2.8: Open-loop condition will be established by opening SW1 and closing SW2 (method 1).

Figure 2.9: Open-loop condition will be established by opening switches SW1 and SW2 and closing SW3 (method 2).

### Switches controlling the PFD (no. 3)

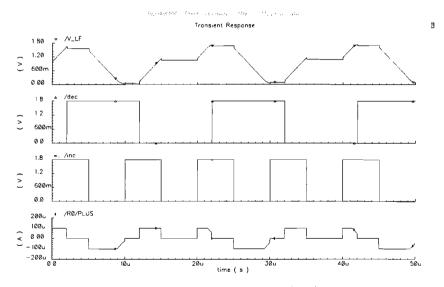

The third method uses switches at the digital inputs of the PFD and is illustrated in figure 2.10. While the PLL is in normal operation, switch SW1 is closed and the reference clock is connected to the input of the PFD. In open-loop condition, this input of the PFD is at a constant level, either  $V_{ss}$  or  $V_{dd}$ . Therefore, the loop-filter voltage will settle at  $V_{ss}$  after a certain time. On the other hand, if the switching would be applied in the feedback line of the PLL, then the loop-filter voltage would settle at  $V_{dd}$ .

To demonstrate a *drawback* of this method, the state-machine behavior of the PFD will be recalled: The PFD has three states. In the case that the PFD is in the "UP" state, two rising edges at the feedback input (FB) of the PFD are required, to set the PFD into the "DOWN" state. If the PLL is lock (before opening the loop), the frequency of the FB-signal is the same as the frequency of the reference clock and the delay time can be calculated as follows:

Example: If the reference frequency  $f_{ref} = 1 \text{MHz}$ , then the worst-case delay time is  $2\mu s$ , see simulation result in appendix B. One way to decrease this delay time is by decreasing the divider ratio in the feedback loop, another way is to use of the next mentioned method.

### Switches controlling the CP (no. 4)

The switches, directly controlling the charge-pump of the PLL, are illustrated in figure 2.11. During normal operation, the switches SW1 and SW2 are closed. In open-loop condition, these switches are open and  $V_{dd}$  will be connected to the DOWN or UP input of the CP. This will result in a loop-filter voltage of  $V_{ss}$  or  $V_{dd}$ , respectively.

The settling-time of the loop-filter voltage to  $V_{ss}$  or  $V_{dd}$  depends on the chargepump output current  $(I_{CP})$  and the value of capacitor  $C_2$  in the loop-filter and can be approximated with

$$I_{CP} = C_2 \frac{dV}{dt} \tag{2.2}$$

Example: The charge-pump output current is  $200\mu$ A and the value of  $C_2$  is 3pF. Then the worst-case settling-time is approximately 30ns, which is much faster than the previous mentioned  $2\mu$ s of method three. Simulation results of the settling-time of the third and fourth system can be found in appendix B.

Figure 2.10: In open-loop condition, one input of the PFD will be at a constant level, driving the loop filter voltage to either  $V_{ss}$  or  $V_{dd}$  (method 3).

Figure 2.11: In open-loop condition, switches SW1 and SW2 are open and the CP will be set in the UP or DOWN state (method 4).

### 2.3 Summary

A commonly used PLL architecture is the integer-N charge-pump PLL architecture. This PLL consists of a PFD, CP, LF, VCO, a feedback divider and a reference divider.

The frequency divider in the feedback loop will give a frequency multiplication of the input reference frequency. If the divider is adjustable, the output frequency of a PLL becomes programmable.

A PFD can detect both phase and frequency differences. The outputs of the PFD are not complementary and are usually called "UP" and "DOWN". Therefore, the behavioral model in Verilog is a three-state model, see figure 2.4.

A CP consists of two switched current sources and has two inputs. The output of the CP drives the loop filter and the output current of a CP must be a function of the loop-filter voltage. A CP behavioral model has been derived from a charge-pump build in CMOS18. Three advantages of the behavioral model are: The output current is easy changeable, the UP and DOWN currents are exactly matched and the leak output current is zero.

The minimum LF configuration found in practice consists of a capacitor  $(C_2)$  in parallel to a  $R_1C_1$ -section. The capacitor  $C_2$  decreases the loop filter trans-impedance for higher frequencies, yielding a second order filter and a third-order PLL system.

The complete behavioral model for a charge-pump PLL has been made in Verilog. In brief, the divider ratio N, the charge-pump output current and LF component values can be changed. Simulation of this charge-pump PLL model, in combination with a behavioral model of the first example VCO (see chapter 1), shows phase-lock exactly at the desired frequency.

Four methods setting a PLL in an open-loop condition have been presented. Whereas the first two mentioned methods use switches in the sensitive analog part of the PLL, the third and fourth method use switches in the digital part of the PLL. Therefore, these methods do not interfere with the sensitive analog part of the PLL. But, these methods (using switches in the digital part of the PLL) can only set the VCO at the start (or end) of each frequency band. Especially the fourth method, controlling the CP inputs directly, drives the loop-filter voltage to  $V_{ss}$  or  $V_{dd}$  with a minimized settling-time. Therefore, this method will be used in the design automatic frequency control systems given in chapter 5 and 6.

## Chapter 3

## Discrete frequency control

Automatic frequency control (AFC) systems can be classified into two types of systems: coarse frequency control and frequency spread calibration, both systems will be discussed in the next two sections. After that, the state-of-the-art AFC systems will be classified into four main architectures. In particular, the all digital AFC system is the most promising solution; in addition to the four main architectures, the all digital dual-loop systems will be subdivided into two subclasses: variable divider and constant divider architectures. Finally, two types of digital frequency detectors will be discussed.

## 3.1 Coarse frequency control

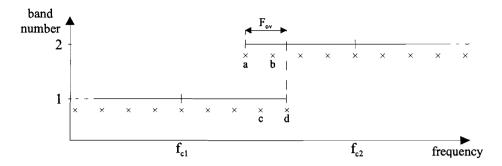

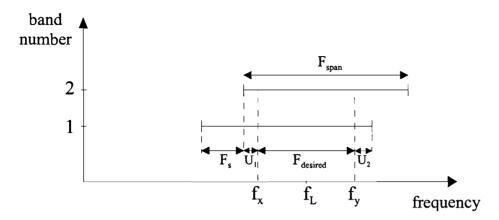

Course frequency control (CFC) is often used in wide-band systems, where the required frequency range is large. As mentioned earlier, a way to achieve a large tuning range and a small  $K_{vco}$  simultaneously, is by using several narrow-range sections with some (small) frequency overlap. Every time a new frequency is selected in the system, a CFC system must select the appropriate frequency band. After that, the PLL can lock on the (exact) desired frequency. In general, each frequency band must be able to compensate for the quantization error of the discrete CFC system.

### 3.2 Frequency spread calibration

In narrow-band systems the desired relative tuning range (<5%) is small in comparison with the implemented relative tuning range ( $\approx30\%$ ), to compensate for external variations. As mentioned before, a number of overlapping frequency bands can be used instead of one broad frequency band covering the whole desired frequency range. Then, a frequency spread calibration (FSC) system must select the proper frequency band at power-up. After that, further control of the discrete tuning is disabled. Therefore, the minimum frequency overlap between two adjacent frequency bands is at least the required absolute frequency range of the given standard (for examples, see table 1.1). This guarantees that at least one frequency band can cover the whole required frequency range.

Obviously, each frequency band must still be able to compensate for external variations (e.g. temperature changes) during operation, which are assumed to be relatively small in comparison to the process spread variation.

### 3.3 State-of-the-art

This section roughly divides the AFC systems, found in the literature, into four main architectures, which are described below. After that, the used algorithms are briefly described, followed by some implementation examples. Finally, an overview of the state-of-the-art AFC systems will be given.

### 3.3.1 Used architectures

The AFC systems can be divided into four main architectures and the most important properties of these architectures are described below.

### AFC relies on $V_{LF}$ architecture (no. 1)

The first automatic frequency control architecture is given in figure 3.1. In this topology, the automatic frequency calibration (AFC) system uses the phase detector and the charge-pump of the PLL. A major drawback of this architecture is interference with the sensitive analog part of the PLL.

The automatic frequency tuning works in the following way: Switch SW1 is opened and SW2 is closed. Then, a reference voltage  $(V_{ref})$  is applied to the VCO and this reference voltage could be the center of the voltage range, e.g. at mid-range voltage. The loop filter voltage  $(V_{LF})$  is applied to the AFC through a high-input impedance amplifier. The AFC system applies a sequence of digital control values to the N discrete tuning inputs of the VCO, selecting different operating curves. For each VCO operating curve an output signal (out) is generated. The charge pump will drive the loop-filter voltage  $V_{LF}$  either to the negative supply voltage or to the positive. This depends on whether the frequency of the feedback signal (FB) is greater than or less than the frequency of the reference signal divided by the input divider (M). Each digital control input value N in the sequence is applied for a period of time, and the AFC system can eventually identify two VCO operating curves that have center frequencies just above and just below the frequency of the reference signal. One of these two operating curves is be selected for use during normal PLL operations. After automatic tuning, switch SW1 is closed and switch SW2 is opened to enable normal PLL operations.

Lock-up time of the selection of the appropriate frequency band, can be minimized by setting the feedback frequency to its maximum by adjusting the divider ratio N to the minimum. Especially, in combination with a maximized frequency of the reference signal, by adjusting the divider ratio of divider M to the minimum.

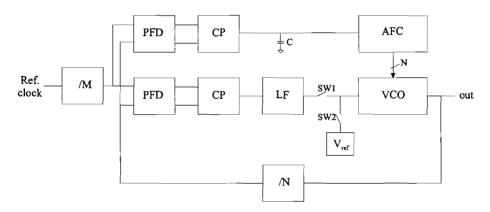

### AFC includes separate PFD/CP architecture (no. 2)

The second architecture (see figure 3.2) uses two separate PLL loops, one for automatic frequency control and one for fine-tuning. This results in a higher complexity, because the PFD and CP are implemented twice. On the other hand, this results in less interaction with the sensitive loop filter voltage in the fine-tuning loop. Furthermore, the settling-time of the additional loop can be made much faster than the settling-time of the normal PLL.

The PFD in the automatic tuning loop generates up and down error signals and therefore, the CP generates an "UP" or "DOWN" current into the capacitor C. This affects the input voltage of the automatic frequency control system. In most cases, an additional comparator is needed to convert the capacitor voltage into digital signals for AFC system. For further explanation of the automatic frequency tuning is referred to the explanation of the first architecture.

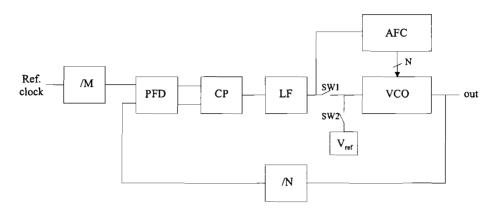

### Digital AFC architecture (no. 3)

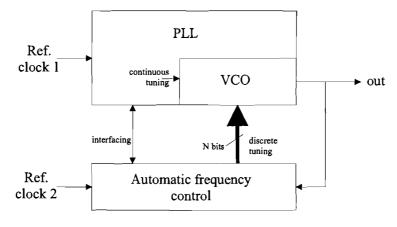

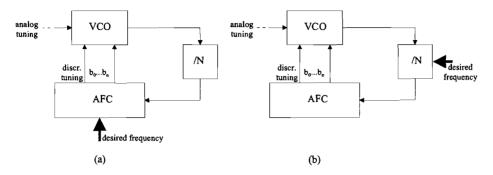

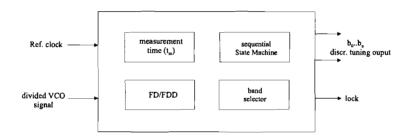

The architecture given in figure 3.3 uses a digital frequency detector or frequency difference detector, instead of the PFD/CP combination in the second architecture. Therefore, the AFC system can be realized completely in the digital domain.

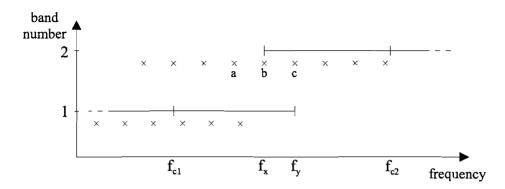

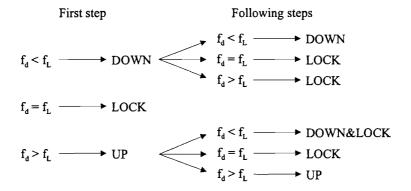

The concept of the digital frequency difference detector (FDD) is analogous to the PFD/CP combination, except that the FDD detects a difference in frequency rather than phase. The FDD also generates up/down error signals and the automatic frequency control system can use different algorithms (see section 4.3.2) to find the appropriate VCO frequency band. In the case of using an frequency detector, the detected frequency can be truncated into an up/down error signal, or the output of the frequency detector can directly be used to select the appropriate frequency band.

Also digital AFC systems can use an open-loop step, followed by a closed-loop step. In the open-loop step, the appropriate frequency band of the VCO is selected by the digital AFC system. After that, the PLL is returned into closed-loop operation and the PLL exactly tunes at the desired output frequency. The digital AFC system can use one of the four methods given in section 2.2.5. to set the PLL in an open-loop condition.

### Digital AFC with automatic gain control (no. 4)

AFC systems that correct the VCO gain  $(K_{VCO})$  as well as the VCO center frequency, have been reported by [12, 23]. After the first iteration of VCO center frequency calibration is completed, the VCO gain is calibrated. The VCO center frequency control word, N, is provided to a VCO gain detection/control block. This block can use a lookup table to determine the value K for the correct VCO gain curve. After the gain correction, the VCO center frequency calibration is repeated. (This architecture is not illustrated in a figure.)

Figure 3.1: PLL with AFC that relies on  $V_{LF}$  [19]

Figure 3.2: PLL with separate AFC loop [19]

Figure 3.3: PLL with all digital AFC loop

### 3.3.2 Band search algorithms

A state machine can select a VCO center frequency with the discrete VCO tuning. This state machine may identify two VCO operation curves that have, for example, center frequencies just above and just below the desired frequency. One of these two must be selected for use during normal PLL operations.

### Linear search algorithm

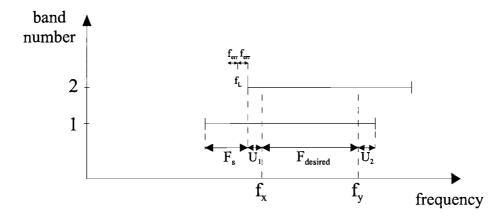

The state machine can perform a linear search algorithm in which the values of the center frequency control value are selected linearly, starting at one end of the range of possible values (e.g. 0) and proceeding to the other end of the range until the error signal provided by the FDD changes polarity.

### Binary search algorithm

If the state machine is using a binary search algorithm each new value of N is selected midway between two previously selected values that yielded opposing error signal values [24]. The binary search stops when two consecutive values are detected that yield opposing error signals.

### Linear interpolation search algorithm

Another method is a linear interpolation search algorithm. This algorithm estimates the frequency of the VCO and converts this into a certain change of the digital VCO codeword N. For example, in [15] this is done by referring to a conversion table.

### Combination algorithm

A combination of the previous mentioned algorithms is also a possibility: e.g. the VCO has a discrete tuning input of 7 bits; linear interpolation principle is used to set the 4 MSBs and the 3 LSBs are set by using a 3 bit linear search algorithm.

### Power-up measurement algorithm

The AFC algorithm can also rely on power-up measurement of the frequency coverage for each frequency band of the VCO and store these measurements into a lookup table. The lookup table is then used in normal operation to select and appropriate band of the VCO such that the PLL can lock on the desired frequency [17].

### 3.3.3 Example implementations

This section gives some information about example implementations of all digital AFC systems.

### Frequency detection based on two counters

In [11] an automatic frequency control system based on two counters is introduced. The digital AFC centers the VCO frequency, thereby reducing the voltage swing needed from the analog control and increasing the pulling range of the VCO. This is an all digital AFC architecture. The AFC system

Figure 3.4: AFC system with two counter FDD [11]

generates a frequency difference indication, using a digital frequency difference detector (FDD), and uses this to increment or decrement the capacitance value of the VCO.

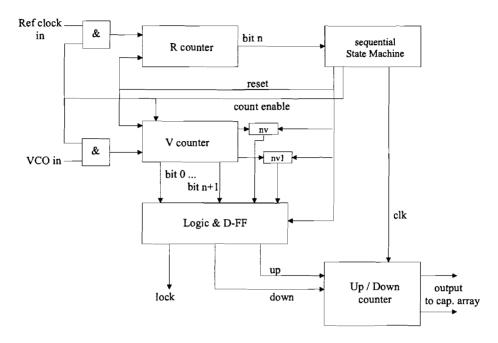

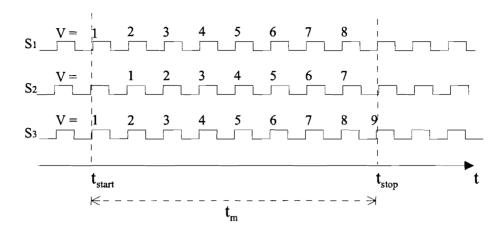

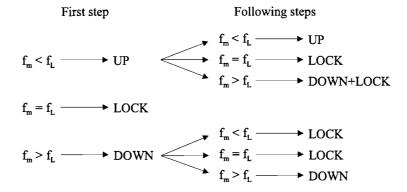

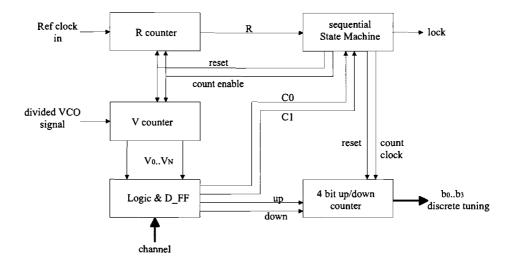

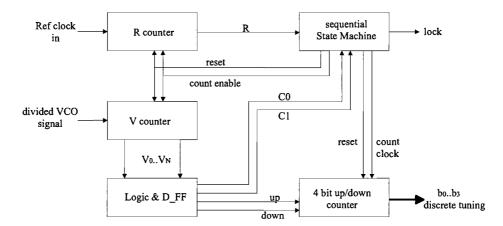

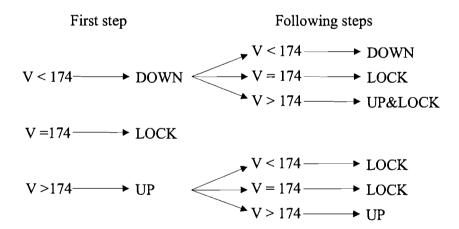

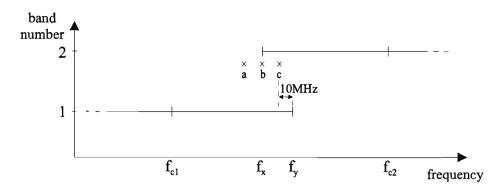

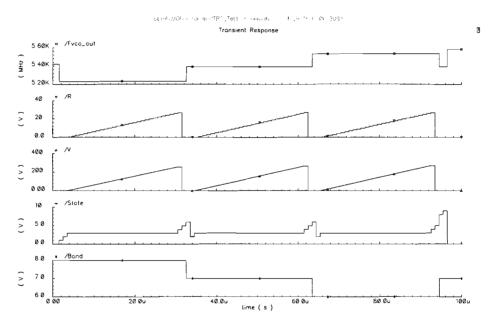

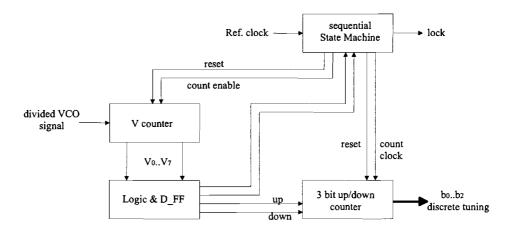

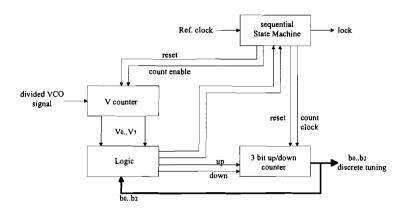

Figure 3.4 shows the digital FDD with two counters (R and V), reported in [11]. These two binary counters, with reset and enable, increment on every edge of the input and are used to count the cycles of the reference and VCO clocks. Counter R counts cycles of the reference clock and is a binary counter of n bits. Counter V counts cycles of the signal generated by the VCO and is at least n+1 bits long. Two one bit latches nv and nv1 are used to remember any overflows. When the R counter bit n is set, which means overflow of n-1 into bit n, the counting of R and V will be stopped.

The contents of the R and V counter is used to determine the relative frequency difference between the reference clock and the VCO. The relative frequency difference is used to set 3 latches, indicating whether the VCO is too fast, too slow or in the appropriate frequency band. The controlling state machine then generates a clock for an up/down counter. Each of the bits of this counter controls one of the MOS switches in the capacitor array in the VCO. The measurement is used to increment or decrement this counter to correct the center frequency of the VCO. The direction of the change for the counter is dependent on the relation between band number and center frequency of the VCO.

The calibration system in [10] also uses two counters that race side by side. If the counter R counts faster and finishes the race before the node V, the N-bit control is incremented to speed up the VCO. The counter length determines the limited accuracy of the frequency comparison. The initial phase offset between R and V will have a minimal influence on the accuracy of the comparison, provided that the length of the counters is long enough. Once the node V wins the race, the N-bits are frozen for the normal operation of the PLL and the calibration circuit is disabled until the reset/calibrate signal is reactivated by power-up.

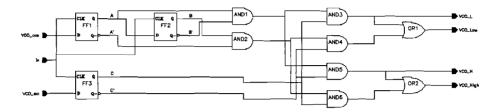

## Frequency detection based on a digital logic quadricorrelator

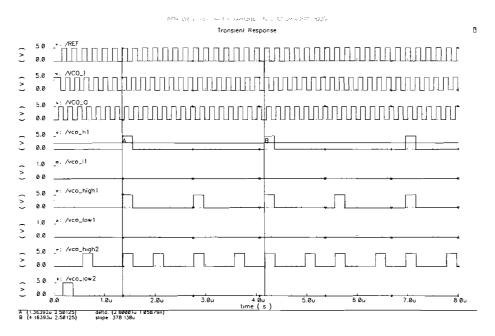

In [27]<sup>1</sup> a frequency calibration circuit that uses a digital logic quadricorrelator [9] is presented. Furthermore, it seems that the circuit makes use of method 4 (directly controlling the CP, see chapter 2) to set the PLL in an open-loop condition.

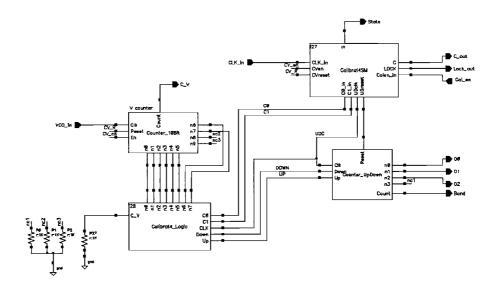

A frequency calibration circuit based a digital logic quadricorrelator (DLQ) determines the course tuning settings for the required channel. The direction of rotation of the in-phase and quadrature samples determines the polarity of the frequency difference. Initially, the PLL is disabled, the counter is reset and the counter is incremented or decremented with the quadricorrelator UP/DOWN outputs. A state machine determines convergence and freezes its state and re-enables the PLL for final phase-locking.

#### Digital center frequency and VCO tuning constant calibration

In [12] an automatic frequency control system is presented that also corrects the VCO tuning constant. The control circuit consists of a decoder and a state machine. It extracts the frequency and gain message from the output bits of the counter and generates a K bit signal to trim the VCO tuning constant. This system makes use of method 2, presented in chapter 2, to set the PLL into an open-loop state: Both up and down charge pump switches are opened and the switch between the reference voltage source and the VCO is closed in order to place a fixed reference voltage (e.g. mid-level) at the VCO control input.

After finding the appropriate frequency band and tuning constant, the digital auto-trimming circuit sets a *start level* on the VCO control input through a simple digital to analog converter, to achieve the desired frequency within a tolerance of 10%, which ensures a fast settling time of the closed-loop step. Then, the calibration circuit is de-activated and the PLL can operate in conventional mode.

<sup>&</sup>lt;sup>1</sup>This article has been published in June 2003, after I had been working on the AFC systems using the DLQ.

#### 3.3.4 Overview

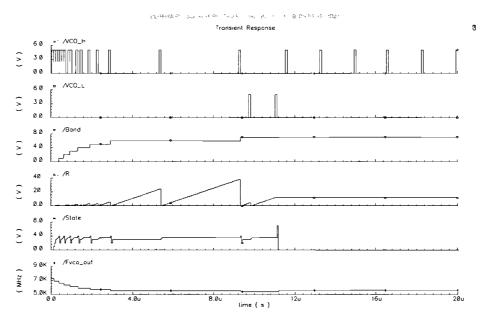

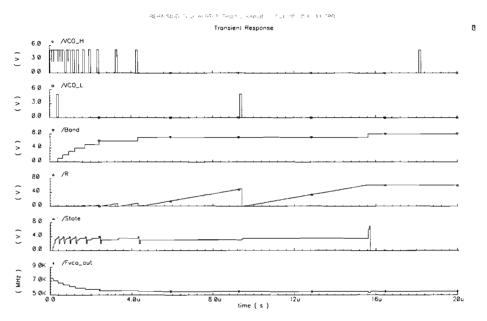

Table 3.1 gives the results of the comparison of automatic frequency control systems presented in the references: First of all, the type of oscillator is given, together with the frequency range or operating frequency of the oscillator. Next, the architecture number (see section 3.3.1) is listed in the table as well as the method setting the PLL in open-loop condition, which were introduced in section 2.2.5. If no method number is given in the table, then the way of setting the PLL into an open-loop condition is not known. Finally, the division into two types of automatic frequency control systems is made.