#### MASTER

Realisation of the Area Segmentation Processor for ESPRIT project #2017 : TRIOS

de Winne, P.T.M.

Award date: 1993

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

EINDHOVEN UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING Measurement and Control Section

## REALISATION OF THE AREA SEGMENTATION PROCESSOR FOR ESPRIT PROJECT #2017: TRIOS

7016

by P.T.M. de Winne

M.Sc. Thesis/Report on Practical training period carried out from september 1992 to june 1993 commissioned by prof.dr.ir. A.C.P.M. Backx under supervision of ir. R. van Vliet of the TUE and ing. A.J.M. van Lier of Philips CFT date: 7 june 1993

The Department of Electrical Engineering of the Eindhoven University of Technology accepts no responsibility for the contents of M.Sc. Theses or reports on practical training periods.

# Realisation of the Area Segmentation Processor

for Esprit Project #2017: TRIOS

| author :     | P.T.M. de Winne                    |         |

|--------------|------------------------------------|---------|

| id. nr. :    | 318778                             |         |

| institute :  | University of Technology Eindhoven |         |

| department : | Information Engineering            | +11     |

| professor :  | prof.dr.ir A.C.P.M. Backx          | tu      |

| coach :      | ir. R. van Vliet                   |         |

| company :    | Nederlandse Philips Bedrijven B.V. |         |

| department : | CFT-ISP-IMI                        | PHILIPS |

| coach :      | ing. A.J.M. van Lier               |         |

| period :     | september 1992 - june 1993         |         |

## Summary

Philips CFT (Centre For manufacturing Technology) is partner in the ESPRIT project #2017: TRIOS, for the development of an in-line inspection system. The inspection system checks PCBs, which are suitable for surface mounted devices, after solder paste has been laid on the PCB. The purpose of the system is to decide wether or not the solder paste is on the right position and has the right volume.

A laser scanner extracts height and intensity information from a PCB by means of a laser beam. This information is sent to a data processing unit. The data processing unit calculates the position and the height of the solder paste and checks that those values are between certain bounds. The results are given to the host which controls the whole system.

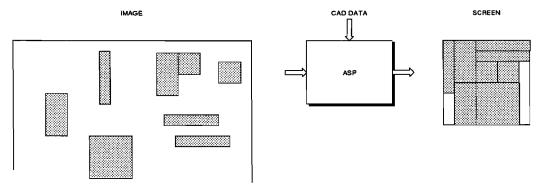

The Area Segmentation Processor (ASP) segments the image information. This to distribute the data over the calculation processors and to reduce the data for the calculation processors. The areas of interest (AOIs), which have to be segmented, are specified in the CAD-data. The ASP composes the stored AOIs into images (called screens), which have a suitable format for the calculation processors and sends these screens to the calculation processors.

The controller of the ASP converts the specification of the areas of interest into addresses on which the data is stored in the circular buffer. Information within an AOI is placed on a unique address in the circular buffer. Information outside an AOI is placed on address zero. After the AOIs are stored, the AOIs are composed to one or more screens by the screen handler. The screens are sent to the calculation processors. The composition of the AOIs is calculated by software.

The hardware of the Area Segmentation Processor is improved and implemented in the system. Software is written and tested so that  $512^2$  images are received and sent. The segmentation software is partly written. The processor, a RISC processor, can be programmed in assembly or in C. Using local variables instead of global variables will save processor time.

## Preface

This report is written by Peter de Winne, student information engineering (ITE) at the University of Technology Eindhoven (TUE), as graduation report. The graduation was carried out at Philips Centre For manufacturing Technology (CFT), section Industrial Signal Processing (ISP), group Industrial Measurement and Inspection (IMI).

The section Industrial Signal Processing provides support for the application of electronic technologies in production processes and products. The main activity areas are Industrial Measurement and Inspection with the emphasis on Machine Vision and Motion Control Technology. The object of the group Industrial Measurement and Inspection is to provide in solving automatic optical inspection problems in production and develop methods, tools and modules for applications in this field.

My graduation assignment was to realize a processor board (the area segmentation processor) that segments areas of an image and places these areas into screens. Therefor the schemes of the hardware are checked, the hardware is build, tested and improved where necessary and the software is written.

I want to thank ir. N.G.M. Kouwenberg who gave me the opportunity to fulfil my graduation assignment at Philips CFT. I want to say special thanks to ing. A.J.M. van Lier who gave me the graduation assignment and did the coaching of my work at Philips CFT and ir. R. van Vliet who did the coaching at the TUE. Further I want to thank ir. F.G.M. Smeets, ing. J.F.J. Hendriks, ir. L.H.D. Geraats, ing. M.F.W. Pechler and H.M. van Meurs for their support during my graduation period.

## Content

|   | Summ    | nary                                    | 2  |

|---|---------|-----------------------------------------|----|

|   | Prefac  | 2e                                      | 3  |

|   | List o  | f figures                               | 6  |

|   | List o  | f tables                                | 7  |

| 1 | Introd  | uction                                  | 8  |

| 2 | In-line | e PCB inspection system                 | 10 |

|   | 2.1     | Global explanation of the system        | 10 |

|   | 2.2     | Data processing system                  | 11 |

| 3 | Hardv   | vare of the Area Segmentation Processor | 13 |

|   | 3.1     | Controller                              | 14 |

|   | 3.2     | VME-bus interface                       | 14 |

|   | 3.3     | Image handler                           | 15 |

|   | 3.4     | Screen handler                          | 16 |

|   | 3.5     | Circular buffer                         | 17 |

| 4 | Softw   | are for the Area Segmentation Processor | 19 |

|   | 4.1     | Manage AOIs                             | 20 |

|   |         | 4.1.1 Compute Lines                     | 20 |

|   |         | 4.1.2 Combine AOIs In Screens           | 22 |

|   |         | 4.1.3 Send Ids And Positions            | 23 |

|   |         | 4.1.4 Control Screen Retrieval          | 23 |

|   | 4.2     | Manage Unit Address Buffer              | 24 |

|   | 4.3     | Manage Unit Buffer                      | 25 |

| 5 | Imple   | mentation of the hardware               | 27 |

|   | 5.1     | VME-interface                           | 27 |

|   | 5.2     | Controller                              | 29 |

|   | 5.3     | Image handler                           | 30 |

|   | 5.4     | Screen handler                          | 31 |

|   | 5.5     | Circular buffer                         | 32 |

|   | 5.6     | Picture bus interface                   | 33 |

|   |         |                                         |    |

| 6     | Implem        | nentation of the software          | 34 |

|-------|---------------|------------------------------------|----|

|       | 6.1           | Software 512x512 images            | 34 |

|       | 6.2           | Segmentation software              | 35 |

|       | 6.3           |                                    | 37 |

|       |               |                                    |    |

|       | Project       | status and conclusions             | 40 |

|       | Abbrev        | viations                           | 41 |

|       | Literati      | ure                                | 42 |

| Appen | dix A T       | he processor CY7C611               | 43 |

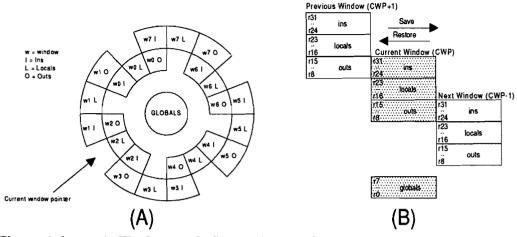

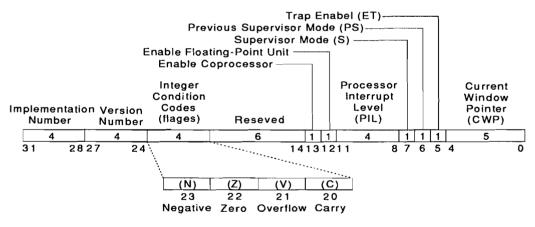

|       | A.1 Re        | egisters                           | 44 |

|       |               | A.1.1 Working registers            | 44 |

|       |               |                                    | 45 |

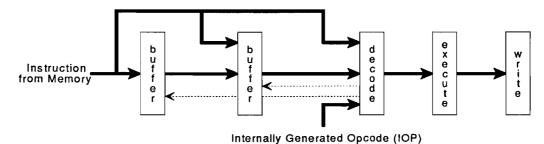

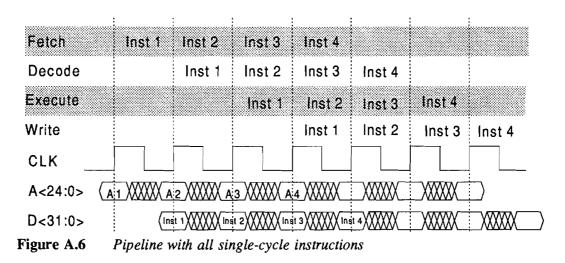

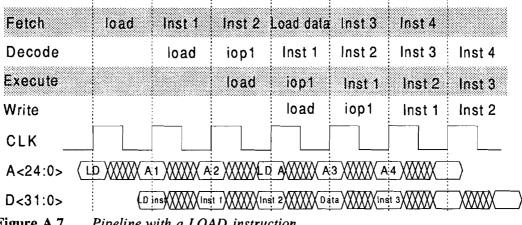

|       | A.2 Pi        | peline                             | 47 |

|       |               |                                    | 49 |

|       |               |                                    | 50 |

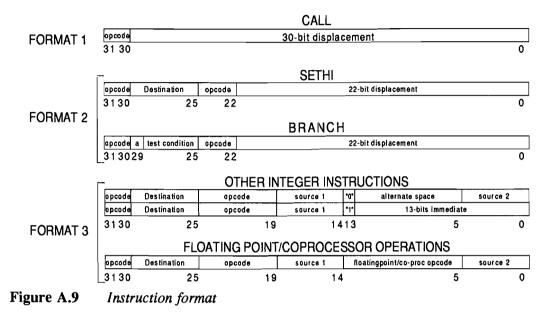

|       | A.5 In        | structions                         | 51 |

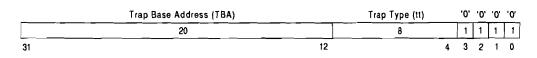

|       | A.6 Tr        | aps                                | 52 |

|       |               |                                    |    |

| Appen | dix B So      | chemes Area Segmentation Processor | 54 |

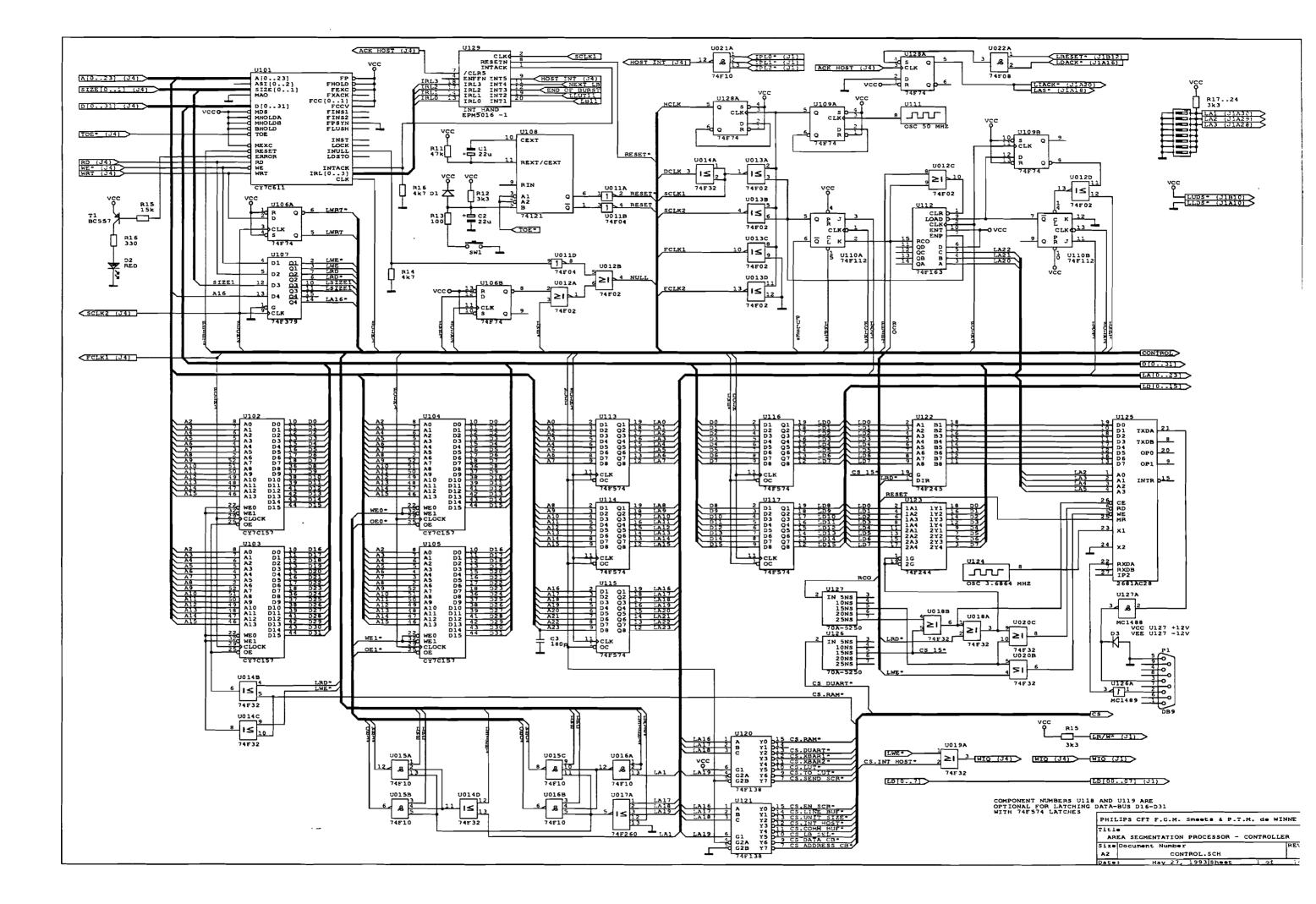

|       | B.1 Co        | ontroller                          | 55 |

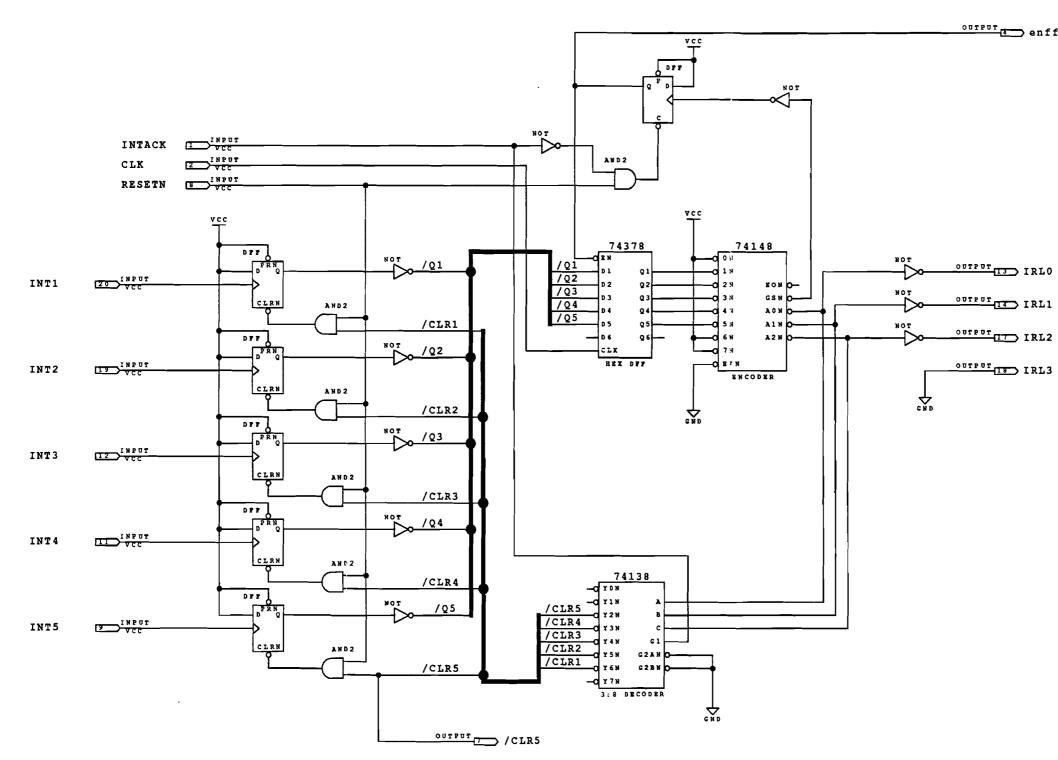

|       | B.2 EF        | PLD interrupt handler              | 56 |

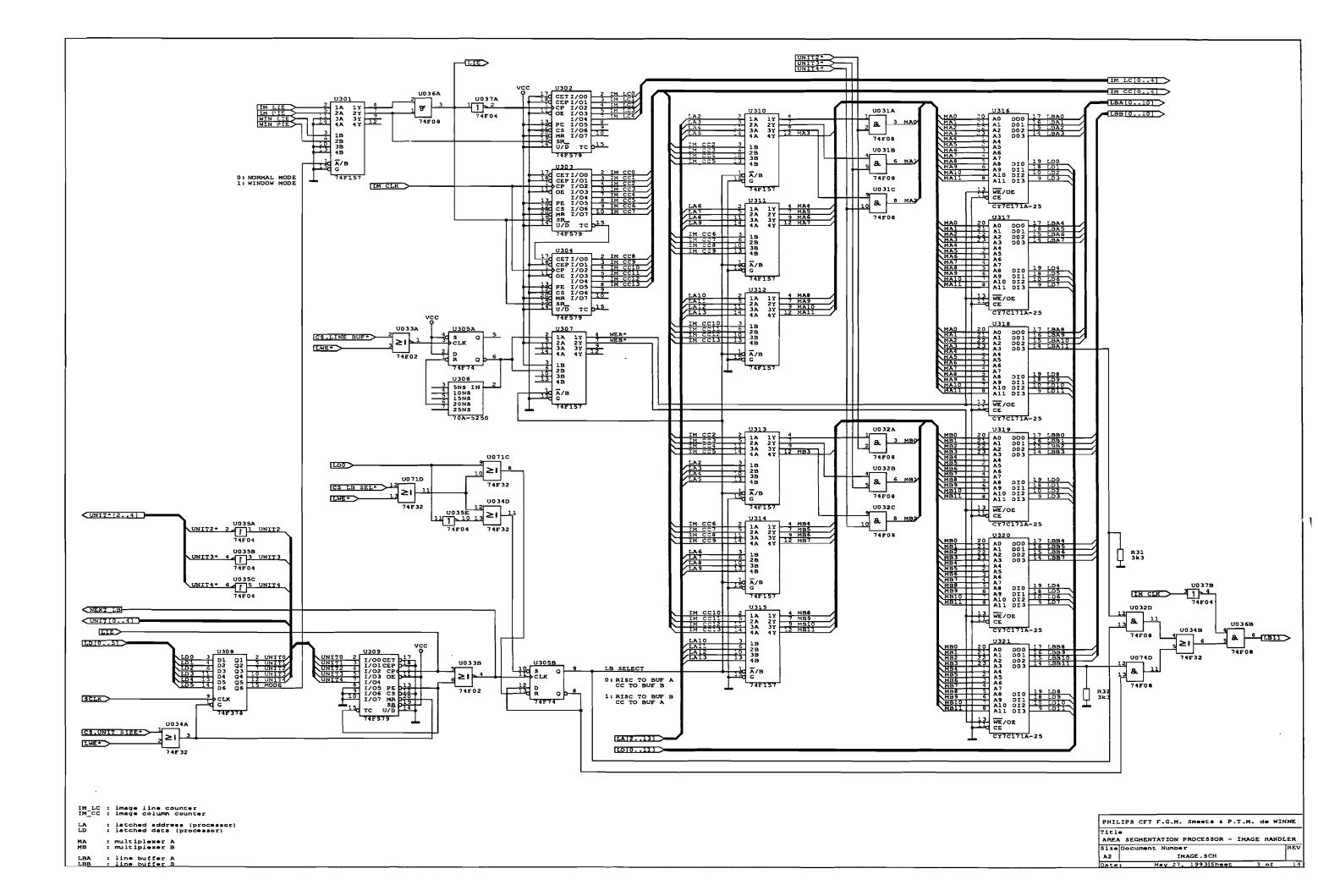

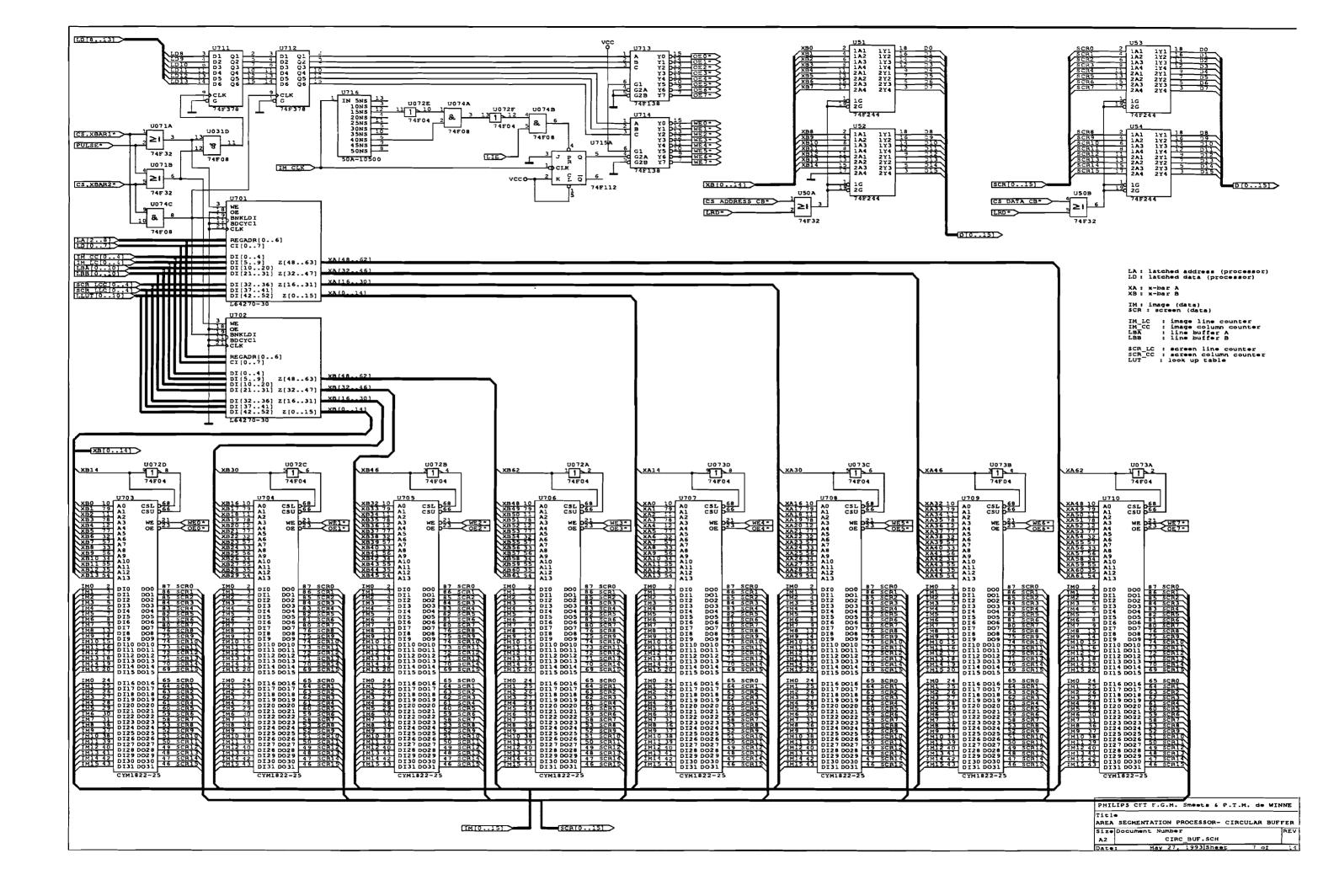

|       | B.3 Im        | hage handler                       | 57 |

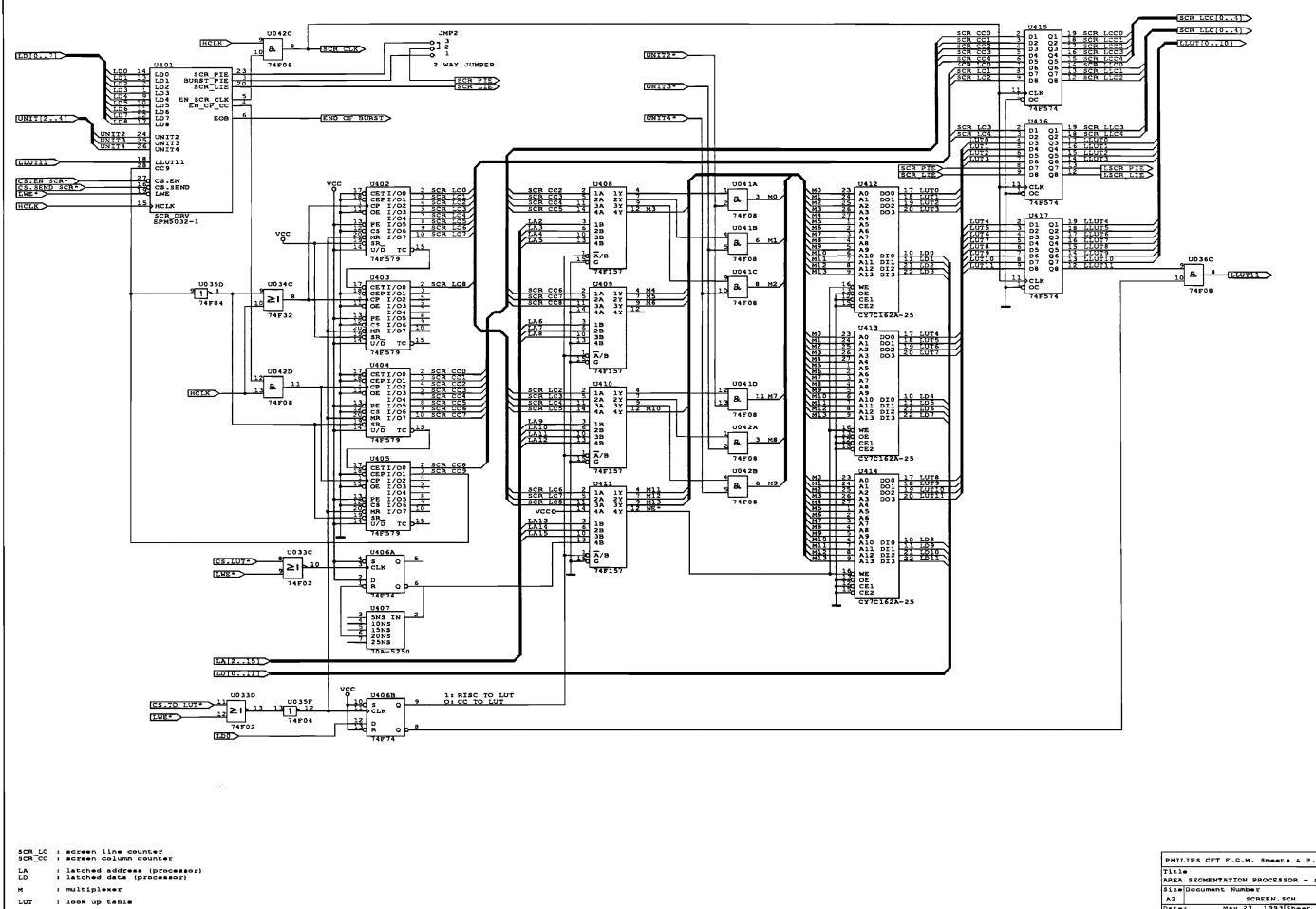

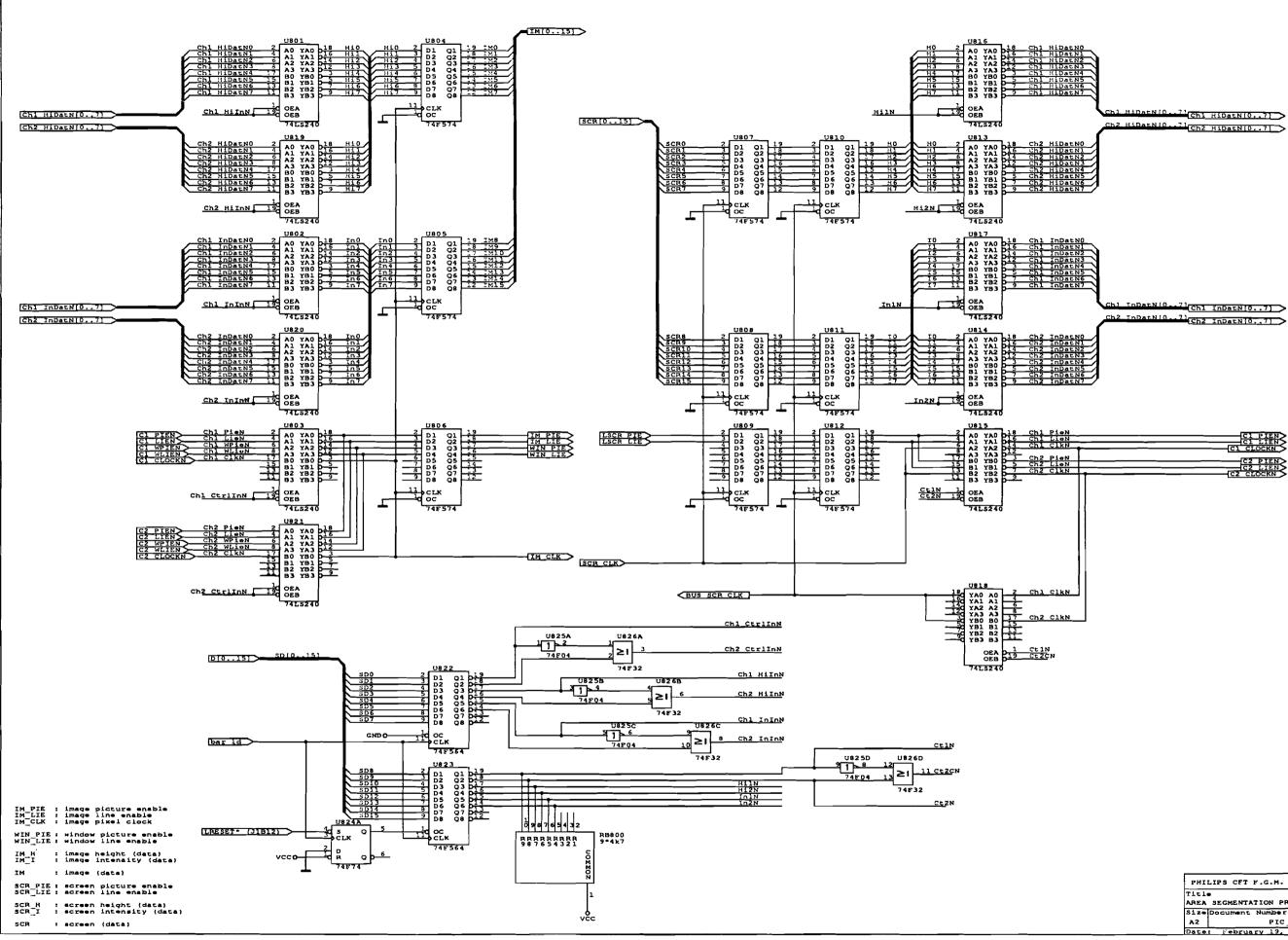

|       | B.4 Sc        | reen handler                       | 58 |

|       | B.5 EF        | PLD screen handler                 | 59 |

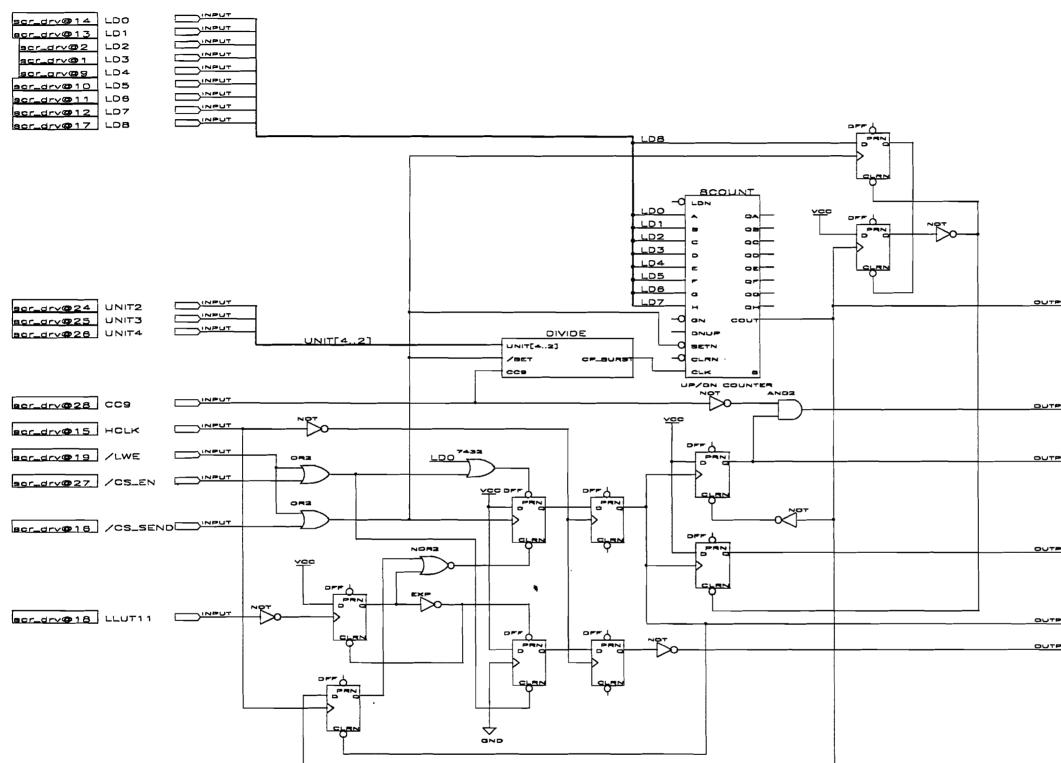

|       | B.6 EF        | PLD divider                        | 60 |

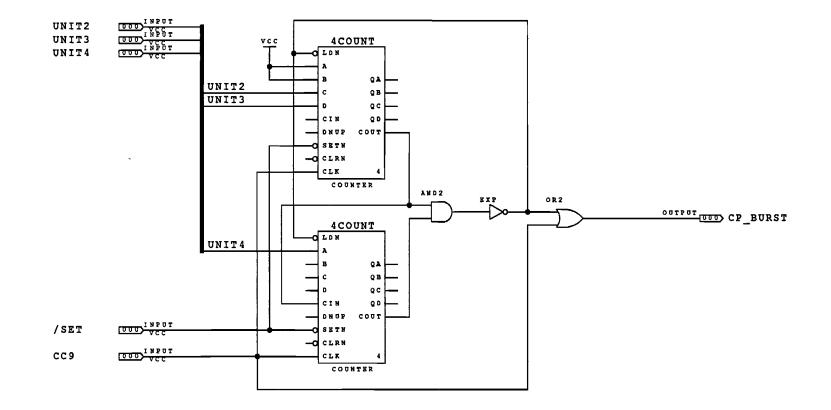

|       | <b>B.7</b> Ci | rcular buffer                      | 61 |

|       | B.8 Pie       | cture bus interface                | 62 |

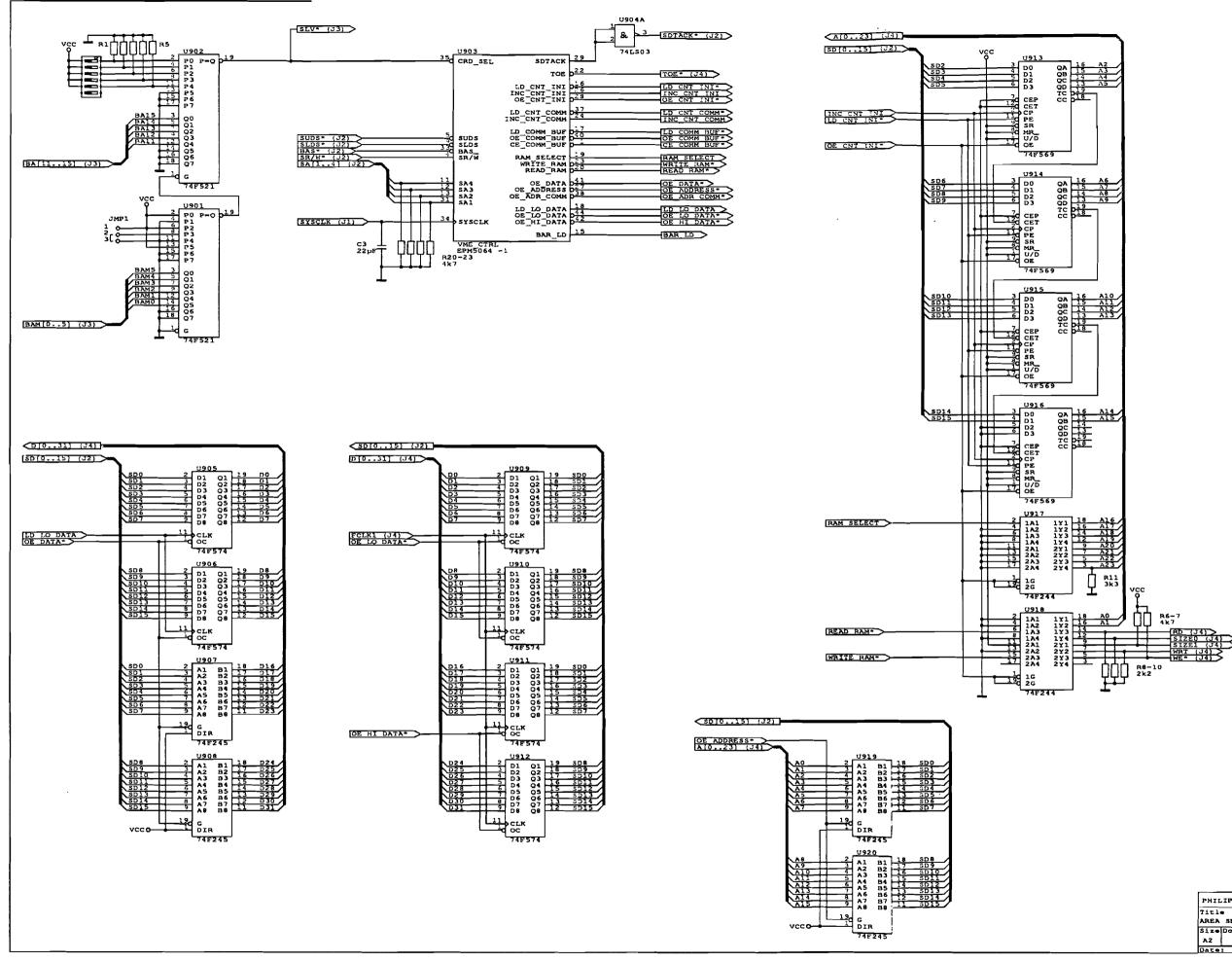

|       | B.9 VI        | ME-interface                       | 63 |

|       | B.10 V        | ME-interface handler               | 64 |

|       | B.11 C        | Communication buffer               | 69 |

| Annon | div C D       | no grom 510 x 510 im and           | 73 |

| Арреп |               | rogram 512x512 image               | 15 |

| Appen | dix D P       | rogram address generation          | 84 |

| Appen | dix E A       | ssembly listings fill_ua_buffer    | 91 |

|       |               |                                    | 91 |

|       |               | -                                  | 92 |

# List of figures

| Figure 2.1 | Diagram in-line inspection system                              | 10 |

|------------|----------------------------------------------------------------|----|

| Figure 2.2 | Diagram of the data processing system                          | 11 |

| Figure 3.1 | Example of image to screen transformation                      | 13 |

| Figure 3.2 | (A) Definition of an AOI, (B) Relation between pixel, unit and |    |

| AOI .      |                                                                | 13 |

| Figure 3.3 | Block diagram of the Area Segmentation Processor               | 14 |

| Figure 3.4 | Unique identifier pixel and unit                               | 15 |

| Figure 3.5 | Address generation for writing units                           | 16 |

| Figure 3.6 | Address generation for reading units                           | 16 |

| Figure 3.7 | Principle of circular buffer                                   | 17 |

| Figure 3.8 | Functional diagram of circular buffer                          | 18 |

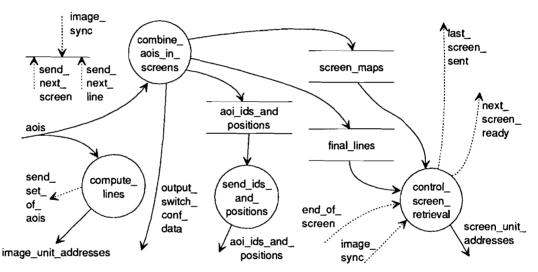

| Figure 4.1 | Functional diagram of the Area Segmentation Processor          | 19 |

| Figure 4.2 | Functional diagram of manage_aois                              | 20 |

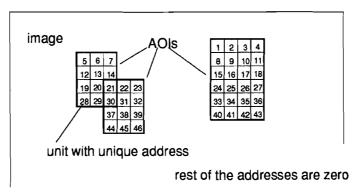

| Figure 4.3 | Addresses for the units in an AOI                              | 21 |

| Figure 4.4 | Examples of places for the switch bit                          | 21 |

| Figure 4.5 | Example of a screen map with the addresses                     | 22 |

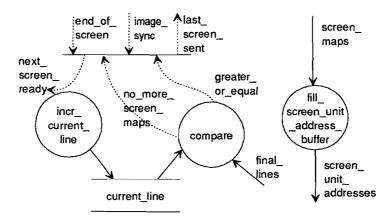

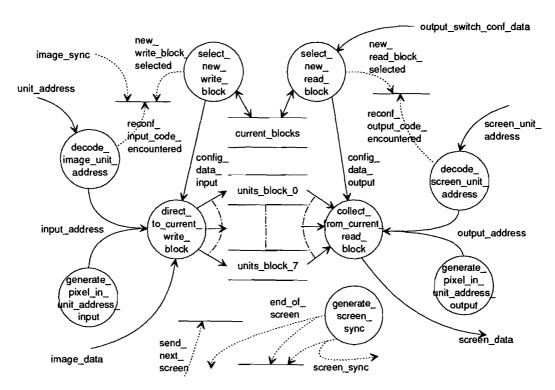

| Figure 4.6 | Functional diagram of control_screen_retrieval                 | 24 |

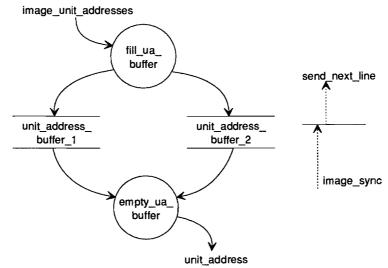

| Figure 4.7 | Functional diagram of manage_unit_address_buffer               | 25 |

| Figure 4.8 | Functional diagram of manage_unit_buffer                       | 26 |

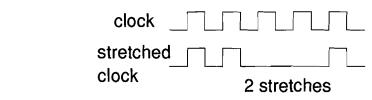

| Figure 5.1 | Example of a 2 times stretched clock                           | 30 |

| Figure 6.1 | Sequence of 512x512 program                                    | 35 |

| Figure 6.2 | Sequence of receiving the image                                | 35 |

| Figure 6.3 | Sequence of sending the screen                                 | 35 |

| Figure 6.4 | Sequence of the address generation                             | 37 |

| Figure 6.5 | Listing fill_ua_buffer                                         | 38 |

| Figure 6.6 | Listing fill_ua_buffer improved                                | 39 |

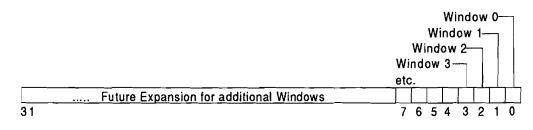

| Figure A.1 | (A) Window stack (B) Window overlap                            | 45 |

| Figure A.2 | Processor State Register (PSR)                                 | 45 |

| Figure A.3 | Window Invalid Mask (WIM)                                      | 46 |

| Figure A.4 | Trap Base Register (TBR)                                       | 46 |

| Figure A.5 | Processor instruction pipeline                                 | 47 |

| Figure A.6 | Pipeline with all single-cycle instructions                    | 48 |

| Figure A.7 | Pipeline with a LOAD instruction                               | 48 |

| Figure A.8 | Delay instruction                                              | 49 |

| Figure A.9 | Instruction format                                             | 51 |

## List of tables

| Table 5.1 | Functions of VME-interface with offset address | 28 |

|-----------|------------------------------------------------|----|

| Table 5.2 | Function selection with base addresses         | 30 |

| Table 5.3 | Line buffer selection with data bit 0          | 31 |

| Table A.1 | Differences between RISC and CISC              | 43 |

| Table A.2 | Internally generated opcodes                   | 49 |

| Table A.3 | Valid data bus for bytes and half words        | 50 |

| Table A.4 | Trap levels                                    | 53 |

|           |                                                |    |

## **1** Introduction

In the production of PCBs much has changed during the last years. The sizes of resistors, capacitors, integrated circuits etc. are getting smaller and smaller. They are placed on the print by machines and nowadays the production of a PCB is checked after every process phase to maintain quality. For this last step Philips CFT (Centre For manufacturing Technology) is partner in the ESPRIT project #2017: TRIOS. Within this project Philips CFT is developing an in-line PCB inspection system. The PCBs are suitable for surface mounted devices (SMD) technology. The inspection system will check the PCBs after the solder paste (= a composure of solder tin and solder flux) has been laid on the solder pads. The purpose of the system is to decide wether or not the solder paste on the PCB is on the right position and has the right volume. When for instance the solder paste isn't at the right position it can cause short circuits or when the volume is too less the SMD will not be connected properly.

As a part of the inspection system the Area Segmentation Processor (ASP) segments the data information from a PCB. This segmentation is necessary for the distribution of the data over the calculation processors and to reduce the data of a PCB so that only interested areas are checked.

The hardware of the Area Segmentation Processor is designed by F.G.M. Smeets who graduated in august 1992 on this design  $([SME]^1)$ . I continued the work with the Area Segmentation Processor. My graduation assignment was:

- build and test the hardware of the ASP,

- develop the software and

- integrate the ASP in the inspection system.

The assignment was carried out by:

- studying the inspection system,

- studying the functions and the schemes of the ASP,

- studying the processor of the ASP,

- making worst case calculations of the timing of the different components,

- connecting and testing the ASP part by part,

- integrate the ASP in the system and writing software for receiving small images so that no segmentation has to be done and

- writing the segmentation software after studying the system development schemes.

<sup>&</sup>lt;sup>1</sup> Reference to literature list at page 42.

The results at the end of the graduation period are that the Area Segmentation Processor has been built and tested. It has been implemented in the system and for small images where no segmentation is necessary the software is written and tested. The segmentation software is written but not tested.

This report describes the realisation of the Area Segmentation Processor. Chapter 2 gives the different functions of the inspection system. In chapter 3 the hardware of the ASP is split into functional blocks. An outline of the software is given in chapter 4. Changes in the hardware are given in chapter 5 and the implementation of the software is given in chapter 6.

## 2 In-line PCB inspection system

The PCB inspection system must be suitable to inspect PCBs after the solder paste has been laid on the PCB. The volume and position of the solder paste must be between certain bounds. PCB sizes are up to 50x30 cm and the inspection time for the largest PCB is maximal 50 seconds. The inspection has to be done with a resolution of 25 µm. With these demands the system is designed. In the first paragraph the design of the inspection system is split into blocks. The function of each block is explained there. In the second paragraph the data processing system, which is a block of the inspection system, is further split into functional blocks and these blocks are explained.

## 2.1 Global explanation of the system

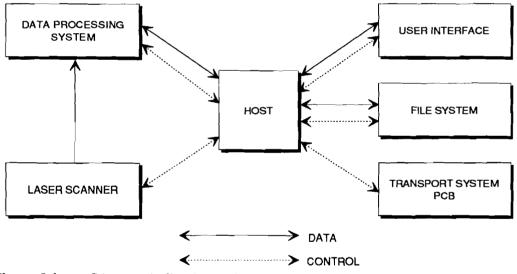

A global diagram of the in-line inspection system is given in figure 2.1. The lines represent data flows and the dotted lines represent control flows.

Figure 2.1 Diagram in-line inspection system

The function of each block is:

- host. The host controls the entire system.

- laser scanner. The laser scanner extracts image information from the PCB by means of a laser beam. The reflected light is translated into two data streams: height and intensity data. The height data is used for the volume measurement and the intensity data for the position measurement. These two streams are sent to the data processing system.

- data processing system. The data processing system selects the solder pad information from the data streams and calculates the position and volume of the solder paste. The solder pads are found using data from the host (which gets it from the file system), called CAD-data. What these data are will be explained later. The results of the calculations are sent to the host.

- user interface. The user interface handles the communication between an operator and the host computer. It is necessary to give information about the status of the running process to the operator or to give commands to the host about starting the inspection of a new PCB. The data stream from the user interface to the host represents new CAD-data, which is necessary when inspection of a new PCB starts.

- file system. The file system is used to store data about the status of the process and to store CAD-data.

- transport system. The transport system brings PCBs to the laser scanner. After inspection of the PCB, it sorts the PCBs into approved and disapproved ones. The sorting is controlled by the host which gets the information from the data processing system.

## 2.2 Data processing system

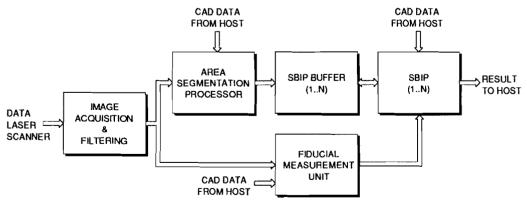

A diagram of the data processing system is given in figure 2.2. The function of each block is:

- image acquisition & filtering. The image acquisition & filtering block has a pre processing function. The laser data are sent to this block. The data are sent through a look up table for conversion of the height and intensity data. This can be used to obtain better contrast. The other function of this block is to put the images on the data bus with the right control signals.

Figure 2.2 Diagram of the data processing system

- area segmentation processor (ASP). The function of the area segmentation processor is to buffer the data received from the acquisition and filtering block, distribute the data over the SBIPs and reduce the data send to the SBIPs. The distribution is done by combining Areas of Interest (AOIs). The AOIs are specified in the CADdata and is received from the host. The combined AOIs (called screens) are sent to the SBIPs in a suitable format (512 x 512 pixels). The host controls to which SBIP the screen is sent. The laser scanner doesn't have to be stopped with the buffer and distribution function of the ASP.

- SBIP buffer (1..N). The SBIP buffer is used to store a screen so that the SBIP can be active continuously. In this way the memory of the ASP can be small.

- SBIP (1..N). The SBIP does the volume and the position calculations of the solder paste. These calculations are done by software algorithms and are therefor relatively slow. To compensate this, a number of SBIPs work in parallel. The host controls the assignment of screens to the SBIPs. The results of the calculations in the SBIPs are sent to the host.

- fiducial measurement unit (FMU). The position accuracy of the PCB in the laser scanner is limited. A small displacement can lead to a deviation which amounts to several pixels. The second problem is that the PCB isn't always perfectly flat. This gives a deviation that varies with the position on the print. The fiducial measurement unit, locates fiducials (characteristic shapes, for example corners in a copper track) using the CAD-data received from the host (originating from the file system) and calculates the displacement between the expected positions and the measured. The displacement vectors are sent to one of the SBIPs.

## **3** Hardware of the Area Segmentation Processor

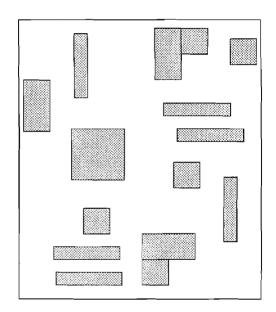

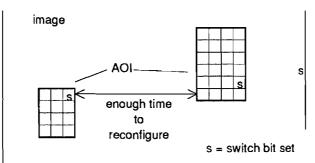

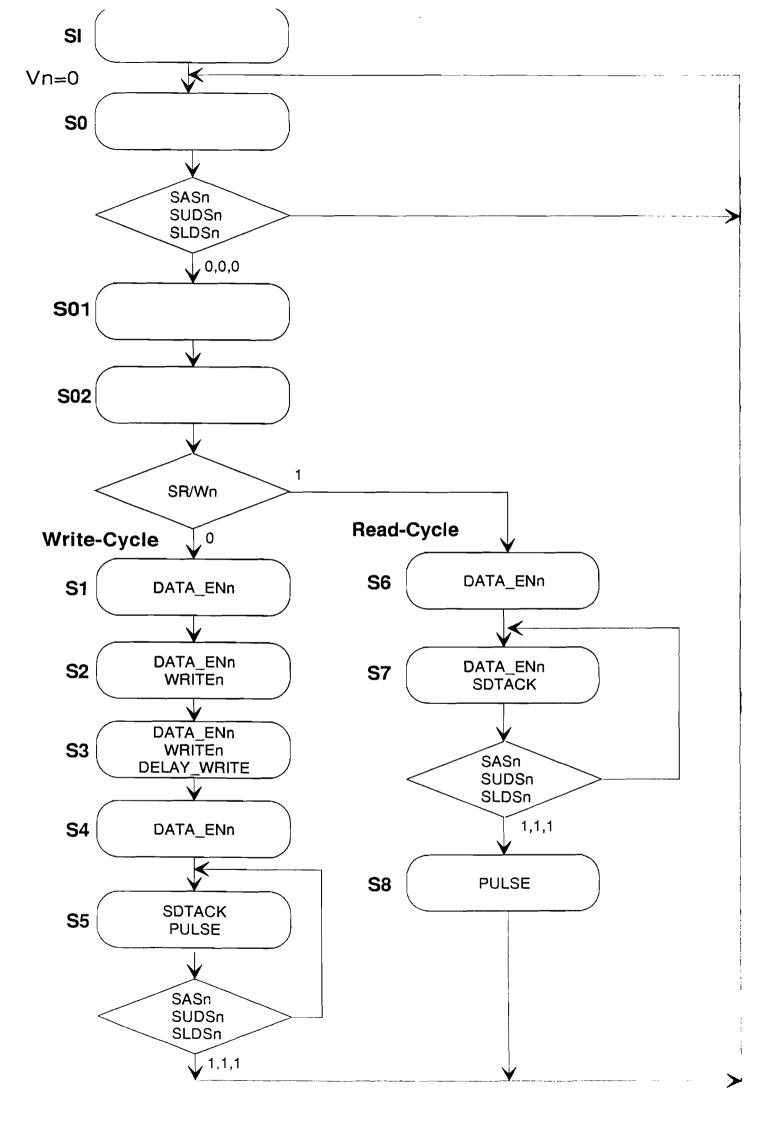

As written in the previous chapter the ASP receives an image from the acquisition board and CAD-data from the host. It segments the specified AOIs and composes them into new screens so that only interested areas are sent to the SBIPs. Combining the AOIs into screens is done by software. The function of the ASP depicted in figure 3.1.

Figure 3.1 Example of image to screen transformation

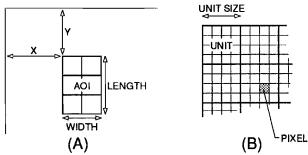

In order to reduce the work for the ASP processor an image is divided into units. A unit is a square which contains 16, 64, 256 or 1024 pixels, depending on the chosen unit size<sup>1</sup> (4, 8, 16 or 32). The reason for this is to give the processor more time for other calculations. When a unit has to be saved, the processor must change the stored information only once per four (eight, sixteen or thirty two) lines. The relation between pixels, units and AOI can be seen in figure 3.2(B). In this figure the definition of an AOI is also given.

Figure 3.2 (A) Definition of an AOI, (B) Relation between pixel, unit and AOI

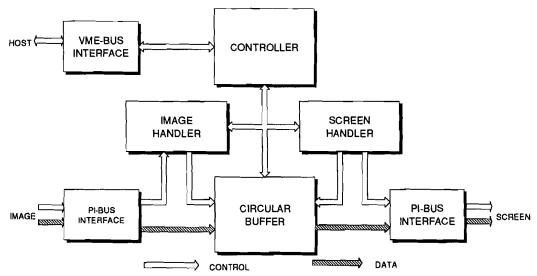

The hardware of the ASP is split into blocks. This is given in figure 3.3. Receiving and segmenting is done by the PI-bus interface and the image handler. After storing the AOIs into a circular buffer a screen is composed by the screen handler and sent to an SBIP by the PI-bus interface. A further explanation of the function of each block is given in the next paragraphs.

<sup>&</sup>lt;sup>1</sup> It is an agreement that the length of a unit is called unit size.

Figure 3.3 Block diagram of the Area Segmentation Processor

## 3.1 Controller

The controller controls the segmentation of the images and the composition of the screens. The processor used is a RISC processor. More about this processor in appendix A. The control block contains two RAMs, one for the program and one for the CAD-data. These RAMs are initially filled via the VME-bus interface. The tasks of the controller are:

- controlling the image handler

- controlling the circular buffer

- controlling the screen handler

- communication with the host (via the VME-bus interface)

- calculating the composition of a screen.

## **3.2** VME-bus interface

The functions of the VME-bus interface are:

- downloading the program

- downloading the CAD-data

- interrupt handling between the ASP and host

- transferring CAD-data from host to ASP

- transferring screen composition information from ASP to host.

During the downloading process, the processor is switched off and the VME-bus interface controls the data- and address bus of the ASP. Normally the processor can't be switched off very easily so when more CAD-data is needed from the host, the host puts this

information in a specific memory, the communication buffer. When sending CAD-data, the processor reads the communication buffer and puts the data in the RAM.

The communication buffer is also used when the screen composition is sent to the host. The screen composition data is data which specifies in which screen an AOI is placed and where in that screen the AOI is placed. Asking more CAD-data or signalling that composition data is ready in the communication buffer is done on interrupt basis.

## 3.3 Image handler

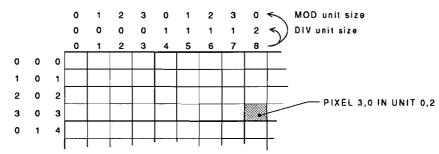

The segmentation takes place in the image handler. From the CAD-data the image handler knows which units have to be saved. Therefor it is necessary to give a unique identifier to every incoming pixel. This is done by a line counter and a column counter. The values of column counter and line counter can be seen as a coordinate. Dividing the counter values by the unit size will give the unique identity of the units. This can also be seen in figure 3.4.

Figure 3.4 Unique identifier pixel and unit

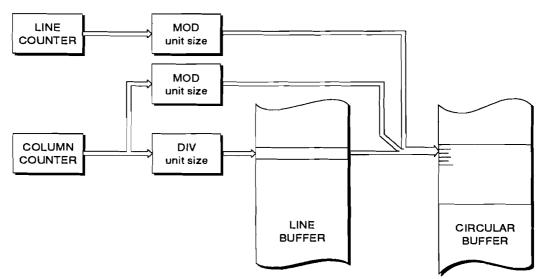

The positions of the AOIs are known from the CAD-data. The processor has to convert this information to the current scan line. This is done by coupling an address to each unit and placing it into a line buffer. This address denotes the start address of each unit in the circular buffer (most significant part). If a unit doesn't have to be stored the start address will be set to a dummy value of zero. The least significant part of the address in the circular buffer is formed by the least significant bits of the line counter and column counter. The principle is shown in figure 3.5.

The line buffer is filled by the processor. Because the pixels arrive continuously two line buffers are used, one for filling the circular buffer and one is filled by the processor. The two line buffers swap their function when "unit size" lines are received.

Figure 3.5 Address generation for writing units

#### 3.4 Screen handler

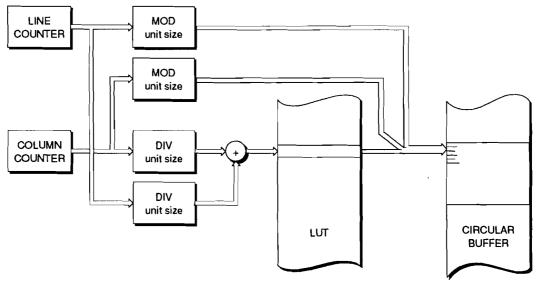

After storage in the circular buffer a screen is sent to an SBIP. The screen handler composes a screen. A line counter and a column counter are used for identification of a pixel in the screen (same principle as image handler). The address for the circular buffer is now generated by a two dimensional Look Up Table (LUT). Here it is chosen for two dimensions because the LUT needs only 16 k addresses (512\*512 pixels / minimal unit). When using a LUT in the image handler, the LUT should have more then 15 million addresses. The advantage of a LUT is that only once per screen the LUT has to be filled. The address generation of the screen handler is given in figure 3.6. The other function of the screen handler is to generate the screen control signals.

Figure 3.6 Address generation for reading units

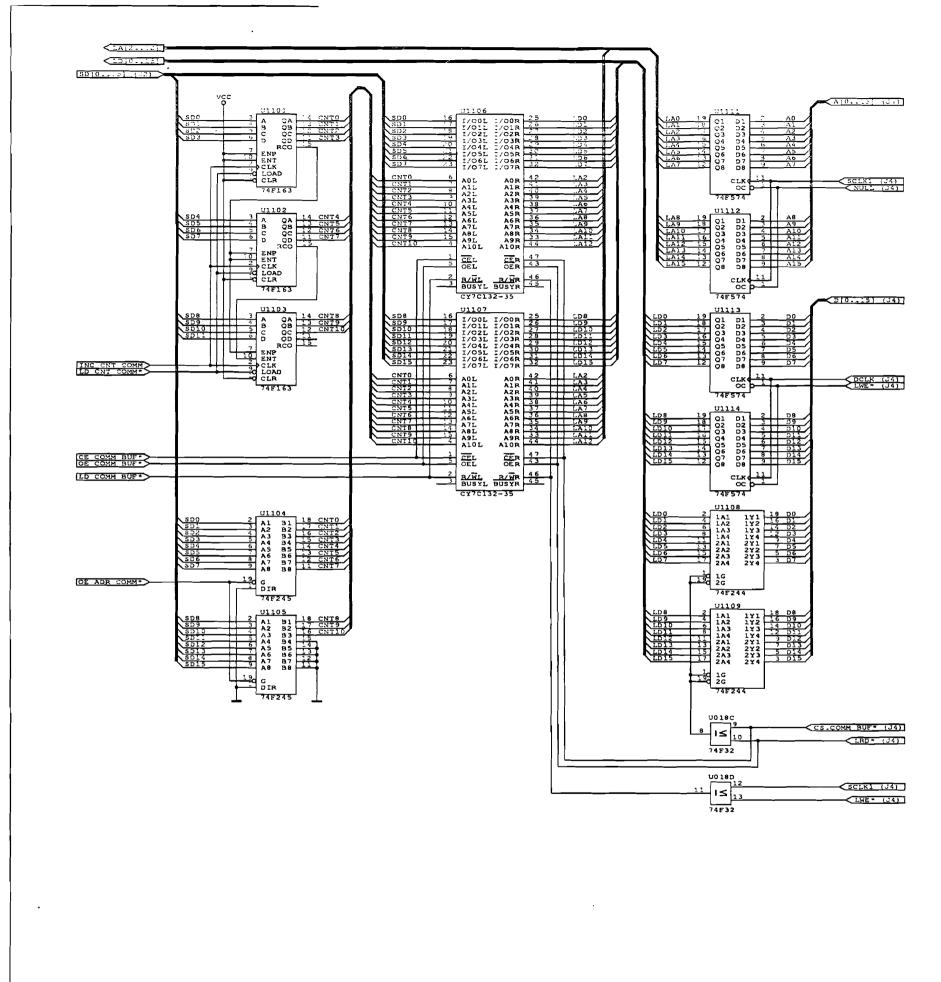

## 3.5 Circular buffer

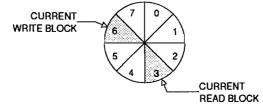

The circular buffer is used as storage for the AOIs of an image. The circular buffer contains  $256k \times 16$  bits, so one screen fits into the memory. Each incoming AOI is stored in the buffer until it has to be sent as a part of a screen. The memory is circular and divided into eight blocks. The eight blocks are related to the hardware components. The RAMs are  $32k \times 16$  bits separated I/O (two separated data busses per RAM). The advantage is that when writing one block the other blocks can be read. The principle of the circular buffer is given in figure 3.7.

Figure 3.7 Principle of circular buffer

The blocks are random access which gives the opportunity to read and write in eight blocks randomly. In this way the screen composition doesn't depend on the sequence of the AOIs in the image.

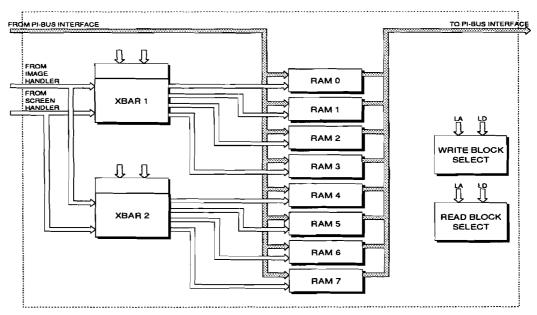

The addresses are generated by the image handler and the screen handler. The number of bits of the addresses generated by the handlers is such that one RAM block can be addressed. Two crossbars lead the address to the correct RAM block. The controller configures the crossbars and sets the write and read block selection. A functional diagram of the circular buffer is given in figure 3.8.

Figure 3.8 Functional diagram of circular buffer

## **4** Software for the Area Segmentation Processor

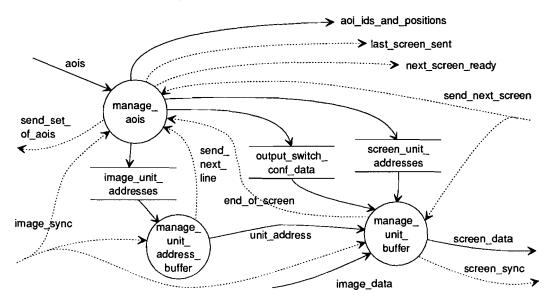

In the previous chapter the hardware of the area segmentation processor was explained. This chapter gives an outline of the software. This is done by schemes made with Promod. Promod is a highly automated system engineering environment to develop a detailed specification for systems. The solid lines in the schemes represent data flows, the dotted lines represent control flows, the circles represent functions, two parallel lines with data flows to or from it, represent data stores and the lines with control flows to/from it represent state machines (see figure 4.2). The functions in the schemes are implemented in hardware or in software.

A functional diagram of the ASP in Promod is given in figure 4.1. The Promod diagrams in this chapter are explained so far that the function of the software is evident. For more information see the report by P. Boots ([BOO]).

Figure 4.1 Functional diagram of the Area Segmentation Processor

The data flow image\_data and the control flow image\_sync come from the image acquisition and filter block (see figure 2.2). Screen\_data and screen\_sync go to one of the SBIPs (see figure 2.2). The other flows are to or from the host. A further explanation of the functions and flows is given in the following paragraphs.

## 4.1 Manage AOIs

The function manage\_aois has several tasks. These are:

- calculating the screen composition, i.e. how and in which screen the AOIs are placed,

- calculating the line buffer content,

- calculating the screen content, which is stored in screen\_unit\_addresses,

- asking the host for more AOIs,

- signalling when a screen is ready,

- signalling when the last screen is sent and

- signalling in which screen the AOI is placed and its position in the screen.

Synchronising the screen calculations is done with send\_next\_screen. The relation between the tasks of manage\_aois is given in figure 4.2.

Figure 4.2 Functional diagram of manage\_aois

All the functions in manage\_aois are implemented in software.

#### 4.1.1 Compute Lines

The function compute\_lines is responsible for segmenting the image. It computes the addresses on which the units of the AOIs are stored. The addresses are stored, line by line, in image\_unit\_addresses. These lines are later placed in the line buffer. A unit of an AOI gets a unique address within a block of the circular buffer. A unit which doesn't have to be saved receives address zero. The addresses for the units within an AOI are given in the order they arrive. Units which lay in two or more AOIs (overlap of AOIs or doubles) get only one number. When the list of AOIs becomes to short a signal send\_set\_of\_aois is sent to the host. An example of the address assignment is given in figure 4.3.

Figure 4.3 Addresses for the units in an AOI

Calculating a line for image\_unit\_addresses is done by checking for every unit in the image if that unit is in an AOI. The list of AOIs is sorted to shorten this searching. It is first sorted on increasing y-coordinate because the image arrives row by row (the y). AOIs with the same y-coordinate are then sorted on x-coordinate because the units in one line arrive with increasing x-coordinate.

The store image\_unit\_addresses is stored in a RAM on the ASP. Every line needs maximal 3000 half words (16 bits) of the RAM. Calculating and storing the whole image (maximal 5000 lines) in advance would cost too much RAM. Therefor only a few lines are calculated in advance.

As written in paragraph 3.5 the circular buffer consists of eight blocks. Switching or reconfiguring these blocks is activated by setting bit 11 of the unit address. Setting this bit is done by compute\_lines. Switching can only be done when there is enough time to reconfigure the blocks. So the switch bit may only be set:

- at the end of a line or

- at the last unit of an AOI in a line or

- between two AOIs when the time between them is enough.

Hereby it is assumed that the time between the end of the image line and the start of the next line is enough to reconfigure. This is also depicted in figure 4.4.

Figure 4.4 Examples of places for the switch bit

#### 4.1.2 Combine AOIs In Screens

The function combine\_aois\_in\_screens combines the received AOIs into one or more screens. An example has already been given in figure 3.1 where the function of the ASP is depicted. This combining of AOIs results in four data flows:

- screen\_maps. Each screen map is a two dimensional array holding addresses from the units of the AOIs in the screen. This screen map can later be placed in the LUT.

Screen 1 2 3 4 5 6 7 21 22 23 8 9 10 11 12 13 14 30 31 32 15 16 17 18 19 20 21 37 38 39 24 25 26 27 28 29 30 44 45 46 33 34 35 36 40 41 42 43 AOIs

The screen map of figure 4.3 is given in figure 4.5.

Figure 4.5 Example of a screen map with the addresses

- output\_switch\_conf\_data. The circular buffer is divided into eight blocks. Therefor it is

necessary to reconfigure the crossbar switch. In the screen map, bit 11 of a

unit\_address, activates this switching. In output\_switch\_conf\_data is specified to

which block of the circular buffer must be switched.

- aoi\_ids\_and\_positions. Where the AOIs are placed in the screen depends on the filling algorithm. Because of the calculations, the SBIP must know which AOI is in which screen and on which position in the screen. This information is held in aoi\_ids\_and\_positions.

- final\_lines. In order to signal the SBIP that the next screen can be sent, the final\_lines of each screen i.e. the image line number that contains the last pixels of the screen, must be known.

In compute\_lines the switch bit could only be set when there is enough time. Here it must be possible to set the switch bit of every unit address, because the filling algorithm decides where the AOI is placed. Thus it is possible that one AOI is stored in block 0 of the circular buffer and that the AOI which lays next to it in the screen is stored in block 1. The hardware is made so that the sending of a screen stops if the switch bit is detected. The crossbar can then be reconfigured by the software and the software restarts the sending.

Combine\_aois\_in\_screens searches a way to fill the screens with AOIs. This filling has conflicting demands:

- The screen must be filled as much as possible because the unused units take time when a screen is sent to the SBIP.

- The calculation time and algorithm length increase a lot when a high filling grade is wanted. Another aspect here is that when the "best" fitting is found units are kept for a long time in the circular buffer. The circular buffer on the ASP is limited so it is desirable that the units are sent away as soon as possible.

- The traffic on the VME-bus must be limited because this will delay the other VME traffic.

With these demands the function combine\_aois\_in\_screen can be located and performed in three different ways:

- An off line process on the host. The host calculates the filling of the screens and the unit addresses for the line buffers and LUT. Advantage of this is that there is enough calculation time to find the "best" fitting and this has to be done only once. Disadvantage is that a mass store is needed and that the down loading gives an enormous VME traffic. Remember that an image can have 5000 lines with 3000 units in it. This means that in this case 15 mega addresses must be down loaded plus 1.5 mega addresses for the screens, assuming that 10 % of the image are AOIs and that the screens are full.

- An off line process on the host for the filling of the screens and the address calculation on the ASP. The advantage is that there is enough calculation time and the filling calculation has to be done only once. The address calculation must be repeated for every image. The only data that must be down loaded are the AOIs and the positions in a screen.

- Everything on the ASP. Disadvantage is that the search algorithm can't be complex because of time and algorithm length. Advantage is that only the AOIs must be down loaded to the ASP and the positions must be loaded to the host.

Testing must decide what the best option is but so far it seems that the second option is the best.

#### 4.1.3 Send Ids And Positions

The function send\_ids\_and\_positions signals to the SBIPs which AOIs are in the screen that is sent to that SBIP and the positions of the AOIs within the screen. The sending is activated with send\_next\_screen. This routine runs on the host if the combining algorithm runs on the host.

#### 4.1.4 Control Screen Retrieval

The function control\_screen\_retrieval waits until the received image line is greater than the next final line in final\_lines and then signals next\_screen\_ready and fills the store screen\_unit\_addresses (the LUT) with information from screen\_maps. These actions may be started only if manage\_unit\_buffer is not sending a (part of a) screen (seen by end\_of\_screen).

Combine\_aois\_in\_screens calculates screen maps which are stored in memory. Parts of these maps are later stored into the LUT if that part of the LUT is free. One screen map takes 16 k half words. The memory on the ASP is not so big, so only a part of the screen map can be stored here. A functional diagram of control\_screen\_retrieval is given in figure 4.6.

Figure 4.6 Functional diagram of control\_screen\_retrieval

The function incr\_current\_line updates the store current\_line every time image\_sync is activated. Current\_line keeps the number of scanned lines of the image. When current\_lines is greater then final\_lines, compare signals greater\_or\_equal what results in an active next\_screen\_ready. When the last element of final\_lines is used no\_more\_screen\_maps is activated. With this signal last\_screen\_send is activated after end\_of\_screen returns. Fill\_screen\_unit\_address\_buffer takes a part of the screen\_map and places it into the screen\_unit\_addresses.

## 4.2 Manage Unit Address Buffer

Manage\_unit\_address\_buffer gets one line of the image\_unit\_addresses, transmits unit\_address one by one and asks for the next line at manage\_aois when a line is sent. This is done under control of the image\_sync signal. A functional diagram of manage\_unit\_address\_buffer is given in figure 4.7.

One line of image\_unit\_addresses is stored into one of the two line buffers "unit\_address\_buffer\_1" or "unit\_address\_buffer\_2" by "fill\_ua\_buffer". If a new line is wanted the signal send\_next\_line is sent to manage\_aois. Send\_next\_line is activated after every 4, 8, 16 or 32 lines of the image depending of the chosen unit size. The "empty\_ua\_buffer" functions empties the store.

Figure 4.7 Functional diagram of manage\_unit\_address\_buffer

The stores are RAMs (the line buffer in figure 3.5) of which each can hold one image line. The empty function is implemented in the hardware. Counters generate an address for reading the RAMs. The filling function is implemented in software. The fill function copies one line of unit\_addresses to the RAM. Multiplexers control which buffer is filled and which buffer is emptied. The signal send\_next\_line is implemented as an interrupt to the processor on the ASP.

## 4.3 Manage Unit Buffer

Manage\_unit\_buffer stores the pixels from image\_data at addresses specified by unit\_address of manage\_unit\_address\_buffer at a rate controlled by image\_sync. The other function of manage\_unit\_buffer is sending screens under control of the screen map in screen\_unit\_addresses. The sending starts after the signal send\_next\_screen. When a screen is sent, manage\_aois is signalled by end\_of\_screen. The functional diagram of manage\_unit\_buffer is given in figure 4.8.

Keep in mind here figure 3.8. The stores unit\_block\_0 to unit\_block\_7 in figure 4.8 are RAM0 to RAM7 in figure 3.8. The functions direct\_to\_current\_write\_block an collect\_from\_current\_read\_block are performed by the two crossbars (xbars). Generate\_pixel\_in\_unit\_address\_input and -output are two counters which generate an address used to write or read the pixel within a unit. Decode\_image\_unit\_address receives the unit\_address and signals by reconf\_input\_code\_encountered (an interrupt to the processor) if the reconfigure code (bit 11 of the address) has encountered. Decode\_screen\_code\_address does the same but then for screen\_unit\_addresses.

Figure 4.8 Functional diagram of manage\_unit\_buffer

Select\_new\_write\_block is implemented in software. As soon as a block is full or almost full a new write block must be selected. Select\_new\_write\_block is activated by reconf\_input\_code\_encountered. Select\_new\_read\_block does the same, but here the data to which block must be switched comes from output\_switch\_conf\_data. The selected read and write block are stored in current\_blocks. This store is a hardware store, which enables read en write signals for the appropriate block and a variable for the program.

## 5 Implementation of the hardware

The work during my graduation period was the realisation of the Area Segmentation Processor. First the timing conditions (set up time, hold time, delay time) were theoretical checked with worst case calculations. Secondly the hardware was measured. This to check the wire wrap connections. Where necessary improvements were made.

For testing the ASP several programs are written. The programs which run on the ERM system (the host), are written in C. The programs which run on the ASP, are written in assembly or in C.

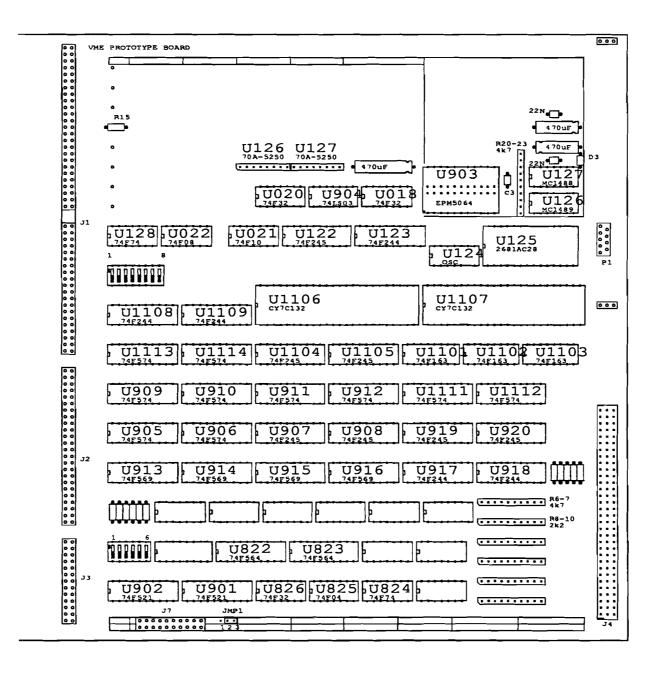

In the following paragraphs several parts of the hardware are discussed. Changes and additions in the design which are mentioned in the following paragraphs are made by the author of this report. Further outlines about the programs for testing the hardware are given. In appendix B the schemes of the area segmentation processor are given.

## 5.1 VME-interface

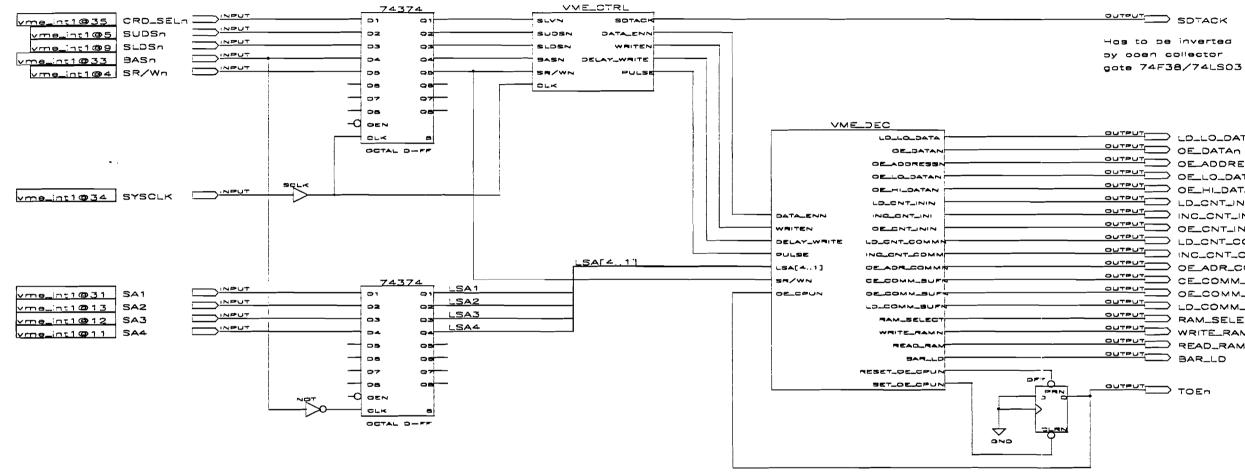

The different cards in the system (host, acquisition card, ASP, SBIPs) communicate via a VME-bus. The image and screen data are sent via two picture busses. VME (= Versa Module Eurocard) uses a protocol for data transfer and interrupt handling (see [VMS]). For correct handling of the protocol a special prototype board (see [VMP]), was used. Data send to the ASP appears on the prototype board. Placing the data on the correct address is done by the VME-interface (scheme in appendix B.9). Getting data from the correct address on the ASP, starting an interrupt action to the host and starting the acknowledge of an interrupt is also done by the VME-interface. The hardware of the interrupt handling is depicted in appendix B.1 (upper right and lower right in the scheme). Testing and improving the VME-interface had to be done first because downloading programs to the ASP can only be done when this part works.

The circuit of the VME-interface was built first with discrete components and was asynchronously clocked. It was very difficult to add new functions and very difficult to get the correct functionality. For these reasons a redesign has been made. The circuit is implemented in an Erasable Programable Logic Device (EPLD). The design has been made, simulated and programmed with MAX+plus.

Some functions are added to the new design. The several functions are reached by a card address plus an offset address. The different functions with the offset address are given in table 5.1.

| Function                                | offset address |

|-----------------------------------------|----------------|

| disable CPU                             | 2              |

| enable CPU                              | 4              |

| read/write counter RAMs                 | 6              |

| read/write counter communication buffer | 8              |

| read/write communication buffer         | 10             |

| read/write bit 150 program RAM          | 12             |

| read/write bit 150 CAD RAM              | 14             |

| read/write bit 3116 program RAM         | 16             |

| read/write bit 3116 CAD RAM             | 18             |

| write bus allocation register           | 20             |

#### **Table 5.1**Functions of VME-interface with offset address

The address range for the host to access the ASP is only 2 k big. This is not enough to map the whole memory of the ASP within the address range of the host. Therefor a counter is used which generates the address on the ASP during downloading. These counters have to be filled with the start address.

The ASP has a 32 bit data bus. The ERM system has only a 16 bit data bus. Downloading data is done by first downloading the lower 16 bit word and than the higher 16 bits. After this second action the data is written in the RAM and the counter is incremented. Reading is done by first reading the lower 16 bits and than reading the higher 16 bits.

Testing the VME-interface is done by writing (downloading) data to the RAMs on the ASP, reading back and comparing the written and read data. With these tests also the read and write signals for the RAMs are verified.

The circuit for the interrupt from the ASP to the host and from the host to the ASP was originally not designed. This part is necessary, for several signals (send\_set\_of\_aois, last\_screen\_send, next\_screen\_ready and send\_next\_screen in figure 4.1) and therefor added.

The communication buffer is used for sending information between the host and the ASP at the time the ASP is running. After power up the data is downloaded to the ASP and the communication buffer isn't used then. The processor must be disabled at that time. When the processor is started the processor can't be disabled because after enabling, the processor won't continue were it was stopped. To send information to the ASP, if the processor runs, the communication buffer is used. The communication buffer is tested by means of writing data into it and reading back. This writing and reading is done by the host and the ASP.

## 5.2 Controller

A SPARC RISC processor CY7C611 controls the ASP. This processor works with a clock frequency of 25 MHz. More information about the processor, especially for programming the processor in assembly, is given in appendix A.

When downloading data to the ASP or reading data from the ASP to the host, the processor must be switched off (disabled). All output drivers are then in high impedance state (tri-state). Therefor it is necessary to connect pull up or pull down resistors at all outputs of the processor which are used in other parts of the circuit.

Two RAMs are connected to the processor. One to store the program and one to store the CAD-data. After downloading, the processor is started by the reset circuit. To test the communication between processor and RAM a program can write a certain data pattern into the RAMs (except the part where the program is stored). The host can read and evaluate the data.

To give information about the status of the program there is a circuit which communicates with a terminal (RS232). When a program is running it can be useful to know in which function the program is and what the values of certain variables are. The conversion from parallel to serial, visa versa, is done by a DUART. The timing of the selection, write and read signals for the DUART are improved because they did not fulfil the specifications.

An other problem which showed up when working with the DUART was that the RAMs are not byte accessible. The program RAM is only 32 bit accessible and the CAD RAM is 16 bit accessible. The standard function "printf" in C, which prints text on the terminal, writes bytes to the RAM to store temporary information. Writing one byte in the program RAM overwrites also three other bytes (the ones with the same address except the two least significant bits). Routines which use byte or half word variables can thus not be used on the ASP. New routines are written to solve this problem because it is not possible to make the RAMs byte accessible.

Not all the components are fast enough for the used clock frequency. Therefor there is a circuit that can stretch the clock. In figure 5.1 an example of the stretched clock is given with the clock 2 times stretched. Bit 23 of the address bus enables the stretch circuit. The number of stretch cycles is the value of the difference: 8 - the value of bit 22..20.

Figure 5.1 Example of a 2 times stretched clock

The different components are selected with bit 19..16. In table 5.2 the different functions are given with the base addresses.

| function           | base address bit 230 | function                | base address bit 230 |

|--------------------|----------------------|-------------------------|----------------------|

| program RAM        | 0x000000             | enable continue screen  | 0x080002             |

| CAD RAM            | 0x010000             | line buffer             | 0x090002             |

| DUART              | 0x920003             | unit size/mode          | 0x0a0003             |

| crossbar 1         | 0xf30002             | interrupt host          | 0x8b0003             |

| crossbar 2         | 0xf40002             | communication buffer    | 0xfc0002             |

| LUT                | 0x050002             | line buffer selection   | 0x0d0003             |

| LUT selection      | 0x060003             | data circular buffer    | 0x8e0002             |

| enable send screen | 0x070002             | address circular buffer | 0x8f0002             |

**Table 5.2**Function selection with base addresses

In the previous chapter number of control signals а are given. Reconf\_input\_code\_encountered, reconf\_output\_code\_encountered, end\_of\_screen, next\_line and the signals from the host are implemented as interrupts to the processor. The interrupt handler converts an interrupt into an interrupt address. This handler is implemented in an EPLD. After power up all flip flops in the EPLD should be zero. Measuring learned that this was not so. Therefor a reset signal is connected to the flip flops in the EPLD so that after the power supply is stable the flip flops are reset.

## 5.3 Image handler

Multiplexers decide to which line buffer the processor can write and which line buffer is read by the counters. The position of the multiplexer depends on a flip flop. In the original design the processor was not able to control that flip flop. After power up the value of the flip flop is random 0 or 1, so which line buffer is selected for the processor is unpredictable. It is necessary to control the flip flop because the line buffer which is connected to the counters, must be switched to the RAM block in the circular buffer by the crossbars. Therefor a circuit is added which enables the processor to set the selection of the flip flop depending on data bit 0 (base address line buffer selection). In table 5.3 is the selection given with data bit 0.

| data bit 0 | processor to: | counter to:   |

|------------|---------------|---------------|

| 0          | line buffer A | line buffer B |

| 1          | line buffer B | line buffer A |

Table 5.3Line buffer selection with data bit 0

The line buffers are tested by writing data in the line buffers and then reading the data back. Reading back can not be done directly because the outputs of the line buffers are not connected to the data bus of the processor. This is solved by adding drivers between the address lines of RAM block0 and the processor data bus. The processor addresses the driver (the offset of the address is lead to the line buffer) and reads the data of the line buffer through the crossbars (when configured in the right way).

The RAMs of the line buffers have only a chip select input and a combined read/write input. When reading or when writing while the write pulse is not active the output drivers are active (an other RAM is not possible as separate I/O is needed). The combination of bit 11 of the line buffers is the reconf\_input\_code\_encountered signal from figure 4.8. When one of the bit 11 is set, the processor is interrupted. The addresses of the processor are always lead to one of the line buffers. Therefor it is possible that an address of the processor is an address of which bit 11 is set. This will interrupt the processor but the processor may only be interrupted when the counter reaches such an address. Components are added to the scheme so that only an interrupt occurs from the line buffer that is connected to the counters and only after the data is valid.

## 5.4 Screen handler

Testing the LUT is done in the same way as testing the line buffers. Data is written in it and then read back through the address driver of RAM block0 of the circular buffer (this is the reason why they are placed after the crossbars).

Reading the LUT back works only when the screen clock runs because a latch between the LUT and the crossbars is clocked by the screen clock. The screen clock (defines the pixel rate) is a clock which is controlled by screen handler. When the crossbar must be reconfigured this clock is stopped by bit 11 of the LUT (reconf\_output\_code\_encountered in figure 4.8). After power up when the LUT isn't initialised, the clock can be stopped

when an address appears where bit 11 is one. To solve this problem two things are changed:

- first: bit 11 may only interrupt the processor and stop the clock when the counters are connected to the LUT

- second: the EPLD screen handler is changed so that there is a possibility to start the clock.

This second improvement is necessary because the clock can still be stopped when bit 11 of address 0 of the LUT (0 is start value of the counters) is 1.

When the clock is stopped by bit 11 the processor can restart the screen sending if it writes to address "enable continue screen" in table 5.2. This is not useful when the screen clock is stopped after power up. Therefor data bit 0 is used now when writing to "enable continue screen":

data bit 0 = 0: continue sending data bit 0 = 1: enable only the clock

## 5.5 Circular buffer

The circuit that generates a write pulse for the RAM blocks was not designed. This had to be done first. Further the timing of the write pulse for the crossbar is improved.

As written in the two previous paragraphs there is an address driver which can read the addresses of RAM block0. The processor can't read (in the first design) the data that is written in the circular buffer. This makes it very difficult to test if there is an error made when writing the data or when reading the data. To solve this problem a second driver is added which connects the output data bus (screen data bus) to the processor data bus. To read the data a number of actions has to be done. For example reading the data in the first block sequentially the following action must be done:

- the RAM block must be selected

- the line buffer must be filled

- the crossbars must be configured in the right way.

The line buffer has 11 data lines connected to the crossbar. A RAM block of the circular buffer has 15 address lines. Normally 4 address lines (when the unit size is 4) come from the counter which generate the addresses within a unit. Now these address lines must be set by the crossbars. This is possible because the crossbar can set every output in different mode: flow through (used normally), pipeline, fixed output levels (0 or 1). With the line buffer outputs connected to the first 11 outputs of the crossbar and the following 4 outputs set to zero the first part of the RAM block can be read. Reconfiguring the 4 output makes it possible to read the other parts of the RAM block.

## 5.6 Picture bus interface

In the first design there was only one input channel on which the image data is received from the acquisition board and one output channel on which the screen data is sent to the SBIPs. In the system there are two channels and every card is made so that the host decides on which channel each card receives data and on which channel it may send data. To fulfil this option the picture bus interface is extended with components and the VME-interface handler is extended with an address that writes data in the bus allocation register. This bus allocation register selects the read and write channel.

## **6** Implementation of the software

In this chapter some remarks on the implementation of the software are given. A program which receives and sends images of 512x512 pixels is used for testing the ASP hardware in the system. In the first paragraph an outline and remarks are given about this program. The second paragraph gives some points for the implementation of the segmentation software. This software is not completely built because there was not enough time to do this. The reason herefor was that the improvement and implementation of the hardware took more time than was expected. The third paragraph shows how C programs can be improved so that less time is needed for execution.

## 6.1 Software 512x512 images

The first major software that is written, except the small test programs, is for receiving 512x512 images. These images are just as big as the screen which is sent by the ASP to the SBIPs. The tasks of the ASP are:

- receiving the image from the acquisition board,

- storing the image in the circular buffer and

- sending the screen to a SBIP.

Here the image doesn't have to be segmented and the CAD-data don't have to be downloaded.

The purpose of this program is to integrate the ASP into the system and test the hardware of the data path (the data path from the PB-bus interface to the circular buffer and from the circular buffer to the PB-bus interface). The data written in the circular buffer can be tested with the method explained in paragraph 5.5. The addresses lead to the circular buffer are tested in an earlier phase.

The program is mostly written in C. Only the trap table, the processor initialisation routine and the routines which communicate with the terminal for debug information, are written in assembly. The sequence of the program is given in figure 6.1.

The line buffers and the LUT are cleared so that no interrupts occur (this is also protected by hardware except for address 0). After the interrupt level is set an interrupt can occur which was pending from before the line buffer and LUT were cleared.

The program sequence when receiving an image is given in figure 6.2. After "unit size" lines are received, an interrupt occurs. The interrupt routine that is started then, selects a new write and read block if necessary, configures the crossbars so that the other line

|            | initialisation:<br>clear:  | processor<br>DUART (terminal)<br>crossbars<br>line buffers<br>look up table |

|------------|----------------------------|-----------------------------------------------------------------------------|

|            | set:                       | communication buffer<br>unit size<br>interrupt level<br>variables           |

|            | receive:<br>test:<br>send: | image<br>image data<br>screen                                               |

| Figure 6.1 | Sequence of 51             | 2x512 program                                                               |

buffer is connected to the RAM block and fills the just used line buffer. Selecting a new read block is necessary because the write and read block may not be the same when writing to that block.

| Figure 6.2 | fill the line buffers<br>select the first write block<br>configure the crossbars<br>wait until image is received<br>Sequence of receiving the image |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|            | fill the LUT                                                                                                                                        |

|            | for $i = 0 7$ do                                                                                                                                    |

|            | select read block i                                                                                                                                 |

|            | configure the crossbars                                                                                                                             |

|            | start sending the block                                                                                                                             |

|            | wait until block is sent                                                                                                                            |

| Figure 6.3 | Sequence of sending the screen                                                                                                                      |

The program sequence of sending an image is given in figure 6.3. The listing of the program is given in appendix C. The program given here receives the whole image and then starts sending the screen. Of course this program can be improved. For example sending a block can start after the block has been received and the host can be signalled to start sending an other image. This is not done because it is not necessary for testing and it makes the software more difficult.

#### 6.2 Segmentation software

In chapter 4 an outline of the segmentation software for the Area Segmentation Processor is given. The combining algorithm and the address calculation can run on the host or on the ASP. We choose to run the combining algorithm on the host and the address calculation on the ASP because this has the most advantages (much calculation time available on the host, it is done only once and it gives a low VME-traffic). In this situation the specifications of the AOIs (x, y, length and width) and the position within the screen (screen number, x and y) must be downloaded.

The combining algorithm runs only one time for every PCB type and can be run in advance. Therefor the time needed for the calculation can be large. The limit for the algorithm is the time that AOIs are kept in the circular buffer. The circular buffer can hold only one screen. Because the addresses for the units of an AOI (in compute\_lines figure 4.2) are given the way they arrive, the AOIs in one block must be sent away before this block is selected again as write block. This to prevent a large adminstration for the addresses which may not be used for writing new AOIs in that block.

The first implementation of the combine algorithm (combine\_aois\_in\_screens in figure 4.2) is a simple one. The AOIs are placed in the screen in the way they arrive (and are sorted). When an AOI doesn't fit at the end of the row, it is placed on the next row below the largest AOI of the "full" row. When the AOI doesn't fit into the screen, because it is almost "full", the AOI is placed in the next screen and the "full" screen is not filled further. This algorithm doesn't fill the screen optimal (fill grade between 40 and 60%), but this is enough for the first tests.

Combine\_aois\_in\_screens runs partly on the host (the combining) and partly on the ASP (the address generation). The address generation must know of every unit which address it has been given in compute\_lines. This can be done by storing the addresses given to the units of the first column of each AOI. With these addresses the rest of the addresses in the AOI can be calculated. The problem hereby is that the length of the AOIs are different. To store each first column, dynamic memory allocation is necessary. The standard routine herefor is available but a difficult memory administration will be necessary. This administration must register for which AOI memory is allocated and where this is allocated. Using a simple allocation and free routine will result in a memory of which small parts are occupied and small parts are free. The second possibility is to recalculate the addresses given to the units. This means that compute\_lines is done twice. The third possibility's implementation is given in appendix D. Here the address generation of the line buffers and the LUT are combined. Compute\_lines computes the line buffers one by one. At the same time lines of the screen map are calculated. When an address is given to a unit of an AOI in the line buffer, this address is also placed in the screen map. The calculations here use the minimum unit size (4). When all AOI are for example a multiple of 8, it is useful to use a unit size of 8.

The memory on the ASP is limited. CAD-data, image lines and screen lines are stored in the CAD RAM. This means that only a limited number of AOIs and lines can be stored. This limitation restricts the combining algorithm. If an address of a unit has to be placed on a screen line which isn't used so far and all the memory for the screen lines is used,

the oldest screen line is placed in the LUT. After that addresses can't be placed on that line any more. This restriction is no problem for the first implementation of the combine algorithm.

```

for y = 0 to PCB length

for x = 0 to PCB width

for every AOI so that AOI.y <= y < AOI.y+AOI.length

if (x,y) in AOI

place address in image line (also handle the switch bit)

if screen lines all occupied

copy line to LUT

place the address in the screen line

Sequence of the address generation

```

The sequence of the address calculation is given in figure 6.4. The inner loop "for every AOI ...." is necessary because AOIs can overlap or be double. This loop is not necessary if only the line buffers are calculated because a unit which is member of two or more AOIs, gets only one address. This loop is only necessary for placing more than one address in the screen map. This loop is restricted to the AOIs which have units on the current image line (the y variable of the loop).

# 6.3 Programming in C

Figure 6.4

The biggest part of the program for the ASP can be written in C. Programming in C is of course easier then in assembly. When a program takes too much time, improvements can be made before the program has to be written in assembly (and hope that it is fast enough in assembly). In this paragraph the implementation of the fill\_ua\_buffer\_1 of figure 4.7 is given as an example for improvements. This routine copies a line of image\_unit\_addresses into the line buffer. The listing of this function is given in figure 6.5. The assembly listing is given in appendix E.1. The 4\*i is necessary so that the addresses written on, are word aligned (the processor has a 32 bit data bus; see appendix A.4).

Several parts of this routine can be improved, which results in a lot of time saving. This improvements costs a few variables (read: working registers of the processor). In this function this is no problem because there are not many variables. If a function has more variables than working registers, variables are stored on the stack in the memory. Variables stored on the stack cost of course more time too access than variables in working registers.

The first improvement is using a local variable instead of the global variable current\_image\_line. Current\_image\_line is the index to the oldest, in advance, calculated

#define LINE LENGTH 3000 #define BUFFER\_SIZE 4 #define LINE\_BUFFER\_BASE\_ADDRESS 0x090002 extern int current\_image\_line; extern int image\_unit\_addresses[BUFFER\_SIZE][LINE\_LENGTH]; void fill\_ua\_buffer () { int i; short \*linebuffer; linebuffer = LINE\_BUFFER\_BASE\_ADDRESS; for(i = 0;  $i < LINE\_LENGTH$ ; i++) \*(linebuffer + 4\*i)= image unit\_addresses[current\_image line][i]; } Figure 6.5 Listing fill ua buffer

line buffer. This global variable is stored in the memory and it takes two instructions (3 clock cycles<sup>1</sup>) to load the value in a register. When this variable is given as a parameter to the function, the variable doesn't have to be loaded in the function (only once when calling).

The second improvement is not to use the two dimensional array image\_unit\_addresses but only a one dimensional array. Accessing an element in the two dimensional array is done by calculation of the address: "image\_line + 12000\*current\_image\_line+(i<<2)" (<< means shift left) and then perform an action to that address. The array is an integer array so 12000 comes from 3000 elements \* 4 bytes. The variable i is shifted to align on integers. This calculation of the array element address contains a multiplication. The multiplication is carried out by the standard function "mul", which uses many clock cycles. When the function fill\_ua\_buffer receives an address of the first element of the one dimensional array, the multiplication, the load of image\_unit\_addresses and the load of current\_image\_unit\_addresses, are not necessary. Only the offset calculation with i and the load of the element stay.

The third improvement can be done with the expression "4\*i". If the multiplication is carried out by a shift left operation (which is possible because 4 is a power of 2) the result is the same but there is only one clock cycle needed.

The forth improvement is also with the "4\*i" statement. This is already improved to "\*(linebuffer + (i<<2)) = ...", but the calculation of the pointer address still needs 2 instructions (shift left and add). If the line buffer address is incremented by 4 in a separate statement every cycle of the loop and the "4\*i" is removed, the offset calculation costs only one instruction. When these improvements are carried out, it results in a program

<sup>&</sup>lt;sup>1</sup> Some instructions need more clock cycles per instruction (see appendix A.2).

which is given in figure 6.6. The assembly listing is given in appendix E.2.

```

#define LINE_LENGTH

3000

#define BUFFER_SIZE

4

#define LINE_BUFFER_BASE_ADDRESS 0x090002

extern int current_image_line;

extern int image_unit_addresses[BUFFER_SIZE][LINE_LENGTH];

void fill()

{

full_ua_buffer(&(image_unit_addresses[current_image_line][0]));

}

void fill_ua_buffer ( image_l )

int image_l[LINE_LENGTH];

{

int i;

short *linebuffer;

linebuffer = LINE_BUFFER_BASE_ADDRESS;

for( i = 0; i < LINE\_LENGTH; i++ )

{

*(linebuffer) = image_l[i];

linebuffer += 4;

]

}

Figure 6.6

Listing fill_ua_buffer improved

```

The loop of the first implementation costs 20 instructions (24 clock cycles) and the last implementation needs 7 instructions (10 clock cycles). The time needed by the function \_\_mul which is called twice is not taken into account. So using local variable instead of global variables can have great influence on the processing time.

# Project status and conclusions

The hardware of the Area Segmentation Processor was built and tested. The hardware was changed on several places: a complete new design was made for the VME-interface, the communication with the terminal was improved, the signalling of the reconfigure bits of the image handler and the screen handler were improved, a write pulse for the circular buffer was made and the PB-bus interface was extended so that it has the same functions as the other cards.

The ASP was integrated in the in-line PCB inspection system. Herefor a program was designed, which receives and sends 512x512 images.

Parts of the segmentation software were built. This is not finished because there was not enough time. The improvement of the hardware cost more time then was expected. The combining algorithm of the segmentation software can best be run on the host because there is enough time and it has only be done only once. The address generation for the screen maps can best be done on the ASP because this gives the lowest VME-traffic. In the first implementation the address generation for the line buffers and the screen maps is combined into one function.

Use of global variables delays C programs, especially when used in a loop. Replacing them by local variables can decrease the execution time of a function.

# Abbreviations

| AOI          | Area Of Interest                                                                    |

|--------------|-------------------------------------------------------------------------------------|

| ASP          | Area Segmentation Processor                                                         |

|              |                                                                                     |

| CAD          | Computer Aided Design                                                               |

| CFT          | Centre For manufacturing Technology                                                 |

| CISC         | Complex Instruction Set Computer                                                    |

| CPU          | Central Processing Unit                                                             |

| DUART        | DUal Asynchronous Receiver Transmitter                                              |

| EPLD         | Erasable Programmable Logic Device                                                  |

| ERM          | Embedded Real-time Monitor                                                          |

| ESPRIT       | European Strategic Programme for Research and development in Information Technology |

| FMU          | Fiducial Measurement Unit                                                           |

| IMI          | Industrial Measurement and Inspection                                               |

| ISP          | Industrial Signal Processing                                                        |

| ITE          | Information Engineering                                                             |

| LUT          | Look Up Table                                                                       |

| РСВ          | Printed Circuit Board                                                               |

| RISC         | Reduced Instruction Set Computer                                                    |

| SBIP         | Single Board Image Processor                                                        |

| SMD          | Surface Mounted Device technology                                                   |

| SPARC        | Scalable Processor ARChitecture                                                     |

| <b>TD100</b> |                                                                                     |

| TRIOS        | TRiangulation based Inspection Optical System                                       |

| TUE          | University of Technology Eindhoven                                                  |

| VME          | Versa Module Eurocard                                                               |

|              |                                                                                     |

,

# Literature

- [BOO] Boots P.; 3D data processing for PCB inspection; TRIOS TB1; Eindhoven 13 march 1992

- [CMO] CMOS BiCMOS Data Book; Cypress Semiconductor; Sonetech Nederland bv, Gulberg, 5674 TE Nuenen; March 1, 1991

- [ERM] Embedded Real\_Time Monitor System PG4100; Philips Export BV, Eindhoven, the Netherlands; 1990;

- [FAS] Fast TTL Logic Series; Philips Data Handbook, Integrated Circuits 15 (IC15); July 1990

- [Lee] Leeuwen Frank van; Development of the CAD Data Correction & Expansion Unit for Esprit Project #2017; Philips CFT Technology; Eindhoven september 1990

- [LSI] LSI Logic; Digital Signal Processing (DSP) Data book; June 1990

- [MIC] Micro processors, micro controllers and peripherals; Philips Data Handbook, Integrated Circuits 14N (IC14N); september 1985

- [SAC] SPARCVIEW and utilities; Assembly reference manual; C reference manual; Flame Computer Corporation, 5301 Commerce Avenue, suite 4, Moorpark Ca. USA; 1989 1990

- [SME] Smeets F.G.M.; Hardware development of the Area Segmentation Processor for Esprit Project #2017: TRIOS; Philips CFT Technology; Eindhoven june 1992

- [SPA] SPARC RISC User's Guide; Cypress Semiconductor Corporation, ROSS Technology, Inc.; Second Edition, February 1990

- [VMP] VMEbus Prototyping Board PG2750/PG2751 Users manual; Philips Export B.V.; 1987

- [VMS] VME bus specification manual, revision B; Philips Export bv; Eindhoven, the Netherlands; 1983

# Appendix A The processor CY7C611