| MASTER                            |

|-----------------------------------|

| A stack cache for the C-processor |

|                                   |

| Paalman, J.A.H.                   |

| Award date:<br>1990               |

|                                   |

| Link to publication               |

|                                   |

|                                   |

|                                   |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Eindhoven, january - august 1990

Master thesis:

# A stack cache for the C-processor

by J.A.H. Paalman

Supervisor: Prof. ir. M.P.J. Stevens

Coach: ir. W.J. Withagen

Eindhoven University of Technology Department of Electrical Engineering Digital Systems Group

The department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of student projects and graduation reports

### **Abstract**

This master thesis discusses the data cache(s), which are to be used on the C-processor. The C-processor is being developed at the Digital Systems group of the department of Electrical Engineering of the Eindhoven University of Technology. The processor is a high performance processor, so caches have to be used to provide instructions and data on the speed of the processor. The C-processor uses a stack to store the local data of procedures and functions. A stack cache is used to provide fast access times to the stack. In this thesis several options for the data cache are discussed. Besides the normal cache parameters like cache size and (transfer) block size, some special features for a stack cache are provided. A linear cache can be used. This type of cache can use some special replacement policies. Besides the cut back K replacement strategy found in literature, a hybrid replacement policy is suggested, which will behave better on task switches. A direct mapped cache is proposed for extremely high task switching frequencies. The miss penalties of the cache can be reduced by using read and write buffers. These buffers can also be used as an extension of the cache when the buffers are almost empty. A special strategy is proposed to speed up the writes and thus producing a better access time.

All cache parameters can influence the performance of the cache. The only way to estimate the performance of the cache realistically is by simulating it. A start has been made to write a simulator for the stack cache. A data format for the traces is provided. To simulate the cache realistic address traces are required. These traces, however, are currently not available. Traces generated by a trace generator will give some insight in the effects of the cache parameters, but the many parameters of an stack address trace make it difficult to produce a realistic performance prediction.

A stack cache can give high speed access to the stack, but global data will still be serviced at main memory speed. Therefore the a global data cache is proposed. Especially if the stack cache has a high hit ratio. An inventory is given of coherence protocols for the global data cache.

The data caches are far from ready. The proposed architectures for the stack cache will have to be simulated to get performance statistics. With these statistics an optimal architecture can be chosen and a decision can be made if a global data cache has to be developed.

## **Contents**

| Chapter 0 Introduction                           | 1  |

|--------------------------------------------------|----|

| Chapter 1 Caches on the C-processor              | 2  |

| 1.1 Why do caches work                           | 4  |

| 1.2 What parameters are used to reach the goals? | 5  |

| 1.2.1 Cache organisation                         | 5  |

| 1.2.1.1 A direct mapped cache                    | 6  |

| 1.2.1.2 A fully associative cache                | 7  |

| 1.2.1.3 A set associative cache                  | 8  |

| 1.2.1.4 Comparison of the cache types            | 9  |

| 1.2.2 What size should the cache have?           | 10 |

| 1.2.3 What set size to chose?                    | 10 |

| 1.2.4 And what about the block size?             | 11 |

| 1.2.4.1 The address format for the cache         | 13 |

| 1.2.5 Replacement policies!                      | 14 |

| 1.2.6 Coherency and task switching               | 15 |

| 1.3 The stack cache and the C-processor          | 16 |

| Chapter 2 Data coherence                         | 19 |

| 2.1 Snoopy coherence schemes                     | 20 |

| 2.2 Description of the various protocols         | 22 |

| 2.2.1 Write through                              | 22 |

| 2.2.2 Write once                                 | 23 |

| 2.2.3 Synapse                                    | 24 |

| 2.2.4 Berkeley                                   | 24 |

| 2.2.5 Illinois                                   | 25 |

| 2.2.6 Dragon                                     | 26 |

| 2.2.7 Firefly                                    | 26 |

| 2.3 Performance of the various coherence schemes | 27 |

| Chapter 3 The stack cache                        | 29 |

| 3.1 The C-processor stack                            | 29 |

|------------------------------------------------------|----|

| 3.2 Stack cache organisation                         | 30 |

| 3.2.1 A linear cache                                 | 31 |

| 3.2.2 A direct mapped cache                          | 33 |

| 3.3 The effects of cache parameters on a stack cache | 34 |

| 3.3.1 The cache size                                 | 35 |

| 3.3.2 The (transfer) block size                      | 36 |

| 3.3.3 Replacement policies                           | 37 |

| 3.3.3.1 The cut back K algorithm                     | 37 |

| 3.3.3.2 The barometer pointer algorithm              | 38 |

| 3.3.3.3 Two-pointer algorithm                        | 39 |

| 3.3.3.4 Comparison of the algorithms                 | 40 |

| 3.3.4 Task switching and caches                      | 41 |

| 3.3.5 Coherency                                      | 45 |

| Chapter 4 Architecture of the data caches            | 46 |

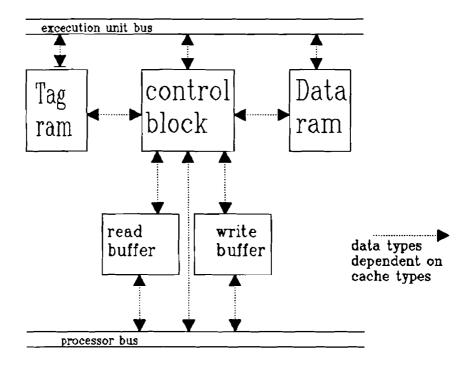

| 4.1 General cache blocks                             | 47 |

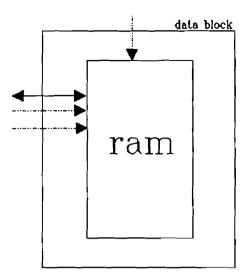

| 4.1.1 The data ram                                   | 47 |

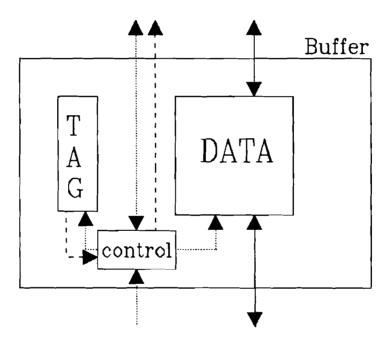

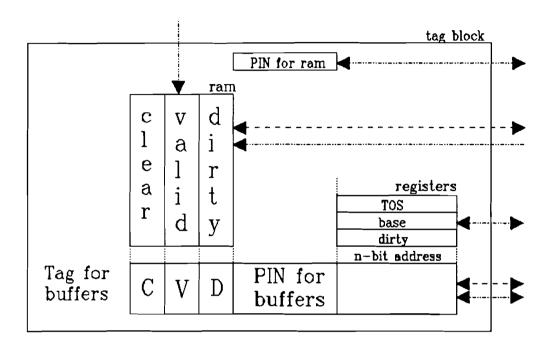

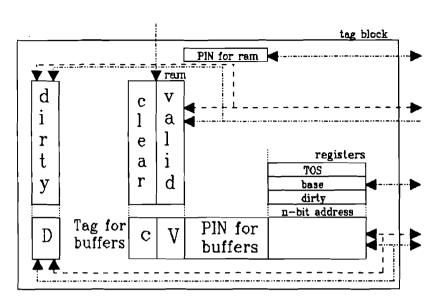

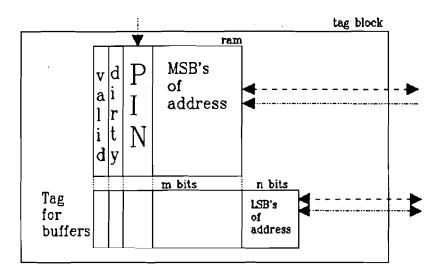

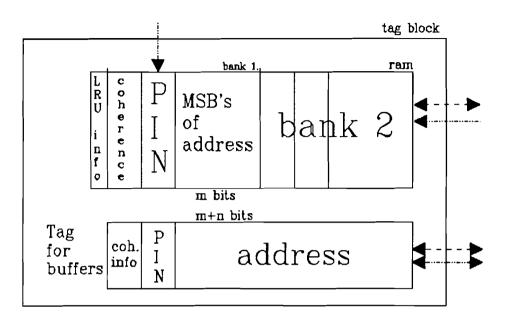

| 4.1.2 The tag block                                  | 48 |

| 4.1.3 The read buffer                                | 49 |

| 4.1.4 The write buffer                               | 50 |

| 4.1.5 Intelligent buffers                            | 52 |

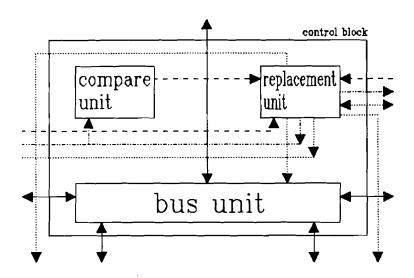

| 4.1.6 The control block                              | 54 |

| 4.2 Communications to the MMU                        | 59 |

| 4.3 The linear stack cache                           | 60 |

| 4.3.1 The control block                              | 61 |

| 4.3.2 The tag block                                  | 68 |

| 4.4 The tag block                                    | 71 |

| 4.4.1 The control block                              | 72 |

| 4.4.2 The tag block                                  | 72 |

| 4.5 The global data cache                            | 73 |

| - 4.5.1 The data ram                                 | 73 |

| 4.5.2 The tag block                                  | 74 |

| 4.5.3 The control block                              | 75 |

| 4.6 Multi port issues and priority         | 76 |

|--------------------------------------------|----|

| 4.7 Thedefinition of local data revisited  | 77 |

| 4.7 The performance of the cache           | 79 |

| Chapter 5 Cache simulations                | 81 |

| 5.1 Why does a cache have to be simulated? | 81 |

| 5.2 What has to be simulated?              | 82 |

| 5.3 Traces for the stack cache             | 83 |

| 5.4 The simulator                          | 86 |

| Chapter 6 Conclusions and recommendations  | 89 |

| 6.1 Conclusions                            | 89 |

| 6.2 Recommendations                        | 90 |

| Literature                                 | 92 |

| Appendix A A trace format                  | 95 |

| Appendix B. The control algorithms         | 98 |

## List of terms used

base pointer: lowest address stored in a linear cache

a block: data ,stored in an aligned, fixed-sized region of (cache) memory.

coherence: the problem of keeping shared data consistent

hit ratio: defined as the ratio of the number times the processor finds a memory

reference in cache to the total number of memory references.

linear cache: a cache containing all memory locations from a certain point to the TOS

local data: definition 1:the continuous part of the stack that fits in the stack cache is

considered local, the rest global.

definition 2: all data on the stack is considered local, all other data global.

definition 3: all data on the stack from the TOS to a certain point is local,

all other data global.

PIN: The process identification number of the process

prefetching: fetching data before the data is wanted by the processor

pseudo-writes: write strategy in which tha address is issued before the data is ready

(section 4.2)

Quad: 4 bytes, standart data type on the C-processor

replacement strategy: strategy guiding all data transfers in a cache

set size: The number of banks or the number of addresses in a cache on which a

memory location can reside.

stack frame: piece of the stack used to store the local variables of a procedure

traffic ratio: defined as the ratio of the number of bytes transferred between cache and

main memory and the number of bytes transferred between processor and

the cache.

Transfer block: The unit of data transfers.

## Chapter 0 Introduction

In the micro processor world many new and fast processors are marketed. As both the addressing space and the speed of the processors grows, it becomes impossible to manufacture large memories which match the speed of the processor and still are cost effective. Therefore cache memories are used. These are small memories which can keep up with the speed of the processor. Replacement strategies try to allocate these memories dynamically to the data or instructions the processor needs at each moment. If this is done successfully, these cache memories give the impression of being large, fast memories. As the VLSI technology moves on, more and more parts of a computer are integrated on a chip. Cache memory is one of the first candidates, since it can also reduce the number of pins of a chip. At the Digital Systems Group of the Department of Electrical Engineering of the Eindhoven University of Technology a high speed processor, called the C-processor, is being developed. This processor too will be equipped with on chip cache memory. The processor will use a split cache architecture. An instruction cache has been developed by Jos Bormans, Yun Chao Hu and Joep Pernot. In this report the cache structure for the data will be discussed.

The C-processor will store the local data on a stack instead of in registers. A specialised stack cache will speed up references to this stack and can be compared to the register sets used in RISC processors. A second data cache for the global data can be necessary if the stack cache is very efficient. In the next chapter the basics of caches are discussed. Chapter 2 gives an inventory of techniques to maintain coherency in the global data cache. In chapter 3 the parameters of the stack cache for the C-processor are discussed and this is followed by a description of a few possible architectures of the stack cache. Also some new features are introduced. To manufacture a optimal cache for the workload, simulations are required. The fifth chapter gives the basics to design a simulator for the stack cache. In the last chapter some conclusions are given and some recommendations for further research are made.

## Chapter 1 Caches on the C-processor

The C-processor is designed to execute high level programming languages, such as the C programming language, at high speed. This is partially done by tailoring the instruction set to the high level languages. Secondly, the architecture has to support some constructions of the high level languages. The C-language is characterised by the use of procedures and functions. To provide easy function calling and to ease the passing of parameters, two approaches for storing local variables and passing parameters are mostly used. One can use multiple register sets and pass parameters by overlapping the register sets. The alternative approach is to use a stack to pass the parameters. In this last approach a stack cache is commonly used, so stack references can be serviced most of the time by fast cache memory or cache registers, rather than by slow main memory.

Characteristics of the register sets approach are the fixed set size and a fixed number of sets. A fixed number of locals can be in registers at the same time, a fixed overlap; a fixed number of parameters can be passed through registers and the registers can be addressed by a few bits. The allocation of local variables to registers can be a mayor task for the compiler.

The use of a stack cache permits a variable number of locals per procedure and the number of parameters also is not fixed. The size of the sets become variable, and the number of sets in the cache too. A compiler can use exactly the number of memory locations (registers) needed for a frame. Thus a frame always fits in a register set, there are no free registers in a set, nor are there to few. The register set size can vary from 0 to the cache size. The stack cache has to be addressed like a memory. This implies that long addresses have to be used. The local variables simply can be put on stack by the compiler. The only allocation problem arises when the stack cache is too small to hold all the locals of a procedure. But even then a register frame larger than the cache size can be chosen, which, depending on the cache replacement strategy, only results in an increase of cache misses.

The stack cache has no fixed frame size, thus register allocation needs no attention. As it is addressed as a memory, all memory addressing modes can be used and, depending on the cache architecture, the penalty for task switching can be lower. The stack cache also is transparent to the software. However, registers can be addressed by a smaller number of bits, are faster and are less expensive. The C-processor will be a stack based machine and will use a stack cache to hold local variables and to pass parameters to procedures and functions.

Besides a stack cache to hold the local variables the C-processor will be equipped with an instruction cache and (probably) a data cache for global data (global data cache) to speed up the processor. There are separate instruction and data caches, because separate instruction and data busses are used (Harvard architecture). To use both busses effectively, the traffic on the busses should be almost equal. In this case the traffic of the instruction cache should be equal to the traffic of both the stack cache and the global data cache. If the traffic on one of the busses is higher, the processor will wait for that bus. One of the caches can be reduced, without reducing the processor throughput, so there is a waste of silicon. The matching of the traffic can be managed by manipulating the miss ratios and the traffic ratios of the caches. The traffic on the data bus depends on both the stack data traffic and the global data traffic. Although the stack cache, and the global data cache can be designed separately, they need to be examined together in the final design phase.

There are two parameters related to cache performance:

- 1) hit ratio (R<sub>hit</sub>), defined as the ratio of the number times the processor finds a memory reference in cache to the total number of memory references.

- 2) traffic ratio (R<sub>trat</sub>), defined as the ratio of the number of bytes transferred between cache and main memory and the number of bytes transferred between processor and the cache.

A global data cache is useful when the hit ratio of the stack cache approaches the percentage of global data references in the data stream.

Example:

Hit ratio stack cache 90%. 10% global references. Of every 100 references, the stack cache now produces 9 references to main memory, while all 10 global references refer to main memory. A higher stack cache hit ratio would not have a large effect on the processor speed.

The goals of the caches are (in order of importance):

- high hit ratio, most of the processor memory requests should be serviced by the caches.

- low cache access time (T<sub>acc</sub>), data should be provided to the processor in a minimal time, because cache access is in the critical path.

- low miss penalty (T<sub>miss</sub>), in case of a miss, the extra access time should be small.

- low traffic ratio; minimize the traffic between memory and cache, but the traffic on both busses should be balanced.

- small area, don't use to much silicon.

The order of importance is only relative. If, for example, the hit ratio is above a certain offset, a further increase in the hit ratio can require so much silicon, that the design is no longer feasible.

Before going into detail about the actual design, the next section will describe some fundamentals of caches.

#### 1.1 Why do caches work?

A cache is a small but fast memory, which contains a part of the contents of main memory. Caches can speed up a processor considerably because of the principle of locality. In a program, instructions near the present instruction are likely to be executed and data near the data being referenced are likely to be referenced (e.g. array structures,

stack). This is called the spatial locality of a program. Besides spatial locality, there is temporal locality. Instructions in a loop will soon be used again, often several operations are done on the same data, etc. If the cache memory contains instructions and/or data near those presently in use and holds instructions/data that were used in the near past, the cache memory is likely to contain the next instruction(s)/data. Thus the processor can operate on the speed of the cache memory.

#### 1.2 What parameters can be used to reach the goals?

There are several architectural choices that gravely affect the performance of the (relatively) small cache memory. Some of these issues are the organisation of the cache, the size of the cache, the use and the size of (transfer) blocks, the replacement policy and, for data caches, the coherence scheme.

#### 1.2.1 Cache organisation

Since the cache memory is a small memory, it can only contain a small part of the instructions or the data of a program. There are three ways to organise a cache:

- a direct mapped cache

- a fully associative cache

- a set associative cache

For each of these organisations the memory of each entry is divided in two parts. A data part which contains the actual data and a tag part, which contains the virtual or real address of the data and some information regarding the validity of the data. The address part of the tag is used to check if a memory location is cached. If data is not in the cache, or if the data is not valid, a cache miss occurs.

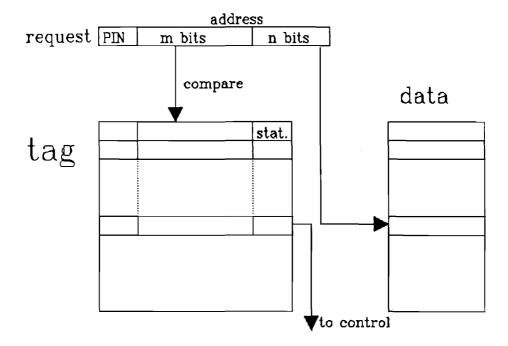

#### 1.2.1.1 A direct mapped cache

In a direct mapped cache (fig. 1.1), normal memory can be used for a cache. The address of each block can be mapped to only one place in the cache. Caches are usually divided in blocks to save tag memory. The tag is only kept for a block (see section 1.2.3). A part of the address (n bits) of the request is used to specify the entry in the cache. This means that on a cache miss, only one cache entry can be replaced; no replacement

Figure 1.1 A direct mapped cache

strategy can be used. The absence of a replacement policy can have a negative effect on the cache performance. If two often used memory locations map to the same cache location, they will replace each other. This will decrease the hit ratio and increase the traffic ratio. The absence of a replacement policy also has a positive effect. No time is spent on determining which entry has to be replaced.

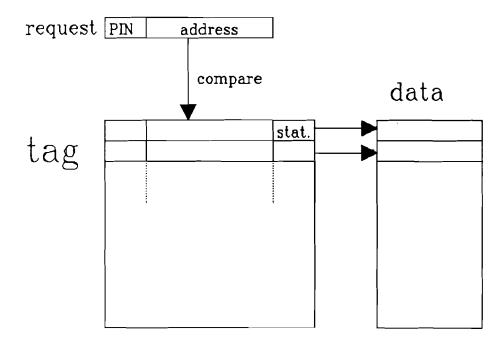

#### 1.2.1.2 A fully associative cache

In a fully associative cache (fig. 1.2) each memory location can be mapped to each cache location. An associative memory has to be used. The entry that has to be replaced on a miss can be chosen by a replacement strategy. An entry with a low probability of being

Figure 1.2 A fully associative cache

used soon, can be replaced, so the hit ratio can be high and the traffic ratio low. However, it takes some time to find this entry. Furthermore associative memory will be larger than normal RAM memory.

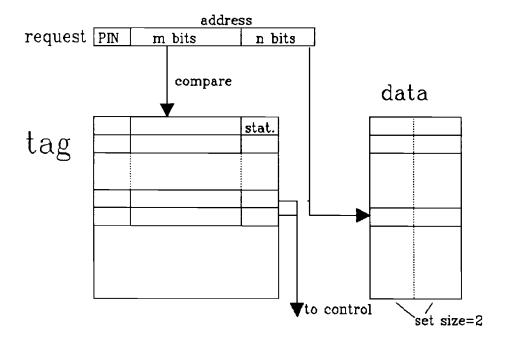

#### 1.2.1.3 A set associative cache

A compromise between a direct mapped and a fully associative cache is the set associative cache (Fig. 1.3). In a set associative cache a memory entry can reside in a few direct mapped cache banks. A memory location can be mapped to only one location in each bank; to a set of a few addresses. The number of banks or the number of addresses in a cache on which a memory location can reside, is called the set size. The

Figure 1.3 A set associative cache

number of sets is equal to the size of each cache bank. The associative search now only has to be performed in one set. The fully associative cache and the direct mapped cache are special cases of the set associative cache. In a fully associative cache the set size is equal to the cache size, and there is only one set; a direct mapped cache has a set size of one, and the number of sets is equal to the cache size. In general, the cache size is equal to the set size times the number of sets. As the set associative cache has associativity, a replacement algorithm can be used. The set size is mostly small, so the access time will be only little longer than the access time of a direct mapped cache.

#### 1.2.1.4 Comparison of the cache types

The advantages of high associativity are important for small caches. As the caches become larger, the hit ratio will increase. The average access time for data (T) is  $T = R_{hit}$  \*  $T_{acc}$  + (1 -  $R_{hit}$ ) \*  $T_{miss}$ . As the  $R_{hit}$  approaches unity, the access time will be more important than the miss penalty. A large direct mapped cache can outperform an equally large (set) associative cache. The choice of associativity not only is a simple comparison of hit ratios and complexities, but also depends on timing aspects for larger cache sizes.

For a stack cache a fourth type of cache can be used, the linear cache. This type of cache contains a contiguous part of the memory. Because this cache only contains one continuous part, it is not useful for an instruction cache, since each jump or function call can cause a replacement of a large amount of instructions in the cache. Because the stack is a continuous area, the cache can contain a continuous part of the stack, containing the top of the stack too. It then suffices to remember the address of only one entry, and calculate the addresses of the other entries, using an offset. The tag memory then consists of validity data only and will be very small. This type of cache is further discussed in section 3.2.1 about stack caches.

#### 1.2.2 What size should the cache have?

The size of the cache has a mayor effect on the hit ratio and the traffic ratio. It also influences the access time. As the cache becomes larger, it can contain more information, thus the chances of a hit increase. This causes an decrease of the traffic ratio, as more hits require fewer bus accesses. Because of the locality of programs, the increase of the hit ratio decreases with the increasing cache size. The extra items in the cache will be older or further away in memory, and are less likely to be referenced.

The main disadvantage of a large cache is the increase in access time, since larger memories have longer access times. Secondly large caches require a large chip surface so there also will be a physical limit to the cache size. The traffic on the data bus must be about the same as the traffic on the instruction bus, so simulations can give information about the cache size needed. The guidelines given by Smith [Smi85(B31)] can be used for a first approximation.

#### 1.2.3 What set size to chose?

The misses in a set associative cache caused by the mapping of various memory locations to the same cache location(s) are called collision misses. If the set size increases from one (direct mapped cache) to two, most of the collision misses are avoided. A further increase of associativity (the set size), further reduces the collision misses. But this decrease becomes less and less. Various studies [Smi82(B24)], [Aga89(P31)], [Hil89(P56)] have shown that a set associative cache with a set size of 8 has almost the same hit ratio as a fully associative cache.

#### 1.2.4 And what about the block size?

In a cache some memory locations can use the same tag. Such a block consists of data stored in an aligned, fixed-sized region of (cache) memory. One reason for using blocks is that it saves tag memory. The tag for a block requires only one address part (see fig. 1.4). Furthermore, using blocks, the cache can make use of the spatial locality: by fetching a block at a time, some memory locations near the desired memory location are fetched too. These locations have a high probability of being used in the future. However not all locations will be used. A large block increases the number of bytes fetched at a

Figure 1.4 Cache memory organisation

read. The data near the requested data have a high probability of being referenced in the near future. For data further away in the block, this probability is smaller, so the ratio of useful data in a block decreases with increasing block size. This effect is due to the spatial locality. Each block fetched, will replace another block. The probability that this block contained useful data increases as the number of blocks that fit in the cache decreases (the cache size remains constant), since it only uses spatial locality. If only one block fits in the cache, at least one data item was referenced in the past. If two blocks of half the size are used, two items were referenced in the past. As the principle of temporal locality dictates, both items are likely to be referenced again. Thus, using temporal locality , one would prefer small blocks, since each block will contain data referenced in the past, and spatial locality prefers large blocks, so all data near the referenced data will be present.

A cache with a small block size, a lot of the data present was used in the past, but probably a large portion of that data was used long ago and has small chances of being used again. The data near the data in use has a small probability of being present if it was not used before. As the block size increases, some of the data used long ago will be replaced by data near the data used at the moment. The hit rate will increase, since the cache will contain data near the presently used data instead of data used long ago. If the block size further increases, the average age of the data will decrease. The cache will now contain data further away from the data in use, but data used recently will not be present. Thus after reaching an equilibrium, the hit ratio will decrease again.

The size of the blocks also has effects on the miss penalty and the transfer ratio. On a cache miss in a full cache a whole block has to be replaced. The cache can use the new data only when the replaced block is written back to the main memory and a whole block is fetched. Thus, an increasing block size results in a larger transfer of data and the miss penalty increases. Secondly if the block size increases, a block is more likely to be dirty (since it contains more data), and needs to be written back, even if the rest of the block does not have to be written back. These two negative effects of large blocks can be minimised by introducing transfer blocks.

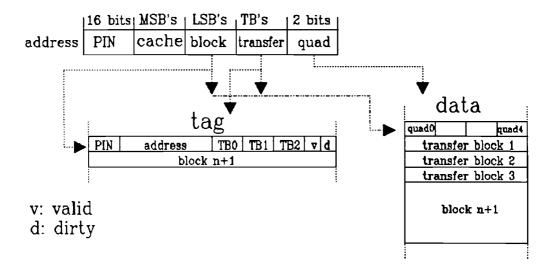

Transfer blocks are the units of data transfers. The tag of a block containing transfer blocks, consists of the address for the whole block and valid and dirty bits for the transfer blocks only (see fig. 1.4). The miss penalty is decreased because only dirty transfer blocks have to be written back, and the transfer block containing the required data can be fetched before the other transfer blocks in the block, and thus be used by the processor before the rest of the block is present.

The optimal block and transfer block size are dependent on the cache size and organisation. Smith [Smi87(P17)] gives guide lines for block sizes (called line sizes by Smith) to get a desired hit rate / traffic ratio. But simulations will, once again, be necessary.

#### 1.2.4.1 The address format for the cache

The use of blocks and transfer blocks has some effects on the addresses used to access the cache. Parts of the address are used to identify quads in transfer blocks and transfer blocks in blocks. In a direct mapped cache, each block can only reside on one place, so a part of the address can be used to identify the block in the cache. The addresses used for the cache have five fields (fig. 1.5):

- PIN: This is the process identification number of the current process

- cache: These bits are used to see if a block is in the cache

- block: These bits determine the place of a block in a linear or direct mapped cache

- Transfer: Select a transfer block within a block

- Quad: Select a quad within a transfer block.

These parts are only used if they are needed; i.e. if the size of the block equals the size of a transfer block, the transfer field will not exist.

|         |     | MSB's |       |          |      |

|---------|-----|-------|-------|----------|------|

| address | PIN | cache | block | transfer | quad |

Figure 1.5 A cache address

#### 1.2.5 Replacement policies!

Replacement policies in caches include all operations on cache memory. This includes the replacement of blocks by other blocks, writing back or fetching blocks in advance, and operations when the active process changes.

When the cache is full and there is a miss, a block in the cache has to be replaced by the block wanted by the processor. The problem at hand is which block to replace. Obviously, the best block in the cache to replace, is the block that will be used last of the blocks in the cache or even never again. Unfortunately, the cache has no knowledge of the future, so an educated guess has to be made. This is done by replacement policies. A first policy is to replace a random block. Since there is no knowledge about the future, each block has the same chance of being replaced, so we can replace a random block. This policy has a minimal overhead, since almost no time is lost to decide what block to replace. Thus the miss penalty is minimal. However, the past can be used to predict the future. The principle of locality can be used. This is done by the FIFO and the LRU replacement policies. In FIFO the block that was fetched the longest time ago is replaced, in LRU the block that was least recently used is replaced. As far as the hit ratio is concerned, LRU performs best, followed closely by random and FIFO is by far the worst. The bad performance of FIFO is not surprising since the block fetched the longest time ago is replaced, even if it is a frequently used block, or was the block last referenced. The closely matched performance of LRU and random can be a surprise. In the following example random even outperforms LRU. (there are of course counter examples, this example just indicates the possibility of a random replacement scheme out[performing the LRU replacement scheme.)

Example:

Cache size 3 blocks, in a loop blocks A, B and C are referenced sequentially. In LRU each block fetched always replaces the block to be referenced; A and B in cache, miss on C, C replaces A; B and C in cache, miss on A; A replaces B; etc. If random is used, the chance that the block to be referenced is replaced is 50%, so the random replacement strategy will give half the number of misses of LRU.

The overhead of LRU however, can be high. The set size (n) is equal to the number of blocks that can be replaced, so n blocks have to be checked and updated at each reference. In the tag field of each block log₂n bits are needed to contain the LRU information. Especially for a fully associative cache the cost can be high. For two or four way associative however, LRU is commonly used. The LRU replacement policy is used in the instruction cache. This policy is also an obvious choice for the data cache.

#### 1.2.6 Coherency and task switching

The C-processor will be used in a multi-processor environment where it has to cooperate with other processors (i.e. a DMA processor). In a multi-processor environment, several copies of the same data can exist (in cache, main memory). This can even happen to data on the stack (which is private to a process) if processes can migrate between processors. Global data can be shared between processes too. The C-processor has a very strict data protection mechanism, which uses process identification numbers (PIN). The only way to share data is to use the real address of the data. If a virtual cache is used, there even can be two copies of the same data in the cache. This last problem can be solved by using a special mapping or by also putting the real address in the tag. The assurance that all of the copies are identical is called data coherence or data consistency. Coherence problems occur when the data in the cache and the data in main memory need not be the same. For example when DMA writes something to main memory, or when the C-processor writes something to cache.

A few of the algorithms used to solve the coherence problem are:

- write through

- write once

- Dragon

- Firefly

- Berkeley

- Illinois

- selective invalidation

These algorithms, and some more, will be evaluated in chapter 2. The coherence problem will only occur in the stack cache if processes can migrate between processors. This problem can occur in the global data cache and has to be solved.

When several processes are running on the same processor, task switching will occur frequently. At a task switch, (almost) all data in the cache will no longer be useful. In some cases, in a linear stack cache where only the base address is available, this means that the cache has to be flushed. The effects of task switching are especially important for the stack cache.

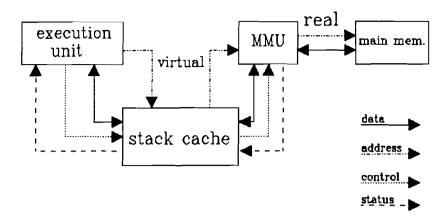

#### 1.3 The stack cache and the C-processor

In the C-processor, two caches are placed in the two data paths between main memory and the processor. In the instruction data path an instruction cache is placed [Bor89]. The stack cache is placed in the data path, between the execution unit and the Memory Management Unit; the connection with main memory (fig. 1.5). The execution unit can issue several stack data requests at the same time. The execution unit is multi ported. The execution unit can also issue some control signals to move the TOS, or to switch off the cache. The cache responds with status signals, to indicate when the data transfer is completed. When some data does not reside in the cache, it must be fetched from main memory. The execution unit and the stack cache use virtual addresses. Main memory is

Figure 1.6 The stack cache in the C-processor

addressed with real addresses. The MMU translates the virtual addresses to real addresses. Between the cache and the MMU the same status and control signals can be used as between the execution unit and the cache. A more complete model of the C-processor is given in [Wit88] and [Bud88].

The stack cache will always handle local data, placed on the stack. The stack cache will contain at least a continuous part of the stack, containing the top of stack. If a global data cache is used too, the division between local data and global data has to be clear. The definition of local data can be difficult; local data in a procedure can be global data for a function called by the procedure. For the distinction between global and local data three options are given below, each having implications for the design of the data cache.

The first definition of local data is the most narrow: the continuous part of the stack that fits in the stack cache is considered local, the rest global. Thus, for a 1 kB cache, data from 1024 bytes below the TOS to the TOS are considered local, all other data are considered global.

Definition 2: all data on the stack is considered local, all other data global.

Definition 3: all data on the stack from the TOS to a certain point is local, all other data global. One could also opt to make the offset the current stack frame, but the size of the frames can vary. Most of the frames are small, but some can be quite large. Thus most times many frames would fit in the cache, sometimes one frame can be to large. Such a dynamic distinction between local and global data is most difficult to implement, and will not be chosen.

A request to the stack cache is considered a stack cache miss, when the request does not fall within the definition of local data. The stack cache miss must not be confused with a miss: data that is not in the cache, but inside the definition of local data. In the next chapters definition 2 will be used. Since it is not yet decided that a global data cache will be present, a stack cache based on this definition will cache more global data and can give better results. The implications on the design will be discussed further in section 4.7.

The performance of the data caches of the C-processor has to match the performance of the instruction cache, specially where the bus traffic is concerned. The design of the instruction cache is almost complete [Bor89], [Hu89]. This will be a two-way associative 1024 quad (=4 bytes) cache with a block size of 32 quads and a transfer block size of 8 quads. The predicted hit rate is 86% [Bor89].

## Chapter 2 Data coherence

When data is distributed over several resources, contradictory information can be present at several places. Problems will occur when two processors operate on different copies of the same data. These coherency problems mainly affect the global data cache. Certain realisations of the stack cache can be affected by coherency problems too. In chapter 3 about stack caches, we will take a closer look at this problem. In the rest of this chapter coherence problems will be discussed in general. There are several ways to solve coherence problems.

The most simple techniques are to disallow private caches for the processors or to declare shared writable data not cachable. These techniques reduce performance, because the processor is either completely dependent on main memory (no caches) or dependent on main memory for all shared writable data. Besides this, the second approach is transparent to neither the user nor the compiler.

A third technique is to flush the cache each time the processor exits a critical section. This scheme can introduce a high overhead (lots of critical sections, large caches) and is difficult to implement on write-back caches.

A fourth scheme employs a centralised global table to store the status of the memory blocks. Cache enforcement signals can be generated on the basis of the block status. When a processor wants to use a block, it has to access the table. To limit the accesses to the global table, local status flags can be provided in the cache directories for the blocks that reside in the cache. Depending on the local flags and the type of the request, the processor may use the cached data, or has to consult the global directory.

In this scheme the global directory can be the bottleneck. Because of the distance between the processors and the directory, the latency of the table will limit the performance and increase the miss penalty.

The directory can also be distributed among the various processors. This approach takes advantage of the broadcast capability of the bus. In the schemes now to be discussed, the consistency is maintained by a bus watching mechanism, also called a snoopy cache controller. The schemes are known as copy back or snoopy cache coherence protocols [Arc86(P59)]. The bus is the limiting factor for the number of processors to be used. Furthermore, the complexity of the bus interface unit will increase, because it has to watch the bus.

For the C-processor with its on chip caches, the snoopy algorithms are more desirable for the following reasons:

- The caches are on chip. The time to consult the on chip tags will be much shorter then the time to consult a central directory in main memory.

- The number of processors will probably be small. There will be no problems with the limited bandwidth of the bus.

- The on chip caches will be small, so the miss ratio will be rather high. Any increase in the miss penalty will seriously affect the performance.

The higher performance of snoopy schemes is confirmed by simulations in [Aga88(B41)] for small multi-processor systems. In the following section the various snoopy coherence schemes will be discussed.

#### 2.1 Snoopy coherence schemes

To ensure the consistency of the data in caches, a cache has to store some information with respect to the other copies of each entry. First one has to know if the data is correct and still up to date. This is called the validity of the data. Secondly the data can be shared with another cache, so information about the exclusiveness has to be in cache. Third a cache can be the owner of an item. Then even main memory can have an invalid copy and the cache has to respond instead of main memory if someone tries to access that data.

A model in which the various states of the data is described uniformly is needed to compare the snoopy coherence protocols. In the so called MOESI (the first letters of the states described below) state model [Swe88(P12)] the attributes validity, exclusiveness and ownership are combined to form five states for the data in a cache. These five states are:

- M modified, the data in the modified state is not shared by any other cache, it has changed since it was read from main memory and main memory has not been updated. The processor may read and write this data.

- O owned, data in the owned state may be shared by other caches and main memory is not updated. The processor may only read owned data.

- exclusive, data in the exclusive state is not shared by other caches, and main memory is up to date. The processor may read the data.

- S shared, data in the shared state can be shared by other caches, and it is owned by either main memory or another cache. The processor can only read this data.

- I invalid, the data in the cache is not consistent with data elsewhere, and may not be read by the processor.

A block that is not in the cache is a sixth state : not present. This state is not included in the MOESI model.

With some of these states (not all are necessary) a cache coherence protocol can be formed. In table 2.1 the various coherence protocols are described in terms of their MOESI states. As can be seen in the table, there are almost no protocols that use the same states. Furthermore they use different states or state changes to write back data to main memory. The protocols are described in detail in the next section.

Table 2.1 MOESI states for various coherence protocols

|               | M                     | 0                         | E                       | S                    | 1       |

|---------------|-----------------------|---------------------------|-------------------------|----------------------|---------|

| write through |                       |                           |                         | valid                | invalid |

| write once    | dirty                 |                           | reserved                | valid                | invalid |

| Synapse       | dirty                 |                           |                         | valid                | invalid |

| Berkeley      | owned<br>exclusively  | owned non-<br>exclusively |                         | unowned              | invalid |

| Illinois      | exclusive<br>modified |                           | exclusive<br>unmodified | shared<br>unmodified | invalid |

| Firefly       | not shared<br>dirty   | shared<br>dirty           | not shared<br>not dirty | shared<br>not dirty  |         |

| Dragon        | dirty                 | shared<br>dirty           | valid<br>exclusive      | shared<br>clean      |         |

#### 2.2 Description of the various protocols

In this section a description of some snoopy protocols will be given. The first protocol, write through, is a very simple protocol which can be implemented at low cost but has very low performance. It is mainly included for comparison of the various schemes.

#### 2.2.1 Write through, states: valid(S) and invalid(I) [Yan89(P32)]

A write can give rise to a hit when the block is in cache and valid, or a miss otherwise. On a miss, the block is loaded from main memory in the VALID state. On a hit, the block is supplied by the cache and the block remains VALID. When a write occurs, the block is written through to main memory. All other caches watch the bus, and invalidate all data in the cache to which a bus write occurs.

2.2.2 Write once, states : dirty(M), reserved(E), valid(S), invalid(I) [Yan89(P32)]

On a read request of the processor the cache responds with a hit or a miss. If the requested word is not in the cache or is invalid the result is a miss. Otherwise the data is supplied without changing the state of the block. On a miss, the data is supplied by another cache if a dirty copy exists, otherwise main memory will send the data. A block is loaded with state VALID. If the block is loaded from main memory, and a cache has a RESERVED copy of the block, this cache will set its state to VALID. If the block is supplied by a cache, this cache will write the block back to main memory and set its state to VALID.

A write of the processor also gives rise to changes of states. If the block is VALID in the cache, its state is changed to RESERVED, all other caches are invalidated and the block is written through to main memory. If the block is RESERVED, the state is changed to DIRTY, and the data are written to the cache. If the block already is DIRTY, all that has to happen is to write the block to cache. The state remains the same. If the block is not in the cache, the block is loaded like on a read miss, all other caches are invalidated, and the block is updated in the cache. The state is set DIRTY.

#### 2.2.3 Synapse, states: dirty(M), valid(S), invalid(I) [Fra84(P37)]

Like some other protocols, this protocol uses ownership to resolve the coherency problems. The main memory itself has an OWNED tag for each block.

A read hit causes no bus activity. On a read miss a public read signal is put on the bus. If main memory is the owner, the block is loaded in the valid state. If another cache is the owner (has a DIRTY copy), it writes back the word to main memory and invalidates its copy. After this transaction main memory is the owner, and the public read is handled as before.

A write hit on a DIRTY block can proceed locally. On a write hit on a VALID block or on a miss, a private read request is issued, and the same actions are taken as on a public read. After the block is updated in the cache, the state is set to DIRTY, so the requesting cache becomes the owner of the block. All caches with a VALID copy monitor the bus and invalidate their copy if they monitor a private read.

## 2.2.4 Berkeley, states: owned exclusively(M), owned non-exclusively(O), unowned(S), invalid(I) [Kat85(P38)]

When a processor read results in a hit, the appropriate word is provided to the processor. On a miss, a block has to be flushed. If this block is OWNED, the block is written to main memory, and to other caches if the state is OWNED NON-EXCLUSIVELY. A write without invalidation is used. Then it reads the block with status UNOWNED. It uses a special read signal; a read-shared. If the block is OWNED by another cache, this cache will provide the data, instead of main memory, and set the state in the cache to OWNED NON-EXCLUSIVELY. If the block is NOT OWNED, it is supplied by main memory. A block is always read in the state UNOWNED.

On a write, the following procedure is used. If there is a hit on an OWNED EXCLUSIVE block, then the processor writes only to the cache. If the hit is in an OWNED NON-EXCLUSIVE or an UNOWNED block, then all other caches must be invalidated, using a write for invalidation. On a miss, some data will be flushed using the protocol of a read miss, and the block is read using a read for ownership signal. On this signal the owner sends the block and all caches (except the new owner) invalidate their copy of block. Then the cache updates the block. After the block is written to the cache the state is set to OWNED EXCLUSIVELY.

2.2.5 Illinois, states: exclusive modified(M), exclusive unmodified(E), shared unmodified(S), invalid(I) [Pap84(P39)]

In this protocol too a read hit is only handled by the cache with no status change. On a read miss, the highest priority cache will give the data (daisy chain). If no cache has the data, then memory will provide the block. All caches that match the data will set the status to SHARED UNMODIFIED. If the status in one of the caches was EXCLUSIVE MODIFIED, the block is written back to main memory. The requesting cache sets the status to SHARED-UNMODIFIED if the block came from another cache, and to EXCL-UNMODIFIED if the block came from main memory. On a write miss the same read cycle is done to cache the block. But an invalidate signal accompanies the read request, on which all caches invalidate their copies of the block. The requesting cache sets the status of the block to EXCLUSIVE-MODIFIED. On a write hit, the cache is updated and the status is set to EXCLUSIVE-MODIFIED. Only if the status of the block was SHARED UNMODIFIED an invalidation signal is sent.

2.2.6 Dragon, states: dirty(M), shared dirty(O), valid exclusive(E), shared clean(S) [McC85(P52)]

This protocol looks like write once, but it uses a shared line to see if a block resides in more caches. A cache that monitors a read or write request for a block it contains, raises the shared line. The shared states can be used to minimise the number of writes.

On a read miss, the data are read. If another cache has a dirty copy, it supplies the data, otherwise the block comes from main memory. All caches that contain a copy of the block, mark their copy as SHARED. Otherwise the cache marks the data as VALID EXCLUSIVE. If the shared line is raised, the block is loaded as SHARED CLEAN, otherwise as VALID EXCLUSIVE.

A write to a DIRTY or VALID EXCLUSIVE block can proceed locally. The state of the block is set to DIRTY. On a write to a shared copy, the data are written to all caches. If a cache has a copy it reads the block as SHARED CLEAN and raises the shared line. By observing the bus, the cache performing the write can determine if the block is still shared. If the shared line is raised, the block is marked SHARED DIRTY, else the state is set DIRTY. Main memory is NOT updated.

On a write miss, the block is read as on a read miss. The block is loaded from the bus as DIRTY or SHARED DIRTY depending on the shared line. If the block is SHARED, the update is written through to the other caches.

2.2.7 Firefly, states: not shared dirty(M), shared dirty(O), not shared not dirty(E), shared not dirty(S), invalid(I) [Tha88(P58)]

This protocol, which is similar to the Dragon scheme, depends on a shared-line. A snoopy controller sets the shared line high if it finds an address on the bus that resides in the

cache. The controller that provided the address watches the shared-line to see if the data also resides in another cache.

On a write that hits in non-shared data, no bus traffic is needed, and the data is marked NOT SHARED DIRTY. If the data is shared, the cache writes through the data to maintain coherence and update main memory. If the data is in another cache too (shared line is set by another cache) it marks the data SHARED NOT DIRTY, otherwise NOT SHARED NOT DIRTY. On a write miss, the same actions are taken as on a write to shared data.

A read hit requires no further action. On a read miss, the data is read from the bus. The received data are marked clean and its shared bit is set to the value of the shared-line. If the data are provided by a cache, this cache sets the shared bit.

#### 2.3 Performance of the various coherence schemes.

The various coherence schemes can be compared in various ways. The first, and probably least reliable comparison is given by the authors of articles about new schemes (their scheme is better than...). A second approach is a comparison on the basis of certain models. The main problem with models is the validity of the models. A last method of comparing coherence schemes is using traces. This is most common practice. There are several articles in which the various schemes are compared using traces. The first comparison of the coherence schemes will be done on the basis of the various comparisons in the various articles.

A comparison on the basis of a queueing model can be found in [Yan89(P32)]. Yang uses a performance parameter called system power (processor utilisation \* the number of processors), to compare the coherence schemes. The highest system power is given by the Dragon and the Firefly protocols. The system power of the Illinois, Write-once, Berkeley and Synapse schemes are almost the same, but considerably lower than the first

two schemes. Of these schemes, the Illinois scheme performs best and the Synapse scheme worse. The Write-once and the Berkeley owner scheme perform similar. Write through results in the lowest system power. The other coherence protocols are not evaluated by Yang.

A simulation of the same six protocols is performed by Archibald and Baer in [Arc86(P59)]. It also uses the system power as a performance measure. The highest system power, in their simulations, is obtained by the Dragon scheme, followed respectively by Firefly, Berkeley, Illinois, Write once, Synapse and, far behind, write through. The performance of the Synapse scheme is in all simulations more than two times higher than write through. The relative performance of the schemes depends highly on the degree of sharing, the percentage of reads and the cache and block size.

The various coherence schemes have a different cost. The Dragon and Firefly scheme require a shared line, and a cache in the Illinois scheme has to see whether a block comes from memory or from a cache. In the schemes where a cache can provide blocks, the extra accesses to the cache can slow down the processor of that cache. The synapse scheme requires an extra memory bit for each block. Besides, all protocols, except write through, need a snoopy controller. The costs of the protocols and the system power both have to be taken into consideration before the choice of a coherency protocol can be made. At the moment, some new snoopy coherence schemes are being developed, the so called competitive snooping schemes [Kar88(P57)]. Their authors claim that their schemes outperform the normal snoopy schemes. It may be necessary to modify a protocol to meet the specific demands of the C-processor. These include the size of the cache, the traffic on the bus, the number and kind of additional processors, second level caches, the way of sharing data, etc.

## **Chapter 3 The Stack Cache**

In this chapter the basics of a stack cache will be discussed. First the stack of the C-processor will be discussed. Then several organisations of caches that are designed specially for a stack will be discussed. This is followed by a discussion of the effects of the (block)size, the replacement strategy and coherency on the stack cache types.

#### 3.1 The C-processor stack

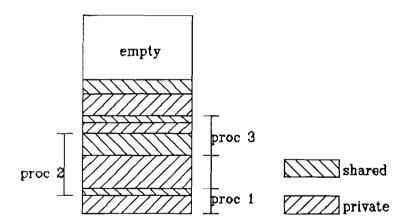

On the stack of the C-processor all parameters used in and passed between procedures and functions are stored (return addresses can be seen as parameters passed between functions). Such a stack is shown in figure 3.1.

Figure 3.1 The C-processor stack

Most procedures will only require a small number of parameters and a small number of local variables, so the typical stack frame (#locals + # parameters) will contain about 10 variables (80% < 11 words [Fur88(A12)], 95% < 13 words [Laz89(A13)], 94% < 13 words

[Sta88(P5)]). Most references to the stack will be to the frame containing the TOS, since that procedure is being processed. The number of frames on the stack will probably vary slowly, and will be about 8 (a window containing 8 frames needs to shift on less than 1% of the calls and returns [Sta88(P50)]). However, some programs and procedures will require more stack space.

The C-processor can access various addresses at a time. At a certain moment, it is possible that the two operands for the next instruction are fetched from the stack, while the result from the last instruction is written on the stack. The execution unit has multiple ports to write to and read from the stack, so the stack cache has to support these multiple ports. Since it will have a high hit rate, the cache will give less memory requests to main memory. Thus the number of ports to main memory can be reduced.

So besides the speed of a cache, it has a second advantage: it can avoid multiple ports to main memory.

The stack cache will have the following requirements besides the requirements from chapter 1:

- it has to contain the highest stack frame

- it has to support multiple requests in one clock cycle

- it must be transparent to the software

## 3.2 Stack cache organisation

The stack cache will contain (a copy of) the memory locations near the top of the stack (TOS). The choice to have an extension of the memory stack or a copy of the memory stack is not very difficult. If the cache is to contain a copy of the locations near the TOS, the cache has to be write through to keep main memory up to date. This involves a lot of traffic. If an extension is chosen, the write back strategy (write back dirty blocks when they are replaced by another block only) can be used to solve consistency problems, and the probability of stack references falling in the cache is very high for a reasonable cache size. The penalty for task switches will be higher if an extension is used (write back dirty

blocks vs. no dirty blocks to write), but can be limited by using buffers. Besides, since task switches will be relatively rare, the performance loss in normal use for the caches using a copy, will be larger than the performance loss on the task switches for the extension caches. So the cache will contain an extension of the stack.

Only those places below the TOS are of interest, places above the TOS are invalid (the stack is growing upward). There are no coherence problems between processes, because a stack is private to a process (each process has its own stack, identified by the PIN). Since the stack is a contiguous area, the stack cache can best be organised as a contiguous area. Only two options for the cache memory organisation remain: the cache can be linear, or it can be direct mapped. The (set) associative cache will not be discussed here. In an associative cache some replacement algorithm must be used, which can replace blocks near the TOS. This behaviour is undesired for a stack cache because, although these blocks may be least recently used, the probability that these blocks will be used in the (near) future is high. The reason for this high probability is that these blocks are near the TOS. In other words: on a stack spatial locality is higher than temporal locality. A compiler can make the spatial locality even higher. The linear cache and the direct mapped cache will be discussed in the following sections.

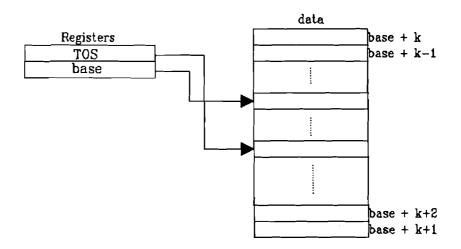

#### 3.2.1 A linear cache.

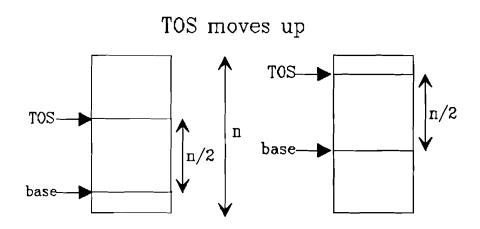

A linear cache contains all memory locations from a certain point, the base pointer, to the stack pointer (see fig. 3.2). The base pointer points to the lowest valid address in the cache. This need not be the frame pointer, since the cache may contain more than one frame. It is possible that this does not fill the cache. The cache can be organised as a linear buffer. When the stack grows, data at the base of the cache are threatened to be overwritten by the TOS and have to be written back to main memory (if they are modified), before more space can be allocated to the stack. No data has to be retrieved from main memory. The resulting free block is allocated to the TOS. This situation is called cache overflow.

Figure 3.2 A linear stack cache

Underflow occurs, when the stack is retreating. Again the stack pointer approaches the base, but this time from the other side. The cache then becomes empty, and new data has to be cached from main memory. Because the data beyond the TOS is invalid, no information has to be written back to main memory.

When an overflow or an underflow occurs, some action has to take place. Several replacement strategies deal with this situation. Some policies even try to avoid under- and overflow situations (some kind of prefetching) These policies, specially designed for stack caches, are dealt with in section 3.3.3.

When another process interrupts the running process, a task switch occurs and the whole cache has to be flushed; the data that has been changed has to be written to main memory and the contents of the cache has to be made invalid. A flush is necessary because the only addresses remembered are the base and the TOS. If any data remained valid in the cache, this would be used erroneously as valid data for the stack of the new

process. At the time of a task switch, the bus will be heavily used, and the processor will be waiting for data from the stack of the new process. The amount of data transferred depends on the replacement algorithm.

A way to reduce the number of task switches is the introduction of a second cache, to be used by the operating system or supervisor. To achieve the same hit ratio as the normal stack cache, the supervisor cache should be larger. If the same amount of data ram would be used, each of the split caches should be half the unified cache. Simulations in [Smi82(b24)] show that a split cache has a lower hit ratio than a unified cache. The larger penalty of the unified cache on supervisor calls can be reduced by architectural measures (chapter 4).

There are no coherence problems in a linear cache. The stack is private memory for a process and the whole cache is flushed on a task switch. Thus it is impossible that two different copies of the stack can be used at any time.

## 3.2.2 A direct mapped cache.

Instead of a linear cache, a direct mapped cache can be used. As long as all references are made to memory locations near TOS, this cache behaves like a linear cache.

Because each block in cache has its address in the tag, it is not obligatory to invalidate the whole cache on a task switch. If the processes can not migrate from one processor to the other, no flushing is needed at all! So if a process is interrupted by another process, which makes almost no use of the stack, a major part of the stack of the interrupted process will stay intact. This remaining part of the stack will probably not be a continuous part. Still, the parts that remained in cache will be valid and will not have to be read again. This minimises the penalty of task switches. When a process is interrupted by a large process, this process will fill the whole stack cache, so, though the cache was not flushed at the task switch, all data is replaced by the new process. The net result is

the same as a flush. The overhead of flushing the cache however, is not at the time of the task switch, but is smeared out over the beginning of the new process.

A disadvantage of a direct mapped cache is that the virtual addresses and the PIN-codes of all blocks have to be kept in the tag memory. So direct mapped caches will be larger than linear caches.

The same replacement strategies as in a linear cache can be used. However, care has to be taken to remove no blocks of other processes, and thus reduce the advantages of a direct mapped cache over a linear cache on task switches. Simulations will have to provide information about the behaviour of the cache organisations.

In a direct mapped cache, coherence problems can occur if a process can migrate from one processor to another. If a process migrates form processor A to processor B, changes some of the data on the stack and moves back to processor A, the contents of the parts of the stack which are still in the cache of processor A might not be the same as in the cache of processor B! If the migrating of processes is allowed, a cache coherence algorithm has to be used (see chapter 2).

# 3.3 The effects of cache parameters on a stack cache.

In this section the cache parameters will be discussed. First the cache size and the block size will be handled, then the replacement policies for stack caches will be compared. Finally the effects of task switching and cache coherency will be taken into account.

#### 3.3.1 The cache size.

In general larger caches give smaller miss ratios, longer access times, smaller traffic ratios and, depending on the cache structure, a larger or smaller penalty for task switching. Although the hit ratio increases with the cache size, the increase of the hit ratio will decrease as the cache becomes larger. In a linear cache the penalty for task switching will grow with increasing cache size since more data has to be flushed. In a direct mapped cache the probability that after a task switch some parts of the stack of the resumed process will still be present increases with the cache size and so the penalty of task switching decreases.

The task of the stack can be compared to the register sets in a RISC processor, so a cache size comparable to the number of registers in a RISC processor will probably suffice. The number of registers in a RISC processor ranges from several dozens to several hundreds (Risc I: 128, AM29000: 192, C/70: 1024). A processor with a stack cache, the CRISP uses 32 registers, each register is one 32 bit word wide. Simulations by Ditzel et al. [Dit87(P60)] proved this size to capture a sufficient amount of data for certain C-programs (using a non optimising compiler). However this included only the data of one procedure or function so "a larger cache size would reduce the amount of flushing on procedure or function calls and returns". Although these numbers are dependent on the instruction set, compilers and optimisers, they give an indication on the number of locals that need to be cached (in register sets) to give a high processor performance. Simulations have to provide data to find a cache size with a good trade-off between stack cache size and hit ratio.

## 3.3.2 The (transfer) block size.

The block size has a great influence on the performance of the cache. In a linear cache, the block size determines the quantity of data that is written to or read from main memory at overflow or underflow. Since a whole block is fetched on an underflow, a whole block will reside in the cache. The TOS will now reside on one block from the bottom of the cache. A large block size will thus increase the time between two underflow situations. A large block size will move the TOS further away from the border of the cache which was crossed. If the block size is to large, the traffic ratio will be high, and too much data will be replaced or fetched. Simulations are necessary to find the optimal block size.

In a direct mapped cache the tag of a block contains its virtual address and information about the validity of the data. Because the address of the data now also resides in the tag, a larger block size can reduce the size of the tag memory with a serious amount.

A block can be divided in transfer blocks. The tag of the block then provides information about the validity of each of the transfer blocks. The address is stored for the whole block. In case of an overflow only those transfer blocks that have been changed have to be written back to main memory. The introduction of transfer blocks thus reduces the amount of write back traffic. Transfer blocks can also reduce the miss penalty. As soon as a transfer block is in the cache, it can be marked valid, and the data can be transferred to the execution unit. Transfer blocks of more than one quad (= bus size) can make use of burst transfers to main memory which improves the average time to fetch a byte. However, large transfer blocks will increase the miss penalty and the amount of data written back.

# 3.3.3 Replacement policies

There are several replacement strategies which have to deal with or prevent overflow and underflow of the stack cache. Since most stack caches discussed in literature are linear caches, a few of the replacement policies for this type of caches will now be discussed. These policies are also discussed in [Sta87(B36)].

- The cut back K algorithm (see also [Has85(B36)]) is the most simple algorithm and acts only on demand.

- The barometer pointer algorithm tries to avoid both overflow and underflow.

- The two-pointer algorithm tries to keep the cache full and to avoid overflow.

In a modified form these can also be used for a direct mapped cache.

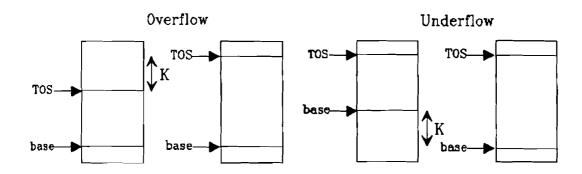

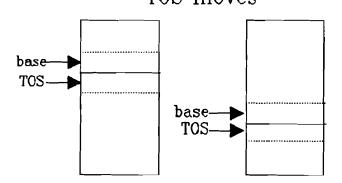

## 3.3.3.1 The cut back K algorithm

If the stack cache overflows (TOS moves above the cache) or underflows (TOS moves below the base), one or more blocks (containing K transfer blocks) are written back to

Figure 3.3 The cut back K algorithm

main memory in order to free cache space, respectively read from main memory to obtain the TOS (figure 3.3). The algorithm makes no attempt at predicting the future needs of the stack cache. On the average, the cache will be more than half full. Besides, the number of over- and underflows can be high. This can be offset by using larger blocks. However, this will increase the number of bytes transferred. More bytes that are not used are fetched, more bytes are replaced on an overflow.

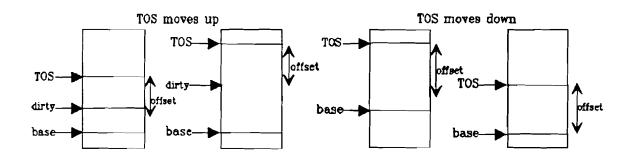

## 3.3.3.2 The barometer pointer algorithm

Figure 3.4 The barometer pointer algorithm

This algorithm keeps the TOS pointing to the middle of the stack cache (figure 3.4). It is possible to let the TOS point to another place in the cache. [Sta87(B36)] describes a simple barometer pointer algorithm. On an overflow the block to be cleared is always written back. Thus the penalties for overflow and underflow are equal (the main memory access for one block). The chance that the stack will grow is about equal to the chance that the stack will shrink. This makes the middle of the cache a logical place for the TOS to point at. The frequency of overflow and underflow is thus reduced. If the penalty for overflow differs from the penalty for underflow, the TOS can be kept pointing to another place in the cache, such that the overall cache miss penalty is minimised. If the TOS is

greater than the middle of the cache, blocks are read from memory until the TOS is in the middle, if the TOS is less than the middle of the cache, blocks are written to memory. A special pointer points at the middle of the cache. By keeping the cache half-full, the usage density is independent of the growth of the stack, but on the average it will be no more than half. Some extra buss traffic is introduced if the stack grows and shrinks without overflow or underflow, compared to the cut back K algorithm. As long as the cache would not overflow or underflow with the cut back K algorithm, these extra bus transfers are useless.

## 3.3.3.3 Two-pointer algorithm

This algorithm keeps the cache full (figure 3.5). It uses the cache to keep a copy of the stack in main memory, and uses a write back strategy (only write to main memory if a block is replaced) to keep main memory up to date. Besides the stack pointer, it uses two TOS moves

Figure 3.5 The two pointer algorithm

pointers to indicate how many blocks need to be written back to main memory (the PUT pointer) and how many blocks need to be fetched (the GET pointer). A detailed description is given in [Sta87(B36)]. If both pointers are zero, the cache is at rest. If a push is performed, the PUT pointer is incremented to indicate that a block has to be written back to main memory to make room in the cache for some new data.

This strategy also introduces a lot of useless bus traffic compared to the cut back K algorithm. Besides, if the stack is growing there is a continuous overflow situation. The mayor advantage of this scheme is that the whole cache is always full.

## 3.3.3.4 Comparison of the algorithms.

In general, some strategies try to minimise over- and underflow by keeping the cache half filled (two pointer algorithm), or try to detect trends (barometer pointer). Although they can succeed in their purpose, they also increase the traffic ratio, because not all space freed by writing blocks back to main memory will be allocated, and not all blocks cached from main memory will be referenced. The strategies can also work against themselves. Especially at the start and end of processes when the stack is continuously growing or shrinking. In general these strategies reduce overflow and underflow a little, while requiring a lot more bandwidth.

Other algorithms (like cut back K) only move blocks when necessary. This can result in a high penalty if a new procedure is started or finished if the cache is full resp. empty. The traffic ratio is completely dependant on the block size. If a fixed frame size is used for procedures, and the block size is equal to the frame size, the stack cache can be compared to the multiple register sets used in RISC (although there are some differences). One of the disadvantages of using a fixed frame size, is that the utilisation of cache memory will be far from optimal. Furthermore the allocation of variables in frames will become a task of the compiler, with a major influence on cache performance. A consequence of this is that the cache is no longer transparent to the software.

In [Sta87(B36)] three TOS management schemes are compared for a TOS buffer. The study uses single pops and pushes to move the TOS. This is not the case in the C-processor, where the TOS moves more than one memory location on a call or a return. Although the situation is not the same, the study can be used to give an indication for the

C-processor. The conclusions of [Sta87(B36)] support the conclusions given above. Their simple algorithm (comparable to the cut back K algorithm) greatly reduces the memory bandwidth by requiring little TOS management. The demand TOS management is nearly as high as the best of the other algorithms. The usage density is better than for the barometer pointer algorithm, but worse than the two pointer algorithm.

The barometer-pointer algorithm reduces the demand TOS management but requires a higher memory bandwidth and the usage density is low.

The two-pointer algorithm has the highest usage density, but requires a high memory bandwidth, the demand TOS management is high and it is the most difficult one to implement.

The study of Stanley clearly indicates that:

The simple algorithm (comparable to the cut back K algorithm) combines a high usage density with low bus traffic. Besides it requires the least extra hardware. This algorithm seems to be a good choice for a linear cache. The barometer pointer algorithm is second best.

However, as stated before, the results only give an indication for the C-processor. Besides, the results the effect of task switches has not been taken into account in [Sta87(B36)]. The effects of task switching will now be discussed.

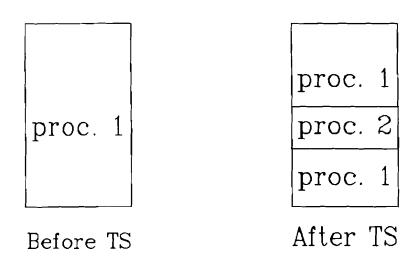

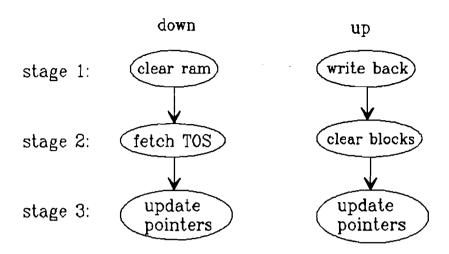

# 3.3.4 Task switching and stack caches.

The linear cache only keeps track of the lowest and the highest address of the data in the cache. If another process wants to use the cache, this information will be lost, so all data in the cache has to be written back to main memory before the new process can use the stack. For large caches these cache flushes can cause a lot of bus traffic and a large time penalty for task switches.

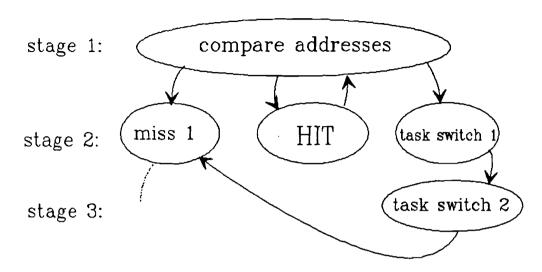

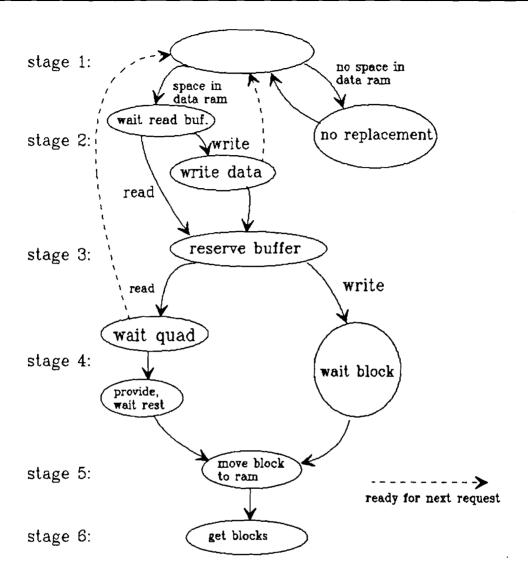

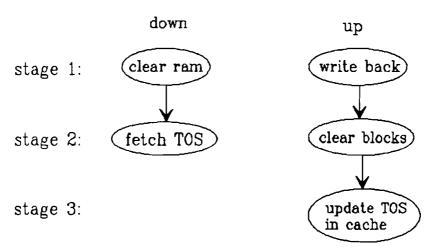

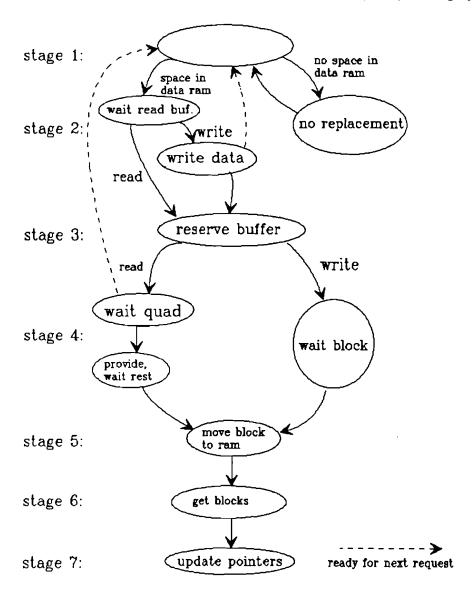

For the replacement algorithms, the effects are most severe for the two pointer algorithm, which keeps the cache full, and the cut back K algorithm. The barometer pointer cache