| onal design level 1 and 2 |

|---------------------------|

|                           |

|                           |

|                           |

|                           |

|                           |

Link to publication

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

4973

ECB 972

Eindhoven University of Technology Department of Electrical Engineering Group of Digital Systems (EB)

X.25 CO-PROCESSOR

FUNCTIONAL DESIGN LEVEL 1 & 2

by A. Klip

Graduation report by A.Klip

Supervisor : Prof. Ir. A. Heetman Coach : Ir. M.P.J. Stevens

Eindhoven, The Netherlands August 1985

The department of Electrical Engineering of the Eindhoven University of Technology does not accept any responsibility regarding the contents of student projects and graduation reports.

### Summary

This report describes the functional design of a X.25 coprocessor for data communication as recommended by the CCITT in X.25. The design of hardware and software of level 1 and 2 will be discussed. Level 3 and testing of the co-processor can be found in other reports from the Digital Systems Group of the Eindhoven University of Technology.

# Contents

|   | Preface                           | 5      |

|---|-----------------------------------|--------|

| 1 | X.25 recommendation 1.1 Layers    | 6<br>6 |

|   | 1.2 Data structure                | 7      |

|   | 1.3 chip outline                  | 8      |

| 2 | Level 1                           | 15     |

|   | 2.1 Level 1 states                | 15     |

|   | 2.2 Level 1 transmitter           | 15     |

|   | 2.3 Level 1 receiver              | 17     |

|   | 2.4 Initialisation of level 1     | 18     |

| 3 | Low level 2 transmitter           | 23     |

|   | 3.1 Pattern generation            | 24     |

|   | 3.2 Zero insertion                | 24     |

|   | 3.3 FCS generation                | 25     |

|   | 3.4 Transmit manager              | 25     |

|   | 3.5 Low level 2 tx/               |        |

|   | high level 2 tx communication     | 26     |

|   | 3.6 Low level 2 tx initialisation | 28     |

| 4 | Low level 2 receiver              | 32     |

|   | 4.1 Pattern recognition           | 33     |

|   | 4.2 Zero deletion                 | 34     |

|   | 4.3 FCS checking                  | 35     |

|   | 4.4 Bit counter                   | 35     |

|   | 4.5 Receive manager               | 36     |

|   | 4.6 Low level 2 rx/               |        |

|   | high level 2 rx communication     | 37     |

|   | 4.7 Low level 2 rx initialisation | 39     |

| 5 | High level 2                      | 43     |

|   | 5.1 Level 2 states                | 43     |

|   | 5.2 Link set up                   | 44     |

|   | 5.3 Link disconnection            | 44     |

|   | 5.4 Link-up states                | 45     |

|   | 5.5 State summary                 | 46     |

| 6 | High level 2 construction         | 60     |

|   | 6.1 High level 2 receiver         | 60     |

|   | 6.2 Wigh lovel 2 termemittee      | A1     |

| 6.3 High level 3 communication 6.4 Low level 3 communication 6.5 Internal level 2 registers 6.6 Other level 2 provisions 6.7 Low level 2 communication 6.8 Initialisation | 62<br>64<br>65<br>66<br>67<br>68 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

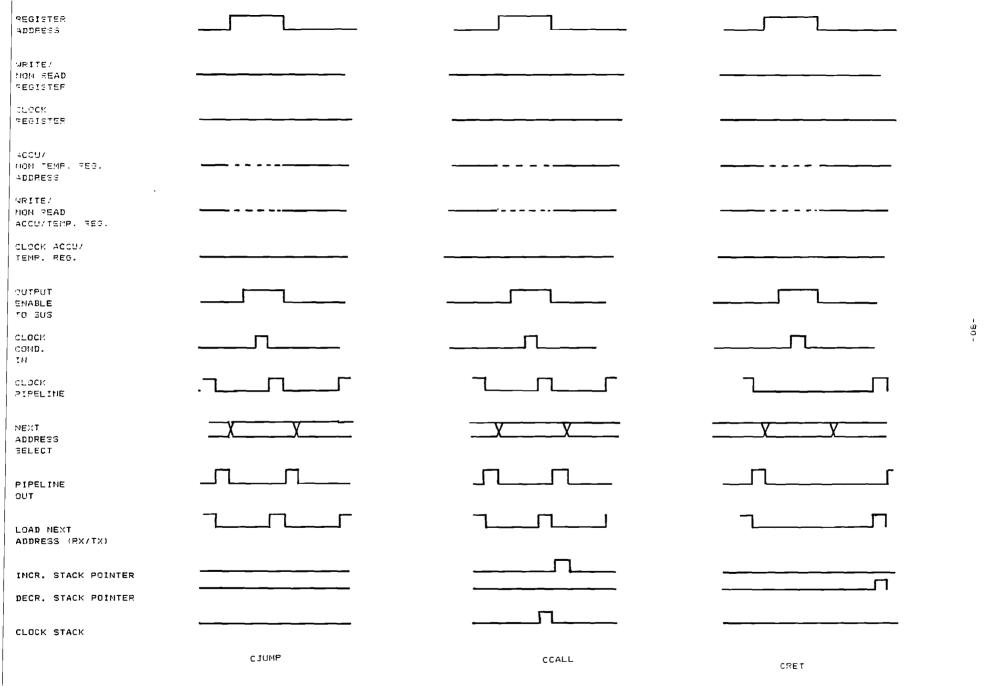

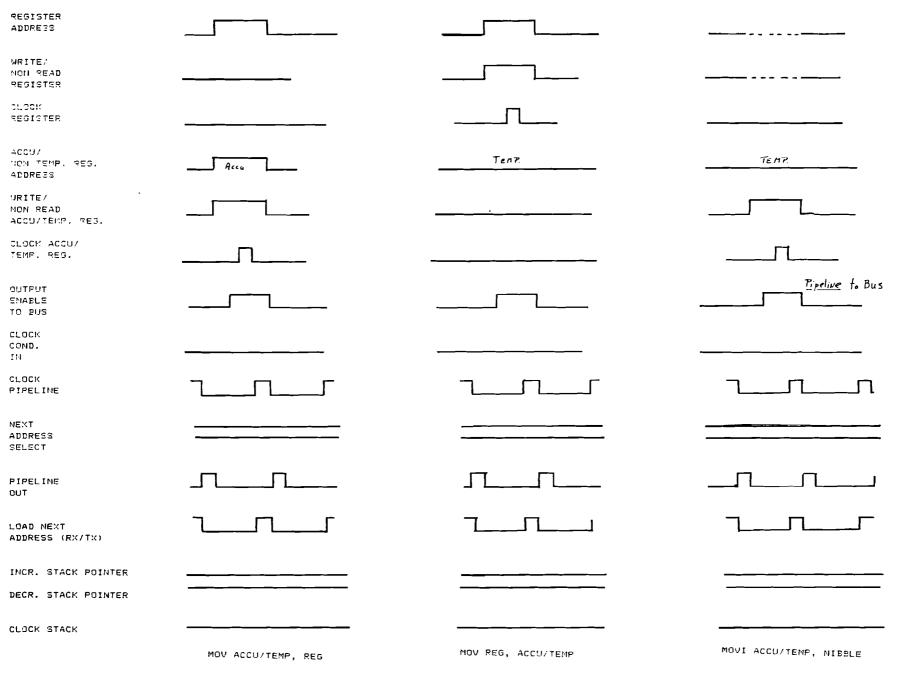

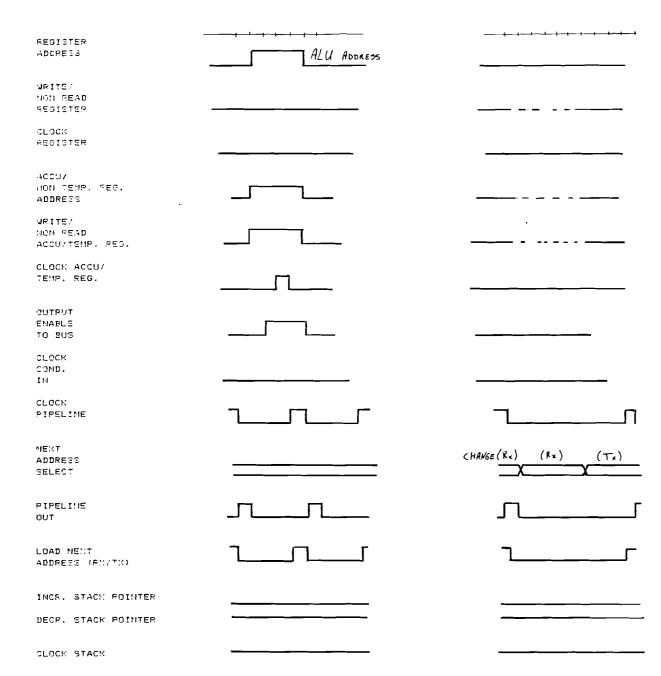

| 7 Microcontroller 7.1 Rx/Tx concurrent programming 7.2 Hardware provisions 7.3 Microinstructions 7.4 Microcode execution and timing 7.5 Controller Initialisation         | 71<br>71<br>72<br>73<br>76<br>77 |

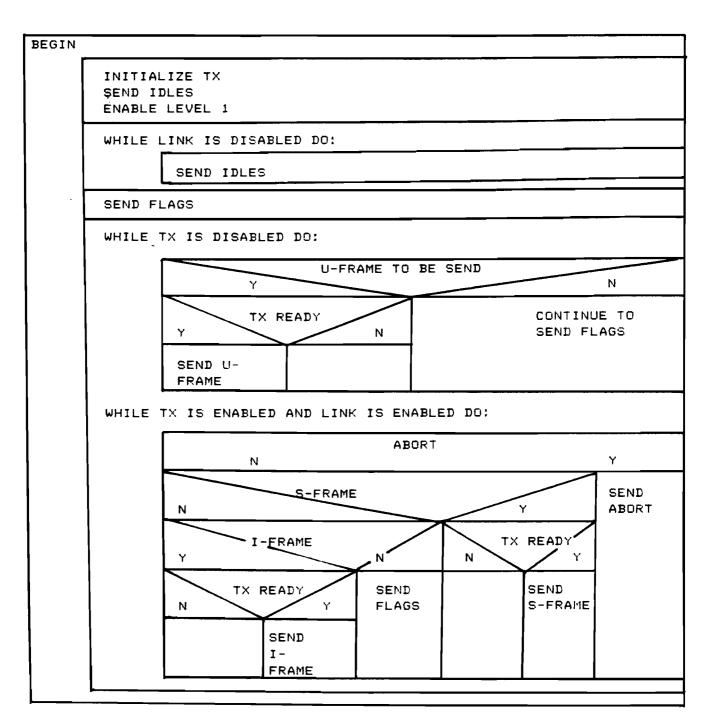

| 8 Microcode program<br>8.1 Nassi Shneiderman<br>8.2 Tx example assembler program                                                                                          | 83<br>83<br>83                   |

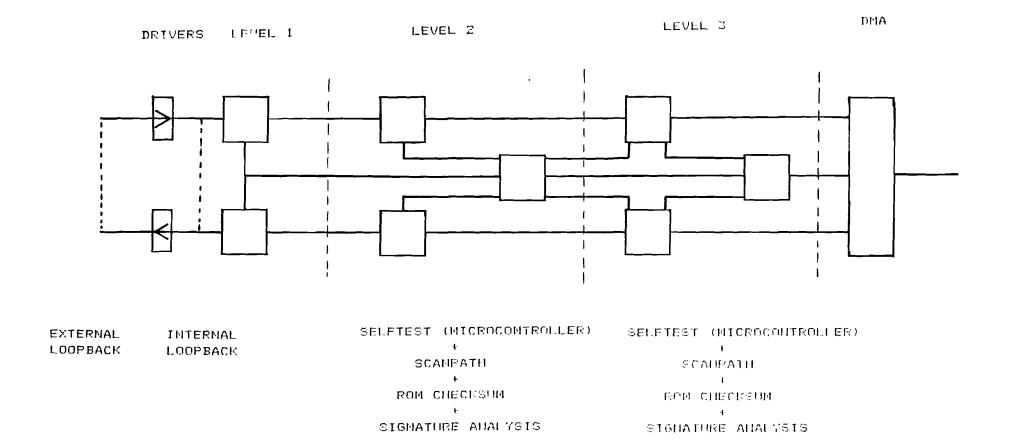

| 9 Testability<br>9.1 Factory test<br>9.2 Go/no go test<br>9.3 Testing by the host                                                                                         | 88<br>88<br>89<br>89             |

| 10 Conclusions                                                                                                                                                            | <b>9</b> 3                       |

| Literature                                                                                                                                                                | 95                               |

| Figure list                                                                                                                                                               | 96                               |

#### Preface

A study has been made of the X.25 protocol together with a design how this protocol can be implemented in a single chip co-processor. Level 3, the communication with the host processor and the data structure in the hosts memory have been studied by H.P.M.J. Schenkelaars.

This report contains the level 2 and level 1 analysis and the functional design of the hard— and software. The coprocessor has been partitioned into several finite state machines, a number of shift registers and several processors, each for a special task in the X.25 protocol.

The chip has been designed for application in a DTE (Data Terminal Equipment) as well in a DCE (Data Circuitterminating Equipment). The initialization procedures and the communication with higher levels will also be discussed. A decomposition of the hardware has resulted in quite simple descriptions of the parts of the chip. The chip is designed to work with an Intel or a Motorola bus, with 8 or 16 bits data structures and for a maximum bit rate of 64 kbit/sec.

The software for the host for the level 4 data handling is under study by E.P.M. Bakker. The test procedures and hardware to be integrated into the chip will be discussed by H. van Ooijen. All reports from the Eindhoven University of Technology.

The aim of this study was to design a X.25 co-processor that would not require large printed circuit boards with expensive software. The chips on the market are considered as only implementing parts of the 3 level deep X.25 protocol. This chip should contain all levels. The layer structure of X.25 should be maintained throughout the design. As a result of the study it seems feasible to develop such a single chip X.25 co-processor.

#### 1 X.25 recommendation

protocol a standard concerning in communication between computers has resulted recommendation of the CCITT. This X.25 recommendation has adopted the lower 3 lavers of the 7 laver ISO (International Standard Organisation) model of Open System Interconnection. Open does not refer to a particular implementation. It simply indicates that the system supports standards which enable these systems to exchange information with all sorts of other users. The recommendation specifies the interfacing between DTE (Data Terminating Equipment) and DCE (Data Circuit-terminating Equipment). More generally speaking the DTE is the computer of a subscriber, or the intelligent terminal, and the DCE the network of the telecommunications company. Mostly the DCE is the first node in the data communications network.

X.25 gives rules for the lowest 3 layers of the ISO model. For the lowest layer parts of the CCITT recommendation X.21 have been used. The protocols described are about communication set-up and disconnection, flow control and error handling and (if possible) recovery. Because the hardware and software for these protocols are quite large, about 2 eurocards and 100k software, a single-chip solution would be very welcome to designers for datacommunication equipment. In this chapter an outline of the functions to be performed and the global architecture chosen are discussed.

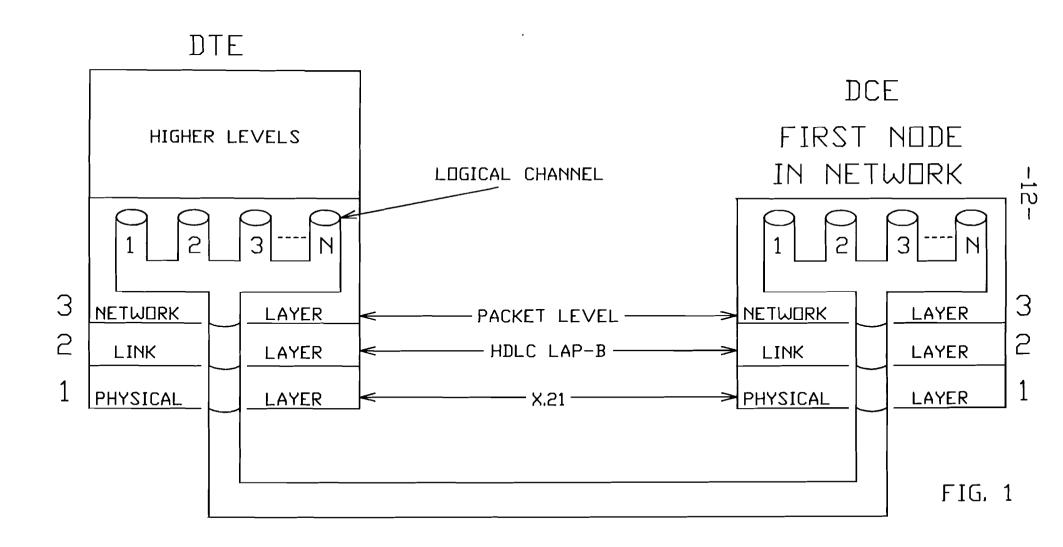

#### 1.1 Layers

The lowest layer of the ISD-OSI model is the Physical layer, also called the physical level. This layer defines the electrical and mechanical connection of the link between DTE and DCE. X.25 gives the paragraphs of recommendation X.21 which are supported for this layer. X.21 bis is a standard which is allowed for an interim period of time, and some administrations may offer a DCE/DTE interface in accordance with this. The design of the chip supports X.21 because this is the recommended protocol. The function of level 1 is to make an electrical connection between level 2 and the network (mostly present in the form of a modem). The working of the physical layer receiver and transmitter will be described in chapter 2.

The second layer is the Data-link layer. This layer concerns the frame level of the data communication. Data bits from higher levels are to be transported between DCE and DTE in such a way that an error free link is reached. To accomplish this, the level 3 data has been packed in frames in such a way that errors occurred during transport over the communication lines will be detected. Then the level 2 protocol has several ways to ask for retransmission. Or the logical link an be reset by transmitting a special purpose frame. Level 2 also offers a logical connection between level 3 of the DCE and level 3 of the DTE and uses transport via the levels 1, the modems and the network.

The third layer is the Network layer. On this so-called packet level, the data from a subscriber will be multiplexed with data packets from other subscribers. Over one logical link there can be more than 4000 logical channels. The host computer only has to allocate space for the receive buffers in the shared memory and to send a request to make a virtual call to an other computer or terminal. Level 3 then opens and closes the logical channels on level 3. It also controls the data flow of each logical channel separately. Error recovery is done by initializing and clearing of a single channel, or of all channels. Level 3 offers the host an opportunity to send a high priority byte of information which passes by the normal flow control.

Figure 1 shows how the principle of datacommunication with the X.25 protocol works. Higher levels present their data to level 3 which opens a logical channel and makes a virtual call to another station. The information from level 3, data or channel management information, are data frames for level 2. Level 2 converts these level 3 packets into level 2 frames and transmits them over the one logical link via the physical layer. At the destination on the other side of the network, the frames will be received and if they are not level 2 link management frames but level 3 information, the packets will be unpacked and if they are correct, passed to level 3 which distributes them to the several channels.

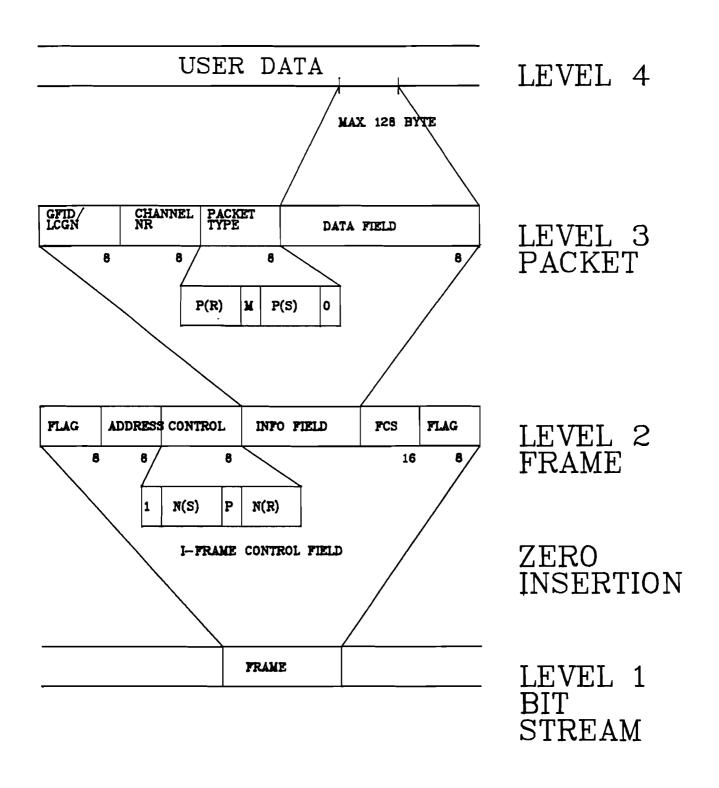

#### 1.2 Data structure

Figure 2 shows how level 2 frames and level 3 packets are constructed. Level 4 data is presented by the host processor to the X.25 co-processor in a data format of 128 octets. Level 3 of the co-processor adds a packet type identifier (8 bit) and a logic channel number (8 bits). Preceding these there is a general format identifier/logical channel group

number. In a report written by H.P.M.J. Schenkelaars packing and unpacking of the level 4 data by level 3 has been described.

Sequencing and distribution of the packets are controlled by the header. Besides that a non-data packet can be sent for instance for setting-up a call or disconnecting one. The level 3 processing is very complex, so level 3 has its own sub-processors.

Level 3 packets have to be transferred between DCE and DTE, over a single line (logically seen), and free of errors. For this reason level 2 has its own sequence control protocol (for a single line) and an error detection mechanism. The level 3 data, 128 bytes + 3 info bytes, is therefore enveloped by 6 octets of level 2. First of all there is a leading flag, indicating that the data-, or control-frames is starting. After the flag there is an address, indicating if the frame is a command or response, and a control byte for the link maintenance and sequence control. If the frame is not a control frame, the so-called U or S frame, the level 3 packet follows. After the level 3 data an error detecting code, generated by level 2, will be transmitted and a closing flag. This last flag indicates that the transmission of the frame has ended. It can also be the leading flag of a new frame. By the way, the chip can support the sharing of a flag shared as trailing and leading flag by two frames. The level 2 bits are fed into level 1 and transmitted without change. So level 1 adds no extra data to the level 2 frame. The operations of level 1 and 2 will be explained in this report, level 3 can be found in the report of H.P.M.J. Schenkelaars. The level 3 report also explains the communication with a host-processor in an Intel or Motorola environment.

#### 1.3 Chip outline

A decomposition of the X.25 protocol gives the different functions to be performed.

For the receiver these are:

frame in: - handles the X.21 protocol procedures for physical link setup.

address control

information if present Frame Check Sequence

- handles data transparency.

Packet disassembler:

- disassembles a packet into GFID/LCGN (General Format Identifier/ Logical Channel Group

Number)

LCN (Logic Channel Number)

PT (Packet Type)

Data for higher levels

(P)VC de-multiplexer:

puts the data and additional housekeeping information of the various channels in their corresponding channel descriptors.

- generates housekeeping information to keep track of the state of that

channel.

(P)VC control:

- location to put and read data and control information of a single channel (channel descriptor)

For the transmitting part of the co-processor these functions are:

(P)VC control:

- location to put and read data and control information about that channel (channel descriptor).

(P)VC multiplex:

- reads housekeeping information and data and initializes the corresponding registers in the packetassemble module and handles the state of each channel

packet assembler:

- assembles the header of the packet by shifting the octets out of their registers, like

GFID/LCGN

LCN PT

fetches data out of memory to

#### transmit them

frame assembler:

- assembles a frame by shifting out

the registers containing:

flags

address control byte information

- generate a FCS and shift it out.

- handles the transparency of the transmission. This is done by the zero-inserter

frame output:

- handles the X.21 protocol.

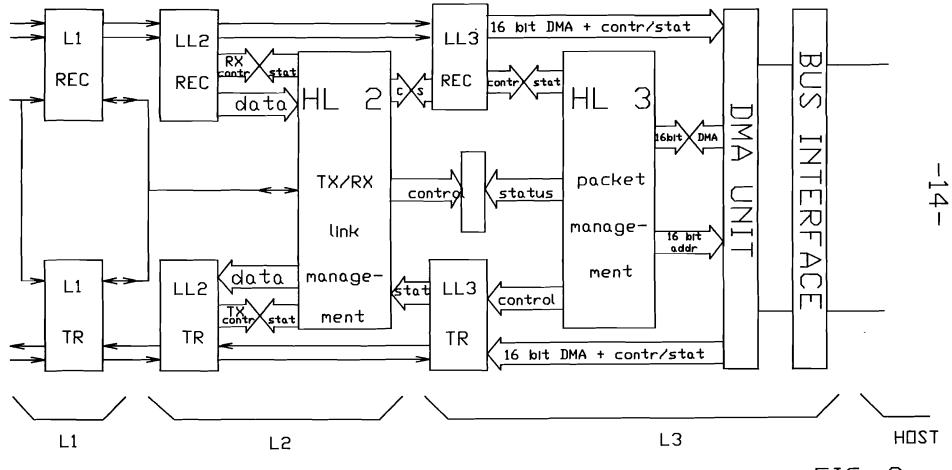

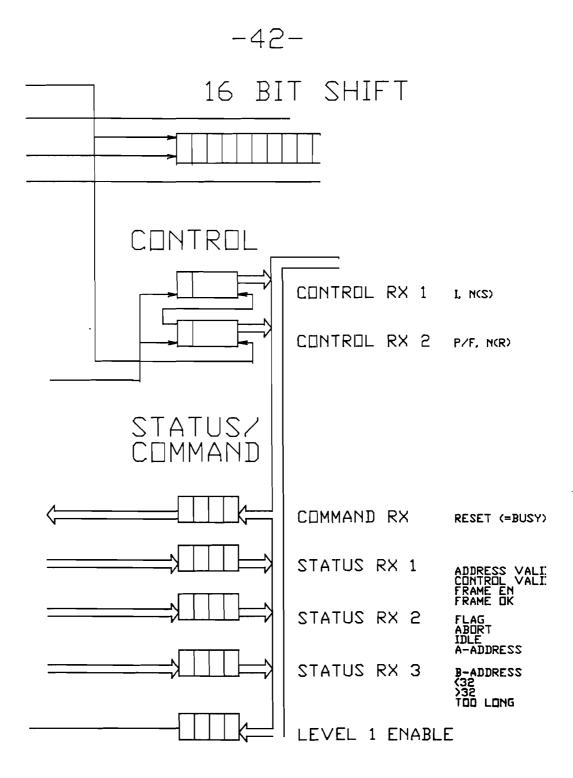

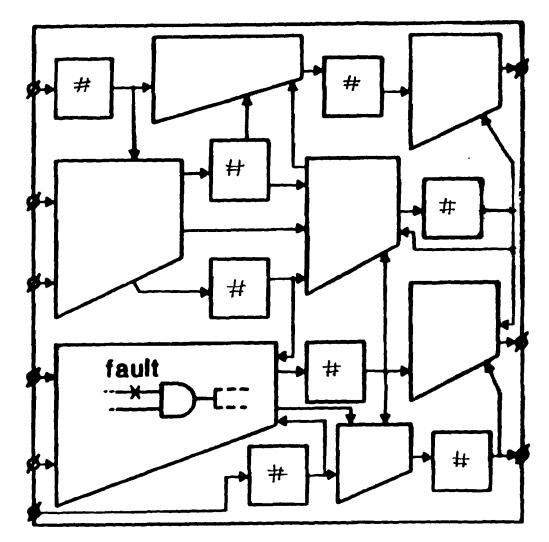

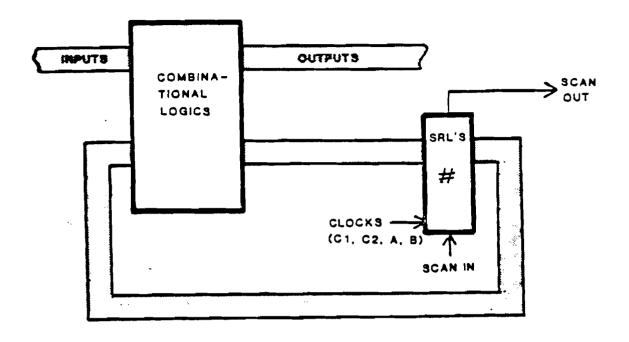

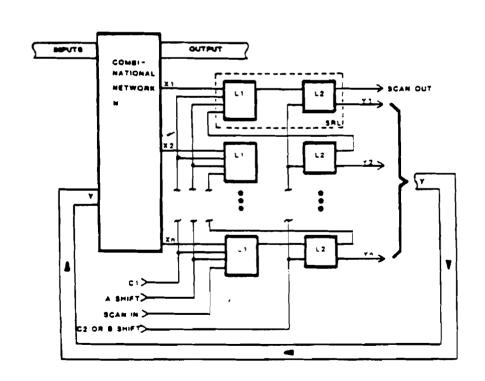

In figure 3 the functional decomposition is recognizable in the main architecture of the X.25 co-processor. The level 1 transmitter and receiver are clearly recognizable. The level 2 functions handled in the low level receiver and transmitter if they are simple enough. Controlling the standard functions of the low level 2 machines is done by high level 2. This is a microprogrammed controller which manages the logical link. Receiver and transmitter use the same microprocessor architecture within high level 2, and a set of communication registers to allow receiver/transmitter communication and concurrent program execution. The communication between low and high level 2 is through a number of 4 bit registers (bitwise accessible from low level 2 and 4 bit parallel from high level 2).

Data for level 3 is passed to the low level 3 receiver where the low level functions like demultiplexing are performed. Via a DMA unit the received data is stored in memory. The Bus interface handles the Intel or Motorola bus. The low level transmitting functions are similarly done by several machines in the low level 3 transmitter. Data and control information is coming from high level 3, and from the host. High level 3 controls the low level 3 machines, level 2 and lower. Data Handling and communication information in the main memory is an important part of the design and is discussed in the level 3 report.

Level 3 uses an 8 bit databus structure for internal communication with the low level 3 machines and the high level 3 provisions. For communication with the host system a 16 bit address and 16 bit data structure has been chosen, with a possible multiplex depending on the package. A 40

pens DIL package has more limits than a 64 pin grid package.

The high level 3 manager communicates with the host via a special command and response area in shared memory, and generates an attention signal to the host. The communication between level 2 and level 3 goes via 4 bit registers for level 3, accessed as 8 bit registers for level 3. Based on the wider databus of level 3. Two 4 bit registers for level 2 are seen as one 8 bit level 3 register. The data is exanged in these four bit as 3 bit data and 1 flagbit ( indicating a change). The communication is strictly controlled to prevent a write action while the other processor is reading or writing. For the different flags, an attention is generated. This attention is checked and processed by high level 3 if its microprogram allows it. Beside high level 2 - high level 3 communication, there is also a command/status exange between high level 2 and low level 3 via a set of 4 bit registers. Level 3 communication will be discussed in chapter 6. Chapter 3 and 4 describes low/high level 2.

# X.25 LOGICAL CHANNELS

FIG. 2

FIG. 3

#### 2 Level 1

Level 1 is designed according to the CCITT X.21 recommendation. This layer is the electrical interface between the network and level 2, the link layer. Level 1, the physical layer, is intended to send data from level 2 if the network is operational (ready). In the same way received data will be delivered to level 2.

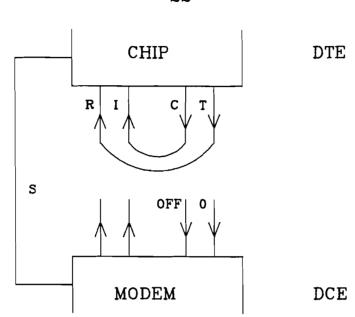

Level 1 consists of four units. A receiver, a transmitter and a test-loop provision. The fourth part is a clock synchronizer. This piece of hardware has to sample the incoming clock (S) with a high sample rate. The outgoing clock signal will only change on an edge of the high frequency system clock, used on the chip. The S signal will be a 48 kHz signal typical, or at most 64 kHz. 48 kbit/sec is the highest bitrate allowed in the X.25 recommendation. The on chip clock will be about 20 MHz with high speed CMOS.

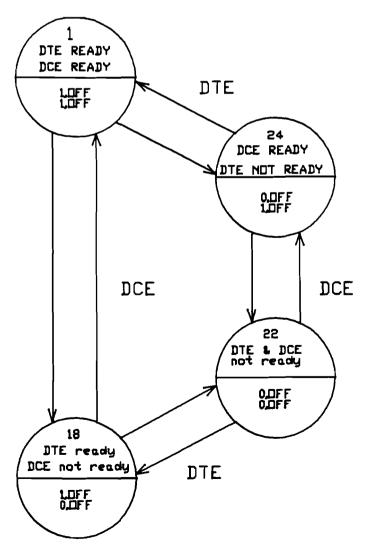

# 2.1 Level 1 states

We can distinguish four states in the level 1 DCE-DTE relation. See figure 4. The first state after power-on is state 22: DTE not ready and DCE not ready. State 24 is the situation in which the DTE is not ready and the DCE is ready. In state 18 is the DCE not ready and the DTE ready. The last state, state 1 is the state in which both DCE and DTE indicate that they are ready, and the data transfer state can be entered. As far as level 1 is concerned, there is no difference between a chip acting as DCE or as DTE. The only difference is a name for the "other side not ready" situation. This state can be called state 18 or state 24, but it is in fact the same state, only the opponent has another name.

In all states a signal is regarded as stable if it has no changes during 16 bittimes. A state has to be presented to the outside for at least 24 bittimes, if the state is to be considered stable.

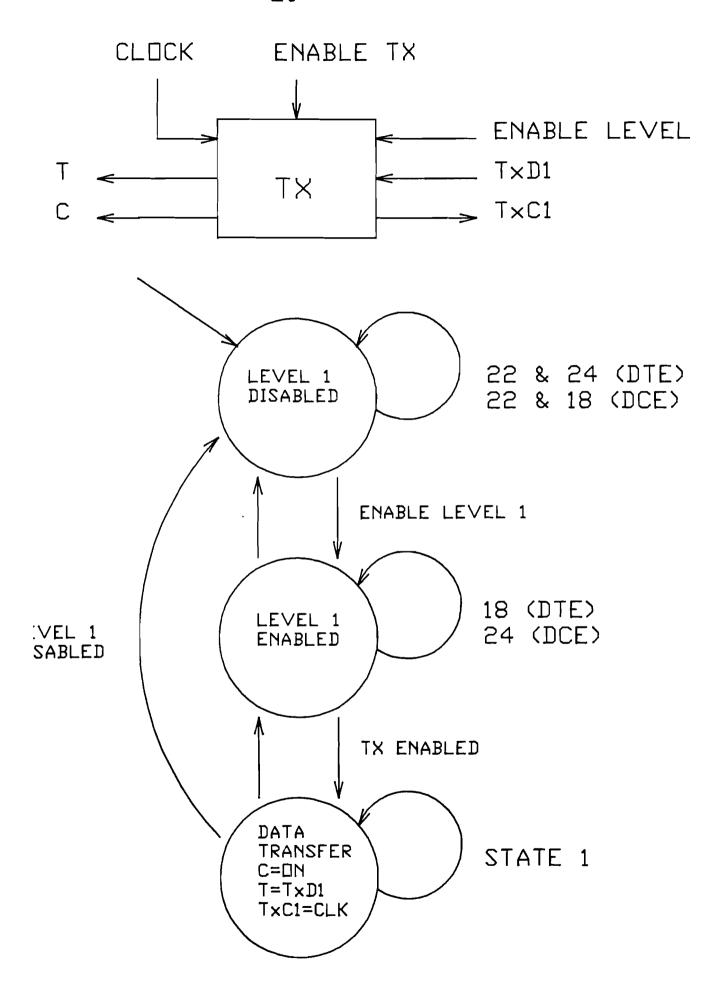

# 2.2 Level 1 Transmitter

The level 1 transmitter is the chain between the level 2 transmitter and the network. The transmitter on level 1 has

to transfer the data from level 2 to the DCE if level enabled and the DCE signals READY (I is low and R is 1) or the I-line from the DCE is high (see figure 4). If level 1 is enabled it means that the higher levels want to make or maintain an electrical connection to the network. signalling ready makes clear that the network can start an electrical connection. If the I-line from the network is high then the bits on the incoming line, the R-line, are valid. Then connection is allowed too. The C-line must be set high in case of transmitting data (level 1 enabled), thus making the bits on the outgoing T-line valid to the DCE. If the DCE is not ready, information transfer is useless. This is further explained by the receiver of level 1. In case of not being enabled, level 1 transmitter must set its T-line O and its C-line low. This means that the chip is not ready for data acceptance. If the chip is ready for data acceptance but the network is not, the C-line must stay low but the T-line can be set to 1. The situation of a network not being ready is detected by the level 1 receiver and given to the level 1 transmitter by an enable-tx line. This is another enable line as the enable from level 2 and higher.

The four states mentioned can be brought back to three states for the transmitter. First of all the reset state, a combination of states 22 and 24 (DTE) or state 22 and 18 (DCE). In this state the tx signals uncontrolled not ready (C=off, T=0). If level 1 is enabled, state 18 is entered, in which case the tx signals ready. If the tx is enabled then, by the receiver, state 1 is reached. In this state the clock is transferred to the low level 2 transmitter and the data from this transmitter goes to the T-line. The C-line is on then. From all states the reset state is entered if level 1 is not enabled anymore. If the tx is not enabled, from state 1 state 18 is entered again.

(Note: The Dutch PTT only enables level 1 and then starts sending data to the DCE.)

### <u>Signals:</u>

input: CLOCK, DATA, enable-tx, enable-level-1

output: CLOCK, C, T

Input data must be delivered to level 1 on the rising edge

of the outgoing clock. On the trailing edge of the clock the data has to be valid. These signals concern level 2 low. On the network side of level 1 the C-line must rise to high level on the leading edge of the clock, and the data on the T-line is allowed to change at the same moment. On the trailing edge the data has to be valid. The clock is given to high level 2, the incoming data is transferred to the T-line and the C-line is made high, if level 1 enable is true and tx enable from the receiver is true.

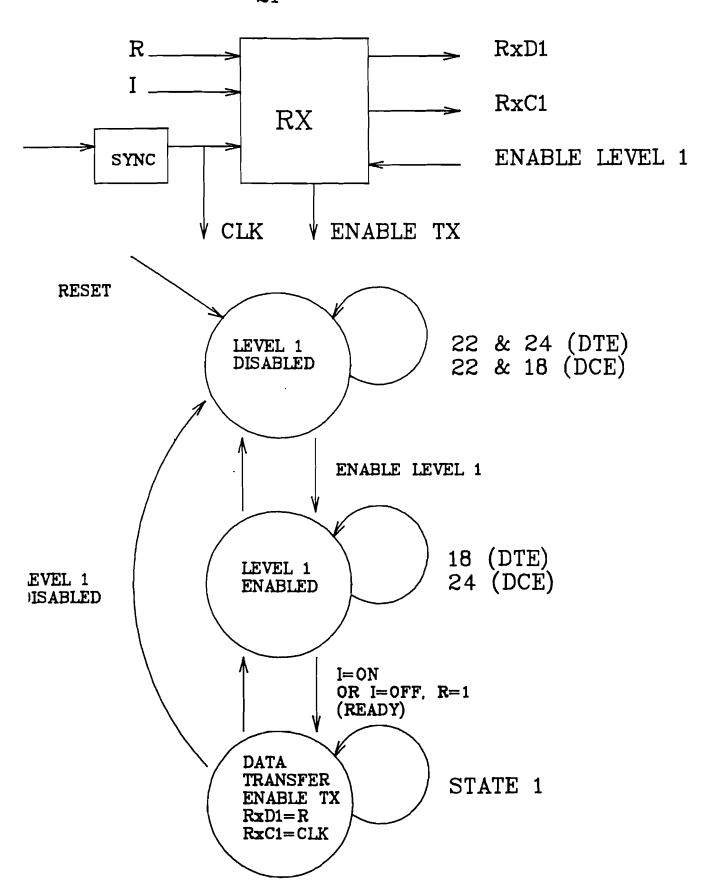

# 2.3 Level 1 Receiver

Received data bits are fed into level 2 if level 1 is enabled and the I-line is high (see figure 4). The enabling comes, as in case of the transmitter, from higher levels, and enables the electrical connection of the network signals to the chip. If the I-line is high then data coming from the DCE by the R-line is valid. It also confirms that the network is present and thus the transmitter is allowed to send data. The situation that the I-line is low and the R-line is low means that the DCE is not ready. In this case no bits are let through to the level 2 receiver.

Again from the four states mentioned above, three states can be distilled. The first state is entered after reset. As long as level 1 is not enabled by level 2, the receiver stays in this combination of states 22 and 24 (DTE) or states 22 and 18 (DCE). After the enable level 1 signal, state 18 is entered, if the DCE is not ready, the receiver stays in state 18, if the I-line goes "on", state 1 is entered and the received data is transferred to the low level 2 receiver. Level 1 tx is then also enabled. If the DCE signals ready, also state 1 is entered, but the data on the R-line is not transferred to the low level 2 receiver until the I-line is on.

If level 1 is not enabled, the first state is entered from state 18 as well as from state 1. If the DCE is not ready, or I is not on, state 18 is entered.

#### Signals:

input: CLOCK,R,I,enable=level=1

output: CLOCK,DATA,enable=tx

Incoming data can change on the leading edge of the clock and is valid at the trailing edge. The outgoing data must have the same characteristics. Enable-tx is only allowed to change on a leading edge. Similarly the enable-level-1 line.

The function of the receiver is also: connect the R-line to the level 2 Rx data entrance if the I-line is high for 16 bittimes and level 1 is enabled. Make enable Tx true if the I-line is high for 16 bittimes, or the I-line is low and the R-line is 1 for 16 bittimes.

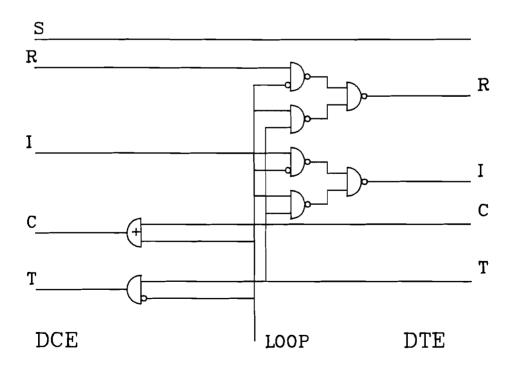

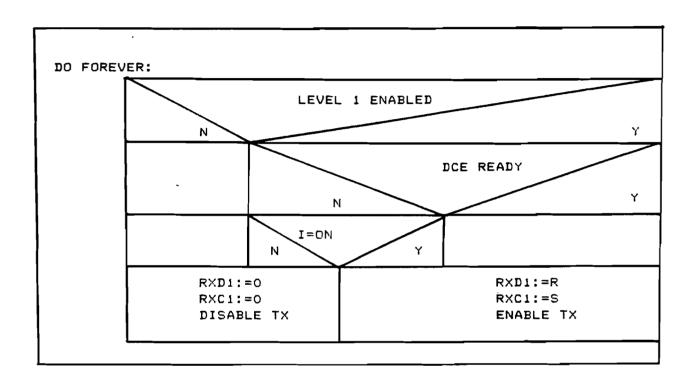

#### 2.4 Initialisation of level 1

Level 1 can be enabled after the higher levels. First these higher levels have to be ready with their own initialization, or restart program. The enabling comes from high level 2, since this is the controlling part of the level just above level 1. There is a possibility to read the status of level 1 by clocking out the states of the receiver and transmitter. So far, there was no need for level know the status of level 1, but the host can be curious why level 2 is still in the state of trying to make a connection after a certain time. The state of level 1 can maybe be read with the same mechanism that has to test the chip, and is being developed by another student, H. van Ooijen. provision that is present and can be used for test purposes is the level 1 testloop. In this testloop the I and C lines and the T and R lines are connected. See figure 6. In this way the transmitted data from the chip is fed back into the receiver of the chip. The C line to the DCE must be off, and the T line O in this case. A state of being not ready is so signalled to the network. In this way the whole chip can be tested, without the line drivers and buffers. As can be seen in figure 6 the circuit is quite simple, so this testloop is incorporated in the design.

According ANNEX A to Recommendation X.21 Interface signalling state diagrams

n State number

t Signal on T circuit

c Signal on C circuit

r Signal on R circuit

I Signal on I circuit

FIG. 4

FIG. 5

FIG. 6

Testloop 1

FIG. 7

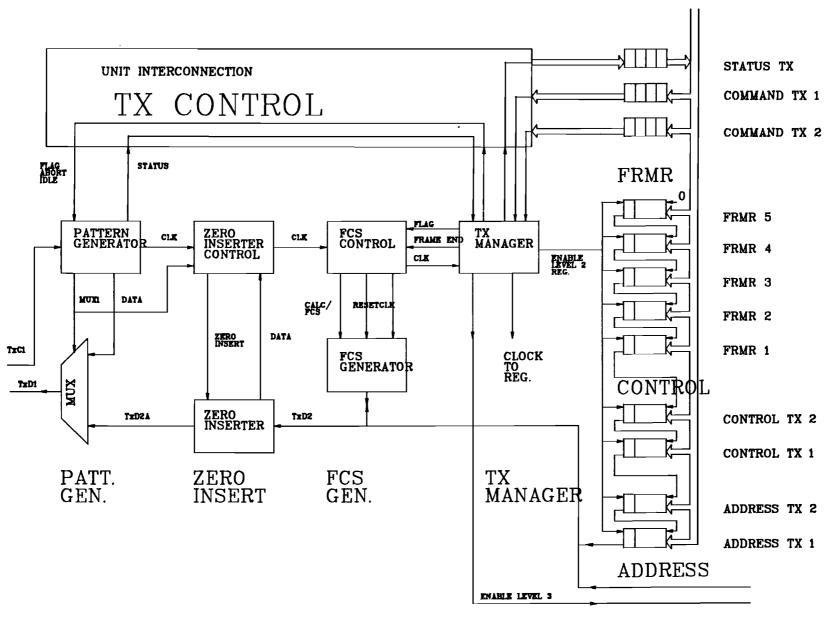

#### 3 Low level 2 transmitter

Level 2 is intended to set up, maintain and disconnect a logical link between a DCE and a DTE. We can distinguish higher and lower level functions. The more intelligent part is called high level 2, and controls the connection, while the more standard functions are called low level 2. The controlling of the link is the task of a microprogrammable controller. This controller is situated in high level 2. Low level 2 is separated in several dedicated task machines. The data manipulation parts and the controlling parts of the finite state machines in the low level transmitter are separated. See figure 8.

Briefly all low level 2 transmitter functions:

- Transmit flags on request of high level 2.

- Transmit on request an information, unnumbered or supervisory frame.

- Transmit on request an FRMR frame.

- Support the transmission of frames with the automatic insertion of a zero after five ones.

- Generate automatically a Frame Check Sequence for the frames being transmitted.

- Transmit on request an ABORT sequence.

- Transmit on request an IDLE sequence.

- Support the transmission of frames with a leading flag, an address byte and a command byte, the latter delivered from high level 2. The same with the FCS and the trailing flag.

#### Signals:

input: DATA from level 3,

CLOCK from level 1,

Commands from high level 2:

FLAG/NON\_TX\_FRAME, ABORT, IDLE, FRMR, PACK\_END, \*\*\*\*(RESET)\*\*\*\*

ADDRESS, CONTROL, FRMR bytes.

output: DATA to level 1, CLOCK, ENABLE to level 3, CLOCK, ENABLE to high level 2, Status to high level 2: ready

#### 3.1 Pattern generation

Information from level 3, or link control data from high level 2 must be transmitted in a standard frame envelop. At the start a flag: 0111 1110. This flag is generated at command of the low level 2 tx manager, by the flag generator. This finite state machine also generates an abort (111 1111): seven ones, or an idle (1111 1111 1111 1111), fifteen ones, if this is requested.

An abort or idle command from high level 2 is followed by an abort or idle sequence consisting of ones, generated by the flag/abort/idle generator. Frames being transmitted are aborted then. If the low level transmitter is ready with the transmission of a single flag, abort or idle, or of a whole frame, the ready state is reported to high level 2 via the ready bit register.

The pattern generator receives the clock from level 1 and gives it to the zero inserter control if the pattern generator is not busy transmitting any sequences. If the generator receives the flag, idle or abort command, it makes the outgoing MUX1 signal high, so the multiplexer selects the pattern generator as source. This same signal disables the other level 2 machines. The DATA line is then fed with the required patterns. If the pattern generator has done its job, it sets its status line high, meaning it is ready for a next command from the Tx manager.

#### 3.2 Zero insertion

During transmission a sequence of five ones is automatically interrupted and a zero is inserted. The data stream then goes on until a next sequence of five ones. The object of this zero insertion is to prevent flag, abort or idle imitation of data transmitted between two flags. This could disturb the correctness of the receiving process. The zero

inserter transfers the incoming data from line TXD2 to the outgoing dataline TXD2A, if the ZERO INSERT line is low. If this line is high the TXD2A line is made zero. The data from line TXD2 is also transferred to the zero inserter control, for analysis.

The zero inserter control counts the number of clock periods the data on line TXD2 is one, and makes after five ones the zero insert line true. The zero insert control starts its work from zero if the MUX1 line goes low. A reset takes place if a zero is inserted, or a zero in the data stream occurs and on th trailing edge of the MUX1 signal. The clock is not transferred to the FCS control if a zero is being inserted, or if the MUX1 line is high.

# 3.3 FCS generation

The FCS control receives the clock from the zero inserter control and transfers it to the Tx manager. from this Tx manager it receives the signals flag, and frame end. On the trailing edge of the flag signal the FCS control generates a reset or preload pulse for the FCS generator. On the leading edge of a frame end signal, the FCS control makes the Calc/non-FCS line low. The clock is also delivered to the FCS generator.

The Frame check sequence generated by the FCS generator is a pattern that is left in a 15 bit register after the division of the transmitted data by a so-called generator polynom. This modulo two division is done in hardware. The generator is drawn in figure 9. The generator polynom is according the CCITT recommendations  $\times 15 + \times 12 + \times 5 + 1$ . The remainder of the division is transmitted with the x15 component first, lower bits after that. The registers in fig. preloaded with ones, on the reset pulse from FCS control. The data comes via two ports in the registers, and the contents of the registers can be shifted out to the zero inserter by making the Calc/not FCS line low. The data is valid on the trailing edges of the clock, and is allowed to change on the leading edges. The flipflops of the shiftregister have to be master slave types.

### 3.4 Transmit manager

After the leading flag, an address is transmitted. The tx manager provides the necessary enabling signals to the high level 2 registers involved. Following the address byte, a

control byte is transmitted. To simplify the design the first control bit is transferred to the last address register bit. The registers concerned are simple shift registers and so an enable signal only has to enable a shift operation, in the rhythm of a clock supplied by level 1. If a FRMR frame has to be transmitted, the enable to the shift register lasts as long as necessary (5 bytes extra). After a leading flag, an address and a control byte, the data from level  $\ensuremath{\mathtt{3}}$  is enabled to flow in the case of an information frame. The end of the frame is reported by the frame-end bit register. This frame-end command initiates the tx manager to disable level 3 and the registers of level 2 finishing the current control or FRMR information transmission. Then the tx manager starts the frame check sequence generator, by making the frame end signal high. This FCS generator is fed with all the bits transmitted after the leading flag and this datastream is modulo 2 divided by a polynom. The remainder of the value is then transmitted before the trailing flag. The trailing flag transmission is again initiated by the tx manager which starts the flag generator. The ending of the flag signal is also a signal for the pattern generator to preload the generator, because a frame can be transmitted after the flag. If the Tx manager is ready with the commanded actions, it reports ready in the STATUS TX register to high level 2.

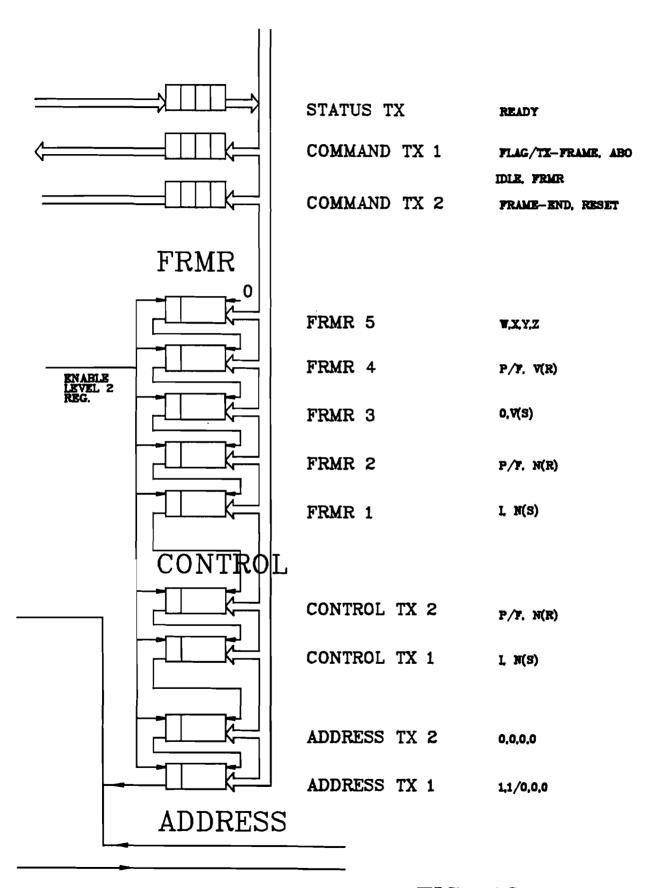

# 3.5 Low level 2 tx/ high level 2 tx communication

See figure 10 for an outline of the registers concerned.

COMMAND:

ACTION:

ABORT

Current transmission must be aborted. Send seven ones. If there is no other command following, send flags. Report ready after the abort sequence is sent.

IDLE

Current transmission must be aborted. Send fifteen ones. IDLE can be continued or a next command or flags can follow. Report ready after the idle signal is completed.

**FLAGS**

Send continuous flags (0111 1110).

Non-TX-FRAME

Send a flag sequence 8 bits

Send an address 8 bits from high

level 2

Send a control byte 8 bits from high

level 2

Enable the DMA controller to deliver data from level 3 and the host. Wait until the

FRAME-END signal.

FRAME-END Send the FCS 16 bits Send a flag 8 bits

> If there is another Non-TX-FRAME send the next frame. Otherwise transmit flags, or idle, or abort. Report the finishing of a

frame by "ready".

FRMR & Non-

TX-FRAME Send flag 8 bits Send address 8 bits

Send control 8 bits Send FRMR information 24 bits 8 bits Send FCS 8 bits

Send flag

RESET Start from scratch. Everything is reset as

if a power-up has occurred.

#### Support:

Automatic zero insertion in all data sequences between an opening and a trailing flag. This is done by the zero inserter unit

abort and idle generation. The pattern Combined flag, generator which makes this sequences is located after the zero inserter because this patterns are not allowed to be disturbed by zeros. These patterns have to be unique.

FCS generator for generating the error detecting code. All bits between the two enclosing flags of a frame is fed through this unit. After the last bit of a frame the contents of the generator is sent before the closing flag.

Address byte, delivered by high level 2 in two 4 bits shift registers.

Control byte, delivered by high level 2 in two 4 bits shift

registers. These registers are connected to the address the registers. In case of shifting the data out, the control data byte goes via the address registers to the low level 2 transmitter.

FRMR registers, containing the frame reject information. These register are connected to the control byte register. The FRMR information is transmitted by shifting via the address and control registers.

Tx-manager for the data flow control and the execution of level 2 high commands. This manager selects the data sources, and starts the different low level 2 machines.

## 3.6 Initialization

The low level 2 transmitter is reset by power up, and can be software reset by the reset register in the COMMAND TX 2 register. After the power-up reset or software reset simply the FLAG command has to be given to start the logical connection to the DCE by transmitting flags. The rest of the link set-up and so on can be directed by the high level 2 transmitter.

FIG. 10

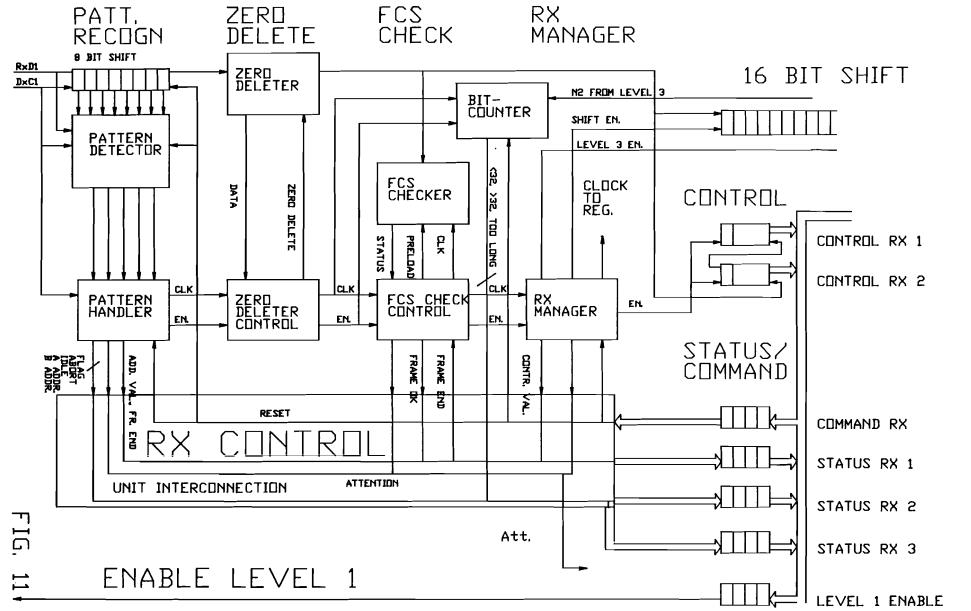

# 4 Low level 2 receiver

The low level receiver handles the standard envelop of packets and supervisory or unnumbered information. Low level 2 supplies high level 2 with all the needed standard information for the link-control. The frames are arriving from the level 1 receiver, and partly go into level 3, the DMA controller, and the high level 2 controller. The data manipulation part and the controlling part of the finite state machines are separated as can be seen in figure 11. The other parts of the low level 2 receiver are an 8 bit shift register on the front end and a 16 bit shift register on the border of level 2 and 3. The 8 bits shift register prevents the trailing flag of a frame from going into the zero deleter and the frame check sequence checker. The 16 bits shift register captures the 16 bits of the frame check sequence before level 3 gets this information. The reason for this "delay registers" is that only when the trailing flag is fully received, the preceding 8 bits can be said to be the flag and the 16 bits before these, the frame check sequence.

A report by J.M.H.M. van Kessel describes the functional tests with TDU of the low level receiver.

High level 2 can tell the low level receiver not to send any data by giving a busy signal via the command rx register.

# Briefly all low level 2 receiver functions:

- Detect a flag (0111 1110) and signal the high level 2 controller.

- Detect and decode A/B address and deliver this to high level 2.

- Catch the control byte in a register and give this to the high level 2 microcontroller.

- Supply a valid signal for the address and control information bytes.

- Support the analysis of the frame check sequence by a 8 bit delay line. This prevents the trailing flag going into the FCS checker.

- Frevent that the frame check sequence goes into level 3. This is done by a 16 bit delay line.

- Check the frame check sequence and signal the correctness of the data to high level 2.

- Give a Frame end signal to the microcontroller.

- Detect and signal an IDLE situation.

- Detect and signal an ABORT situation.

- Delete the during transmission from the DCE inserted extra zeros.

- Check the number of bits after the begin flag: <32: send a FRMR frame. >32: OK, for a I-frame.

- = 32 OK, for all frames, in case of an I-frame: signal level 3 the arrival of a zero information field.

>N2 bits. More than the maximum number of bits allowed are counted after the leading flag.

### Signals:

input: DATA, CLOCK from level 1

status from high level 2: busy

output: DATA, CLOCK\*, enable to level 3

control byte to level 2 in 2 registers, four bits wide.

Status to level 2:

A-ADDRESS, B-ADDRESS, ADDRESS-VALID, FLAG, FRAME END, FRAME-OK, CONTROL-VALID, IDLE, ABORT.

FRAME LENGTH:

<32

=32

to long.

### 4.1 Pattern recognition

A frame delivered from level 1 to level 2 has a general form. The frame begins with a flag sequence of 01111110. The

flag synchronizes the receiver to start a standard procedure decomposition of the frame. After that an address is following: 11000000 or 10000000 depending on the destination being a DCE or DTE and the frame being a command or response frame. The beginning of a frame must be signalled by the low level 2 receiver and the address must be recognized, accepted and delivered to the high level 2 receiver. This recognition is quite simple and can be done by a finite state machine, called the pattern recognizer. Two patterns more can occur which are important to be signalized. These patterns are 1111111 (seven ones) and 1111111 11111111 (fifteen ones), called abort and idle. These patterns, once recognized, must be signalled to the high level 2 receiver. Abort means: stop the current frame consuming and start again with flag hunting. Idle indicates a state of non presence of any information on the line. The end of a frame is also recognized and signalled to high level 2 by the pattern recognition unit.

The leading flag is received in the 8 bit shiftregister, and the flag pattern is recognized and reported to high level 2. The shiftregister is clocked by the trailing edge of the clock, and shifted by the leading edge of the clock. The other patterns are also received and recognized in the 8 bit shiftregister, but the main reason for its presence in the design is that it allows us to destroy the leading flag before the data over which a frame check sequence is generated is checked by the frame check sequence checker. The pattern detector enables after the leading flag is clocked out, and an A, B, C or D address is recognized, the zerodeleter and following machines.

The pattern detector receives the data and clock from the level 1 receiver and gives the flag, abort, idle, A or B address, attention, address valid and frame end reports to high level 2. A reset line resets the pattern recognizer to a state in which it goes flag hunting again. After a flag and a non flag bit pattern a next flag generates a frame end signal.

# 4.2 Zero deletion

The zero deletion machine removes the extra zeros inserted by the transmitter. These zeros are inserted to prevent flag or abort imitation of the transmitted data. After every sequence of five ones a zero is inserted to the data stream. The zero deleter controller compares the incoming data with a one and counts until 5 consecutive ones are counted

without a single zero in between. Than a signal goes to the zero deleter to make the next data bit one. The controller itself skips one clock cycle and so deletes the zero following the 5 ones. Because the zero deletion only works with data without the flag enclosure, the flag is not disturbed by this unit. The unit only works if a flag is recognized by the pattern recognizer and is followed by an address. The zerodeleter gives the enable line unchanged to the FCS check control. The data and clock lines are influenced as described above.

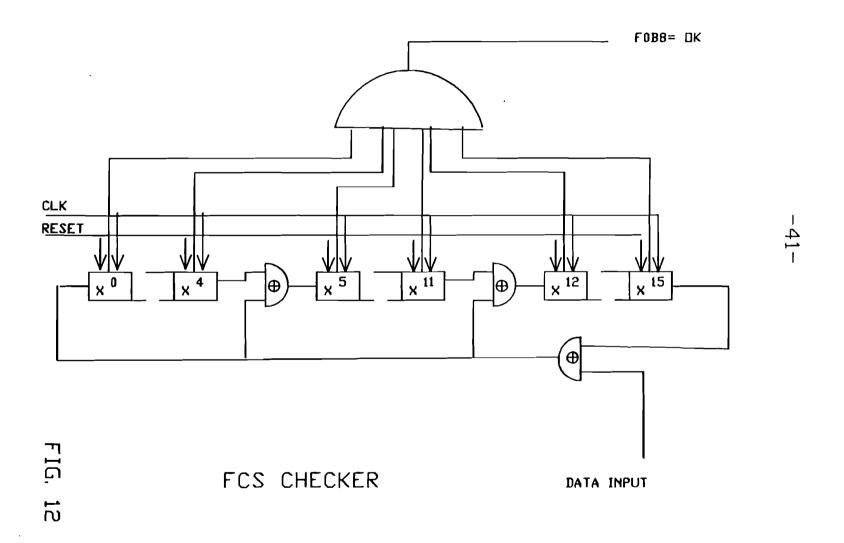

### 4.3 FCS checking

After the data, a 16 bit long error detecting code is added. This so-called frame check sequence is checked on being correct in the frame check sequence checker. The correctness is told to high level 2 via the rx status registers. The FCS check control starts if the enable line goes high with the preload of the FCS checker with ones and supplying the clock to the checker. The Rx manager is supplied with clock and enable, as is the Bit counter. The FCS checker is drawn in figure 12. The reset from the FCS check control preloads the unit with ones and the clock and data input perform the modulo 2 division as described in chapter 3. The remainder of this division is continuously monitorred and results in a high status signal if the remainder is FOB8. The FCS check control samples this status and makes a frame ok report to the STATUS RX 1 register, on the reception of a leading edge of the frame end signal. The frame end signal comes from the pattern handler. An attention signal for the high level 2 receiver is generated and set in a high level 2 register. The detection of an error in the FCS detects all single bit errors, all double bit errors, all even number of errors, all bursts =< 16 bits, 99.997% of the 17 bits bursts and 99.998% of the bursts >= 18 bits. This is only detection! the correction of an error is done by retransmission, or link reset. The FCS checking by the modulo 2 division is according the polynom x15 + x12 + x5 + 1, as used in the FCS generator (see chapter 3).

#### 4.4 Bit counter

The bit counter is started by the enable signal and counts the bits between the leading and trailing flag. The reset line resets the counter. The leading edge of the enable line does also. The bit counter counts the frame bits and gives the following signals to high level 2 via the STATUS RX 3

#### register:

- = 32 The frame is 32 bit long between the flags, and so it is a valid frame. In the case of a I frame this fact of being 32 bit long is to be told to level 3 because the I frame contains no data then.

too long

The frame is longer than N1 bits. This N1 value is read in to the counter during initialisation. The frame is invalid then. The N1 value is continuously compared to the current counter value by a comparator. The most used value is 128 octets, 1024 bits.

The bit counter is only using the clock and data information, and does no operations on them.

#### 4.5 Receive manager

After the flag and address bytes there normally follows a control byte. This control byte must be given to the high level 2 part via 2 registers, each 4 bits wide. The flag and address bytes must be removed before this can happen. This is the task of the low level 2 rx manager. This simple state machine delivers enable-signals to the finite different parts of the chip after the zero deletion machine. The machine is started after the leading edge of the enable The 8 bits of the address are deleted by not enabling any registers after the rx manager for the first 8 clock cycles after the leading edge of the enable signal. The B bits of the control word are fed into the STATUS RX 1 and STATUS RX 2 registers by an enable signal after the address is deleted. The rx manager enables after the 8 bits of the control byte the 16 bit shift register and when this register is full, enables level 3. The received bits are then going to the low level 3 receiver for analysis and to the DMA controller for putting them in the host's memory. When the frame end signal comes from the pattern recognition unit, all lines become disabled. The 16 bit shift register deletes in this way the 16 FCS because the delay of 16 bits before level 3 is reached catches the FCS and something not transferring is deleting it. The reception of the control

byte is reported to high level 2 by generating a control valid report via STATUS RX 1 register and an attention. The signal busy from high level 2 (the reset in the COMMAND RX register) resets the RX manager and the controlling is started again if the pattern recognizer has seen a flag and an address. If the reset line stays high, no flag hunting is started as is described at the part discussing the pattern recognizer. The rx manager distributes clock information to the control shift register, the 16 bit shift register between level 2 and 3 and to level 3.

## 4.6 Low level 2 rx/ high level 2 rx communication

COMMAND: ACTION:

BUSY Stop the data stream to level 3 and start

again with flag hunting. This is more or

less a reset command.

PATTERN RECEIVED:

ACTION:

Flag Set FLAG bit in the STATUS OUT register

and go flag hunting.

Abort Set the ABORT bit in the STATUS OUT

register and go flag hunting.

then set the A\_ADDRESS bit in the STATUS OUT register. Set the ADDRESS-VALID bit in

the STATUS OUT register.

B address If this pattern is following a flag then

set the B-ADDRESS bit in the STATUS OUT register. Set the ADDRESS-VALID bit in the

STATUS OUT register.

addresses are also valid.

Control byte This is the third byte received after the

flag and is fed into a shift register that is accessible from high level 2. If all 8 bits are received the CONTROL-VALID bit is

set in the STATUS OUT register.

Data for level 3 will be send to level 3 via the 16 bit shift register.

Closing flag If the machine is transferring data to level 3 or diagnostic information then a received flag is the closing flag of the frame and the FRAME-END bit is set in the STATUS OUT register. The data transfer is then stopped.

FCS

After stopping the data transfer the FCS code is catched in the 16 bit shift register. The FCS code is checked in the FCS checker. This FCS checker is then read, and the bit "FCS-OK" is then set.

<32 bit A bit sequence consisting of less than 32 bits is invalid and must be reported to high level 2</p>

=32 bit A bit sequence of 32 bits is required for several frames, so this must also be reported.

too long

If a frame bit sequence is longer than N2 bits, the frame is invalid and this must be signalled also.

After the closing flag an attention signal is generated for High Level 2 if the status FCS-OK is set (or left zero if an error occurred).

#### Support:

Automatic zero insertion from all data sequences between an opening and a trailing flag. This is done by the zero deleter unit.

Combined flag, abort, idle A and B address recognition, done by the pattern recognizer. Automatic flag removing. The unit is positioned before the zero deleter because after the zerodeleter, the possibility of flag imitation by the data received arises.

FCS checker for checking the error detecting code. All bits between the two enclosing flags of a frame are fed through

this unit. After the trailing flag, the remaining code in the checker is an acceptance of the frame or not.

Control byte register, for shifting in the control byte received.

$\ensuremath{\mathsf{Rx}}$  manager for enabling the registers and delivering several signals

A 16 bit shift register between level 2 and level 3.

A bit counter for the several frame lengths, and the maximum frame length checking.

#### 4.7 Low level 2 rx initialization

The only action needed for high level 2 is the resetting of the low level 2 receiver. This is done by making the reset bit in the COMMAND RX register high. All the further initialisation is done by the low level 2 receiver itself. The reset bit has to be made low again by high level 2. The only further needed information is delivered by level 3, namely the N1 value for the bit counter. High level 2 can interrupt the receiver by making the reset bit high for as long as the high level 2 receiver is busy. The link set—up and so on is a task of high level 2. Reception of flags is reported via STATUS RX 2 and is a signal for high level 2 that the logical link is possible.

FIG. 13

## 5 High level 2

Level 2 offers to level 3 the logical connection between DCE and DTE. The link is set up and maintained by level 2. For level 3, level 2 is transparent. Only in special conditions there is an exchange of information (apart from the normal information necessary for transmitting and receiving level 3 packets). The packets of level 3 are packed and unpacked in such a way that an error free connection between level 3 in the DCE and DTE can be reached. For doing this level 2 has several finite state machines at his disposal. Besides information frames, containing level 3 packets, level 2 can handle several level 2 frames for link set up and disconnection, retransmission, etc.

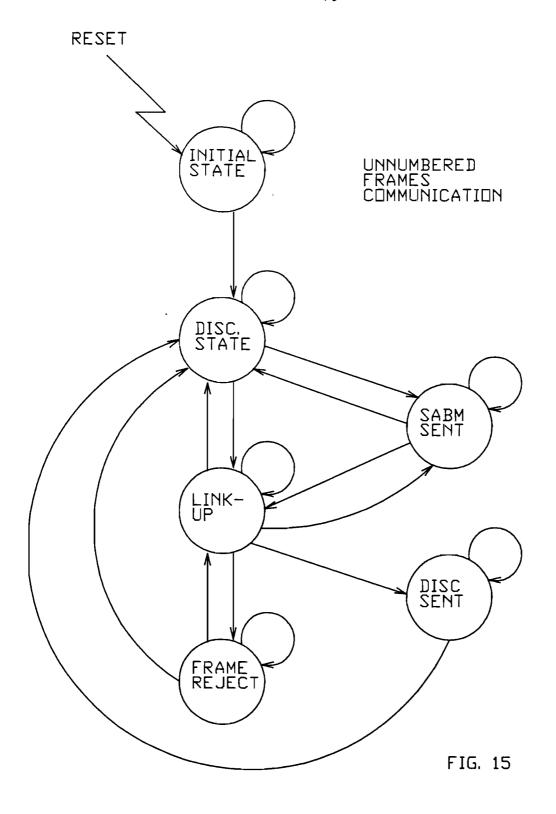

## 5.1 Level 2 states

The operation of level 2 is supervised by the high level 2 controller. This link manager determines whether the link to the network should be established, disconnected or reset, and co-ordinates the operation of the transmitter and receiver. In chapter 6 a hardware description of high level 2 is given.

High level 2 can be in the link-up situation, in the link connect and the link disconnect phase, and in the link-down state. Besides these four states, there is a Reject condition in which level 2 is waiting for a link reset indication from the DCE for instance (the chip being part of a DTE), or a disconnect command. In the link-up situation we can distinguish 5 more states, explained in paragraph 5.4

The link set-up and disconnection is done by so called Unnumbered frames. These frames contain no sequence numbering. The different frame types are:

SABM :Set asynchronous balanced mode (link reset, link set-up).

UA :Unnumbered acknowledge (various acknowledge functions).

DISC :Disconnect (used in case of a wish to disconnect).

DM :Disconnect mode (indicating a state of no connection).

FRMR :Frame reject (not recoverable error detected).

See figure 14 for an complete control byte survey of the different frames.

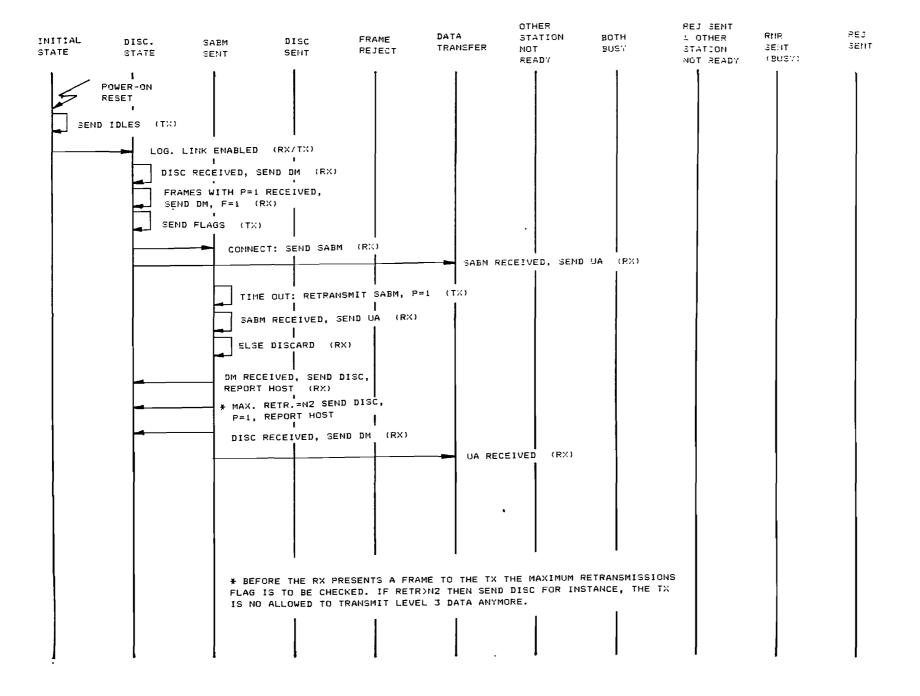

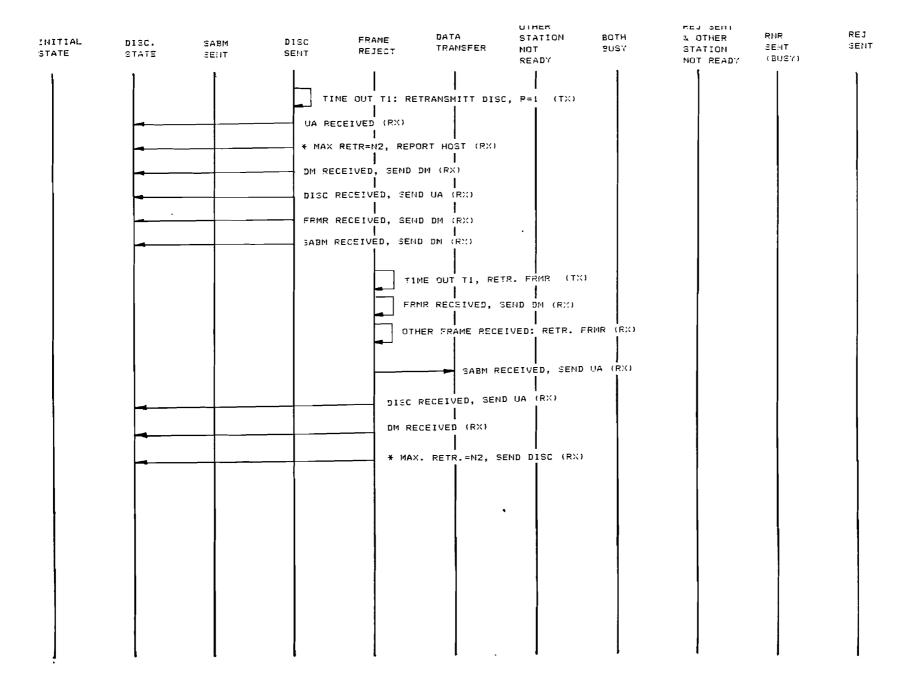

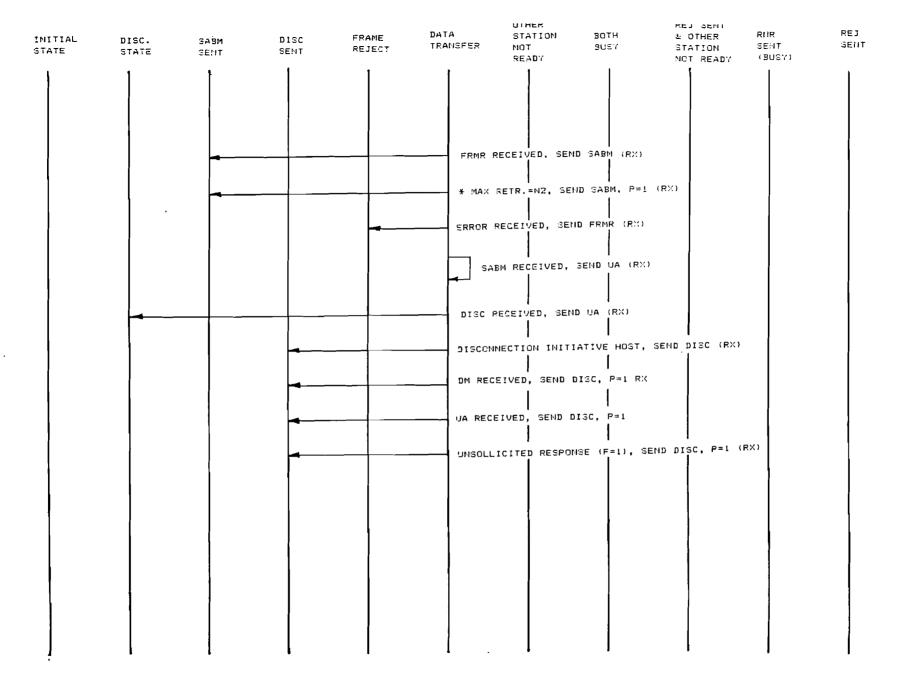

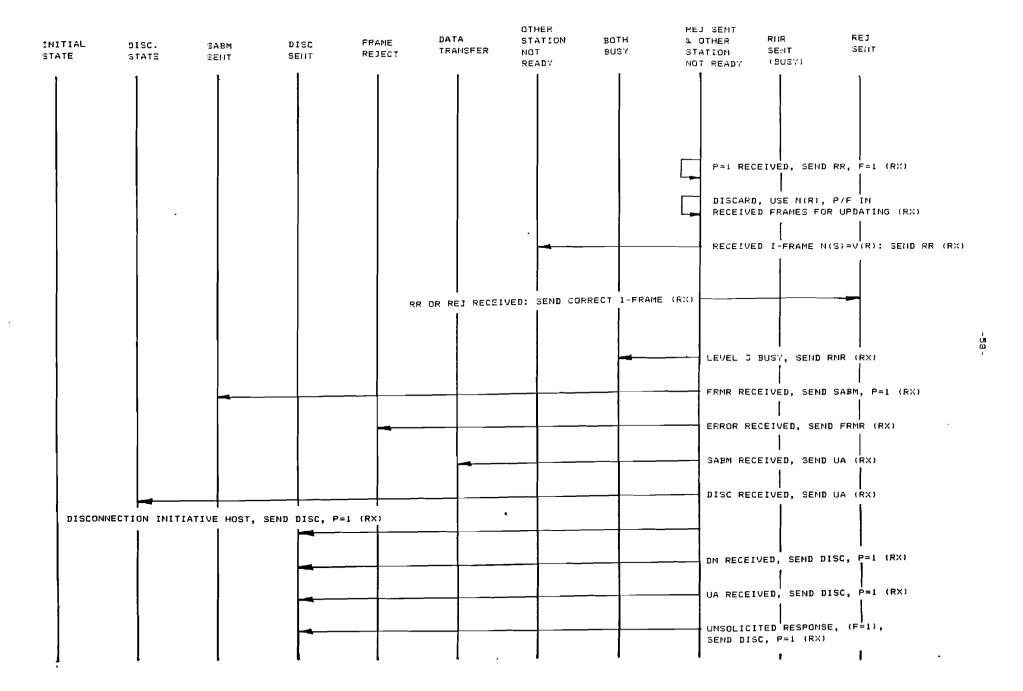

## 5.2 Link set-up

In figure 15 the states important for the link set-up and disconnection are drawn. Starting from a chip reset, the link is in an initial state. In this state idles are transmitted. If the host enables a logical link, the disconnected state is entered. In the disconnected state flags are transmitted, indicating that the chip can accept a logical connection. If a SABM is received, an UA is responsed and the link is up. If the host takes the initiative to connect the station to the network, a SABM is transmitted, and the SABM-sent state is entered. Besides other reactions the solicited frame is an UA, and after the reception of this frame again the link-up state is entered. This is in a short view the normal link set-up. If there are other frames received, then the normal procedure can be possible then. interrupted, and several responses are depending on the received frame. All the responses are in figure 17, and an explanation of this figure is in paragraph 5.5.

#### 5.3 Link disconnection

Link disconnection can be the initiative of the host, and then a DISC command is send out. The DISC-sent state is an intermediate state for waiting for the acceptance of the disconnection, which can be done by several frames. If the other side of the link takes the initiative of disconnection, on the reception of a DISC frame an UA is responsed, and the disconnected phase is entered. The other possibilities of entering the DISC-sent state are in figure 17.

If a FRMR is received, the link is reset by transmission of a SABM. The normal procedure as described in paragraph 5.2 is then followed. In case of a not recoverable error, the chip sends a FRMR and goes to the frame-reject-condition. On the arrival of a SABM the link is reset.

In all states there are several other unnumbered frames both commands and responses possible, but the here mentioned are the most likely. Other frames can result in other state transfers.

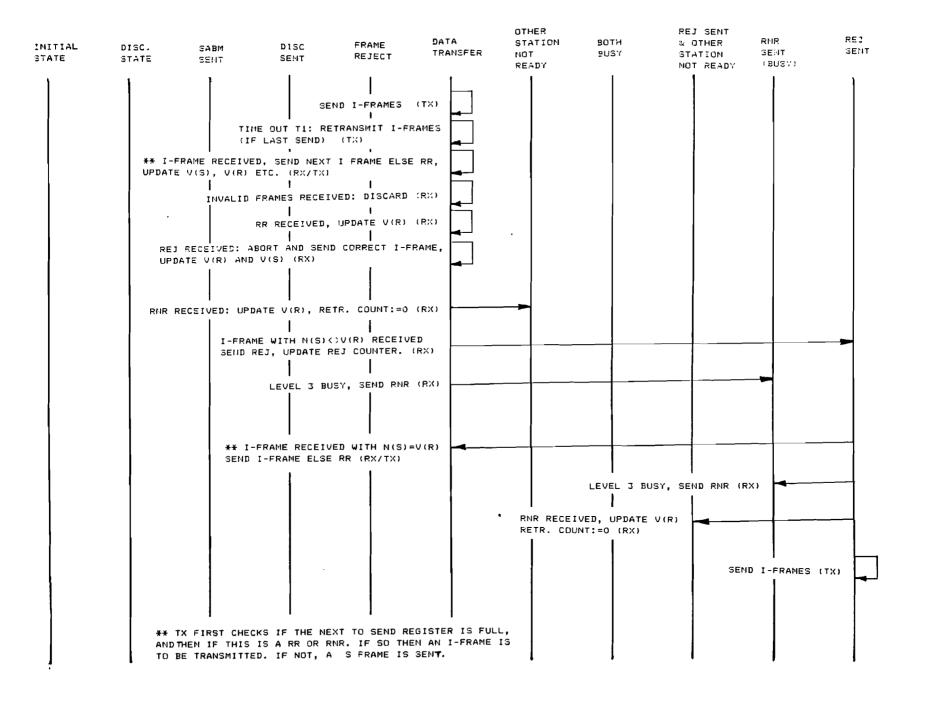

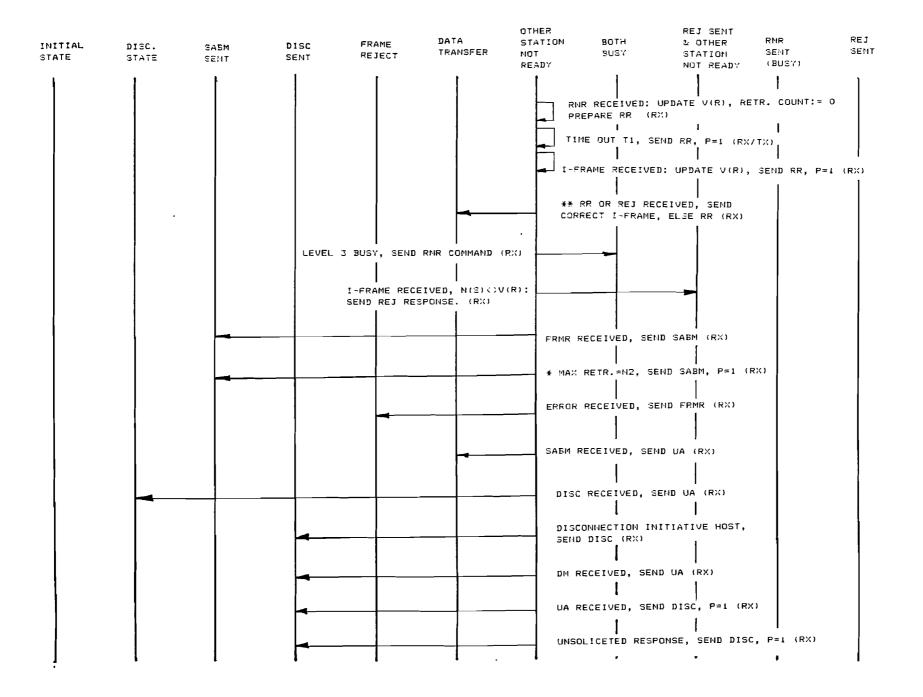

## 5.4 Link-up state

In the link-up state there are four different frames possible. First of all the frame used for data transport:

Besides I-frames, there are frames to maintain the right behaviour of the link. The so-called supervisory frames are:

RR :Receiver ready (indicating a possibility to receive I-frames).

RNR :Receiver not ready (the receiver can not accept I-frames).

REJ :Reject (An out of sequence I-frame is received).

See figure 16 for the control byte contents of these frames.

I-frames, containing level 3 information, have a sequence number. The sequence of this frames is guarded by the level 2 control end maintained with supervisory frames. The S-frames are for indicating a not ready situation, a ready situation and the rejection of out of sequence I-frames. These frames contain a sequence number of the next expected I-frame. The supervisory frames are important in the link-up state. An unnumbered frame is always overruling a supervisory frame.

Inside the link-up state we can distinguish several states. The data transfer state is the state in which both transmission and reception of level 3 frames (I-frames) can occur. We enter in this state after the link set-up or reset. From this state a jump to the other station not ready situation is possible in case of the reception of a RNR frame. No I-frames are transmitted then, but incoming I-frames are accepted. The other station can handle its problems then, until it is able to receive and handle I-frames again. This is signalled by a RR or REJ frame.

If out of sequence frames are received, a REJ is sent, and no incoming I-frames are accepted as long as the right frame is not received. If level 3 signals a busy condition, a RNR is sent out and the RNR sent state is entered. Now incoming I-frames are not handled, and not transferred to level 3. Besides this data transfer state, RNR sent state, other station not ready state, and REJ sent state there are two other states, consisting of a mixture of the preceding states. These states are: the REJ-sent & other station not ready state, and the both stations busy state.

Besides the normal responses to a state change, there are in all states several responses possible, and state changing if required. All these responses to different situations and the initiatives requested are done by the high level 2 microprogrammable processor. A transmitter and receiver process work together, with bus interleaving. Even parts of the controller (for instance the pipeline registers) are shared by the two processes.

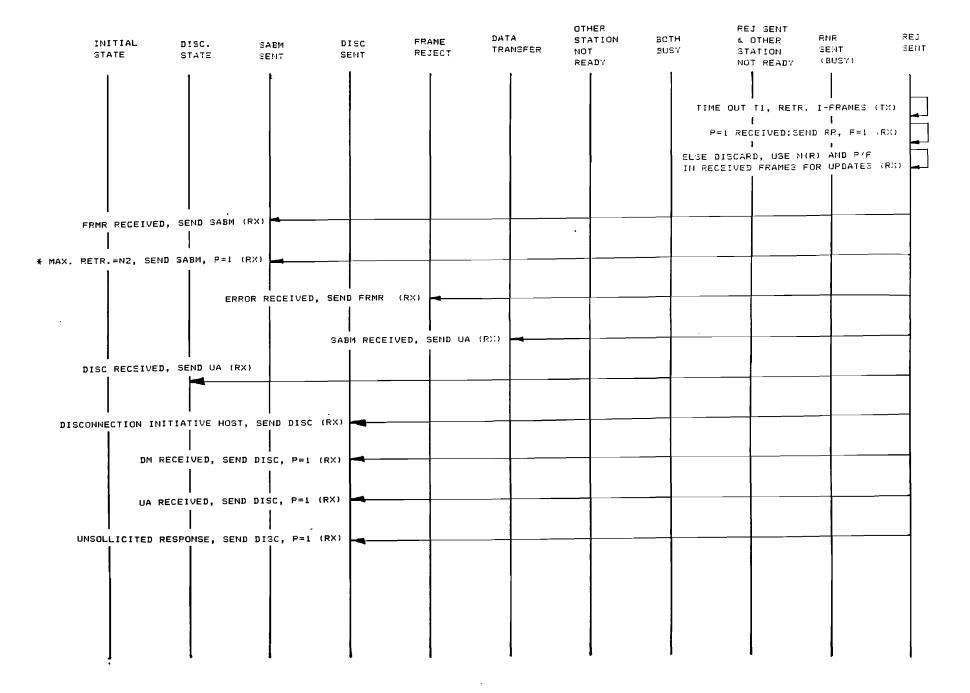

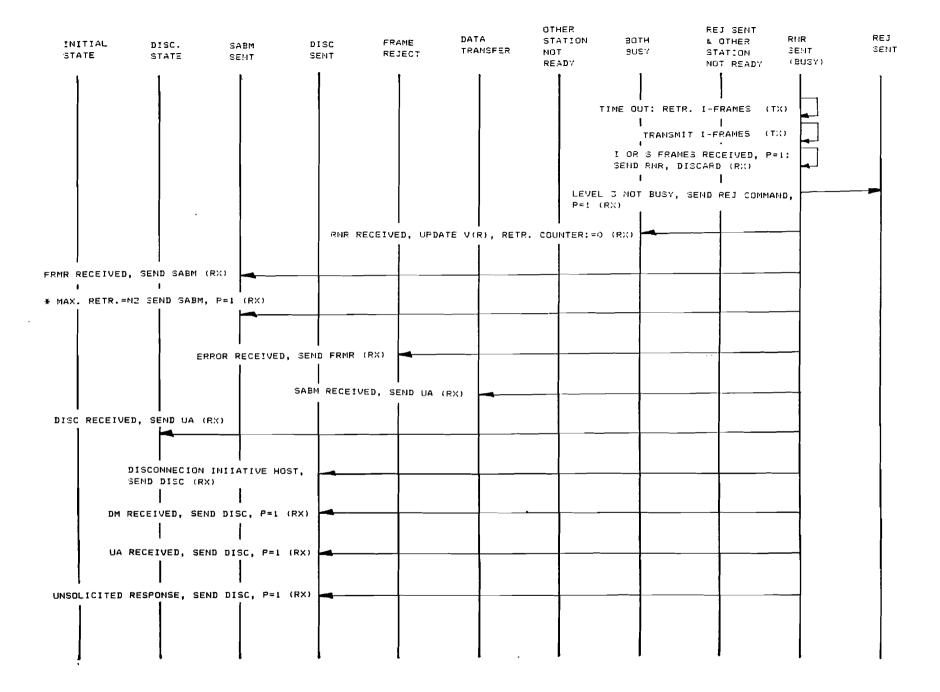

#### 5.5 State summary

As mentioned before, in figure 17 all state changes are drawn. Not all high level 2 actions are with the comments near the arrows, because of the complexity and number of these actions. For the same reason no paragraph numbers of the X.25 recommandation are added.

In the horizontal direction the states are put in the form of lines, and the arrows between these lines represent the state changes with a short reason and a short description of the action. A Rx or Tx addition indicates an action primarly of the receiver or the transmitter.

In chapter 6 the receiver and transmitter functions are described and their cooperation. The stars in the drawing are indicating difficulties in the receiver/transmitter actions. A Single star indicates the situation that N2 retransmissions took place. The retransmission counter update is a transmitter task. The link reset in case of an excess of retransmissions is a receiver task. The solution to this problem is to make the receiver check the retransmission counter before preparing a frame in the next-to-send-1 & 2 registers. The receiver tells in the rest of the state transfers the receiver what to transmit. The transmitter simply transmits receiver frames or if these are not present I-frames. This only if it is allowed. If transmission is

allowed the transmitter retransmits I-frames, else, if no transmission is allowed, only the U and S frames from the receiver. The high level 2 working is in the next chapter described.

The two stars indicate a situation that the transmitter has to make a choice. He is allowed to transmit I-frames, but if they are not available, a RR or RNR as commanded by the receiver must be transmitted. This is a deflection of the general rule of the transmitter only carrying out the receiver commands. The solution to this is to let the Tx check the next-to-send control byte first if it is a RNR or a RR, before transmitting I-frames. In case of a RNR or a RR the I-frame is transmitted, else the frame of the receiver is chosen for transmission.

#### **TABLE 3/X.25**

#### Commands and responses

1 2 3 4 5 6 7 8

| Format                  | Commands                                                |                 | Responses                                                |     | Encoding |       |             |                   |   |                      |   |  |

|-------------------------|---------------------------------------------------------|-----------------|----------------------------------------------------------|-----|----------|-------|-------------|-------------------|---|----------------------|---|--|

| Information<br>transfer | I (informa                                              | ation)          |                                                          | 0   |          | N(S)  |             | P                 |   | N(R)                 |   |  |

| Supervisory             | RR (receive ready) RNR (receive not ready) REJ (reject) | RR<br>RNR<br>y) | (receive<br>ready)<br>(receive<br>not ready)<br>(reject) | 1 1 | 0        | 0 1 0 | 0<br>0<br>1 | P/F<br>P/F<br>P/F |   | N(R)<br>N(R)<br>N(R) |   |  |

| Unnumbered              | SARM (set<br>asynchro<br>response                       |                 | (disconnected mode)                                      | 1   | 1        | 1     | 1           | ЖF                | 0 | 0                    | 0 |  |

|                         | SABM (set<br>asynchro<br>balanced                       |                 |                                                          | 1   | 1        | 1     | 1           | P                 | 1 | 0                    | 0 |  |

|                         | DISC (disconne                                          | ect)            |                                                          | 1   | 1        | 0     | 0           | P                 | 0 | 1                    | 0 |  |

|                         |                                                         | UA              | (unnumbered<br>acknowledge-<br>ment)                     | 1   | 1        | 0     | 0           | F                 | 1 | 1                    | 0 |  |

|                         |                                                         | CMDF            | reject)                                                  | 1   | 1        | 1     | 0           | F                 | 0 | 0                    | 1 |  |

Note 1 - The need for, and use of, additional commands and responses are for further study.

Note 2 - DTEs do not have to implement both SARM and SABM; furthermore DM and SABM need not be used if SARM only is used.

# HDLC-TABLE

| FRAMES      | DIRECTION  | ADDRESS |

|-------------|------------|---------|

| COMMANDS    | DCE — DTE  | A       |

| COMMANDS    | DTE — DCE  | В       |

| RESPONSES   | DTE — DCE  | A       |

| VE31,0142E2 | DCE —— DTE | В       |

N85 (

# ADDRESS-TABLE

FIG. 16

#### 6 High level 2 construction

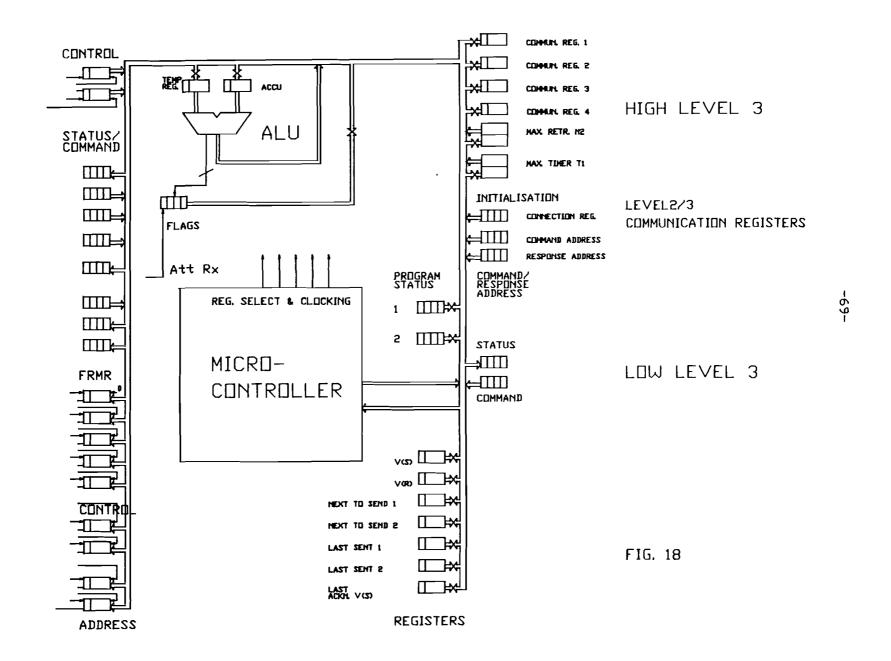

To support the different functions of the receiver there are a 4 bit wide bus and an ALU shared with the transmitter part of high level 2. The bus is separated in  $\ensuremath{\mathfrak{I}}$  bit data and a single bitline for the microprogrammable controller only. The data is so organized that always a 3 bit number and a single information bit are together in the different frames, so a 4 bit bus is a natural choice. The different registers in the high level 2 receiver are mostly also accessible by the transmitter. Figure 18 shows the high level 2 hardware. On the left side the low level 2 machines and communication registers, and on the right side low and high level bus interleaving mechanism assures that no collision can occur. After every sequence of microinstructions, the last microinstruction switches the microcontroller to a part of the transmitter program, pointed to by the tx-program count register. This register can be found in the microcontroller. See chapter 7. The other registers shown in figure 18 are registers used for the program status and flow control of the frames.

#### 6.1 High level 2 receiver

The receiver must analyse the received control byte of a frame and the received address information. This includes the different valid signals, delivered by the low level 2 receiver. Depending on the information delivered by this process action must be taken. This actions are described in the X.25 recommendation of the CCITT.

The functions of the receiver are:

- First of all: check the validity of the frame. If this is not OK, then discard the bits that are received.

- Maintain the sequence of level 3 packets.

- Signal to level 3 the receipt of level 2 diagnostic information (FRMR frame). The FRMR frame contains an indication of the detected error in a frame.

- Handle a BUSY signal from level 3. A RNR must be transmitted, and no incoming I-frames can be accepted.

- Handle the frame information as there is PACKET\_END and PACKET\_VALID, and deliver this to level 3.

- update the information for level 3 concerning the last acknowledged frames, etc.

- Take action on the receipt of an ABORT, IDLE or flag signal from the low level 2 receiver.

- Count the number of REJ frames transmitted. This is an indication of the line quality of the channel to the receiver.

The receiver action in the different states can be read from fig. 17. Every receiver action has an addition "Rx" near the arrow indicating a state change.

## 6.2 High level 2 transmitter

The transmitter is much simpler than the receiver part of high level 2. The transmitter has only to transmit the frames of the receiver which have to be send to the other station, and the I-frames of level 3. All the different responses to the incoming frames are not handled by the transmitter. Only transmit sequence information (V(s)) and Next-packet-to-be-send pointer are updated by the transmitter. Beside this simple actions the only actions are commanded by level 3 or initiated by a counter or timer overflow.

#### Briefly all transmitter functions:

- Check the time-out by means of a max-timer (loaded from level 3). This time-out occurs when no response is received after a maximum time. The timer is started when a frame (command) is transmitted, with a bit set, the so-called P(oll) bit. The timer is reset when, as an answer to the poll, a bit set in a received frame, the so-called F(inal) bit.

- Check the number of retransmissions. There is a maximum-retransmission counter that can be preset

from level 3.

- Transmit on request from level 3 the level 3 packets. This includes the preparation of an address, an control byte and the sending of several signals to the low level 2 transmitter.

- Sending of a FRMR frame if required. For this purpose a shiftregister is accessible from the 4 bit bus.

- Keep the send sequence numbers V(s) and nextpacket-to-transmit up to date, as well as the retransmission counter.

- Send REJ on fault sequence numbers.

- Control the transmission of packets from level 3 by the lines Packet-Request, Packet-Ready and Transmit-packet-end.

- Communicate with level 3 about the last acknowledged packet number, the next packet to send and the maximum number of outstanding packets.

- If necessary transmit an idle or abort by signalling this commands to low level 2.

- Transmit the different control frames.

The transmitter actions can be read from fig. 17. Mainly transmitter actions have the addition "Tx" near the arrows.

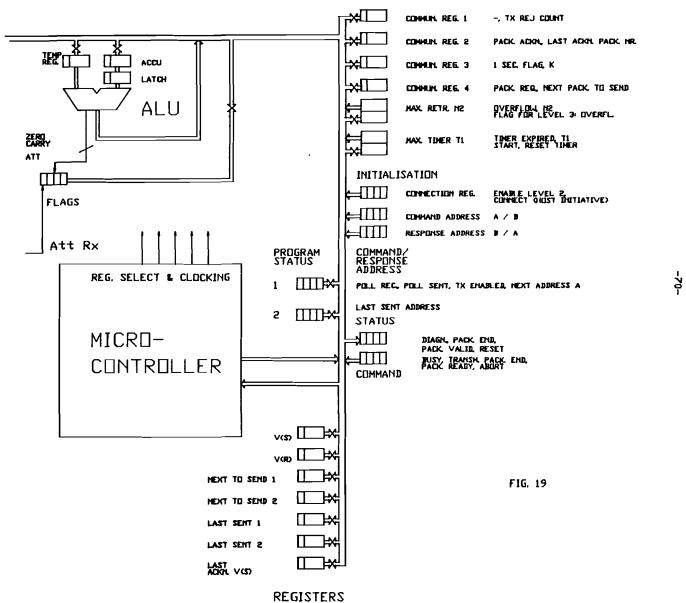

## 6.3 High level 3 communication

Between high level 2 and the high level 3 controller there is an exchange of information. This communication goes via the registers upper right in the drawing 19. Over these registers an attention is generated, if the first bit of the register is set. The bits are reset by level 3. Setting by level 2 is only allowed if first is tested if the bit is reset. In the same way the registers over which the bits are signalling to be filled with information are only allowed to be accessed by level 2 if the bit in the register is reset. Level 3 of course can only read the registers reporting the reject counter value, the last acknowledged packet number and the next packet to send number. As can be read

hereafter, the other registers are only once set in a certain value at the initialisation. Because of the construction of the level 2 and level 3 controllers there is no problem with the timing. The controllers work exactly on the same clock and on the same microcycle timing, so a collision for instance with a processor writing and at the same time the other processor also writing can not occur.

REJ count

3 bit (or 4 bit) countervalue, counting the reject packets transmitted (COMMUN. REG 1)

Pack. ackn/

Last ackn.

pack. nr.

Flag indicating that a packet is acknowledged./ The number of the last acknowledged packet. (COMMUN. REG 2)

1 sec. timer/

A timing flag supplied for level 3 by level 2./ K is the maximum number of outstanding I frames, set at initialisation. Maximum is seven, mostly k is set to 2 (Dutch PTT). (COMMUN. REG 3)

Pack. request/ next pack. to send

A flag indicating that a packet can be transmitted by level 2./ The number of the packet that can be transmitted. (This is the sequence numbering of the packets in the hosts memory). (CDMMUN. REG 4)

Max. retransmissions N2

The maximum number of retransmissions that level 2 is allowed to do before the situation is becoming special. N2 is set at initialisation and is mostly 5 (Dutch PTT). The register is accessible from level 2 and has a parallel register with the actual value of the retransmissions that where necessary up to that moment. There is a maximum overflow flag in this register for level 3 available. This is the reason discussing this register with the level 3 communication and not with the initialisation procedure.

Max. timer T1

The maximum time a packet is allowed not to be acknowledged. The value of T1 is again set at initialisation and can be 2,125 sec. or 200 msec. (Dutch PTT). The register with the maximum timer value has a counter connected to it and this counter can set a flag that can be read by level 2, and by level 3. This is the reason this register is also put in this part of the report and not with the initialisation.

## 6.4 Low level 3 communication

Low level 3 handles the standard assembling and disassembling of the level 3 packets. For doing this a certain synchronisation with the transmitter and receiver of level 2 is necessary. The communication goes via the STATUS and COMMAND register. Over these registers no attention is generated.

STATUS:

Diagn./Pack. end/Pack. valid/ reset (soft)

Diagnostics flag indicates that the data being transferred to level 3 is diagnostic information, the contents of a FRMR frame./ Packet end indicates that the frame end flag of the information frame is received./ Packet valid is the signal that no error has occurred in the transmission and that the packet sequence number is allright./ Reset is a possibility to reset level 2. This is also possible by changing the enable level 2 and start connection bits.

## COMMAND:

Busy/Transmit pack. end/pack. ready/abort

Busy is a command for level 2 to stop the transfer of level 3 info to the level 3 receiver. A RNR frame has to be send./ Transmit packet end is the command to end the transmission of data from level 3. A

FCS code must be transmitted and a closing flag./ Abort is a command to end the current transmission also, by transmitting an abort sequence./ Packet ready is an indication that the requested level 3 packet is ready for transmission.

#### 6.5 Internal level 2 registers

For the controlling of the link several values are necessary to remember. The sequence control and the retransmission are examples of recalling previous used information. Hereafter the registers for storing the used information. The next frame to be send is stored in the Next-to-send registers 1 & 2, and gives the transmitter the frame control word the receiver wants to be transmitted. The transmitter always tries to transmit the receivers frame first, and after that the I-frames, if allowed.

V(s) The sequence number of the next I-frame to be transmitted.

V(r) The sequence number of the next I-frame that is expected to be received.

Last\_ackn.\_V(s) The number of the last I-frame that is acknowledged from the opposite station.

Last\_frame\_sent\_1 The first nibble of the control byte that is sent with the last transmitted frame.

Last\_frame\_sent\_2 The second nibble of the control byte that is sent with the last transmitted frame.

Frame\_to\_send\_1 The first nibble of the control byte of the frame to be send next.

Frame\_to\_send\_2 The second nibble of the control byte of the frame to be send next.

Beside whole nibbles also singular bits are exchanged between receiver and transmitter. For this purpose a PROGRAM STATUS 1 register and a PROGRAM STATUS 2 register are present.

Poll\_received A flag indicating that a poll is received

and thus a final has to be transmitted.

Poll\_send A flag indicating that a poll is send and a final is expected in response to this.

Tx\_enabled A bit, allowing the transmitter to transmit level 3 info.

Last\_address\_sent The last frame was addressed to the command address if this bit is set, else the response address was used. This is used in cooperation with the last sent control byte.

Next\_address The next destination address for the transmitter, when using the next to transmit byte. A one indicates a command, a zero a response

The transmitter is able to test if there is a frame to be transmitted from the receiver by testing the first bit of the next-to-send 1 register. If there is some U or S frame control byte, the first bit is always a one, as can be seen in fig. 14.

#### 6.6 Other level 2 provisions

The transport of data nibbles between the registers in high level 2 is always done via a temporary register or the accu. The accu is a register with a latch for temporary storage in the case of arithmatic operations. For this arithmatic an 4 bit ALU is present and a flag register, both with a port to the 4 bit data bus.

Accumulator Used as stocking area for the result of ALU operations. The accu is 4 bit wide.

Temporary reg. This register is used by register-register transfers, and for temporary information memory for ALU operations.

Arithmatic Logic Unit

The ALU is used for the different logic and arithmatic operations needed in the different programs. The ALU can perform AND, OR, ADD and SUB actions. All modulo 16 (4 bit wide ALU).

Flag register

The flag register contains in sequence: a carry bit, indicating an overflow during the previous ALU operation, a zero bit, indicating a zero result in the accu and an attention bit, indicating that the low level 2 receiver asks for service.

#### 6.7 Low Level 2 communication

The registers communicating with the level 2 receiver are already explained about their contents. The receiver has one command register, and 3 status registers. In the Control\_rx registers the control byte of the received frame is stored. This register Control\_rx\_1 can contain for instance in case of an I\_packet, a zero and the send sequence number N(s). Register Control\_rx\_2 then contains a poll bit (0 or 1) and the receive sequence number N(r).

The register for the status of the transmitter is called Status\_tx. It contains only the ready message of transmitter. The command registers are called Command\_tx\_1 and Command tx 2. Their contents is also explained before. The Address\_tx\_1 register is filled with the A or B address first nibble. This is 1100 or 1000. The Address\_tx\_2 register is always containing zeros. The Control\_tx\_1 register contains the first control nibble, and the Control\_tx\_2 register the second nibble. In the case of an I-frame they contain a zero, and N(s) respectively a poll (0 or 1) and N(r). The FRMR registers 1 to 5 contain in the first two registers the control byte of the rejected frame, in the third register a zero and the current V(s), and in the fourth register a zero if the rejected frame was a and a one if the rejected frame was command a response. After this the fourth register contains the current V(r). The fifth register contains the W,X,Y and Z parameters about the reason of the frame rejection. W is set if the received control field was invalid or not implemented. X is set if the U or S frame had an incorrect length or if the frame contained an information field, which is not permitted with an U or S frame. Bit W must be set in conjunction with this bit. Y indicates a too long information field. Bit Z is set if the receiver control field contained an invalid N(R).

The following five bits in a frame reject are always zero, so the input of this last shift register is connected to zero. All zeros are loaded in this way during the shift operation.

#### 6.8 Initialisation

The initialisation of high level 2 is done by level 3. Level 3 sets the maximum number of outstanding packets (I-frames), k, in comm. reg. 3. The maximum number of retransmissions is also set in a register, as is the maximum timer value  $\ \ \mathsf{T1.}\ \ \mathsf{K}$ is mostly set to 2, N2 at 5 and T1 at 2,125 or 200 msec the maximum depending on the class of operation. N1, framelenght is also set in low level 2. The command address must be initialized, and the response address. These addresses make the level 2 processor act as a DCE or DTE. See fig 14. The last register is the connection register, and is accessed if level 3 is ready with its own initialization. The first bit is the enable level 2 bit and starts the level 2 controller with the initialization and enables the other side of the link to make a call chip. The second bit in the connection register is a connection command and commands the level 2 controller to make a call to the other station. In the state diagram (figure 15) this causes an SABM and a state change to the SABM-sent state. With these actions, the initialization is completed. Low level 2 is than initialized as described. High level 2 only resets in the case of a general reset the V(S) and V(R) to zero and fills the other registers with zeros, and than starts the logical connection if enabled.

enable level 2/ start connection

The enabling flag indicating that level 1 can be enabled to make an electrical connection to the network and that level 2 after its initialisation is allowed to accept a request to make a logical connection./Start connection is a flag indicating that the host via level 3 wants a call set up and that level 2 has to take the initiative to do so.

Command address/ Response address

These registers contain a 4 bit address each. These addresses tell the chip to behave as a DCE or as a DTE, as far as level 2 is concerned. If the command register contains for instance an A address, the response register contains a B address

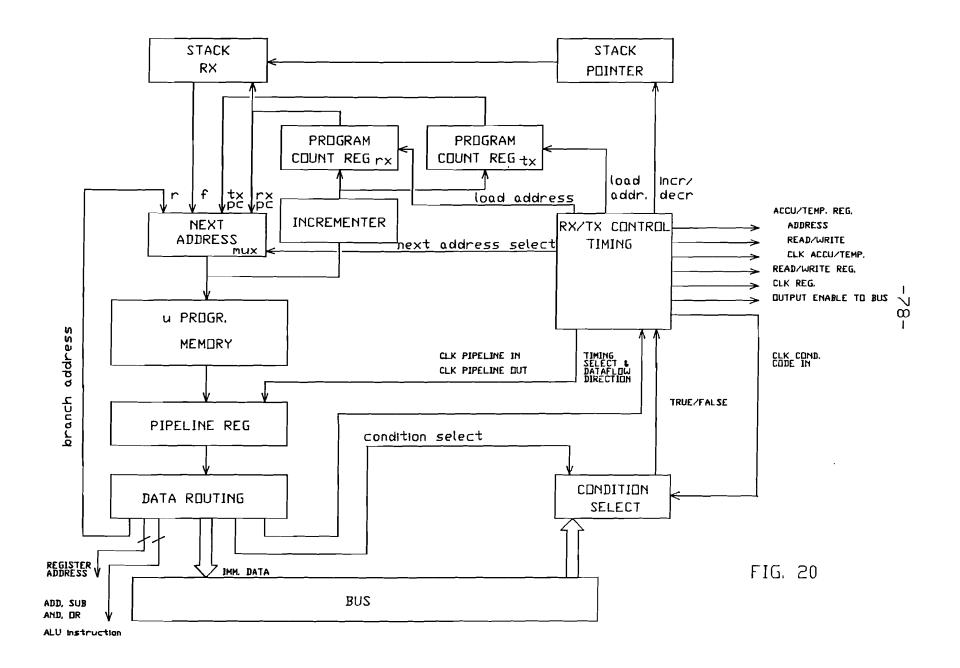

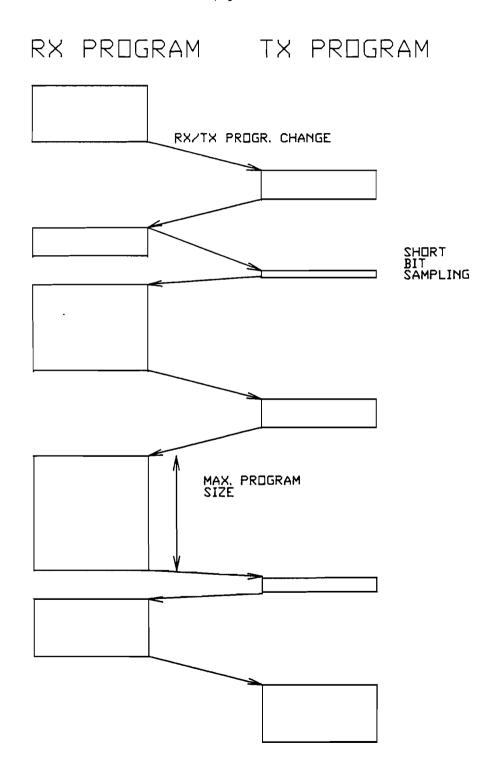

## 7 Microcontroller