# MASTER

Requirements and architecture modeling tool specifying synchronization and communication for implementing concurrent transformations in VLSI

Benders, L.P.M.

Award date: 1988

Link to publication

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

EB 131

5320

Eindhoven University of Technology Department of electrical engineering Digital systems group (EB)

#### REQUIREMENTS AND ARCHITECTURE MODELING TOOL SPECIFYING SYNCHRONIZATION AND COMMUNICATION FOR IMPLEMENTING CONCURRENT TRANSFORMATIONS IN VLSI

Leon Benders

software techniques translated into hardware

August, 1988

Master thesis report. Coach: Prof. ir. M.P.J. Stevens

.

The department of Electrical Engineering of the Eindhoven University of Technology doesn't accept any responsibility regarding the context of student projects and graduation reports.

#### ABSTRACT

In application specific VLSI designs e.g. real-time and complex data transformation applications, it is essential to implement concurrent processes, which access shared data, share resources, communicate with each other and are synchronized to execute their functions. The number of transformations and events is limited and known. But even in this class of problems deadlock and starvation can occur.

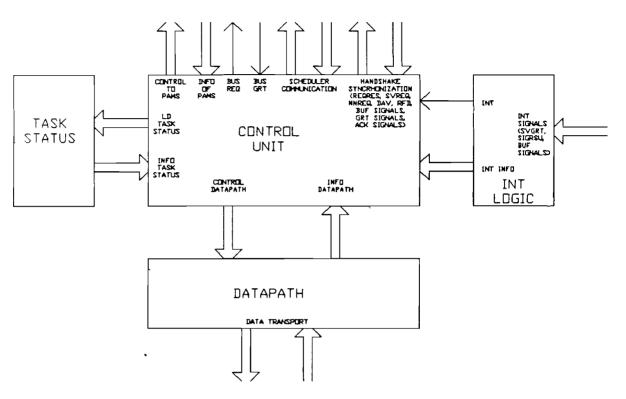

This master thesis report presents a solution for modeling, locating, implementing parallel processes and their synchronization and communication in one VLSI circuit. Only process synchronization, scheduling, mutual exclusion, request/acknowledge synchronization and data communication primitives are required to specify parallel processes in a VLSI design. These primitives based on simplified software techniques are implemented in hardware using architecture modules to execute the control.

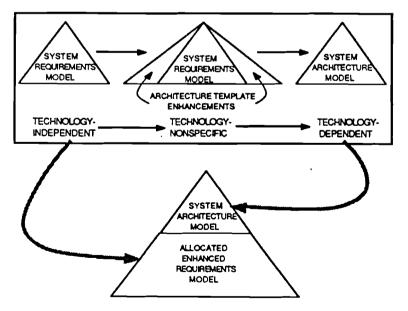

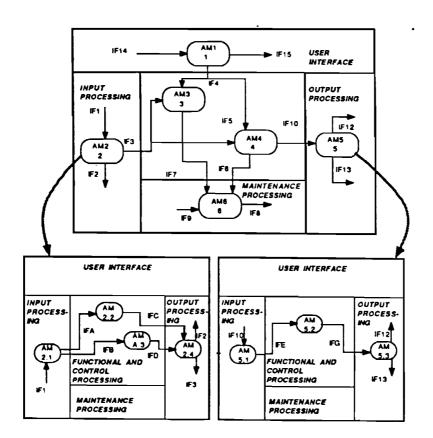

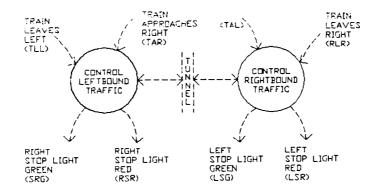

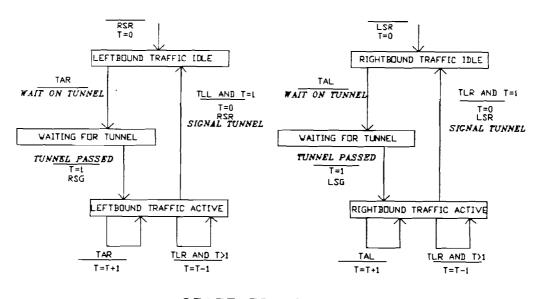

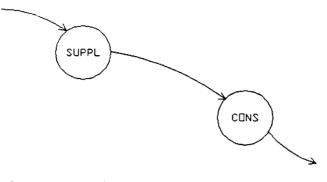

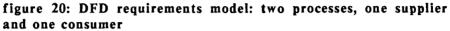

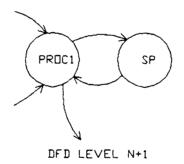

A digital system design starts with a global functional description. The concurrent processes have to be recognized to fullfil that function. A tool consisting of two models (requirements and architecture model) locates these parallel processes focussing on the data flow and transformation's data processing. The function of the digital system is defined and further specified in the requirements model. The transformation's description specifies the data transformation, but also contains the necessary primitives for the process interaction. The method avoids an implementation bias and sequentialization of processes. The description should prevent deadlock and starvation, but this can't be guaranteed.

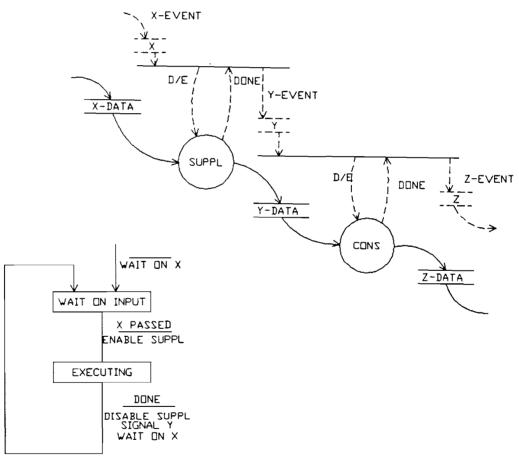

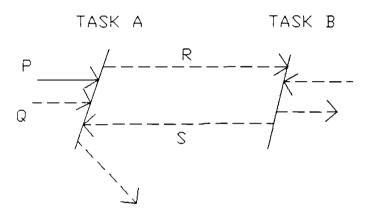

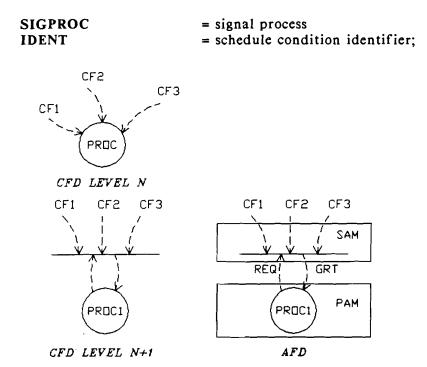

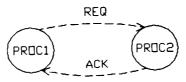

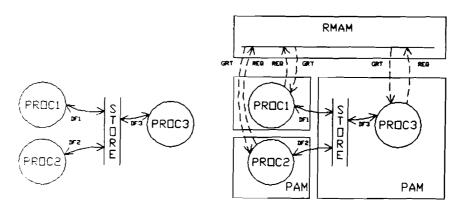

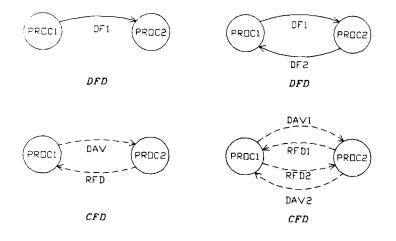

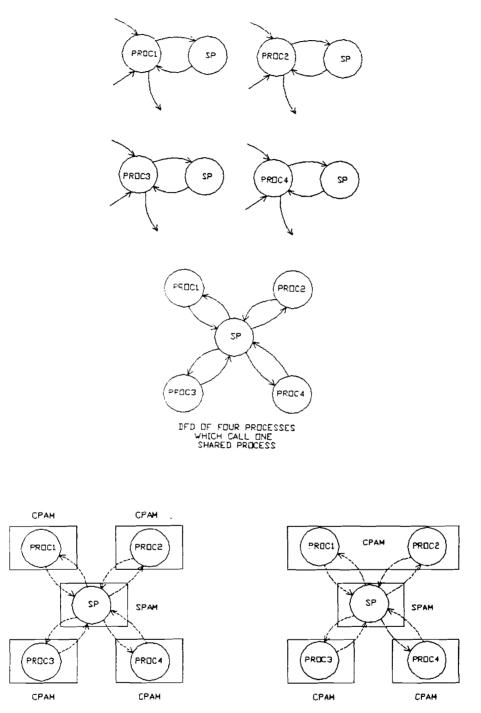

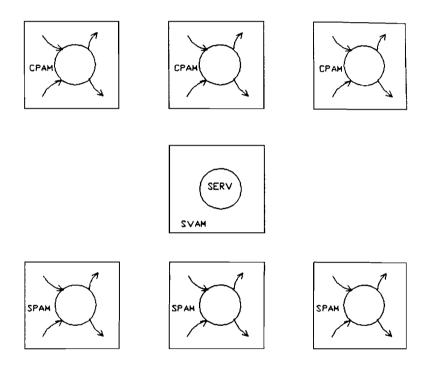

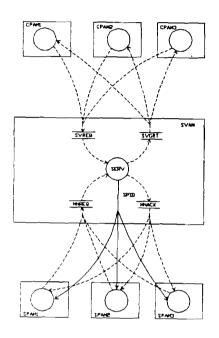

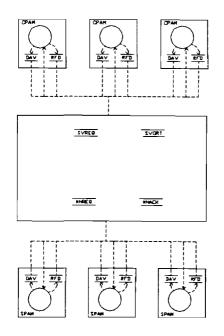

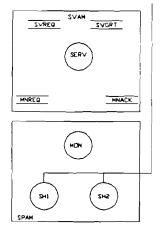

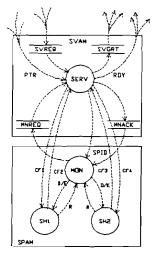

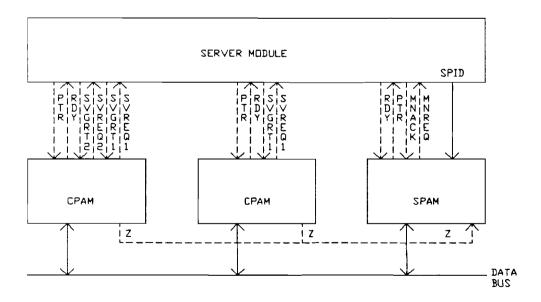

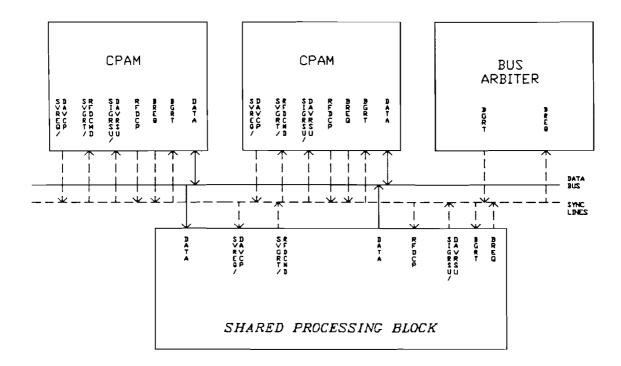

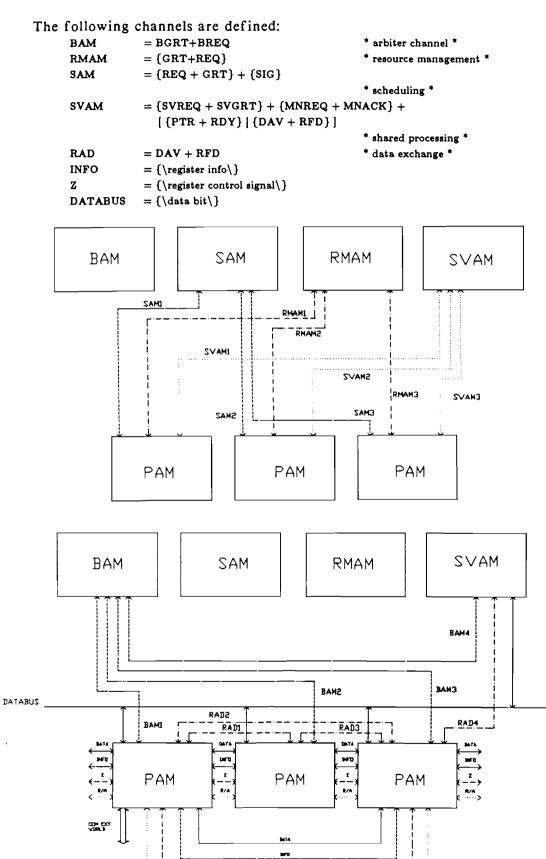

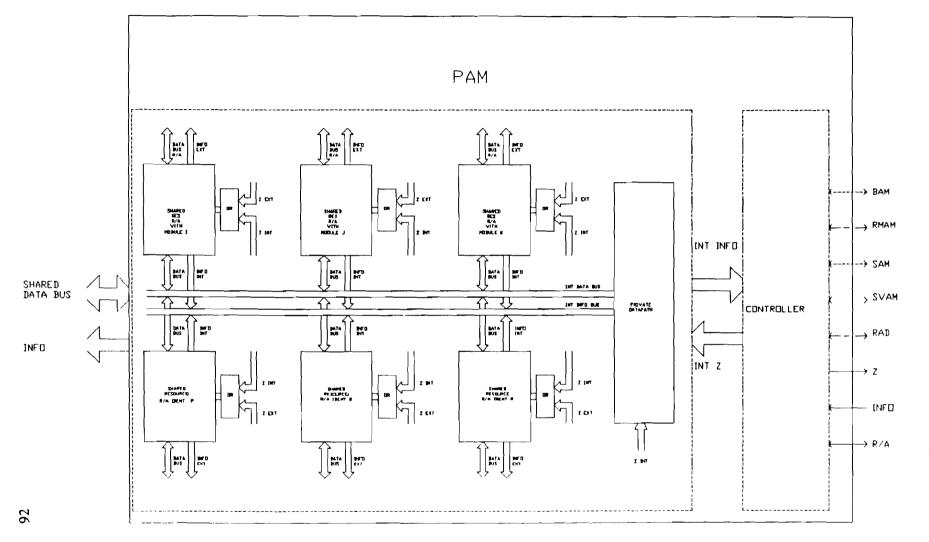

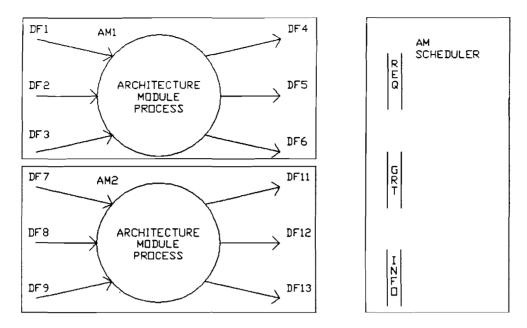

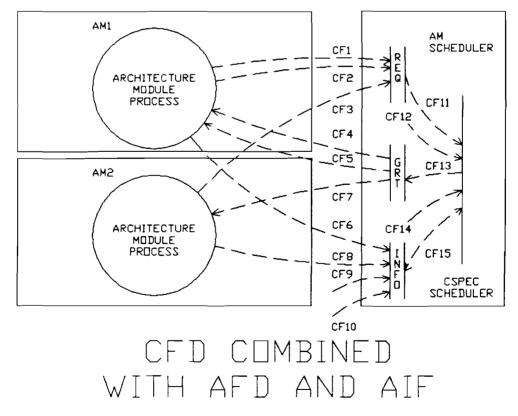

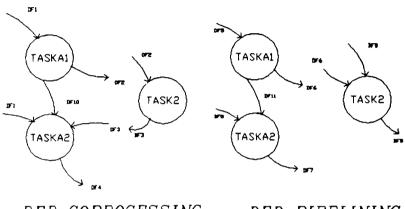

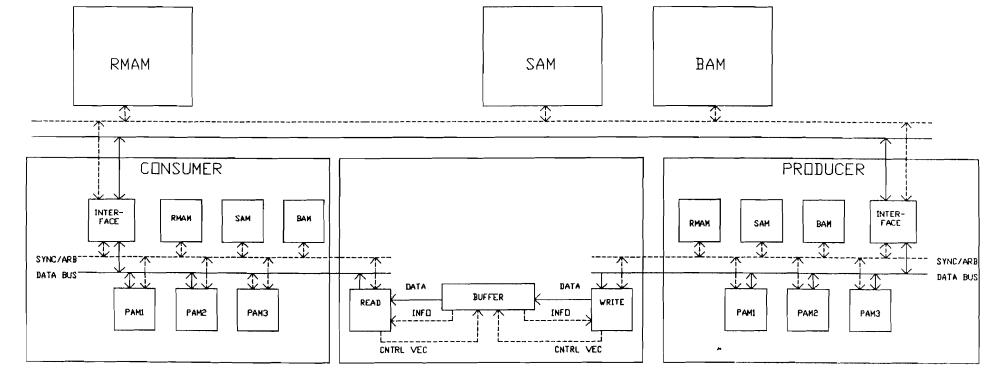

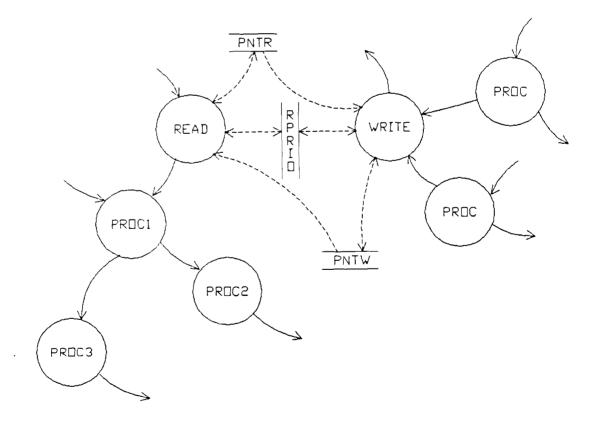

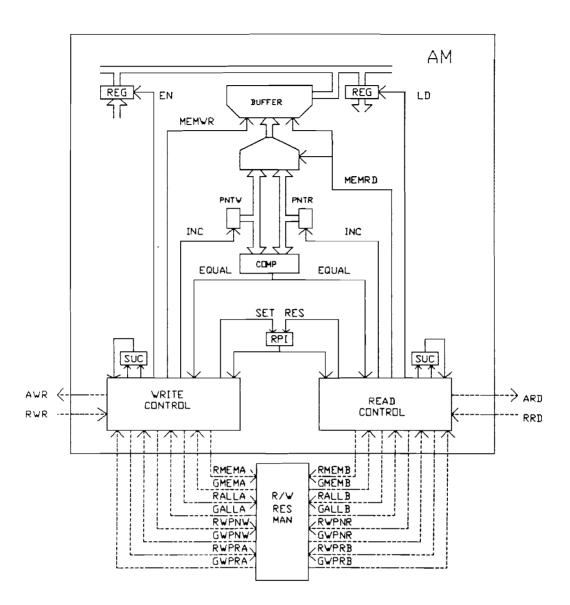

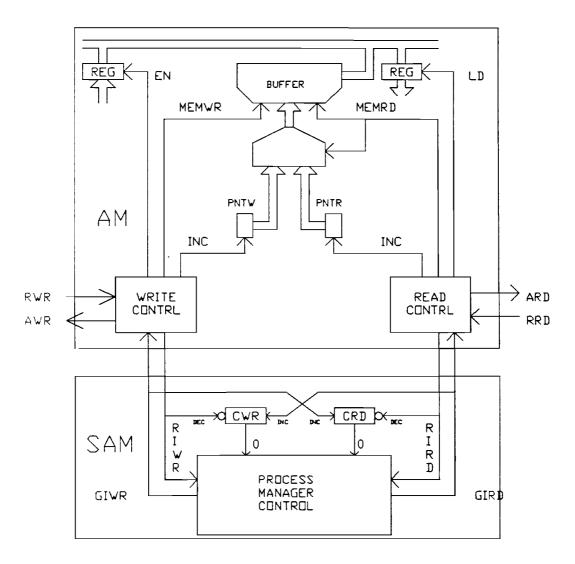

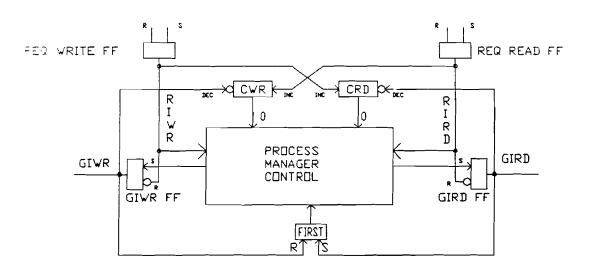

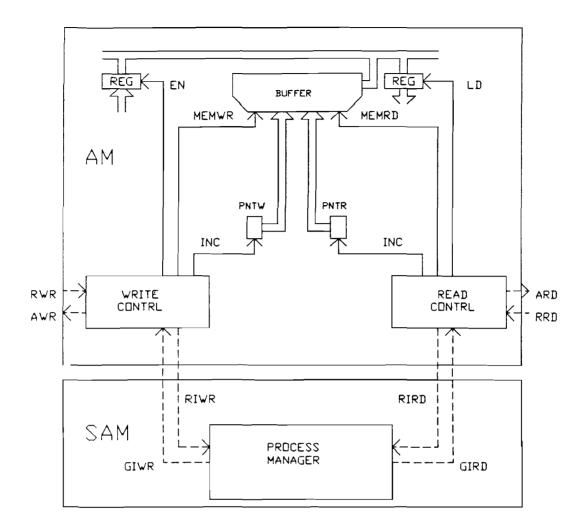

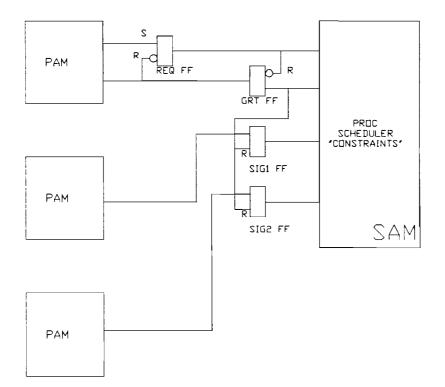

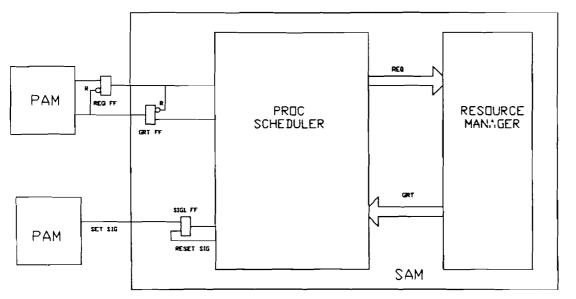

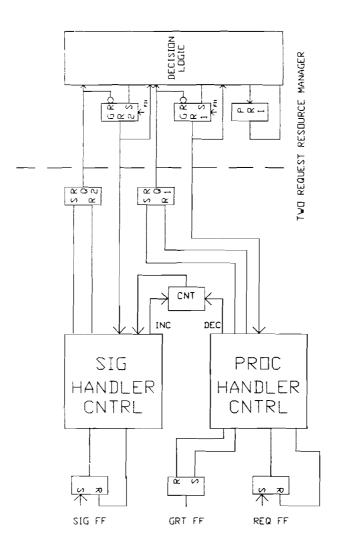

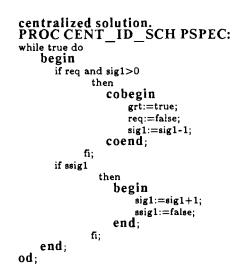

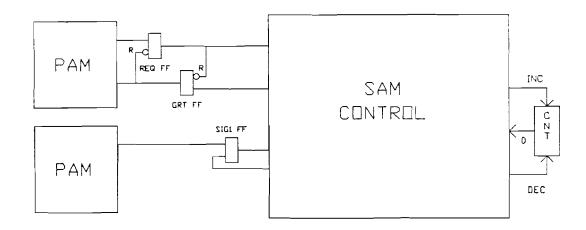

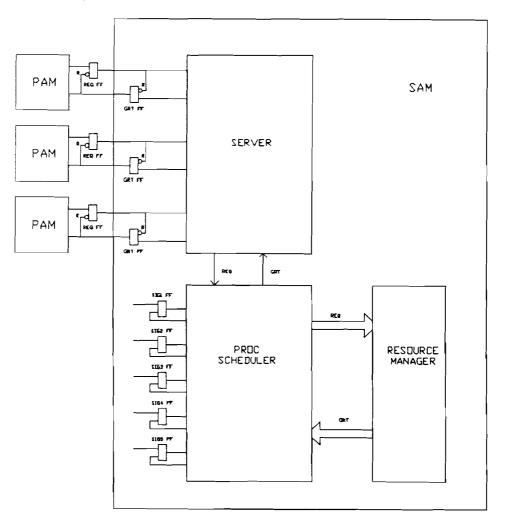

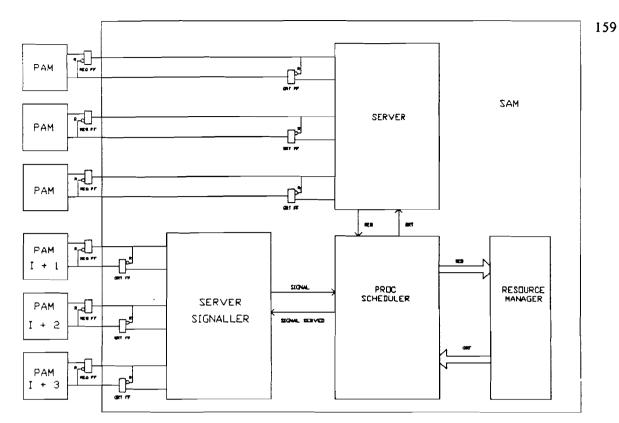

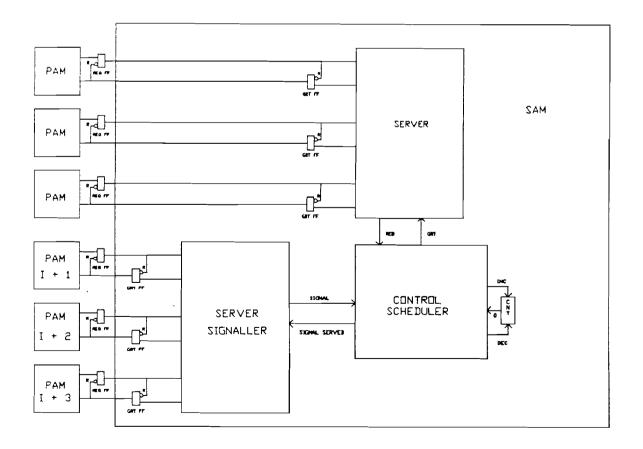

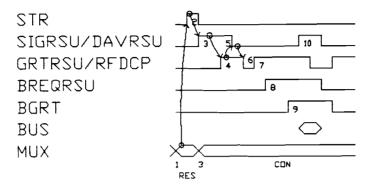

In the next phase all transformations are allocated to parallel operating architecture modules in the architecture model. The allocation may sequence the transformations, when the timing requirements allow this. It redefines process descriptions especially the required synchronization and mutual exclusion and introduces new transformations to implement the allocation. Data transformations are allocated to processing architecture modules (PAM); the control transformations for synchronization, mutual exclusion to resource management (RMAM) and to scheduling architecture modules (SAM). To simplify implementation and to avoid too much synchronization overhead process knowledge may be implemented in these modules.

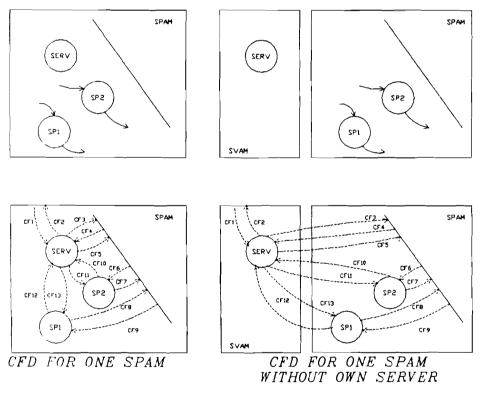

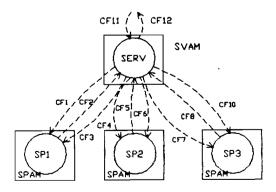

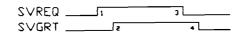

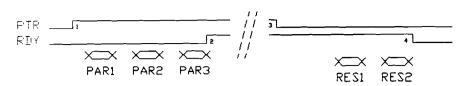

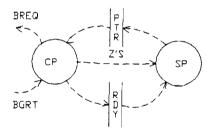

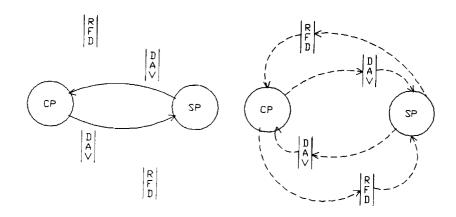

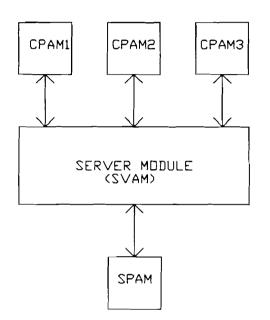

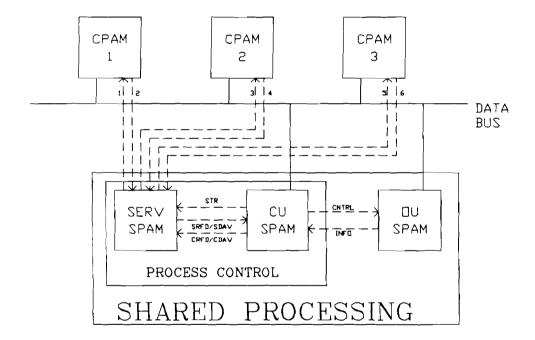

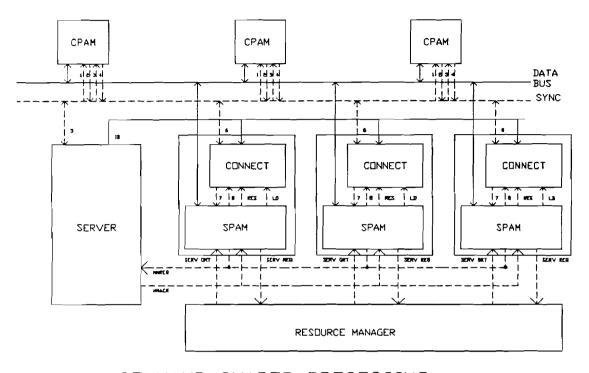

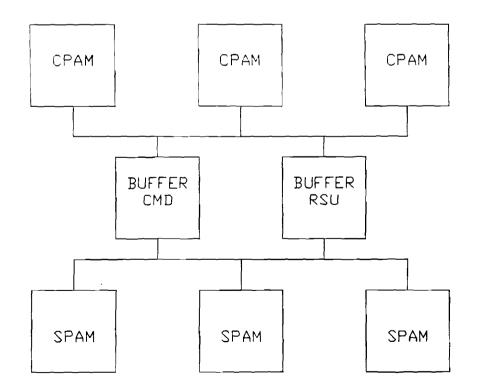

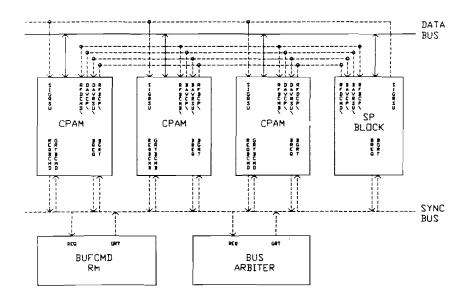

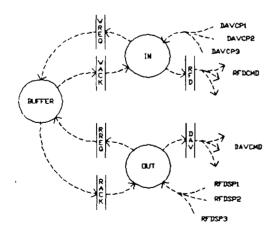

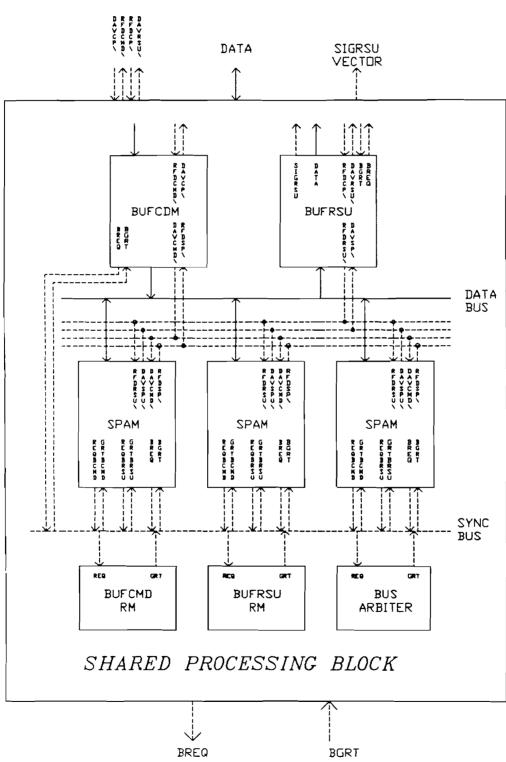

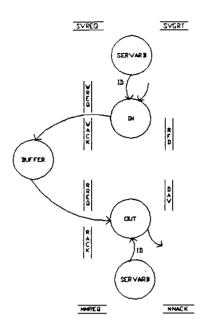

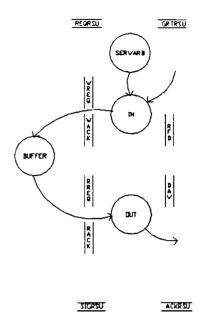

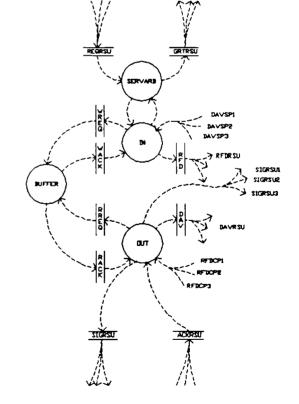

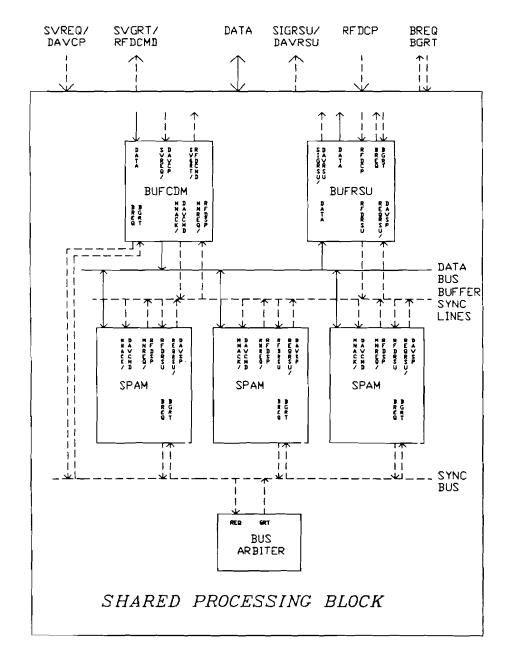

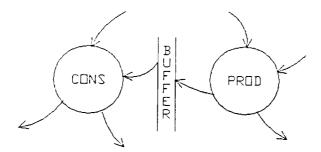

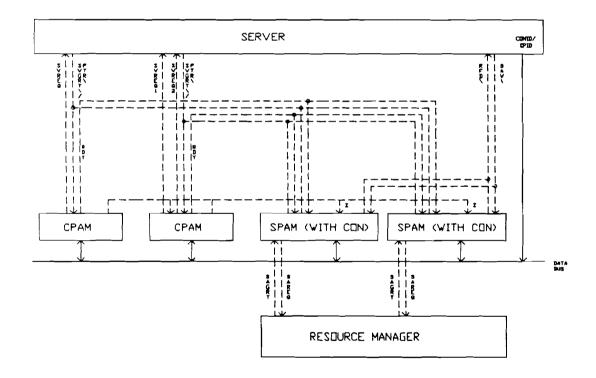

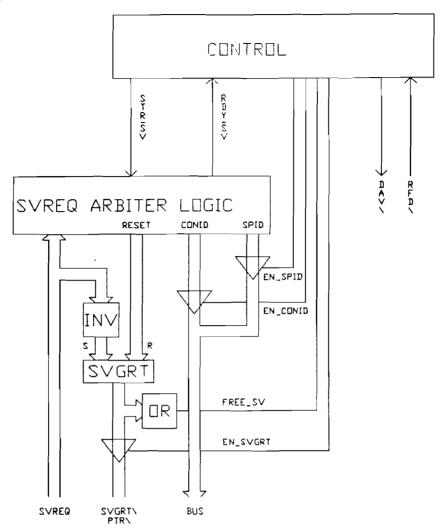

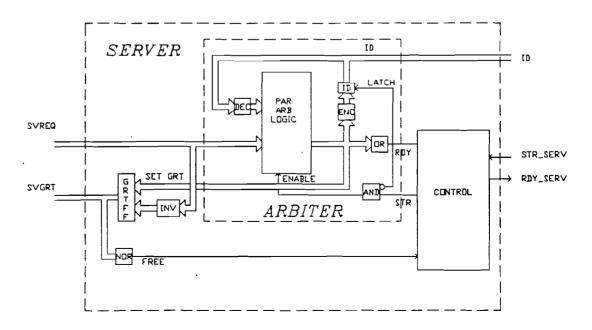

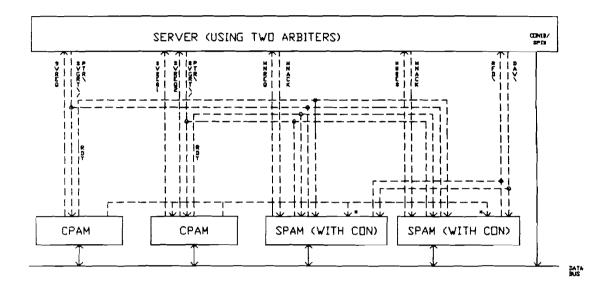

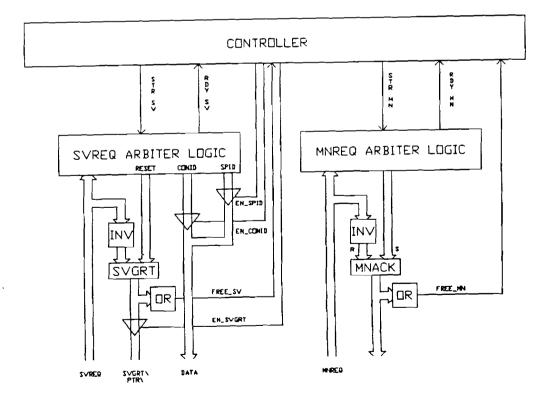

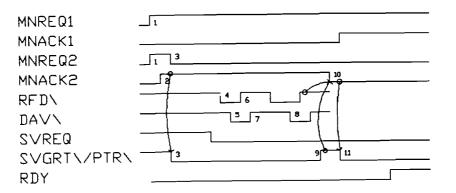

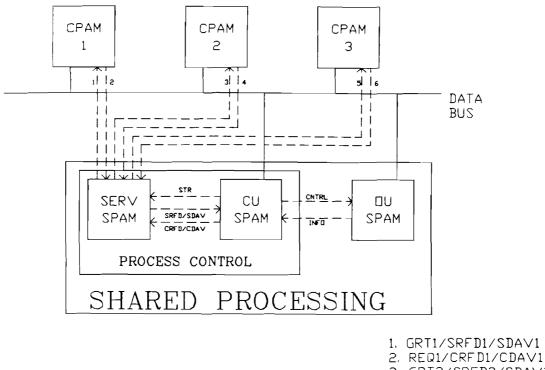

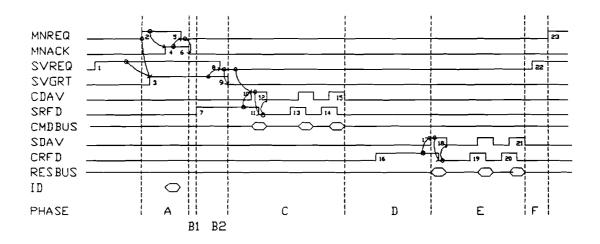

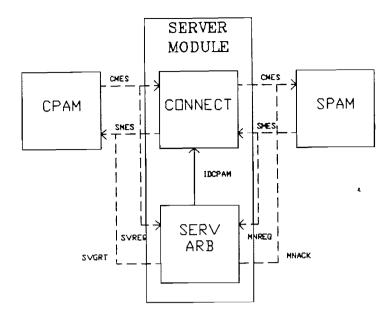

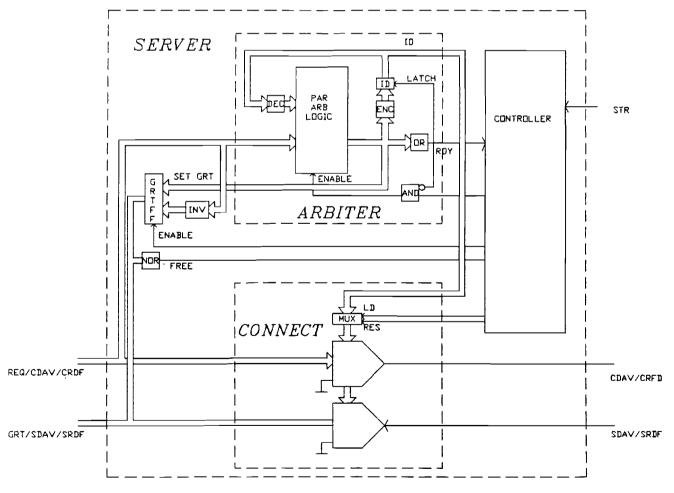

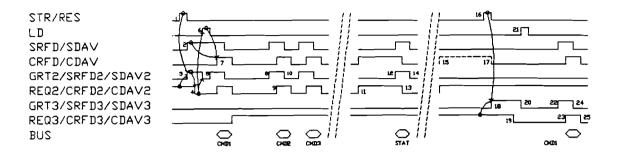

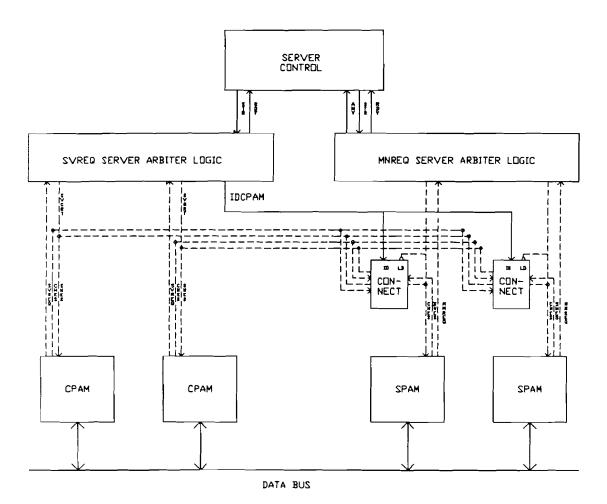

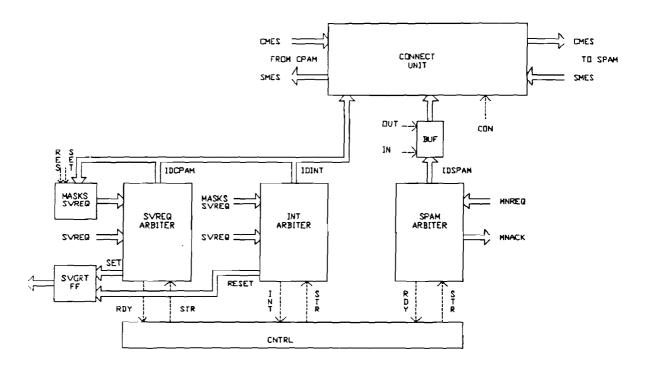

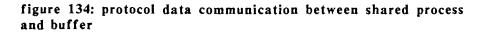

Often encountered identical transformations in the requirements model are allocated to special modules redefining the model. The transformation is started by other modules (shared processing). The requests are scheduled/served by the server architecture module (SVAM), which connects the caller with the executer, so that both can exchange data (parameters and result) and synchronization signals. Instead of direct information exchange connections, a buffer for the parameters and results can be used reducing the waiting time of the partners and increasing flexibility.

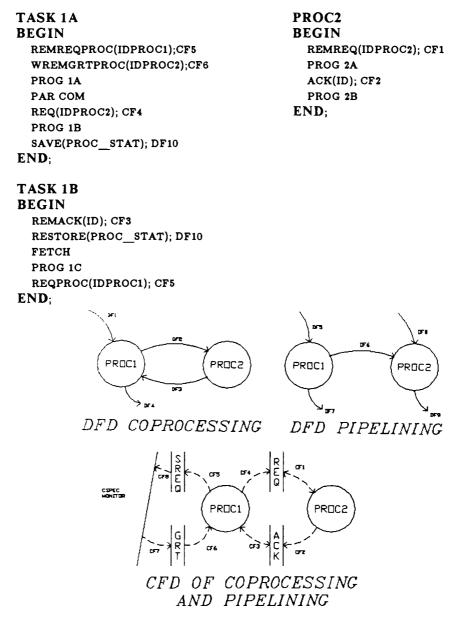

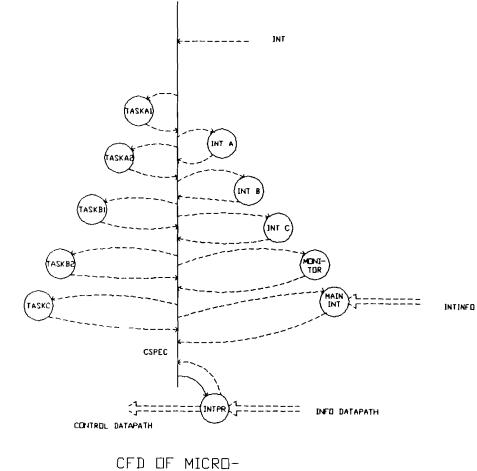

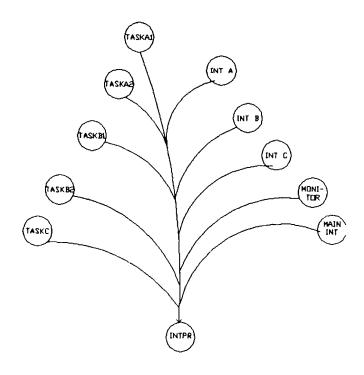

To prevent busy-waiting for synchronization and shared processing events a simple dispatching scheme can be implemented in the PAM using interrupts to react immediately to events. The contents of the datapath is not effected by the interrupt handling. Primitives divide the transformation into tasks, which are made runnable by the occurrence of an interrupt event or by the SAM. "Er bestaat geen mogelijkheid om na te gaan welke beslissing beter is, want er is geen vergelijking. Wij maken alles zomaar voor het eerst en onvoorbereid mee, net als een acteur die voor de vuist weg een stuk speelt. Maar wat kan het leven waard zijn, als de eerste repetitie voor het leven al het leven zelf is? ... Het leven lijkt daarom altijd op een schets. Hoewel het woord 'schets' evenmin juist is, want een schets is altijd een ontwerp voor iets, de voorbereiding van een schilderij, terwijl de schets van ons leven een schets is voor niets, het ontwerp zonder een schilderij."

> Milan Kundra "De ondraaglijke lichtheid van het bestaan"

# CONTENTS

| <ol> <li>IDENTIFICATION OF PARALLEL PROCESSES AND<br/>SYNCHRONIZATION USING A MODELING TOOL</li> <li>1. Introduction to system development and specification.</li> <li>2. The model and the modeling techniques</li> <li>3. The requirements model</li> <li>2.3. I. The structure of the requirements model</li> <li>2.3. The control model</li> <li>2.3. The structure of the model</li> <li>2.4. The architecture model</li> <li>2.4. The structuring of architecture modules</li> <li>2.4. Allocation to hardware and specifications</li> <li>2.4. Allocation to hardware and software</li> <li>2.5. The mapping process and its problems</li> <li>2.5.1. Architecture module allocation</li> <li>2.5.2. Task modeling</li> <li>2.5.3. Interface modeling</li> <li>2.6. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5.1. Semaphores</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching.</li> <li>3.7. Conclusion</li> <li>4. Mutual exclusion and correct synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.2. Parallel operating spams</li> </ol> | 1. INTRODUCTION                                   | • |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---|

| 2.1. Introduction to system development and specification.         2.2. The model and the modeling techniques         2.3. The requirements model         2.3.1. The structure of the requirements model         2.3.2. The data processing model         2.3.3. The control model         2.3.4. Timing requirements         2.3.5. Requirement dictionary         2.4. The structure of the model         2.4.1. The structure of the model         2.4.2. The structuring of architecture modules         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.6. Summary and conclusions         3.3. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4.4. Mutual exclusion and correct synchronization         4.5. WICHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization <t< td=""><td>2. IDENTIFICATION OF PARALLEL PROCESSES AND</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2. IDENTIFICATION OF PARALLEL PROCESSES AND       |   |

| 2.1. Introduction to system development and specification.         2.2. The model and the modeling techniques         2.3. The requirements model         2.3.1. The structure of the requirements model         2.3.2. The data processing model         2.3.3. The control model         2.3.4. Timing requirements         2.3.5. Requirement dictionary         2.4. The structure of the model         2.4.1. The structure of the model         2.4.2. The structuring of architecture modules         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.6. Summary and conclusions         3.3. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4.4. Mutual exclusion and correct synchronization         4.5. WICHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization <t< td=""><td>SYNCHRONIZATION USING A MODELING TOOL</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SYNCHRONIZATION USING A MODELING TOOL             |   |

| <ul> <li>2.2. The model and the modeling techniques</li> <li>2.3. The requirements model</li> <li>2.3.1. The structure of the requirements model</li> <li>2.3.2. The data processing model</li> <li>2.3.3. The control model</li> <li>2.3.4. Timing requirements</li> <li>2.3.5. Requirement dictionary</li> <li>2.4. The architecture model</li> <li>2.4.1. The structure of the model</li> <li>2.4.2. The structure of a chitecture modules</li> <li>2.4.4. Allocation to hardware and specifications</li> <li>2.5.4.4. Allocation to hardware and software</li> <li>2.5.5. The mapping process and its problems</li> <li>2.5.1. Architecture modelial</li> <li>2.5.2. Task modeling</li> <li>2.5.3. Interface modeliag</li> <li>2.5.4. Autoritication</li> <li>2.5.5. The modeling</li> <li>2.5.6. Summary and conclusions.</li> <li>3.5.0 Software SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.6. Synchronization</li> <li>3.7. Conclusion</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Synchronization</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Mutual exclusion and correct synchronization</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3.1. One spam.</li> </ul>                                                                                                                                                                                                                                                                                              |                                                   |   |

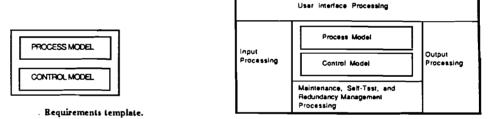

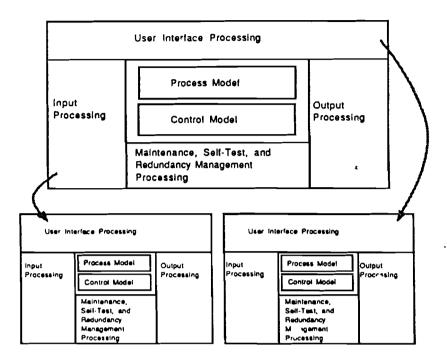

| <ul> <li>2.3. The requirements model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |   |

| <ul> <li>2.3.1. The structure of the requirements model</li> <li>2.3.2. The data processing model</li> <li>2.3.3. The control model</li> <li>2.3.4. Timing requirements.</li> <li>2.3.5. Requirement dictionary</li> <li>2.4. The architecture model</li> <li>2.4.1. The structuring of architecture modules.</li> <li>2.4.2. The structuring of architecture modules.</li> <li>2.4.3. Architecture diagrams and specifications</li> <li>2.4.4. Allocation to hardware and software</li> <li>2.5. The mapping process and its problems</li> <li>2.5.1. Architecture module allocation</li> <li>2.5.2. Task modeling</li> <li>2.5.3. Interface modeling</li> <li>2.5.4. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.5.1. Semaphores</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching</li> <li>3.7. Conclusion</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |                                                   |   |

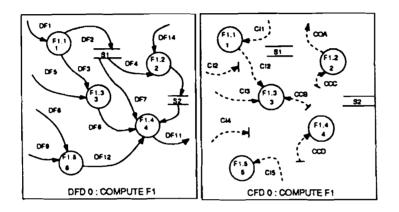

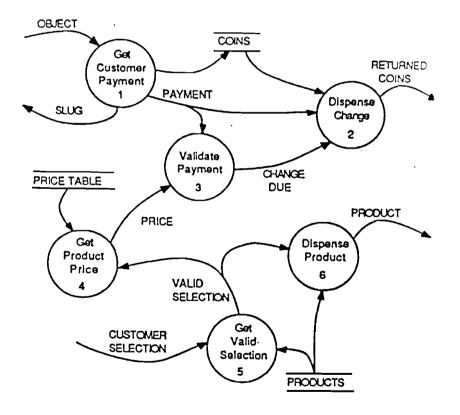

| 2.3.2. The data processing model         2.3.3. The control model         2.3.4. Timing requirements.         2.3.5. Requirement dictionary         2.4. The architecture model         2.4.1. The structure of the model         2.4.2. The structuring of architecture modules.         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.6. Summary and conclusions.         3.6. Software SOLUTIONS TRANSLATABLE INTO HARDWARE?         3.1. Introduction         3.2. Operating systems and process management         3.3. Software SOLUTIONS TRANSLATABLE INTO HARDWARE?         3.1. Introduction         3.4. Serialization         3.5. Synchronization         3.6. Scheduling/dispatching         3.7. Conclusion         3.7. Conclusion         3.8. Synchronization         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         4.6. DIRECT CONNECTION SHARED PROCESSING METHODS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |   |

| 2.3.3. The control model         2.3.4. Timing requirements.         2.3.5. Requirement dictionary         2.4. The architecture model         2.4.1. The structuring of architecture modules.         2.4.2. The structuring of architecture modules.         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.6.3. Interface modeling         2.6.4. Summary and conclusions.         3.5. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1. The primitives for starting a shared process         6.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |   |

| 2.3.4. Timing requirements.         2.3.5. Requirement dictionary         2.4. The architecture model         2.4.1. The structure of the model         2.4.2. The structure of architecture modules         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.6. Summary and conclusions         2.6. Summary and conclusions         3.1. Introduction         3.2. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4.8. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         4.6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1.1. Server and caller synchronization         6.2. Parameter and result communication protocol         6.3. A hardwired process call identity allocation model and pspecs <td>2.3.2. The data processing model</td> <td>•</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.2. The data processing model                  | • |

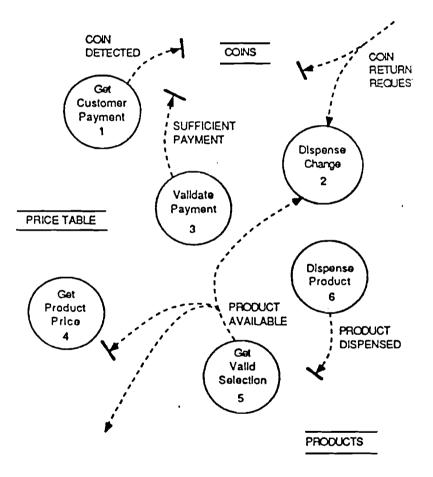

| <ul> <li>2.3.5. Requirement dictionary</li> <li>2.4. The architecture model</li> <li>2.4.1. The structuring of architecture modules</li> <li>2.4.2. The structuring of architecture modules</li> <li>2.4.3. Architecture diagrams and specifications</li> <li>2.4.4. Allocation to hardware and software</li> <li>2.5. The mapping process and its problems</li> <li>2.5.1. Architecture module allocation</li> <li>2.5.2. Task modeling</li> <li>2.6. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.5. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. The primitives for starting a shared process</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3.3. The control model                          |   |

| <ul> <li>2.3.5. Requirement dictionary</li> <li>2.4. The architecture model</li> <li>2.4.1. The structuring of architecture modules</li> <li>2.4.2. The structuring of architecture modules</li> <li>2.4.3. Architecture diagrams and specifications</li> <li>2.4.4. Allocation to hardware and software</li> <li>2.5. The mapping process and its problems</li> <li>2.5.1. Architecture module allocation</li> <li>2.5.2. Task modeling</li> <li>2.6. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.5. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. The primitives for starting a shared process</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3.4. Timing requirements.                       |   |

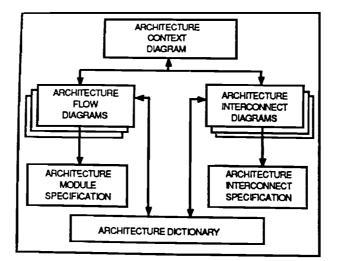

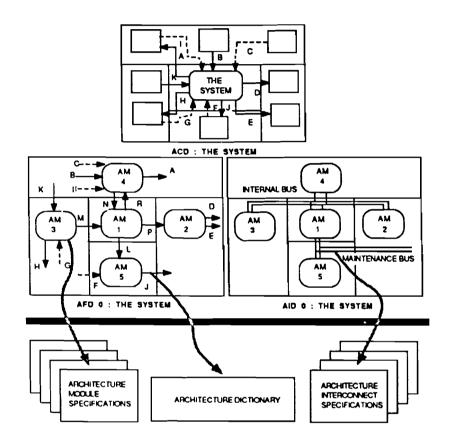

| <ul> <li>2.4. The architecture model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |   |

| 2.4.1. The structure of the model.         2.4.2. The structuring of architecture modules.         2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.5.4. Architecture module allocation         2.5.5. Interface modeling         2.5.6. Summary and conclusions         3.6. Summary and conclusions         3.7. Operating systems and process management         3.8. Operating systems and process management         3.9. Mutual exclusion         3.4. Serialization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         4.6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1.1. Server and caller synchronization         6.2. Parameter and result communication protocol         6.3. A hardwired process call identity allocation mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |   |

| 2.4.2. The structuring of architecture modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |   |

| 2.4.3. Architecture diagrams and specifications         2.4.4. Allocation to hardware and software         2.5. The mapping process and its problems         2.5. The Architecture module allocation         2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.6.5.3. Interface modeling         2.6.5.4. Marchitecture         3.5.7. Task modeling         2.6.5.3. Interface modeling         2.6.5.4. Summary and conclusions         3.5.5.5. Summary and conclusions         3.6.5. Summary and conclusions         3.7. Operating systems and process management         3.8. Operating systems and process management         3.9. Mutual exclusion         3.4. Serialization         3.5. Synchronization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                   |   |

| <ul> <li>2.4.4. Allocation to hardware and software</li> <li>2.5. The mapping process and its problems</li> <li>2.5.1. Architecture module allocation</li> <li>2.5.2. Task modeling</li> <li>2.5.3. Interface modeling</li> <li>2.6. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |   |

| <ul> <li>2.5. The mapping process and its problems</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                   |   |

| <ul> <li>2.5. The mapping process and its problems</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.4.4. Allocation to hardware and software        |   |

| 2.5.1. Architecture module allocation         2.5.2. Task modeling         2.5.3. Interface modeling         2.6. Summary and conclusions         3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?         3.1. Introduction         3.2. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5. Synchronization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1. The primitives for starting a shared process         6.1.1. Server and caller synchronization         6.2. Parameter and result communication protocol         6.3. A hardwired process call identity allocation model and pspecs         6.3.1. One spam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |   |

| 2.5.2. Task modeling         2.5.3. Interface modeling         2.6. Summary and conclusions.         3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?         3.1. Introduction         3.2. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5. Synchronization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1. The primitives for starting a shared process         6.1. Server and caller synchronization         6.2. Parameter and result communication protocol         6.3. A hardwired process call identity allocation model and pspecs         6.3. A hardwired process call identity allocation model and pspecs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                   |   |

| 2.5.3. Interface modeling         2.6. Summary and conclusions.         3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?         3.1. Introduction         3.2. Operating systems and process management         3.3. Mutual exclusion         3.4. Serialization         3.5. Synchronization         3.5. Synchronization         3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1.1. Server and caller synchronization         6.1.2. Spam monitor and server synchronization         6.1.2. Spam monitor and server synchronization         6.3. A hardwired process call identity allocation model and pspecs         6.3.1. One spam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |   |

| <ul> <li>2.6. Summary and conclusions.</li> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5. Synchronization</li> <li>3.5.1. Semaphores</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.2. Spam monitor and server synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |   |

| <ul> <li>3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE?</li> <li>3.1. Introduction</li> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5. Synchronization</li> <li>3.5.1. Semaphores</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.1. Server and caller synchronization</li> <li>6.2. Spam monitor and server synchronization</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                   |   |

| <ul> <li>3.1. Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.6. Summary and conclusions.                     | • |

| <ul> <li>3.1. Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3. SOFTWARE SOLUTIONS TRANSLATABLE INTO HARDWARE? |   |

| <ul> <li>3.2. Operating systems and process management</li> <li>3.3. Mutual exclusion</li> <li>3.4. Serialization</li> <li>3.5. Synchronization</li> <li>3.5. Synchronization</li> <li>3.5.2. Block and wakeup</li> <li>3.5.2. Block and wakeup</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |   |

| <ul> <li>3.3. Mutual exclusion.</li> <li>3.4. Serialization.</li> <li>3.5. Synchronization.</li> <li>3.5.1. Semaphores.</li> <li>3.5.2. Block and wakeup.</li> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching.</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction.</li> <li>4.2. Process synchronization.</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6.1. The primitives for starting a shared process</li> <li>6.1.1. Server and caller synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.2 Operating systems and process management      | • |

| <ul> <li>3.4. Serialization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2. Operating systems and process management     | • |

| <ul> <li>3.5. Synchronization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   | ٠ |

| 3.5.1. Semaphores         3.5.2. Block and wakeup         3.5.3. High level mechanism: monitor         3.6. Scheduling/dispatching         3.7. Conclusion         4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES         4.1. Introduction         4.2. Process synchronization         4.3. Request/acknowledge synchronization         4.4. Mutual exclusion and correct synchronization         4.5. Communication         5. SHARED PROCESSING         6. DIRECT CONNECTION SHARED PROCESSING METHODS         6.1. The primitives for starting a shared process         6.1.2. Spam monitor and server synchronization         6.2. Parameter and result communication protocol         6.3. A hardwired process call identity allocation model and pspecs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |   |

| <ul> <li>3.5.2. Block and wakeup</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |   |

| <ul> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching.</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization.</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1.1. Server and caller synchronization</li> <li>6.1.2. Spam monitor and server synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.5.1. Semaphores                                 |   |

| <ul> <li>3.5.3. High level mechanism: monitor</li> <li>3.6. Scheduling/dispatching.</li> <li>3.7. Conclusion</li> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES</li> <li>4.1. Introduction</li> <li>4.2. Process synchronization.</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1.1. Server and caller synchronization</li> <li>6.1.2. Spam monitor and server synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.5.2. Block and wakeup                           |   |

| <ul> <li>3.6. Scheduling/dispatching</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.5.3. High level mechanism: monitor              |   |

| <ul> <li>3.7. Conclusion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.6 Scheduling/dispatching                        |   |

| <ul> <li>4. SYNCHRONIZATION AND COMMUNICATION PRIMITIVES <ul> <li>4.1. Introduction</li> <li>4.2. Process synchronization</li> <li>4.3. Request/acknowledge synchronization</li> <li>4.4. Mutual exclusion and correct synchronization</li> <li>4.5. Communication</li> </ul> </li> <li>5. SHARED PROCESSING</li> <li>6. DIRECT CONNECTION SHARED PROCESSING METHODS</li> <li>6.1.1. Server and caller synchronization</li> <li>6.1.2. Spam monitor and server synchronization</li> <li>6.2. Parameter and result communication protocol</li> <li>6.3. A hardwired process call identity allocation model and pspecs</li> <li>6.3.1. One spam</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.7. Conclusion                                   | • |

| <ul> <li>4.1. Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |   |