# Self-aligned flexible waveguides for interfacing flip-chip assembled InP photonic integrated circuits on SiN

*Citation for published version (APA):* Tian, W., Wörhoff, K., Dekker, R., Khachikyan, A., Mittelstädt, C., van Kerkhof, J., Ren, Y., Santos, R., Williams, K. A., & Leijtens, X. J. M. (2021). Self-aligned flexible waveguides for interfacing flip-chip assembled InP photonic integrated circuits on SiN. In 25th Annual Symposium of the IEEE Photonics Society Benelux

Document status and date: Published: 01/01/2021

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Self-aligned flexible waveguides for interfacing flipchip assembled InP photonic integrated circuits on SiN

W. Tian,<sup>1\*</sup> K. Wörhoff,<sup>2</sup> R. Dekker,<sup>2</sup> A. Khachikyan,<sup>3</sup> C. Mittelstädt,<sup>3</sup> J. van Kerkhof, <sup>4</sup> Y. Ren, <sup>5</sup> R. Santos,<sup>1</sup> K. Williams,<sup>1</sup> and X.J.M. Leijtens<sup>1</sup>

<sup>1</sup> Institute for Photonic Integration, Eindhoven University of Technology, 5600 MB Eindhoven, The Netherlands

<sup>2</sup> LioniX International, Hengelosestraat 500, 7521 AN Enschede, The Netherlands <sup>3</sup> Research & Development, ficonTEC Service GmbH, Rehland 8, Achim, 28832, Germany

<sup>4</sup> PHIX Photonics Assembly, De Veldmaat 17, 7522 NM, Enschede, The Netherlands

<sup>5</sup> SMART Photonics B.V., 5656 AE Eindhoven, The Netherlands

\*Email: w.tian1@tue.nl

Scalable and cost-effectively connecting optical inputs and outputs to photonic integrated circuits (PICs) is challenging in photonic assembly. We utilize a TriPleX (SiN) interposer with suspended waveguides for interfacing optical fiber arrays to waveguides on InP PICs. Spot size converters on TriPleX are employed for high coupling efficiency. We apply this method in a multiport photonics assembly concept, in which an InP PIC is p-side-down soldered on the TriPleX carrier, which simultaneously provides electrical and optical interconnection. A design is made to deliver up to 112 optical interfaces between the TriPleX interposer and InP PIC. Designs and preliminary measurement results are presented.

## Introduction

Photonic integrated circuits (PICs) find application in many fields such as data communication networks and sensing [1]. However, the expensive photonic packaging is a barrier to the commercialization and application of PICs. The optical inputs and outputs (I/Os) are most challenging in photonic packaging because of the large mismatch of the optical mode size between a waveguide ( $\sim 1 \times 1 \mu m$ ) and optical fiber ( $\sim 10 \times 10 \mu m$ ), as well as tight alignment tolerances. Low-loss waveguide mode coupling requires submicron alignment accuracy which typically necessitates time-consuming active alignment[2]. Such alignment accuracies cannot be obtained even with high-end automated assembly machines that typically provide down to 2  $\mu m$  placement accuracy. To overcome this problem one can use integrated spot-size converters (SSCs) on the InP or SiPH chip, to enlarge the mode in the waveguides to match that of the optical fiber and relax the alignment tolerance[2-5]. However, SSCs take up significant chip space and the minimum pitch limits the number of optical connections to less than 10 per mm which is insufficient for the trend of high optical port density in the next-generation data communication[6, 7].

In this paper, we present a passive alignment approach utilizing suspended waveguides based on TriPleX (SiN) technology, which has previously been demonstrated to interconnect densities of 40 per mm[8]. We apply this approach in a scalable and cost-effective photonic assembly concept. This process is targeted to deliver up to 112 optical I/Os which are self-aligned simultaneously during a flip-chip bonding.

## Concept

The self-aligning structure connecting the InP chip to the TriPleX carrier consists of two parts: the suspended flexible waveguides on TriPleX and a triangular landing trench on

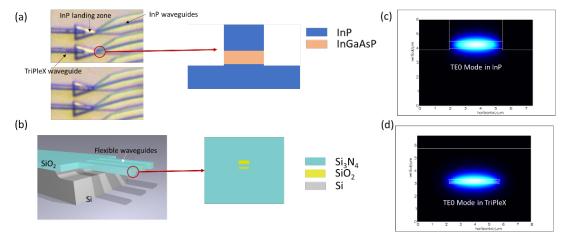

Figure 1: Schematic of flexible waveguides on TriPleX and their corresponding triangular landing trenches on InP. (a): Schematic of two types of triangular landing trenches ended with a straight and 7-degree angled lateral tapering waveguide on InP, the enlarged view is the cross-section of deeply-etch ridge waveguide geometry; (b): Schematic of 3 suspended waveguides, the enlarged view is the cross-section of asymmetric double-stripe (ADS) geometry. (part of the waveguides are omitted for simplicity); (c) and (d): Simulated optical fields (TE0) in a straight InP waveguide and a TriPleX ADS waveguide.

the InP chip that provides the mechanical guiding of the flexible finger to the correct position. This is shown in Figure 1 (a, b).

The landing trench on InP is in a triangular shape as shown in Figure 1a. There are two types: one connecting a straight waveguide and one connecting to a 7-degree-angled waveguide. The 7-degree-angle (as shown in Figure 1a) is chosen for minimizing the reflection. The enlarged view shows the cross-section of a deeply etched ridge waveguide. Figure 1b depicts a schematic of the TriPleX finger waveguide[9]. The waveguides are released and suspended by locally etching away the substrate during fabrication. The suspended waveguides are 500-750 µm long. The cross-section of flexible waveguides is in an asymmetric double-stripe (ADS) geometry that consists of two stripes of silicon nitride (Si<sub>3</sub>N<sub>4</sub>) on top of each other, separated by an intermediate 100 nm silicon oxide (SiO<sub>2</sub>) layer as shown in Figure 1(b). The thickness for the upper Si<sub>3</sub>N<sub>4</sub> stripe is 175 nm and the lower one is 75 nm. The waveguide geometry is offered within the standard TriPleX platform and is designed for coupling to and from optical fiber arrays with low loss by the integration of SSCs [9].

### Simulation results

The TripleX and InP waveguides at the location of the triangular trench were simulated in Photon Design's FIMMWAVE and FIMMPROP software. The modes of both were designed to be matching by tailoring the waveguide geometry through adiabatic tapering sections. The coupling efficiency of the self-aligned structure depends on the geometries of the tips of the flexible waveguides and the triangular trenches, which is determined by fabrication tolerances.

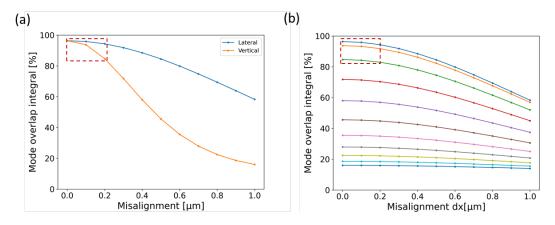

Figures 1c and 1d depict the simulated optical fields of the fundamental TE mode of both whose mode field diameters are 2.7  $\mu$ m ( $\Delta x$ , in-plane) and 0.9  $\mu$ m ( $\Delta y$ , out-of-plane direction). To study the feasibility of the fabrication processes, the coupling efficiency is investigated by calculating the overlap integral between those modes as a function of the misalignment in vertical and lateral directions. Figure 2a presents simulated mode overlap integral as a function of misalignment in lateral ( $\Delta x$ , in-plane), vertical ( $\Delta y$ , out-of-plane) directions from 0  $\mu$ m to 1  $\mu$ m. Note that the vertical alignment is critical.

Figure 2: Simulation results: (a): Mode overlap integral versus lateral ( $\Delta x$ ) or vertical ( $\Delta y$ ) misalignment; (b): Mode overlap integral versus the product of misalignments in both lateral and vertical directions, each curve from top to bottom represents the mode overlap for a vertical misalignment from 0 to 1  $\mu$ m at a 100nm step.

Figure 2b shows the total mode overlap integral as a function of the product of misalignments in both lateral and vertical directions. In this figure, each curve, from top to bottom, represents the mode overlap of a vertical misalignment from 0 to 1  $\mu$ m at a 100 nm step.

With high-resolution fabrication, the alignment difficulty can be shifted to fabrication tolerance, by using the flexible waveguides. The coupling efficiency then depends on the fabrication tolerance of waveguide geometries. Since the fabrication tolerance of the high-resolution lithography is less than 200 nm, more than 80% mode overlap can be achieved, indicating a coupling loss below 1 dB.

## Assembly concept

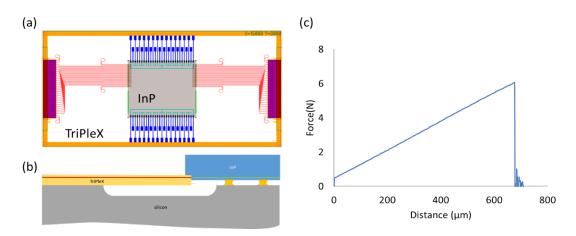

The self-alignment approach is applied in a hybrid assembly concept, as shown in Figure 3. We standardize on-chip dimensions and connections, including up to 112 optical interconnects and 58 electrical interconnects. The detailed standardized parameters can be found in [10]. The standardization allows us to reuse various parts and to focus on the functional and operational process, without limiting the applications space. A TriPleX carrier acts as an interposer that provides the optical interfaces to an InP PIC. One side of the waveguides on the TriPleX carrier connects to a standard optical fiberarray, the other side is self-aligned to the InP PIC. In addition, the TriPleX carrier provides the electrical interfaces to the InP PIC, which can be used for electrical probing and bonding to external electronic circuitry. Solder bumps are on top of the bonding pads which is fluxless Eutectic Gold-Tin (AuSn) with an 80-20 weight composition.

During the assembly, the InP PIC is flipped and moved to the pre-defined location by an automated pick-and-place machine. The PIC and carrier can be joined together by heating up the AuSn solder bumps locally by leveraging laser soldering technology. After the electrical connections are soldered, the InP chip is in position and the 112 optical I/Os are self-aligned to the waveguides on the TriPleX carrier. Shear force tests are performed afterward to check solder joint performance. Figure 3c shows that the maximum shear force is 6 N, which indicates a strong contact.

External fiber-arrays provide the connections to the TriPleX carrier. They are attached with established assembly processes, since the TriPleX waveguides at the edge of the carrier are mode-matched to standard single-mode fibers.

Figure 3: Schematic of a flip-chip assembled InP PIC on a TriPleX carrier. (a): the mask layout of TriPleX carrier and InP PIC with optical and electrical interconnects; (b): Schematic of a self-aligned flexible TriPleX waveguide to its counterpart on the InP PIC after flip-chip bonding; (c): Shear force test results of electrical interconnects.

## Conclusion

In this paper, we presented the design of a self-aligned optical interconnect from fiber arrays to waveguides on an InP PIC. The concept is described and simulated, and critical elements are being experimentally investigated. This multiport assembly process promises to provide a scalable and cost-effective way for connecting a large number of optical and electrical ports to a photonic integrated circuit.

### References

- [1] M. Smit *et al.*, "An introduction to InP-based generic integration technology," *Semiconductor Science and Technology*, vol. 29, no. 8, 2014, doi: 10.1088/0268-1242/29/8/083001.

- [2] T. Barwicz *et al.*, "Automated, high-throughput photonic packaging," *Optical Fiber Technology*, vol. 44, pp. 24-35, 2018, doi: 10.1016/j.yofte.2018.02.019.

- [3] X. Mu, S. Wu, L. Cheng, and H. Y. Fu, "Edge Couplers in Silicon Photonic Integrated Circuits: A Review," *Applied Sciences*, vol. 10, no. 4, 2020, doi: 10.3390/app10041538.

- [4] Y. J. Chen *et al.*, "Hybrid III-V-on-SOI optical spot size converter by self-aligned selective undercut dry etching of Si," *Opt Lett*, vol. 45, no. 15, pp. 4188-4191, Aug 1 2020, doi: 10.1364/OL.396361.

- [5] T. Barwicz *et al.*, "Integrated Metamaterial Interfaces for Self-Aligned Fiber-to-Chip Coupling in Volume Manufacturing," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 25, no. 3, pp. 1-13, 2019, doi: 10.1109/jstqe.2018.2879018.

- [6] A. Janta-Polczynski *et al.*, "Packaging challenges for next-generation high bandwidth optoelectrical switch modules," presented at the Optical Interconnects XX, 2020.

- S. Fathololoumi *et al.*, "1.6 Tbps Silicon Photonics Integrated Circuit and 800 Gbps Photonic Engine for Switch Co-Packaging Demonstration," *Journal of Lightwave Technology*, vol. 39, no. 4, pp. 1155-1161, 2021, doi: 10.1109/jlt.2020.3039218.

- [8] X. Leijtens, R. Santos, and K. Williams, "High Density Multi-Channel Passively Aligned Optical Probe for Testing of Photonic Integrated Circuits," *IEEE Photonics Journal*, vol. 13, no. 1, pp. 1-15, 2021, doi: 10.1109/jphot.2020.3045346.

- [9] K. Wörhoff, R. G. Heideman, A. Leinse, and M. Hoekman, "TriPleX: a versatile dielectric photonic platform," *Advanced Optical Technologies*, vol. 4, no. 2, 2015, doi: 10.1515/aot-2015-0016.

- [10] S. Latkowski, D. Pustakhod, M. Chatzimichailidis, W. Yao, and X. J. M. Leijtens, "Open Standards for Automation of Testing of Photonic Integrated Circuits," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 25, no. 5, pp. 1-8, 2019, doi: 10.1109/jstqe.2019.2921401.