# **3D-Integration on Wafer Level of Photonic and Electronic** Circuits

#### Citation for published version (APA):

Spiegelberg, M. (2021). 3D-Integration on Wafer Level of Photonic and Electronic Circuits. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven.

Document status and date: Published: 02/03/2021

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# 3D-Integration on Wafer Level of Photonic and Electronic Circuits

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T Baaijens, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op dinsdag 02. Maart 2021 om 16:00 uur

door

Marc Spiegelberg

geboren te Frankfurt (Oder), Duitsland

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

| voorzitter:<br>1e promotor: | prof. dr. ir. P.G.M. Baltus<br>dr. J.J.G.M. van der Tol |                                        |

|-----------------------------|---------------------------------------------------------|----------------------------------------|

| 2e promotor:                | prof. dr. K.A. Williams                                 |                                        |

| leden:                      | prof dr. ir. A.M.J. Koonen                              |                                        |

|                             | prof. dr. ir. J. Bauwelinck                             | (IDLab, Universiteit Gent)             |

|                             | prof dring. habil. V. Krozer                            | (Goethe-Universität Frankfurt am Main) |

|                             | dr. U. Troppenz                                         | (Fraunhofer Institut,                  |

|                             |                                                         | Heinrich Hertz Institut, HHI)          |

| adviseur:                   | dr. Y. Jiao                                             |                                        |

Het onderzoek of ontwerp dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

## 3D-Integration on Wafer Level of Photonic and Electronic Circuits by Marc Spiegelberg

A catalogue record is available from the Eindhoven University of Technology Library.

ISBN: 978-90-386-5218-4

Copyright © 2021 by Marc Spiegelberg. All Rights Reserved.

This work has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement No. 688572 (WIPE). The publication reflects only the author's views. The European commission is not responsible for any use of the information this publication contains.

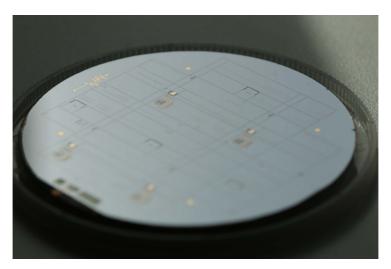

Cover designed by Marc Spiegelberg based on a microscope picture of the integrated indium phosphide wafer with partly removed substrate (Appendix B, step 54). Typeset using  $\&T_EX$ . Style design based on Joos Buij's template. Printed by: Gildeprint – The Netherlands

# Dedicated to my Ohana

"Hawaiian Vibes" painted by Merel van Eck

#### Summary

#### 3D-Integration on Wafer Level of Photonic and Electronic Circuits

A novel integration technique is demonstrated for the first time. It combines state-of-the-art photonic wafers, based on generic indium phosphide (InP) technology, with matching electronic wafers, realized with bipolar CMOS (BiCMOS) technology. The new technique encompasses adhesive wafer bonding and through-polymer electrical interconnects.

Optical modules used for datacenters and telecommunication face bandwidth limitations based on the non-optimal electrical interfaces between photonic and electronic integrated circuits (ICs). One possibility to improve the performance of the electrical connections is to simply shortening them, and thereby reduce the parasitic characteristics. With adhesive bonding it is possible to bring the photonic and electronic circuits in close contact. The intermediate polymer layer functions as an optical, electrical and thermal isolator. Bonding is performed on a wafer scale level and thus enables maximum scalability. The photonic wafer is reduced to its functional epitaxial layer stack, by removing the "useless" substrate on which the circuits are initially realized, which makes it possible to etch through the remaining membrane and the bonding layer to create electrical connections between the photonic and electronic ICs. This 3-D integration technique offers new design possibilities regarding placement of I/O's and functionalities.

In this work a design and process flow is created, taking into account the different wafer sizes by dicing a 200 mm BiCMOS wafer into several identical 3-inch wafers to match the InP wafer dimensions. The photonic layout is designed to match the electronic one. Bonding these wafers, which have topologies of several microns, with alignment accuracies of less than 4  $\mu$ m is achieved. A process to create the electrical interconnects is developed and is successfully demonstrated.

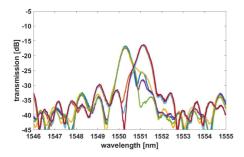

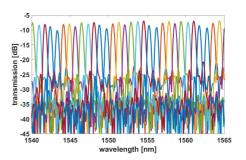

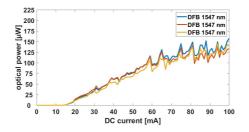

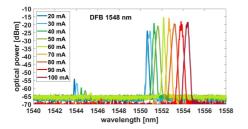

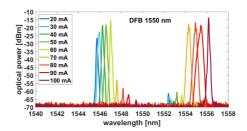

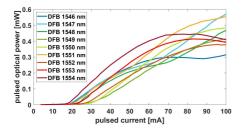

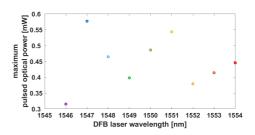

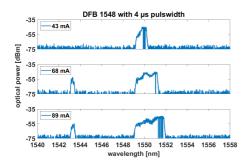

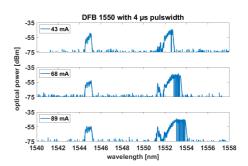

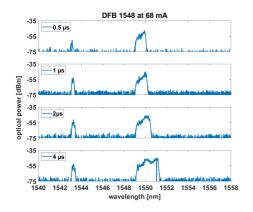

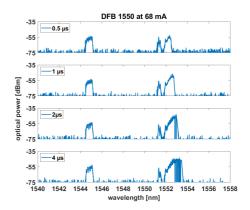

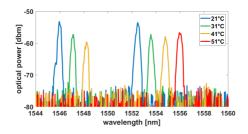

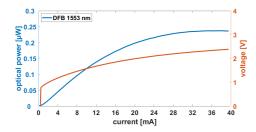

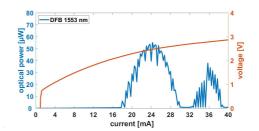

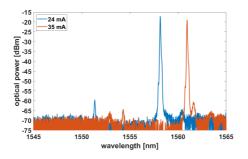

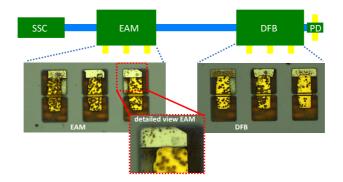

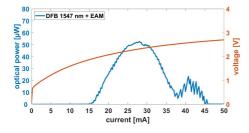

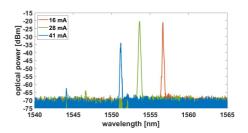

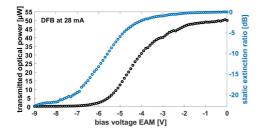

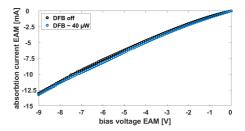

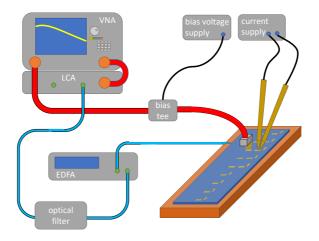

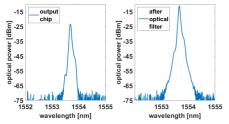

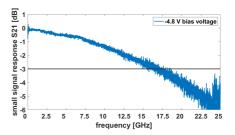

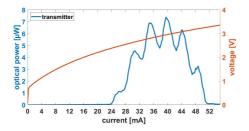

To monitor the photonic devices during the processing, vertical mirrors and several test structures are implemented. These have been used to characterize the impact of the integration technology on the device performance. Passive components show only minimal changes in performance, due to the added adhesive polymer, which functions as a cladding, and to the thermal expansion of the photonic membrane, resulting from the different coefficients of linear thermal expansion. Active components have been included to enable data transmission experiments. The modulated optical signal is generated with an electro-absorption modulator (EAM) and detected with a PIN photodiode (PD). The small signal response measured after the integration process is 16.5 GHz (EAM) and 27.5 GHz (PIN PD), respectively. As light source a distributed feedback (DFB) laser is integrated. Its performance suffers strongly from the lack of a cooling element at the photonic membrane side. A series of DFB laser is used with Bragg wavelengths between 1545 and 1554 nm. An average optical power of 48  $\mu$ W (coupled into a fibre) is measured for injection currents up to 45 mA.

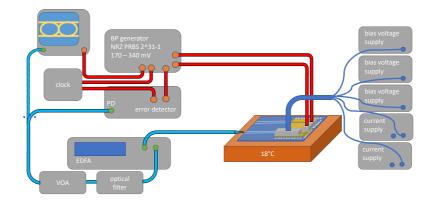

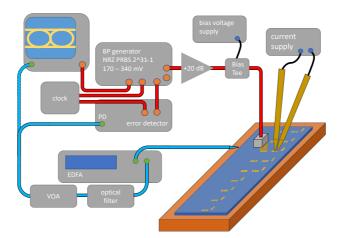

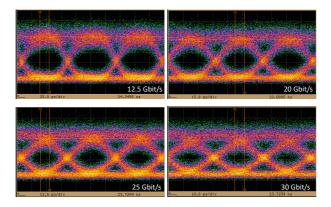

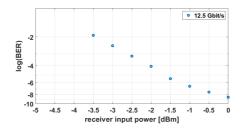

In cooperation with the TU/e IC-group and Ghent University hybrid transmitter (TX) and receiver (RX) designs have been created to demonstrate the feasibility of this new integration technology. The RX module achieved a data transmission rate of 10 Gbits/s, which is limited by the used electronic circuit design. In case of the TX, a data transmission experiment of the hybrid module is not performed as the EAM bias point does not match the initial design value. However, characterizing the photonic circuit itself showed open eye diagrams for bit rates up

to 25Gbit/s and a bit error rate (BER) of 3E-9 for 12.5 GBit/s.

The results achieved, show the feasibility of this new 3-D integration technology. Further development, in particular regarding thermal management and optical interfacing, will make it suitable for industrial applications.

# List of abbreviations

| μΤΡ    | micro transfer printing                 | FSR        | free spectral range                                            |

|--------|-----------------------------------------|------------|----------------------------------------------------------------|

| ALD    | atomic layer deposition                 | GDSII      | graphic design system II                                       |

| AR     | anti-reflection                         | GSG        | ground-signal-ground                                           |

| ASE    | amplified spontaneous emission          | HHI        | Fraunhofer Institut for Tele-<br>communication, Heinrich Hertz |

| AWG    | arrayed waveguide grating               |            | Institut                                                       |

| BB     | building block                          | IC         | integrated circuit                                             |

| BER    | bit error rate                          | ICP        | inductively coupled plasma                                     |

| BERT   | bit error rate tester                   | ICP-CVD    | inductively coupled plasma chemical vapour deposition          |

| BiCMOS | bipolar CMOS                            | IL         | insertion loss                                                 |

| BPG    | bit-pattern generator                   | IMOS       | InP membrane on silicon                                        |

| BSA    | backside alignment                      | IP         | intellectual property                                          |

| CBB    | composite building block                | IR         | infrared                                                       |

| CMOS   | complementary metal oxide semiconductor | LCA        | lightwave component analyser                                   |

| OTT    |                                         | LNA        | low noise amplifier                                            |

| CTE    | coefficient of linear thermal expansion | MMI        | multi mode interferometer                                      |

| CW     | continuous wave                         | MPW        | mutli project wafer                                            |

| DC     | direct current                          | MZI        | Mach Zehnder interferometer                                    |

| DFB    | distributed feedback                    | NRZ        | non return to zero                                             |

| DUT    | device under test                       | OSA        | optical spectrum analyser                                      |

| EAM    | electro-absorption modulator            | PCB        | printed circuit board                                          |

| EBR    | edge bead removal                       | PD         | photodiode                                                     |

| EDFA   | erbium-doped fiber amplifier            | PDK<br>PIC | process design kit<br>photonic integrated circuit              |

| EIC    | electronic integrated circuit           | PRBS       | pseudorandom binary sequence                                   |

| EUV    | extreme ultra violet                    | RF         | radio frequency                                                |

| FP     | Fabry-Perot                             | RIE        | reactive ion etching                                           |

| FPR    | free propagation region                 | RX         | receiver                                                       |

|        |                                         |            |                                                                |

| SEM  | scanning electron microscope | TPV  | through polymer vias                  |

|------|------------------------------|------|---------------------------------------|

| SMF  | single mode fiber            | TU/e | Eindhoven University of<br>Technology |

| SMP  | Smart Photonics              | ТХ   | transmitter                           |

| SMSR | side mode suppression ratio  | UHNA | ultra high numerical apperature       |

| SOL  | short open load              | UV   | ultra violet                          |

| SOP  | state of polarisation        | VNA  | vector network analyser               |

| SSC  | spot size converter          | VOA  | variable optical attenuator           |

| TEC  | thermoelectric cooler        | WDM  | wavelength devision multiplexing      |

| TIA  | transimpedance amplifier     | WGT  | waveguide transition                  |

# List of chemicals

| $Al_2O_3$        | aluminium oxide      | InGaAs                  | indium gallium arsenide |

|------------------|----------------------|-------------------------|-------------------------|

| AlF <sub>3</sub> | aluminium fluoride   | InP                     | indium phosphide        |

| BCB              | benzocyclobutene     | IPA                     | isopropanol             |

| CHF <sub>3</sub> | fluoroform           | KCN                     | potassium cyanide       |

| $H_2O$           | water                | кон                     | potassium hydroxide     |

| $H_2O_2$         | hydrogen peroxide    | $\mathbf{N}_2$          | nitrogen                |

| $H_2SO_4$        | sulfuric acid        | $\mathbf{O}_2$          | oxygen                  |

| $H_3PO_4$        | phosphoric acid      | Si                      | silicon                 |

| HCl              | hydrochloric acid    | <b>SiN</b> <sub>x</sub> | silicon nitride         |

| HMDS             | hexamethyldisilazane | SiO <sub>2</sub>        | silicon dioxide         |

# Contents

| Li | st Of                                                       | Abbreviations                                                                                                                                                                                                                                                   | x                                                  |

|----|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1  | Intr<br>1.1<br>1.2<br>1.3                                   | <b>roduction</b> Existing integration concepts         Motivation         Outline                                                                                                                                                                               | 1<br>2<br>4<br>5                                   |

| 2  | Inte<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6              | Thermal design considerations                                                                                                                                                                                                                                   | 7<br>8<br>11<br>13<br>15<br>16<br>19               |

| 3  | <b>Tec</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Foundry Requirements         Wafer Preparation         Wafer Bonding         InP substrate removal         Impact of thermal expansion         Electrical Interconnects         3.6.1         Fabrication         3.6.2         First hybrid module realization | 21<br>23<br>25<br>31<br>32<br>34<br>34<br>39<br>42 |

| 4  | <b>Pho</b> 4.1                                              | Passive Structures   4.1.1                                                                                                                                                                                                                                      | 52                                                 |

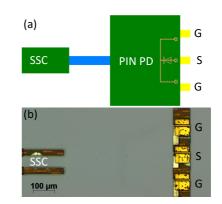

|    |                   | 4.2.1 Photodiode                         | 56 |

|----|-------------------|------------------------------------------|----|

|    |                   | 4.2.2 Distributed feedback laser (DFB)   | 62 |

|    |                   | 4.2.3 Electro absorption modulator (EAM) | 68 |

|    | 4.3               | 2nd wafer generation                     | 72 |

|    |                   | 4.3.1 Waveguide loss structures          | 72 |

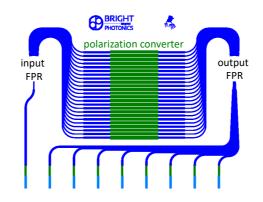

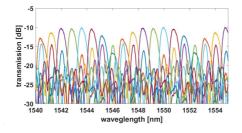

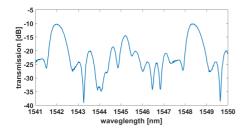

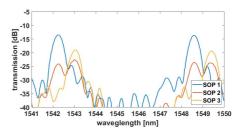

|    |                   | 4.3.2 Polarization independent AWG       | 75 |

|    | 4.4               | Conclusion                               | 77 |

| 5  | Co-               | designed assemblies                      | 79 |

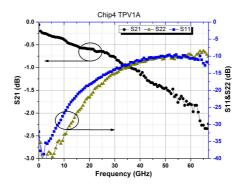

|    | 5.1               | High bandwidth electrical connections    | 79 |

|    | 5.2               | Receiver                                 | 80 |

|    | 5.3               | Transmitter                              | 82 |

|    | 5.4               | Conclusion                               | 87 |

| 6  | Con               | clusions and Outlook                     | 89 |

|    | 6.1               | Conclusion                               | 89 |

|    | 6.2               | Outlook                                  | 92 |

| A  | IR-v              | vafer shine through technique            | 95 |

| B  | Pro               | cess Flow                                | 97 |

| Bi | bliog             | raphy 1                                  | 03 |

| Ac | Acknowledgments 1 |                                          |    |

# Chapter

# Introduction

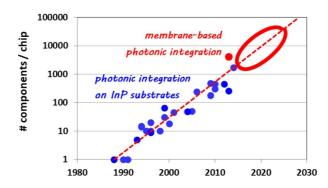

One of the most cited statements in electrical engineering is the prediction of Gordon E. Moore [1], which says that the density of electrical components in electronic integrated circuits (EICs) is doubling roughly every two years. A similar trend can be seen for photonic integrated circuits (PICs) [2, 3] (see figure 1.1). The increase of PICs density requires corresponding EICs, to provide the necessary electronic control interfaces. However, this introduces the question on how to integrate the electronic and photonic circuits. One example

Figure 1.1: Moore's law for photonics: number of components per chip plotted for the year of publication, originally published in [2]

on how to combine both circuits is placing them side-by-side and connecting them electrically via wire bonds. This technique is limited by the physical boundaries (number, length and uniformity of the wire bonds) and the achievable bandwidth. Alternative solutions on how to integrate photonics and electronics are proposed in literature. An overview of the most relevant concepts will be given in the next section. At the end of this chapter a motivation is given and the content of the thesis is listed.

# 1.1 Existing integration concepts

Classical photonic and electronic circuits are fabricated within different technologies and material systems. Electronics is based on silicon (Si) and is fabricated using complementary metal oxide semiconductor (CMOS) technology, or a similar one. For photonic components the used material depends on the desired wavelength range. Within this work the focus is on near infrared light, which is used for optical communication. Compositions of III-V materials especially those based on indium phosphide (InP), are used for this purpose.

The integration of photonics with electronics can be achieved by including both functionalities within one of the existing technologies (monolithic integration) or by combining them (heterogeneous integration).

#### Monolithic: InP

For InP this means the realization of electronic circuits. This is possible and has been demonstrated [4]. The InP material system offers transit frequencies of beyond 400 GHz at breakdown voltages of 5.5 V [5], which makes it suitable for high speed EICs. However, due to the fact that InP wafers are expensive and not available in large sizes, the use of this material is still limited to specialized electronic application [6].

#### Monolithic: CMOS

CMOS technology is providing Si wafers with diameters up to 450 mm. The fabrication processes are highly optimized and can achieve 7 nm nodes by using extreme ultra violet (EUV) lithography. This facility is the motivation for the rapidly growing interest in silicon photonics. Any platform that uses a Si based waveguide structure belongs to the silicon photonics category [7]. It offers many of the functionalities of a photonic platform, except a very important one: an efficient light source. Si has an indirect bandgap, which prohibits the efficient emission of light. Several groups are working on a concept to overcome this limitation [8], with a recent breakthrough in achieving a direct bandgap structure by growing Si with a hexagonal lattice structure [9]. However, these structures are still far away from being usable, let alone that it can be integrated within the CMOS fabrication process flow.

#### Heterogeneous: CMOS and InP

The heterogeneous concept can combine the advantages of both platforms. The existing concepts can be sorted into four technology groups:

- 1. III-V integrated in silicon photonics platform

- 2. micro transfer printing ( $\mu$ TP)

- 3. hybrid integration

- 4. InP membrane on Si (IMOS)

For the first approach reference [7] classifies three different categories on how the integration of a III-V laser source into a silicon photonic platform can be achieved. These are: direct growth of III-V on Si, bonding of III-V material with subsequent device processing, or a combination of both by growing the III-V material on Si and subsequently bonding this with a patterned Si wafer. The growth of III-V material on Si suffers strongly from the lattice mismatch, resulting in dislocations. To reduce the induced defects in the grown material several techniques are explored, like the use of strain superlattices layers [10] or the introduction of quantum dot layers to filter dislocations [11]. Bonding of III-V material onto the silicon photonics wafer resulted in several successful realizations [12, 13]. Two different bonding techniques are explored: direct and adhesive bonding. In both cases the III-V elements provide the gain material required for a laser. Different integration concepts are used, with a wide application range for which the III-V material can be selected specifically. However, the scalability of this technology seems challenging.

The  $\mu$ TP approach relies on fully fabricated III-V components and uses a sacrificial layer to enable a transfer process from the original wafer substrate onto the Si wafer. This stamp process requires a high alignment accuracy of 1.5  $\mu$ m and enables good scalability and throughput [14]. It also enables the use of several different materials to be transferred to the target wafer.

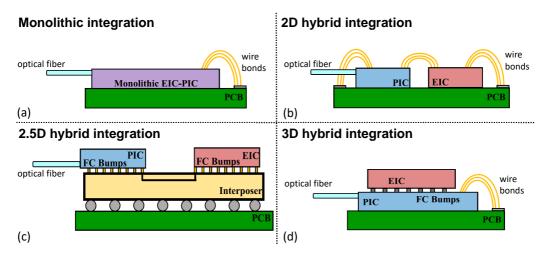

The term "hybrid integration" refers to the combination of two or more independently operating circuits realized within different technologies. Depending of the level of integration the concepts can be categorized in 2D, 2.5D or 3D approaches. In figure 1.2 (b),(c) and (d) an overview of these categories is presented. The 3D integration refers to stacking the two circuits on top of each other, using a flip-chip approach. The resulting electrical interconnects are short and enable high bandwidth operation [15]. In case of 2.5D integration an interposer

Figure 1.2: Schematic overview of the different integration concepts, [16]

carrier is used, through which both circuits are connected [16]. The interposer enables additional radio frequency (RF) lines, to optimise the signal transmission. The 2D integration is based on a side by side placement of the two circuits with wire bond connections in-between. Within the Eindhoven University of Technology (TU/e) another integration method is pursued, which can not be assigned into any of the introduced concepts. It is a wafer level integration, whereby an InP wafer is combined with a silicon wafer, using adhesive wafer bonding. This platform is called InP membrane on silicon (IMOS). The InP wafer assembles a full PIC environment relying on III-V waveguides [17, 18]. The technology uses the high refractive index contrast with the underlying adhesive polymer to form high density photonic circuits, enabling the full functionality of a InP platform. The silicon wafer is used only as a carrier so far, but has the perspective of being replaced with a CMOS wafer for a full photonic electronic integration.

## 1.2 Motivation

A new integration technology is proposed for integrating PICs with matching EICs. The main difference with IMOS is that the PIC and EIC are operating independently with classifies this approach to be hybrid. The used photonic platform relies on a generic process in contrast to the IMOS high refractive index platform. The fabrication is envisioned on wafer level to enable scalability. The technology is based on adhesive wafer bonding. Thereby a polymer is used in between the two wafers to mechanically combine them. The optical, thermal and electro-magnetic domains of the two wafers will be decoupled after the integration, because of the properties of the polymer used. The electrical connections between the two circuits are realised through the photonic membrane and through the polymer bonding layer. This concept enables high density of short interconnects. The research presented in this work is aiming to identify the opportunities and limitations of the proposed technology. Special attention will be paid towards the thermal, optical and electrical interfaces of the resulting devices.

The aim of this work is furthermore a successful demonstration of the proposed technology through realizing co-designed hybrid transmitter and receiver modules. Both the photonic and electronic circuit are created by using a mature foundry process. Adaptations will be needed to enable the integration of both platforms, which will be explained within this work.

The creation of a hybrid module requires matching photonic and electronic designs. However, there is no software available which is capable of directly creating this. Therefore a design flow will be presented to design matching wafer layouts.

To define the integration process it is important to understand the limitations of the materials and available technologies. A concept for wafer alignment is needed, which should be compatible with the intended bonding approach. Fabrication parameters like process temperature, chamber pressures and chemical selectivity have to be explored and adapted towards the integration technology.

The used PICs and EICs are highly valuable, which makes it important to monitor the functionality through the whole integration process. Therefore a new optical coupling interface will be used to monitor the passive structures on the photonic wafer. The performance of the bonded active photonic components will be compared to the foundry specifications.

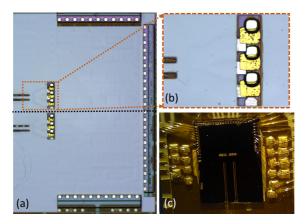

At the end of the integration process modules have to be created from the wafer. Therefore a new singulation process will be introduced. The resulting modules can be used with standardized packaging solutions, which puts certain requirements on the optical and electrical interfaces.

The analysis of the resulting modules regarding the impact of the developed 3D integration technology is a central part of the research presented in this thesis.

## 1.3 Outline

Within this work a new integration technology, combining generic PICs with matching EICs is proposed, fabricated and characterized to evaluate its potential. The content of this thesis is structured as follows:

- **Chapter 1** lists an overview of existing integration concepts to combine photonic and electronic circuits. A short descriptions of the proposed 3D integration technology is given, highlighting the conceptual approach.

- **Chapter 2** elaborates on the proposed design and process. A roadmap is given, describing the integration path towards the realization of hybrid modules. The design flow is presented in detail, including analysis of the optical, electrical and thermal limitations of the hybrid assembly. A compact process flow description is given as guidance for the explicit report following in chapter 3.

- **Chapter 3** concentrates on the developed technology, starting with defining the necessary foundry requirements for a successful integration. Furthermore, this chapter contains a description of the first hybrid module realization, explaining the required adaptions with respect to the initially proposed process flow .

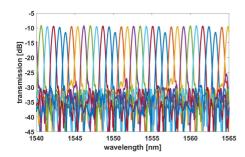

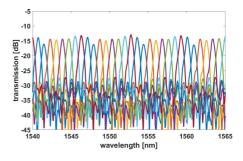

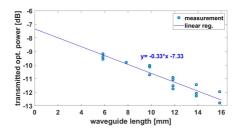

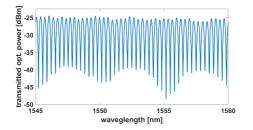

- **Chapter 4** reports the measurement results of the photonic components. The chapter is divided into sections on the passive and active components. The former will be characterized before and after the demonstration of the investigated integration technology, while the active components will mainly be characterized after the integration. Both will be compared with the foundry specification. The measurements results identify the impact of the technology. The corresponding test structures are introduced in this chapter. A wafer of the second generation is characterized before the integration process to compare and evaluate the wafer quality difference between the two fabrication runs.

- **Chapter 5** presents the performance achieved for the electrical interconnects and the hybrid photonic-electronic demonstrator. A transmitter and receiver module are created, and data transmission experiments are executed.

- **Chapter 6** summarizes the understanding gained of the investigated integration technology, and proposes future research questions and technology improvements.

# Chapter 2

# **Integration Roadmap**

The novel approach of integrating a state-of-the-art InP wafer with a matching electronic CMOS wafer, using adhesive wafer bonding, enters a technological domain which promises many new opportunities. However, it also creates uncertainty on how to best link these two worlds. In this chapter the challenges of the integration concept are introduced and the various technology decisions made are motivated.

Both technology platforms have been developed over many years, but the development of the electronic IC process (CMOS) started several decades before that of the photonic one. Therefore its foundry procedures are advanced and set to certain standards. This has the advantage that boundaries for simulation and design are well known, because of the availability of a robust and reproducible process. However, due to this the CMOS process is less flexible or adaptable towards the integration with PICs. Therefore it is the more flexible PIC process that needs to adapt towards the integration requirements. Thereby it is a key requirement that several photonic foundries are supported. Consequently adaptations should be generally applicable to these different PIC foundry platforms.

Here three platforms are considered: the Fraunhofer Institut for Tele-communication, Heinrich Hertz Institut (HHI) [19], Smart Photonics (SMP) [20] and IMOS [17, 18]. SMP and HHI are two generic foundries, enabling a fundamental set of photonic building blocks (BBs), such as gain or laser sections, modulators and detectors, to be integrated in their particular platforms. Next to those they provide several unique BBs, only supported by one specific foundry. Both platforms generate individual devices or PICs fabricated on an InP substrate. IMOS on the other hand is a membrane platform, based on a thin layer of InP which is applied with adhesive wafer bonding to a silicon wafer. The InP material there has a total thickness of a few 100 nanometres. The TU/e develops the IMOS process towards a mature platform, which is under constant improvement to enhance process stability and device performance. The experience with adhesive wafer bonding offers a promising approach towards integration with the electronic circuitry. This forms the basis for the wafer scale integration of photonics and electronics demonstrated in this work.

An IMOS structure consist of the silicon wafer as a carrier, the adhesive polymer and the InP membrane on top. To create the latter a sacrificial InP substrate is needed on which the layer stack is epitaxially grown. This layer stack is processed from the topside to prepare the BBs. Subsequently the InP wafer is bonded to a silicon wafer with the grown and pre-processed

layer stack facing the silicon wafer. After removing wet-chemically the InP substrate, and an sacrificial etch stop layer, the InP membrane is obtained. Its backside is now exposed and can be further processed to finalize the actual photonic structures. The IMOS platform uses this possibility of double side processing, which offers a promising approach to connect the photonic layer with underlying structures, like electronic circuits, by using through polymer viass (TPVs).

The generic foundries, Smart Photonics and HHI, also process their PICs within a grown epitaxial layer stack on top of an InP substrate. The approach of bonding this layer on a new carrier wafer is possible. To enable this approach a few adaptations have to be made to enable the wet-chemical removal of the substrate and to guarantee the performance of all BBs. The membrane that will remain is up to 10  $\mu$ m thick, which is 20 times the thickness of an IMOS-membrane.

In this chapter the integration concept is introduced by explaining the different design considerations. First the general design flow is explained followed by sections, concentrating on specific design aspects: electrical, thermal and optical. At the end of this chapter the integration concept is explained including a compact description of the intended realization. In the following the photonic wafer material refers to the HHI generic foundry, which provided all the InP wafer used in this work.

## 2.1 Design flow

Creating photonic and electronic integrated circuits (ICs), using mature foundry processes, starts with the design. The software used for designing these ICs is quite different as each material system focuses on technology specific simulations and design values. They are developed by different industries, which do not have a direct overlap in applications. Each foundry provides access to its designer through an intellectual property (IP) protected process design kit (PDK). At the moment, there is no combined PDK for the used photonics and electronic platforms. Thus, there is no software to simulate and design a complete hybrid device, which induces difficulties for efficient co-design. Fortunately the mask file format "graphic design system II (GDSII)" is used in both electronic and photonic industries. This offers the opportunity to align wafer layouts by matching them on the GDSII level.

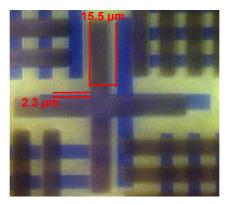

The wafer dimensions used in the photonic and electronic fabrication do not match in size. Standard InP-wafers are available with a diameter of 50.8, 76.2 and 100 mm (2, 3 and 4 inch), while bipolar CMOS (BiCMOS)-wafers are normally 200 or 300 mm across. In this work a diameter of 76.2 mm for the photonic and 200 mm for electronic wafer are used, which are defined by the corresponding foundry. Within the NanoLab facilities at TU/e process tools are limited to 3 inch. Therefore 200 mm BiCMOS wafer has to be diced into several 3 inch wafers. The electronic material comes from a mutli project wafer (MPW) run. Such a wafer has one fundamental cell, called a reticle, which is repeated over the wafer with a constant pitch. This reticle contains designs of various projects and from multiple designers, who share the available area. With this approach the manufacturer can fabricate on one wafer a number of submitted designs. To increase the amount of produced circuits for each design, several identical wafers can be fabricated. This is cheaper than the fabrication of a dedicated wafer run for each designer, as high costs are connected with the lithography mask sets. However, this means that the influence a designer has on the BiCMOS wafer layout is rather limited. Due to the number of participants, each designer obtains only a small design area within the **BiCMOS** reticle.

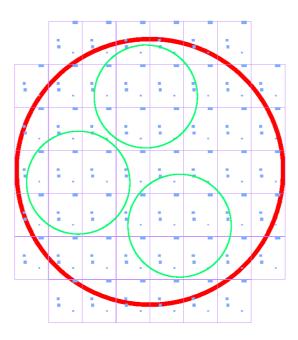

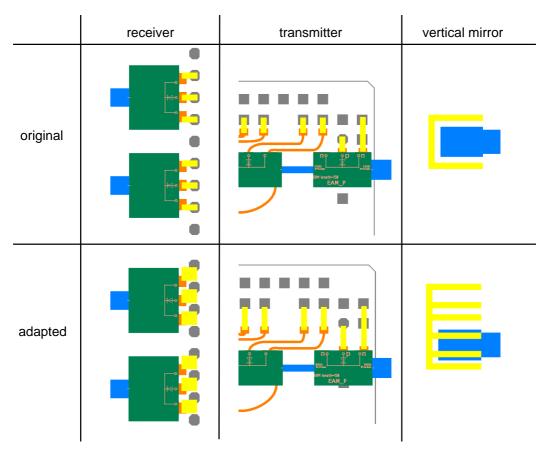

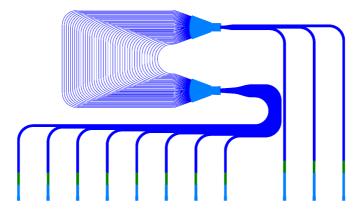

To demonstrate and test the wafer-scale integration technology a transmitter (TX) [21,22] and receiver (RX) [23,24] circuit are designed for the electronic MPW run , as well as an electronic interconnect test cell. These three different cells are designed by research partners<sup>1</sup>. The GDSII files of these circuits are created by the designer. The remaining content of the BiCMOS reticle is not known. To design a matching InP wafer it is important to know the position of the electronic cells on the 200 mm BiCMOS wafer. This floorplan is a GDSII file which is not shared. To define the design positions within the 200 mm wafer the reticle grid is defined first by using the fundamental cell size, the reticle placement pitch in 2 perpendicular directions and the absolute positioning on the 200 mm wafer. Adding the TX, RX, and test cell layout files, at the relative positions within the reticle, which are provided by the foundry, leads to the reconstructed 200 mm wafer GDSII layout. A picture of this is presented in figure 2.1. Based on this layout the dicing of the 3 inch BiCMOS wafer can be defined, and only after this is done the design of the InP wafer layout can start.

Figure 2.1: Reconstructed GDSII of the 200 mm BiCMOS wafer (red circle) including the 3 inch cut-out positions (green circle)

A disadvantage of this approach is that the final design of the photonic wafer has to wait for the availability of the electronic floorplan, which extends the total design time. To reduce this effect the design process is divided into several sub tasks. First the co-design of the photonic and electronic cells is addressed. The electronic cell designs are then submitted to the foundry. Thereby a few boundary conditions have to be taken into account. The orientation of the electronic designs should be fixed, since it is related to the orientation of the photonic design. This is because, for technological reasons, several photonic building blocks (BB) have to be orientated in the same direction over the InP wafer. Examples are the active BBs, like the distributed feedback (DFB) laser, the electro-absorption modulator (EAM) and the

<sup>&</sup>lt;sup>1</sup>Gertjan Coudyzer, University of Ghent; Xi Zhang, IC group TU/e, now with NXP Semiconductor

PIN-photodiode (PD). These all have to be orientated perpendicular to the major wafer flat. Furthermore, the minimal distance between the cells is defined by the size mismatch of the photonic and electronic cell design. This is because the photonic design is larger, due to the presence of spot size converters (SSCs). Therefore it is important that the designed electronic cells are placed with sufficient distance to compensate for this footprint mismatch. Both of these boundary conditions are taken into account by the electronic foundry.

With the reconstructed 200 mm floorplan the 3 inch cut outs are planned carefully, according to the following conditions:

- 1. all obtained 3 inch wafers should be identical

- 2. the number of our design cells included is maximized

- 3. an equal amount of the different designs is preferred

- 4. the designs are aligned towards further processing

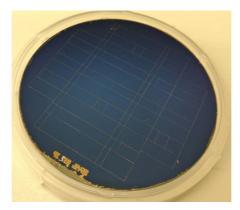

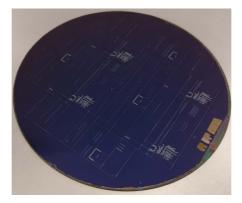

The first condition is used to ensure that only one photonic wafer has to be designed, and therefore reduces the required design time. For each wafer a matching photonic wafer has to be created, which requires a set of optical masks. By using identical wafers only one mask set is needed, resulting in a reduction of costs. Based on this first condition the total number of 3 inch wafers is limited to three. The second and third point aim at a maximum yield for the three different designs. The last condition refers to process related limitations. The equipment that is used requires alignment markers within certain position windows. These markers are part of the designed cells itself and have to align towards the requirements of the processing tool. A more detailed explanation will be given in section 3.3. The cutting of the wafers is done with laser dicing. Subsequent grinding of the wafer edges is applied to remove the debris resulting from the laser cut<sup>1</sup>.

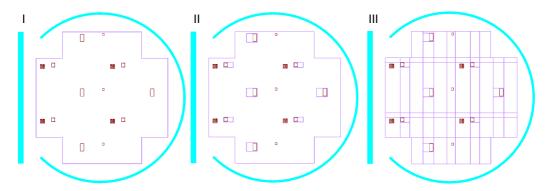

Figure 2.2: Cell definition process starting with (I) the 3 inch wafer surface including the actual design area (cross) and the electronic ICs, (II) defining the final hybrid module dimensions, (III) dividing the remaining area in groups of cells

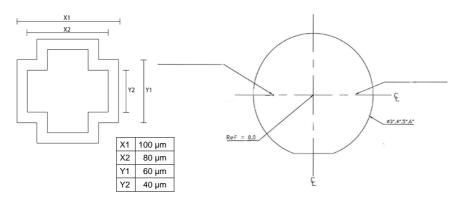

Regarding the InP wafer the next task is to define the design area and the cell division. For this special dicing lanes are defined, their functionality will be explained in section 2.4. In figure 2.2 the different steps for placing these lanes are presented. In the left figure the outside of

<sup>&</sup>lt;sup>1</sup>This task was outsourced to Philips Innovation Lab

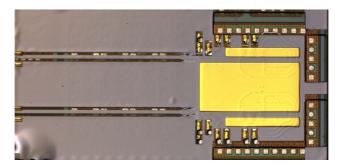

the 3 inch InP wafer is drawn in blue. It is aligned towards the 3 inch cut out from the 200 mm BiCMOS wafer, which defines the position of the included electronic cells (brown). The outline of the effectively usable InP design area, which has the shape of a cross, is also shown. This cross is predefined by the HHI foundry. It is 60 mm wide and equally high. The outline of the cross is part of the dicing lane definition. The centre figure shows the design, including the frames of the photonic cells of the transmitter and receiver designs. These boxes are predefined by the co-designed cell definitions. Based on these initial lines, the rest of the wafer is divided. The final result of this design process is shown in figure 2.2 (III).

The wafer is divided in cells of various sizes. The amount of different cells has been minimised as much as possible, thereby enabling repetition of each type. This concept has the advantage that each design is created several times at different positions on the wafer. Therefore the influence of local defects on the wafer is minimised. The approach of dividing the InP design area into groups of various cells sizes is chosen to gain the maximum design area. It also enables a minimum size of the final hybrid modules.

To make the best use of the remaining surface of the InP-wafer, the rest of the design space is filled with photonic test cells, alignment markers and additional functionalities. The test cells are used to characterize the different photonic BBs, which will be further explained in chapter 4. After finishing this design it is submitted to HHI for processing. Finally the post processing masks need to be designed, which are used for processing after receiving the foundry wafers. The post processing will be described in chapter 3.

## 2.2 Electronic design considerations

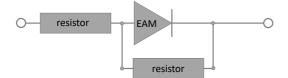

Usually photonic and electronic modules are designed independently and rely on a standardized impedance to transfer high frequency signals across interfaces. The standard value is based on a patent from 1929 from Lloyd Espenschied and Hermann Affel describing the coaxial cable [25]. The value is chosen to be 50 Ohm, which is a trade-off between the maximum power handling capability within the coaxial cable (at 30 Ohm) and the minimum attenuation (at 77.5 Ohm) [26]. This traditional value however doesn't ensure the best impedance for photonic-electronic co-design. Several publications present InP structures that rely on termination resistance [27, 28] to diminish RF reflections and optimize performance, but this leads effectively to an increase of the total energy consumption.

Co-design interface optimization is a key opportunity to create more power efficient devices. Within this work two InP building blocks rely on electrical high frequency input or output signals: the EAM within the TX design and the high speed PIN- PD, which is the heart of the RX design. To minimize the power consumption the interface impedance between the electronic ICs and these photonic BBs is optimized. The BBs are electrically represented by equivalent circuit models, which are provided by the InP foundry. Applying impedance matching to these models reduces reflections without using termination resistances on the InP membrane. This consequently translates into an improved power consumption of the hybrid modules. This concept assumes that the influence of the electrical interconnects itself is either negligible, or can be included in the model. Which of these two options is valid depends on the design choice made on how to integrate the two circuits.

In general two possible concepts are applicable. The first one relies on placing the matching photonic and electronic circuits directly on top of each other, enabling perpendicular TPVs. This results in very short interconnects. Their length is mostly defined by the polymer layer thickness itself. The second approach uses a metal routing layer between the two circuits, if

they are placed with an lateral offset with respect to each other. The routing could for example be realized within an intermediate polymer layer. The flexibility that this gives for connecting designs which are not pre-aligned on the two wafers can speed up the design and fabrication process, as each wafer can be designed and processed independently. The disadvantage is however that the interconnects can become extremely long. This might be compensated with high frequency transmission lines within the routing layer, to avoid bandwidth degradation and prevent reflections. Nevertheless, the fabrication seems challenging. This approach seems to be too complex and should be avoided. The new 3D integration technology that is presented here is aiming at techniques that lead to a manageable fabrication process. Therefore the first approach (short interconnects between aligned designs) is chosen for further investigation.

Placing the corresponding high frequency metal pads on the two wafers relatively close to each other creates short interconnects. The realization developed in this work relies on a small lateral shift of the pads, in the order of the polymer layer thickness. The interconnect length is then approximately  $\sqrt{2}$  times the polymer layer thickness. This offset is needed in the processing and will be further explained in chapter 3. However, the interconnect is still very short, despite the offset. Its performance is simulated and the results are presented in [21]. To verify the performance of the interconnect a test cell is included<sup>1</sup>, the results of which are presented in section 5.1. The simulated properties of the interconnects and the equivalent circuits of the InP BBs are used to optimize the BiCMOS ICs.

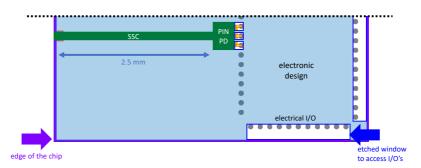

To enable a compact hybrid module assembly within a standard electronic package requires electrical control interfaces via the BiCMOS side. The InP circuit is therefore completely controlled through the electronic IC. All external interfaces are placed on the edges of the BiCMOS chips. A main advantage of this approach is the possible usage of several independent metal layers, which enables efficient signal routing and line crossings. Additionally it offers RF transition lines, which can be fabricated with a high precision. Within this work two full design

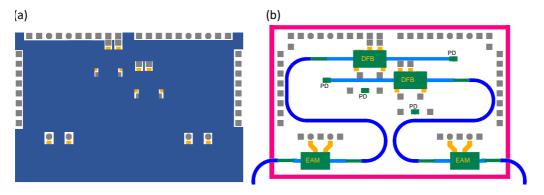

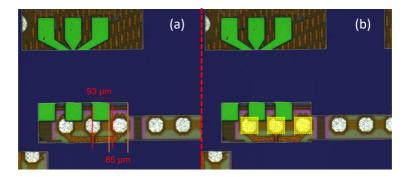

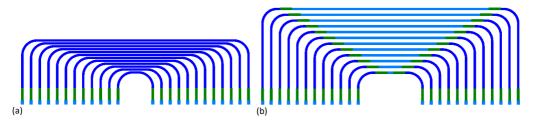

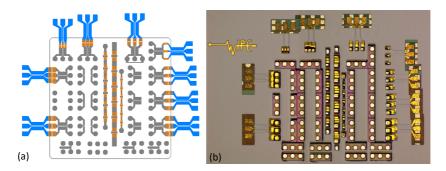

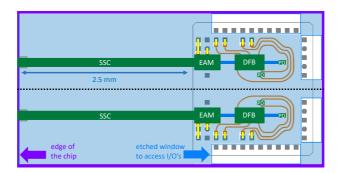

Figure 2.3: Top view of the TX design from the second generation; (a) with the InP membrane in blue, sealing most of the area, (b) with a transparent photonic membrane to identify the different BB

cycles have been completed, each including a transmitter and receiver circuit. The second generation constitutes a progression with respect to the first one. In figure 2.3 a schematic top view of the 2nd TX generation design is show. In (a) the InP membrane (blue) is covering most of the hybrid module area, thus representing the final appearance; (b) shows the actual design embedded in the photonic layer. The metal contact pads are represented in orange for the

<sup>&</sup>lt;sup>1</sup>Design by Xi Zhang (BiCMOS) and Arezou Meighan (InP)

photonic layer and in silver for the electronic one. The pads along the three edges (left, top, right) of the chip are intended to be used as external probing interface. The pads within the design area are used for connecting the electronic and photonic wafer. The shown schematic represents a dual channel design, which is based on two nearly identical designs. Only three sides of the electronics are used for external electrical interfacing as the remaining side is reserved for optical fibre coupling. The electrical pads placed at the top are used for high frequency and direct current (DC) signals, while the other pads are used for DC only. These general design principles are the same for the TX and RX designs of both generations.

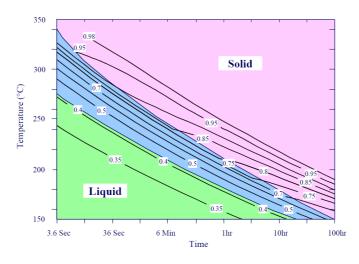

## 2.3 Thermal design considerations

In active photonic components heat is generated due to mechanisms like joule heating, non-radiative recombination, reabsorption of radiation and mirror absorption [29]. Depending on the amount of heat generated and its flow, the device temperature increases. This can lead to performance penalties, device degradation or even complete destruction. To avoid this, it is important to optimize the heat flow by adding passive or active cooling elements and/or by limiting the heat generation. For example in a gain section this could be achieved by reducing the pump current. The InP and BiCMOS wafer both include active

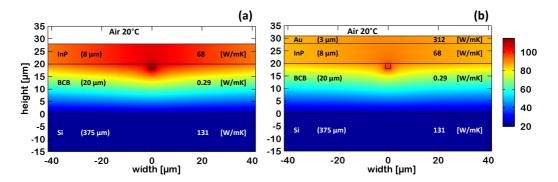

Figure 2.4: Colour coded temperature map resulting of the two dimensional thermal simulation of the envisioned structure without (a) and with (b) gold heat spreader, including the thermal conductivity values for the different materials and the thickness used

components that dissipate heat. These wafers are separated by the intermediate bonding polymer, which has a relatively low thermal conductivity. Commercially available software is used to simulate the heat flow within a simplified 2D cross section.

In figure 2.4 (a) a fraction of the simulation environment is presented. The interfaces of the different materials are displayed with black lines. The colour code represents the temperature at stationary condition. In this simulation the electronic wafer is at the bottom and thermally represented with a 375  $\mu$ m thick silicon layer. On top of it is a 20  $\mu$ m thick bonding polymer layer followed by an InP layer of 8  $\mu$ m, representing the photonic membrane. The simulation area is 500  $\mu$ m wide and is restricted to the sides with an isolating boundary condition. The bottom of the Si wafer is attached to an ideal heat sink with a fixed temperature of 20 °C. The topside of the InP wafer is surrounded by air with a temperature of 20 °C resulting in convective heat flux (5 W/m<sup>2</sup>K).

In the centre of figure 2.4 (a) a 2-by-2  $\mu$ m wide InP waveguide is placed, connected with the membrane on top and surrounded by the polymer layer. This waveguide is used to represent a laser structure, which is the only heat source for this simulation. The dissipated heat for the laser is calculated from the electrical input power of 175 mW (50 mA, 3.5 V) reduced by the emitted optical power of 5 mW, resulting in 170 mW. This value has to be divided by the total laser length of 420  $\mu$ m to determine the heat dissipated per unit length, which is used in 2D. The thermal conductivity values which have been used are given in figure 2.4. For InP and Si the numbers are taken form the software data base. The polymer used is benzocyclobutene (BCB), for which thermal conductivity is given by the supplier [30]. It can be seen that the value for BCB is more than 200 times smaller than for InP. The dimensions used are representative for the envisioned structure. In figure 2.4 (a) it can be seen that the temperature in the laser structure rises to a maximum value of 112 °C. Because of the thick polymer layer the heat flux through the silicon wafer is reduced dramatically and the heat flux at the surface is limited. A possibility to improve the heat sinking is an increase of the lateral heat spreading, and therefore to enlarge the surface used for this convective heat flux.

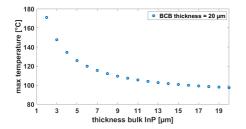

Figure 2.5: Simulated maximum temperature within the InP membrane for different InP layer thickness

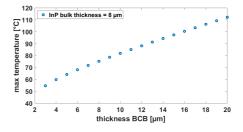

Figure 2.6: Simulated maximum temperature within the InP membrane for different BCB layer thickness

Because of the substrate removal the InP material is thinned down and lateral heat spreading within the membrane is limited. This can be seen by simulating the maximum temperature in the InP laser structure as a function of the InP membrane thickness. The resulting graph is presented in figure 2.5. The thicker the membrane is, the lower the temperature. However, for large layer thickness this effect is limited by the thermal conductivity of the material itself. As the membrane thickness is predefined by the foundry an alternative method is proposed to increase the lateral heat spreading. It relies on metal structures, which are created on the backside of the InP membrane. This can be fabricated as part of the electrical interconnection step (described in section 3.6). The resulting metal structures are  $2-4 \mu$ m thick. A comparison of a structure with and without metal heat spreader is presented in figure 2.4 (a) and (b) respectively. The maximum temperature is reduced by 13 °C with a 3  $\mu$ m thick and 250  $\mu$ m wide gold structure. Beside this property of spreading the heat the metal can also be used as an interface for a passive or active cooling element to reduce the temperature even further.

The intermediate polymer can thermally isolate the photonic from the electronic wafer, depending on its thickness. In figure 2.6 the maximum temperature within the simulated InP laser is plotted as a function of the BCB thickness. Because of the poor heat flux towards air the temperature is increasing nearly linearly with polymer thickness. For the envisioned process an intermediate BCB layer of 20  $\mu$ m is anticipated, which is needed to enable the adhesive wafer bonding (see section 3.3).

The actual structure will have heat sources both in the PIC and the EIC. The intermediate bonding polymer reduces the thermal crosstalk between these two circuits. However, isolating the two sides means that each one has to have a sufficient heat sinking on its own, to reduce temperature increase. While the electronic ICs will work up to a temperature of 150 °C, the photonic circuits requires stable values to operate at the target wavelength.

The refractive index of InP is temperature depended [31], which influences all BBs, especially the arrayed waveguide gratings (AWGs). Another example is the temperature dependency of the DFB emission wavelength, which changes roughly with 1 nm per 10  $^{\circ}$ C [32].

Heat generation in the photonic membrane can also be used to control these BBs. A heating element is included into the DFB BB to manipulate the temperature, and therefore shift the wavelength. The aspect of using heat for controlling BBs has not been further investigated here.

To determine the actual temperature in the photonic membrane the dark current of a photodiode can be used. The temperature dependency [33] has to be characterized beforehand by heating the sample and measuring at steady state condition the resulting dark current. Also the wavelength shift of the DFB laser can be used to determine the temperature.

It is important to extract sufficient heat from the membrane to enable operating devices. For the hybrid module double side cooling is envisioned. That means both the electronic and photonic circuits will be cooled separately by adding passive or active cooling elements. The actual development of the thermal packaging was beyond the scope of this work. The alternative would be to cool both circuits simultaneously from the BiCMOS-side, which would require a heat flow through the bonding polymer. This could be achieved by designing the placement of thermal vias.

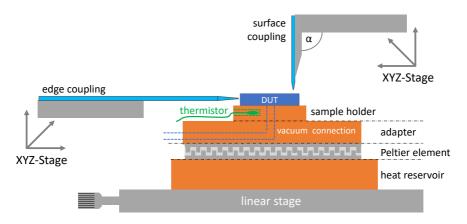

## 2.4 Optical design consideration

Emitting and receiving optical signals with the hybrid modules requires optical interfaces to couple light into (and from) a single mode fiber (SMF). The requirements for such an interface are: low coupling loss, polarization independence, robust and stable fixture, tolerant alignment, no reflection and minimal influence on the transmitted signal itself. Optical interfaces can be divided in two groups, based on the coupling scheme: edge and surface coupling. Both have their advantages and disadvantages and will be used within this work. For the monitoring of the process surface coupler are used to enable wafer level measurements. Edge coupling is the selected option for the hydride modules as it is intended to package them into standard housing solutions.

Edge coupling requires smooth facets, which are normally created when cleaving the InP wafer along its crystal planes into bars and subsequently into single chips. This approach is not applicable for the combined layer stack of InP and BiCMOS.

The here proposed solution consist of two steps: first the InP facets are created when etching the dicing lines into the InP-wafer, before bonding. These will be filled with the adhesive polymer. After bonding, followed by substrate and etch stop layer removal, the lines are accessible. The second step is sawing along these lines to separate the modules. Thereby most of the polymer is removed, while a few micrometre thick layer is left in front of the InP facets. The polymer facet resulting after sawing is not smooth and includes some debris. This will induce some scattering . Based on the relatively small refractive index difference between polymer and air this scattering effect will be reduced, as compared to a similar rough InP air interface. Nevertheless, it would be best to remove the polymer completely, leaving the

undamaged smooth InP facet for optical coupling.

The coupling efficiency between the photonic chip and the glass fibre depends on the optical mode matching and their alignment. Using identical modes shapes and sizes the coupling will be defined solely by the alignment. The coupling efficiency is calculated with the mode overlap integral. If they are perfectly aligned and no reflections are present its value is 1. If the two modes vary in size or shape the value is smaller, which translates to coupling loss. For optical transmission SMFs are used which have an outer diameter of 125  $\mu$ m. These have a round core with a diameter of 9  $\mu$ m, surrounded by a cladding material with a slightly lower refractive index. The mode guided within this fibre is circularly shaped and has a mode field diameter of round 10  $\mu$ m. On chip level the used modes are not circular, and have mode field diameters of 1 to 2  $\mu$ m. Coupling a SMF directly to a standard InP waveguide mode therefore induces large coupling loss, mainly due to the mode size mismatch. There are special fibres using an ultra high numerical apperature (UHNA), which have a reduce mode field diameter, down to 4  $\mu$ m, which is however still too large for efficient coupling. Therefore it is necessary to increase the mode diameter on chip. The BB that achieves this is called a sport size converter (SSC). These are foundry specific BBs which expand the mode diameter to match SMF or UHNA fibres as closely as possible. The increased mode size on the chip has the additional advantage that the polymer facet roughness has a reduced influence.

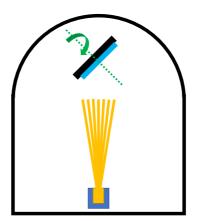

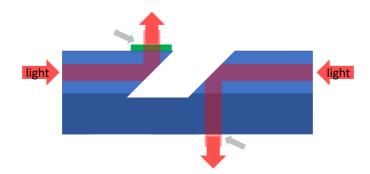

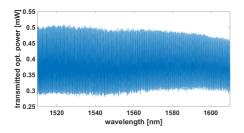

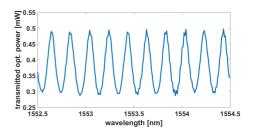

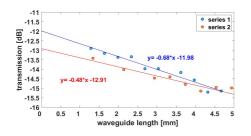

A disadvantage of edge coupling, however, is the fact that it is not possible to use it before separating the wafer into single chips. Therefore one can not monitor the behaviour of photonic devices during the process. It is important to guarantee the operation of the two foundry wafers before starting the bonding process, and to monitor changes during it. For the electronic circuits this can be realized with electrical probing and measuring the characteristic properties. The photonic wafer on the other hand needs additionally optical probing to verify its performance. Coupling light into the devices on wafer level can be achieved by using surface couplers. HHI developed a special BB, the vertical mirror, applicable for this purpose. It is a facet etched into the membrane under an angle close to 45  $^{\circ}$  with the surface of the membrane. This facet acts like a mirror, due to total internal reflection, directing the light perpendicular out of the wafer surface (or conversely, allow light to couple in). This enables monitoring of the photonic circuits before and after bonding. More details about that BB are given in section 4.1.1.

## 2.5 Integration Concept

The research presented in this work is intended to create a new hybrid platform, which enables short electrical interconnects between the photonic and electronic domain to increase the bandwidth and reduce the power consumption of the resulting modules. Additionally the target here is to develop a technology based on robust wafer scale fabrication processes, using state-of-the-art materials and devices.

The technology is intended to be adapted towards different photonic and electronic foundries. It can be divided in six steps: design, wafer bonding, substrate removal, opening electrical interfaces, creating interconnects and a back-end process. The design flow is presented in section 2.1.

#### Wafer bonding:

The physical integration starts after obtaining the two co-designed wafers from the foundries. Bonding two wafers to each other is a well-known concept and several different techniques have already been developed. In [34] the existing bonding techniques are summarized as: direct bonding, anodic bonding, solder bonding, eutectic bonding, thermo-compression bonding, direct metal-to-metal bonding, ultrasonic bonding, low-temperature melting glass bonding and adhesive bonding. This list shows the variety of approaches. A few boundary conditions have to be considered when choosing a suitable concept for our case.

The two materials that are bonded, InP and BiCMOS, have to form a stable bond to enable post processing. After bonding several steps are needed to create a functioning module. The bond has to sustain these without severely limiting the process. Additionally, each of the two wafers should operate without influencing the other, therefore optical, electromagnetic and thermal decoupling of both materials is necessary. The bonding technique needs to support patterned surfaces, as both wafers incorporate several microns of topology. All these requirements are fulfilled best by adhesive bonding, when using an appropriate intermediate material.

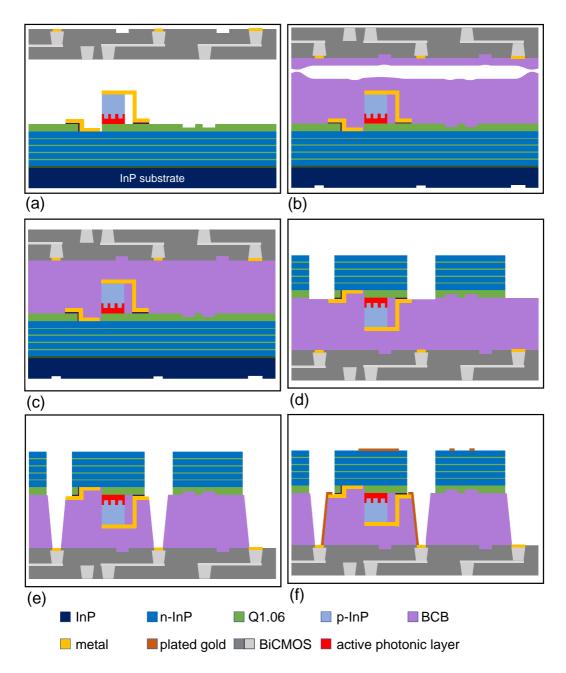

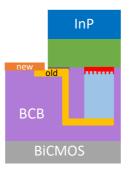

The IMOS technology uses such an adhesive wafer bonding. It relies on the fact that both wafer surfaces have a negligible topology. Replacing the silicon wafer with a BiCMOS wafer already changes this. Using generic InP material instead of IMOS increases the topology even more dramatically. Mimicking the initial assumption of bonding flat surfaces, the adhesive polymer is used to planarize the wafers before bonding them. In figure 2.7 a schematic is presented showing the 3D integration approach. The starting point in the figure 2.7 (a) shows the InP wafer (bottom) and BiCMOS wafer (top), both facing upwards. The topology derives from the BBs fabricated within the epitaxial layers. The second figure (b) shows the electronic wafer flipped and aligned with respect to the electronic wafer, where both surfaces are planarized with polymer to cover the existing topology. After bonding the two wafers (figure 2.7 (c)) the polymer provides mechanical stability for the assembly throughout the subsequent processing. It also provides isolation between the two wafers.

#### Substrate removal:

To enable electrical interconnects between the photonic and electronic circuits it is needed to etch through one of the wafers. The InP wafer is chosen for this. This is because etching through the BiCMOS wafer is highly impracticable, due to the many metal layers present there. Preparing for further processing requires thinning of the InP material. By removing the substrate the photonic wafer is reduced to its epitaxial layer stack. While the substrate is not required for the functionality of the photonic circuits, it does provide mechanical stability. During the bonding process both wafers are heated, glued and cooled down again. As the coefficients of linear thermal expansion (CTEs) for InP and Si are different, the mechanical fixation at high temperatures, by cross-linking of the polymer, is followed by an unequal material shrinking, which creates strain. This can be determined by measuring the bow of the combined wafer stack after bonding. This warping however is reduced due to the substrate removal. As the InP material becomes thinner, it becomes more flexible and can adjust better to the BiCMOS-wafer, which is a positive effect of the substrate removal.

#### **Opening electrical interfaces:**

The bonded assembly is constructed further by opening the InP membrane locally to access the underlying electrical pads. In figure 2.7 (d) the schematic cross section is presented. It is flipped so that the photonic membrane is on top and facing down. The schematic shows the

Figure 2.7: Schematic of the process flow; (a) starting point, InP wafer at the bottom, BiCMOS wafer at the top, both facing upwards; (b) pre-bonding, both wafers aligned and facing each other, topology is planarized with adhesive polymer; (c) bonded wafer stack; (d) flipped assembly, InP substrate removed, photonic membrane opened; (e) opening of the polymer layer; (f) realization of the electrical interconnects with electroplating

assembly after substrate removal and subsequent opening of the InP windows. The InP metal contact pads are accessible immediately after etching through the InP layer stack, while the BiCMOS metal pads are opened subsequently, by etching through the polymer resulting in the cross-section presented in figure 2.7 (e).

#### Creating interconnects:

In the last step the interconnects are created with electroplating. All electrical contacting of the final module will be realized through the BiCMOS. The benefit of this is that all contacting pads, including those for the active photonic devices, can be placed at the edge of the chips. The routing through BiCMOS is very efficient, as several metal layers are available for this purpose, which for example enables electrical line crossings. Additionally, the process is highly reproducible; each signal line and its interaction can be simulated with standard design software, resulting in accurate RF lines wherever they are needed. Finally, use can be made of well-developed contacting techniques to connect the modules electrically to the outside world. The electronic and photonic layers are connected with electro-plated gold interconnects. A schematic is presented in figure 2.7 (f). This also shows additional metal depositions on the backside of the InP membrane. These are intended as heat spreaders and heat transfer contact to be used for cooling the photonic membrane. At this point the wafer process is complete and a separation into modules has to be achieved.

#### Back-end process:

InP wafers are normally cleaved along crystal planes of the wafer. The BiCMOS wafer is normally sawed along dicing lanes, since cleaving of Si is not a reliable process. The process of sawing however constitutes a high risk of damaging the InP membrane. Especially the roughness due to sawing on the InP facets would be unacceptable for coupling light.

In section 2.4 the two-step approach has been introduced. First pre-dicing lanes in the InP wafer are defined by etching deep trenches into the membrane before bonding. These dicing lanes are 50  $\mu$ m wide and separate the different InP cell designs. This etching process is performed by HHI and provides good quality facets to the InP waveguides. After bonding and removing the substrate these lanes become visible. They are sealed with polymer used during the wafer bonding process. The stacked wafer can then be separated by sawing the BiCMOS wafer along the predefined dicing lanes, through the BCB. The sawing blade has a width of 30  $\mu$ m, so with careful positioning it leaves some of polymer on each InP facet. Ideally this layer would be removed afterwards, however that has not been realized within this work.

#### 2.6 Conclusion

In this chapter the 3D-integration concept has been presented, giving an general overview of the different challenges engaged in this work. A method to co-design the PICs and EICs is reported using the GDSII files. The used design flow on how to create matching wafers is given, followed by an introduction for the electrical, thermal and optical design considerations. The process flow, including wafer bonding, substrate removal, opening electrical interfaces, creating interconnects and a back-end process, has been introduced. In the following chapter the creation of the hybrid modules is given thereby describing the created technology platform.

# Chapter 3

# Technology

The III-V cleanroom from Nanolab@TU/e is well equipped and offers all necessary tools to process photonic devices. Years of research have resulted in reliable processes and tool expertise for InP PIC fabrication. The possibility of integrating photonics and electronics is proposed for the IMOS platform. A short description is given in chapter 2. An integration of InP photonics with CMOS based electronics has however not yet been demonstrated. Up to now IMOS has used bare silicon wafers as carriers instead of CMOS, having comparable mechanical and thermal properties.

In this chapter a new integration technology is presented to integrate generic InP single project wafers provided by HHI with BiCMOS MPWs provide by NXP. Each wafer itself is highly valuable and the fact that both the electronic and photonic wafer are co-designed increases this value even more. Therefore it is decided to rely on known processes as much as possible, to reduce the risk. Fabrication approaches from the IMOS platform are the starting point for the development of the integration technology, but are adapted towards new requirements. It is important to create a reliable integration technology with an optimized risk management. In the following the process flow is presented, highlighting technology based decisions.

## 3.1 Foundry Requirements

The materials used for the realization of integrated photonics and electronics are provided by HHI and NXP Semiconductor, respectively. As mentioned in section 2.5 our goal is to create a process that can make use of different foundry providers. To enable such an integration process a few changes have to be introduced to the foundry supplied wafers.

The electronics is based on a 200 mm silicon wafer and is created in a 0.25  $\mu$ m SiGe:C BiCMOS process. The wafer is thinned down to a total thickness of 375  $\mu$ m. This is more than the regular 200  $\mu$ m in order to keep a safe minimum thickness for handling. The BiCMOS wafer doesn't need any further adaptations.

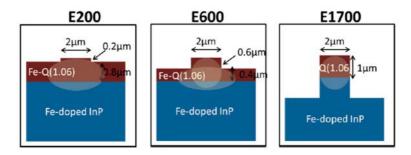

The photonic material is fabricated on a 3 inch InP wafer. Integrating both wafers is done by using adhesive wafer bonding. For the hybrid module only the processed epitaxial layer stack of the InP wafer is required. This membrane can be obtained after the bonding of the two wafers by removing subsequently the InP substrate and a sacrificial etch stop layer. This etch

stop layer has to be added by the foundry below its standard layer stack. Additionally a few of the InP BBs might need to be adapted, because the resulting structures will have no InP substrate any more, which may change optical, electrical and/or thermal properties of the devices. One of the affected BBs is the SSC. It is used to couple light efficiently from the edges of the photonic membrane into a SMF, and vice versa. For this a diluted waveguide is used, which is placed below the rest of the InP layer stack. The SSC BB is designed to enable adiabatic coupling between the standard and the diluted waveguide. The latter has an effective refractive index close to that of the InP substrate. Therefore the optical mode can partly expand into this substrate. Without it, the diluted waveguide has an air cladding. In that case the refractive index contrast is increased substantially and the optical mode is more confined within the diluted waveguide, which results in an overall smaller mode size. This leads to higher optical coupling losses between chip and SMF. It has been verified that the BB will function also without the substrate<sup>1</sup>. Nevertheless, the mode diameter will be smaller than with the substrate. Alternatively, it is possible to replace this BB with one based on a different approach. A concept, that has been thought of, uses the bonding layer to create an optical waveguide structure, with a mode field diameter matching a standard SMF. For the remaining BBs no adaptations are implemented. The standard HHI PDK is used, complemented by EAMs based on aluminium containing quaternary material.

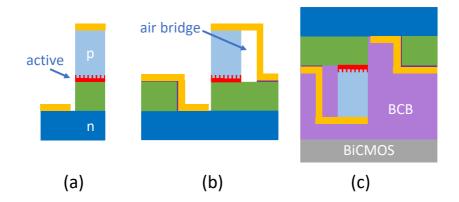

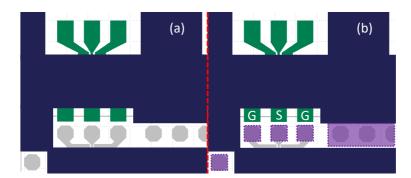

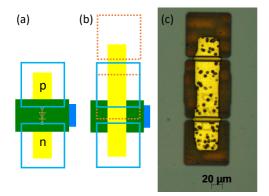

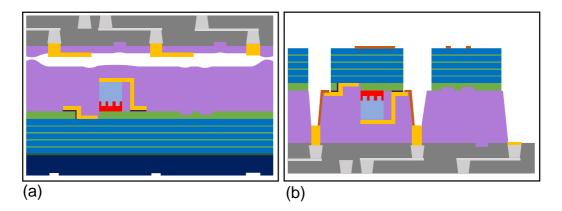

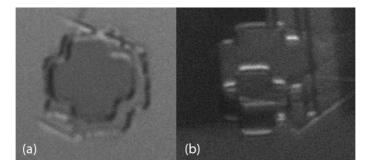

Figure 3.1: Schematic cross section of a DFB laser (a), with extended metal routing (b) and after flipping and bonding (c)

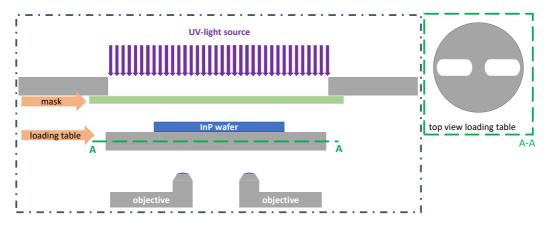

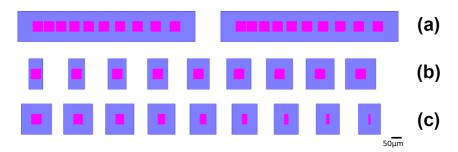

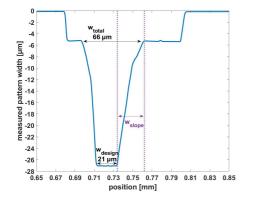

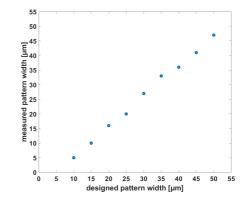

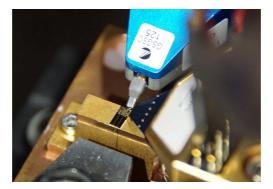

To integrate the photonic membrane with the electronic wafer, post processing is needed. This requires marker structures, which are used after bonding to align the post processing masks. It is decided to etch marker structures through the entire functional InP layer stack and into the etch stop layer. In that way the markers will become visible after removing the substrate and the etch stop layer. The same etching step is also used to create dicing lanes. These fulfil two basic functions. First, they provide separation of the InP cells, as needed in the final creation of hybrid modules from the bonded wafer. Second, the resulting facets form the optical coupling interfaces. It is important that this etch goes all the way through the InP membrane and stops inside the etch stop layer. If the etch is too shallow the marker structures and dicing lanes will not be opened. On the other hand, if the etch is through the etch stop layer the wet chemical etchant for substrate removal will damage the InP membrane. HHI creates these structures by

<sup>&</sup>lt;sup>1</sup>This analysis has been done by HHI, contact Francisco Soares

using a dry etch step. While the etch rate is well controlled, the total layer stack thickness varies with foundry specific tolerances up to several percent. To compensate for this, it is important that the etch stop layer is thick enough. Thus the foundry has more tolerance on the etch depth, while guaranteeing not to etch into the substrate.

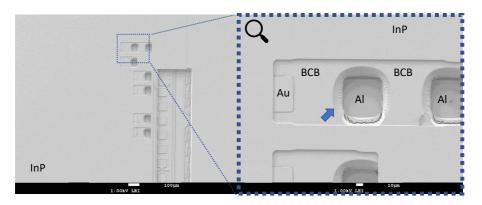

Part of the post processing is the creation of the electrical interconnects. This will be explained in section 3.6. To support this the foundry creates a single accessible contact layer. In figure 3.1 (a) a schematic of a DFB laser is presented. The semiconductor contacts of the laser are connected with metal tracks for current feeding. These are further routed to one common horizontal layer (b). This enables accessing the contacts after bonding (c) with a single etching step. As the routing creates some distance towards the actual devices, this reduces the risk of damaging them during the contact opening step. In Figure 3.1 (b) it is also visible that HHI uses an air-bridge in the metal routing. HHI normally fills the space below the air-bridge with polymer in one of the last fabrication steps. This step is skipped for our purpose, as it might create enclosed air bubbles, which would be detrimental for the hybrid integration process.

As this overview shows only a few limited, but necessary, adaptations have been made to the foundry platform and process. The fundamental structure of the PDK is not changed and no foundry specific knowledge is needed to fulfil the requirements for co-integration with an electronic wafer. Therefore every photonic foundry could in principle provide suitable material, which is one of the requirements itself.

#### 3.2 Wafer Preparation

The integration process starts, after receiving the wafers, by preparing them for the actual fabrication. The necessary steps to prepare the two wafers are presented in this section, starting with the electronic wafer.

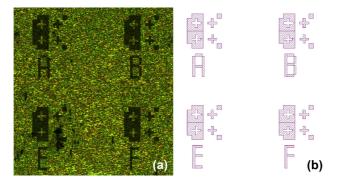

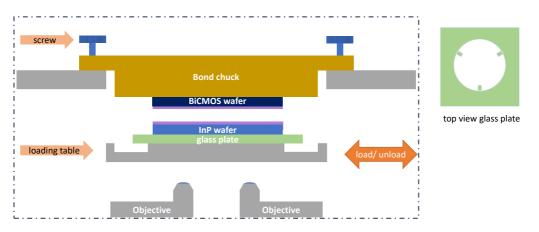

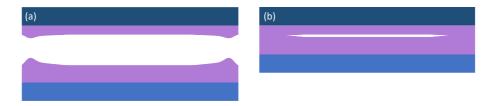

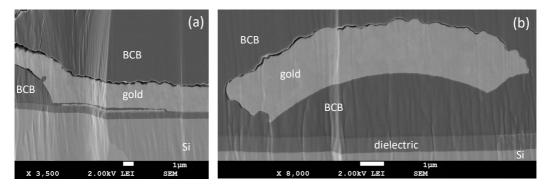

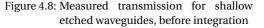

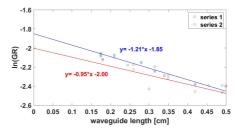

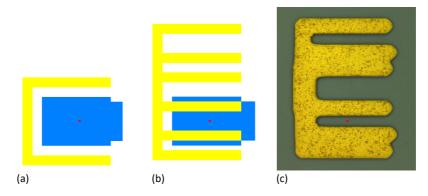

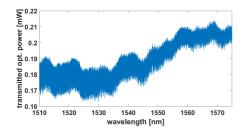

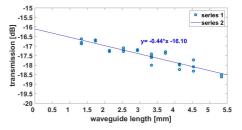

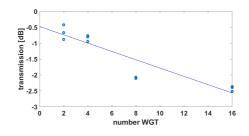

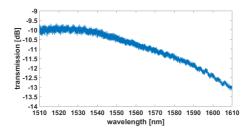

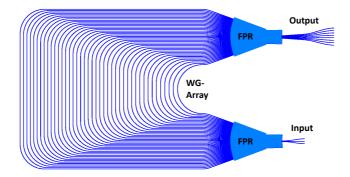

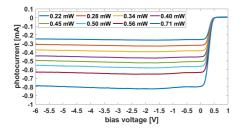

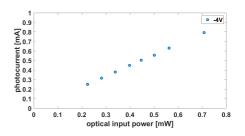

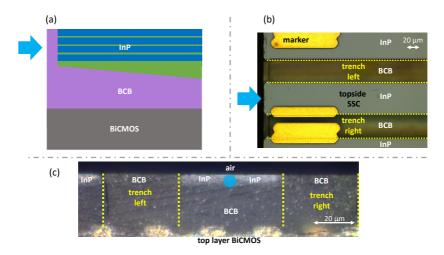

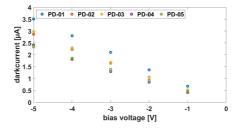

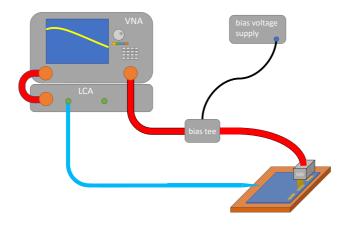

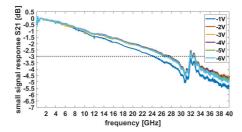

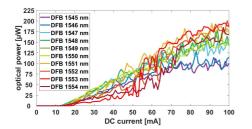

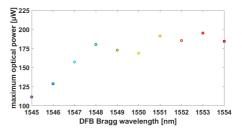

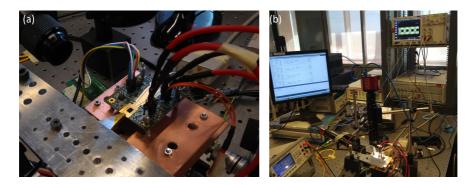

The 200 mm large BiCMOS wafer has to be cut into 3 inch wafers. This is performed with laser dicing, a process that releases a lot of heat at the cutting edge. The heat creates warping, leaving debris on the wafer edge, thus adding extra topology. To remove this unwanted material a grinding step is added. This reduces the wafer size, therefore it is important that the wafer is cut somewhat larger than the target size. Additionally, the removal of material leaves particles on the surface, which could affect the further process. To avoid this the 200 mm wafer is initially protected with a resist layer of sufficient thickness, which seals the actual surface and will be removed after the grinding step. The laser dicing and grinding is done by an external company.