#### Integrated circuits for wearable systems based on flexible electronics

Citation for published version (APA):

Zulqarnain, M. (2020). Integrated circuits for wearable systems based on flexible electronics. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven.

#### Document status and date:

Published: 02/12/2020

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 05. Oct. 2023

## Integrated Circuits for Wearable Systems based on Flexible Electronics

Mohammad Zulqarnain

The work in this thesis was carried out in the Integrated Circuits (IC) group of the

Department of Electrical Engineering at the Eindhoven University of Technology in

collaboration with imec-NL/Holst Centre under the framework of the project "In-

tegrated Circuits for Conformal Wearable Systems".

Integrated Circuits for Wearable Systems based on Flexible Electronics

by Mohammad Zulqarnain.

Eindhoven: Technische Universiteit Eindhoven, 2020. Proefschrift.

This thesis was typeset using LaTeX. Template adapted from Version 1.0

by Joos Buijs, Eindhoven, 2014.

Front cover: Photo by Solen Feyissa on Unsplash including main picture

by Mohammad Zulqarnain

Back cover: Photo by Ranurte on Unsplash

A catalogue record is available from the Eindhoven University of Technology

Library

ISBN: 978-90-386-5163-7

Copyright © 2020 by Mohammad Zulqarnain.

All Rights Reserved.

Reproduction in whole or in part is prohibited

without the written consent of the copyright owner.

# Integrated Circuits for Wearable Systems based on Flexible Electronics

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische

Universiteit Eindhoven, op gezag van de rector magnificus

prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het

College voor Promoties, in het openbaar te verdedigen op woensdag

2 december 2020 om 13:30 uur

door

Mohammad Zulqarnain

geboren te Aligarh, India

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. S.M. Heemstra de Groot

1<sup>e</sup> promotor: prof.dr.ir. E. Cantatore

$2^e$  promotor: dr. ir. P.J.A. Harpe

co-promotor: dr. M. Fattori

leden: prof.dr.ir. J. Genoe (KU Leuven)

prof.dr.ir. W. Dehaene (KU Leuven)

prof.dr.ir. M. Mischi

adviseur: dr. S. Stanzione (imec)

Het onderzoek of ontwerp dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

## Declaration concerning the TU/e Code of Scientific Conduct for the PhD thesis

I have read the TU/e Code of Scientific Conduct<sup>i</sup>.

I hereby declare that my PhD thesis has been carried out in accordance with the rules of the TU/e Code of Scientific Conduct

| <u>Date</u>                   |

|-------------------------------|

| 7 <sup>th</sup> October, 2020 |

| Name                          |

| Mohammad Zulqarnain           |

| Signature                     |

| Mohammed Kulgarnam            |

<sup>&</sup>lt;sup>i</sup> See: <a href="http://www.tue.nl/en/university/about-the-university/integrity/scientific-integrity/">http://www.tue.nl/en/university/about-the-university/integrity/scientific-integrity/</a>

The Netherlands Code of Conduct for Academic Practice of the VSNU can be found here also.

More information about scientific integrity is published on the websites of TU/e and VSNU

"Hum to mā.il-ba-karam haiñ koī saa.il hī nahīñ Raah dikhlā.eñ kise rah-rav-e-manzil hī nahīñ Koī qābil ho to hum shān-e-ka.ī dete haiñ Dhūñdne vāloñ ko duniyā bhī na.ī dete haiñ" — Allama Iqbal

[Behold, my hands are full of gifts, but no one comes seeking here,

And whom shall I show the right path, when there is no traveller,

On him who merits well, I bestow the brightest diadem,

And those who truly come questing, I unveil even a new world to them.]

### Contents

| 1 | Intr | oduction                                                    | 1  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | Introduction                                                | 2  |

|   |      | 1.1.1 Flexible electronic technologies                      | 3  |

|   |      | 1.1.2 Design challenges                                     | 5  |

|   |      | 1.1.3 Applications                                          | 7  |

|   |      | 1.1.4 State-of-the-art flexible wearable biomedical sensors | 7  |

|   | 1.2  | Problem statement                                           | 9  |

|   | 1.3  | Aim of the thesis                                           | 10 |

|   | 1.4  | Scope of the thesis                                         | 11 |

|   | 1.5  | Original contributions                                      | 11 |

|   | 1.6  | Outline of the thesis                                       | 13 |

| 2 | a-IG | ZO TFT Technology                                           | 21 |

|   | 2.1  | Introduction                                                | 22 |

|   | 2.2  | Device stack                                                | 22 |

|   | 2.3  | Etch stop layer TFT technology                              | 22 |

|   | 2.4  | Dual-gate self aligned TFT technology                       | 24 |

|   | 2.5  | Device channel current modelling                            | 25 |

|   |      | 2.5.1 ESL channel current modelling                         | 25 |

|   |      | 2.5.2 DUGA channel current modelling                        | 28 |

xii CONTENTS

|   | 2.6               | Device 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | noise modelling                                  | 29                                                 |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|

|   | 2.7               | Conclus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ions                                             | 30                                                 |

| 3 | Desi              | ign Trad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e-offs in a-IGZO TFT based Bio-signal Front-ends | 33                                                 |

|   | 3.1               | Introdu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ction                                            | 34                                                 |

|   | 3.2               | Design o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | constraints for bio-signal front-ends            | 35                                                 |

|   | 3.3               | Bio-sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | al front-end architectures                       | 37                                                 |

|   | 3.4               | Limitati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ons of a-IGZO TFT technology                     | 41                                                 |

|   | 3.5               | Bio-sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | al front-ends based on a-IGZO TFTs               | 43                                                 |

|   |                   | 3.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FE-I and FE-II                                   | 44                                                 |

|   |                   | 3.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FE-III                                           | 46                                                 |

|   |                   | 3.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FE-IV                                            | 46                                                 |

|   | 3.6               | Measure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ement results                                    | 47                                                 |

|   | 3.7               | Conclus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ions                                             | 54                                                 |

|   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |                                                    |

| 4 | A H               | eart-Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e Measurement Interface on a Flexible Foil       | 59                                                 |

| 4 | <b>A</b> Ho       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Measurement Interface on a Flexible Foil       |                                                    |

| 4 |                   | Introdu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  | 60                                                 |

| 4 | 4.1               | Introduc<br>Single s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ction                                            | 60<br>62                                           |

| 4 | 4.1               | Introduction Single state 4.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ction                                            | 60<br>62<br>62                                     |

| 4 | 4.1               | Introduc<br>Single s<br>4.2.1 1<br>4.2.2 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ction                                            | 60<br>62<br>62<br>65                               |

| 4 | 4.1<br>4.2        | Single s 4.2.1 d 4.2.2 d Heart-ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ction                                            | 60<br>62<br>62<br>65<br>67                         |

| 4 | 4.1<br>4.2        | Introduction Single state 4.2.1 delete 4.2.2 delete 4.3.1 state 4. | ction                                            | 60<br>62<br>62<br>65<br>67                         |

| 4 | 4.1<br>4.2        | Introduction Single state 4.2.1 depends 4.2.2 depends 4.3.1 state 4.3.1 state 4.3.2 depends 4.3.2 de | ction                                            | 60<br>62<br>62<br>65<br>67<br>67                   |

| 4 | 4.1<br>4.2        | Introduction Single state 4.2.1 depends of the state of t | ction                                            | 60<br>62<br>65<br>67<br>67<br>69<br>72             |

| 4 | 4.1<br>4.2<br>4.3 | Introduction Single state 4.2.1 depth 4.2.2 depth 4.3.1 state 4.3.2 depth 4.3.3 depth 4.3. | ction                                            | 60<br>62<br>62<br>65<br>67<br>67<br>69<br>72<br>78 |

| 4 | 4.1<br>4.2<br>4.3 | Introduct<br>Single s<br>4.2.1 1<br>4.2.2 0<br>Heart-ra<br>4.3.1 3<br>4.3.2 0<br>4.3.3 1<br>Time ba<br>4.4.1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ction                                            | 60<br>62<br>62<br>65<br>67<br>67<br>69<br>72<br>78 |

| 4 | 4.1<br>4.2<br>4.3 | Introduct Single s 4.2.1 1 4.2.2 0 Heart-ra 4.3.1 5 4.3.2 0 4.3.3 1 Time ba 4.4.1 1 4.4.2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ction                                            | 60<br>62<br>65<br>67<br>67<br>72<br>78<br>78       |

CONTENTS xiii

| 5 | A Fl | exible ECG Patch Compatible with NFC RF Communication        | 91    |

|---|------|--------------------------------------------------------------|-------|

|   | 5.1  | Introduction                                                 | . 92  |

|   | 5.2  | System architecture                                          | . 95  |

|   | 5.3  | Circuit design                                               | . 96  |

|   | 5.4  | Measurement results                                          | . 100 |

|   |      | 5.4.1 Electrical characterization                            | . 100 |

|   |      | 5.4.2 <i>In-vivo</i> characterization                        | . 103 |

|   | 5.5  | Conclusions                                                  | . 106 |

| 6 | A M  | Iultichannel EOG Acquisition System based on Flexible TFTs a | nd    |

|   | CMO  | OS Technologies                                              | 113   |

|   | 6.1  | Introduction                                                 | . 114 |

|   | 6.2  | System architecture                                          | . 115 |

|   |      | 6.2.1 Hybrid high pass filter                                | . 118 |

|   |      | 6.2.2 Frontend on flexible foil                              | . 121 |

|   |      | 6.2.3 Silicon backend                                        | . 122 |

|   | 6.3  | Measurement results                                          | . 127 |

|   |      | 6.3.1 Preamplifier chain characterization                    | . 128 |

|   |      | 6.3.2 Full system characterization                           | . 130 |

|   | 6.4  | Conclusions                                                  | . 132 |

| 7 | A Di | igitally Assisted Tunable High Pass Filter                   | 137   |

|   | 7.1  | Introduction                                                 | . 138 |

|   | 7.2  | System architecture                                          | . 138 |

|   | 7.3  | Circuit principle                                            | . 139 |

|   | 7.4  | Simulation results                                           | . 142 |

|   | 7.5  | Conclusions                                                  | . 145 |

| 8 | Con  | clusions                                                     | 149   |

|   | 8.1  | Conclusions                                                  | . 150 |

|   | 8.2  | Future work                                                  | . 152 |

## List of Figures

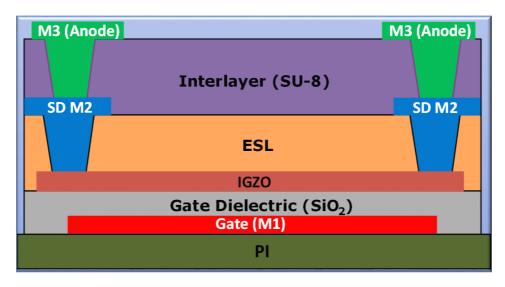

| 2.1 | Cross section of an a-IGZO TFT based on ESL flow                       | 23 |

|-----|------------------------------------------------------------------------|----|

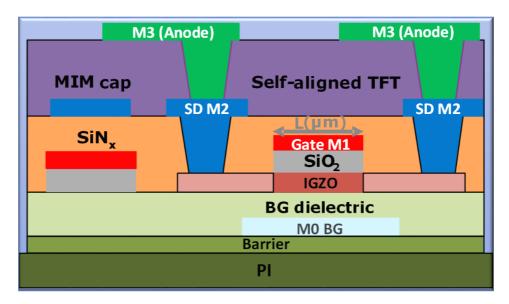

| 2.2 | Cross section of an a-IGZO TFT based on DUGA flow                      | 25 |

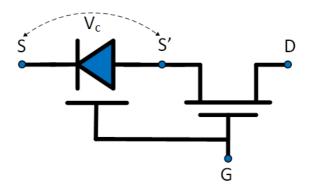

| 2.3 | Schematic device model including a reverse biased Schottky-gated       |    |

|     | diode                                                                  | 27 |

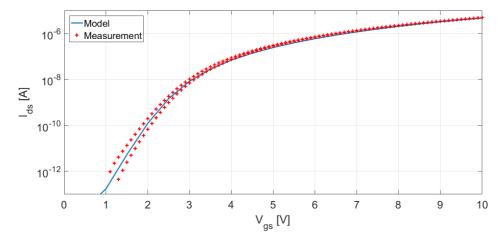

| 2.4 | Measured transfer characteristics of ESL TFT (in hysteresis mode)      |    |

|     | compared to model simulations                                          | 27 |

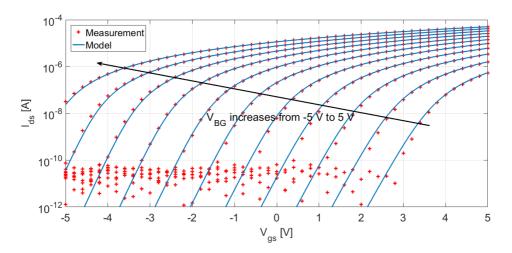

| 2.5 | Measured transfer characteristics of DUGA TFT compared to model        |    |

|     | simulations when $V_{BG}$ is varied between -5 V to 5 V. Note that the |    |

|     | points under $10^{-10}$ A are dominated by noise [8]                   | 29 |

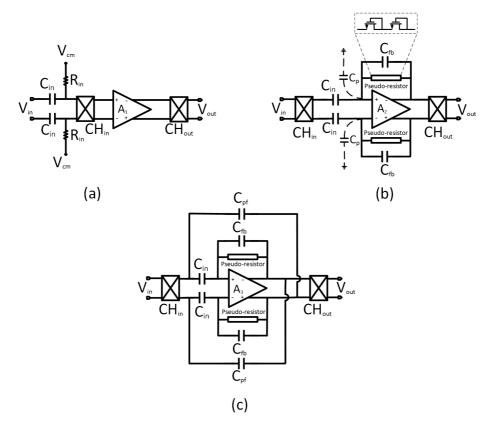

| 3.1 | Bio-signal front-ends implemented with (a) an open loop amplifier      |    |

|     | (b) an amplifier in capacitive feedback (c) an amplifier in capacitive |    |

|     | feedback with additional impedance-boosting positive feedback loop.    | 38 |

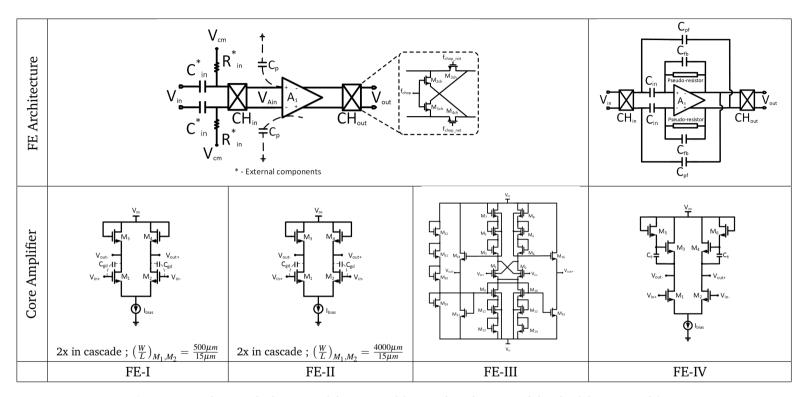

| 3.2 | Architectural schematics of the presented front-ends with structural   |    |

|     | details of the core amplifiers                                         | 45 |

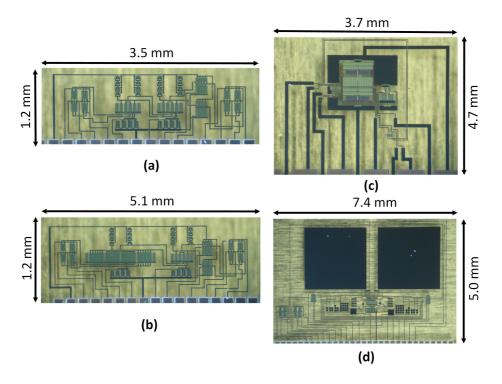

| 3.3 | Foil micrograph of the fabricated front-ends (a) FE-I, (b) FE-II, (c)  |    |

|     | FE-III and (d) FE-IV                                                   | 48 |

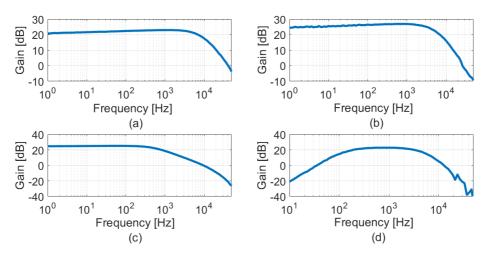

| 3.4 | Frequency response of the amplifiers (a) FE-I, (b) FE-II, (c) FE-III   |    |

|     | and (d) FE-IV.                                                         | 48 |

xvi LIST OF FIGURES

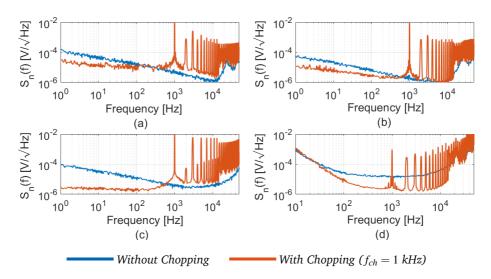

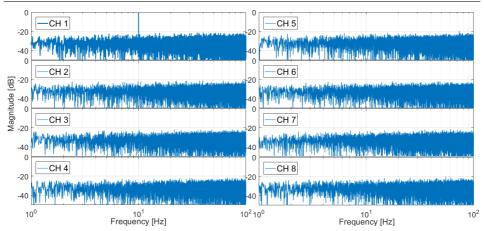

| 3.5  | Input referred noise density of the different front-ends (a) FE-I, (b)       |    |

|------|------------------------------------------------------------------------------|----|

|      | FE-II, (c) FE-III and (d) FE-IV.                                             | 49 |

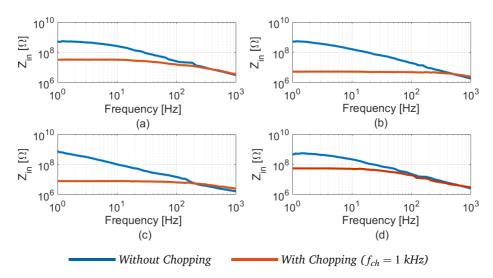

| 3.6  | Input impedance of the different front-ends (a) FE-I, (b) FE-II, (c)         |    |

|      | FE-III and (d) FE-IV.                                                        | 51 |

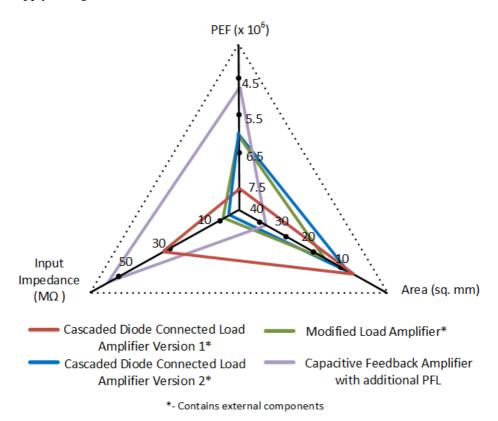

| 3.7  | Performance comparison of the presented front-ends                           | 52 |

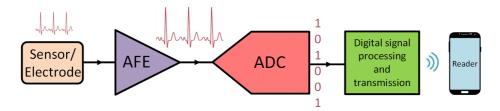

| 4.1  | General bio-signal acquisition system architecture                           | 60 |

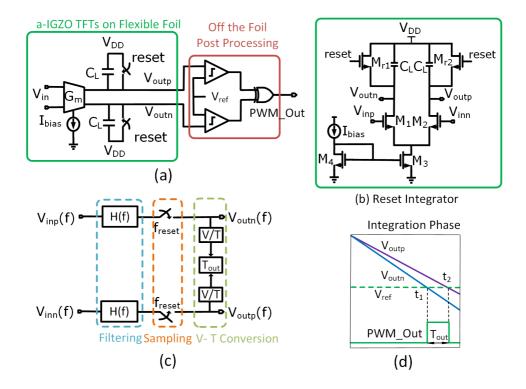

| 4.2  | (a) Architecture of the single slope reset integrator, (b) Circuit schematic | С  |

|      | of the single slope reset integrator, (c) Functionality of the reset in-     |    |

|      | tegrator in terms of signal processing operations, (d) Principle of          |    |

|      | operation.                                                                   | 62 |

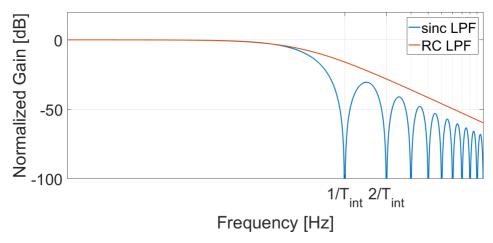

| 4.3  | Comparison of sinc LPF response with RC LPF response                         | 64 |

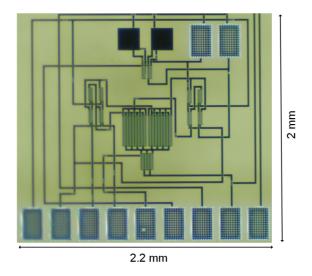

| 4.4  | Micrograph of the single slope reset integrator on foil. $\dots \dots$       | 66 |

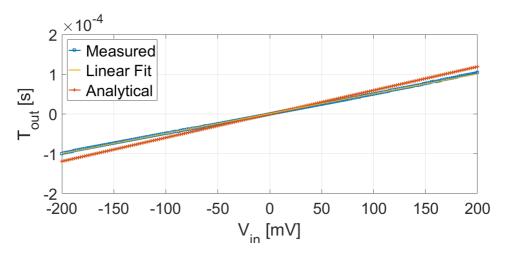

| 4.5  | DC transfer characteristics                                                  | 67 |

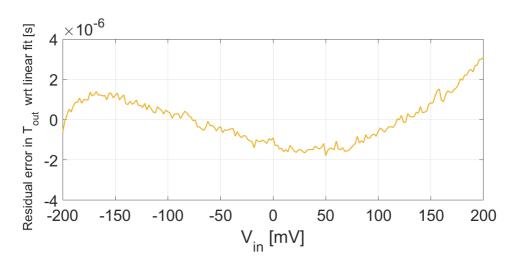

| 4.6  | Residual error in measured $T_{out}$ with respect to linear fit              | 67 |

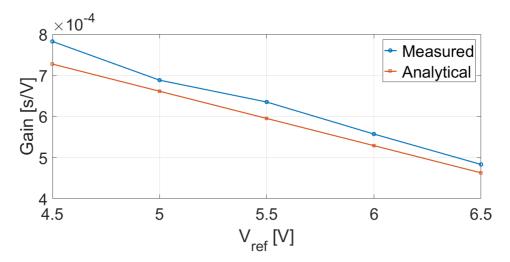

| 4.7  | Variation of gain with $V_{ref}$                                             | 68 |

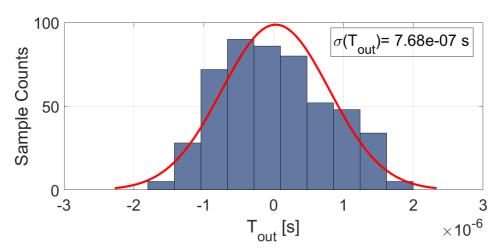

| 4.8  | Measured output jitter.                                                      | 68 |

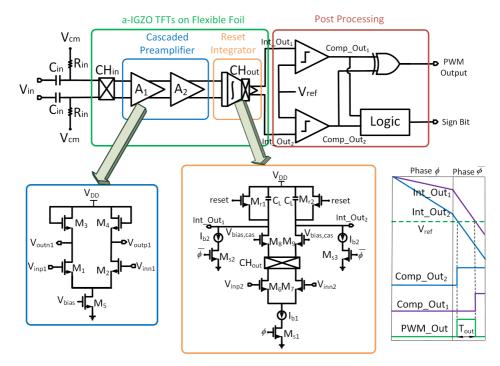

| 4.9  | General system architecture.                                                 | 69 |

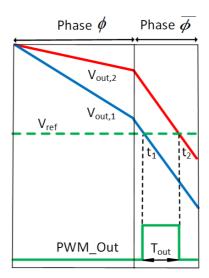

| 4.10 | Principle of operation                                                       | 70 |

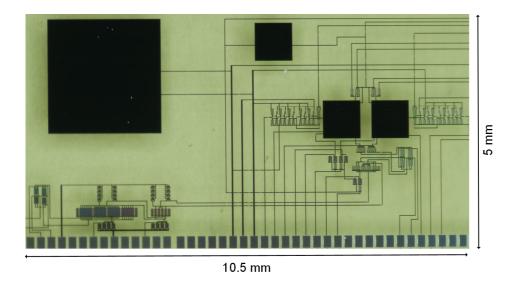

| 4.11 | Micrograph of the preamplifier and reset Integrator on foil                  | 73 |

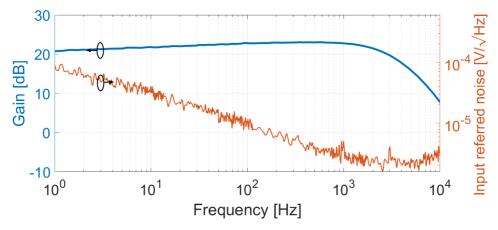

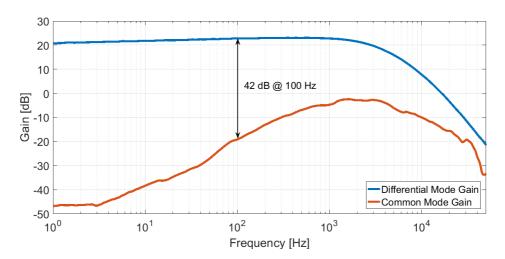

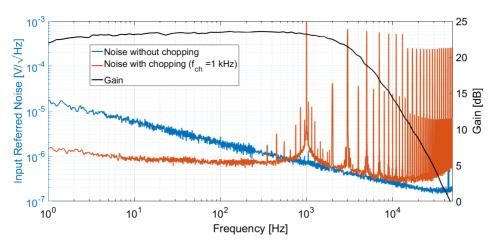

| 4.12 | Measured preamplifier frequency response and input-referred noise.           | 74 |

| 4.13 | Measured CMRR of the preamplifier                                            | 74 |

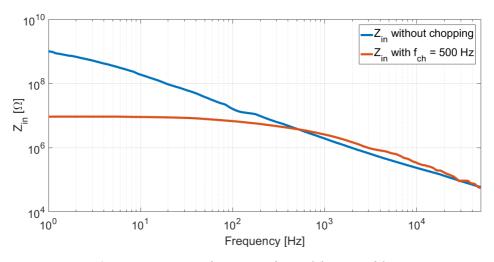

| 4.14 | Measured input impedance of the preamplifier                                 | 75 |

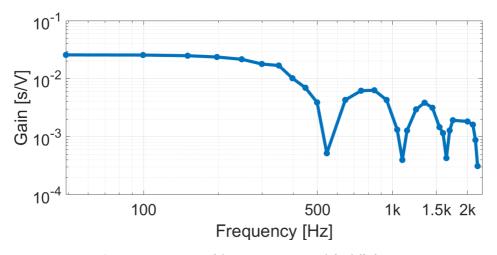

| 4.15 | Measured frequency response of the full chain                                | 75 |

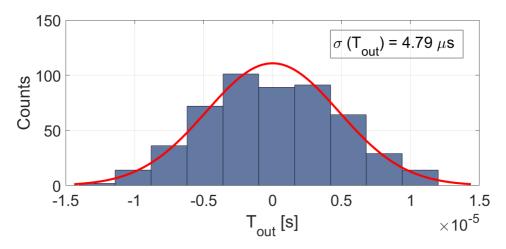

| 4.16 | Measured output jitter in absence of an input signal                         | 76 |

| 4.17 | Response of the measurement interface to an ECG signal provided              |    |

|      | by a signal generator.                                                       | 76 |

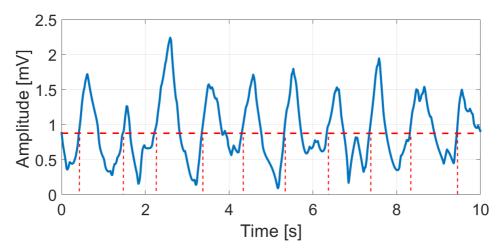

| 4.18 | Reconstructed signal from PWM waveform showing heartbeat from                |    |

|      | in-vivo measurement.                                                         | 77 |

LIST OF FIGURES xvii

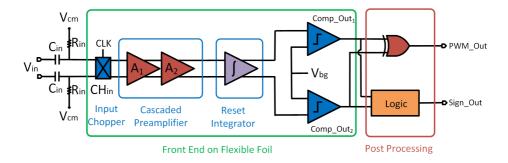

| 4.19 | System architecture of the improved version of the system shown in                   |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | Figure 4.9                                                                           | 79  |

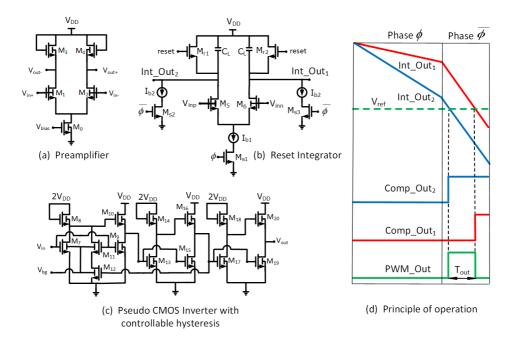

| 4.20 | Schematics of (a) the preamplifier, (b) the reset integrator, (c) pseudo             |     |

|      | CMOS inverter and (d) working principle of the reset integrator                      | 79  |

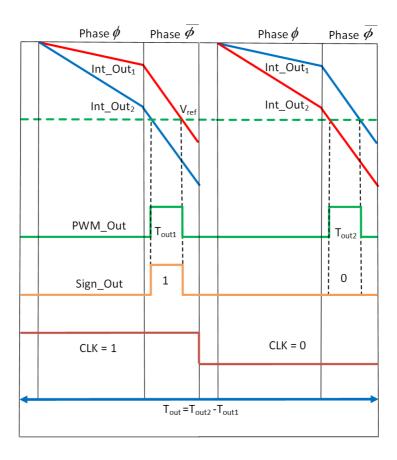

| 4.21 | Principle of system level CDS                                                        | 80  |

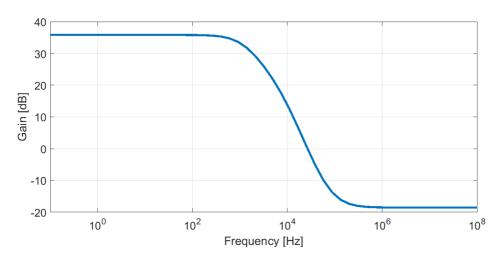

| 4.22 | Simulated frequency response of the preamplifier                                     | 82  |

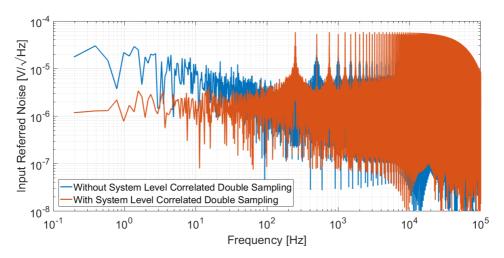

| 4.23 | Simulated noise spectrum of the proposed system                                      | 82  |

| 4.24 | Simulated DC transfer curve of the inverter with cascading three                     |     |

|      | pseudo-CMOS inverters                                                                | 83  |

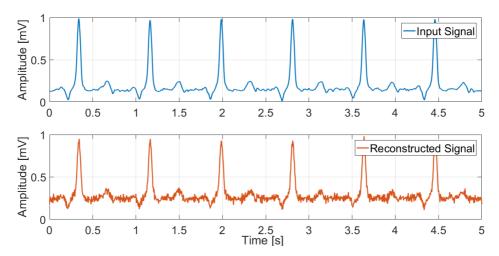

| 4.25 | Simulated response of the full system to an ECG source signal                        | 83  |

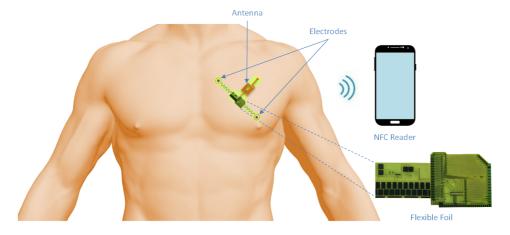

| 5.1  | Representative application scenario of the presented ECG patch                       | 93  |

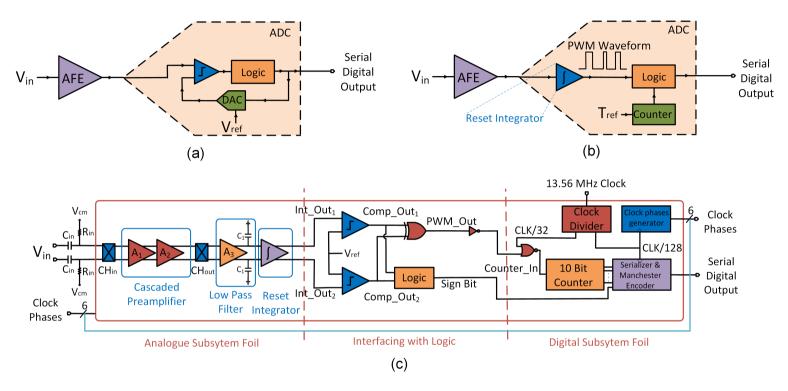

| 5.2  | System architecture. (a) Conventional bio-potential acquisition sys-                 |     |

|      | tem, (b) System-level diagram of the presented ECG acquisition sys-                  |     |

|      | tem, (c) Detailed architecture of the presented system                               | 94  |

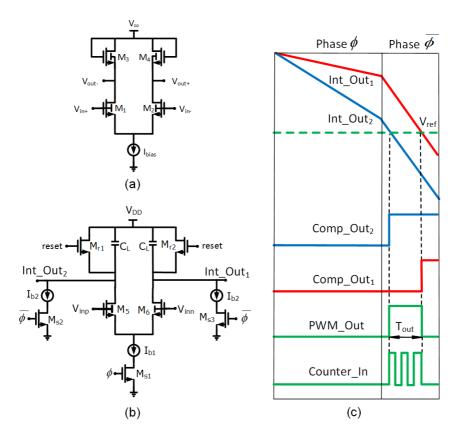

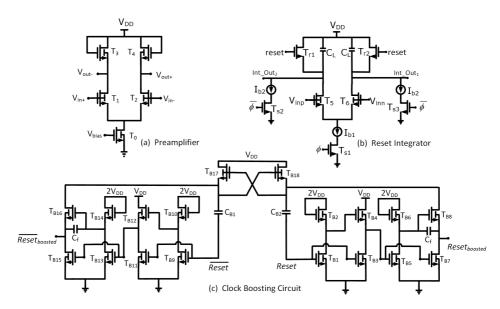

| 5.3  | Circuit schematics and working principle. (a) Schematic of each of                   |     |

|      | the two cascaded diode-load amplifiers in the preamplifier, (b) Reset                |     |

|      | integrator, (c) Reset integrator working principle. $\ \ \ldots \ \ldots \ \ \ldots$ | 99  |

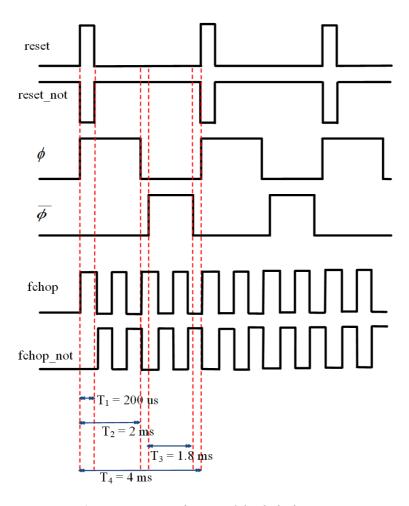

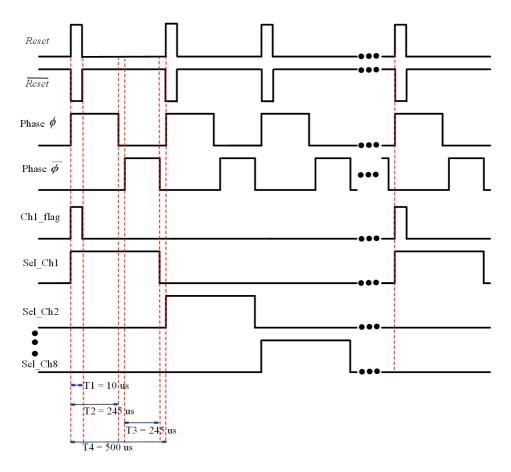

| 5.4  | Timing diagram of the clock phases                                                   | 101 |

| 5.5  | Measured frequency response and input-referred noise of the cas-                     |     |

|      | caded preamplifier.                                                                  | 102 |

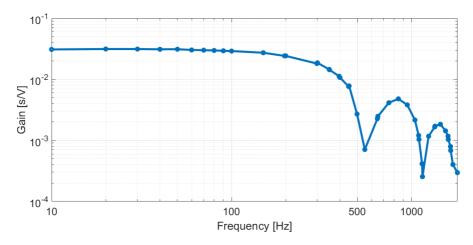

| 5.6  | Measured transfer function of the full analogue chain (from input to                 |     |

|      | output PWM)                                                                          | 102 |

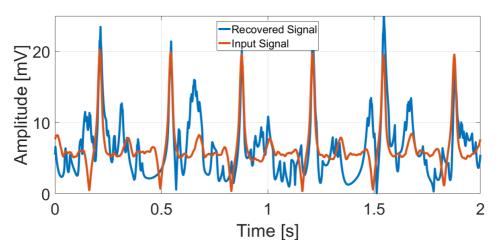

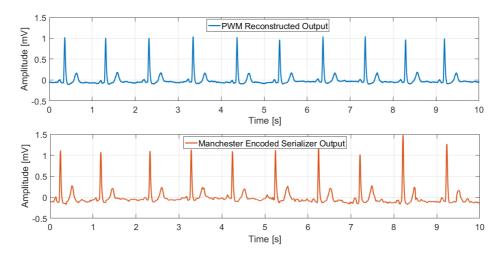

| 5.7  | (Top panel) In-vivo ECG measured signal reconstructed from the                       |     |

|      | output PWM, (Bottom panel) In-vivo ECG measured signal recon-                        |     |

|      | structed from Manchester encoded output                                              | 103 |

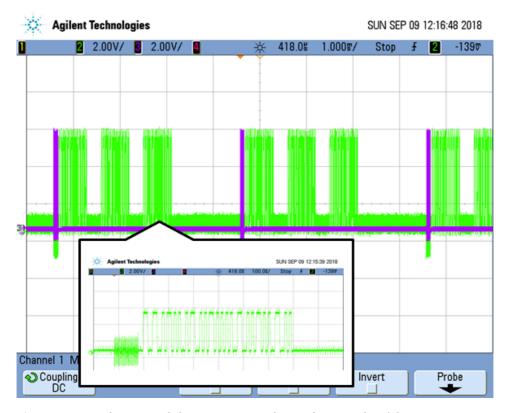

| 5.8  | Manchester encoded output corresponding to three samples of the                      |     |

|      | in-vivo measurement and a zoom-in of the Manchester encoding of                      |     |

|      | the output bits                                                                      | 104 |

| 5.9  | Foil micrograph of the presented system.                                             | 105 |

xviii LIST OF FIGURES

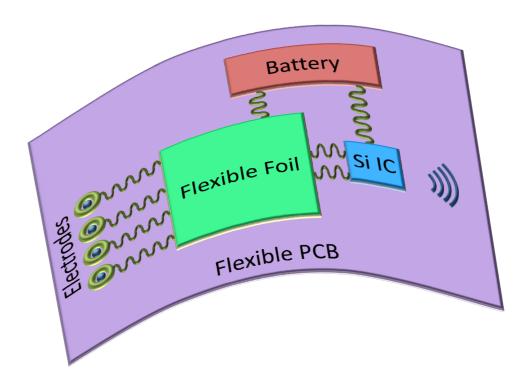

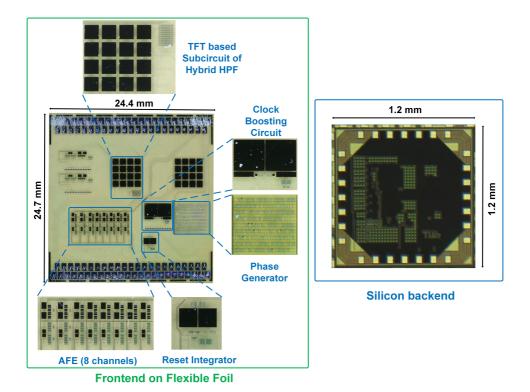

| 6.1  | Representative integration of the flexible hybrid system 116                   |

|------|--------------------------------------------------------------------------------|

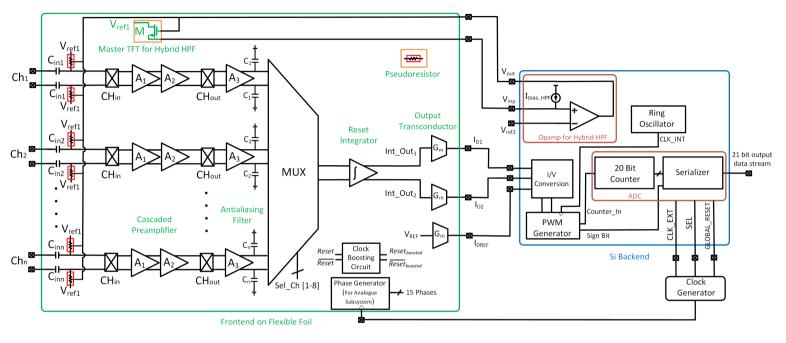

| 6.2  | System architecture of the flexible hybrid system                              |

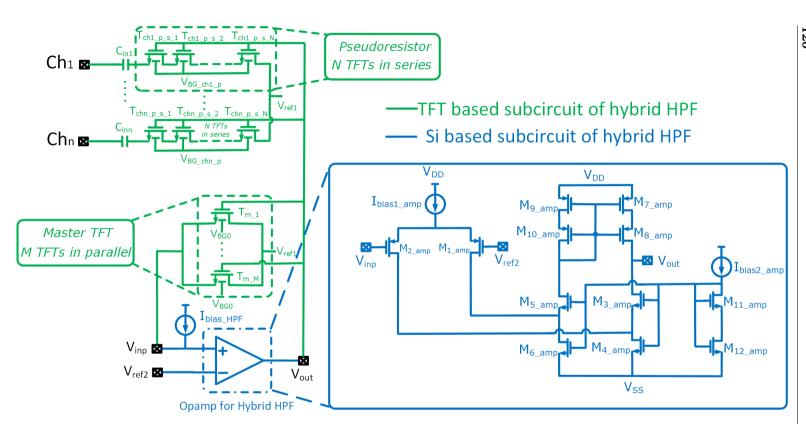

| 6.3  | Architecture of the flexible hybrid HPF                                        |

| 6.4  | Circuit schematic of analogue frontend (a) Schematic of the diode-             |

|      | connected load amplifier, (b) Reset integrator, (c) Clock boosting             |

|      | circuit                                                                        |

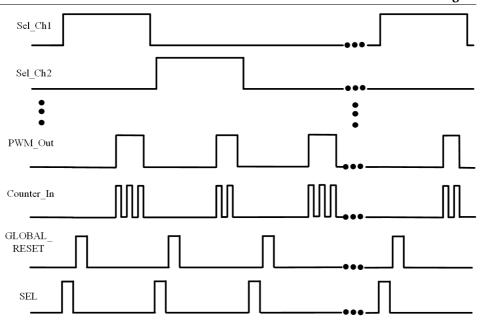

| 6.5  | Timing diagram of the frontend on flexible foil                                |

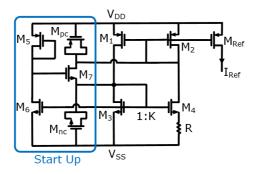

| 6.6  | Circuit schematic of the current reference                                     |

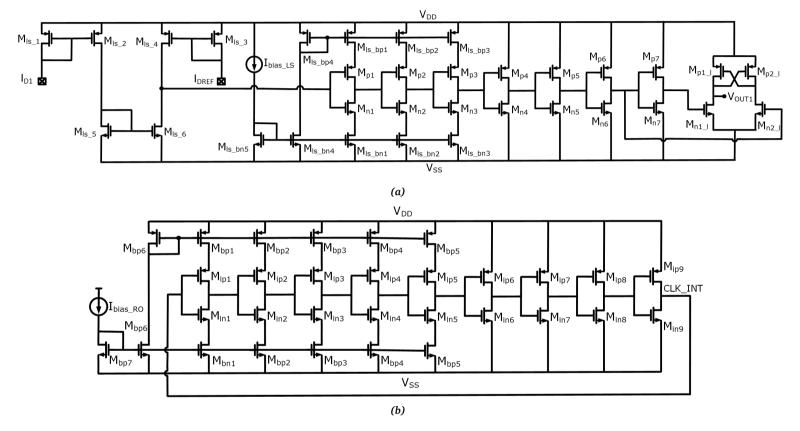

| 6.7  | (a) Circuit schematic of the I/V conversion (single ended version              |

|      | shown for illustration), (b) Circuit schematic of the ring oscillator $125$    |

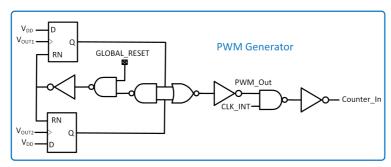

| 6.8  | Circuit schematics of the PWM generator, counter and serializer. $$ 126        |

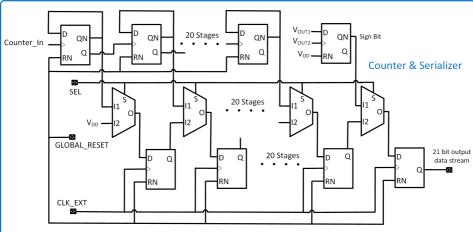

| 6.9  | Timing diagram for the PWM generator block                                     |

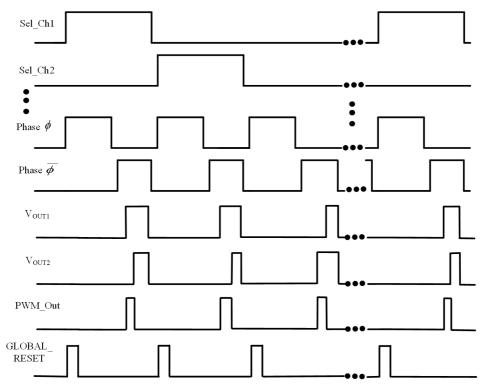

| 6.10 | Timing diagram for the Silicon backend                                         |

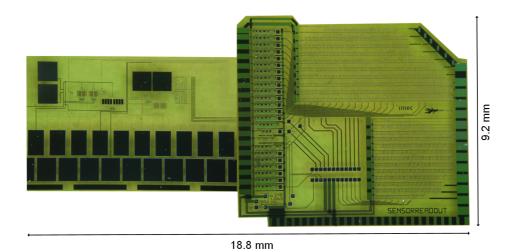

| 6.11 | Micrograph of the full system including frontend on flexible foil and          |

|      | Silicon backend                                                                |

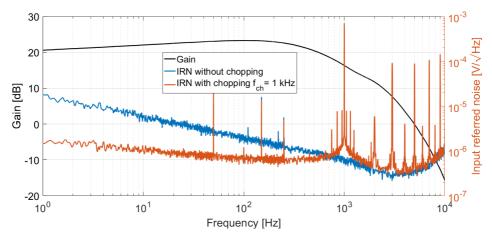

| 6.12 | Measured frequency response and input-referred noise of the pream-             |

|      | plifier chain $(A_{1-3})$                                                      |

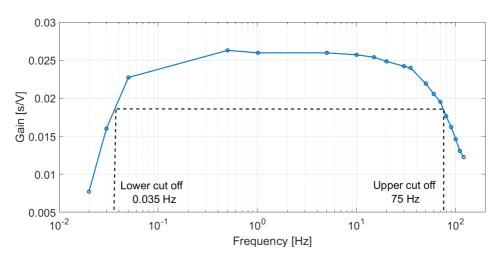

| 6.13 | Measured transfer function of the full system                                  |

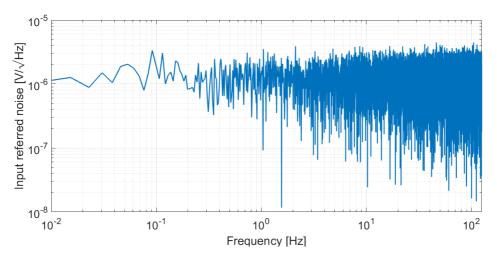

| 6.14 | Measured input referred noise of the full system                               |

| 6.15 | Measured crosstalk of the full system                                          |

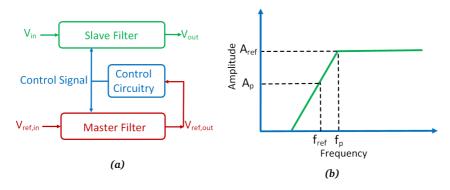

| 7.1  | (a) General system architecture and (b) General high pass filter re-           |

| /.1  | sponse                                                                         |

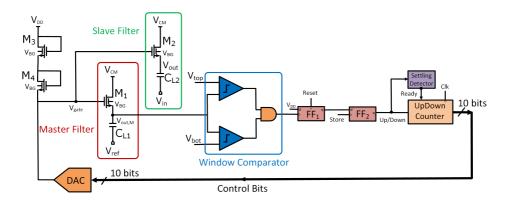

| 7 2  | Circuit schematic of the proposed system                                       |

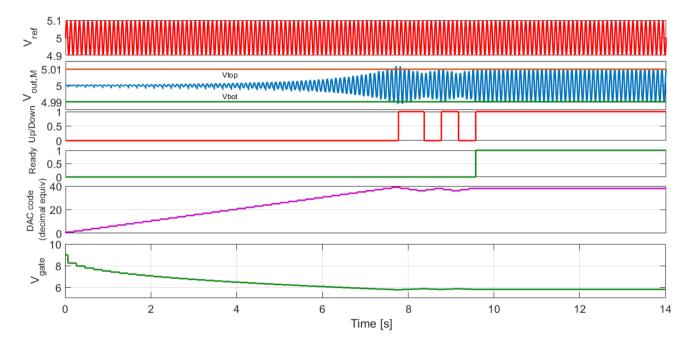

|      | Waveforms at different nodes of the system depicting operation of              |

| 7.3  | the system. To show more clearly how the system works, an 8 bit                |

|      |                                                                                |

|      | counter and DAC are used to generate this figure                               |

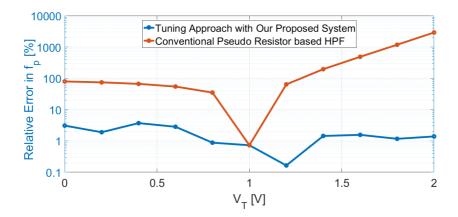

| 7.4  | The effect of threshold voltage variation on the relative error in $f_p$ . 143 |

| 7.5  | The effect of $V_{DD}$ variation on the relative error in $f_p$                |

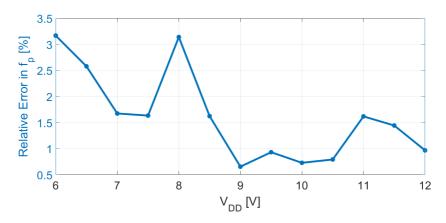

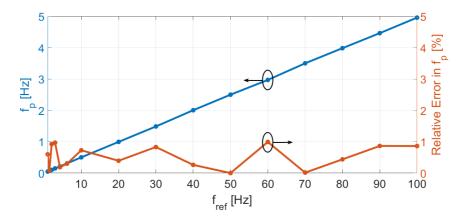

| 7.6  | The effect of $f_{ref}$ variation on $f_p$ and the relative error in $f_p$ 144 |

LIST OF FIGURES xix

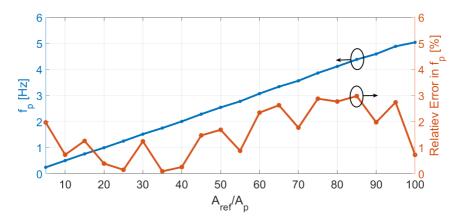

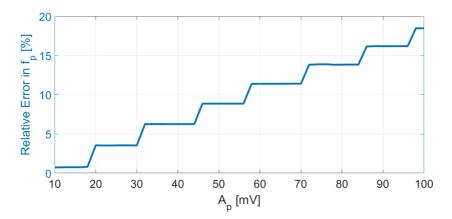

7.7 The effect of  $A_{ref}/A_p$  ratio variation on  $f_p$  and the relative error in  $f_p$ . 145

7.8 The effect of  $A_p$  variation in  $f_p$  (keeping the  $A_{ref}/A_p$  ratio constant). 145

## List of Tables

| 3.1 | Relevant design parameters of the presented front-ends 47          |

|-----|--------------------------------------------------------------------|

| 3.2 | Performance comparison of the presented front-ends with the state- |

|     | of-the-art                                                         |

| 4.1 | Circuit parameters of the single slope reset integrator 66         |

| 4.2 | Optimized design parameters of the system shown in Figure 4.9 $72$ |

| 4.3 | Comparison to the state-of-the-art                                 |

| 4.4 | Comparison to prior literature                                     |

| 5.1 | Specifications of ECG recording systems as dictated by the ANSI    |

|     | AAMI standard                                                      |

| 5.2 | Comparison with the state-of-the-art                               |

| 6.1 | Comparison with the state-of-the-art                               |

## Chapter 1

Introduction

#### 1.1 Introduction

The electronics field has witnessed a transformation phase in the recent years, due to the rapid rise of wearables and ubiquitous sensors, thanks to the advent of the Internet of Things (IoT). There are applications which do not suit traditional electronics such as displays, imagers, photovoltaic cells, NFC tags, wearable sensors for biomedical signals monitoring etc.

Indeed, applications that require a large surface to be covered with electronics are difficult or costly to achieve with conventional Silicon-based Integrated Circuits (ICs). However, advancements in the technology of thin-film transistors (TFTs) have paved the way to fabricate devices over large areas and have opened the possibility, thanks to a low process temperature budget, to use plastic foils as flexible substrates, enabling what is called "flexible and large area electronics". This type of devices not only result in electronics distributed over a large area, but also leads to lower cost per unit area compared to conventional ICs. The inherent flexible nature of the substrates in these technologies can be leveraged in applications requiring conformability, bendability, foldability and stretchability. A specific category of applications that can strongly benefit from flexible electronics is the domain of flexible and comfortable wearable devices for wellness and healthcare monitoring.

The dimensions of the transistors in flexible technologies are in micrometre regime, that leads to low cost solutions. Although these devices do not perform on par with conventional Silicon technologies, these devices are useful in the applications where high performance is not required. Thus, the driving requirements are flexible form factor, large surface area and reduced system cost. The ultimate purpose of flexible electronics is to enable electronic platforms that are not feasible and/or not cost-efficient with existing Silicon-based technologies. Besides, it should be noted here that the goal of flexible electronics is not to replace mainstream Silicon technologies, but rather to implement those functions that are not well addressed by conventional Silicon technologies. The main enablers of flexible

1.1 Introduction 3

electronics include its mechanical flexibility, large-area manufacturing and potential low-cost in volume. Hence, the focus of flexible electronics is on those applications where properties such as flexibility, conformability and light weight are demanded, or for applications where a large area is required.

#### 1.1.1 Flexible electronic technologies

Flexible electronic technologies can be divided in the following categories depending on the nature of the semiconductor material used.

#### **Amorphous Silicon**

Amorphous Silicon (a-Si:H or a-Si) is the most well-known thin-film semiconductor [1], generally used in display backplanes. The fabrication process of a-Si based TFTs requires only 4-5 mask steps and it results in n-type only devices. The standard process temperature for a-Si is about 250°C-350°C. The amorphous nature of a-Si gives it a good uniformity but the charge carrier mobility is very low ranging between 0.5-1  $cm^2V^{-1}s^{-1}$ . Moreover, the electrical stability of a-Si based devices is poor, which results in threshold voltage shifts of as large as 10 V [2, 3].

#### Low temperature polycrystalline Silicon

Low temperature polycrystalline Silicon (LTPS) can be used as an alternative semi-conductor for high-performance display backplanes. LTPS transistors exhibit mobility in the range of  $50-100 \ cm^2 V^{-1} s^{-1}$  due to the polycrystalline nature of the semiconductor, with the additional possibility of fabrication of both p-type and n-type transistors. However, the small crystals give rise to grain boundaries resulting in device-to-device non-uniformity. A higher process temperature (around  $500^{\circ}$ C) is one other drawback while the more complex process flow with additional mask steps [4] results in larger cost and lower yield compared to a-Si.