# Wake-up receiver based ultra-low-power WBAN

Citation for published version (APA):

Lont, M. (2013). Wake-up receiver based ultra-low-power WBAN. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR762409

DOI:

10.6100/IR762409

Document status and date:

Published: 01/01/2013

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 05. Oct. 2023

# Wake-up Receiver Based Ultra-Low-Power WBAN

# Maarten Lont

# Wake-up Receiver Based Ultra-Low-Power WBAN

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op woensdag 6 november 2013 om 16:00 uur

door

Maarten Lont

geboren te Steinheim, Duitsland

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. A.C.P.M. Backx

1<sup>e</sup> promotor: prof.dr.ir. A.H.M. van Roermund

copromotor: dr.ir. D. Milosevic

leden: prof.dr.ir. B. Nauta (University of Twente)

dr.ir. W.A. Serdijn (Delft University of Technology)

prof.dr.ir. P.G.M. Baltus dr.ir. F.M.J. Willems

adviseur: dr.ir. G. Dolmans (Holst Centre)

Wake-up Receiver Based Ultra-Low-Power WBAN / by Maarten Lont Eindhoven University of Technology

ISBN: 978-94-6191-908-3

Copyright © Copyright 2013, Maarten Lont, Eindhoven

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission from the copyright owner.

# **CONTENTS**

| Li | st of S | Symbols  | 8                                  | V  |

|----|---------|----------|------------------------------------|----|

| Li | st of A | Abbrevi  | ations                             | xi |

| 1  | Intr    | oductio  | n                                  | 1  |

|    | 1.1     | Wake-    | up Receiver                        | 2  |

|    | 1.2     | Wake-    | up Receiver Challenges             | 3  |

|    | 1.3     | Aims o   | of the Thesis                      | 5  |

|    | 1.4     | Scope    | of the Thesis                      | 5  |

|    | 1.5     | Origin   | al Contributions                   | 6  |

|    | 1.6     | Thesis   | Outline                            | 7  |

| 2  | Wir     | eless Bo | ody Area Networks                  | 9  |

|    | 2.1     | Wirele   | ess Sensor Network Properties      | 9  |

|    | 2.2     | MAC      | Layer Energy Consumption Model     | 11 |

|    |         | 2.2.1    | Address Coding                     | 12 |

|    |         | 2.2.2    | Radio Model                        | 16 |

|    |         | 2.2.3    | Network Statistics                 | 18 |

|    |         | 2.2.4    | WURx-enhanced Asynchronous Network | 19 |

|    |         | 2.2.5    | WURx-less Asynchronous Network     | 21 |

|    |         | 2.2.6    | Synchronous Network                | 22 |

|    |         | 227      | Application Example                | 25 |

ii CONTENTS

|   | 2.3 | Applic  | cations                                              | 26 |

|---|-----|---------|------------------------------------------------------|----|

|   | 2.4 |         | on Space                                             | 27 |

|   | 2.5 |         | usion                                                | 32 |

| 3 | Wak |         | eceiver System Level Design                          | 35 |

|   | 3.1 | _       | of the Art                                           | 36 |

|   | 3.2 |         | lation Complexity                                    | 39 |

|   | 3.3 |         | F Architecture                                       | 40 |

|   | 3.4 |         | Receiver Model                                       | 41 |

|   |     | 3.4.1   | Non-Ideal Receiver Front-End                         | 43 |

|   |     | 3.4.2   | Receiver Phase Noise and Jitter                      | 44 |

|   |     | 3.4.3   | Limiter Discriminator Model                          | 46 |

|   | 3.5 | Effects | s of Receiver Imperfections on FSK BER               | 47 |

|   |     | 3.5.1   | Bit Error Rate Analysis                              | 48 |

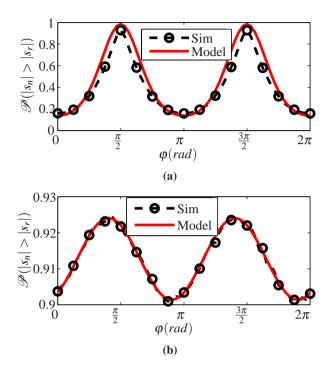

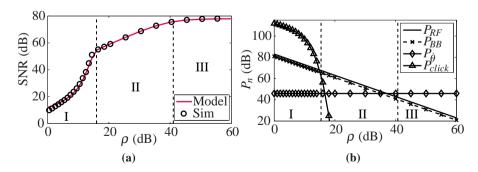

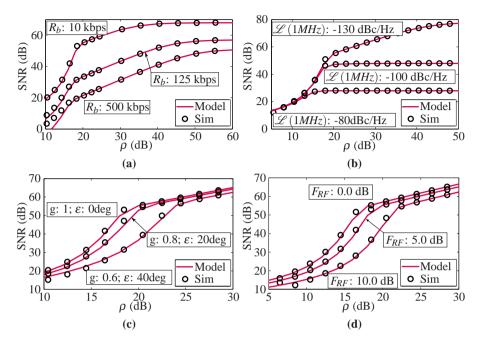

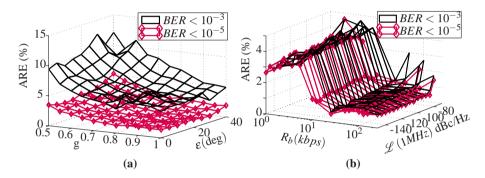

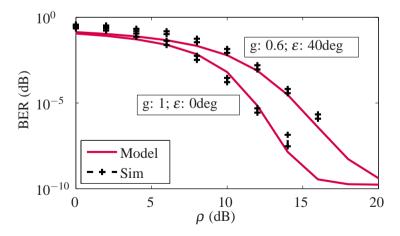

|   |     | 3.5.2   | Simulation and Model Results                         | 60 |

|   | 3.6 | Wake-   | up Receiver Specifications                           | 66 |

|   |     | 3.6.1   | Interferer robustness                                | 66 |

|   |     | 3.6.2   | Sensitivity and Noise Figure                         | 66 |

|   |     | 3.6.3   | Phase Noise                                          | 67 |

|   | 3.7 | Conclu  | usion                                                | 68 |

| 4 | Low | -Power  | Zero-IF Receiver Design                              | 69 |

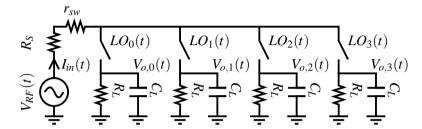

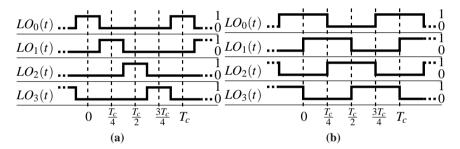

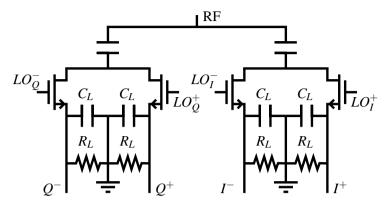

|   | 4.1 | Passive | e Mixer-First Design                                 | 70 |

|   |     | 4.1.1   | Time-Domain Passive Mixer Model                      | 71 |

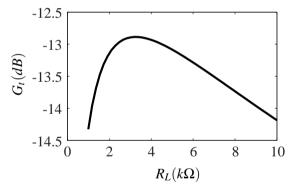

|   |     | 4.1.2   | Voltage Conversion Gain                              | 75 |

|   |     | 4.1.3   | Input Impedance                                      | 77 |

|   |     | 4.1.4   | Transducer Power Gain                                | 80 |

|   |     | 4.1.5   | Maximal Transducer Power Gain                        | 80 |

|   |     | 4.1.6   | Noise Figure                                         | 82 |

|   |     | 4.1.7   | Optimal Design                                       | 84 |

|   | 4.2 | Low-P   | Power Local Oscillator Design                        | 86 |

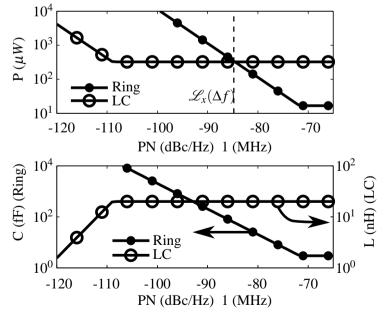

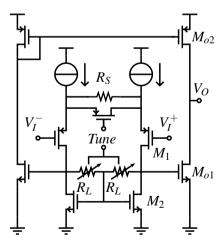

|   |     | 4.2.1   | Oscillator Design Considerations for Minimum Power . | 86 |

|   |     | 4.2.2   | LC Oscillator Design                                 | 87 |

CONTENTS

|   |     | 4.2.3    | Ring Oscillator Design                 | 88  |

|---|-----|----------|----------------------------------------|-----|

|   |     | 4.2.4    | LC and Ring Oscillator Design Approach | 90  |

|   |     | 4.2.5    | LC vs Ring Oscillators                 | 92  |

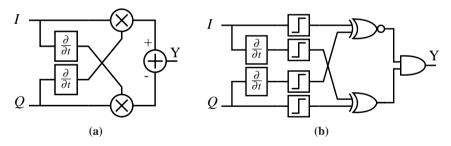

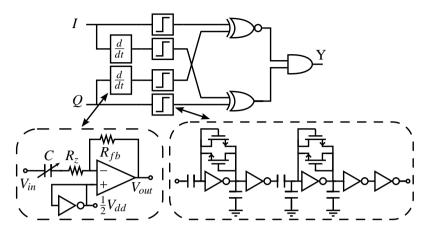

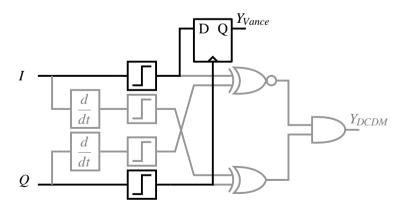

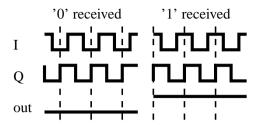

|   | 4.3 | FSK D    | Demodulator                            | 95  |

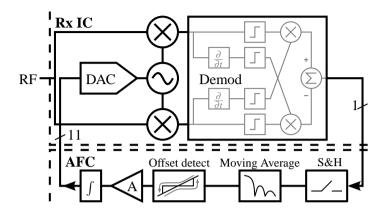

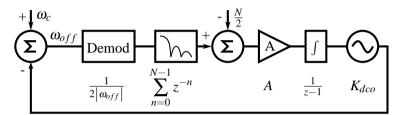

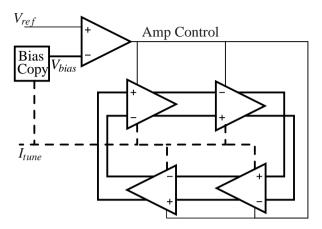

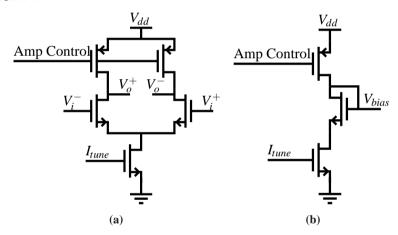

|   | 4.4 | Autom    | natic Frequency Control Loop           | 96  |

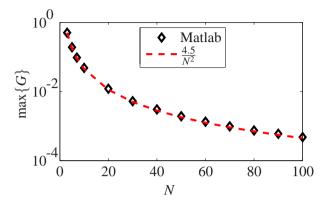

|   |     | 4.4.1    | Closed Loop Analysis                   | 97  |

|   |     | 4.4.2    | System Level Implications              | 100 |

|   | 4.5 | Conclu   | usion                                  | 101 |

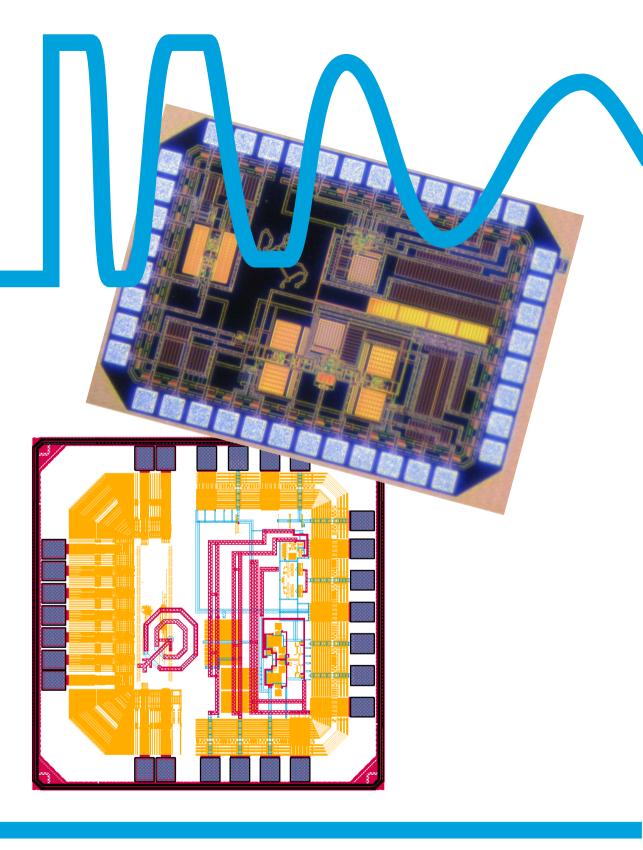

| 5 | Rec | eiver Fr | cont-End Version 1                     | 103 |

|   | 5.1 | Impler   | nentation                              | 103 |

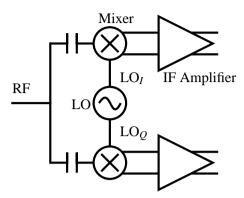

|   |     | 5.1.1    | Mixer                                  | 104 |

|   |     | 5.1.2    | Local Oscillator                       | 105 |

|   |     | 5.1.3    | IF Amplifier                           | 107 |

|   | 5.2 | Measu    | rement Results                         | 108 |

|   |     | 5.2.1    | LO Measurements                        | 110 |

|   |     | 5.2.2    | Amplifier Measurements                 | 111 |

|   |     | 5.2.3    | Receiver Front-End Measurements        | 112 |

|   | 5.3 | Compa    | arison with Literature                 | 114 |

|   | 5.4 | Conclu   | usion                                  | 117 |

| 6 | Rec | eiver Fr | cont-End Version 2                     | 119 |

|   | 6.1 | Design   | n Targets                              | 119 |

|   | 6.2 | Impler   | mentation                              | 120 |

|   |     | 6.2.1    | Passive Mixer                          | 121 |

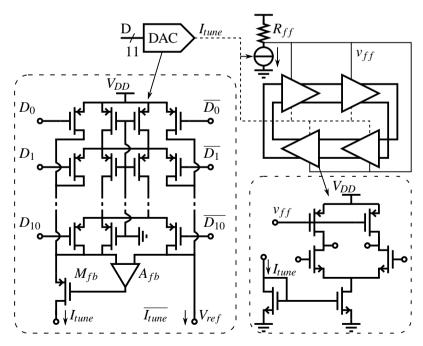

|   |     | 6.2.2    | Local Oscillator                       | 121 |

|   |     | 6.2.3    | Variable Gain Amplifier                | 124 |

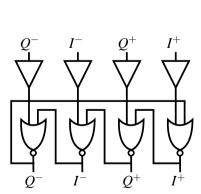

|   |     | 6.2.4    | Demodulator                            | 125 |

|   |     | 6.2.5    | Automatic Frequency Control Loop       | 127 |

|   | 6.3 | Receiv   | ver Front-End Measurements             | 131 |

|   |     | 6.3.1    | DCDM Demodulator                       | 135 |

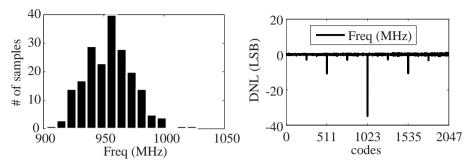

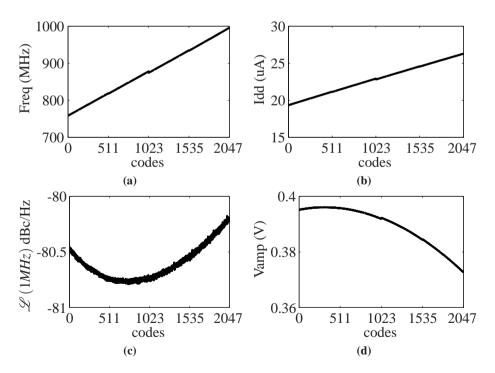

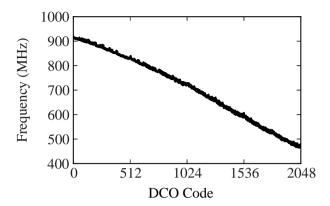

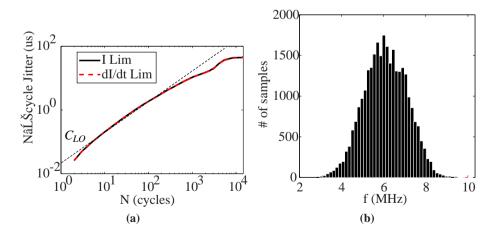

|   |     | 6.3.2    | DCO                                    | 135 |

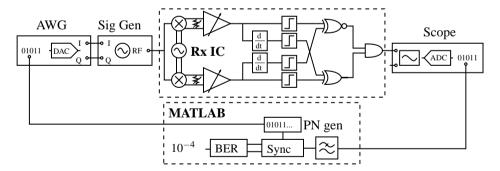

|   |     | 6.3.3    | Bit Error Rate                         | 138 |

iv CONTENTS

|             | 6.3.4 Blocker Rejection                                                   | 141                                                                                                                                                                                                                                                                                                                                          |

|-------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 6.3.5 AFC Loop                                                            | 142                                                                                                                                                                                                                                                                                                                                          |

| 6.4         | Comparison with Literature                                                | 143                                                                                                                                                                                                                                                                                                                                          |

| 6.5         | Conclusion                                                                | 146                                                                                                                                                                                                                                                                                                                                          |

| Con         | clusions                                                                  | 147                                                                                                                                                                                                                                                                                                                                          |

| comr        | nendations                                                                | 149                                                                                                                                                                                                                                                                                                                                          |

| AC P        | rotocol Packet Statistics                                                 | 151                                                                                                                                                                                                                                                                                                                                          |

| <b>A</b> .1 | Number of Wake-up Calls                                                   | 151                                                                                                                                                                                                                                                                                                                                          |

| A.2         | Number of Acknowledgments                                                 | 153                                                                                                                                                                                                                                                                                                                                          |

| A.3         | False Wake-up Statistics                                                  | 155                                                                                                                                                                                                                                                                                                                                          |

| A.4         | Synchronized Transceiver Packet Statistics                                | 157                                                                                                                                                                                                                                                                                                                                          |

| rdic        | Radio Parameters                                                          | 159                                                                                                                                                                                                                                                                                                                                          |

| nulat       | tion Script                                                               | 161                                                                                                                                                                                                                                                                                                                                          |

| feren       | uces                                                                      | 163                                                                                                                                                                                                                                                                                                                                          |

| st of I     | Publications                                                              | 171                                                                                                                                                                                                                                                                                                                                          |

| mma         | ary                                                                       | 173                                                                                                                                                                                                                                                                                                                                          |

| menv        | vatting                                                                   | 175                                                                                                                                                                                                                                                                                                                                          |

| dex         |                                                                           | 177                                                                                                                                                                                                                                                                                                                                          |

| know        | vledgment                                                                 | 181                                                                                                                                                                                                                                                                                                                                          |

|             |                                                                           | 183                                                                                                                                                                                                                                                                                                                                          |

|             | 6.5 Com AC P A.1 A.2 A.3 A.4 ordic mulat feren st of I mma menv dex eknow | 6.4 Comparison with Literature 6.5 Conclusion  Conclusions  Commendations  AC Protocol Packet Statistics  A.1 Number of Wake-up Calls  A.2 Number of Acknowledgments  A.3 False Wake-up Statistics  A.4 Synchronized Transceiver Packet Statistics  ordic Radio Parameters  mulation Script  ferences  st of Publications  mmary  menvatting |

# LIST OF SYMBOLS

| $a_{f,n}$                                    | $n^{th}$ order Fourier cosine coefficient of function $f(t)$                                                                                      | 75             |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

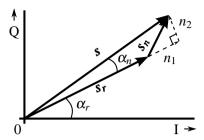

| $egin{array}{l} lpha_n \ lpha_r \end{array}$ | Phase of the receiver generated noise vector Bit n from the bipolar bit sequence Phase of the received FSK signal corrupted by the LO phase noise | 49<br>42<br>49 |

| $egin{aligned} BAW \ b_{f,n} \end{aligned}$  | Bulk Acoustic Wave filter $n^{th}$ order Fourier sine coefficient of function $f(t)$                                                              | 39<br>75       |

| $c_{f,n} \ C_{LO}$                           | $n^{th}$ order complex Fourier series coefficient<br>Phase noise thermal noise parameter                                                          | 77<br>45       |

| $\Delta\omega$<br>$\Delta P_x$               | FSK frequency deviation  Power consumption increase in mode x com-                                                                                | 42<br>16       |

| $\Delta T[n]$                                | pared to sleep mode $P_x - P_{sleep}$<br>Cycle-to-cycle jitter of the nth period                                                                  | 46             |

| ε                                            | I/Q phase error                                                                                                                                   | 43             |

| $F$ $f_{osc}$                                | Noise factor<br>Oscillator oscillation frequency                                                                                                  | 43<br>87       |

| g                                            | I/Q gain error                                                                                                                                    | 43             |

vi List of Symbols

| $G_{BB}$             | Gain in the baseband stage                                     | 49  |

|----------------------|----------------------------------------------------------------|-----|

| $G_{RF}$             | RF gain                                                        | 44  |

| $G_t$                | Mixer transducer power gain                                    | 80  |

| $G_v$                | Mixer voltage conversion gain                                  | 75  |

| h                    | FSK modulation index $h = \frac{\Delta \omega}{\pi R_h}$       | 42  |

| $H_{I\&D}(\omega)$   | b                                                              | 41  |

| $H_{IF}(\omega)$     | Intermediate frequency filter                                  | 40  |

| k                    | Packet length                                                  | 16  |

| $k_B$                | Boltzmann's constant                                           | 42  |

|                      | $1.38065 \times 10^{-23}  m^2  kg  s^{-2}  K^{-1}$             |     |

| $K_{LO}$             | Phase noise 1/f noise parameter                                | 45  |

| $\mathscr{L}(f)$     | Phase noise at $f$ Hz offset given in dBc/Hz                   | 45  |

| l                    | Address length                                                 | 12  |

| λ                    | Average packet rate                                            | 11  |

| $\mathbf{M}_{rx}(t)$ | Receiver matrix                                                | 44  |

| μ                    | Electron mobility                                              | 125 |

| $\mu_{ACK}$          | Expected number of acknowledgments                             | 154 |

| $\mu_{ACKx}$         | Expected number of acknowledgment retransmissions              | 18  |

| $\mu_{bcn/pkt}$      | Expected number of synchronization beacons per received packet | 24  |

| $\mu_{FACKx}$        | Expected number of retransmitted false acknowledgments         | 18  |

| $\mu_{slot}$         | Expected number of TDMA slots per received packet              | 18  |

| $\mu_{WUC}$          | Expected number of wake-up calls                               | 18  |

| $n_{bb}$             | Baseband input related noise                                   | 43  |

| $n_i(t)$             | Receiver input noise                                           | 42  |

| $N_{node}$           | Number of nodes in the network                                 | 11  |

| $n_{rf}$             | RF input related noise                                         | 43  |

| $N_{WUC}^+$          | Maximal number of wake-up call transmissions                   | 18  |

| $\omega_o$           | Carrier frequency                                              | 42  |

List of Symbols vii

| $\omega_{off}$            | FSK frequency offset                                   | 95  |

|---------------------------|--------------------------------------------------------|-----|

| $P_{1dBc}$                | Input referred 1dB compression point                   | 112 |

| $p_{ACK \ge 1}$           | Probability of initial acknowledgment transmis-        | 18  |

|                           | sion                                                   |     |

| $P_{BB}(	au)$             | Baseband generated noise power at the output of        | 58  |

|                           | the FSK demodulator                                    |     |

| $P_{click}(	au)$          | Click noise power at the output of the FSK de-         | 54  |

| . ,                       | modulator                                              |     |

| $p_{FACK \geq 1}$         | Probability of at least one false acknowledgment       | 18  |

|                           | transmission                                           |     |

| $p_{FACK, n}$             | Probability that <i>n</i> false acknowledgment packets | 155 |

| ,                         | are send                                               |     |

| $p_{false}$               | False wake-up probability                              | 18  |

| $\boldsymbol{\varphi}(t)$ | Instantaneous phase of FSK modulated signal            | 42  |

| $\varphi(t)$              | FSK signal phase                                       | 42  |

| $P_{IIP3}$                | Input referred third order interception point          | 112 |

| $P_{LO}$                  | Local oscillator power used to drive the mixer         | 71  |

| $p_{miss}$                | Packet miss probability                                | 18  |

| $P_R$                     | Power consumption in receive mode                      | 16  |

| $P_{RF}(	au)$             | RF generated noise power at the output of the          | 57  |

| ( )                       | FSK demodulator                                        |     |

| $P_{Rset}$                | Power consumption when settling to receive             | 16  |

|                           | mode                                                   |     |

| $P_s(	au)$                | Signal power at the output of the FSK demodula-        | 58  |

| ~ ( )                     | tor                                                    |     |

| $P_{sleep}$               | Power consumption in sleep mode                        | 16  |

| $P_{standby}$             | Power consumption in standby mode                      | 16  |

| $P_T$                     | Power consumption in transmit mode                     | 16  |

| $P_{\dot{m{	heta}}}(	au)$ | Phase noise power at the output of the FSK de-         | 58  |

| 0 ( )                     | modulator                                              |     |

| $P_{Tset}$                | Power consumption when settling to standby             | 16  |

|                           | mode                                                   |     |

| $P_{wake}$                | Power consumption when switching between               | 16  |

|                           | sleep and standby mode                                 |     |

|                           |                                                        |     |

| r                         | Radius of gyration                                     | 55  |

viii List of Symbols

| $R_{\dot{lpha}_n}(	au)$ | Autocorrelation of the total demodulator output noise | 51 |

|-------------------------|-------------------------------------------------------|----|

| $R_{lpha_{nbb}}(	au)$   | Autocorrelation of the baseband noise phase           | 52 |

| unbb ( ')               | component at the output of the receiver front-end     |    |

| $R_{lpha_{nrf}}(	au)$   | Autocorrelation of the RF noise phase compo-          | 51 |

| unrf ( ' )              | nent at the output of the receiver                    |    |

| $R_b$                   | Bit rate                                              | 16 |

| $R_{bw}$                | Wake-up receiver bit rate                             | 20 |

| $R_f(	au)$              | Autocorrelation of the transfer function from the     | 52 |

| <i>J</i> ( <i>)</i>     | baseband noise source to the signal phase at the      |    |

|                         | receiver output                                       |    |

| $R_g(	au)$              | Autocorrelation of the transfer function from the     | 52 |

| 8 ( )                   | RF noise source to the signal phase at the receiver   |    |

|                         | output                                                |    |

| ρ                       | Carrier to noise ratio                                | 42 |

| $R'_L$                  | Normalized load impedance                             | 73 |

| $R_{nbb}(\tau)$         | Autocorrelation of the baseband noise source          | 52 |

| $R_{nrf}(\tau)$         | Autocorrelation of the RF noise source                | 51 |

| $r_{sw}$                | Switch on-resistance                                  | 70 |

| r(t)                    | Received signal                                       | 40 |

| S                       | Signal vector at the output of the receiver front-    | 49 |

|                         | end                                                   |    |

| SAW                     | Surface Acoustic Wave filter                          | 39 |

| $\sigma_{abs}$          | Absolute time jitter standard deviation               | 46 |

| $\sigma_{bb}$           | Standard deviation of the baseband generated noise    | 43 |

| $\sigma_i$              | Standard variation of the receiver input noise        | 42 |

| $\sigma_{pn}$           | Standard deviation of the receiver generated          | 44 |

|                         | phase noise                                           |    |

| $\sigma_{rf}$           | Standard deviation of the RF generated noise          | 43 |

| $s_n$                   | Receiver generated noise vector                       | 49 |

| $S_{nbb}(\omega)$       | Power spectral density of the baseband noise at       | 53 |

|                         | the FSK demodulator output                            |    |

| $S_{nrf}(\omega)$       | Power spectral density of the RF noise at the FSK     | 53 |

|                         | demodulator output                                    |    |

| $s_r$                   | FSK signal vector corrupted by LO phase noise         | 49 |

List of Symbols ix

| $S_y(\omega)$ | Power spectral density of the FSK demodulator output             | 52  |

|---------------|------------------------------------------------------------------|-----|

| T             | Address decoding threshold                                       | 13  |

| $T_{abs}[n]$  | Absolute jitter measure over n periods                           | 46  |

| $T_b$         | Bit period $\left(\frac{1}{R_h}\right)$                          | 42  |

| $T_{beacon}$  | Maximal time between two TDMA synchronization beacons            | 23  |

| $\theta(t)$   | Local oscillator phase noise                                     | 43  |

| $T_{lat}$     | Maximally allowed link-setup latency                             | 10  |

| $T_{mavg}$    | Integration time constant of the moving-average filter           | 128 |

| $	au_{off}$   | Mixer time constant when the switch is turned off                | 73  |

| $T_{off,n}$   | Mixer switch turn-off time of phase n                            | 72  |

| $	au'_{off}$  | Mixer normalized off-state RC time constant                      | 73  |

| $	au_{on}$    | Mixer time constant when the switch is turned on                 | 73  |

| $T_{on,n}$    | Mixer switch turn-on time of phase n                             | 72  |

| $	au'_{on}$   | Mixer normalized on-state RC time constant                       | 73  |

| $T_s$         | Sample time                                                      | 97  |

| $T_{set}$     | Receiver or transmitter settling period                          | 16  |

| $T_{skew}$    | Maximal allowed clock skew between a TDMA master and sensor node | 23  |

| $T_{wake}$    | Transition time between sleep and standby mode                   | 16  |

| $V_T$         | Thermal voltage $\left(\frac{kT}{q}\right)$                      | 125 |

| y(t)          | FSK demodulator output signal                                    | 49  |

| $Z_{in}$      | Mixer input impedance at the carrier frequency                   | 77  |

List of Symbols

# LIST OF ABBREVIATIONS

| ACK  | Acknowledgment                                       | 18  |

|------|------------------------------------------------------|-----|

| AFC  | Automatic Frequency Control                          | 94  |

| ARE  | Average relative error                               | 63  |

| BAN  | Body Area Network                                    | 9   |

| BAW  | Bulk Acoustic Wave                                   | 36  |

| BER  | Bit Error Rate                                       | 15  |

| CNR  | Carrier to noise ratio                               | 42  |

| CW   | Continuous-Wave interferer                           | 138 |

| DCDM | Digital Cross-Differentiate Multiply FSK demodulator | 93  |

| DCO  | Digitally Controlled Oscillator                      | 119 |

| DNL  | Differential Non-Linearity                           | 119 |

| EVM  | Error Vector Magnitude                               | 39  |

| FACK | False Acknowledgment                                 | 18  |

| FOM  | Figure of Merit                                      | 114 |

| FSK  | Frequency Shift Keying                               | 35  |

| FSPL | Free Space Path Loss                                 | 64  |

| IC   | Inversion Coefficient                                | 122 |

| IIP3 | Input referred third order interception point | 111 |

|------|-----------------------------------------------|-----|

| LO   | Local Oscillator                              | 44  |

| MAC  | Media Access Control                          | 9   |

| OOK  | On-Off Keying                                 | 35  |

| pdf  | Probability Density Function                  | 54  |

| PLL  | Phase Locked Loop                             | 36  |

| PSD  | Power spectral density                        | 45  |

| PVT  | Process, Voltage and Temperature variation.   | 98  |

| RSSI | Received Signal Strength Indicator            | 98  |

| SIR  | Signal-to-Interferer-ratio                    | 138 |

| TDMA | Time Division Multiple Access                 | 11  |

| VGA  | Variable Gain Amplifier                       | 122 |

| WBAN | Wireless Body Area Network                    | 9   |

| WUC  | Wake-up call used to wake-up the sensor nodes | 11  |

| WURx | Wake-up Receiver                              | 11  |

# INTRODUCTION

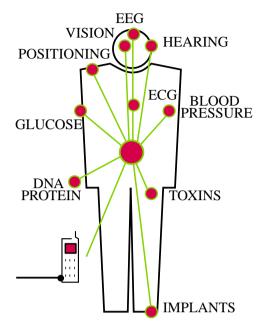

WIRELESS Body Area Networks (WBAN) are small-scale, in both area and node count, networks centered on a human body. The low-power wireless nodes can contain many different sensors, for example: ECG, EEG, blood-pressure and temperature sensors. This is graphically depicted in figure 1.1. While the required bit rate of the different sensors varies from a few kilobits per second up to a few hundred kilobits per second, most applications require a bit rate around 100kbps, see [1] and [2]. Additionally, the average packet rate of a sensor node is very low. Some nodes like temperature sensors may only transmit the measured data a couple of times a day, hence they are in sleep mode for more than 90% of the time. Other sensor types like EEG and ECG might have high peak bit rates when they are active. However they are not activated most of the time. Additionally the required link to link setup latency requirement is relaxed, which favors asynchronous networks.

The sensor nodes are battery powered and have to operate for a long period of time, while it is often impossible or impractical to recharge or replace the batteries on a regular basis. Therefore, the sensor nodes need to have very low power consumption. Furthermore, since the network is centered around the human body, it is a small scale network by definition. The maximal distance between two nodes is approximately 10m. Combining the small network scale with the low power requirement, a single-hop star network topology is a good fit. In such a network there is one master node, for example a smart phone, with a bigger power supply and higher processing capabilities. Thus the body area sensor

**Figure 1.1:** Example of a Wireless Body Area Network in which different sensor nodes around the body cooperate in a small-scale network.

network is highly asymmetric. The asymmetric nature of the network can be used to reduce the power consumption of the sensor nodes by mapping power intensive tasks on the high power master node or by choosing a synchronization scheme to make maximal use of the asymmetric power supply. Additionally, the sensitivity of the sensor node can be decreased by increasing the transmit power of the master node.

## 1.1 Wake-up Receiver

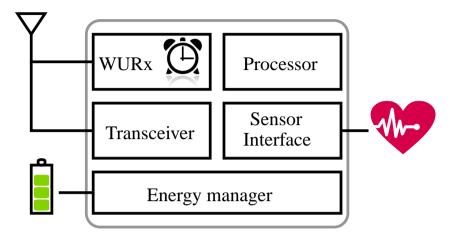

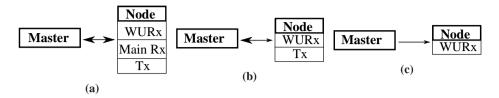

To reduce the sensor node power consumption to a level where the node can operate for months on a small battery the node needs to sleep as long and often as possible. A low-power Wake-up Receiver (WURx) is added to the sensor node which wakes up the node when it receives a Wake-up Call (WUC) transmitted by the master node. Figure 1.2 gives the overview of a general wireless sensor node. Depending on the application the main transceiver might be omitted. A remote control application might only need a WURx for example.

**Figure 1.2:** A general wireless sensor node overview.

The WURx should be capable of receiving and decoding a wake-up call containing an address and possibly a few bits of settings and information. An address should be sent since we do not want to wake-up all the nodes in the network, as this would lead to a waste of power. In fact, the WURx is used to synchronize the master and sensor nodes only during the transmission of a packet. In between packet transmissions the network is not synchronized in order to save power.

This thesis focuses on the design and implementation of the wake-up receiver, both on the system level and circuit level.

## 1.2 Wake-up Receiver Challenges

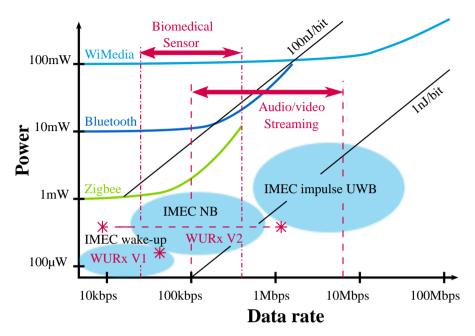

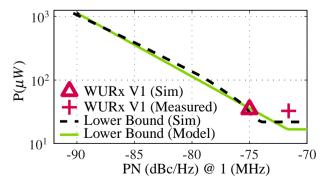

Figure 1.3 shows a schematic overview of the required bit rates and corresponding power consumption of current wireless standards. The depicted bit rate is the bit rate over the air. From the application point of view the actual bit rate may be lower because of channel coding, and synchronization overhead such as packet headers. It has to be noted that besides the bit rate and power consumption also sensitivity and linearity are important parameters. There is a clear trade-off between bit rate and power consumption. The figure also shows the three IMEC application scenarios, depicted by the blue clouds. Within this thesis we target the low-power WURx application scenarios and low-bit-rate narrow-band (NB) applications. As can be seen the targeted power consumption is much lower than state-of-the-art low-power standards like Zigbee, while still fulfilling the WBAN specific receiver requirements. The stars show the measurement results of the

**Figure 1.3:** Schematic overview of wireless standards and the low-power IMEC application areas.

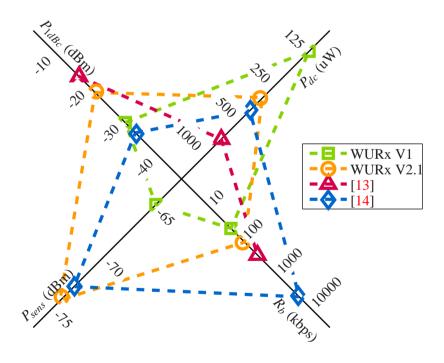

first (WURxV1) and second (WURxV2.1) wake-up receiver presented in chapters 5 and 6 in this thesis. The first version of the wake-up receiver front-end has a fixed bit rate of 50kbps with a power consumption of 126µW. While the second version has a constant power consumption of 329.6µW with a variable bit rate between 6.25kbps and 1250kbps. Therefore, the second WURx is denoted by a region confined by two stars. For more information on the first and second version of the wake-up receiver front-end see chapters 5 and 6, respectively.

A small scale Wireless Body Area Network (WBAN) is targeted. Since the WBAN is inherently small-scale, the maximal transmission distance is 10m. To reduce the power in the sensor nodes an asymmetric star-topology network is chosen. Moreover, there is a clear trade-off between power consumption and linearity. To reduce the power consumption the linearity is sacrificed. To avoid in-band interferer collision the master node manages the network, making sure that only one node is active. Additionally, the master node can avoid collisions with other networks by means of carrier sensing. The WURx itself should be able to cope with out-of-band interference. For a more in-depth discussion on the WURx specifications and requirements see section 3.6.

#### 1.3 Aims of the Thesis

As shown in the introduction wireless sensor nodes targeted towards WBAN applications can profit from a low-power wake-up receiver. However, the power consumption of the WURx should be lower than standard compliant receivers. The aim of this thesis is to study the feasibility of low-power wake-up receivers, with special attention on power reduction techniques. To attain the desired power consumption, the network, system and circuit levels are taken into account. The following aspects are addressed:

- Typical WBAN requirements (chapter 2)

- Effects of media access control (MAC) layer synchronization on the power consumption (chapter 2)

- The interaction between wideband FSK modulation and receiver front-end design (chapter 3)

- Power consumption reduction, by removing the low-noise-amplifier from the receiver front-end and using a mixer-first architecture (chapter 4)

- Low-power synchronization by replacing power-consuming phase-locked-loops by a low-power automatic frequency control loop (chapter 4)

- Implementation and evaluation of the proposed power reduction techniques (chapters 5 and 6)

## 1.4 Scope of the Thesis

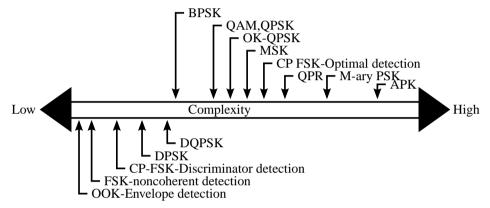

Within this thesis the implications of MAC layer synchronization on the power consumption will be studied, but the implementation of MAC protocols is beyond the scope of this thesis. Furthermore, there exists a large variety of wireless sensor networks with widely different requirements and characteristics. Each different network type demands different design trade-offs in order to come to an optimal low-power receiver front-end. Therefore, the thesis will only focus on small scale wireless networks, like wireless body area networks, and the design of low-power receiver front-ends used in the low-power sensor nodes in these networks. Moreover, this thesis focuses on the optimal circuit design of low-power Frequency Shift Keying (FSK) modulation based wake-up receivers. On-Off Keying (OOK) modulation will be mentioned but not analyzed in further detail since it is less robust against interferers. Circuits will only be implemented

in silicon with the aim of validating proposed power reduction strategies. This thesis does not have as a goal to demonstrate a fully-integrated transceiver system. The circuits will only be implemented in CMOS technology since it is the most widely used technology and the technology of choice for highly integrated mixed-signal systems.

# 1.5 Original Contributions

The original contributions of this thesis are:

- Closed-form energy consumption models of network synchronization.

- Modeling and analysis of the interaction between wideband-FSK modulation and receiver impairments.

- Mixer-first architecture geared towards low-power receiver front-ends and time-domain based modeling of the key performance parameters transducer power gain and noise figure.

- Optimal design strategy for mixer-first front-ends targeted towards low power consumption.

- Analysis of power consumption and phase noise performance differences between LC and ring oscillators taking technology scaling and limitations into account.

- Implementation and evaluation of mixer-first receiver front-ends.

- Design and implementation of an automatic frequency control loop using the in-place FSK demodulator as an alternative for power-hungry phase locked loops.

- Graphical comparison between different receiver front-ends as an extension to Figure of Merit (FOM) based comparison.

1.6. Thesis Outline 7

#### 1.6 Thesis Outline

The thesis outline is depicted in figure 1.4.

Figure 1.4: Thesis outline.

Chapter 1 introduces Wireless Body Area Networks and the Wake-up Receiver concept. Furthermore, the trends in both industrial and academic research are summarized and remaining research challenges are identified.

In chapter 2 several network and applications aspects of body area networks are studied. Since low energy consumption is essential, the impact of network synchronization on the energy consumption is studied at the Media Access Control (MAC) level. Additionally, common application related requirements are extracted from literature. By combining the application related WURx requirements and the MAC layer study the WURx solution space is derived.

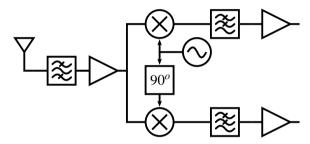

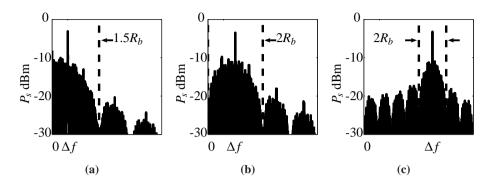

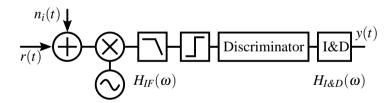

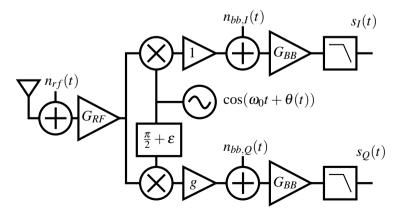

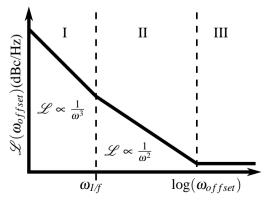

Chapter 3 delves into the system-level aspects of the WURx design, starting with a literature study of state-of-the-art low-power receivers with special attention on the chosen modulation schemes. A Zero-IF receiver architecture is chosen, because of the low power consumption target. Additionally, wideband-FSK modulation is proposed to overcome the inherent zero-IF design challenges like DC offset, self-mixing and 1/f noise, and the effects of receiver impairments on the Bit Error Rate (BER) are analyzed. The chapter concludes with WURx circuit level design specifications.

Chapter 4 focuses on circuit level design and modeling with special attention on power consumption reduction. The power consumption is reduced at circuit level by omitting the Low Noise Amplifier (LNA) from the receiver front-end, leading to a mixer-first architecture. The input impedance, transducer power

gain and noise figure of a passive mixer are modeled and used in the presented optimal design methodology for mixer-first receivers. Additionally, the power-consuming local oscillator is studied, and the LC and ring oscillator topologies are compared. Also an Automatic Frequency Control (AFC) loop which makes use of the FSK demodulator is presented as a power-efficient alternative for a power hungry PLL.

The feasibility of the mixer-first architecture is studied in chapter 5, by implementing and measuring a low-power receiver front-end. Furthermore, a graphical method for comparing different receiver front-ends given application requirements is presented.

In chapter 6 a second version of the mixer-first receiver front-end with decreased noise figure is presented. The AFC loop introduced in chapter 4 is implemented in an FPGA and tested in combination with the receiver front-end.

At the end of the thesis conclusions are drawn in chapter 7.

# WIRELESS BODY AREA NETWORKS

THERE has been a lot of research into Wireless Body Area Networks (WBAN); see for example the surveys presented in by [3] and [4]. In a WBAN, sensors are placed on or near the body. Each node needs to be very small; hence it can only have a small battery. Additionally, it is impractical or even impossible to replace the batteries on a regular basis. Alternatively, the node can make use of energy harvesting. In both cases the power consumption needs to be very low. This is one of the biggest challenges in the design of WBAN nodes and can only be achieved by making use of the special properties of WBANs.

In this chapter different sensor network aspects and reported WBAN applications are analyzed and summarized. Additionally, several Media Access Control (MAC) protocols are compared using the WBAN properties. Since low power consumption is of primary importance, the sensor node energy consumption of the different MAC-layers are compared. With the energy consumption models, the solution space is examined. At the end of the chapter the receiver requirements are obtained.

# 2.1 Wireless Sensor Network Properties

The power consumption of wireless sensor nodes can be greatly reduced by optimizing the nodes with respect to network symmetry, synchronization, scale and packet rate.

Firstly, the network symmetry has a big impact on the system design. In a symmetric network the wireless sensor nodes have similar power supply and processing power. On the other hand, in an asymmetric network there can be large differences between nodes. In other words, the network is heterogeneous. Body area networks (BAN) usually are asymmetric [3]. In such a network at least one node has a bigger power supply and more processing power, and can take over energy-consuming tasks from the low-power simple sensor nodes.

Additionally, the network size is an important network property. Unlike environmental sensor networks, a WBAN is inherently small-scale. The maximal distance between two nodes is less than 10m, and each network has less than 100 nodes [1]. In such a small network, it is more power efficient to use single-hop communication instead of multi-hop.

Since the network is small-scale, asymmetric and single-hop, a star topology is suitable, which is used by most WBANs [3, 5]. In a star topology there is only one master node which manages the network, as is depicted in figure 1.1. Since the master has a bigger power supply it can transmit with higher power and acts as a gateway to the outside world. The rest of the network consists of low-power, simple sensor nodes. Additionally, the master can be used for in-band interference avoidance. Firstly the master node manages the network and makes sure that only one sensor node is active at any given moment. Secondly, the master can implement carrier sensing to reduce collisions with other networks operating in the same band.

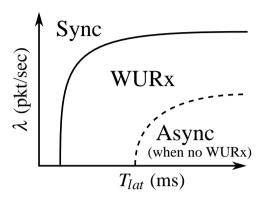

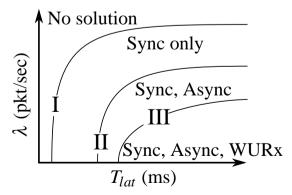

Finally, the packet rate  $\lambda$  and maximal allowed link setup latency  $T_{lat}$  are important in WBAN design. When the packet rate is low and the allowed network latency is high, the nodes can sleep for very long periods to save power. In such a network the network does not have to stay synchronized the entire time, because there is enough time to synchronize before each transmission. Since the network does not need to be kept synchronized in the long pauses between two consecutive packages, the synchronization overhead is reduced. On the other hand, when the latency needs to be very low or when the packet rate is very high, there is no time to synchronize the network before every transmission. A more in-depth analysis of network synchronization, with special attention for the Media Access Control (MAC) layer, is given in the next section.

# 2.2 MAC Layer Energy Consumption Model

Before data can be transferred between two nodes, they need to be synchronized. This can be achieved in either of two ways: synchronize the network just before the data transfer takes place, or keep the network synchronized continuously. The first case is an asynchronous or contention-based network; the sensor nodes ask for permission to start transmitting or the master node polls the sensor nodes for data when needed. The latter type is a synchronized, or schedule-based network, i.e. each node knows when it can transfer the data, for example in a Time Division Multiple Access (TDMA) protocol.

The MAC-layer protocol, and therefore synchronization type, has a big influence on the power consumption. Depending on the type of synchronization, power is wasted because of:

- idle listening

- · overhearing

- · synchronization overhead

In an asynchronous network the idle listening and overhearing penalties can have a big influence on the power consumption. Since each node does not know when it needs to listen for incoming data it needs to listen regularly even when there is no data present. Additionally, a node also does not know when other nodes do get a transmission slot. Therefore, the sensor nodes can overhear packets meant for another node and react on it. Examples of asynchronous MAC protocols targeted towards sensor networks are B-MAC [6] and X-MAC [7].

The idle listening can be reduced by adding a very-low-power receiver to the wireless sensor node. The receiver only listens for wake-up calls (WUC) from the master node and wakes-up the rest of the sensor when needed. Additionally, this wake-up receiver (WURx) can reduce the overhearing penalty when an address is added to the WUC. It is only beneficial to add a WURx, when its power consumption is less than the idle listening and overhearing penalties.

On the other hand, in a synchronous network, the master needs to assign slots to nodes and the nodes need to listen for synchronization beacons. This synchronization overhead consumes power. Furthermore, when the synchronization between a sensor node and the network master is lost, the node needs to listen continuously for the next synchronization beacon.

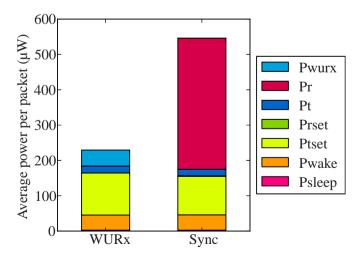

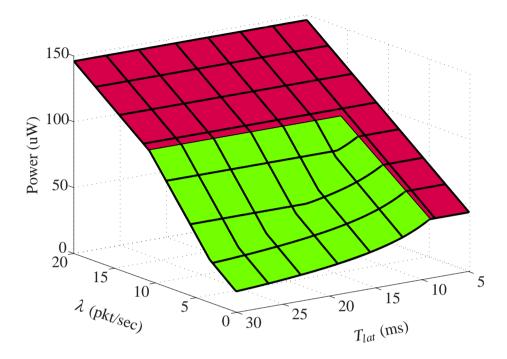

Within this section the power consumption of each type of network synchronization is modeled. The energy consumption of the node is calculated per received packet, taking into account the maximally allowed link-setup latency  $T_{lat}$ , the

number of nodes  $N_{node}$  and the average packet rate  $\lambda$ . The energy needed to transmit the data is not taken into account since it is equal for both synchronization schemes.

Firstly, address coding and required address length are discussed. Next, the traffic statistics and generic radio model are presented. The radio and traffic model are used to obtain the energy consumption models for the different network types. These models are eventually used in the following sections to explore the design space and determine in what cases which network type is optimal.

### 2.2.1 Address Coding

Each node has a unique address to reduce the overhearing penalty. The node correlates the received address with its own address, and compares the result to a threshold. If the correlation is higher than the threshold, the node is woken up. Although maximum likelihood decoding leads to more reliable results than correlation decoding, it is also much more complex and power consuming. Therefore, correlation decoding is chosen. Correlation coding is very similar to minimum distance or Hamming codes.

A correlation decoding function can be implemented power efficiently by NXOR operations,

$$C = \sum_{n=1}^{l} a_n \text{ NXOR } r_n,$$

where l is the address length,  $r_n$  the received address bit and  $a_n$  the address bit of the node. The output of the correlation function is the number of correct bits, and the maximal value is l. The minimum number of bits that differ between two addresses is called the Hamming distance, and is denoted by M. A code can correct  $\lfloor \frac{1}{2}(M-2) \rfloor$  errors and detect (M-1) errors. It is better to choose an odd Hamming distance M, since it can correct as many bits as a longer code with distance M+1. The correlator threshold T has to be in the range:  $l-M \leq T < l$  to make sure the node wakes up only if its own address is received. In practice, noise will induce bit errors which can lead to a missed wake-up call or a false wake-up, with probabilities  $p_{miss}$  and  $p_{false}$  respectively.

#### **Number of Nodes**

The maximum number of addresses, and therefore sensor nodes, depends on the address length l and the minimal number of different bits between two addresses

*M*. It is impossible to give an exact number of possible addresses, this problem is known as the sphere packing problem; the number of available addresses is equal to the number of spheres with diameter *M* that can be packed in a *l* dimensional space where each dimension has only two states: "0" or "1".

However, an upper bound can be given: the number of addresses with Hamming distance M ( $N_{nodes}$ ) is less than the total number of nodes divided by the number of nodes in a sphere with radius  $\lfloor \frac{M-1}{2} \rfloor$ . The radius is rounded half down, since the number of bits is integer and the radius of two neighboring addresses should be less or equal to the Hamming distance between the addresses. The radius is the Hamming distance divided by two, since the distance between the centers of two equally sized and neighboring spheres is the sum of their radii.

The total number of possible unique nodes without taking into account the Hamming distance is

$$N_{nodes,max} = 2^l, (2.1)$$

and the number of addresses in a sphere with radius  $\lfloor \frac{M-1}{2} \rfloor$  is

$$N_{nodes,sphere} = \sum_{n=0}^{\lfloor \frac{M-1}{2} \rfloor} {l \choose n}.$$

Combining the total number of nodes and the nodes per sphere, an upper bound on the number of nodes with Hamming distance *M* is

$$N_{nodes} \le \frac{2^{l}}{\sum_{n=0}^{\lfloor \frac{M-1}{2} \rfloor} \binom{l}{n}}.$$

(2.2)

#### **Coding Performance**

A WUC is missed when the correct address was sent but the output X of the correlator is smaller than the threshold T. Noting that the bit errors have a binomial distribution with success probability p and number of trials n, and the probability of a single bit error is given by  $p_e$ , the miss probability is

$$p_{miss} = P(X \le T | p = 1 - p_e, n = l).$$

(2.3)

Additionally, the probability a WUC is missed after  $N_{WUC}^+$  attempts is

$$p_{wuc,miss} = p_{miss}^{N_{WUC}^+}$$

.

It is more difficult to calculate the false wake-up probability than the packet miss probability. The probability of a false wake-up is highest when a 'neighboring' address with Hamming distance M is received; this case is taken as a conservative false wake-up estimation. Since the distance is equal to M the received and actual addresses share l-M bits. It is assumed that the false wake-up probability when a non-neighboring address is send is negligible.

The false wake-up event can be divided in two independent events: a false wake-up with all the shared bits correctly received, and one with the shared bits containing bit errors. The false wake-up probability is the sum of the probabilities of these two events. Assuming none of the shared bits change and only the unique bits change, the node is woken up when bit errors change T - (l - M) unique bits and  $p_{false}$  is

$$p_{false}|_{\text{No shared bits change}} = P(X > T - (l - M)|p = p_e, n = M) \times P(Y = 0|p = p_e, n = l - M),$$

(2.4)

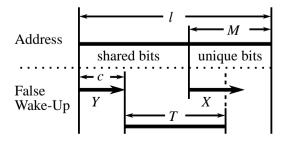

where X specifies the number of unique bits that change and Y specifies the number of shared bits that change, see figure 2.1. When c shared bits change also c extra unique bits have to change. The probability on this event is

$$p_{false}|_{\text{c shared bits change}} = P(X > T + c - (l - M)|p = p_e, n = M) \times P(Y = c|p = p_e, n = l - M).$$

(2.5)

The maximal number of changed shared bits is by definition smaller than the number of shared bits

$$c < l - M$$

.

Additionally, for a false wake-up to occur,

$$c + T < l$$

,

**Figure 2.1:** Address coding and the false wake-up event

should hold, see figure 2.1. Combining these bounds, c is bound by

$$c < \min \{l - M, l - T\}.$$

No longer assuming that only the shared bits can change,  $p_{false}$  becomes

$$p_{false} = \sum_{c=0}^{\min(l-M, l-T)} P(X > T + c - (l-M)|p = p_e, n = M) \times P(Y = c|p = p_e, n = l-M).$$

(2.6)

When the bit error probability is less than 1% and the address length is large enough, e.g. larger than 10,  $p_{false}$  can be approximated

$$p_{false} \approx P(X > T - (l - M)|p = p_e, n = M)P(Y = 0|p = p_e, n = l - M).$$

The approximation error is less than 0.4% when l = 10 and  $p_e = 1\%$ .

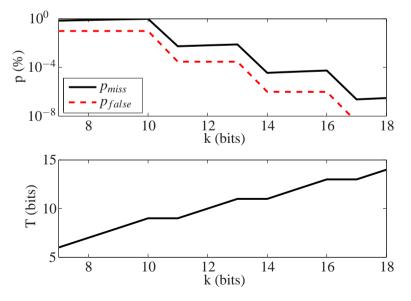

It is clear that the probabilities  $p_{miss}$  and  $p_{false}$  depend on the address length and the bit error rate (BER). Depending on the application the threshold T can be changed to sacrifice  $p_{miss}$  for  $p_{false}$  or vice versa. Here we assume that both probabilities need to be low, thus the threshold T is chosen in a way to equate

**Figure 2.2:**  $p_{miss}$ ,  $p_{false}$  and T as function of the address length l for a network of 100 nodes and a BER of 0.1%. T is chosen in a way to equate both error probabilities.

both error probabilities. Taking into account that most WBAN have less than 100 nodes [1] and a BER of  $10^{-3}$ , figure 2.2 gives the error probabilities as a function of the address length. For the minimal address length both  $p_{miss}$  and  $p_{false}$  are less than 1%, which is already acceptable. Adding extra bits decreases both the probabilities. However, the effect on the energy dissipation will be negligible since the error is already very low. Taking a Hamming distance of 3, an address length of 10 bits is good enough.

#### 2.2.2 Radio Model

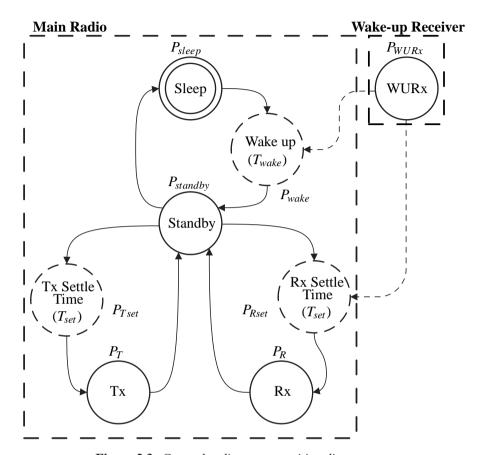

The state-transition diagram of a generic radio is shown in figure 2.3, and the corresponding parameters are listed in table 2.1. The initial start-up behavior is not shown; it is assumed that the radio is already initialized and that the main radio starts in the sleep state. There are two radios depicted in the diagram: the main radio and the WURx. Since the wake-up receiver is optional, it is placed outside the main radio whose states are depicted within the large dashed rectangle. The additional WURx can trigger the main radio to wake up or go into

**Table 2.1:** Radio platform parameters

| Parameter                         | Explanation                                              |  |

|-----------------------------------|----------------------------------------------------------|--|

| $T_{wake}$                        | Switching duration: Sleep → Standby                      |  |

| $T_{set}$                         | Switching duration: Settling period when switching to Rx |  |

|                                   | or Tx.                                                   |  |

| $P_{sleep}$                       | Power consumption in sleep mode.                         |  |

| $P_{standby}$                     | Power consumption in standby mode.                       |  |

| $P_R$                             | Power consumption in receive mode.                       |  |

| $P_T$                             | Power consumption in transmit mode.                      |  |

| $P_{Rset}$                        | Power consumption when switching to Rx mode.             |  |

| $P_{Tset}$                        | Power consumption when switching to Tx mode.             |  |

| $P_{wake}$                        | Power consumption when switching between sleep and       |  |

|                                   | standby mode.                                            |  |

| $\Delta P_{\scriptscriptstyle X}$ | Power increase in mode x compared to sleep mode $P_x$ –  |  |

|                                   | $P_{sleep}$                                              |  |

| k                                 | Length of minimal packet in bits. Used for: sync, ACK,   |  |

|                                   | WUC                                                      |  |

| $R_b$                             | Bit rate of main radio                                   |  |

Figure 2.3: General radio state-transition diagram.

receive mode depending on the current state of the main radio.

The states with a solid line are stable radio states, i.e. the radio can be in these states for an arbitrary amount of time. The dotted lines are transition states, and the time spent in this state is given within brackets. Furthermore, the power consumption in each state is given outside the states.

In the sleep mode the radio is in its lowest power down state, while in the standby mode the receiver consumes more power. On the other hand, the radio can wake-up faster from the standby mode than from the sleep mode. Therefore, using the sleep mode can be disadvantageous because the energy needed for waking up might be larger than the energy saved by staying in the sleep mode instead of the standby mode. In the following sections the conditions for which the sleep mode is advantageous are analyzed.

Some radios may not provide a sleep and standby mode or may not need settling time between receive and transmit modes.  $T_{wake}$  should be set to zero in the former case and  $T_{set}$  should be set to zero in the latter case. When the radio is always on and does not need to settle, both of the parameters should be set to zero.

In this thesis the Nordic nRF24L01 radio chip is used in the application analysis, but the radio parameters are general enough to allow for other radios.

#### 2.2.3 Network Statistics

In an asynchronous network the master node transmits wake-up calls (WUC) and waits for the node to transmit an acknowledgment (ACK). When a WUC or ACK packet gets missed with probability  $p_{miss}$ , they need to be retransmitted. However the maximum number of transmissions is limited to  $N_{WUC}^+$ ; after this number of transmissions the transmitter quits and the wake-up process has failed. In each WUC a counter value is transmitted which specifies the number of transmissions left. Using this counter value the receiver knows exactly how many times it can try to transmit an acknowledgment. The node will transmit the acknowledgments until either the connection is set-up or the maximum number of transmissions is reached.

It is also possible for the node to wake up when a WUC is received which was meant for another node: a false wake up. After such an event the node starts transmitting false acknowledgment (FACK) packets. The false wake-up event leads to the overhearing penalty previously mentioned. The probability of a false wake up is given by  $p_{false}$ .

Table 2.2 gives a list of asynchronous and synchronous MAC layer packet statistics expressed as functions of  $p_{miss}$ ,  $p_{false}$  and the maximal number of transmissions  $N_{WUC}^+$ . The probabilities and statistics are derived in appendix A.

The synchronous MAC protocol is discussed in-depth in section 2.2.6. The expected number of TDMA slots per received packet is given by  $\mu_{slot}$ , which is very similar to the expected number of wake up calls. The variable  $\mu_{slot}$  is derived in appendix A.4 and is approximately

$$\mu_{slot} \approx \frac{1 - p_{miss}^{N_{WUC}^+}}{1 - p_{miss}},$$

assuming  $N_{WUC}^+ > 1$  and  $p_{miss} \lesssim 1\%$ .

| Statistic       | Probability/Value                                      | Explanation                                                                                        |

|-----------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------|

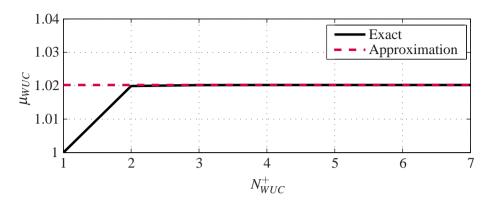

| $\mu_{WUC}$     | $pprox rac{1+p_{miss}}{1-p_{miss}}$                   | Average number of WUC transmissions per received packet.                                           |

| <i>PACK</i> ≥1  | $1-p_{miss}^{N_{WUC}^+}$                               | Probability that the sensor node transmits at least one ACK packet.                                |

| <i>PFACK</i> ≥1 | $pprox p_{false}$                                      | Probability that the sensor node transmits at least one false ACK packet.                          |

| $\mu_{ACKx}$    | $pprox rac{p_{miss}}{1-p_{miss}}$                     | Average number of retransmitted acknowledgments per received packet.                               |

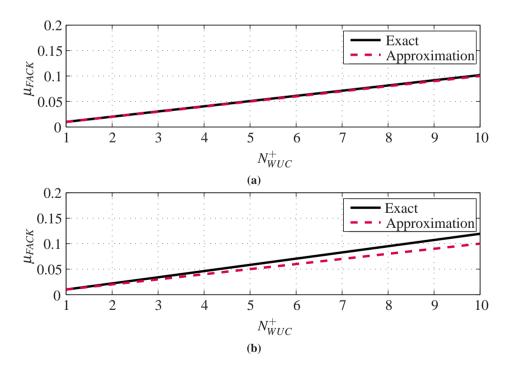

| $\mu_{FACKx}$   | $\approx p_{false} \left( N_{WUC}^+ - 1 \right)$       | Average number of retransmitted false acknowledgments per received packet and node in the network. |

| $\mu_{slot}$    | $\approx \frac{1 - p_{miss}^{N_W^+ UC}}{1 - p_{miss}}$ | Expected number of TDMA slots per received packet.                                                 |

**Table 2.2:** *List of the used asynchronous (top) and synchronous (bottom) MAC layer packet statistics.*

### 2.2.4 WURx-enhanced Asynchronous Network

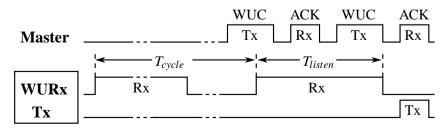

In the WURx-enhanced scheme, a WURx is added to the sensor node, which is used to listen for wake-up calls and waking up the sensor node when needed. There are two sub-categories of the WURx-enhanced MAC scheme: with and without main receiver. When the node needs to receive a lot of data and the low bit rate of the WURx is not sufficient an additional receiver can be added at the cost of higher power consumption. When the node is woken-up it transmits an acknowledgment and the data transfer can commence. Figure 2.4 shows a

**Figure 2.4:** *Wake-up event for a WURx-enhanced MAC protocol.*

simplified overview of a wake-up event when the WURx enhanced scheme is used. To save power the WURx can be duty-cycled when the latency requirement allows for it, as is shown in the figure. The duty cycle period is chosen as long as possible to minimize the power consumption. Additionally the master needs to be able to transmit  $N_{WUC}^+$  calls within the latency requirement. Therefore, the cycle period is chosen equal to the latency requirement  $T_{lat}$  divided by the maximum number of attempts, i.e.

$$T_{cycle} = rac{T_{lat}}{N_{WUC}^+} \, .$$

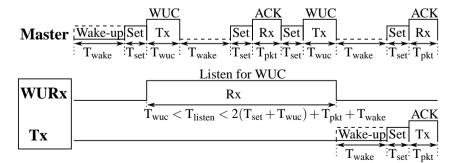

A detailed wake-up cycle is shown in figure 2.5. The radio parameters correspond with the parameters used in the radio state model depicted in figure 2.3. The wake-up periods are only present when the nodes go to the deep sleep mode. To ensure that the WURx will also wake up the node when the listen cycle starts in the middle of a WUC packet, at least two WUCs have to fit within the listen period  $T_{listen}$ ,

$$T_{listen} > 2(T_{set} + T_{wuc}) + T_{pkt} + T_{wake}$$

. (2.7)

Additionally, the listen period can never be longer than the complete cycle

$$T_{listen} \le T_{cycle}$$

, (2.8)

and the duty cycle ratio  $\eta$ , the fraction of time a sensor node is active, is

$$\eta = rac{N_{WUC}^{+}T_{listen}}{T_{lat}} \ = rac{T_{listen}}{T_{cycle}} \, .$$

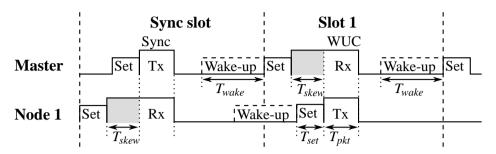

**Figure 2.5:** *Detailed view of a wake-up event.*

The packet lengths k of the WUC and ACK are assumed to be equal. However, the bit rates of the main radio  $R_b$  and WURx  $R_{bw}$  can be different and therefore the WUC and ACK packet durations can be different,

$$T_{wuc} = rac{k}{R_{bw}}$$

$T_{pkt} = rac{k}{R_b}$ .

A lower bound on the required  $R_{bw}$  is obtained by combining (2.7) and (2.8)

$$R_{bw} \ge \frac{2k}{T_{cycle} - 2T_{set} - T_{wake} - T_{pkt}}. (2.9)$$

The average energy dissipation per received packet is obtained by assuming that on average each node receives the same number of packets and a packet is received every  $\frac{1}{\lambda}$  seconds. The dissipation of the sensor node is divided in 4 parts,

$$E_{node} = \frac{P_{sleep}}{\lambda} + \eta \frac{P_{WURx}}{\lambda} + \left[ p_{ACK \ge 1} + p_{FACK \ge 1} \left( N_{nodes} - 1 \right) \right] E_{ACK1}$$

$$+ \left[ \mu_{ACKx} + \mu_{FACKx} \left( N_{nodes} - 1 \right) \right] E_{ACKx}, \qquad (2.10)$$

the first term specifies the transceiver energy consumption in sleep mode, the second term the energy consumption of the duty-cycled WURx, the third term is the energy required when transmitting the first acknowledgment and the fourth and final term specifies the energy needed for retransmitting the acknowledgments. The false acknowledgment statistics  $p_{FACK \ge 1}$  and  $\mu_{FACKx}$  were defined per 'other node' in the network. Therefore, they are multiplied by number of 'other nodes', or the total number of nodes minus 1. The expected number of transmitted acknowledgments and retransmitted acknowledgments are derived in section 2.2.3, and the energy consumed per acknowledgment is

$$E_{ACK1} = \Delta E_{wake} + \Delta E_{Tset} + T_{pkt} \Delta P_{T}$$

$$E_{ACKx} = (T_{wake} + T_{WUC} + T_{set}) \Delta P_{standby} + \Delta E_{Tset} + T_{pkt} \Delta P_{T}.$$

# 2.2.5 WURx-less Asynchronous Network

The asynchronous network scheme is very similar to the WURx-enhanced scheme, with the difference that the WURx is not present and the main receiver

**Figure 2.6:** Detailed view of a synchronization cycle for the WURx-less asynchronous MAC protocol.

listens for the wake-up calls. Therefore, in the asynchronous MAC protocol the WUC and ACK packets duration is the same. Although this scheme consumes more power than the WURx enhanced scheme, it has benefits for systems with very strict latency requirements since the wake-up time is shorter. Figure 2.6 shows the synchronization cycle.

The energy consumption of the sensor node is similar to the WURx-enhanced case (2.10)

$$\begin{split} E_{node} = & \frac{P_{sleep}}{\lambda} + \frac{1}{\lambda T_{cycle}} E_{cycle} + \left[ p_{ACK \geq 1} + p_{FACK \geq 1} \left( N_{nodes} - 1 \right) \right] E_{ACK1} \\ & + \left[ \mu_{ACKx} + \mu_{FACKx} \left( N_{nodes} - 1 \right) \right] E_{ACKx} \,, \end{split}$$

where the values  $p_{ACK \ge 1}$  and  $\mu_{ACKx}$  were derived in appendix **A** and summarized in table 2.2, and

$$\begin{split} E_{ACK1} &= \Delta E_{Tset} + T_{pkt} \Delta P_T \\ E_{ACKx} &= \left(T_{pkt} + T_{set}\right) \Delta P_{standby} + \Delta E_{Tset} + T_{pkt} \Delta P_T \\ E_{cycle} &= \Delta E_{wake} + \Delta E_{Rset} + T_{listen} \Delta P_R \,. \end{split}$$

# 2.2.6 Synchronous Network

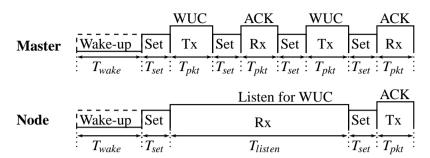

The synchronous MAC scheme is different from the two MAC schemes mentioned in the previous sections. The main difference is that the whole network is always synchronized, whereas in the asynchronous MAC protocols the transmitter and receiver are only synchronized before a transmission. Furthermore,

**Figure 2.7:** Synchronous MAC scheme in case of a wake-up event. As an example the timing diagrams of the master and node 1 are shown.

the system is highly asymmetric. Within this section the energy consumption of a sensor node in a low-power TDMA MAC protocol similar to [8] is presented. The energy consumption of the master node is not taken into account, since it is assumed that its power supply is much bigger than that of a wireless sensor node.

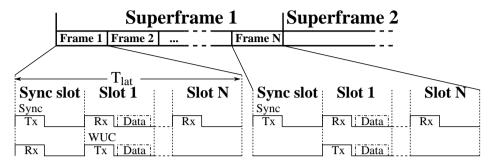

Figure 2.7 shows an overview of the synchronous scheme. The master node transmits synchronization beacons at known intervals to keep the network synchronized. Additionally, the master node assigns the time slots to the nodes in the network. Each frame is divided in multiple time slots; one for every node, within these slots only the assigned nodes can transmit their data. The nodes notify the master they have data to transmit using a wake-up call and then start sending the data.

A receiving node only needs to receive a synchronization beacon every superframe; the time between two beacons is determined by the stability of the local clock. The local clock accuracy given by  $\Theta$  is expressed in ppm. The maximally allowed clock skew is given by  $T_{skew}$ , which is used as guard time. A more detailed view is shown in figure 2.8. Again the wake-up periods are only present when the nodes go to deep sleep mode. The gray areas are needed to deal with clock skew. The latency has to be smaller than  $T_{lat}$ , and within the latency period all the  $N_{node}$  nodes need to be able to transmit  $N_{WUC}^+$  wake-up calls. Therefore, the TDMA slot time is

$$T_{slot} = \frac{T_{lat}}{N_{WUC}^{+}(N_{node} + 1)}.$$

It is assumed that the minimal time between two beacons is large enough to ensure correct transmission:  $T_{beacon} \gg \frac{T_{lat}}{N_{WUC}^+}$ . On the other hand, the maximum time between two synchronization beacons to keep the network synchronized is

**Figure 2.8:** Detailed view of the synchronous MAC scheme in case of a wake-up event with the radio state variables. The clocks of the master node and Node 1 are not fully synchronized.

a function of the clock accuracy and the time reserved for the clock skew:

$$T_{beacon} \leq \frac{T_{skew}}{\Theta(ppm)} 10^6$$

.

In the following analysis we assume the time between beacons is minimal to reduce the energy consumption. The average number of beacons per received packet  $\mu_{bcn/pkt}$  is

$$\mu_{bcn/pkt} = \frac{1}{\lambda T_{beacon}}.$$

When a node misses the synchronization beacon it stays in receive mode until it receives the next beacon in order to resynchronize. While resynchronizing, all the packets are lost. The probability of this event is assumed to be equal to the packet miss probability  $p_{miss}$ . If  $T_{beacon}$  is large, the resynchronization penalty is severe.

The average energy consumption of a sensor node, calculated per received packet is:

$$E_{node} = \frac{P_{sleep}}{\lambda} + \mu_{bcn/pkt} E_{sync} + p_{miss} \frac{\Delta P_R}{\lambda} + \mu_{slot} E_{slot}, \qquad (2.11)$$

where

$$E_{sync} = \Delta E_{wake} + \Delta E_{Rset} + (T_{skew} + T_{pkt}) \Delta P_R$$

$$E_{slot} = \Delta E_{wake} + \Delta E_{Tset} + T_{pkt} \Delta P_T.$$

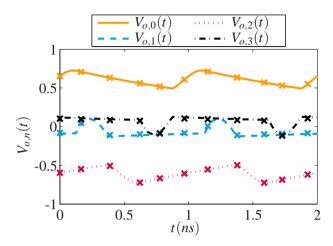

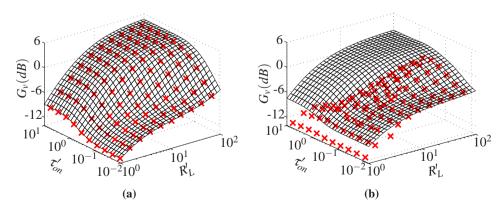

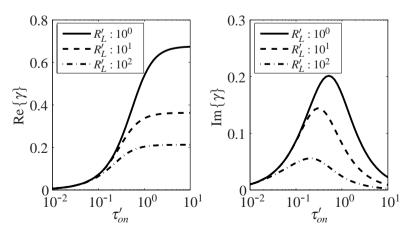

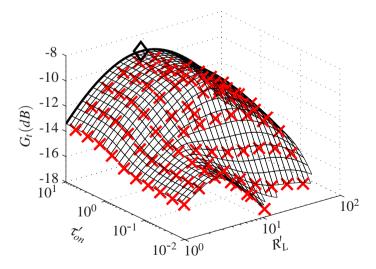

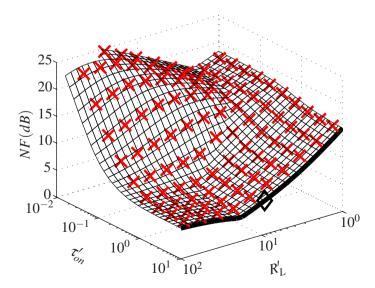

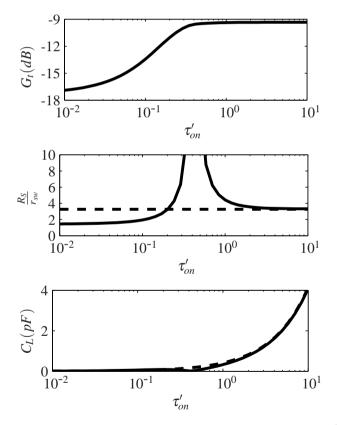

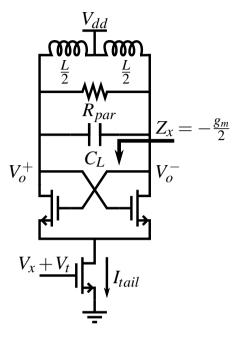

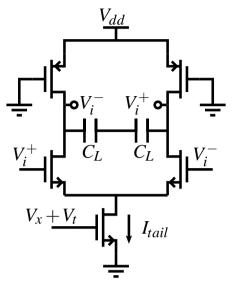

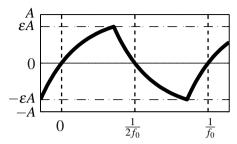

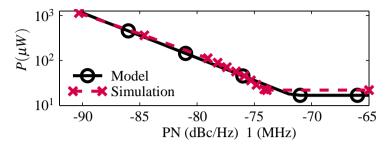

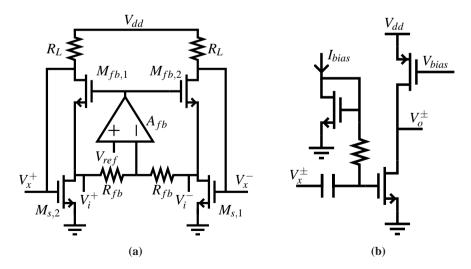

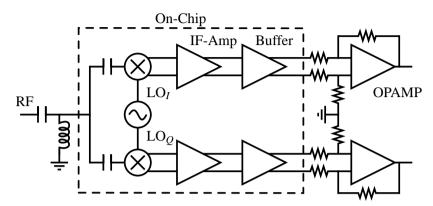

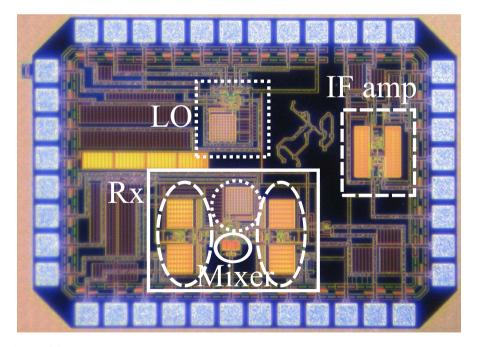

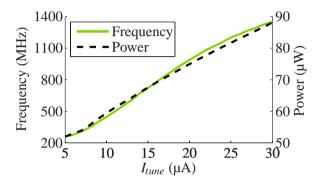

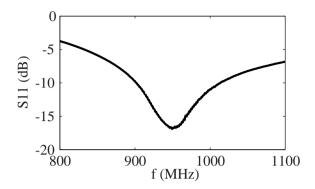

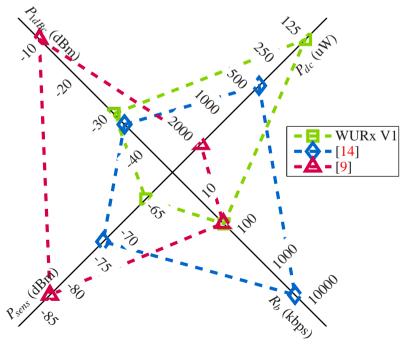

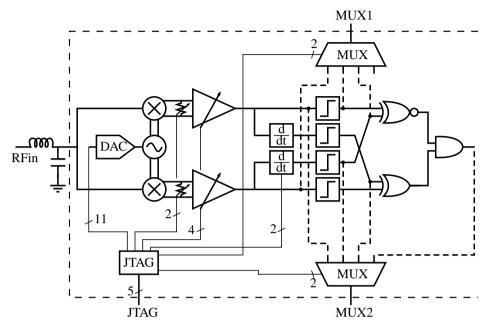

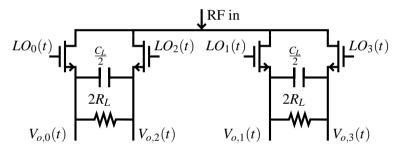

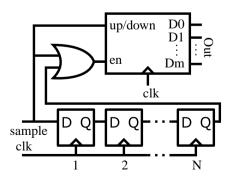

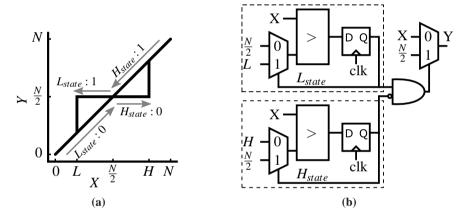

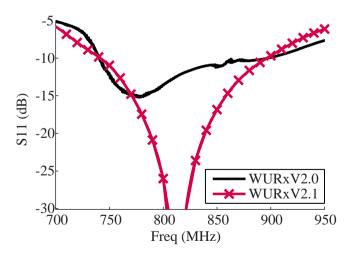

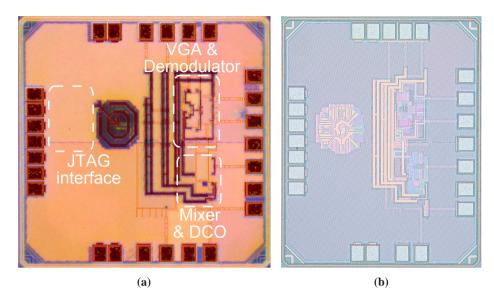

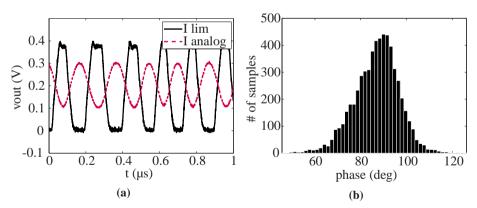

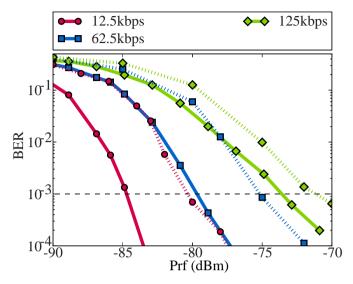

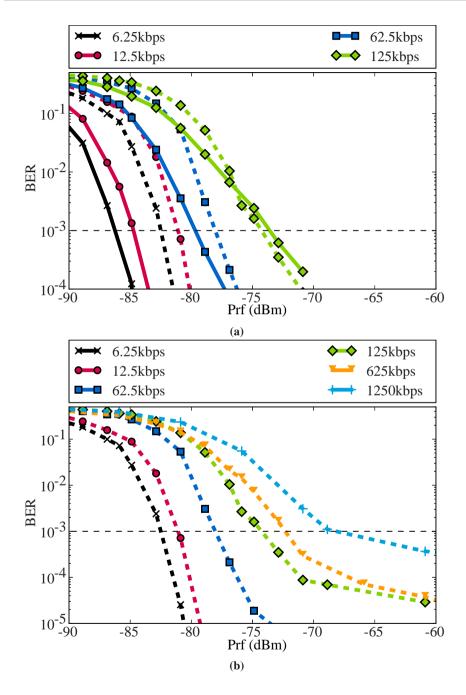

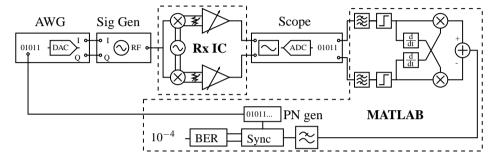

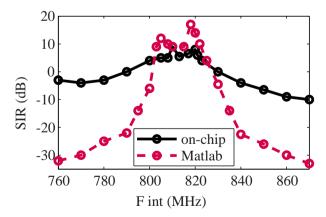

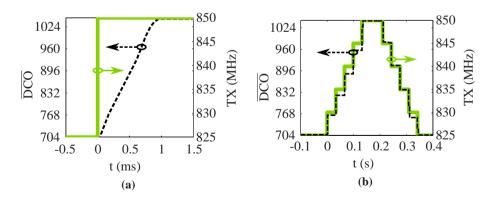

## 2.2.7 Application Example