# Power and area efficient reconfigurable delta sigma ADCs

Citation for published version (APA):

Porrazzo, S. (2013). Power and aréa efficient reconfigurable delta sigma ADCs. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR761378

DOI:

10.6100/IR761378

Document status and date:

Published: 01/01/2013

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 17. Nov. 2023

# POWER AND AREA EFFICIENT RECONFIGURABLE $\Delta \Sigma$ ADCs Serena Porrazzo

# POWER AND AREA EFFICIENT RECONFIGURABLE $\Delta\Sigma$ ADCs

### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de

Technische Universiteit Eindhoven, op gezag van de

rector magnificus prof.dr.ir. C.J. van Duijn,

voor een commissie aangewezen door het College

voor Promoties, in het openbaar te verdedigen op

dinsdag 26 november 2013 om 16:00 uur

door

Serena Porrazzo

geboren te Como, Italië

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. J.H. Blom

1e promotor: prof.dr.ir. A.H.M. van Roermund

copromotor: dr.ir. E. Cantatore

leden: dr.ir. M. Mischi

prof.dr.ir. G. Gielen (Katholieke Universiteit Leuven)

prof.dr. K.A.A. Makinwa (TU Delft)

prof.dr.ir. C. Van Hoof (Katholieke Universiteit Leuven)

adviseur: dr. R.F. Yazicioglu (imec)

### TABLE OF CONTENTS

| List of figures                                                         | ix              |

|-------------------------------------------------------------------------|-----------------|

| List of tables                                                          | xiii            |

| List of abbreviations.                                                  | xv              |

| List of symbols                                                         | xvii            |

| 1 Introduction                                                          | 1               |

| 1.1 Background                                                          | 2               |

| 1.1.1 Reconfigurability                                                 | 4               |

| 1.1.2 Power-efficiency and area-efficiency                              | 9               |

| 1.1.3 State-of-the-art reconfigurable ADCs                              | 12              |

| 1.2 Problem statement                                                   | 16              |

| 1.3 Aim of the thesis                                                   | 17              |

| 1.4 Scope of the thesis                                                 | 17              |

| 1.5 Approach                                                            | 19              |

| 1.6 Original contributions                                              | 20              |

| 1.7 Outline of the thesis                                               | 21              |

| 2 Power-efficient reconfigurable $\Delta\Sigma$ modulators for autonomo | ous             |

| biomedical applications                                                 | 23              |

| 2.1 $\Delta\Sigma$ modulation for reconfigurable and power-efficient h  | nigh-resolution |

| ADCs                                                                    | 24              |

| $2.2\Delta\Sigma$ ADCs: basics and topologies                           | 26              |

| 2.3 State-of-the-art reconfigurable $\Delta\Sigma$ modulators           | 30              |

| 2.4 Reconfigurable $\Delta\Sigma$ Ms for biomedical applications        | 32              |

| 2.5 Conclusion                                                          | 33              |

| 3 Power optimal design of SC $\Delta\Sigma$ modulators for given resolu | tion and        |

| bandwidth                                                               | 35              |

| 3.1 Introduction                                                        | 36              |

| 3.2 Power optimization method                                                     | 37    |

|-----------------------------------------------------------------------------------|-------|

| 3.2.1 Global design methodology                                                   | 38    |

| 3.2.2 Step 1 - Choosing OL, STF/NTF for each (N, B, OSR)                          | 42    |

| 3.2.3 Step 2 - Sizing of the sampling capacitors                                  | 44    |

| 3.2.4 Step 3 - Power consumption estimation                                       | 46    |

| 3.2.5 Static power                                                                | 47    |

| 3.2.6 Dynamic power                                                               | 58    |

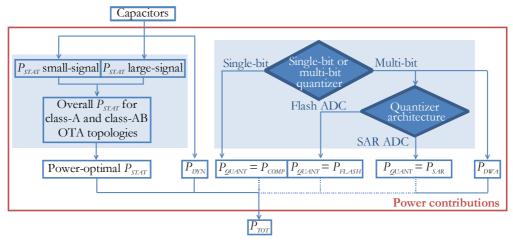

| 3.2.7 Quantizer power                                                             | 59    |

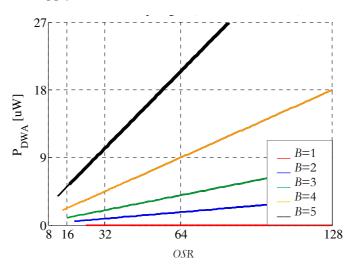

| 3.2.8 DWA Power                                                                   | 63    |

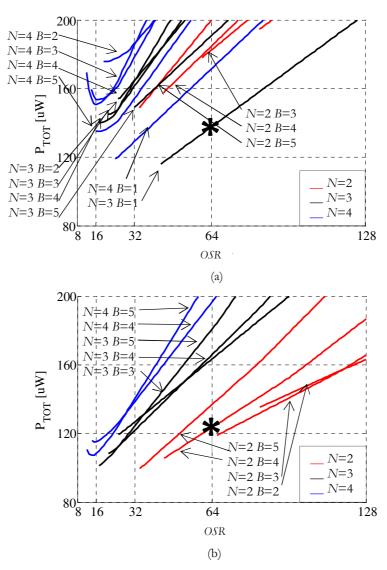

| 3.2.9 Total Power consumption                                                     | 65    |

| 3.2.10 Power optimization of a $\Delta\Sigma M$ for hearing aids application      | and   |

| impact of design parameters on power consumption                                  | 66    |

| 3.2.11 Results of the power optimization procedure                                | 76    |

| 3.3 Design techniques for power-efficient SC feed-forward $\Delta\Sigma Ms$       | 77    |

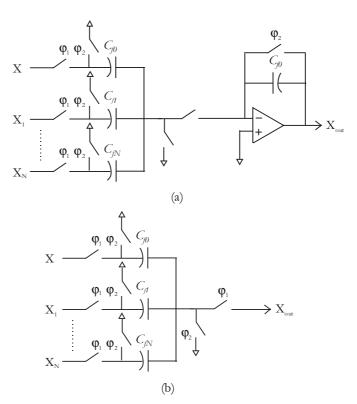

| 3.3.1 Active addition                                                             | 78    |

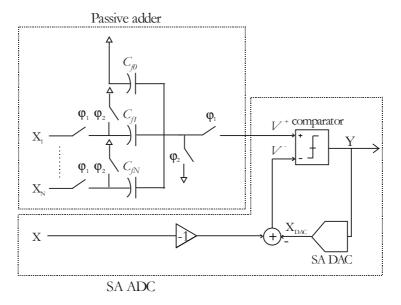

| 3.3.2 Passive addition                                                            | 79    |

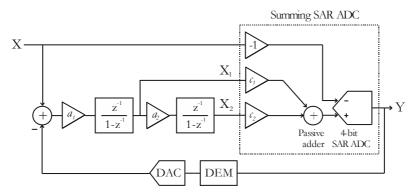

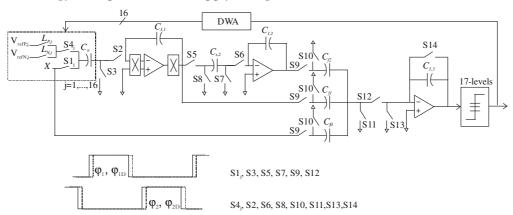

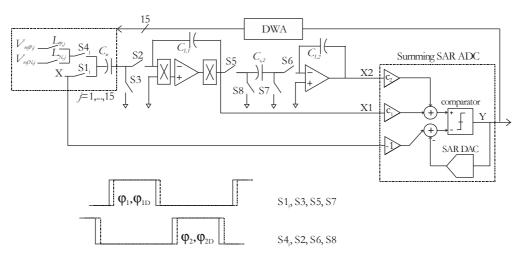

| 3.3.3 The summing SAR quantizer                                                   | 80    |

| 3.4 Design examples                                                               | 82    |

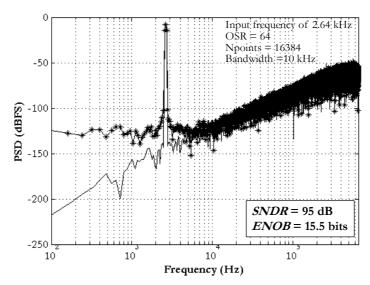

| 3.4.1 A 95dB DR 10-kHz SC $\Delta\Sigma$ M for digital hearing-aids application . | 83    |

| 3.4.2 A 1.8-V 88dB DR $\Delta\Sigma M$ for digital hearing aids using a r         | novel |

| summing SAR quantizer                                                             | 87    |

| 3.5 Conclusion                                                                    | 95    |

| 4 Power-efficient design of reconfigurable SC $\Delta\Sigma Ms$                   | 97    |

| 4.1 Introduction                                                                  | 98    |

| 4.2 Power efficient approach to reconfigurability                                 | 99    |

| 4.2.1 Overview of the methodology                                                 | 100   |

| 4.2.2 Case study: design of a reconfigurable $\Delta\Sigma M$ for a biomedical         |

|----------------------------------------------------------------------------------------|

| application set                                                                        |

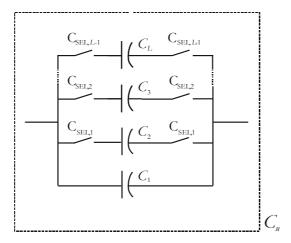

| 4.3 Circuit design techniques for power-efficient reconfigurable $\Delta\Sigma Ms$ 111 |

| 4.3.1 Modular C <sub>s,1</sub> implementation                                          |

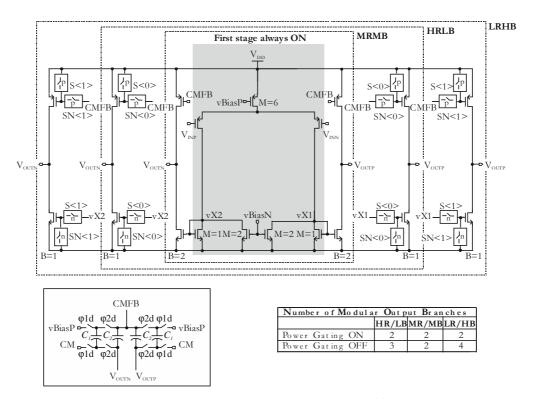

| 4.3.2 Programmable OTAs for power- and speed-scalability                               |

| 4.4 Design example: a 1-V 99-to-75 dB SNDR 256-to-16kHz reconfigurable                 |

| $\Delta\Sigma M$                                                                       |

| 4.5 Conclusion                                                                         |

| 5 Conclusions 131                                                                      |

| References                                                                             |

| Publications list                                                                      |

| Summary                                                                                |

| Curriculum Vitae                                                                       |

# List of figures

| Fig. 1. Conversion bandwidth versus $SNDR$ performance of state-of-the-art           |

|--------------------------------------------------------------------------------------|

| ADCs6                                                                                |

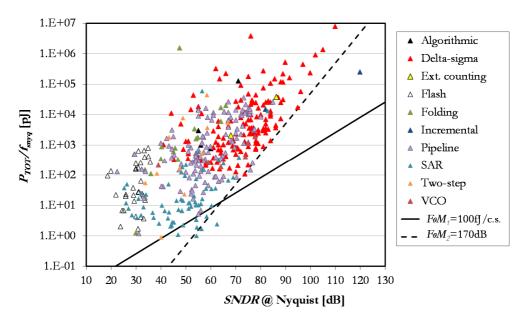

| Fig. 2. Power-efficiency versus <i>SNDR</i> performance of state-of-the-art ADCs10   |

| Fig. 3. Power-efficiency versus SNDR performance of state-of-the-art tailored        |

| (ISSCC- VLSI 1997-2012) and reconfigurable ADCs13                                    |

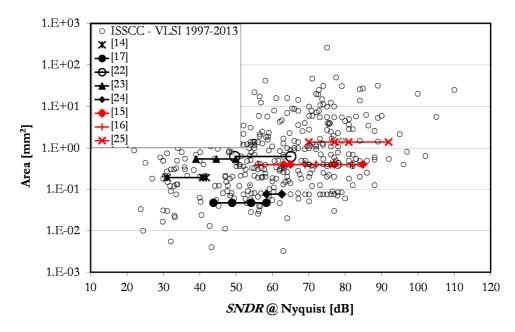

| Fig. 4. Area-efficiency versus $SNDR$ performance of state-of-the-art tailored       |

| (ISSCC- VLSI 1997-2012) and reconfigurable ADCs15                                    |

| Fig. 5. Power-efficiency versus SNDR performance of state-of-the-art ADCs24          |

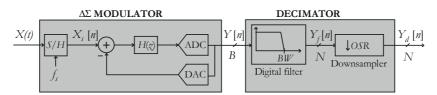

| Fig. 6. Generic scheme of a $\Delta\Sigma$ ADC                                       |

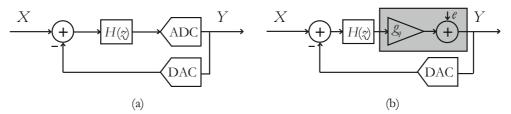

| Fig. 7. $\Delta\Sigma M$ architecture (a) Basic scheme, (b) Linear model             |

| Fig. 8. State-of-the-art reconfigurable ADCs for multi-standard applications.        |

| Continuous-time $\Delta\Sigma$ architectures are depicted in red, discrete-time      |

| $\Delta\Sigma Ms$ in black; single-loop topologies are represented as empty shapes,  |

| cascade as filled shapes                                                             |

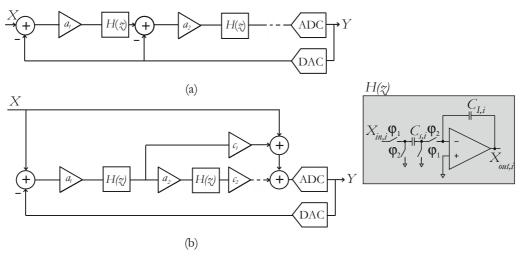

| Fig. 9. Conventional FB (a) and FF (b) single loop $\Delta\Sigma$ modulators. The    |

| implementation of the SC integrators $H(z)$ is shown the inset37                     |

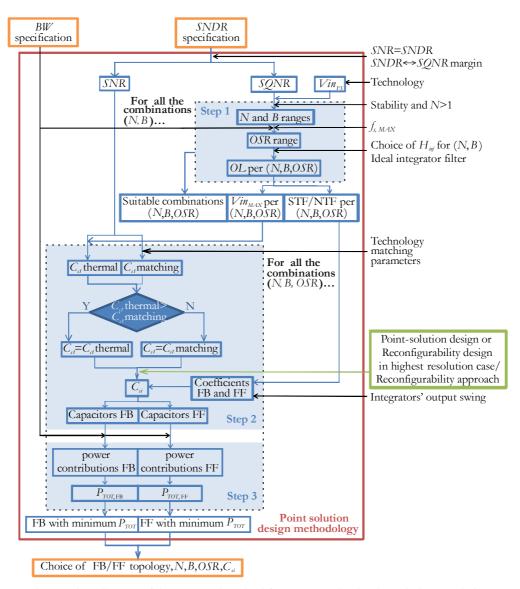

| Fig. 10. Flow diagram of the proposed method for power-optimal point-solution        |

| $\Delta\Sigma$ designs. The index $i$ ( $i=1,,N$ ) indicates the position of each    |

| integrator in the $\Delta\Sigma M$ starting from the input                           |

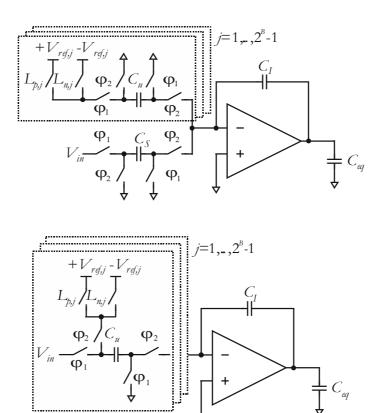

| Fig. 11. Different feedback configurations of an SC integrator. A single-ended       |

| implementation is shown for simplicity. $L_{p,j}$ and $L_{n,j}$ are feedback signals |

| driving the DAC ( $j=1,, 2^{B}-1$ )45                                                |

| Fig. 12. Flow diagram of the procedure to calculate the power contributions of       |

| the $\Delta\Sigma M$                                                                 |

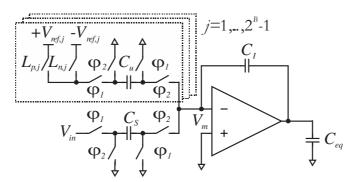

| Fig. 13. Single-ended implementation of an SC integrator. The feedback signal         | ls |

|---------------------------------------------------------------------------------------|----|

| $L_{p,j}$ and $L_{n,j}$ are controlled by the digital output code of the quantizer 50 | )  |

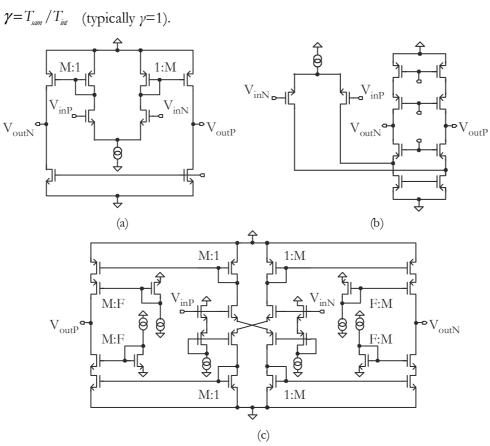

| Fig. 14. Simplified circuit schematic for current-mirror (a) OTA, folded-cascod       | e  |

| OTA (b) and Castello OTA (c) [58]5                                                    | 7  |

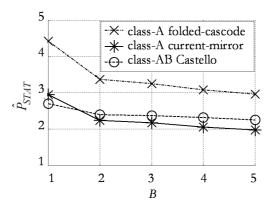

| Fig. 15. Normalized power dissipation of class-A and class-AB topologies as           | a  |

| function of B for $N=3$                                                               | 3  |

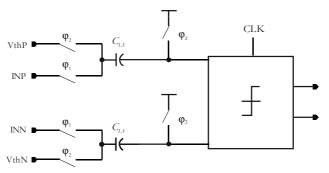

| Fig. 16. Circuit implementation of the fully-differential comparator60                | )  |

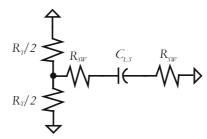

| Fig. 17. Simplified model of the resistor ladder generating the thresholds of the     | e  |

| flash ADC62                                                                           | l  |

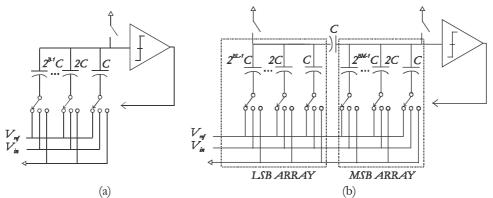

| Fig. 18. Schematic representation of a SAR ADC using (a) a conventional $B$ -b        | it |

| binary weighted capacitor DAC (b) a "split" B-bit capacitor DAC wit                   | h  |

| unit value bridge capacitor                                                           | 2  |

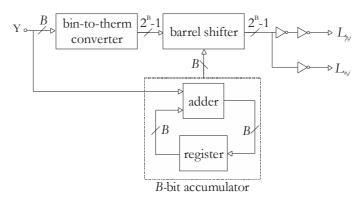

| Fig. 19. Practical implementation of the DWA64                                        | 1  |

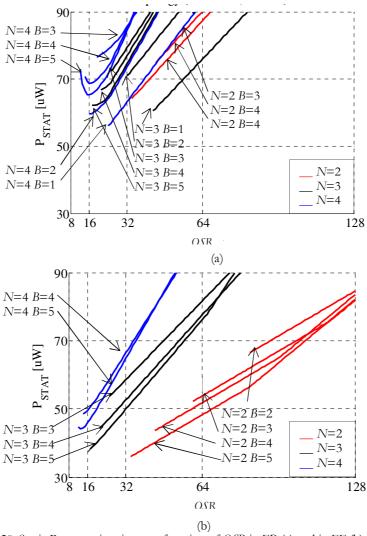

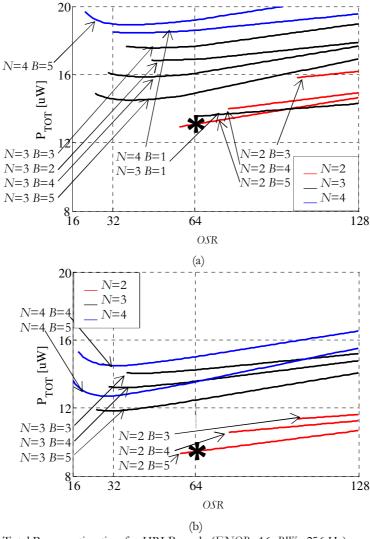

| Fig. 20. Static Power estimation as a function of OSR in FB (a) and in FF (b)         | )  |

| implementations 69                                                                    | )  |

| Fig. 21. Dynamic Power estimation as a function of OSR in FB (a) and in FF (b)        | )  |

| implementations                                                                       | )  |

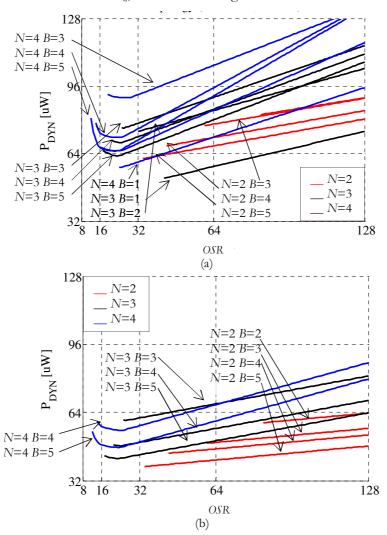

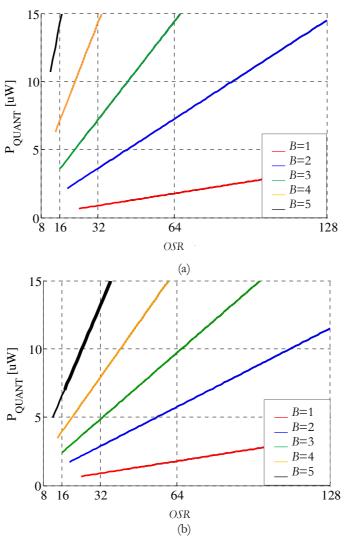

| Fig. 22. Flash quantizer(a) and SAR quantizer (b) Power estimation as a function      | n  |

| of OSR in FB and FF implementations                                                   | l  |

| Fig. 23. DWA Power estimation as a function of OSR in FB and in F                     | F  |

| implementations                                                                       | 2  |

| Fig. 24. Total Power estimation as a function of OSR in FB (a) and in FF (b)          | )  |

| implementations. The minimum power consumption for both cases                         | is |

| marked with an asterisk                                                               | 3  |

| Fig. 25.Second-order 4-bit FF architecture                                            | 3  |

| Fig. 26. Active addition (a) and passive addition (b)                                 | )  |

| Fig. 27. Simplified representation of the summing SAR ADC80                           | )  |

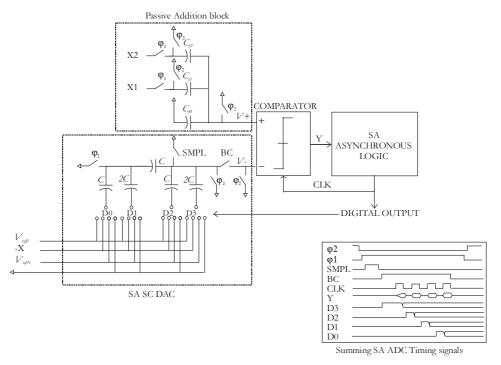

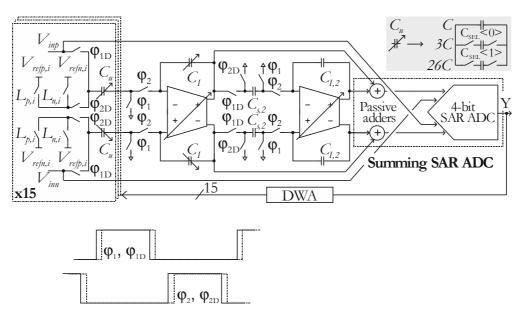

| Fig. 28. SC implementation of the FF modulator                                                 |

|------------------------------------------------------------------------------------------------|

| Fig. 29. Output spectra obtained by transistor-level simulation in Cadence                     |

| environment (curve with asterisk marks) and by behavioural simulation in                       |

| Simulink environment (solid line)                                                              |

| Fig. 30. SC implementation of the $\Delta\Sigma M$                                             |

| Fig. 31. Single-ended implementation of the Summing SAR ADC90                                  |

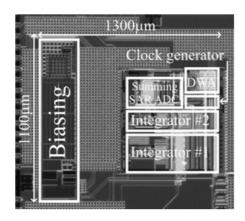

| Fig. 32. Microphotograph of the implemented $\Delta\Sigma M$                                   |

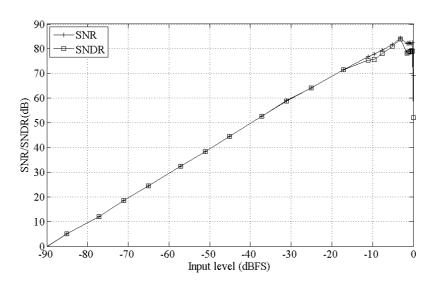

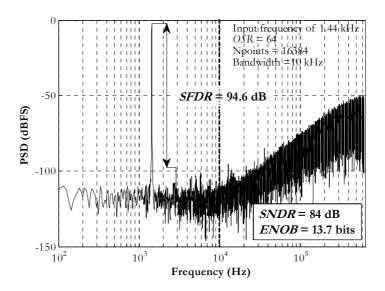

| Fig. 33. Measured SNR/SNDR characteristic versus input amplitude92                             |

| Fig. 34. Measured output spectrum for -3.2-dBFS input level92                                  |

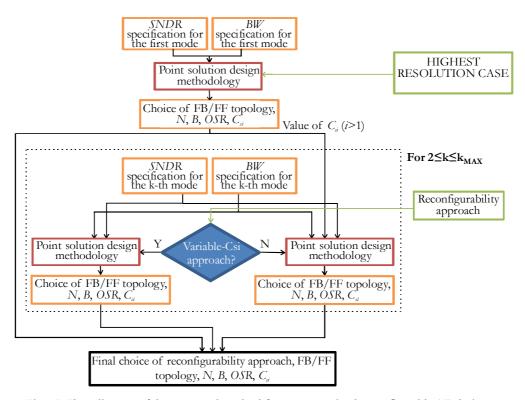

| Fig. 35. Flow diagram of the proposed method for power-optimal reconfigurable                  |

| $\Delta\Sigma$ designs                                                                         |

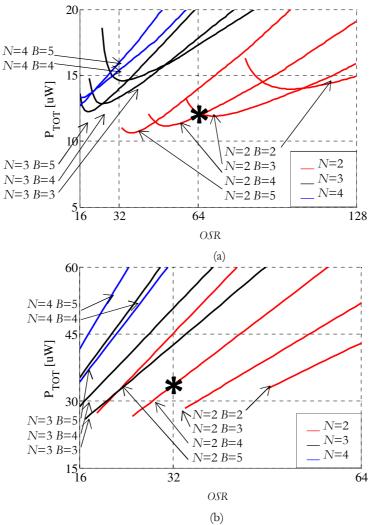

| Fig. 36. Total Power estimation for HRLB mode ( $ENOB=16$ , $BW=256$ Hz) as a                  |

| function of OSR in FB (a) and in FF (b) implementations105                                     |

| Fig. 37. Variable-C <sub>s,t</sub> approach: Total Power estimation as a function of OSR using |

| FF implementations for (a) MRMB mode (ENOB=14, BW=2 kHz) and                                   |

| (b) LRHB mode ( <i>ENOB</i> =12, <i>BW</i> =16 kHz)107                                         |

| Fig. 38. SC implementation of the programmable first-integrator $C_n$                          |

| Fig. 39. Programmable gain-enhanced current mirror OTA schematic115                            |

| Fig. 40. SC implementation of the $\Delta\Sigma M$                                             |

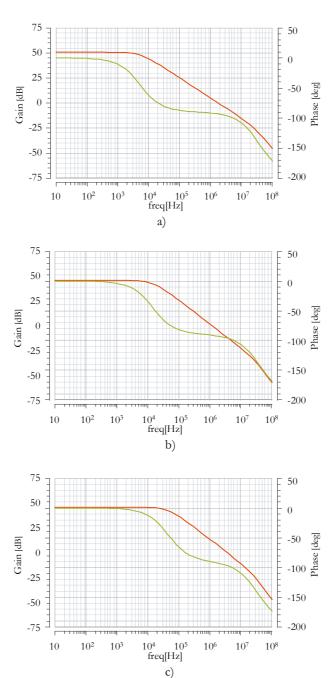

| Fig. 41. OTAs frequency response in HRLB mode (a) MRMB mode (b) and                            |

| LRHB mode (c)119                                                                               |

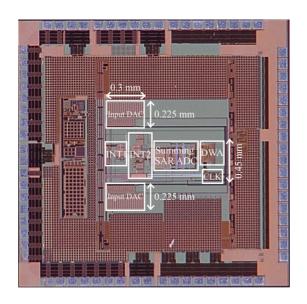

| Fig. 42. Microphotograph of the reconfigurable $\Delta\Sigma M$                                |

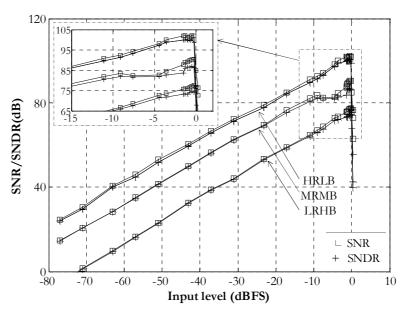

| Fig. 43. Measured <i>SNR/SNDR</i> vs. input amplitude                                          |

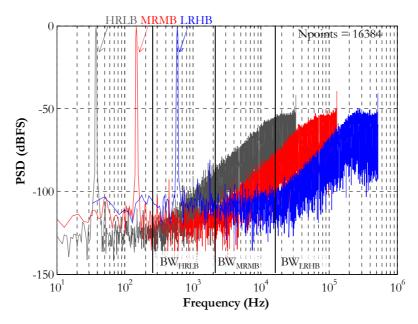

| Fig. 44. Measured spectra at peak SNDR for HRLB (grey curve), MRMB (red                        |

| curve) and LRHB modes (blue curve) for -0.5-dBES input level 122                               |

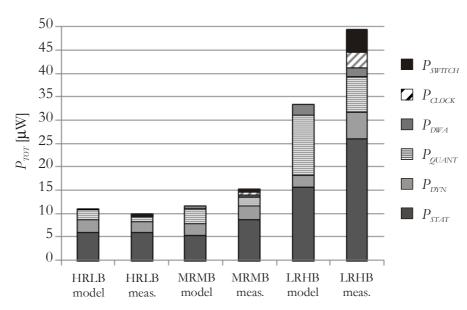

| Fig. 45. Power consumption breakdown: comparison between theoretical model |

|----------------------------------------------------------------------------|

| and transistor-level implementation in HRLB, MRMB and LRHB modes.          |

| 124                                                                        |

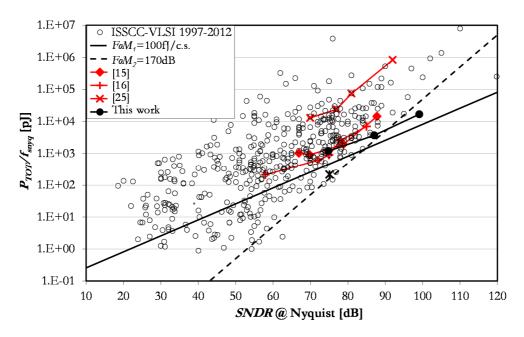

| Fig. 46. Power-efficiency versus SNDR performance of this work compared to |

| state-of-the-art tailored (ISSCC- VLSI 1997-2012) and reconfigurable       |

| oversampling ADCs [5]126                                                   |

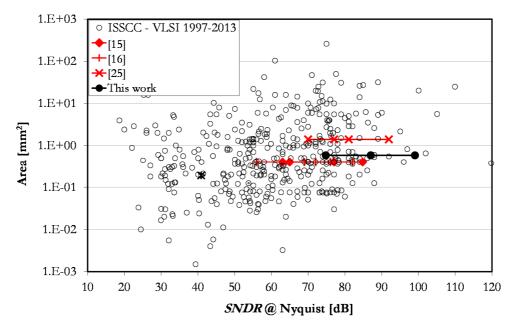

| Fig. 47. Area-efficiency versus SNDR performance of this work compared to  |

| state-of-the-art tailored (ISSCC- VLSI 1997-2012) and reconfigurable       |

| oversampling ADCs [5]127                                                   |

### List of tables

| Table I    | 3   |

|------------|-----|

| Table II   | 56  |

| Table III  | 57  |

| Table IV   | 65  |

| Table V    | 76  |

| Table VI   | 84  |

| Table VII  | 85  |

| Table VIII | 89  |

| Table IX   | 93  |

| Table X    | 95  |

| Table XI   | 103 |

| TABLE XII  | 108 |

| TABLE XIII | 109 |

| TABLE XIV  | 110 |

| TABLE XV   | 117 |

| Table XVI  | 120 |

| Table XVII | 123 |

### List of abbreviations

| ADC Analogue-to-digital converter                   | 1   |

|-----------------------------------------------------|-----|

| BW Bandwidth                                        | 4   |

| CT Continuous-time                                  | 17  |

| DAC Digital-to-analogue converter                   | 7   |

| <b>DR</b> Dynamic range                             | 10  |

| <b>DSP</b> Digital signal processor                 | 2   |

| <b>DT</b> Discrete-time                             | 17  |

| DWA Data weighted averaging                         | 43  |

| ECG Electrocardiogram                               | 1   |

| EMG Electromyogram                                  | 1   |

| <b>ENOB</b> Effective number of bits                | 8   |

| FB Feedback                                         | 35  |

| FF Feed-forward                                     | 35  |

| FoM Figure of Merit                                 | 8   |

| GBW Gain-bandwidth                                  | 48  |

| ISSCC International Solid-State Circuits Conference | 9   |

| MUX Multiplexer                                     | 63  |

| <b>OL</b> Overload level                            | 36  |

| OSR Oversampling ratio                              | 13  |

| PM Phase margin                                     | 117 |

| <b>r</b> <sub>ON</sub> Switch ON-resistance         | 111 |

| SAR Successive approximation register               | 7   |

| SC Switched-capacitor                               | 17  |

| SI Switched-current                                 | 29  |

| SNDR Signal-to-noise-and-distortion-ratio | 7  |

|-------------------------------------------|----|

| STF Signal transfer function              | 27 |

| VLSIC VLSI Circuit                        | 9  |

| WBAN Wireless body area networks          | 1  |

| WSN Wireless Sensor Network               | 3  |

| <b>ΔΣM</b> Delta Sigma Modulator          | 11 |

# List of symbols

| $\frac{\mathbf{k(t)}}{\mathbf{2^B - 1}}$ B-bit DAC feedback signal normalized with respect to $V_{ref}$ | 51 |

|---------------------------------------------------------------------------------------------------------|----|

| <b>A</b> <sub>c</sub> Capacitor area                                                                    | 44 |

| ${f a}_{f i}$ Gain coefficient of the $\Delta\Sigma$ loop                                               | 36 |

| <b>B</b> $\Delta\Sigma$ M internal quantizer resolution                                                 | 7  |

| <b>C</b> Unit capacitor of the SAR DAC array in a SAR quantizer                                         | 60 |

| <b>C</b> <sub>A</sub> Capacitance per unit area for a given technology                                  | 44 |

| $\mathbf{C}_{eq}$ Capacitive equivalent load of the OTA                                                 | 48 |

| $\mathbf{C}_{\mathrm{f}}$ Feed-forward capacitor                                                        | 78 |

| ${f c}_{f i}$ Feed-forward coefficient of the $\Delta\Sigma$ loop                                       | 36 |

| $\mathbf{C}_{\mathrm{I}}$ Integrating capacitor                                                         | 48 |

| $\mathbf{C}_{inv}$ Equivalent input capacitance of a minimum size inverter for a given                  |    |

| technology                                                                                              | 63 |

| $\mathbf{C}_{\mathtt{L}}$ Capacitive output load of the SC integrator                                   | 50 |

| CLK Clock signal                                                                                        | 59 |

| $\mathbf{C}_{\mathtt{LS}}$ Capacitor of the SC level shifter in a flash quantizer                       | 58 |

| $\mathbf{C}_{\mathbf{p}}$ OTA input parasitic capacitance                                               | 50 |

| $\mathbf{C}_{\mathrm{s}}$ Sampling capacitor                                                            | 7  |

| ${f C}_{ m TOT}$ Total capacitance commuting in the $\Delta \Sigma { m M}$                              | 57 |

| $\mathbf{C}_{\mathrm{u}}$ Capacitive unit element of the input DAC                                      | 43 |

| e Quantization error                                                                                    | 26 |

| <b>F</b> Ratio between $I_{\it bias}$ and $I_{\it tail}$                                                | 55 |

| $\mathbf{f}_{\mathrm{s}}  \Delta \Sigma \mathrm{M}$ sampling frequency                                  | 49 |

| $\mathbf{g}_{m,in}$ OTA input transconductance                                                          | 50 |

| $\mathbf{g}_{	ext{q}}$ Quantization gain                                                                | 27 |

| :                                                                                                       |    |

| $\mathbf{H}(\mathbf{z})$ transfer function of the $\Delta\Sigma$ loop filter                | 26  |

|---------------------------------------------------------------------------------------------|-----|

| $\mathbf{I}_{	ext{bias}}$ Extra current to bias the class-AB output branch in class-AB OTAs | 55  |

| I <sub>SAT</sub> OTA's maximum output current                                               | 48  |

| $\mathbf{I}_{tail}$ OTA tail current                                                        | 55  |

| k Boltzmann constant                                                                        | 38  |

| $\mathbf{K}_{\sigma}$ Capacitors' matching constant for a given technology                  | 44  |

| L Number of reconfigurability modes                                                         | 111 |

| $\mathbf{L}_{min}$ Minimum gate length for the given technology                             | 58  |

| $\mathbf{L}_{p,j}$ , $\mathbf{L}_{n,j}$ Positive and negative feedback signals of the DWA   | 48  |

| M OTA current mirror ratio                                                                  | 55  |

| n Weak inversion slope factor in a MOS transistor                                           | 50  |

| ${f N}$ $\Delta\Sigma{f M}$ loop-filter order                                               | 7   |

| $\mathbf{P}_{\mathbf{COMP}}$ Power consumption of the comparator                            | 58  |

| $\mathbf{P}_{\mathrm{DWA}}$ Power dissipated by the DWA digital circuitry                   | 45  |

| $\mathbf{P}_{	extbf{DYN}}$ Dynamic power for charging the capacitors                        | 45  |

| $\mathbf{P}_{	ext{ENC}}$ Power consumption of the encoder in a flash quantizer              | 59  |

| $\mathbf{P}_{\mathbf{HD}}$ Power of the in-band distortion components                       | 36  |

| $\mathbf{P}_{\mathrm{la}}$ Static power consumed during the large-signal period             | 49  |

| $\mathbf{P}_{\mathbf{Q}}$ Power of the in-band quantization error                           | 36  |

| $\mathbf{P}_{\mathbf{QUANT}}$ Power dissipated by the quantizer                             | 45  |

| $\mathbf{P}_{\text{RES}}$ Power consumption of the resistor ladder in a flash quantizer     | 59  |

| $\mathbf{P}_{\mathrm{sm}}$ Static power consumed during the small-signal period             | 49  |

| $\mathbf{P}_{\mathtt{STAT}}$ Static power dissipated by the OTAs                            | 45  |

| $\mathbf{P}_{Th}$ Power of the in-band thermal noise                                        | 36  |

| $\mathbf{P}_{	ext{TOT}}$ total power consumption                                            | 8   |

| $\mathbf{R}_{\mathrm{T}}$ Value of the resistor ladder in a flash quantizer                 | 59  |

| T Absolute temperature                                                                      | 38  |

| $\mathbf{T}_{int}$ Integrating time                                                     | 55 |

|-----------------------------------------------------------------------------------------|----|

| T <sub>sam</sub> Sampling time                                                          | 55 |

| $\mathbf{V_{DD}}$ Supply voltage                                                        | 42 |

| ${f V}_{	ext{	ext{eff}}}$ Comparator's effective voltage                                | 58 |

| $\mathbf{V}_{in,FS}$ Full scale input range of the $\Delta\Sigma\mathrm{M}$             | 36 |

| $\mathbf{V}_{in,MAX}$ Maximum input range of the $\Delta\Sigma\mathrm{M}$               | 36 |

| $\mathbf{V}_{\mathtt{m}}$ Voltage at the inverting input node of the OTA                | 48 |

| $\mathbf{V}_{	ext{ref}}$ Reference voltage of the quantizer                             | 42 |

| ${f V}_{sw}$ Comparator's input signal swing                                            | 58 |

| ${f V}_{ m Th}$ Thermal voltage                                                         | 50 |

| x Input signal normalized with respect to the reference voltage                         | 51 |

| lpha,eta OTA's parameters dependent on the topology                                     | 49 |

| $\gamma$ Ratio between $T_{sam}$ and $T_{int}$                                          | 55 |

| δ, ε, η Comparator's efficiency parameters                                              | 58 |

| $\Delta V_{th}$ Differential input voltage at which the output current saturates to its |    |

| maximum value $I_{SAT}$ .                                                               | 48 |

| <b>ζ</b> , <b>θ</b> OTA's timing corrective terms                                       | 49 |

| τ Settling time constant                                                                | 59 |

| $\varphi_1$ Sampling phase of the SC integrator                                         | 36 |

| φ <sub>2</sub> Integrating phase of the SC integrator                                   | 36 |

| 1 Introduction                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

| This chapter introduces the design of reconfigurable analogue-to-digital converters as focus of this thesis. Applications, problems and opportunities with respect to the state of the art are |

| identified, and performance criteria, i.e. power- and area-efficiency, are presented. Also, the                                                                                                |

| scientific aim and the scope of the thesis are clarified, together with the explanation of our design approach and an overview of the original contributions.                                  |

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

|                                                                                                                                                                                                |

| <br>                                                                                                                                                                                           |

|                                                                                                                                                                                                |

Ē

į

### 1.1 Background

Recently, there has been a growing interest in the research community and industry in the development of ultra-low power devices for various applications in the domain of wireless body area networks (WBAN). Although extensive measurement of physiological information is nowadays possible, the monitoring is generally limited to short time intervals and often to situations difficult to realize in normal life, like lying supine and sedated, or performing artificial exercise tests. The emergence of miniaturized sensors offers great promise for continuous and unobtrusive wireless monitoring, which would allow for a more timely response to any potential warning signs. The WBANs will be intelligent, context aware sensing architectures for the development of pervasive monitoring systems [1].

The basic concept of WBAN is a network of miniaturized, low cost and wireless wearable sensors that are energy-autonomous and capable of self-organizing into a collaborative network.

The design of sensor node hardware is constrained by several factors. To be energy-autonomous, nodes must be powered entirely by an energy harvesting source. This places demanding low-energy requirements on the constituent circuits [2]. It is also desirable to have sensors with redundant data to extract reliable information from biological data that are often prone to errors [1]. To give an example, different biopotentials need to be acquired and combined to define the overall health status. For instance, ECG (Electrocardiogram) signals are cross-correlated to respiration data and affected by motion artefacts, and EMG (Electromyogram) signals can be used to detect motion artefacts.

Fundamentally, the architecture of an intelligent sensor node consists of a sensor and a sensor front-end, an analogue-to-digital converter (ADC), a digital

signal processor (DSP), and a short range radio. The focus of this work is the design of an ADC suitable for sensor nodes and specifically for biopotential signals. Based on the considerations above, several key features need to be implemented:

- 1. The ADC has to be power-efficient to comply with the limited power budget of wireless sensors.

- 2. The ADC has to be area-efficient to match to the small form factor of modern sensor nodes and decrease costs.

- 3. The ADC should offer high-resolution and linearity to enable accurate conversion of small amplitude signals in the vicinity of strong interferences.

- 4. The ADC must be reconfigurable to adapt to heterogeneous biopotential signals, which are characterized by different amplitude levels and frequency ranges.

For instance, we can apply reconfigurability to the readout of biopotential signals (EEG, ECG, and EMG) according to the specifications of Table I (see also Table X in Section 4.2.2).

TABLE I

EXAMPLE OF SPECIFICATIONS FOR RECONFIGURABILITY

|                                 | ENOB | BW[Hz] | Target application |

|---------------------------------|------|--------|--------------------|

| High resolution/ low BW (HRLB)  | 16   | 256    | EEG, ECG           |

| Medium resolution and BW (MRMB) | 14   | 2048   | EMG                |

| Low resolution/ high BW (LRHB)  | 12   | 16 k   | Hearing-aids       |

Considering the working modes of Table I, it is clear that, to meet the required performance and ensure low power consumption, a high-resolution reconfigurable ADC is needed which can change its resolution and adjust its power according to the requirements of different physiological signals.

The concepts of reconfigurability, power- and area-efficiency will be explained in detail in Section 1.1.1 and Section 1.1.2, respectively. Subsequently, the state-of-the-art of reconfigurable ADCs will be summarized in Section 1.1.3.

### 1.1.1 Reconfigurability

An increasing number of applications require the acquisition of signals with a wide range of bandwidths and with varying resolution. These applications range from multi-standard communication systems to sensor systems in and around the body.

In mobile communication systems, the most advanced smart phones already support a large number of standards. The trend toward an ever-increasing flexibility of use demands radio transceivers that can operate complying with a variety of standards [3]. The multi-standard transceivers must fulfil the performance requirements of each standard separately and, in some cases, concurrently. For instance, wireless hand-held terminals may use simultaneously Bluetooth and GSM standards in a voice transmission using Bluetooth headphones. At the same time, the mobile terminal can be used to check the e-mail via a WLAN/UMTS data network [4].

In biomedical applications, a high recurrent design cost of wireless sensor networks (WSNs) is due to tailoring the sensors to a specific application. Ad hoc deployment will be possible if sensor nodes become fault tolerant and able to cope with different biosignals [2]. Sensors that monitor physiological parameters have indeed to process signals that have different amplitude levels and frequency ranges. Besides, the characteristics of the same physiologic signal may vary with time according to the body activity.

In order to satisfy the above mentioned system-level requirements, flexible analogue mixed-signal circuits and systems are needed. In multi-standard mobile terminals and wireless sensor nodes the most challenging part in the hardware design is probably the ADC interface. The ADC must indeed handle with flexibility a wide range of signals at varying sampling rates and resolutions, a feature which is difficult to implement in the analogue domain. Moreover, as power autonomy is still a major challenge in both these applications, the ADC must meet different design specifications while keeping the lowest possible power consumption.

To meet all these requirements, *reconfigurable* ADCs are needed that can change their resolution and bandwidth (BW) and adapt their power consumption accordingly.

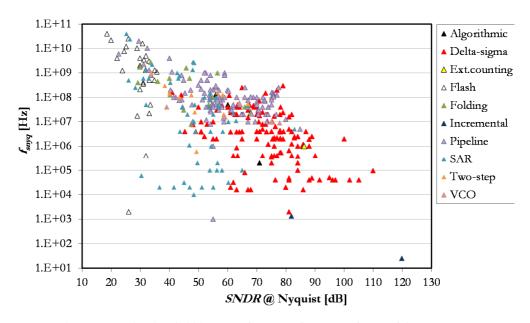

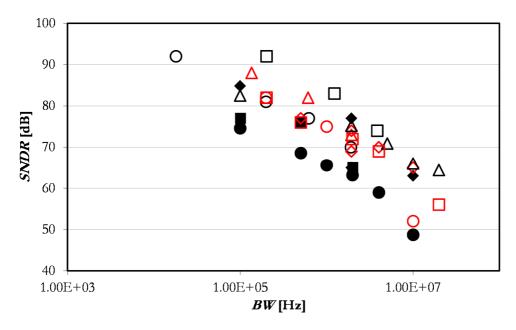

Several ADC architectures (like algorithmic, flash, pipeline, and delta–sigma converters) have been discussed in literature. Each of these architectures, however, can work optimally only for a specific range of resolution and BW. Fig. 1 shows different types of state-of-the-art ADCs with different input signal bandwidth  $f_{appg} = 2 \cdot BW$  and different resolution [5]. Looking at Fig. 1 it can be noticed that pipeline converters are typically used at low-to-medium resolutions and medium-to-high speeds, while delta-sigma ( $\Delta\Sigma$ ) and incremental converters are mostly exploited for medium-to-high resolution applications in the low-to-medium frequency range. Flash and folding ADCs are suitable for applications requiring very large bandwidths and relatively low resolution, while extended counting ADCs are used for medium bandwidth and medium-to-high resolution applications [6]- [7]. SAR and VCO-based ADCs most commonly range in resolution from 8 to 14 bits. From this analysis, it is clear that a conventional ADC with fixed topology and parameters cannot efficiently convert signals over a wide range of bandwidths at varying resolutions while optimizing power consumption [3].

Fig. 1. Conversion bandwidth versus SNDR performance of state-of-the-art ADCs.

A simple approach to reconfigurability would be to employ an array of ADCs, each one customized to work for a narrow range of resolution and input BW. Such a converter implementation, however, would require many ADCs and would result in a significant increase of the overall silicon area. As demonstrated by recent reconfigurable implementations, a power- and area-efficient approach to reconfigurability is possible using one single ADC able to achieve different resolution and bandwidth with minimal area overhead. However, reconfigurable solutions are still not competitive with state-of-the-art point- solution ADCs in terms of performance and power efficiency.

Reconfigurable ADCs reported in literature feature reconfiguration at different levels:

### • Algorithm-type reconfiguration

For each given combination of resolution and BW, the most suitable ADC algorithm is chosen to minimize the power consumption. For instance, at low-to-medium resolutions and medium-to-high speeds a pipeline algorithm is adopted, at high resolutions and low-to-medium speeds the  $\Delta\Sigma$  algorithm is used [8]- [9]. ADC topologies are indeed composed of similar basic components such as opamps, comparators, switches, and capacitors. Reconfigurability can thus be implemented by using these analogue building blocks in conjunction with configurable switches. A drawback of this approach is that switch parasitics often lead to performance degradation.

### • Bandwidth reconfiguration

Assuming a constant supply voltage, the power consumption of both digital and analogue circuits (in weak inversion) is directly proportional to their operating speed. In the case of digital circuits (or fully-dynamic analogue implementations), the power automatically scales with the operating frequency  $f_i$  according to  $\frac{1}{2}f_iCV_{DD}^2$ . The BW reconfiguration approach can thus be easily applied to mostly-digital ADC architectures [10]- [11]. In the case of analogue circuits, the power does not scale automatically with the sampling rate as static currents are used to bias analogue transistors in their operating region. A common method to achieve a scalable analogue power is to adaptively scale transistor bias currents with the sampling rate [12]- [13]. However, this approach can be affected by implementation problems. For a wide variation of sampling rates, indeed, the bias currents must vary largely, even by more than one order of magnitude. MOS transistors can thereby be driven into deep weak inversion, where they are more susceptible to mismatch and variability [2]. Alternatively, power scalability can be achieved in burst mode by performing conversions at a constant, maximum rate and by power-gating analogue

circuits when a reduced sampling rate is desired [14]. This approach requires, on the other hand, careful design to minimize the bias-up time in the transition between sleep and active mode.

### • Algorithm-parameter reconfiguration

In this approach the type of ADC algorithm is kept the same and the ADC is modified at the architectural level by changing the parameters which determine its resolution. The most common approach consists in using switchable blocks which are opportunely enabled to increase the ADC performance and disabled to save power. The advantage of this reconfigurability approach is that the bias conditions of the ADC can be kept mostly unchanged, mitigating the need of tuning the bias of analogue building blocks [15]. In pipeline ADCs like [3] and [16] the size of the capacitors and the length of the pipeline can be modified. In  $\Delta\Sigma$  architectures the parameters determining the final resolution can be adapted to the target resolution: the number of stages (in cascade architectures), the filter order (N), the quantizer resolution (B) and the size of the sampling capacitors ( $C_0$ ) are opportunely changed to achieve the required signal-to-noise-and-distortion-ratio (SNDR) [17]-[18]. In successive approximation (SAR) ADCs, the architecture of the internal logic, the digital-to-analogue converter (DAC) and the comparator are changed according to the target resolution [19].

By using and combining these techniques, more and more ADC programmability has been achieved during the last years. For the future, it is expected that this trend will continue until a large resolution and bandwidth space is covered with minimal power at each performance level. In this respect, the reconfigurability trend will lead new opportunities to ADC design, but will also have to cope with new challenges. An important challenge is for example the fact

that nanometer CMOS processes are optimized for digital circuitry and high speed, but can be disadvantageous for analogue circuits and for low-frequency applications. On the other hand, the use of oversampling strategies for the analogue signal processing facilitates the integration of reconfigurable ADCs in modern IC technologies.  $\Delta\Sigma$  ADCs, for instance, use redundant temporal data to reduce the quantization noise. This approach results in high-performance, robust ADCs which are able to exploit the inherent time resolution of modern technologies also for low frequency signals.

### 1.1.2 Power-efficiency and area-efficiency

As stated above, ADCs are among the most challenging parts of multi-standard mobile transceivers and biomedical sensor nodes and, as the number of applications is continuously increasing, it is expected that the flexibility required to reconfigurable ADCs will be larger and larger.

A reconfigurable ADC must offer two main characteristics, power-efficiency and area-efficiency.

A reconfigurable ADC is power efficient if the power-efficiency of the ADC can be kept constant and optimal as much as possible, despite the change in desired resolution and bandwidth. This requires that the ADC is scalable in terms of resolution, bandwidth and power.

In literature the power-efficiency of analogue-to-digital converters is commonly quantified using the Figure of Merit (FoM) [20]:

$$FoM_1 = \frac{P_{TOT}}{2 \cdot BW \cdot 2^{ENOB}} [J/c.s.]$$

(1)

where  $P_{TOT}$  is the total power consumption and BW is the input signal bandwidth;  $SNDR_{dB}$  is the signal-to-noise-and-distortion ratio expressed in dB and the effective number of bits is  $ENOB = \frac{SNDR_{dB} - 1.76}{6.02}$ .

In (1) the power per Nyquist sample  $P_{TOT}/2 \cdot BW$  is normalized by the effective number of quantization steps  $2^{ENOB}$ . This is based on the assumption that doubling precision would double power, which finds only empirical justification [20]. Moreover, the 2x relationship between precision and energy is not valid for high-resolution designs. Fig. 2 shows a scatter plot of state-of-the-art ADC designs, presented at the IEEE International Solid-State Circuit Conference (ISSCC) and the VLSI Circuit (VLSIC) Symposium [5]. It represents the power per Nyquist sample  $P_{TOT}/2 \cdot BW$  against the achieved SNDR [21]. The FoM in (1) is included as a straight line for the numerical example of 100fJ/c.s., while the FoM in (2) is included as a dashed line for the numerical example of 170 dB.

Fig. 2. Power-efficiency versus SNDR performance of state-of-the-art ADCs.

Fig. 2 shows that state-of-the-art high-resolution designs (*SNDR*>75dB) do not obey the 2x increase per bit implied by (1). In theory, indeed, if a converter is purely limited by thermal noise, its power quadruples per added bit [22]. In this case, a different *FoM* is used, defined as [23]:

$$FoM_2 = DR_{dB} + 10 \log_{10} \frac{BW}{P_{TOT}} [dB]$$

(2)

where  $DR_{dB}$  is the dynamic range of the converter. This equation is represented in Fig. 2 as a dashed line for the numerical example of 170dB.

Given the controversy about the definition of a Figure-of-merit for ADCs, the following twofold approach is chosen here.

When we compare data across a large range of architectures and resolutions, we avoid using (1) or (2). We represent instead the ADCs power performance in terms of power per Nyquist sample  $P_{TOT}/2 \cdot BW$  versus SNDR, like in the plot of Fig. 2 [21].

When we benchmark implementations targeting comparable resolutions, we employ  $FoM_1$  or  $FoM_2$  depending on the fundamental limit for the resolution of those ADCs. If the ADC is matching limited (low-to-medium SNDR) we will use  $FoM_1$ , if the ADC is thermal-noise limited (medium-to-high resolution) we will use  $FoM_2$ . In the rest of this work, we will refer to the expression in (1) simply as FoM as this expression is broadly used here.

A reconfigurable ADC is called area-efficient if the reconfigurability implies negligible area overhead with respect to point-optimized solutions. The areaefficiency is evaluated by comparing the area occupied by the reconfigurable ADC with the area of point-optimized implementations that achieve similar maximum SNDR. To compare different designs, we will plot their reported area against the achieved SNDR [21].

In Section 1.1.3 the power-efficiency and the area-efficiency of some state-of-theart reconfigurable ADCs is evaluated.

### 1.1.3 State-of-the-art reconfigurable ADCs

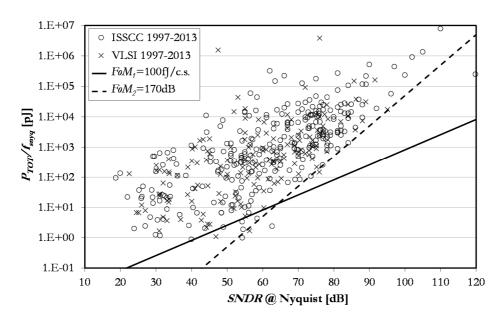

As an illustration of state-of-the-art reconfigurable ADCs, Fig. 3 plots some of the most recent reconfigurable designs in the plane power per Nyquist sample  $P_{TOT}/f_{snyq}$  ( $f_{snyq} = 2 \cdot BW$ ) versus resolution. Data are displayed as curves connecting the points associated to their different modes of operation. Reconfigurable ADCs are compared in terms of power-efficiency with state-of-the-art tailored designs already represented in [5]. Reconfigurable Nyquist ADCs ( [16], [19], [24], [25], [26]) are displayed as black curves, while reconfigurable oversampling ADCs ( [17], [18], [27]) are shown as red curves. Please note that the power reported for oversampling ADCs is only the power dissipated by the  $\Delta\Sigma$  modulator ( $\Delta\Sigma$ M) blocks. Both FoM lines of Fig. 2 are included, corresponding to the trends shown in equations (1) and (2). They are plotted as a straight line and as a dashed line for the numerical value of 100f]/c.s. and 170dB, respectively.

On the one hand, it can be noted that  $\Delta\Sigma$  architectures (for instance [18] or [27]) are able to cover wider SNDR regions than Nyquist-rate ADCs (see [16] or [25]). Thanks to the oversampling technique, indeed,  $\Delta\Sigma$  ADCs are able to trade off speed for resolution which offers inherent reconfigurability [27]. Moreover  $\Delta\Sigma$  ADCs are able to filter the noise (noise shaping) and push it out of the signal band. The use of these analogue signal-processing strategies results in high-performance, robust ADCs, which have lower sensitivity to circuit imperfections than Nyquist-rate ADCs.

Fig. 3. Power-efficiency versus *SNDR* performance of state-of-the-art tailored (ISSCC-VLSI 1997-2012) and reconfigurable ADCs.

These properties make it easier to change resolution and speed without significant performance degradation and have motivated the use of  $\Delta\Sigma$  approaches in the majority of reconfigurable ADCs reported so far [4].

On the other hand, Fig. 3 shows that reconfigurable Nyquist ADCs are always matching-limited designs, and they follow the trend implied by  $FoM_1$  for different configurations.  $\Delta\Sigma$  designs, instead, do not follow the same  $FoM_1$  trend in all modes of operation. At low-to-medium resolutions (SNDR < 75 dB) they are matching-limited as well. But, for higher resolutions, reconfigurable  $\Delta\Sigma$  architectures break away from the  $FoM_1$ -line and follow the  $FoM_2$ -line. This fact has two main reasons:

- Firstly, beyond the threshold SNDR of 75dB most state-of-the-art ADCs can be considered to be limited by thermal noise [21]. Therefore, their power tends to

increase more than 2x per bit, until it reaches the 4x increase per additional bit associated to the  $FoM_2$ -line.

- Secondly, although oversampling plus noise shaping helps in relaxing some specifications of  $\Delta\Sigma$  analogue building blocks,  $\Delta\Sigma$  still share some design constraints of Nyquist converters. More specifically, the signal swing at the OTAs output can be large, especially in single-bit topologies, or if loop coefficients are not specifically chosen to reduce integrators' output swing. Also high oversampling ratios (OSRs) pose challenging specifications to the settling speed of the OTAs [28]. Moreover, high linearity is required in the input DAC when multi-bit quantizers are employed. Indeed, as the errors of multi-bit DACs are injected at the modulator input, the corresponding non-linearities are not mitigated by the noise shaping. The linearity of a multi-bit modulator will be thus no better than that of the multi-bit embedded DAC and the latter must be designed to reach the linearity targeted for the whole  $\Delta\Sigma$ M [29]. These technology constraints strongly affect also the power-efficiency of our implementations, as it will be shown in Section 5.

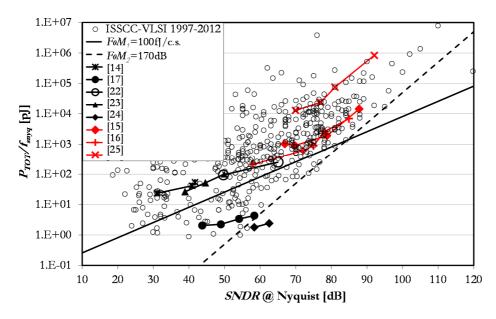

We can now focus on the area-efficiency of state-of-the-art reconfigurable ADCs. As discussed before, a reconfigurable ADC is called here area-efficient if its area is comparable to the area of custom ADCs targeting the same maximum *SNDR*. Fig. 4 shows the same reconfigurable designs as in Fig. 3 in the area versus *SNDR* plane. The designs from the IEEE ISSCC and the VLSIC Symposium are plotted on the same plane for comparison [21].

Fig. 4. Area-efficiency versus SNDR performance of state-of-the-art tailored (ISSCC-VLSI 1997-2012) and reconfigurable ADCs.

As mentioned before, state-of-the-art custom designs which target *SNDR* below 75 dB are mostly Nyquist-rate designs, while point-solution designs which target *SNDR*>75 dB are generally oversampling ADCs [21].

Reconfigurable Nyquist ADCs (black curves) are generally not optimized in terms of area. The area occupied by these designs is indeed much higher than the area of custom ADCs targeting the same maximum SNDR. The area overhead is due to the fact that reconfigurability is achieved here by using switchable blocks which are opportunely enabled to increase the ADC performance and disabled to save power (algorithm-parameter reconfiguration). Reference [19] represents an exception to this trend. In this implementation area-efficiency (as well as power-efficiency) is

obtained by minimizing the capacitors size in the SAR DAC, which usually dominates the overall area budget in SAR ADCs<sup>1</sup>.

$\Delta\Sigma$  modulators (red curves) show better area-efficiency when compared to point-solutions achieving the same maximum resolution. Both point-solution and reconfigurable designs target indeed high-resolution (maximum SNDR > 75 dB). The area is thus dominated in both cases by the size of the sampling capacitors, fixed by thermal noise requirements. The area overhead to implement reconfigurability is, on the other hand, mostly negligible.

# 1.2 Problem statement

From the prior art discussed in Section 1.1.3, it becomes clear that reconfigurable AD converters exist, but their performance is not optimized in terms of power-efficiency and area-efficiency.

More specifically, in the design of medium-to-high-resolution (*SNDR*>75 dB) reconfigurable ADCs, three problems constitute the scientific focus of our research:

- We want to demonstrate that it is possible to design a reconfigurable ADC which is able to keep state-of-the-art power-efficiency in all its reconfigurability modes.

- 2. We want to investigate whether the power performance of the reconfigurable ADC will be thermal-noise-limited or technology-limited over its *SNDR* range. In other words, our aim is to check whether the ADC power will increase 4x

16

<sup>&</sup>lt;sup>1</sup> In this design the unit capacitor elements of the SAR DAC are implemented as custom interdigitated capacitors with an extremely small value of 0.5fF which are made possible by the 90nm CMOS technology used.

per added bit, following the trend given by  $FoM_2$  in Fig. 3, or 2x per added bit, following the  $FoM_1$  trend.

3. We want to show that a reconfigurability approach can be implemented with negligible area overhead with respect to point-solution ADCs targeting the same maximum *SNDR*.

## 1.3 Aim of the thesis

The aim of this thesis is to show that it is possible to design reconfigurable medium-to-high resolution ADCs which are both power-efficient and area-efficient. In doing so, the combination of reconfigurability and power-efficiency is addressed as the main design challenge. In other words, the reconfigurable ADC has to achieve FoM values which are both close to minimum with respect to state-of-the-art and constant over the whole conversion range.

Pursuant to this aim, a design methodology is proposed to optimize both the power- and the area-efficiency of reconfigurable ADCs.

# 1.4 Scope of the thesis

Some limitations on the scope of the thesis are described below. A detailed explanation of these choices will be provided in Section 2.4.

• Delta-sigma AD converters with focus on  $\triangle \Sigma Ms$

$\Delta\Sigma$  architectures will be studied to extend reconfigurability to high-resolution AD conversion. This is motivated by the fact that these architectures are the preferred ones in this resolution area. Moreover, as aforementioned, they offer

inherent reconfigurability as they are able to trade resolution with speed. The limitation to  $\Delta\Sigma$  modulators is motivated by the fact  $\Delta\Sigma$ Ms have largest influence on the overall performance and power consumption of  $\Delta\Sigma$  ADCs. Digital filters are not going to be studied in our research as they are far less constraining.

### • Discrete-time (DT) and single-loop switched-capacitor (SC) implementation

Discrete-time (switched-capacitor)  $\Delta\Sigma$ Ms will be studied for the implementation of reconfigurable  $\Delta\Sigma$  modulators. Moreover, the work is limited to single-loop architectures. The limitation to discrete-time architectures is motivated by their high potential for reconfigurability, especially in biomedical applications. They offer indeed a straightforward reconfigurability of the system by arbitrarily adjusting the sampling frequency [30]. This is not the case for continuous-time (CT) modulators. The limitation to single-loop  $\Delta\Sigma$ Ms is motivated by simplicity as it is sufficient for the demonstration of the proposed reconfigurability approach. The approach, however, can be extended to cascaded architectures if high-order noise-shaping is needed and stability becomes a constraint.

### • CMOS technology

CMOS is the preferred technology choice for the implementation of digital circuits. As  $\Delta\Sigma$  AD conversion implies the integration of analogue circuits (the  $\Delta\Sigma$  modulator) and digital circuits (the digital filter), the limitation to CMOS technology is a logical choice. Because of practical reasons (technology availability in this project), all simulations, calculations and implementations are focused to a 0.18 $\mu$ m CMOS technology. However, the proposed concepts could be implemented in other technologies as well.

### • Biomedical applications

The structured design approach to the power-optimal design of reconfigurable  $\Delta\Sigma$ Ms does not aim for a specific application. In other words, the method can be adapted to any purpose by opportunely incorporating constraints and assumptions related to the target application. However, for the design cases here presented, the design procedure is aimed at the biomedical case. More specifically, out approach will take advantage of the low-frequency nature of the input signals and considers designs as thermal-noise limited. The latter assumption is valid for high-resolution AD conversions.

# 1.5 Approach

As anticipated in Section 1.3, a design methodology is proposed here to improve the performance of high-resolution reconfigurable ADCs with respect to powerefficiency and area-efficiency.

Our method can be summarized as follows:

- Definition of target specifications.

- Investigation of the fundamental constraints to be considered in the design.

- Analysis of the actual constraints determined by technology.

- Evaluation of prior-art and identification of the trade-offs limiting reconfigurable ADCs performance.

- Identification of a design strategy to implement reconfigurability.

The last step deserves further explanation. Our design strategy consists indeed of the following sub-steps:

- 1. As a starting point, we identify the possible approaches to reconfigurability.

- 2. We compare the reconfigurability approaches in terms of power-efficiency.

- 3. We evaluate them subsequently in terms of area-efficiency.

- 4. Based on the results of the comparison both in terms of power- and areaefficiency, we select the most promising reconfigurability approach to be implemented and identify a generic design strategy for it.

# 1.6 Original contributions

This work aims at advancing state-of-the-art in different fields:

### Analysis

- Analysis of the power consumption of DT single-loop  $\Delta\Sigma$ Ms, both feedback and feed-forward. The specific focus is on the dependency of the different power contributions on the main design parameters of the modulator, namely filter order, quantizer resolution and oversampling ratio.

- Analysis of the conventional ways to implement the analogue addition required in feed-forward topologies at the input of the quantizer: active addition and passive addition. Analysis of the impact of these solutions on power consumption.

### Design

- Introduction of a power-optimal high-level design method for point-solution single-loop  $\Delta\Sigma$ Ms.

- Introduction of a power-optimal high-level design method for reconfigurable single-loop  $\Delta\Sigma$ Ms.

- Design of an alternative summing SAR ADC quantizer based on passive addition and SAR analogue-to-digital conversion algorithm.

Implementation and verification

- Implementation and experimental evaluation of a  $\Delta\Sigma M$  for hearing aids application including the summing SAR ADC quantizer solution.

- Implementation and experimental evaluation of a power-efficient reconfigurable  $\Delta\Sigma M$  for biomedical applications.

# 1.7 Outline of the thesis

The outline of this thesis is briefly explained below.

Chapter 2 introduces  $\Delta\Sigma$  architectures foundations with respect to their ideal behaviour and performance criteria. A classification of practical implementations of  $\Delta\Sigma$  modulators is presented. Moreover, an overview of state-of-the-art reconfigurable  $\Delta\Sigma$ Ms is given and design choices which limit the scope of the thesis are motivated.

Chapter 3 presents a methodology for the power-optimal design of high-resolution low-bandwidth switched-capacitor  $\Delta\Sigma$ Ms. The method is based on an analytic model of all different contributions to the power dissipation of a SC single-loop  $\Delta\Sigma$ M. As a second step, techniques that enable power-efficiency at the circuit level are discussed, with particular emphasis on a novel circuit solution which combines multi-bit quantization and analogue addition, i.e. the summing successive-approximation ADC quantizer. Finally, the design of two high-resolution  $\Delta\Sigma$ Ms for hearing aids application is discussed both at the system and circuit level, together with the corresponding simulation and experimental results.

Chapter 4 presents a methodology to design reconfigurable switched-capacitor  $\Delta\Sigma$  modulators that are able to keep the power-efficiency constant and optimal for a

set of different resolutions and bandwidths. The method is based on the structured design method for point-solution  $\Delta\Sigma$ Ms presented in Chapter 3. As the size of the sampling capacitors is crucial to determine power consumption, three approaches to achieve reconfigurability are compared: dimension the sampling capacitors to achieve the highest resolution and keep them constant, change only the first sampling capacitor according to the targeted resolution or program all sampling capacitors to the required resolution. The second approach results in the best compromise between power-efficiency and low design complexity. A reconfigurable  $\Delta\Sigma$ M for biomedical applications is fabricated in a 0.18 $\mu$ m CMOS process for validating the proposed methodology.

Finally, conclusions are drawn in Chapter 5.

# 2 Power-efficient reconfigurable $\Delta\Sigma$ modulators for autonomous biomedical applications

This chapter introduces  $\Delta\Sigma$  architectures foundations with respect to their ideal behaviour and their performance criteria. A classification of practical implementations of  $\Delta\Sigma$  modulators is also presented. Moreover, an overview of state-of-the-art reconfigurable  $\Delta\Sigma$ Ms is given and design choices which limit the scope of the thesis are presented and motivated: the focus of this work will be on low-pass discrete-time  $\Delta\Sigma$  single-loop architectures implemented using SC techniques.

# 2.1 $\Delta\Sigma$ modulation for reconfigurable and powerefficient high-resolution ADCs

Fig. 5 depicts again the state-of-the-art ADC designs in the plane power per Nyquist sample  $(P_{TOT}/2 \cdot BW)$  against achieved SNDR [5]. Different AD algorithm types are identified by different colours.

Fig. 5. Power-efficiency versus SNDR performance of state-of-the-art ADCs.

Among all the ADC topologies,  $\Delta\Sigma$  architectures and incremental ADCs are suited for the implementation of high resolution AD converters. Incremental ADCs are  $\Delta\Sigma$  ADCs operated in "one-shot" mode, which perform a fixed number of conversion steps and then reset [31].

As aforementioned,  $\Delta\Sigma$  ADCs combine redundant temporal data with filtering to reduce the quantization noise and to push this noise out of the signal band,

respectively. The use of these analogue signal-processing strategies results in high-performance, robust ADCs, which have lower sensitivity to circuitry imperfections than Nyquist-rate ADCs, thus making easier to increase their resolution [4]. Further, as resolution increases beyond 70-dB SNDR, they are shown in Fig. 5 to be the most power efficient ADCs [2]. Moreover,  $\Delta\Sigma$  ADCs cover a wide SNDR region, ranging over more than 50 dB. This feature motivates the use of this data conversion technique for the implementation of reconfigurable ADCs. As mentioned above,  $\Delta\Sigma$  ADCs have demonstrated to be very advantageous when reconfigurability is needed, thanks to their inherent trade-off between accuracy and sampling speed [4].

An alternative, similar to approaches chosen in [14] and [32], would be to operate incremental  $\Delta\Sigma$  architectures with the same bandwidth and sample rate, and power down circuits between conversions. The resettable operation of incremental ADCs makes them suitable for power-scaled operation which is not straight-forward with oversampled ADCs. At the same time, they are able to achieve high-resolution and good energy-efficiency (see [33] and [34] in Fig. 5). However, the medium bandwidth required for some ADC modes of Table I are more amenable to the use of oversampled  $\Delta\Sigma$  ADCs. In view of these considerations,  $\Delta\Sigma$  architectures are chosen as focus of our research.

Different architectural- and circuit-level strategies are studied to increase the programmability and adaptability of the  $\Delta\Sigma$  ADC performance to a wide number of biomedical specifications with power consumption scalability (for power-efficiency) and large hardware reuse (for area-efficiency). In Section 2.2 the foundations of  $\Delta\Sigma$  architectures are introduced. The basic scheme of a  $\Delta\Sigma$  ADC is presented, together with its ideal behaviour and a definition of its performance criteria. A classification of practical implementations of  $\Delta\Sigma$  modulators is also presented. In Section 2.3 a survey of the state-of-the-art performance of

reconfigurable  $\Delta\Sigma$ Ms is given. As aforementioned in Section 1.1.1, these  $\Delta\Sigma$ Ms are mostly employed in highly integrated wireless transceivers for multi-standard telecom systems. Finally, in Section 2.4, we detail and motivate the design choices limiting the scope of this thesis, as anticipated in Section 1.4.

# $2.2 \Delta \Sigma$ ADCs: basics and topologies

Fig. 6 illustrates the basic scheme of a  $\Delta\Sigma$  ADC. As shown, a  $\Delta\Sigma$  converter is made of two main blocks:

- **Delta-Sigma Modulator.** It simultaneously performs the oversampling and quantization of the band-limited input signal. Quantization error is also high-pass filtered by means of a given noise-shaping technique. This is accomplished by placing an appropriate loop filter H(z) before a low-resolution B-bit quantizer and closing a negative feedback loop around them. The in-band quantization noise is therefore greatly decreased in comparison to that of the embedded quantizer. The output of the  $\Delta\Sigma M$  is a B-bit digital stream at  $f_s$  sampling rate.

- **Decimator.** It reduces the rate of the  $\Delta\Sigma M$  output stream down to the Nyquist rate. At the same time, the word length increases from B to the final effective number of bits (ENOB) in order to preserve resolution as the word rate decreases.

The  $\Delta\Sigma$  modulator is the block that has most influence on the ADC performance, basically because it is responsible of the sampling and quantization processes and, therefore, ultimately limits the accuracy of the AD conversion [4]. It also determines the most stringent constraints on power consumption. This analogue block will be thus the object of the research described in this work.

Fig. 6. Generic scheme of a  $\Delta\Sigma$  ADC

Fig. 7 (a) shows the basic scheme of a  $\Delta\Sigma$  modulator. It consists of a feed-forward path formed by a loop filter H(z) and a B-bit quantizer and a negative feedback path around them using a B-bit DAC.

Fig. 7.  $\Delta\Sigma M$  architecture (a) Basic scheme, (b) Linear model.

Assuming that H(z) has large gain inside the signal band and small gain outside of it, the error signal X- Y is zero in the signal band thanks to the negative feedback. This way, most of the differences between X and Y will therefore be placed at higher frequencies, shaping quantization error and pushing it outside the signal band. Fig. 7 (b) shows the linear model of a  $\Delta\Sigma$ M, in which the DAC is assumed to be ideal, and the additive white noise approximation is considered for the quantization error e. According to this model, the modulator can be viewed as a two-input system whose output is represented in z-domain as

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(3)

where X(z) and E(z) are the z-transform of the input signal and the quantization noise, respectively, and STF(z) and NTF(z) are the respective transfer functions, given by

$$STF(z) = \frac{g_q H(z)}{1 + g_q H(z)}, \qquad NTF(z) = \frac{1}{1 + g_q H(z)}$$

(4)

$g_q$  is the gain of the quantizer (see Fig. 7 (b)) .

Since the signal and the noise pass through different transfer functions, H(z) can be chosen such that the noise shaping does not affect the signal. Using a loop filter with large gain within the signal band, the signal and noise transfer functions can be indeed approximated to

$$STF(z) \approx 1, NTF(z) \approx \frac{1}{g_q H(z)} \ll 1$$

(5)

The noise-shaping function can be built with proper selection of H(z). The simplest loop filter that exhibits the desired frequency performance is an integrator, whose z-domain transfer function is

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{6}$$

Such a modulator is called a 1st-order  $\Delta\Sigma$ M, referring to the order of the noise shaping. Assuming that the quantizer gain  $g_q$  equals unity, the  $\Delta\Sigma$ M output yields

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z).$$

(7)

The dynamic range of an ideal N-order  $\Delta\Sigma M$  with a B-bit embedded quantizer that operates at a given oversampling ratio is [35]

$$DR = 10 \log_{10} \left( \frac{3}{2} (2^{B} - 1)^{2} \cdot \frac{(2N + 1) OSR^{(2N + 1)}}{\pi^{2N}} \right)$$

(8)

and therefore it can be increased if N, OSR and/or B become higher. The advantages and disadvantages of each possibility are discussed below:

- Increasing the modulator order considerably improves the performance of a  $\Delta\Sigma$ M, since quantization error will be more attenuated at low frequencies and pushed to high frequencies. However, stability problems arise when using high-order shaping (N>3).

- Increasing the oversampling ratio OSR leads to an increase in the dynamic range of 3(2N+1) dB/octave for an ideal N-order  $\Delta\Sigma$ M. The combined action of oversampling and noise shaping considerably improves performance. However, for a given signal band, larger OSRs lead to higher sampling frequencies and penalize power dissipation.

- Increasing the resolution of the modulator embedded quantizer leads to an increase in the DR of approximately 6dB (1bit) per extra bit in the quantizer [36]. A higher B also decreases the stability issues that are induced by the nonlinear errors in the quantizer, and consequently allows higher input signals. However,  $\Delta\Sigma$ Ms with an internal multi-bit quantizer require a multi-bit DAC in the feedback loop, and this block is not inherently linear. As aforementioned, the linearity required in the DAC equals the overall linearity required to the  $\Delta\Sigma$  modulator.

The above-mentioned strategies can be combined in many different ways giving rise to different  $\Delta\Sigma$ M topologies reported in literature. These can be grouped according to the following criteria [37]:

- The nature of the signals being converted: low-pass versus band-pass  $\Delta\Sigma$ Ms.

- The type of dynamics of the loop filter: discrete-time or continuous-time  $\Delta\Sigma$  modulators. CT  $\Delta\Sigma$ Ms use CT loop filters but DT quantizers. Also hybrid CT-DT modulators have been reported recently [38].

- The number of quantizers employed. Single-loop  $\Delta\Sigma$ Ms employ only one quantizer. Cascade  $\Delta\Sigma$ Ms employ several quantizers.

- The number of bits in the embedded quantizer. Single-bit  $\Delta\Sigma M$  modulators featuring a single-comparator as quantizer are inherently linear. Multi-bit  $\Delta\Sigma M$ s use instead multi-bit quantizers, mostly flash-ADC or SAR-ADC topologies.

- Type of circuitry employed, devices available in the fabrication process, voltage supply, etc. Most of the reported DT implementations employ switched-capacitor (SC) circuits with dedicated high-density and high-quality capacitors, other employ capacitors available in standard CMOS technologies, active capacitors built with MOS transistors, switched-current (SI) circuits, etc.

Describing all possible  $\Delta\Sigma M$  architectures derived from these classification criteria goes beyond the scope of this work. In the next sections, we will use these basic concepts to analyse state-of-the-art reconfigurable  $\Delta\Sigma M$  performance and trends and to address the challenge of designing reconfigurable  $\Delta\Sigma Ms$  for biomedical applications.

# 2.3 State-of-the-art reconfigurable $\Delta\Sigma$ modulators

$\Delta\Sigma$ Ms are very suited for the implementation of reconfigurable ADCs [39]. Indeed, the combination of different architectural and circuit strategies overviewed in Section 1.1.1, together with the variation of basic  $\Delta\Sigma$ M parameters, i.e., OSR, N, and B, can contribute to adapt the ADC performance to different specifications with a high level of hardware reuse [40].

Several state-of-the-art reconfigurable  $\Delta\Sigma$ Ms are able to handle more than two standard specifications. Fig. 8 depicts state-of-the-art reconfigurable ADCs employed for multi-mode applications on the resolution-bandwidth plane. The same

symbols represent different reconfigurability points for the same IC. Discrete-time  $\Delta\Sigma$  architectures are depicted in black, continuous-time  $\Delta\Sigma$ Ms in red. Single-loop topologies are represented as empty shapes while cascade  $\Delta\Sigma$ Ms are filled shapes.

Fig. 8. State-of-the-art reconfigurable ADCs for multi-standard applications. Continuous-time  $\Delta\Sigma$  architectures are depicted in red, discrete-time  $\Delta\Sigma$ Ms in black; single-loop topologies are represented as empty shapes, cascade as filled shapes.

In Fig. 8 the following trends can be observed:

- State-of-the-art reconfigurable  $\Delta\Sigma$ Ms cover in total a range of more than 40 dB in SNDR, and approximately 3 decades in signal bandwidth, between 18 kHz and 20 MHz, respectively. These ranges of resolution and BW make them suitable for multi-standard wireless transceivers applications.

- ullet The majority of state-of-the-art  $\Delta\Sigma$ Ms are DT implementations. They offer indeed a straightforward reconfigurability of the system by arbitrarily adjusting the sampling frequency, which is not the case for CT modulators (this concept will be further

clarified in the next section). CT circuits are sometimes used to implement functions like blocker-rejection filtering, frequency-mixing process, channel-selection and antialiasing filtering. The resulting  $\Delta\Sigma$ M-based transceivers may become more efficient than conventional ones in terms of analogue circuit complexity, shared building blocks, and reduced power consumption [39].

• Most of the designs choose single-loop  $\Delta\Sigma$  topologies because of their robustness to non-idealities of circuit components. Furthermore the relatively simple structure makes it more suitable for the complex reconfigurable circuit design [41].

# 2.4 Reconfigurable $\Delta\Sigma Ms$ for biomedical applications

Existing reconfigurable  $\Delta\Sigma$ Ms are conceived for medium-resolution high-frequency radio-transmission applications. The design alternatives for the implementation of state-of-the-art ICs are outlined in the previous section (Fig. 8). To extend the use of reconfigurable modulators to low-frequency high-resolution biomedical applications, we will hereafter focus on discrete-time  $\Delta\Sigma$  single-loop architectures implemented using SC techniques.