### Improving GPU performance : reducing memory conflicts and latency

*Citation for published version (APA):* Braak, van den, G. J. W. (2015). *Improving GPU performance : reducing memory conflicts and latency*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven.

Document status and date: Published: 25/11/2015

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

## Improving GPU Performance Reducing Memory Conflicts and Latency

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op woensdag 25 november 2015 om 14:00 uur

$\operatorname{door}$

Gerardus Johannes Wilhelmus van den Braak

geboren te 's-Hertogenbosch

Dit proefschrift is goedgekeurd door de promotor en de samenstelling van de promotiecommissie is als volgt:

| voorzitter: | prof.dr.ir. A.C.P.M. Backx                        |

|-------------|---------------------------------------------------|

| promotor:   | prof.dr. H. Corporaal                             |

| copromotor: | dr.ir. B. Mesman                                  |

| leden:      | prof.dr. N. Guil Mata (Universidad de Málaga)     |

|             | prof.dr.ir. G.J.M. Smit (Universiteit Twente)     |

|             | prof.dr.ir. P.P. Jonker (TU Delft)                |

|             | prof.dr.ir. D.H.J. Epema (TU Delft, TU Eindhoven) |

|             | prof.dr.ir. P.H.N. de With                        |

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# Improving GPU Performance Reducing Memory Conflicts and Latency

Gert-Jan van den Braak

Doctorate committee:

| prof.dr. H. Corporaal      | TU Eindhoven, promotor   |

|----------------------------|--------------------------|

| dr.ir. B. Mesman           | TU Eindhoven, copromotor |

| prof.dr.ir. A.C.P.M. Backx | TU Eindhoven, chairman   |

| prof.dr. N. Guil Mata      | University of Malaga     |

| prof.dr.ir. G.J.M. Smit    | University of Twente     |

| prof.dr.ir. P.P. Jonker    | TU Delft                 |

| prof.dr.ir. D.H.J. Epema   | TU Delft, TU Eindhoven   |

| prof.dr.ir. P.H.N. de With | TU Eindhoven             |

This work was supported by the Dutch government in their Point-One research program within the Morpheus project PNE101003 and carried out at the TU/e.

© Gert-Jan van den Braak 2015. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Printed by CPI Koninklijke Wöhrmann – The Netherlands

A catalogue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-3964-2

Abstract

### Improving GPU Performance Reducing Memory Conflicts and Latency

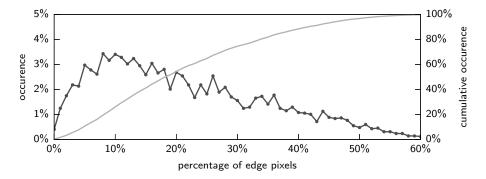

Over the last decade Graphics Processing Units (GPUs) have evolved from fixed function computer graphics processors to energy efficient and programmable general purpose compute accelerators. During this period the number of cores in a GPU increased from 128 to 3072, an increase of  $24\times$ . However, the peak compute performance only increased by  $12\times$ , and memory bandwidth by a mere  $3.9\times$ . Algorithms with an abundance of parallelism, such as matrix multiplication, can be implemented relatively easily on these GPUs and scale well with an increase in core count. Other, irregular algorithms are much harder to implement efficiently and benefit less of the increased number of cores. In this work a class of irregular algorithms, the so called 'voting algorithms' such as histogram and Hough transform, are analyzed, implemented and optimized on GPUs. Histograms are not only used in statistics or for displaying the distribution of colors in an image, but also for contrast adjustments in images, image segmentation and feature detection, such as in the Scale Invariant Feature Transform (SIFT) and Histogram of Oriented Gradients (HoG). The Hough transform can be used to detect the lines on a road, or the circles of a traffic sign, but also to track particles, e.g. in the Large Hadron Collider. In voting algorithms a set of input values is mapped to a, usually much smaller, set of output bins. The main challenge in mapping voting algorithms to GPUs is to efficiently update the output bins in a parallel manner.

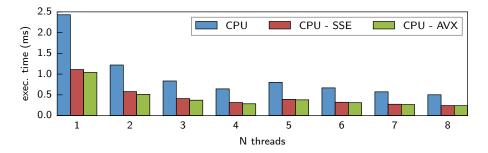

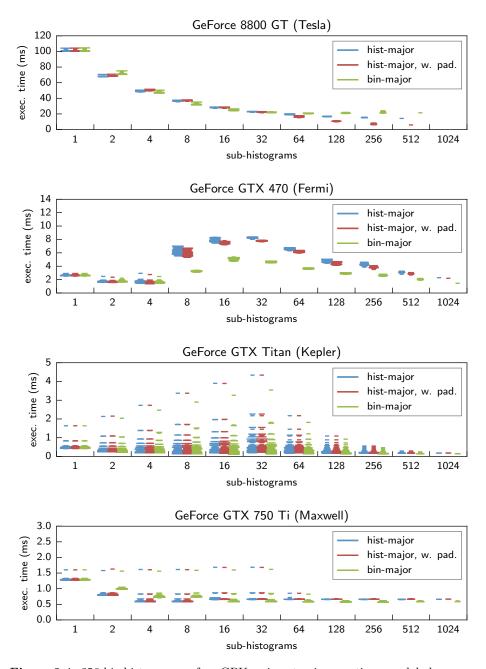

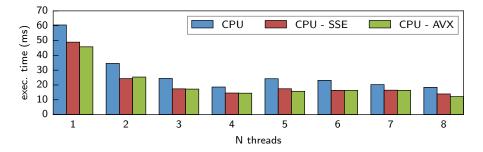

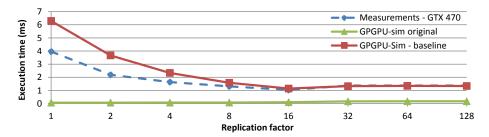

The first contribution of this work is a set of software techniques to improve the parallel updating of the output bins in the voting algorithms. Voting algorithms use atomic operations to update the bins. By duplicating all the bins a significant performance improvement can be achieved. Multi-core CPU implementations are made which utilize the SSE and AVX vector extensions of the processor. These optimizations improve the performance of the histogram application on a CPU by  $10 \times$  over a single thread CPU implementation. The baseline GPU implementation

has a similar performance as a single core CPU implementation, but by using the proposed software techniques the best GPU histogram implementation outperforms the optimized multi-core CPU implementation by  $4.8 \times$ .

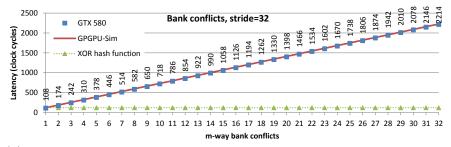

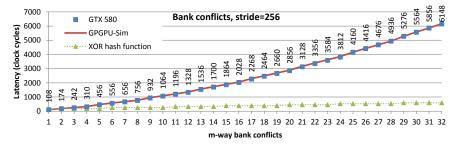

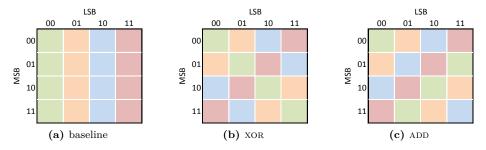

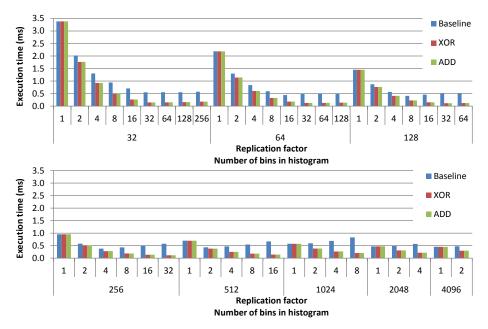

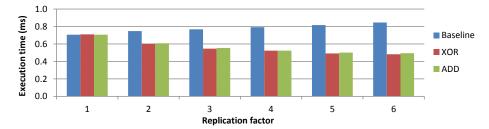

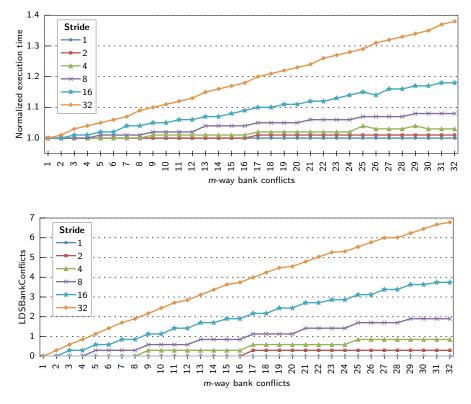

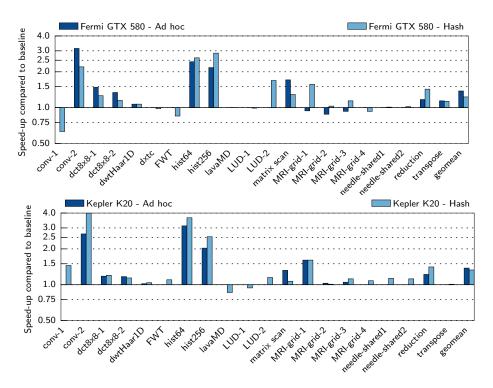

The second contribution of this thesis is a hardware change of the scratchpad memory. The GPU's on-chip scratchpad memory is divided in banks and contains locks to support atomic operations. The duplication of the output bins requires more scratchpad memory and causes an uneven distribution of the memory accesses over the banks and locks. Hash functions in the addressing of the banks and locks are proposed to distribute the memory accesses more equally over the memory's banks and locks. A simple hardware hash function improves performance up to  $4.9 \times$  for the aforementioned optimized GPU histogram application. Applications which use the scratchpad memory, but do not rely on atomic operations, still experience an average performance gain of  $1.2 \times$  by using a more complicated configurable hash function.

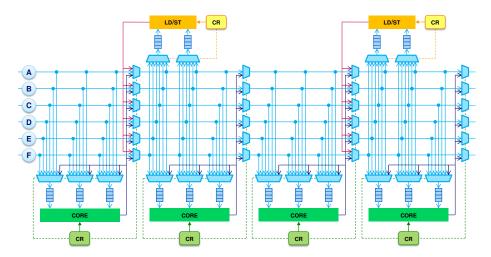

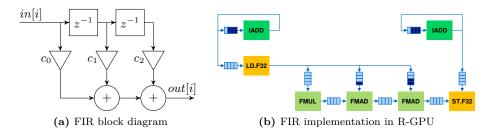

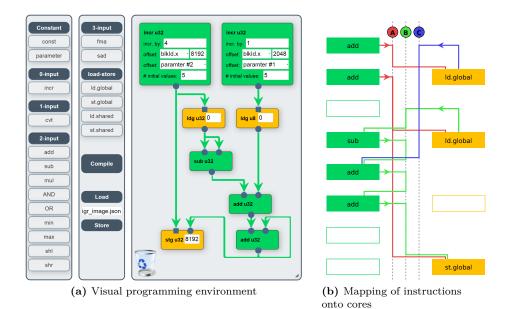

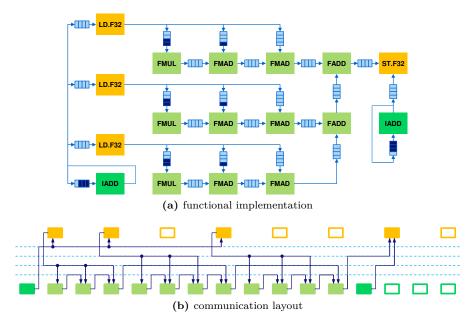

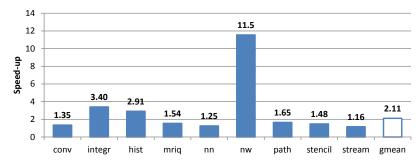

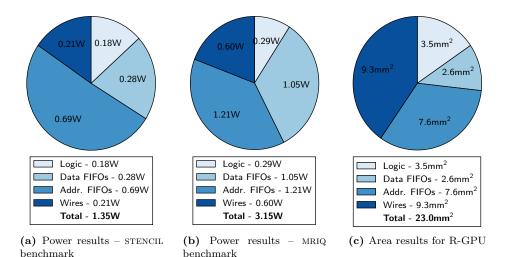

The final contribution is an extension to the GPU architecture, resulting in a reconfigurable GPU, called R-GPU. This extension improves not only performance but also power and energy efficiency. R-GPU is an addition to a GPU, which can still be used in its original form, but also has the ability to reorganize the cores of a GPU in a reconfigurable network. In R-GPU data movement and control is implicit in the configuration of this network. Each core executes a fixed operation, reducing instruction decode count and increasing power and energy efficiency. R-GPU improves the performance of voting algorithms, e.g. histogram is improved 2.9× over an optimized GPU implementation. Other benchmarks profit as well. On a set of benchmarks an average performance improvement of  $2.1 \times$  is measured. Especially algorithms which have a limited level of parallelism due to data dependencies, such as calculating an integral image, benefit from the proposed architecture changes. Furthermore, power consumption is reduced by 6%, leading to an energy consumption reduction of 55%, while the area overhead of R-GPU is only 4% of the total GPU's chip area.

With the above software techniques and hardware modifications GPUs are now much more applicable for the class of voting algorithms.

### Contents

| <b>1</b> | Intr | oduction                              | 1  |

|----------|------|---------------------------------------|----|

|          | 1.1  | GPU history                           | 2  |

|          | 1.2  | Trends in GPGPU research              | 6  |

|          | 1.3  | Problem statement                     | 8  |

|          | 1.4  | Contributions & thesis overview       | 9  |

| <b>2</b> | GP   | U architecture & programming model    | 11 |

|          | 2.1  | CPU vs. GPU: multi-core vs. many-core | 12 |

|          | 2.2  | CUDA & OpenCL programming models      | 13 |

|          | 2.3  | GPU architecture                      | 16 |

|          |      | 2.3.1 Tesla architecture              | 17 |

|          |      | 2.3.2 Fermi architecture              | 17 |

|          |      | 2.3.3 Kepler architecture             | 18 |

|          |      | 2.3.4 Maxwell architecture            | 19 |

|          |      | 2.3.5 Scratchpad memory               | 21 |

|          | 2.4  | GPU compilation trajectory            | 22 |

| 3        | Effi | cient histogramming                   | 23 |

|          | 3.1  |                                       | 25 |

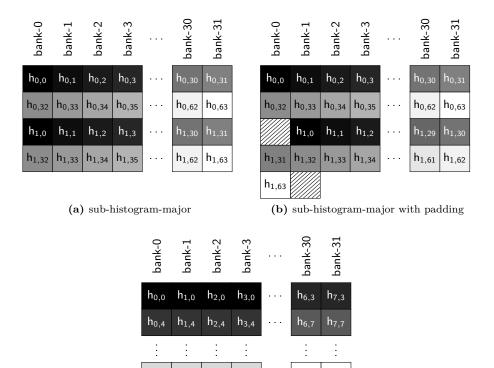

|          | 3.2  | Sub-histogram memory layout           | 27 |

|          | 3.3  | GPU: global memory atomics            | 29 |

|          | 3.4  |                                       | 34 |

|          | 3.5  | GPU: warp-private histogram           | 38 |

|          | 3.6  |                                       | 43 |

|          | 3.7  | Discussion                            | 46 |

|          | 3.8  | Related work                          | 48 |

|          | 3.9  | Conclusions                           | 49 |

| 4 | Hou | 1gh transform                                     | 51  |

|---|-----|---------------------------------------------------|-----|

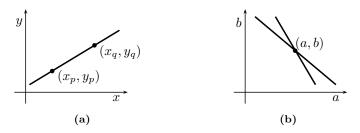

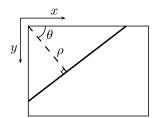

|   | 4.1 | Hough transform algorithm for lines               | 53  |

|   |     | 4.1.1 Cartesian coordinate system                 | 54  |

|   |     | 4.1.2 Polar coordinate system                     | 54  |

|   | 4.2 | Hough transform on CPU                            | 55  |

|   | 4.3 | GPU: global memory atomics                        | 57  |

|   | 4.4 | GPU: scratchpad memory atomics                    | 60  |

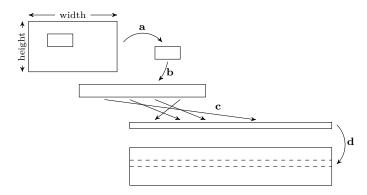

|   |     | 4.4.1 Step 1: creating the coordinates array      | 61  |

|   |     | 4.4.2 Step 2: voting in Hough space               | 62  |

|   | 4.5 | GPU: constant time implementation                 | 63  |

|   | 4.6 | Related work                                      | 66  |

|   | 4.7 | Conclusions                                       | 67  |

| 5 | Imr | proving GPU scratchpad memory atomic operations   | 69  |

|   | 5.1 | Execution model of atomic operations              | 70  |

|   | -   | 5.1.1 Lock mechanism                              | 71  |

|   |     | 5.1.2 Performance model                           | 72  |

|   |     | 5.1.3 Latency estimation                          | 73  |

|   | 5.2 | Implementation in GPGPU-Sim                       | 75  |

|   | 5.3 | Proposed hardware improvements                    | 78  |

|   | 5.4 | Evaluation of hardware improvements               | 80  |

|   |     | 5.4.1 Synthetic benchmarks                        | 80  |

|   |     | 5.4.2 Histogram                                   | 80  |

|   |     | 5.4.3 Hough transform                             | 82  |

|   | 5.5 | Related work                                      | 83  |

|   | 5.6 | Conclusions                                       | 83  |

| 6 | GP  | U scratchpad memory configurable bank addressing  | 85  |

|   | 6.1 | Motivation                                        | 86  |

|   | 6.2 | Access patterns to scratchpad memory              | 89  |

|   |     | 6.2.1 Memory access pattern classification        | 90  |

|   |     | 6.2.2 Examples of access pattern classifications  | 90  |

|   | 6.3 | Hash functions                                    | 93  |

|   |     | 6.3.1 Bit-vector permutation hash function        | 94  |

|   |     | 6.3.2 Bit-vector XOR hash function                | 94  |

|   |     | 6.3.3 Bitwise permutation hash function           | 95  |

|   |     | 6.3.4 Bitwise XOR hash function                   | 95  |

|   |     | 6.3.5 Hardware design and evaluation              | 96  |

|   | 6.4 | Hash function configuration                       | 98  |

|   |     | 6.4.1 Bit-vector exhaustive search algorithm      | 98  |

|   |     | 6.4.2 Bitwise search algorithm based on heuristic | 99  |

|   | 6.5 |                                                   | 103 |

|               | 6.6    | Experimental results                                                                           | 104 |

|---------------|--------|------------------------------------------------------------------------------------------------|-----|

|               |        | 6.6.1 Hardware hash function results                                                           | 105 |

|               |        | 6.6.2 Software hash function results                                                           | 108 |

|               | 6.7    | Related work                                                                                   | 111 |

|               | 6.8    | Conclusions                                                                                    | 112 |

| _             |        |                                                                                                | 110 |

| 7             |        | 8                                                                                              | 113 |

|               | 7.1    |                                                                                                | 114 |

|               | 7.2    |                                                                                                | 115 |

|               |        | 7.2.1 Inter SM communication                                                                   |     |

|               | 7.0    | 7.2.2 Programming model                                                                        |     |

|               | 7.3    |                                                                                                | 121 |

|               |        | 7.3.1 Benefit 1: removing redundant memory loads                                               |     |

|               |        | I B B B B B B B B B B B B B B B B B B B                                                        | 122 |

|               | 7.4    |                                                                                                | 123 |

|               |        | 7.4.1 Front end                                                                                |     |

|               |        | 7.4.2 Back end                                                                                 |     |

|               |        | 7.4.3 Simulator                                                                                | -   |

|               | 7.5    | Evaluation                                                                                     |     |

|               |        | 7.5.1 Benchmarks                                                                               |     |

|               |        |                                                                                                | 129 |

|               |        |                                                                                                | 131 |

|               |        |                                                                                                | 131 |

|               |        | 7.5.5 Power & area estimation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |     |

|               | 7.6    |                                                                                                | 136 |

|               | 7.7    | Conclusions                                                                                    | 137 |

| 8             | Cor    | clusions & future work                                                                         | 139 |

| Bi            | ibliog | graphy                                                                                         | 143 |

| A             | cknov  | wledgements                                                                                    | 155 |

| C             |        | ulum Vitae                                                                                     | 157 |

| C             | urric  | ulum vitae                                                                                     | 157 |

| $\mathbf{Li}$ | st of  | publications                                                                                   | 159 |

### CONTENTS

# chapter 1

### Introduction

Modern day life is unimaginable without all the ICT technology we use every day, like computers, tablets, smart phones, digital cameras, etc. All this technology uses an enormous amount of compute power to perform its designated task. As an example, let's take a picture of a group of people with our mobile phone, and upload it to a social media website. The process starts with demosaicing the image sensor data into pixel values [57], applying some lens corrections [19], color space conversion [6] and color corrections [31]. After the picture is compressed to a (relatively) small file, it can be uploaded to the social media website. In the *cloud* of the social media website the photo can be analyzed, and faces can be automatically detected, recognized<sup>1</sup> and annotated [99].

All these steps require a large amount of compute power, preferably with the lowest amount of energy consumption possible. For a mobile phone energy efficiency is essential to support a battery life of at least one day. The social media website on the other hand would like to keep its energy bill low. Some of the processing steps are usually implemented in application-specific hardware, like the low-level image processing in the mobile phone. This is an energy efficient way of implementing this functionality, but also a very non-flexible one. Other processing steps, like face recognition, are usually performed on large clusters of CPUs in data centers, which is flexible but not very energy efficient.

The processing steps in this example can also be implemented on Graphics Processing Units (GPUs). GPUs are many-core processors that execute huge amounts of *threads* in SIMD style vectors. SIMD processors in general are very energy efficient [36], as they only fetch, decode and dispatch a single instruction

<sup>&</sup>lt;sup>1</sup>With the compute power of contemporary mobile devices, like NVIDIA's Tegra [80] chip, it is also possible to perform face recognition on the processor of the smart phone [116].

for a vector of processing elements. The many threads in a GPU keep it flexible, or at least flexible enough to perform all kinds of computations. This became known as General-Purpose computing on Graphics Processing Units, or GPGPU.

The history of GPUs and how they became the many-core processors suitable for all kinds of computations is described in Section 1.1. Next the trends in GPU and GPGPU research over the last decade are given in Section 1.2. Finally the problem statement and contributions of this thesis are listed in Sections 1.3 and 1.4 respectively.

### 1.1 GPU history

Graphics processors started out as fixed function display controllers which were used to offload the rendering of a (computer) screen from a general purpose CPU. The first graphics chips were only used for 2D rendering and could only draw lines, arcs, circles, rectangles and character bitmaps. Later graphics processors could also perform 3D rendering, a feature particularly interesting for computer games. In the beginning many of the rendering steps, especially those with floating point computations, were still performed on a CPU. Later graphics chips gained more and more capabilities, and could perform more and more steps of the rendering process by itself. At the turn of the century the first graphics processor which was actually called a GPU was released, the NVIDIA GeForce 256 [75]. It could do all the geometry calculations by itself, no longer relying on the host CPU and its floating point computations. A GPU was defined by NVIDIA in 1999 as:

**Definition** A GPU is a single-chip processor with integrated transform, lighting, triangle setup/clipping, and rendering engines that is capable of processing a minimum of 10 million polygons per second [75].

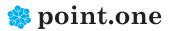

These first GPUs consisted of fixed processing pipelines. Each stage in the pipeline had a specific function, implemented in specialized hardware. An overview of a basic graphics rendering pipeline is shown in Fig. 1.1. Common steps in such a pipeline are [55]:

- *model transformations:* transform objects' coordinates to a common coordinate system (e.g. rotation, translation, scaling).

- *lighting:* computation of each triangle's color based on the lights in the scene. Traditionally Phong shading [91] was used in this step.

- *camera simulation:* projection of each colored triangle onto the virtual camera's film plane.

- *rasterization:* conversion of triangles to pixels, including clipping to the screen's edges. The color of each pixel is interpolated from the vertices that make up a triangle.

**Figure 1.1:** Basic graphics rendering pipeline. At the left primitives and vertices forming a 3D scene enter the pipeline. A primitive consists of one or more vertices. Each vertex has attributes such as position, color and texture. The *vertex shader* transforms the vertices' coordinates and projects them on the virtual camera's film plane. The *rasterizer* converts the triangles into fragments and the *pixel shader* maps a texture to them. Finally all fragments are combined into a 2D array of pixels to be displayed.

• *texturing:* mapping of textures to pixels in case a texture is used for added realism. Texture coordinates are calculated before in the rasterization step.

Step by step these fixed, hardwired functions were replaced by programmable processors, usually called *shaders* in GPUs. For example, the NVIDIA GeForce 3, launched in February 2001, introduced programmable vertex shaders [52]. The vertex shader can be used for model transformations, lighting calculations and camera simulation. These calculations consist mainly of matrix-vector multiplications, exponentiation and square root computations; therefore vertex shaders provided hardware capable of doing these calculations efficiently.

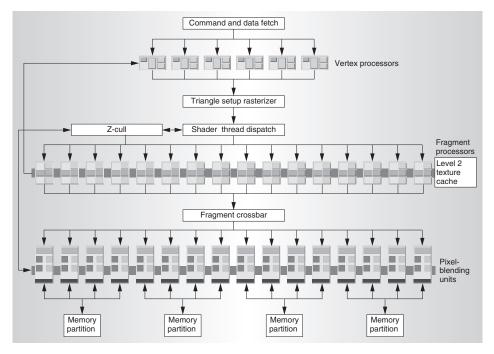

The only data type supported by the vertex shaders in the GeForce 3 is single precision floating point [52], either as a scalar value or as a four component vector. The instruction set of the vertex shader [52] was tailored to its graphics rendering task and contained 17 operations. There are the basic operations such as add, multiply and multiply-add, but also three and four term dot products and a special instruction for Phong lighting. No branch instructions are available in the GeForce 3 vertex processor. Simple if-then-else evaluation is only supported through sum-of-products using 1.0 and 0.0 [52]. The GeForce 3 vertex processor uses multi-threading to hide pipeline latency, just like modern day GPUs.

Later, GPUs also added a programmable pixel shader (called fragment shader by OpenGL) which computes the color and other attributes of each fragment, usually a pixel. With the introduction of OpenGL version 2.0 in 2004 [95] the OpenGL Shading Language (GLSL) [46] was introduced. GLSL made it possible to program shaders in a C-like language instead of the ARB assembly language?

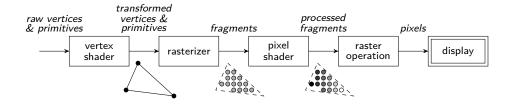

An example of a GPU with programmable vertex and pixel shaders is the NVIDIA GeForce 6800, introduced in 2004. A block diagram of its architecture

<sup>&</sup>lt;sup>2</sup>The ARB assembly language is a low-level shading language. It was created by the OpenGL Architecture Review Board (ARB) to standardize GPU instructions controlling the hardware graphics pipeline.

**Figure 1.2:** GeForce 6800 block diagram with 6 vertex processors, a rasterizer, 16 fragment processors and 16 pixel blending units. [61]

**Figure 1.3:** GeForce 6800 vertex processor block diagram consisting of a vector multiply-add unit, a scalar special-function unit and a texture unit. [61]

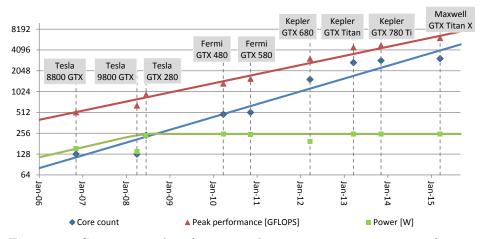

Figure 1.4: Core count, peak performance and maximum power consumption of various high-end GPUs at their time of introduction and their corresponding trend lines over the last 8 years.

with dedicated hardware for the vertex shaders, rasterizer and fragment shaders is shown in Fig. 1.2. A detailed overview of the vertex shader is shown in Fig. 1.3. More details about the GeForce 6800 and its design process can be found in [61].

Although the programmable shaders are more flexible than the fixed function pipeline, shaders can still be underutilized significantly. One video game might require more vertex than pixel shaders, while another might have the reverse requirements. Even in a single frame an imbalance can occur. For example, when a blue sky is drawn at the top of a frame, the vertex shader is mostly idle while the pixel shader is busy. In another part of the frame a complex figure, such as a tree with many branches and leafs, is drawn, which saturates the vertex shader.

This problem was solved by combining the different types of shaders in unified shaders. These were first introduced in the ATI Xenos chip found in the Xbox 360 game console [55] and later also in the NVIDIA GeForce 8800 GPUs [53] used in personal computers. By having one type of shader for all operations the load-balancing problem was resolved, as a varying part of the available shaders can be allocated to each processing stage.

Unified shaders made GPUs much more interesting for GPGPU applications. To simplify the programming, new programming paradigms were introduced. First NVIDIA launched CUDA [64] for their GPUs in 2007. Later, in December 2008, the Khronos Group released OpenCL 1.0 [32], an open standard for programming heterogeneous systems (e.g. single, multiple or combinations of CPUs, GPUs, DSPs and FPGAs).

The first NVIDIA architecture with unified shaders was the GeForce 8800 GTX introduced in November 2006. Its Tesla architecture [53] contains 128 cores. This number increased exponentially over the next eight years with the introduction of new GPU architectures to thousands of cores [78], an increase of  $24 \times$  in just eight

years. More features were added to improve not only graphics rendering, but also general purpose performance. For example, in the Tesla GPUs the texture cache was often (ab)used by GPGPU programmers to speed-up their applications. Later GPUs added a general L1 cache to improve memory access performance.

Compute performance did not scale at the same pace as the number of cores did. In the same eight year period (2006-2014) compute performance has increased "only"  $12\times$ . Performance per Watt (calculated as compute performance over power consumption) has improved even less, by a mere  $7\times$ . Even worse is the memory bandwidth scaling, which improved by  $3.9\times$  over the last eight years, while memory latency has stayed almost constant.

Power consumption has reached a ceiling of 250 W in 2008, which is the maximum amount of power a GPU can dissipate in a regular desktop computer. At the same time the clock frequency of GPUs diminishes in order to fit the ever increasing number of cores in the power budget of a GPU. This together reveals a trend in which more parallelism by more cores is preferred over clock frequency. In other words, more hardware is used in bigger chips to be able to increase performance and energy efficiency. This trend is clear from Fig. 1.4, where the number of cores, compute performance and power consumption of a number of GPUs introduced over the last eight years is shown. A similar trend can be seen for CPUs. Since 2005 their clock frequency hardly increases anymore but the number of cores started to increase [18]. Also for CPUs the only road to more performance was found in adding cores, rather than increasing the clock frequency.

### **1.2** Trends in GPGPU research

Early GPU research focused largely on improving the quality of the generated images. One of the most cited papers in this field is *Illumination for computer* generated pictures by Phong [91]. In this work the *Phong reflection model* and the *Phong shading interpolation method* are introduced. Combined the two methods are called *Phong shading* and describe the way a surface reflects light as a combination of the diffuse reflection of rough surfaces with the specular reflection of shiny surfaces.

With the introduction of the C-based GLSL shading language in OpenGL 2.0 in 2004 (see Section 1.1), more and more researchers started to investigate the use of GPUs for other purposes than rendering images. With the various shaders in the GPU now being relatively easily programmable, creative solutions were found to utilize the floating point capabilities of the GPUs. For example, the OpenVIDIA project [20] created a computer vision and image processing library implemented in OpenGL. Fragment shaders were used as filters, for example an edge detection filter. Inputs and outputs are mapped to textures. Also more complex computer vision algorithms, such as the Hough transform, are implemented on a vertex shader. An overview of the use of GPUs and their graphics APIs in applications other than computer graphics is made by Owens et al. in [87].

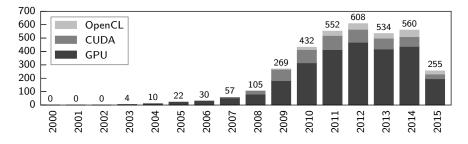

Figure 1.5: Number of papers in the *IEEEXplore* database with the words *GPU*, *CUDA* or *OpenCL* in the title since 2000. Note: the number of papers for 2015 are up to October 12 only.

The first GPGPU papers appeared in the *IEEEXplore* database in 2003. As programming GPUs was still hard, the number of papers was low, only 6 papers in 2003 and 10 papers in 2004. After the introduction of unified shaders in 2006 and the release of the CUDA and OpenCL programming languages the number of papers published rose to 30 in 2006, 57 in 2007 and 105 in 2008. While the programming models became more mature, and easily programmable GPUs became available to a large audience, GPGPU research became a hot topic, with over 400 GPU related papers published every year in the *IEEEXplore* database since 2010. Over 3400 papers with the words *GPU*, *CUDA* or *OpenCL* in the title have appeared in the *IEEEXplore* database since 2003, as illustrated in Fig. 1.5.

At first many papers focused on mapping algorithms to GPUs. Enormous speed-ups of GPUs over CPUs of hundreds or even thousands of times were presented. This trend was suddenly stopped after a group of Intel engineers published the paper *Debunking the 100X GPU vs. CPU myth: an evaluation of throughput computing on CPU and GPU* [48]. The focus changed to GPU architecture research, creating a more versatile, easily programmable and energy efficient GPU.

The first paper with the word GPU in its title appeared in the International Symposium on Computer Architecture, ISCA, the most important computer architecture conference, in 2009. The analytical model for a GPU by Hong and Kim [39] was the only GPU paper that year presented at ISCA. The year after there were two GPU related papers, with Hong and Kim presenting an extension of their model [40] and the aforementioned debunking paper [48]. During the next years the number of papers about GPU architecture increased steadily. Since 2012 a complete session is devoted to GPUs. ISCA 2015 dedicated even two sessions to GPU papers, showing that GPU architecture research is still a hot topic.

NVIDIA's research project *Echelon* [45] from 2011 investigates an architecture for a heterogeneous high-performance computing system. The goal is to create a GPU which has three times the performance, and four times the energy efficiency of a modern day GPU. The plan is to improve data locality by adding caches and scratchpad memories. All potential parallelism is exploited, including instruction-level parallelism (ILP), data-level parallelism (DLP), and fine-grained task-level parallelism (TLP). Hardware utilization is improved by creating a multilevel thread scheduling, and a dynamic warp width is used to handle divergent code. Data accesses are made more energy efficient by using 3D stacked memory which requires less energy per access than regular GDDR memory. Furthermore, the CPU and GPU are integrated to remove costly memory transfers. Extrapolating the graphs in Fig. 1.4 shows that these goals could be achieved in 2018.

### **1.3** Problem statement

The ever increasing number of cores in a GPU can be used efficiently by applications with an abundance of parallelism. The performance gains of newly introduced GPUs is often shown using applications which operate on large datasets of millions of elements, e.g. matrix multiplication and FFT. For other algorithms with an inherent much lower level of parallelism it is much harder to efficiently use the increasing number of cores. One might say that these algorithms are more suited for a CPU, and hence should be executed on a CPU. However, these algorithms are not executed in isolation but interleaved with other applications. Executing an algorithm on the CPU would imply that the data has to be copied from the GPU to the CPU and back again.

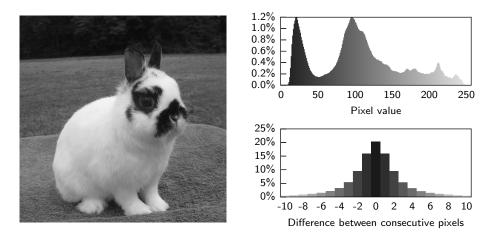

For example, in an image processing pipeline an image is first constructed using demosaicing of the pixels in a Bayer pattern. Then noise reduction can be applied, after which a histogram of the image is made which is used within an equalization step to improve the contrast of the image. The demosaicing, noise reduction and equalization steps are embarrassingly parallel and map well to the many cores of a GPU. However, updating bins in a histogram is sequential. A pixel's value has to be read and the corresponding bin in the histogram updated before the next pixel can be processed. The reason is that when multiple updates to the same bin occur at the same time, only one of these updates will be saved. The other updates are lost, leading to an incorrect histogram. The performance of the parallel algorithms scales with the increase in the number of cores of new GPUs. The performance of the sequential algorithms does not scale, and hence will quickly become the bottleneck in the image processing pipeline.

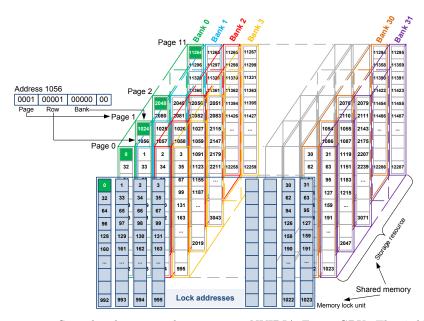

On a GPU histogramming is usually implemented using atomic operations on the banked scratchpad memory for updating the bins. Atomic operations are supported in GPU hardware by locking the memory address of a histogram bin to a specific thread. The thread with access to the bin can update it, all others have to wait. Although the performance of atomic operations has been improved significantly over the last couple of generations of GPU architectures, the serialization caused by locking conflicts results in severe performance penalties.

Applications suffer more and more from the ever increasing gap between compute performance and memory bandwidth. Furthermore, memory access latency has not been improved much for the last generations of GPUs. Improving off-chip memory bandwidth is relatively easy, as more memory chips can be put in parallel, or run at a higher clock frequency. Also memory compression [85] can be used to mitigate the memory bandwidth problem. This provides a larger throughput of pixel data when rendering graphics, but does not help for GPGPU applications.

The GPUs on-chip memories are commonly used as small scratchpads with a higher bandwidth and lower latency than the off-chip memory. However, the obtained bandwidth in reality is often much lower due to bank conflicts.

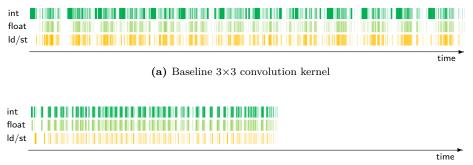

Not only the compute performance, but also the energy efficiency of GPUs has to be improved, as GPUs are often limited by the maximum amount of power they can dissipate. Future directions for GPU architectures to improve on both these issues are described in [69]. Reducing stall cycles by increasing the number of active threads is one solution to hiding off-chip memory latency, but is dependent on the available resources of the GPU to support the extra threads. Often stall cycles occur when many threads access the same resources at the same time. For example, threads first calculate an address, then load data from memory and finally perform some computations on the data. All these actions use different parts in the GPU, such as integer units, load-store units or floating point units. If these resource requirements could be spread over time, stall cycles could be avoided, resulting in improved performance and energy efficiency.

Summarizing above, this thesis addresses the following three problems:

- 1. Voting applications, like histogram and Hough transform, show poor performance on GPGPUs due to serialization caused by atomic operations.

- 2. In addition, many (voting) applications experience memory bandwidth problems on GPGPUs, caused by lock access and bank conflicts.

- 3. Finally, many GPGPU applications under-utilize the available memory bandwidth due to unbalanced resource usage, which is primarily caused by the GPU's execution model.

Above problems severely reduce the applicability of GPUs for general purpose computing. This thesis researches these three problems in depth, and provides several solutions, sketched in the following section, and presented in detail within Chapters 3–7.

### 1.4 Contributions & thesis overview

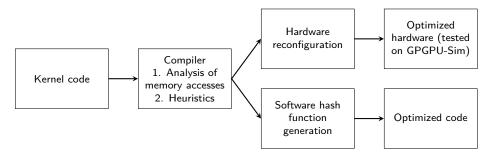

This thesis follows the trend of GPU related research over the last years (see Section 1.2). After an overview of a contemporary (NVIDIA) GPU architecture in Chapter 2, mappings to GPUs of algorithms with a low inherent level of parallelism are explored first. Next, small architectural changes to the GPU are proposed, which aid the performance gains created by the previously explored software techniques. Finally a larger change to a GPU architecture is presented, called R-GPU. This architecture adds a communication network in between the cores of a GPU, transforming it into a spatial computing architecture. The first contribution of this work is a set of software techniques that improve the parallel updating of bins in voting algorithms, histogram and Hough transform in Chapters 3 and 4 respectively. These techniques are based on results published in [108, 109]. Parallel updating of voting bins is done on GPUs using atomic operations. By duplicating the bins a significant performance improvement can be gained. First multi-core CPU implementations are made which utilize the SSE and AVX vector extensions of the CPU. These optimizations improve the performance of the histogram application on a CPU by  $10\times$ . The baseline GPU implementation has a similar performance as a single core CPU implementation, but by using the proposed software techniques the best GPU histogram implementation outperforms the optimized multi-core CPU implementation by  $4.8\times$ .

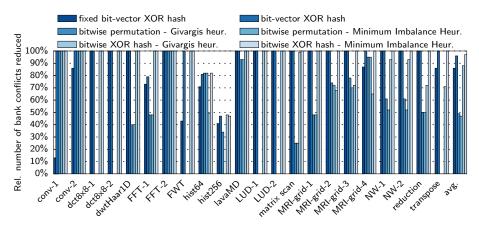

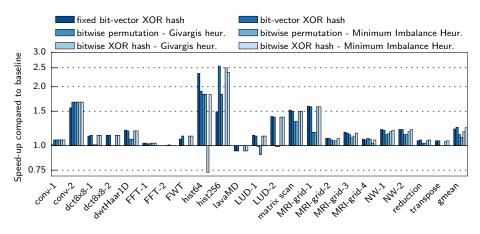

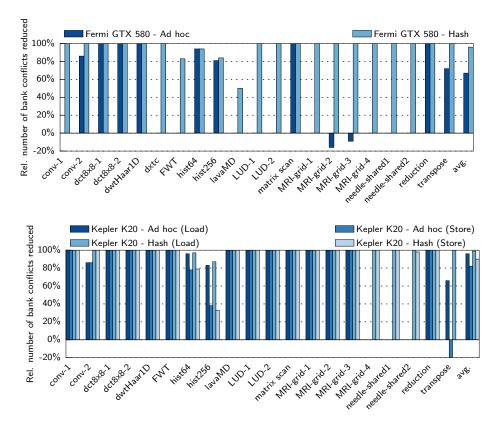

The second contribution is a hardware change in the addressing of the banks and locks of the GPU's on-chip scratchpad memory. The scratchpad memory is divided into banks and contains locks to support atomic operations. The duplication of the output bins requires more scratchpad memory and causes an uneven distribution of the memory accesses over the banks and locks. A fixed hash function is introduced in Chapter 5, distributing the memory accesses more equally over the memory's banks and locks. This improves performance between  $1.8 \times$ and  $4.9 \times$  for histogramming, depending on the software technique used. Hough transform is improved up to  $1.8 \times$  by this hash function. The fixed hash function and its results are published in [105]. Hash functions can also be beneficial for applications without atomic operations, which can still suffer from bank conflicts. Configurable hash functions to mitigate these conflicts are introduced in Chapter 6, which remove nearly all conflicts and increase performance  $1.2 \times$  on average. The configurable hash functions and their results are published in [106].

The last contribution is an extension to the GPU architecture as proposed in Chapter 7. This reconfigurable GPU, called R-GPU, not only improves performance but also power and energy efficiency for various applications. R-GPU is an addition to a GPU, which can still be used as such, but also has the ability to reorganize the cores of a GPU in a reconfigurable network. In R-GPU data movement and control is implicit in the configuration of the network. Each core executes a fixed operation, reducing instruction decode count and increasing power and energy efficiency. R-GPU improves the performance of voting algorithms, for example histogramming is improved  $2.9 \times$  over an optimized GPU implementation. Other benchmarks profit as well. On a set of benchmarks an average performance improvement of  $2.1 \times$  is measured. Especially algorithms which have a limited level of parallelism due to data dependencies, such as integral image, benefit from the proposed architecture changes. Furthermore, power consumption is reduced by 6%, leading to an energy consumption reduction of 55%, while the extra area costs of R-GPU are only 4% of the total GPU's chip area. R-GPU and its results are published in [103, 104].

Finally, Chapter 8 concludes this thesis and summarizes possible directions for future work.

# CHAPTER 2

### GPU architecture & programming model

As illustrated in the previous chapter, GPUs first appeared as dedicated accelerators for graphics rendering. Later, the various programmable processors in a GPU, called shaders, became programmable. An example of such a GPU is the GeForce 6800, shown in Section 1.1. The last step for GPUs to become truly applicable for General-Purpose computing on Graphics Processing Units (GPGPU) was when the various shaders were merged into unified shaders, also known as streaming multiprocessors (SMs).

Even with only one type of shaders, the microarchitecture of a modern day GPU can still be very complicated. The cores within an SM (often called processing elements or PEs) are simple and support only a handful of instructions. Shared resources in each SM and the high level of multi-threading make it a very intricate architecture. Combining multiple SMs in a GPU which have to share resources as well only adds to this complexity.

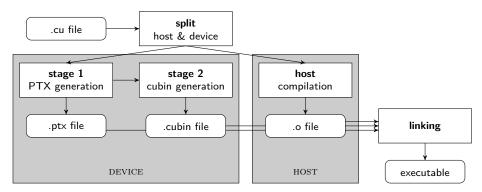

In this chapter a brief introduction on the architecture of contemporary GPUs is given. The last four GPU architectures by NVIDIA, all used in this thesis, are discussed: Tesla [53], Fermi [76, 117], Kepler [77, 78] and Maxwell [84, 85]. First a comparison is made between a modern day CPU and GPU in Section 2.1. Section 2.2 gives a short summary of the programming model of GPUs, including the CUDA and OpenCL terminology. Section 2.3 discusses the GPU microarchitecture in detail. An overview of all relevant parameters of the four GPUs used in this thesis can be found in Table 2.2. Section 2.4 concludes this chapter with a short description of the compilation trajectory used for GPUs.

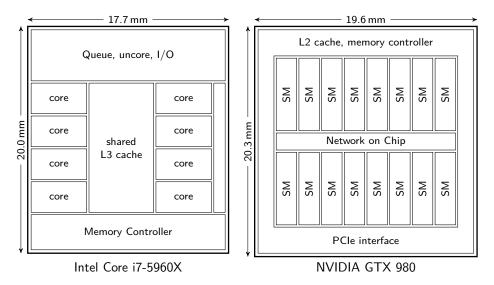

Figure 2.1: Chip layout comparison of an Intel<sup>®</sup> Core<sup>TM</sup> i7-5960X eight core CPU and an NVIDIA GTX 980 with sixteen Streaming Multiprocessors (SMs).

### 2.1 CPU vs. GPU: multi-core vs. many-core

Where CPUs spend most of their chip area on a couple of large, sophisticated cores, GPUs spend their chip area on a large number of clustered processing elements. Clusters of processing elements, or cores, are called Streaming Multiprocessors by NVIDIA. A comparison of chip layout between an eight core Intel® Core<sup>TM</sup> i7-5960X CPU and an NVIDIA GTX 980 with sixteen SMs is shown in Fig. 2.1. The layouts are based on actual die photos and renderings. Both chips are approximately the same size  $(356 \text{ mm}^2 \text{ vs. } 398 \text{ mm}^2)$ , but the Intel CPU is manufactured using Intel's 22 nm technology, while the NVIDIA GPU is manufactured using TSMC's 28 nm technology.

The Core i7-5960X uses approximately one third of its area for its eight cores. About 20% is used for the 20 MB of L3 cache, which is shared among the cores. One quarter of the chip area is used for uncore parts and I/O of the CPU, such as the PCIe controller. The DDR4 memory controller takes approximately 17% of the area, and another 5% is undefined.

The core of the Intel processor is optimized for single thread performance. Many hardware elements do not contribute to the compute power of the processor, i.e. they do not perform computations themselves, but are there to improve the throughput of instructions. For example, the pipeline bypassing network makes results earlier available for subsequent instructions. Also, a branch prediction unit reduces pipeline stalls by keeping track of branch conditions. Large caches (L1-instruction, L1-data and combined-L2) are included to reduce memory access latency. To further enhance performance, CPUs have been equipped with vector instructions. These SIMD (single instruction multiple data) instructions perform the same operation on all elements in the vector. The Core i7-5960X supports the MMX, SSE and AVX vector extensions. These vector instructions work on 64, 128 and 256 bit data elements respectively. For example, an MMX, SSE or AVX instruction works on two, four or eight 32-bit values at the same time. All these vector extensions together add about 500 instructions to the baseline x86 instruction set. This creates a (relatively) large core. Combined with a large L3 cache, a big memory controller and some I/O they fill up the entire chip.

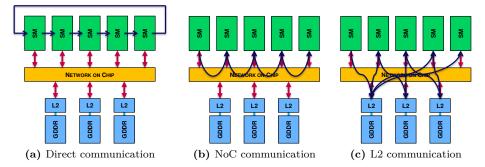

The NVIDIA GTX 980 uses about half of its chip area for its sixteen SMs. Each SM consists of 128 cores, a register file, scratchpad memory and L1 cache, as will be discussed in Section 2.3. The other half is used for the Network on Chip (NoC), L2 cache, memory controller and PCIe interface. The NoC is used to connect the SMs to the L2 cache and memory controller, but not for communication between SMs.

To fit all 2048  $(16 \times 128)$  cores on the chip, they have to be (relatively) simple and small. Cores are grouped in vectors of 32, and four of these vectors are combined in an SM in the GTX 980. Grouping cores in vectors means they can share common parts, such as instruction-fetch-and-decode. In essence a GPU only executes instructions on vectors of 32 elements. Furthermore, these cores don't have a bypassing network or branch predictor. Branch instructions are only supported via predicate instructions. L1 caches are available in each SM, but are much smaller than on a CPU. Latency is hidden using multi-threading. The GPU's architecture will be explained in more detail in the next section.

The main concept of a GPU is to use many, small processing elements working in parallel. The latency of computations and memory accesses is hidden using multi-threading. These concepts were already used in the NVIDIA GeForce 3 in 2001. This was the first GPU with a programmable vertex shader [52], as discussed in Section 1.1. How this evolved in the GPGPU capable GPUs of today is described in Section 2.3. The programming model for these GPUs is described first in the next section.

### 2.2 CUDA & OpenCL programming models

To support the many multi-threaded cores in a modern GPU, new programming models have been developed. Since GPUs are used as compute accelerators which are attached to a CPU, programs consist of two parts. A *host* part is a regular application which runs on the CPU. This host part will launch the *device* part, called a kernel, which runs on the GPU.

The main programming languages for GPUs are CUDA [64] and OpenCL [32]. Alternatives are directive based languages (e.g. pragmas in C/C++) such as OpenACC and OpenMP 4. Both CUDA and OpenCL are extensions to the Cprogramming language. They require a programmer to write host code which

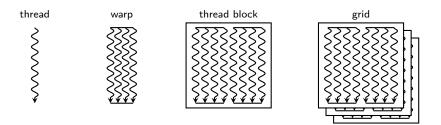

Figure 2.2: Hierarcy of threads, warps, thread blocks and grids in the CUDA programming model.

runs on a CPU. This host code is responsible for allocating memory on the GPU and copying data between CPU and GPU. Host code also starts the kernels which run on the GPU.

Kernels are so called device code, which runs on the GPU. CUDA introduces the concepts of threads, warps, thread blocks and grids, as also illustrated in Fig. 2.2. These concepts are called work-items, wavefronts, work-groups and computation domains in OpenCL. The CUDA vs. the OpenCL terminology is listed in Table 2.1. The number of threads (work-items) in a thread block (work-group) and the total number of thread blocks have to be specified by the programmer for each kernel individually. The size of the grid (computation domain) is determined as the product of the thread block size times the number of thread blocks.

Thread blocks (work-groups) consist of multiple threads (work-items), usually several hundred in a GPU. A specific thread block is executed on one SM, but multiple thread blocks can share an SM. On a GPU the threads of a thread block are (automatically) grouped in warps (wavefronts), which are executed like SIMD vectors. This makes executing warps energy efficient, since an instruction has to be fetched and decoded only once for all threads in a warp. It also causes GPUs to suffer from branch divergence. If one part of the threads in a warp takes the

| CUDA                          | OpenCL             |

|-------------------------------|--------------------|

| thread                        | work-item          |

| warp                          | wavefront          |

| thread block                  | work-group         |

| grid                          | computation domain |

| global memory                 | global memory      |

| shared memory                 | local memory       |

| local memory                  | private memory     |

| streaming multiprocessor (SM) | compute unit       |

| scalar core                   | processing element |

Table 2.1: CUDA vs. OpenCL terminology.

```

void saxpy(int n, float a, float *x, float *y)

2 {

int i;

з

for(i=0; i<n; i++) {</pre>

// calculate y = a * x + y

4

// for every index i<n

\mathbf{5}

y[i] = a * x[i] + y[i];

7

6

7 }

8

9 void sequential_example()

10 {

saxpy(n, 2.7, x, y);

11

12 }

```

Listing 2.1: sequential C implementation of SAXPY computing y = ax + y

```

__global__ void saxpy(int n, float a, float *x, float *y)

1

2 {

int i = blockIdx.x * blockDim.x + threadIdx.x;

3

if(i < n) {

// calculate y = a*x+y

4

y[i] = a * x[i] + y[i];

// for every index i<n</pre>

\mathbf{5}

6

}

7 }

8

9 void parallel_example()

10 {

saxpy << <ceil(n/256), 256>>>(n, 2.7, x, y);

11

12 }

```

**Listing 2.2:** parallel CUDA implementation of SAXPY computing  $\mathbf{y} = a\mathbf{x} + \mathbf{y}$

*if* part of a branch, and the other part of the threads takes the *else* branch, both branches have to be executed. In all current GPUs warps are formed statically; in NVIDIA GPUs a warp is a group of 32 threads with consecutive indexes. However, dynamic warp formation was already proposed by Fung et al. [21] in 2007.

Tens to thousands of thread blocks form a grid (compute domain). Thread blocks are assigned dynamically to SMs by the GPU, and cannot communicate with each other. The number of thread blocks in a kernel is independent of the number of SMs in a GPU. Specifying a large number of thread blocks for a kernel ensures that the kernel will perform well on small and large GPUs. The main difference between small and large GPUs is the number of SMs they have. Small GPUs will simply execute a smaller number of thread blocks at the same time than the larger GPUs, and hence take longer to execute all thread blocks.

The total number of threads active on a GPU at any given point in time (i.e. the resident threads) is usually much larger than the number of cores on a GPU. In order to hide pipeline- and memory access latency a GPU uses *fine-grained multi-threading*. After executing an instruction from one warp, the GPU switches immediately to another warp. This is made possible by the large register files on a GPU, which contain the context of all resident threads. This style of executing

many threads in SIMD style vectors, and switching threads after every instruction, is called *single-instruction*, *multiple-thread* (SIMT) processing [53].

### CUDA example

A sequential implementation of the SAXPY routine [66] is shown in Listing 2.1. Given scalar a and vectors  $\mathbf{x}$  and  $\mathbf{y}$  containing n elements each, it calculates the update  $\mathbf{y} = a\mathbf{x} + \mathbf{y}$ . An equivalent parallel implementation in CUDA is shown in Listing 2.2.

The kernel (device code) is shown on lines 1-7, the host code on lines 9-12. Each thread will calculate one element of **y**. The kernel starts by calculating the index **i** based on the thread index (inside the thread block) **threadIdx.x**, the thread block dimension **blockDim.x** and the thread block index **blockIdx.x** on line 3. As there may be more threads than elements in the vectors, the index is checked to be within the array bounds on line 4. Finally the actual SAXPY computation is performed on line 5.

The host code on line 11 launches the kernel. In CUDA the number of thread blocks and threads per block used to run the kernel are annotated within the  $\langle <$  and  $\rangle >$  brackets. On line 11 the kernel is started with 256 threads in each of the  $\lceil n/256 \rceil$  thread blocks. This ensures there are at least as many threads as there are elements in the vectors **x** and **y**.

### 2.3 GPU architecture

Contemporary CPUs, such as the Intel® Core<sup>TM</sup> i7-5960X described above, consists of a small number of cores, usually two, four or eight. GPUs on the other hand have many cores, hundreds or even thousands of cores. These cores are much simpler than the cores in a CPU. For example, the GPU cores execute instructions in-order and have no bypassing network or branch predictor.

The basic design of a modern day GPU contains groups of cores in what is called by NVIDIA streaming multiprocessors (SMs). The number of cores in an SM is fixed, but varies from one GPU architecture to another. The number of SMs in a GPU ranges from one or two for low-end GPUs to sixteen in high-end GPUs. Only some GPUs have more SMs, like the recently introduced NVIDIA Titan X which has twenty-four SMs.

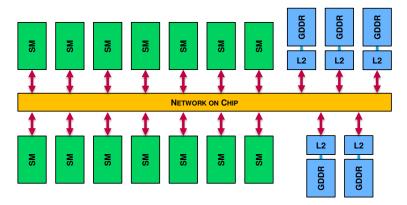

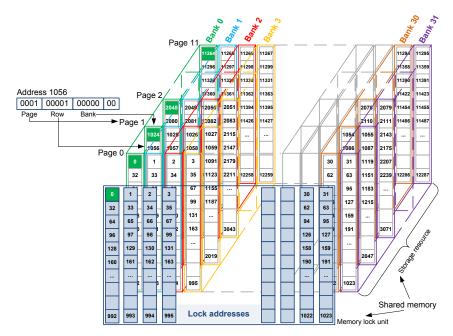

All SMs in the GPU are connected to a shared L2 cache and the off-chip memory (GDDR) via a network on chip (NoC), as shown in Fig. 2.3. It is not possible for SMs to communicate directly with each other via the NoC. The memory and the L2 cache are divided into partitions. Each memory partition is connected to one part of the L2 cache. The number of partitions is directly related to the width of the memory bus and the number of GDDR memory chips on the GPU card. In case of an NVIDIA GeForce GTX 470 (Fermi architecture) there are 14 SMs which connect to five memory partitions via the NoC.

Figure 2.3: A GPU consisting of 14 SMs and 5 memory partitions (GDDR) with L2 cache, all connected by a network on chip. This specific configuration can be found in an NVIDIA GTX 470.

The basic layout is the same for all GPUs: SMs are connected via a NoC to the L2 cache and off-chip memory. The design of the SMs itself changes significantly from one GPU generation to the other. In the next sections four GPU architectures from NVIDIA are discussed: Tesla, Fermi, Kepler and Maxwell. The scratchpad memory plays an important role in this thesis, and is discussed separately in Section 2.3.5.

### 2.3.1 Tesla architecture

Tesla was NVIDIA's first architecture with unified shaders [53]. It's SMs consist of eight cores, two special function units (SFUs), a scratchpad memory and a single warp scheduler. As warps comprise 32 threads, issuing a warp to the eight cores took four cycles. The cores in the SM are used for general computations, such as integer and floating point operations. The SFUs are used for more complex operations, such as sine, cosine and reciprocal calculations. This division is similar to the earlier GPUs such as the GeForce 3 and GeForce 6800 described in Section 1.1. The NVIDIA 8800 GT with the Tesla architecture is used in this thesis. It contains 14 SMs, more details can be found in Table 2.2.

### 2.3.2 Fermi architecture

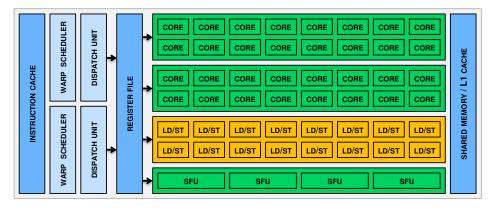

The SMs in the Fermi architecture [76,117] are much more complicated than the ones in the Tesla architecture. They consist of an instruction cache shared by two warp schedulers which have one dispatch unit each. There are also two groups of 16 cores, one group of 16 load-store units (LD/ST) and a group of four special function units (SFUs). The load-store units are used for memory accesses, both to the on-chip and the off-chip memory. Each SM also contains a scratchpad

**Figure 2.4:** Streaming multiprocessor (SM) design of an NVIDIA Fermi GPU, consisting of two warp schedulers and two dispatch units, a register file, two groups of sixteen cores (CORE), one group of sixteen load-store units (LD/ST), one group of special function units (SFU) and a combined scratchpad (shared) memory and L1 cache.

memory (called shared memory by NVIDIA) and an L1 data cache. A schematic overview of an SM in the Fermi architecture is given in Fig. 2.4.

Each of the two warp schedulers issues instructions via its dispatch unit to either a group of cores, the group of load-store units or the SFUs. The division of warps between the schedulers is static, one scheduler processes warps with an even index, the other scheduler processes the warps with an odd index. In case both schedulers want to issue an instruction to the load-store units, one of the schedulers has to stall, as there is only one group of load-store units available in each SM. The same holds when the two schedulers want to use the SFUs. Both schedulers can issue an instruction to their respective group of cores simultaneously. Or one scheduler can issue an instruction to a group of cores, and the other to either the load-store units or the SFUs.

A second generation of the Fermi architecture [117] was targeted for consumer graphics, where the first generation also aimed at high-performance computing. It added a third group of cores, but more importantly, a second dispatch unit to each warp scheduler. This made the GPU a superscalar architecture which could exploit instruction level parallelism (ILP). Each scheduler could now issue two instructions from the same warp to each group of processing elements as long as the instructions have no dependency on each other.

### 2.3.3 Kepler architecture

The Kepler architecture [78] extended the design of an SM to six groups of 32 cores each, two groups of SFUs and two groups of load-store units, as shown in Fig. 2.5. In total there are ten groups of processing elements and four schedulers with two dispatch units each. Keeping all ten groups of processing elements busy

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Instruction Cache               |      |      |      |      |       |         |        |        |                                                                 | Г     | Instruction Cache |         |       |         |                     |                                               |            |                     |              |            |     |                                 |             |                     |      |             |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|------|-------|---------|--------|--------|-----------------------------------------------------------------|-------|-------------------|---------|-------|---------|---------------------|-----------------------------------------------|------------|---------------------|--------------|------------|-----|---------------------------------|-------------|---------------------|------|-------------|------|

| Warp Scheduler Warp Scheduler Warp Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |      |      |      |      |       |         | V      | Varp S | chedul                                                          | ər 👘  |                   |         |       |         |                     |                                               |            | nstructi            | ction Buffer |            |     |                                 |             |                     |      |             |      |

| Dispatch Unit Di |                                 |      |      |      |      |       |         | Dispat |        |                                                                 |       |                   |         |       |         |                     | Warp Scheduler<br>Dispatch Unit Dispatch Unit |            |                     |              |            |     |                                 |             |                     |      |             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Register File (65,536 x 32-bit) |      |      |      |      |       |         |        |        |                                                                 |       |                   | + + + + |       |         |                     |                                               |            |                     |              |            |     |                                 |             |                     |      |             |      |

| * * * * * * * * * * * * * * * * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |      |      |      |      |       |         |        |        | Register File (16,384 x 32-bit) Register File (16,384 x 32-bit) |       |                   |         |       |         |                     |                                               |            |                     |              |            |     |                                 |             |                     |      |             |      |

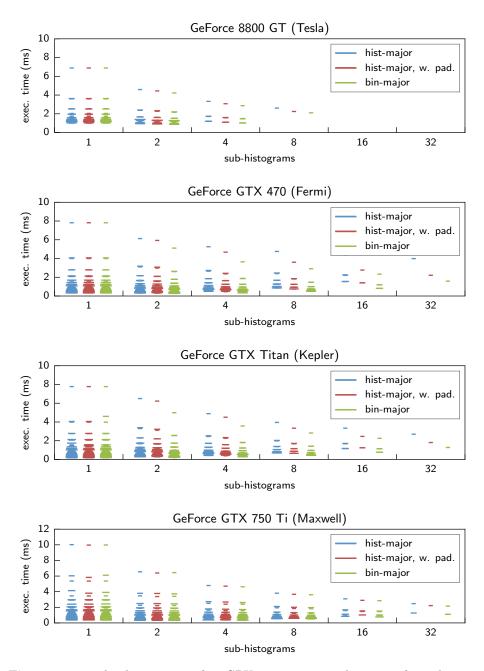

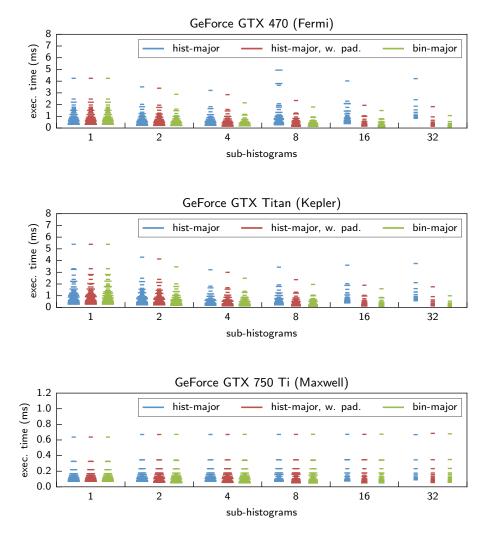

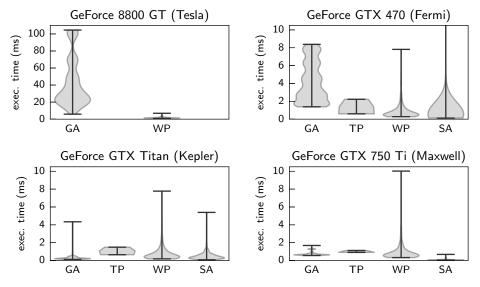

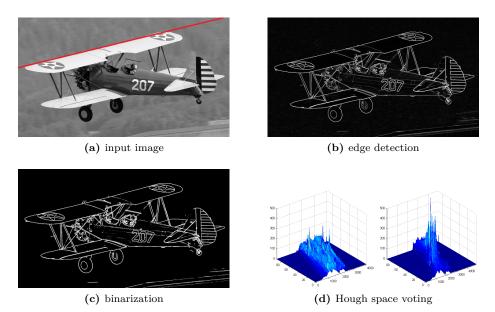

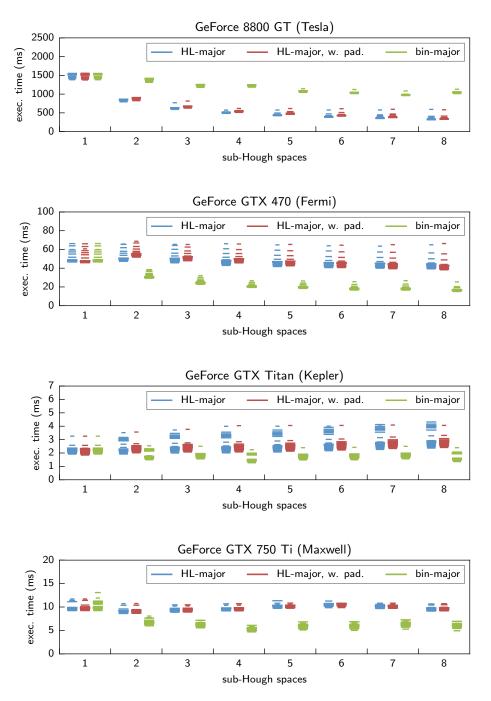

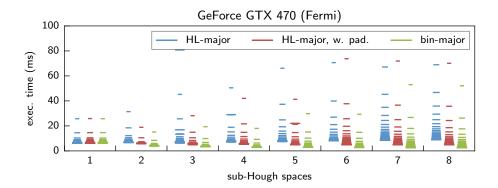

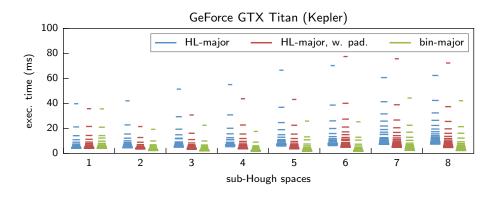

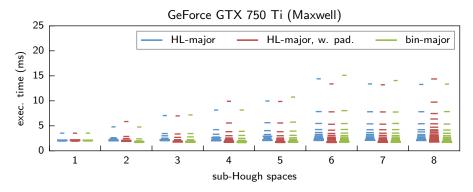

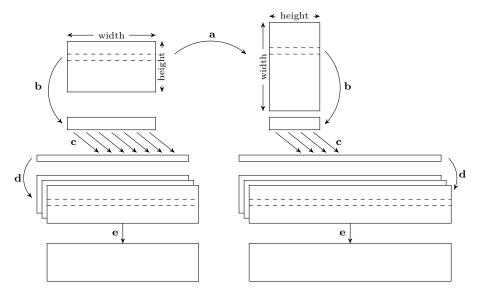

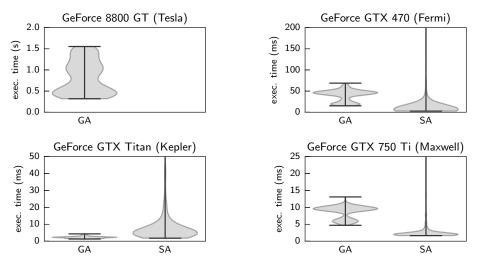

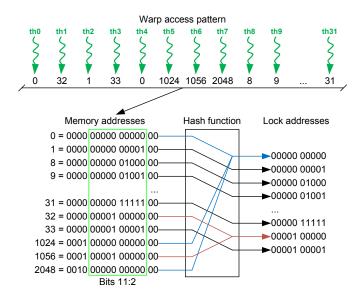

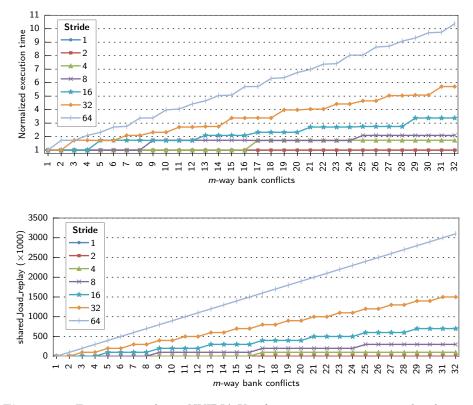

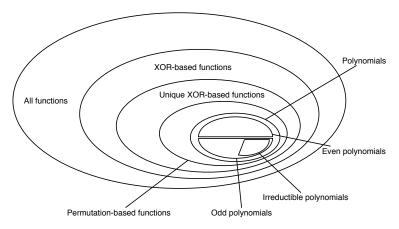

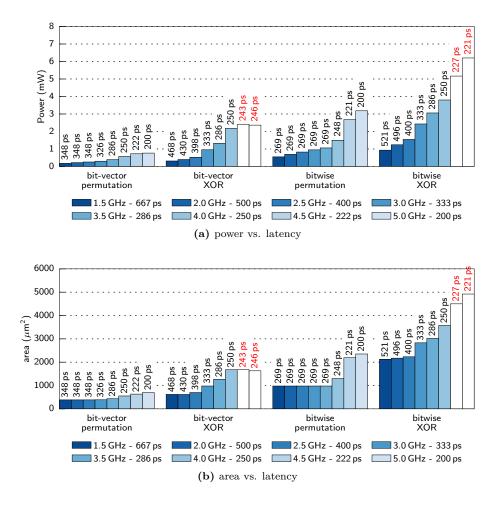

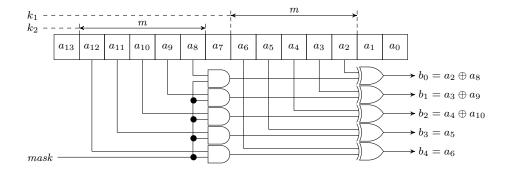

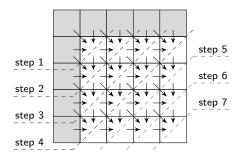

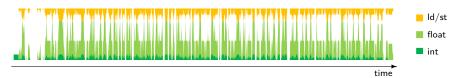

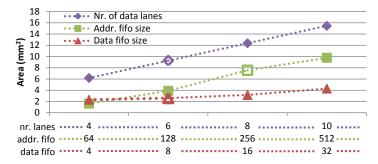

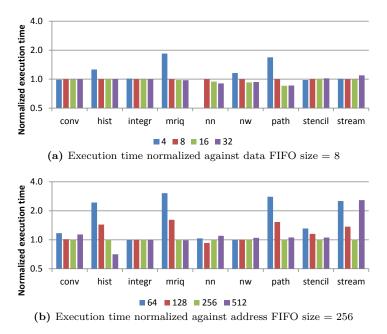

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core                            | Core | Core | Core | Core | LD/ST | SFU     | Core   | Core   | Core                                                            | Core  | Core              | Core    | LD/ST | SFU     |                     | Core                                          | Core       | Core                | Core         |            | SFU | Core                            | Core        | Core                | Core |             | SFU  |