# Instruction-set architecture synthesis for VLIW processors

## Citation for published version (APA):

Jordans, R. (2015). Instruction-set architecture synthesis for VLIW processors. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven.

Document status and date: Published: 01/12/2015

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

## Instruction-set Architecture Synthesis for VLIW Processors

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 1 december 2015 om 14.00 uur

$\operatorname{door}$

Roel Jordans

geboren te Roosendaal en Nispen

Dit proefschrift is goedgekeurd door de promotor en de samenstelling van de commissie is als volgt:

| voorzitter:     | prof.dr.ir. A.C.P.M. Backx                                       |

|-----------------|------------------------------------------------------------------|

| $1^e$ promotor: | prof.dr. H. Corporaal                                            |

| copromotor:     | dr. L. Jóźwiak                                                   |

| leden:          | prof.dr.Tech. J.H. Takala MSc (Tampere University of Technology) |

|                 | prof.dr. K.L.M. Bertels (Technische Universiteit Delft)          |

|                 | prof.dr.ir. P.H.N. de With                                       |

| adviseurs:      | dr.ir. J.A.J. Leijten (Intel Benelux)                            |

|                 | dr.ir. B. Mesman                                                 |

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# Instruction-set Architecture Synthesis for VLIW Processors

**Roel Jordans**

Doctorate committee:

| prof.dr. H. Corporaal         | Eindhoven University of Technology, promotor   |

|-------------------------------|------------------------------------------------|

| dr. L. Jóźwiak                | Eindhoven University of Technology, copromotor |

| prof.dr.ir. A.C.P.M. Backx    | Eindhoven University of Technology, chairman   |

| prof.dr.Tech. J.H. Takala MSc | Tampere University of Technology               |

| prof.dr. K.L.M. Bertels       | Delft University of Technology                 |

| prof.dr.ir. P.H.N. de With    | Eindhoven University of Technology             |

| dr.ir. J.A.J. Leijten         | Intel Benelux                                  |

| dr.ir. B. Mesman              | Eindhoven University of Technology             |

|                               |                                                |

This work is supported in part by the Artemis Joint Undertaking, project ASAM 100265.

© Copyright 2015, Roel Jordans

All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Cover design by Roel Jordans

Printed by CPI-Koninklijke Wöhrmann – The Netherlands

A catologue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-3963-5

# Summary

# Instruction-set Architecture Synthesis for VLIW Processors

The high energy efficiency and performance demands of image and signal processing components of modern mobile and autonomous applications have resulted in a situation where it is no longer feasible to only use general purpose processing systems to serve those applications. This has caused a strong shift to heterogeneous systems containing multiple highly specialized processors. While some tool support for the design process of such specialized processor architectures exists, key decisions are still made by human designers, usually based on incomplete and imprecise information. Combining this with the short interval between different product generations and limited design times strongly reduces the number of design alternatives that can be considered, and results in a sub-optimal design quality.

Current state-of-the-art technologies offer design automation for several steps of the design process by automating key activities such as the construction of a processor architecture from a high level description, the evaluation of candidate designs through simulation or emulation, or proposing extensions to an existing processor architecture. While these tools already substantially improve the design times over a completely manual design, further significant improvements can still be obtained, specifically through automation of the design analysis and decision making process. This dissertation proposes several significant improvements of the design effectiveness and efficiency through automation of several stages of the design process.

A three step approach to processor architecture design is presented which starts by using our new application analysis methods to obtain parallelism and performance estimates for the various compute intensive parts of the target application. These estimates are then used during an application restructuring phase which aims at improving the available parallelism and decides upon the mapping of application data into the processors internal memories. Taking this transformed version of the target application, its memory hierarchy as defined by the memory mapping, and the parallelism estimates allows us to propose an initial processor architecture which completes the second step. The third step is then to further refine the processor architecture and results in a highly specialized processor architecture description.

The research presented in this dissertation focusses on improving the following steps in the design process.

- A parallelism estimation method for estimating the instruction-level parallelism exposed by the application is presented. This method provides parallelism feedback used during the exploration of the application restructuring, but is also used for determining the appropriate number of issue-slots in the initial architecture. As a result, we are able to construct an initial processor architecture that both meets the performance requirements for the target application yet still is reasonably close to the final refined processor design.

- A processor architecture refinement method which allows us to avoid the (time consuming) construction of intermediate candidate processor architectures. Our approach only needs to construct both the initial and refined designs, all other considered candidate architectures need not be constructed.

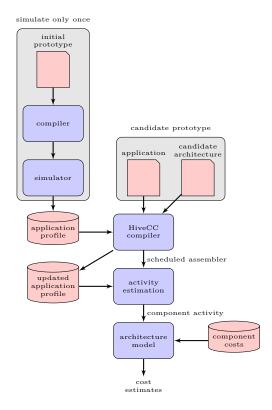

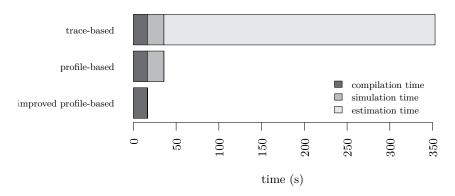

- A rapid energy consumption methodology which combines the block execution profile of a simulation of the target application with its scheduled assembly listing. This makes our energy estimation method independent of the number of simulated processor clock cycles and enables the use of larger, more representative, input data sets, thus allowing for a both a faster and more realistic evaluation of the candidate designs.

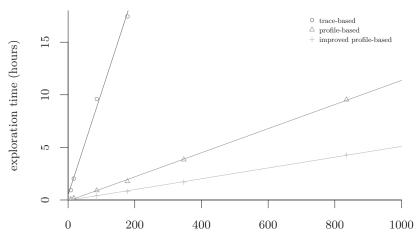

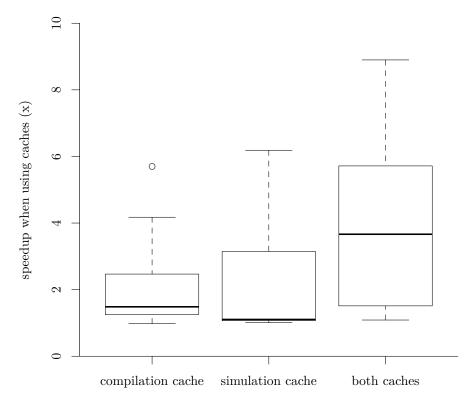

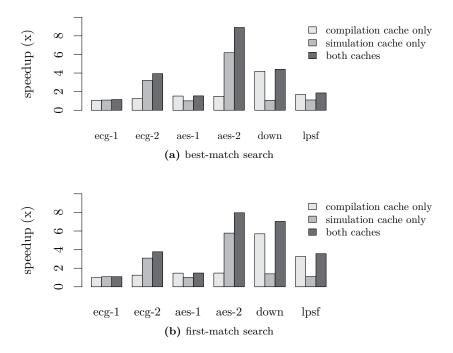

- An architecture exploration framework called BuildMaster, which simplifies the implementation of our architecture refinement exploration strategies. This framework automatically detects when compilation and simulation results obtained for previously considered candidates can be re-used for the evaluation of newly proposed candidate architectures. This intermediate result caching system allows us, for example, to avoid on average over 90% of the originally required simulation time by re-using previously obtained profile information for the energy estimation.

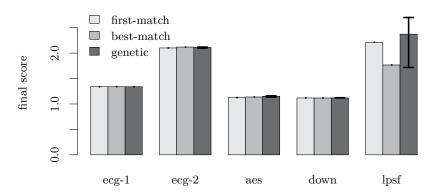

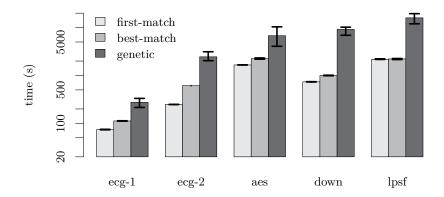

- A set of exploration strategies which effectively refine the processor architecture and a comparison between these strategies on both the quality of the obtained result, as well as, the required exploration time. We show that the proposed exploration heuristics find results whose quality is comparable to the results found using a genetic algorithm while requiring an order of magnitude less exploration time.

Combining the presented techniques results in a highly efficient and extensible instruction-set architecture exploration methodology. In our experiments we show that our framework is able to explore hundreds of processor architecture variations per hour while consistently producing compact results that meet the expected performance.

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                                           | <b>1</b> |

|----------|-----------------|--------------------------------------------------------------------|----------|

|          | 1.1             | Parallelism in processor architectures                             | 3        |

|          |                 | 1.1.1 Different kinds of parallelism                               | 4        |

|          |                 | 1.1.2 Real life examples                                           | 6        |

|          | 1.2             | Context of this work                                               | 7        |

|          | 1.3             | Problem statement                                                  | 9        |

|          | 1.4             | Contributions                                                      | 10       |

|          | 1.5             | Dissertation outline                                               | 12       |

| <b>2</b> | Rela            | ated work                                                          | 13       |

|          | 2.1             | Commercial EDA tools                                               | 15       |

|          |                 | 2.1.1 Cadence                                                      | 15       |

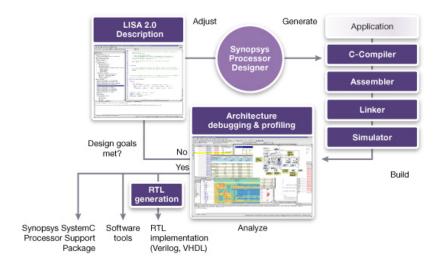

|          |                 | 2.1.2 Synopsys                                                     | 17       |

|          | 2.2             | Research projects                                                  | 19       |

|          |                 | 2.2.1 Architecture description languages                           | 19       |

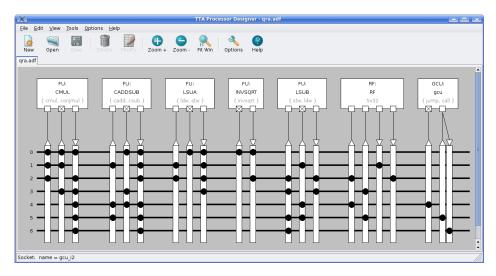

|          |                 | 2.2.2 TCE: TTA-based Co-design Environment                         | 20       |

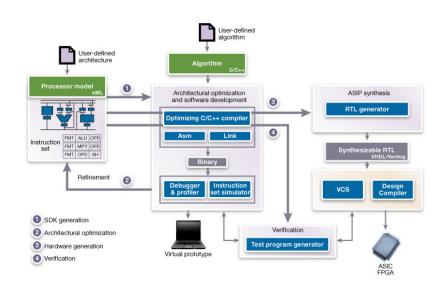

|          |                 | 2.2.3 PICO: Program-In Chip-Out                                    | 23       |

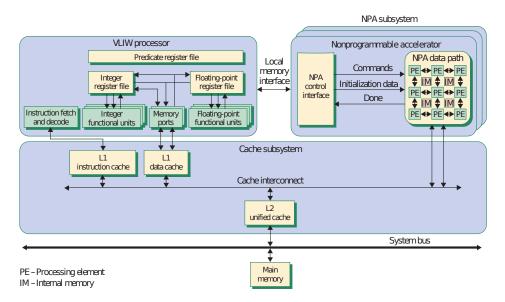

|          | 2.3             | The SiliconHive tools                                              | 27       |

|          |                 | 2.3.1 Overview                                                     | 27       |

|          |                 | 2.3.2 Architecture template                                        | 28       |

|          | 2.4             | Compiler support                                                   | 32       |

|          |                 | 2.4.1 Source code annotation                                       | 32       |

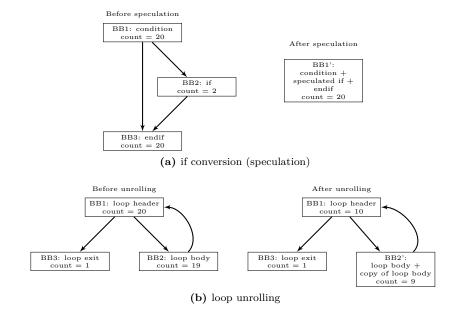

|          |                 | 2.4.2 Code transformations                                         | 34       |

|          |                 | 2.4.3 Extensions for architecture exploration                      | 35       |

|          | 2.5             | Conclusion                                                         | 36       |

| 3        | VLI             | W processor design in the ASAM project                             | 37       |

|          | 3.1             | Overview                                                           | 39       |

|          |                 | 3.1.1 Macro- and micro-architecture exploration                    | 39       |

|          | 3.2             | ASIP architecture exploration: An example                          | 41       |

|          |                 | 3.2.1 Application code restructuring and initial architecture con- |          |

|          |                 | struction                                                          | 43       |

|          |                 | 3.2.2 ASIP instruction-set synthesis through architecture refine-  |          |

|          |                 | ment                                                               | 49       |

|   | 3.3  | Conclusion                                                                                                                                                        |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Ear  | y performance estimation 5'                                                                                                                                       |

|   | 4.1  | Parallelism estimation of straight-line code                                                                                                                      |

|   |      | 4.1.1 Methods                                                                                                                                                     |

|   |      | 4.1.2 Experimental results                                                                                                                                        |

|   |      | 4.1.3 Conclusion on parallelism estimation                                                                                                                        |

|   | 4.2  | VLIW issue-width optimization                                                                                                                                     |

|   |      | 4.2.1 Possible search strategies                                                                                                                                  |

|   |      | 4.2.2 Experimental results $\ldots \ldots \ldots$ |

|   |      | 4.2.3 Conclusion on the issue-width optimization                                                                                                                  |

|   | 4.3  | Parallelism estimation of pipelined loops                                                                                                                         |

|   |      | 4.3.1 Determining the minimum initiation interval                                                                                                                 |

|   |      | 4.3.2 Methods                                                                                                                                                     |

|   |      | 4.3.3 Experimental results                                                                                                                                        |

|   | 4.4  | Conclusion                                                                                                                                                        |

| 5 | Are  | a and energy modeling 7'                                                                                                                                          |

|   | 5.1  | Estimating area and energy 74                                                                                                                                     |

|   |      | 5.1.1 Issue-slots and operations                                                                                                                                  |

|   |      | 5.1.2 Register files and memory-like interfaces                                                                                                                   |

|   |      | 5.1.3 Interconnect                                                                                                                                                |

|   |      | 5.1.4 Miscellaneous                                                                                                                                               |

|   |      | 5.1.5 Model calibration                                                                                                                                           |

|   | 5.2  | Activity estimation                                                                                                                                               |

|   |      | 5.2.1 Trace-based energy estimation                                                                                                                               |

|   |      | 5.2.2 Profile-based energy estimation                                                                                                                             |

|   |      | 5.2.3 Improved profile-based energy estimation                                                                                                                    |

|   |      | 5.2.4 Further improvements                                                                                                                                        |

|   | 5.3  | Initial experiments                                                                                                                                               |

|   | 5.4  | Conclusion                                                                                                                                                        |

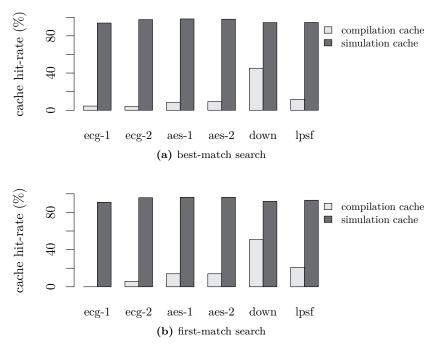

| 6 | Inte | rmediate result caching 93                                                                                                                                        |

|   | 6.1  | The simulation cache                                                                                                                                              |

|   | 6.2  | The compilation cache                                                                                                                                             |

|   | 6.3  | Experiments                                                                                                                                                       |

|   |      | 6.3.1 Exploration time speedup                                                                                                                                    |

|   |      | 6.3.2 Cache hit-rates                                                                                                                                             |

|   |      | 6.3.3 Caching induced exploration path divergence 9                                                                                                               |

|   | 6.4  | Conclusion                                                                                                                                                        |

|   |      |                                                                                                                                                                   |

| <b>7</b> | Aut   | omated design space exploration 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 03  |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | 7.1   | Exploration method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104 |

|          |       | 7.1.1 Growing versus shrinking strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105 |

|          |       | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 106 |

|          |       | 7.1.3 Exploration algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107 |

|          | 7.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

|          | 7.3   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110 |

|          |       | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110 |

|          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 111 |

|          |       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112 |

|          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 112 |

|          | 7.4   | I · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113 |

|          |       | 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

|          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 116 |

|          |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117 |

|          | 7.5   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 119 |

| 8        | Con   | clusions and future work 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21  |

|          | 8.1   | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|          | 8.2   | Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Bi       | bliog | graphy 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29  |

| Α        | ASI   | P construction and exploration tools 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37  |

|          | A.1   | Processor architecture construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 137 |

|          |       | A.1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 138 |

|          |       | A.1.2 Installation and usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 138 |

|          |       | A.1.3 XML input specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 138 |

|          |       | A.1.4 Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 139 |

|          | A.2   | Design-space exploration tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 139 |

|          |       | A.2.1 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 141 |

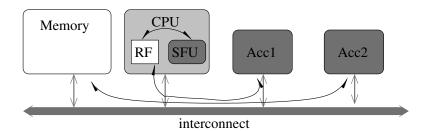

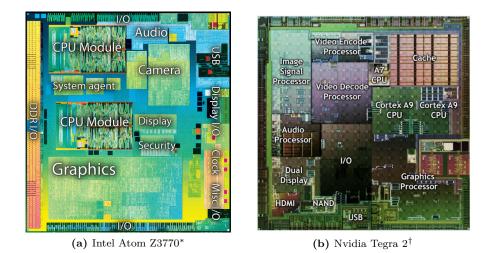

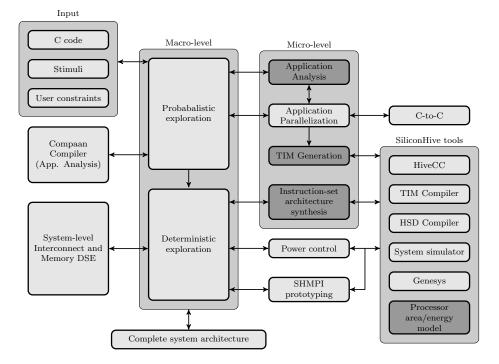

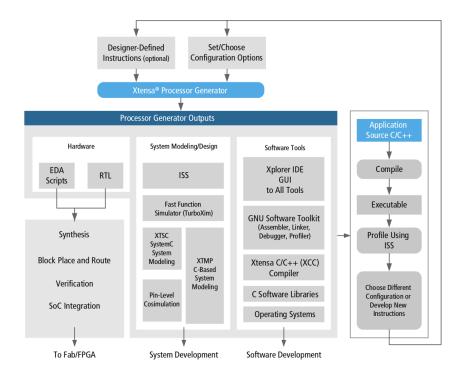

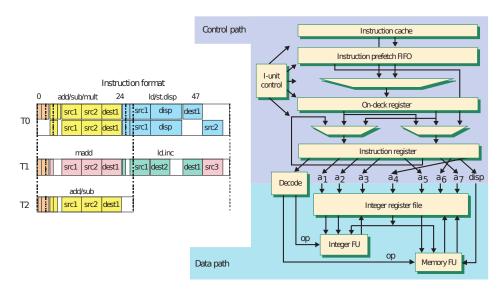

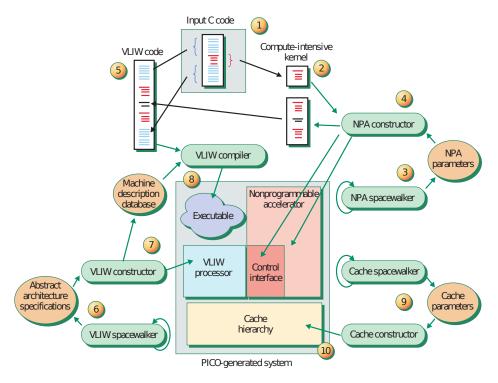

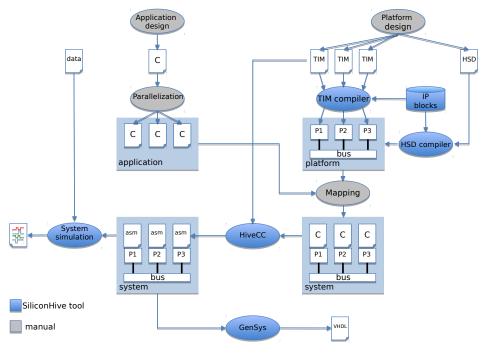

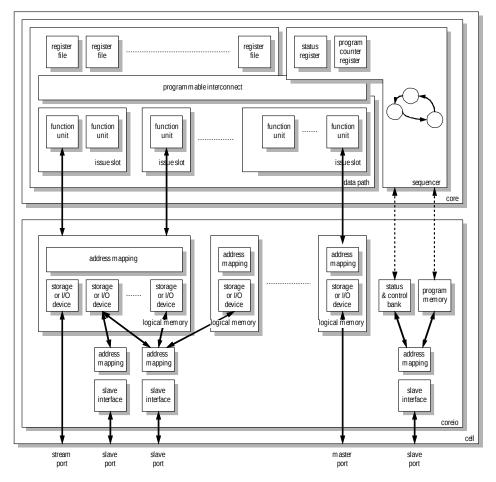

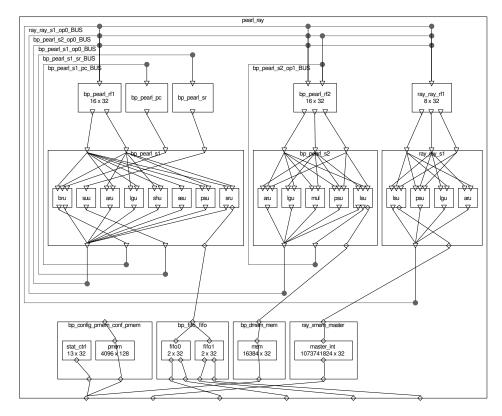

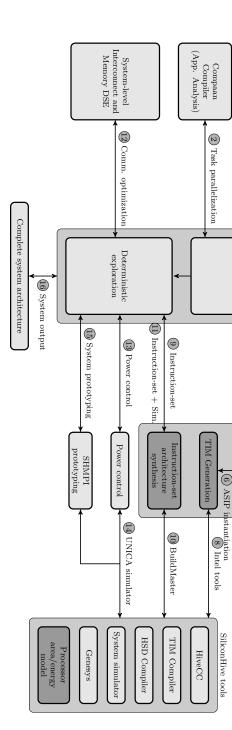

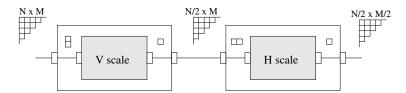

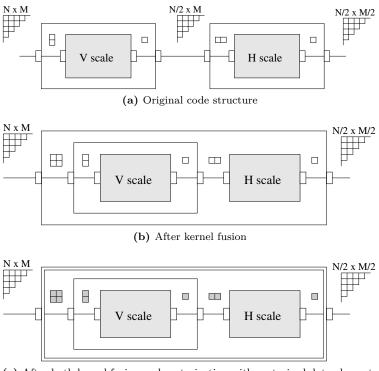

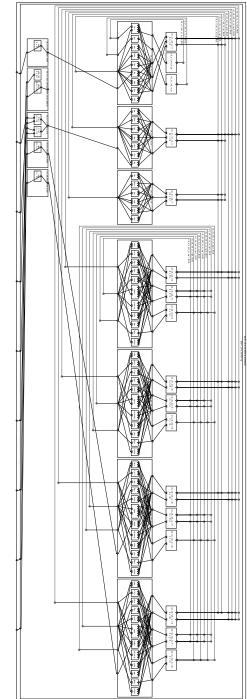

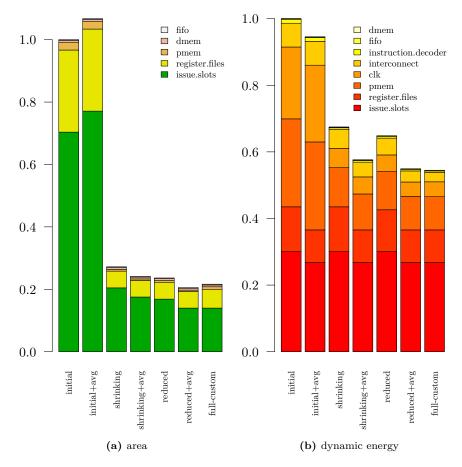

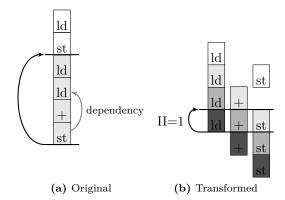

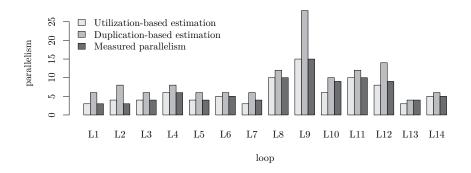

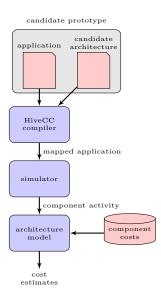

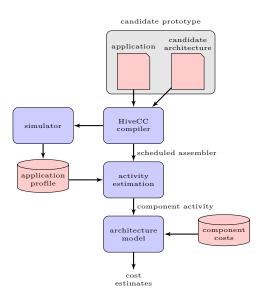

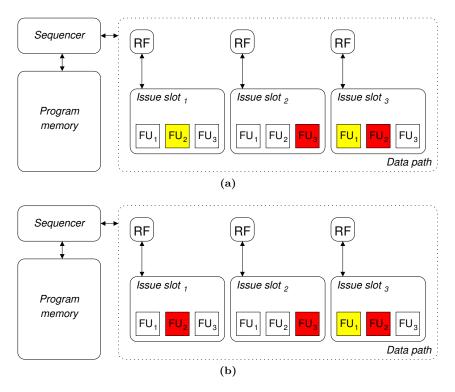

|          |       | A.2.2 Initial prototype preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 141 |