## The predictor-adaptor paradigm: automation of custom layout by flexible design

Citation for published version (APA):

Ginneken, van, L. P. P. P. (1989). The predictor-adaptor paradigm: automation of custom layout by flexible design. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR303176

DOI:

10.6100/IR303176

Document status and date:

Published: 01/01/1989

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 17. Nov. 2023

# The Predictor - Adaptor Paradigm

Automation of Custom Layout by Flexible Design

Lukas P.P.P. van Ginneken

# The Predictor - Adaptor Paradigm

Automation of Custom Layout by Flexible Design

Dit proefschrift is goedgekeurd door de promotoren

Prof.dr.-ing. J.A.G. Jess en Prof.dr.ir. R.H.J.M. Otten

© Copyright 1989 Lukas P.P.P. van Ginneken All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Druk: Dissertatiedrukkerij Wibro, Helmond

#### CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Ginneken, Lukas Paul Pieter Pepijn van

The predictor-adaptor paradigm: automation of custom layout by flexible design / Lukas Paul Pieter Pepijn van Ginneken. - [S.l.:s.n.]. - Fig., tab. Proefschrift Eindhoven. - Met lit.opg., reg., index. ISBN 90-9002703-3 SISO 663.43 UDC 621.382:681.3.06 NUGI 832 Trefw.: geïntegreerde schakelingen; computer aided design / algorithmen.

# The Predictor - Adaptor Paradigm

Automation of Custom Layout by Flexible Design

#### **PROEFSCHRIFT**

Ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof. ir. M. Tels, voor een commissie aangewezen door het college van dekanen in het openbaar te verdedigen op dinsdag 11 April 1989 om 16.00 uur

door

Lukas Paul Pieter Pepijn van Ginneken geboren te Tilburg

### **Contents**

| Abst  | rac  | t.   | •    | •    | •    | •          | •    | •    |      | •    | •   | •   | • |   | • |   | • |   | • | • | 6  |

|-------|------|------|------|------|------|------------|------|------|------|------|-----|-----|---|---|---|---|---|---|---|---|----|

| Sam   | env  | /att | ing  |      |      | •          |      |      |      |      |     |     |   | • | • | • |   |   |   |   | 8  |

| Prefa | ace  |      |      |      | •    |            |      | •    |      |      | •   | •   |   |   |   | • |   |   |   |   | 10 |

| 1. T  | he   | pre  | dict | or-  | ada  | apt        | or   | pai  | ad   | ign  | ı   |     |   |   |   |   |   |   |   |   | 14 |

| 1.    | .1   | Des  | ign  | th   | eor  | <b>y</b> 0 | fcc  | m    | olex | c sy | yst | ema | 3 |   |   |   |   |   |   |   | 15 |

| 1.    | .2   | Ste  | owi  | se : | refi | ne         | me   | nt   |      |      |     |     |   |   |   |   |   |   |   |   | 18 |

|       |      | Des  |      |      |      |            |      |      |      |      |     |     |   |   |   |   |   |   |   |   | 21 |

|       |      | Joir |      |      |      |            |      |      |      |      |     |     |   |   |   |   |   |   |   |   | 24 |

|       |      | Exa  | _    |      |      |            | _    |      |      |      |     |     |   |   |   |   |   |   |   |   | 28 |

| 2. B  | uil  | din  | g bl | ock  | la   | you        | ıt   |      |      |      |     |     |   |   |   |   |   |   |   |   | 32 |

| 2.    | .1   | Floc | r p  | lar  | mii  | ng         |      |      |      | •    |     |     |   |   |   |   |   |   |   |   | 34 |

| 2.    | .2 ' | The  | poi  | nt   | coi  | nfig       | ur   | atio | n    |      |     |     |   |   |   |   |   |   |   |   | 36 |

| 2.    | .3   | Cha  | nne  | el a | ıssi | gn         | me   | nt   |      |      |     |     |   |   |   |   |   |   |   |   | 38 |

| 2.    | .4 ' | The  | int  | erf  | ace  | 8          |      |      |      |      |     |     |   |   |   |   |   |   |   |   | 40 |

|       |      | Mas  |      |      |      |            |      |      |      |      |     |     |   |   |   |   |   |   |   |   | 42 |

| 3. Jo | oin  | t sh | ape  | or   | tin  | niz        | atio | on   |      |      |     |     |   |   |   |   |   |   |   |   | 50 |

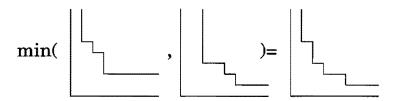

| 3.    | .1   | Sha  | pe i | fun  | cti  | ons        | ;    |      |      |      |     |     |   |   |   |   |   |   |   |   | 51 |

| 3.    | .2   | Opt  | imi  | zat  | ion  | of         | a 8  | slic | ing  | flo  | or  | pla | n |   |   |   |   |   |   |   | 56 |

|       |      | Opt  |      |      |      |            |      |      |      |      |     |     |   |   |   |   |   |   |   |   | 58 |

| 3.    | 4    | Effi | cier | су   | of   | the        | sli  | icir | ıg a | lgo  | rit | hm  | ì |   |   |   | • | • | • |   | 63 |

| 4. A  | st.e | ine  | r tr | ee   | hei  | uris       | stic | •    | _    |      | _   | _   |   | _ | _ |   | _ |   |   |   | 68 |

Contents 5

|    | 4.1  | The shortest steiner tree proble  | m | in | gra | iph | s |   |   |    |     |   | 68  |  |  |

|----|------|-----------------------------------|---|----|-----|-----|---|---|---|----|-----|---|-----|--|--|

|    | 4.2  | The topology of the steiner tree  |   |    |     |     |   |   |   |    |     |   | 71  |  |  |

|    | 4.3  | Applying the paradigm             | ı |    |     |     |   |   |   |    |     |   | 75  |  |  |

|    | 4.4  | An efficient implementation .     |   |    | *   |     |   |   |   |    |     |   | 77  |  |  |

| 5. | Two  | o-dimensional folding             |   |    |     |     |   |   |   |    |     |   | 82  |  |  |

|    |      | The folding problem               |   |    |     |     |   |   |   |    |     |   | 82  |  |  |

|    |      | The hierarchical folding algorith |   |    |     |     |   |   |   |    |     |   | 88  |  |  |

|    |      | Partitioning the groups           |   |    |     |     |   |   |   |    |     |   | 88  |  |  |

|    |      | Performance improvements .        |   |    |     |     |   |   |   |    |     |   | 90  |  |  |

|    |      | Some practical experiences        |   |    |     |     |   |   |   |    |     |   | 92  |  |  |

|    | Lay  | Layout of unidimensional modules  |   |    |     |     |   |   |   |    |     |   |     |  |  |

|    |      | The wire plan                     |   |    |     |     |   |   |   |    |     |   | 96  |  |  |

|    |      | Transistor matrix layout          |   |    |     |     |   |   |   |    |     |   | 99  |  |  |

|    |      | Parameterized transistors         |   |    |     |     |   |   |   |    |     |   | 100 |  |  |

|    | 6.4  | Track assignment                  |   |    |     |     |   |   |   |    |     |   | 103 |  |  |

|    | 6.5  | Nor matrix layout                 |   |    |     |     |   |   |   |    |     |   | 100 |  |  |

|    | 6.6  | The power and ground rails .      | , |    |     |     |   |   |   | ٠. |     |   | 108 |  |  |

|    |      | A comparison of automatic layor   |   |    |     |     |   |   |   |    |     |   | 110 |  |  |

| 7. | Sha  | hape control and prediction       |   |    |     |     |   |   |   |    |     |   |     |  |  |

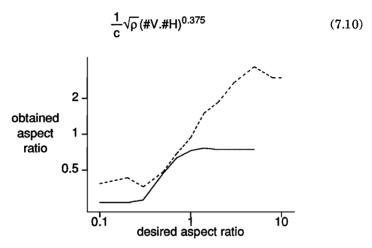

|    | 7.1  | Shape control                     |   |    |     |     | • | • | - | •  | •   | • | 114 |  |  |

|    |      | Shape function prediction         |   |    |     |     |   |   |   |    |     | • | 119 |  |  |

| ,  |      | Partitioning before folding       |   |    |     |     |   |   |   |    |     | - | 121 |  |  |

|    |      |                                   |   |    |     |     |   |   |   |    |     |   |     |  |  |

| 8. |      | cussion                           |   |    |     |     |   |   |   |    |     |   | 124 |  |  |

|    |      | The predictor-adaptor paradigm    |   |    |     |     |   |   |   |    |     |   | 124 |  |  |

|    |      | Architecture of a design package  |   |    |     |     |   |   |   |    |     |   | 130 |  |  |

|    |      | Further research                  |   |    |     |     |   |   |   |    |     |   | 132 |  |  |

|    | 8.4  | Conclusions                       |   | •  | ٠   | •   |   | • | • | •  | • . | • | 135 |  |  |

| Re | fere | nces                              |   |    |     |     |   |   |   |    |     |   | 136 |  |  |

| In | dex  |                                   |   |    |     |     |   |   |   |    |     |   | 144 |  |  |

| No | tati | ons                               |   | •  |     |     |   |   |   |    |     |   | 150 |  |  |

| n: |      | _1_                               |   |    |     |     |   |   |   |    |     |   | 187 |  |  |

#### **Abstract**

This book is about the automation of the design of masks for custom integrated circuits. The predictor-adaptor paradigm is the general pattern of collecting information followed by taking design decisions. This pattern is the result of top-down design or design by stepwise refinement. The book explains how this general paradigm can be applied to design problems of custom IC's. Several algorithms are given.

The blocks in a floor plan are designed according to parameters. First the freedom of these parameters must be determined by the predictor. Then the important design decisions can be taken. Taking the global design decisions has been called floor planning. The parameters are then determined and the blocks are adapted to their environment.

A new polynomial algorithm for the optimal slicing of point configurations is presented. Given the shape functions of the blocks and a point configuration, the algorithm finds the slicing structure that has the smallest total area. Although there are an exponential number of possible slicing structures, the number of possible slices is polynomial. This makes a dynamic programming approach feasible. The complexity of the algorithm is  $O(n^6)$  where n is the number of blocks. The dimensions of the blocks must be expressed as small integers.

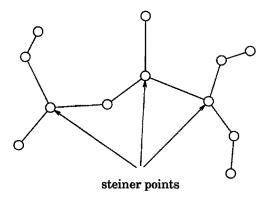

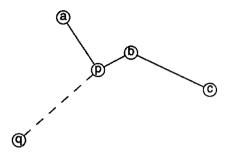

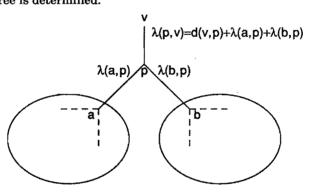

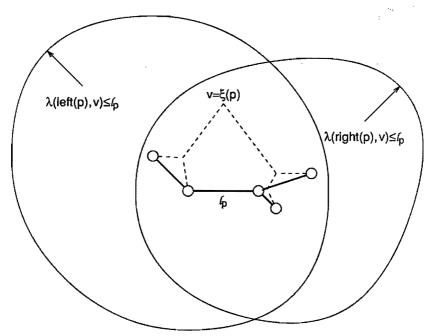

A heuristic for the shortest steiner tree problem is presented. The heuristic starts with a shortest spanning tree from which the topology is derived. The optimal positions of this topology can then be determined using a polynomial algorithm. This algorithm first determines the freedom to choose steiner points. Then the points are chosen in a top-down order.

Abstract 7

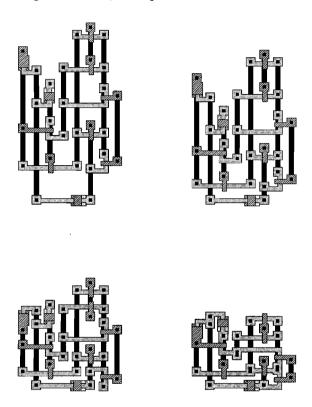

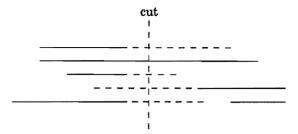

An algorithm is presented is for the unconstrained two-dimensional folding problem. In this problem horizontal and vertical strips must be assigned to rows and columns. Strips in the same row or column should not overlap, while the connection pattern of the strips must be realized. The algorithm uses an elegant hierarchical divide and conquer technique to gradually refine the folding. Each refinement step consists of partitioning a group of strips. A cutting line separates the groups of strips in horizontal or vertical direction.

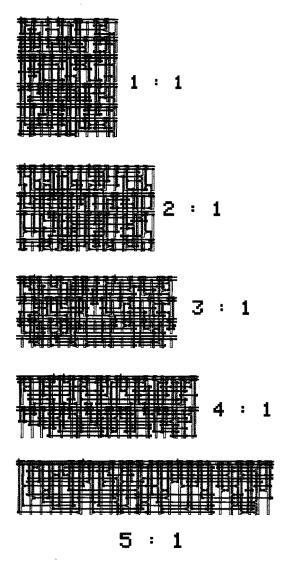

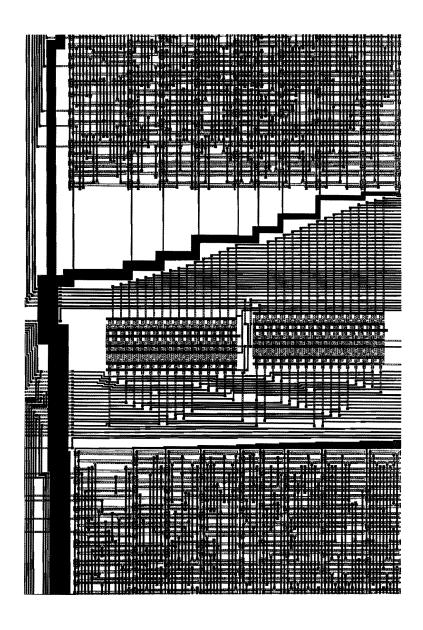

Two new layout styles based on this algorithm are presented. They are called 'nor matrix layout' and 'transistor matrix layout'. The nor matrix style is similar to the weinberger array. The nor matrix consists of multilevel nor gates. Several rows of pull-ups are used to allow for folding in both dimensions. The transistor matrix style can handle any circuit of transistors. The W/L ratio of each transistor can be specified. Although the implementation handles only nMOS circuits, an extension to CMOS is straightforward.

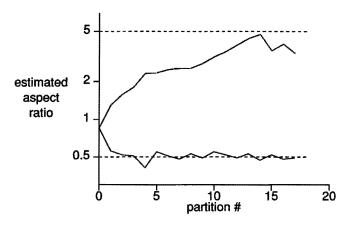

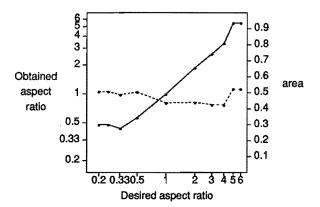

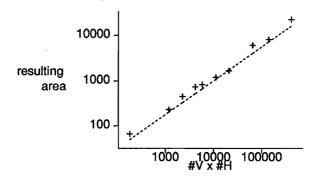

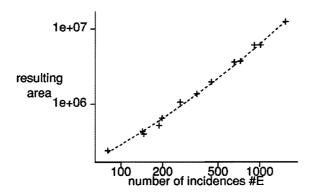

The folding algorithm allows for easy adaptation of the pin positions and the shape. This is important in combination with floor planning. It is shown that the area of the blocks can be accurately predicted and the aspect ratio can be accurately controlled. The orientation of the cutting line influences the aspect ratio. The new layout styles give much smaller layouts than conventional layout styles.

Using the flexibility of the sub-designs design problems can be solved more easily. Specialized sub-designs allow the design to be more critical.

#### Samenvatting

Dit proefschrift gaat over het ontwerpen van geïntegreerde schakelingen, ook wel *chips*. Het einddoel van het ontwerpen bestaat uit een aantal maskers, die met fotografische en scheikundige processen worden afgebeeld op het silicium. Omdat deze maskers erg ingewikkeld kunnen zijn willen we het ontwerpen hiervan zoveel mogelijk automatiseren. Dit spaart tijd en verminderd het aantal fouten. Ook moeten we de ontwerpmethode zeer precies beschrijven om hem door een computer te kunnen laten uitvoeren. Een methode die geschikt is voor een computer wordt een algoritme genoemd.

Het ontwerpen is vooral moeilijk omdat de schakelingen erg groot zijn. Daarom wordt het ontwerp gesplitst in een aantal deelontwerpen. Ieder van die deelontwerpen wordt ook weer gesplitst tot de delen wel hanteerbaar zijn.

Tijdens het ontwerpen van een chip moet er een groot aantal beslissingen worden genomen. Sommige beslissingen hebben een grote invloed op het resultaat, andere een kleinere. Beslissen welke schakelingen links op de chip worden geplaatst en welke rechts heeft veel meer invloed dan het trekken van een enkel draadje. Omdat de grote beslissingen veel meer invloed hebben willen we die het eerst nemen. De kleinere beslissingen kunnen we dan aanpassen aan de grotere.

De titel slaat op het algemene patroon dat we gebruiken in onze ontwerpmethoden. Dat patroon bestaat uit het voorspellen van de eigenschappen van nog niet ontworpen deelontwerpen, en dan het aanpassen van die deelontwerpen aan elkaar en aan de eerdere beslissingen. In dit proefschrift wordt dit patroon toegepast op een aantal problemen die we tegenkomen bij het ontwerpen van chips.

De ruimte op de chip wordt verdeeld in rechthoekige stukken, de blokken. Een deelontwerp kan bestaan uit een blok, maar afhankelijk van het probleem ook uit een groepje blokken of een stuk van een blok. Het kan ook een stuk van een draadje zijn.

Voor een aantal problemen worden in dit proefschrift nieuwe methoden beschreven. Dit zijn het verdelen van de ruimte in blokken, het trekken van draadies tussen de blokken en het ontwerpen van de blokken zelf.

Het verdelen in blokken wordt behandeld in hoofdstuk 3. Ieder blok heeft een aantal mogelijke vormen, die worden weergegeven door een vorm functie. Eerst krijgen alle blokken een punt op de chip. Deze puntenwolk wordt daarna doorsneden met rechte lijnen, de *slicing* lijnen. Het nieuwe algoritme kiest deze lijnen zo dat de chip zo klein mogelijk wordt. Het vindt altijd de beste oplossing. Het is ook redelijk snel: de tijd die nodig is is kleiner dan a.n<sup>6</sup>+b, waarbij n het aantal blokken is, en a en b constanten zijn.

Het trekken van de draadjes wordt behandeld in hoofdstuk 4. Dit ontwerpprobleem is bekend als het steiner probleem in grafen. Het algoritme dat wordt gegeven vindt niet altijd de beste oplossing, maar het is wel snel.

De blokken zelf kunnen worden ontworpen met een methode die 'vouwen' wordt genoemd. Een blok is bijvoorbeeld opgebouwd uit draadjes en transistoren. Voor de draadjes worden lange dunne verticale strips gebruikt. De transistoren zijn ook lang en dun, en lopen horizontaal. Het vouwalgoritme kent draadjes aan kolommen toe, en transistoren aan rijen. Het algoritme probeert zoveel mogelijk draadjes in dezelfde kolom of dezelfde rij te stoppen en ook zoveel mogelijk transistoren in dezelfde rij. Natuurlijk mogen ze niet overlappen en moeten de juiste aansluitingen worden gemaakt. Door meer in de ene of in de andere richting te vouwen kunnen we de vorm van het blok aanpassen aan zijn buren.

Door het gebruiken van de flexibiliteit van de deelontwerpen kunnen we veel ontwerpproblemen gemakkelijker oplossen. Door deelontwerpen aan te passen wordt het hele ontwerp beter.

The first time I met Ralph Otten was September 1982 when I was doing an assignment for him as an undergraduate student at Eindhoven University. The assignment was to make a channel router that used simulated annealing. These two subjects, simulated annealing and layout design, have dominated the research we did in the following years. Later we used simulated annealing for floor planning, but after that the two subjects were investigated independently. Both have lead to a number of publications over the years. Our simulated annealing research has lead to a book called "The Annealing Algorithm" [53] that is to appear shortly.

This thesis was the result of the work I did on layout design. It is about top-down layout design by stepwise refinement. The predictor-adaptor paradigm refers to the general pattern of first collecting information and then taking decisions. The predicted design freedom is used to adapt sub-designs to the global specifications.

Of course, many researchers have pointed out the advantages of a topdown approach to layout design. In this book, however, this principle has been applied more universally; it has been applied to many sub problems as well as to the global chip layout problem. The work presented here is an application and extension of the ideas of Ralph Otten on automatic floor planning to all aspects of layout design. He explained his ideas in several papers, among others the paper called 'Stepwise Layout Refinement' [79]. In this book these ideas were also applied to several problems that arise in the design of the sub circuits of a floor plan.

The major contribution of this book is the consistent application of stepwise refinement to many aspects of the automatic layout design of integrated circuits. It features a new algorithm for the Steiner tree problem in graphs and a new algorithm for optimal slicing of point configurations. The hierarchical folding algorithm was due to Jos van Eijndhoven. Using this algorithm some new layout styles have been developed. The transistor matrix style applies principles of stepwise refinement to the design of the smallest possible circuits: the transistors.

The book consists of eight chapters, which each, except for the first and last one, describe an application of stepwise refinement. Since the reader may be interested in only one of the algorithms, each chapter is more or less independent. As a whole, the book forms a consistent application of stepwise refinement to layout design. The book describes solutions to most problems arising in the design of custom layouts for integrated circuits.

In chapters 2-4 the conventional method is described in which the circuits occupy two dimensional rectangular areas. Chapters 5-7 assume unidimensional circuits, in an entirely new approach to matrix style layout.

The first chapter looks at layout design from an abstract point of view. This chapter explains the philosophy of this book in terms of adaptive design using flexible parameterized circuit generators. This is the background against which the rest of the chapters should be seen.

The second chapter describes the usual floor planning - circuit design - routing approach to building block layout. It serves as the framework into which the algorithms in the next two chapters fit.

In chapter 3 the aspect ratio trade-off of the circuits in a floor plan is addressed. An algorithm for slicing of point configurations is presented. This algorithm finds the slicing structure with the smallest possible area in polynomial time.

Chapter 4 describes a heuristic for the steiner tree problem. In this heuristic the steiner tree is viewed as a hierarchy tree. In this tree the positions of the steiner points can be chosen optimally and polynomially in a top-down sequence.

The next three chapters, 5-7 describe a less conventional top-down approach to layout design. In this approach the circuits are not blocks

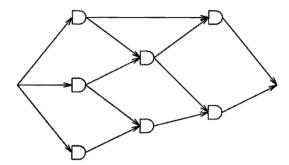

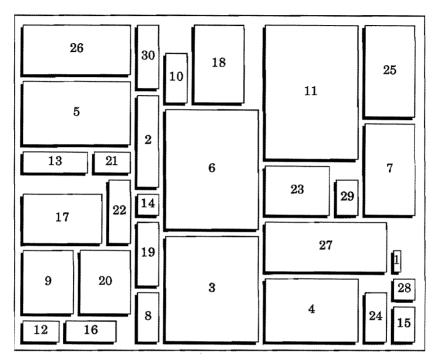

Figure 3.1. The organization of the chapters in this book. Chapters 2 and 6 describe two different approaches to structured layout by stepwise refinement. Chapters 3, 4, 5 and 7 describe specific sub problems. Chapter 1 gives an introduction and 8 gives a review of the methods used.

but unidimensional transistors or gates. The layout problem is formulated as an unconstrained folding problem. In chapter 5 the folding problem is solved by a stepwise refinement heuristic.

Chapter 6 describes two new layout styles that use this folding algorithm. One is a variation on the weinberger array style, the other is called 'transistor matrix layout'. In transistor matrix layout the adaptable circuits are the smallest possible circuits: single transistors.

Chapter 7 describes the shape adaptation of these transistor matrices. Also an prediction is made of their shape function for the floor planner. Some comparisons with conventional layout styles show the very small areas that these new circuit styles need.

The last chapter, chapter 8, a review is given of the algorithms and how they are consistent with the principles. We also look the requirements for a complete layout design package. Some possible areas of further research are indicated.

Finally, I would like to mention those who contributed to this work. I'm grateful to Jochen Jess and Bob Brayton for the opportunity to work in their research groups. My advisors, Jochen Jess and Ralph Otten did the proofreading of the thesis. Jos van Eijndhoven came up with the idea for the folding algorithm just when the need for such an

algorithm arose. I would also like to mention the students who developed parts of the package: Paul van Teeffelen, Gert-Jan van Lieshout, Tony Brans, Jos Brouwers and Theo Deckers. My work was supported financially by the foundation FOM under project number EEL 36.0417 and IBM.

I'm especially indebted to Ralph Otten for his continuous support of my work. Our numerous discussions have been major source of inspiration to me. Without his efforts and his insight this book would not have been possible.

Lukas P.P.P. van Ginneken Eindhoven, January 6, 1989

#### 1. The predictor-adaptor paradigm

In this chapter we will introduce the predictor-adaptor paradigm as an approach to hierarchical design. First we will look at the complexity of design methods and at hierarchy as a means to deal with this complexity.

Then we will introduce the stepwise refinement as a strategy aimed at global optimality. Global optimality is facilitated by taking the first design decisions at a high level. Subsequently, the design is further developed by taking design decisions at the lower levels. Hence the names 'top-down design' or 'stepwise refinement'.

The design decisions must be based on some information. Since the sub-designs have not yet been designed, their properties must be predicted. The *predictor* derives the global design freedom from the properties of the sub-designs. The *adaptor* then adapts the sub-designs to the global design specifications.

The sub-designs are designed according to parameters that have been determined by the top level decisions and the global specifications. These parameters should preferably be optimized simultaneously.

Finally, an example algorithm will be presented that incorporates many principles of the predictor-adaptor paradigm in a simple and concrete manner.

#### 1.1 Design theory of complex systems

When we study the process of design, we study the design methods. For developing a theory of design, we would like to describe these methods formally. A formally described method is an algorithm. When such an algorithm is formulated in an algorithmic language, we speak of a program.

In this book we will study formal design methods for integrated electronic circuits. These design methods formulated in an algorithmic language are software. In short, we will study software to design hardware. In this book the design problem will be limited to the design of the layout of an integrated circuit.

The practical limits to the design of hardware and software systems are set by the complexity of the systems, and our ability to deal with this complexity. Much of theory of the design of hardware and software systems is the theory of the design of complex systems.

The time complexity of an algorithm describes how the time needed to execute the algorithm grows asymptotically with the size of the problem. The size of a problem can be measured as the number of bits to describe a problem instance. Suppose we need n bits to describe the problem instance, and the time needed to execute the algorithm is at most t(n) seconds. If there are two constants a and b such that  $t(n) \le a.f(n)+b$  for all n then the complexity of the algorithm is said to be O(f(n)). Mostly the simplest function which is a sharp bound for large n is taken for f(n). If f(n) can be expressed as  $n^k$  then the algorithm is called polynomial. If this is not possible, the algorithm is called exponential [26]. Many of the combinatorial problems posed in this book cannot be solved by a polynomial algorithm.

There is a large class of problems, called the *NP-complete* problems [26]. These problems are formulated as decision problems, for instance: is there a solution with a score better then a given k? It is generally believed that no algorithm exists that can solve these problems in polynomial time, but so far no one has been able to prove or disprove that. The related optimization problems (what is the best solution?) are in the class of *NP-hard* problems.

To reduce the complexity of the algorithms several methods have been devised. Perhaps the most general method to cope with any kind of complexity, is the use of hierarchy [61,54,83]. A hierarchy is a

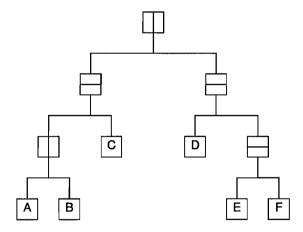

recursive tree structure of modules within modules: A module M is a set of modules  $M=\{m_1,m_2,\cdots,m_{\#M}\}$ . The modules  $m_i$  are the submodules of M. Each sub-module may be decomposed itself. Decomposed modules are called compound modules. Primitive modules are modules without sub-modules. M is the super module of  $m_i$ . There is exactly one module without a super module called the root module.

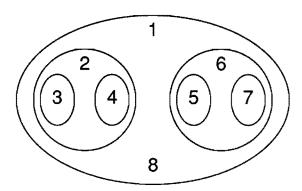

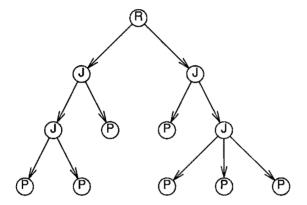

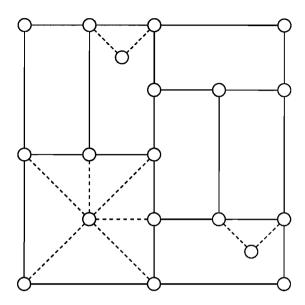

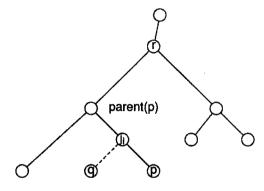

Figure 1.1. A hierarchy of modules. R = root module, J = compound module, P = primitive module.

The hierarchy can be represented as a rooted tree. The modules are represented by the nodes: the root represents the system, the leaves of the tree represent the primitive modules and the internal nodes represent the compound modules. The arcs point from each module to its sub-modules.

The complexity of the design problem can be reduced by representing the design as a hierarchy. The design problem is decomposed into sub designs, called modules. The root module represents the whole design. In stead of solving the entire design problem at once, the design problem is solved in steps. In each step a sub-problem is solved. In algorithms this principle is known as 'divide and conquer' [4].

An example of a hierarchy is the decomposition of an electronic circuit into sub-circuits. The circuits  $C=\{c_1,c_2,\cdots\}$  are the modules of the hierarchy. The circuits are connected by nets. A *net list* is a bipartite graph  $\mathcal{N}(C\cup\{C\},N,P)$ , in which N is the set of *nets* and  $P\subset(C\cup\{C\})\times N$  is the set of *pins*. The pins are the edges between the circuit and the nets.

The pins  $P \cap \{C\} \times N$  are the pins of circuit C itself, that is, the pins to the outside. In this book we will assume that the design is given as a hierarchy of circuits to the layout algorithms. The primitive circuits are the circuit elements like transistors and resistors. Note that they are the simplest indivisible circuits since they cannot be represented by a net list.

Hierarchy can help to reduce the complexity, by restricting the view to the immediate sub-modules. When looking at a compound module, we are in fact looking at all the leaf nodes in the sub-tree. However, in stead of looking at the leaf nodes and their interactions directly, we look at a *model* of this sub-tree. We look at the compound module as a 'black box' of which we can see only its outside shape, but not its internal structure. Such a model is the *interface* of the module to its super module.

The use of hierarchy can have advantages other than the decrease in complexity by modeling compound modules. Some of the modules in the hierarchy may be identical. The design may be repeated, so the circuit needs to be designed only once. Sometimes this property is used to design an entire *library* of circuits, ready for use.

The design problems of the sub-modules become mutually independent when their inter-relations are explicitly known. The designs can therefore be done simultaneously: Several sub-modules may be designed in parallel. Finally, no single design method may be suitable for the entire design. A different design method can be used on different modules of the hierarchy.

There are two requirements for the hierarchy concept to work. First, the complexity is only reduced if the interface description of a compound module is simpler than a structural description of all the component modules together with their interrelations. Secondly, this interface description must be a sufficiently accurate model for the compound module.

Hierarchy is no panacea, nor is it always obvious how it should be used. Introducing hierarchy almost always means a longer algorithm. It is essential that the interfaces are chosen such that they form a good model, while they provide sufficient simplification. An oversimplification will lead to a 'short sighted' algorithm, while an exact and concise model may lead to a polynomial and optimal algorithm. The better models we have, the better is our 'understanding'

of the problem.

#### 1.2 Stepwise refinement

High level decisions are likely to have the most influence on the quality of the design. Therefore the high level decisions should be taken first, when the freedom to take decisions is still large. The first decisions can guide the lower level decisions towards global optimality. The design starts at the root node and progresses down the hierarchy. Hence the name top-down design. When the design starts with the leaf nodes, it is called bottom-up design.

Stepwise refinement has been widely advocated for the design of complex systems by human designers [47]. Its application to software development was first proposed by Niklaus Wirth in his paper Program development by stepwise refinement' [72]. Its application to automatic layout design was described in [64,79].

Before a module can be designed, some information is needed to base design decisions on. This can be done by preliminary designs, or by predictions derived from key parameters. The *predictor* is an algorithm that makes a such predictions. The information of the predictions can be propagated up the design hierarchy. Of course the quality of the high level decisions depends on the accuracy of the predictions.

The second phase is the top-down adaptor. During this phase important design decisions are taken. The first decisions are taken on a high level of the hierarchy. Therefore they will have a large influence on the whole design. The design is then refined, and the sub-modules adapted to the earlier design decisions. The decisions taken in the sub-modules have a smaller influence, and are guided by the decisions taken earlier. This way the design strategy is targeted towards global optimality.

The design decisions taken at a high level must be represented by an intermediate representation of the design. This intermediate representation is a *plan*. Examples of such plans are a floor plan, a wire plan or a data flow graph. A floor plan of a chip for instance spatially orders the circuits on the chip. It relates the shape and positions of the circuits to each other.

Another approach to design which uses hierarchy is bottom-up design. In bottom-up design, the modules that are lowest in the hierarchy are

designed first. These modules are then combined to create more complex modules, until the system design has been realized.

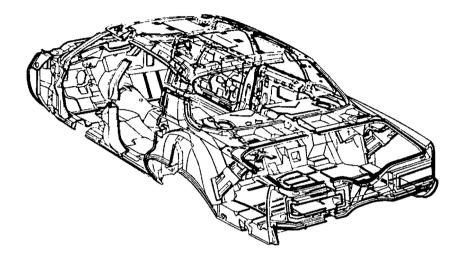

Figure 1.2. This car was designed top-down. The parts are especially designed for this particular car. This requires a lot of time and craftsmanship.

The most important advantage of bottom-up design is that the design of a module, ignoring environment information, is simpler. Only the function has to be specified. For an automatic design algorithm, this means a simpler interface. Also, the design is usually general enough to allow repeated usage. Furthermore, the sub-modules are exactly specified when designing a compound module. The design can be done using exact data, not just predictions.

The price to be paid however, is that the modules are unadapted. The more complex the modules are the more variation is possible. In the layout design of circuits, bottom-up design is often done up to a certain level, for instance the standard cell level. For each specific design top-down design is then used down to the standard cell level. This compromise is also known as a 'meet in the middle' design strategy.

Most design methods use such a compromise. The approach that is presented in this book however aims at a completely top-down design

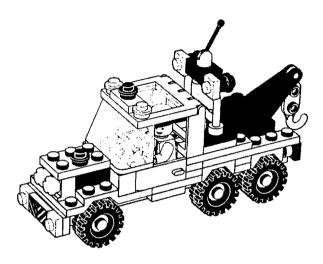

Figure 1.3. This car was designed bottom-up. The building blocks have been designed beforehand, and are not committed to a particular function. The quality of the car is poor, but the job can be done by a child.

flow down to the transistors. The transistors are the primitive circuits because they cannot be represented by a decomposition with a net list.

Top down design can also be looked at as postponing design decisions. It is important that sufficient information is available when taking a decision. Decisions reduce the freedom for further decisions. Taking decisions leads to a gradual stiffening of the design. Decisions should be based on reliable information, limit the freedom of further decisions as little as possible, and result in a maximal amount of new information.

In top-down design, design criteria can often be met by propagating the design criteria towards the sub-modules. The design criteria are merely translated to criteria for the sub-modules. In the sub modules, the problem of meeting these criteria must be solved. Of course, unless the sub-module is a primitive module, the design problem can be delayed further, and moved down the hierarchy again.

The decisions that are taken in a top-down design process are 'self fulfilling'. That is, for the modules that are finally used, the design that has been made with them is likely to be the best possible with these modules.

When the modules have not yet been designed, there is no good reason to assume rigid constraints on the freedom of the modules in advance. We may assume that the modules are completely flexible in all their parameters. Of course not every combination of parameters is possible: parameters can be traded against each other. But within certain bounds each parameter can take any value.

#### 1.3 Design parameters

For a top-down design method, the modules must be adaptable to their environment. The design decisions taken at a high level are presented to the designers of the sub-modules as *parameters*. Such parameters are used in the hierarchy of circuits and in other hierarchies yet to be introduced.

In the design of the layout of a circuit, the design decisions are translated to parameters for the design of the sub circuits. The parameters form the specifications of the circuit; they form the interface through which the circuit generators receive their information. For an electronic circuit on a chip we can distinguish the following important classes of parameters:

- 1. Function

- 2. Testability

- 3. Delay

- 4. Power consumption

- Technology

- 6. Design rules

- 7. Shape

- Pin positions

- 9. Design effort

With so many parameters, it becomes infeasible to maintain a library. Some parameters, like function, would need a very large set. Even if the number of choices per parameter is small, the number of combinations may be enormous. An application specific design must be done for most circuits. Such a design for each circuit is too expensive to do by hand. However if this could be done by an automatic program, a different design for each circuit becomes feasible.

In stead of having a large number of different standard cells, the design software should have a small number of automatic *circuit generators*. The circuit generators should be able to generate circuits according to parametric specifications. Preferably, the circuit generator should take as many parameters into account as possible.

It seems obvious that the function of a circuit should be parameterized. The circuit should be able to do any function within the class of functions of the circuit generator. The PLA generator was the first general function generator that could generate any boolean function. Generators may be relatively uncommitted, and generate random logic or finite state machines. For certain classes such as multipliers, memories or register files dedicated circuit generators may be necessary. We will assume that the circuit is given as a hierarchy of circuits with net lists.

Testability can also be built into a circuit. For instance, depending on a parameter, level sensitive scan paths may be built in. Also self test may be built in or spare parts may be included, to replace faulty parts. Finally, extra pins may be added to make internal signals visible.

The delay of a circuit should be a parameter. Because timing constraints are often an important and rigid design parameter at the top level, the delay should be a parameter that is set, while the power is minimized. The delay can be shortened by increasing transistor widths, adding buffers, or it may be decreased by adding extra hardware, by duplicating part of the logic to reduce the logic depth, or by introducing parallel processing.

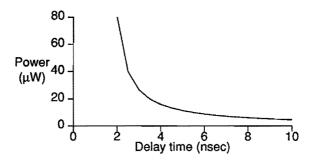

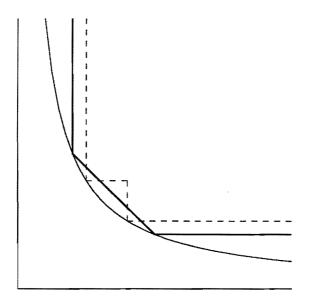

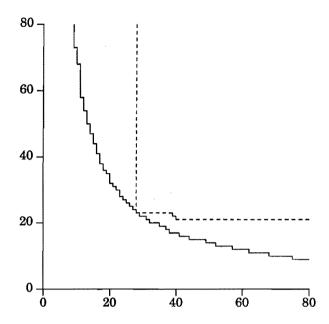

When the delay of the circuit is decreased the *power consumption* of the circuit is likely to increase. Figure 1.4 shows the relation between the delay and power parameters of an inverter. The power consumption also depends on the switching behavior of the circuit, and can therefore only be determined exactly by a realistic simulation.

Figure 1.4. Static power dissipation of an nMOS inverter as a function of the rise time.

The power consumption, and its trade-off with speed depends on the *technology*. With technology we mean the kind of process: for instance bipolar, nMOS or CMOS. This is strongly related to the kind of gate circuits that can be used. In general, this will be a difficult parameter to take into account. Certainly on a lower level, the design method depends heavily on the technology.

The design rules are structural and numeric constraints on the geometry of the layout. As far as the design rules are numeric rather than structural, they are often easy to parameterize. The numeric design rules are taken into account during the mask generation. In this phase, a topological structure is translated to mask data. The numeric rules determine the minimum width and spacing of the mask elements. Structural rules are difficult to implement, since they often influence design strategy that can be used. Such rules can not easily be parameterized, they must often be built into the algorithms.

The *shape* of the circuit follows from its environment and the shapes of the circuits surrounding it. The shapes of the larger circuits will be restricted to rectangles, but the aspect ratio can be chosen freely. The use of rectangles with variable aspect ratio makes a dense packing of the circuits easy.

The pin positions adapt to the environment. The positions of the pins are determined by the neighbors of the circuit. Sometimes through the cell routing is desired. In this case several pins for the same net are necessary.

Finally, the *effort* needed to design the circuit, or the cost to design it could be taken into account. In general, a better design may be expected when the effort that went into the design was greater. For instance certain critical circuits may be redesigned by hand. Less critical circuits can be designed automatically. For an automatic design tool such a parameter may also be useful. For instance, a simulated annealing algorithm may invest more time to achieve a better solution for a critical circuit, while a less critical circuit may use a fast and non-equilibrium schedule.

#### 1.4 Joint parameter optimization

The parameters of the modules must be optimized to match the environment of the modules. The requirements of the super module are translated to requirements of the sub-modules. The optimal parameters of the modules depend on each other. Therefore the parameters of the modules should be chosen simultaneously. Hence the name 'joint parameter optimization'.

Pin positions are an example of a parameter that should be optimized for all circuits simultaneously. When the floor plan is known, an approximate direction for the wire can be derived, and the pin position can be determined. However, when the positions of pins of some circuits are fixed, this optimization problem can become difficult. When two circuits are abutting, the pin position must be chosen for both circuits simultaneously. Preferably, the positions of the two pins should be facing each other, giving a minimum length connection.

Several parameters can be viewed as valuable resources. These parameters are related to the time, space and energy needed to perform the function and perhaps the effort to design the function. For each of these there is a price to be paid in terms of another parameter. These parameters can be traded against one another.

Well known is the trade-off between speed and power. More power can be used to make a gate or a macro faster (see figure 1.4). Such trade-off's can be represented by a *trade relation*. This is a relation between the resources that can be traded against each other. In a trade relation, a parameter cannot increase because another increases.

The parameters are related to each other, often by a partial order. The partial order relates the parameters of the sub-modules to the

parameters of the super module. In timing such a partial order is a data flow graph. The data flow graph is a partial order of the computations that are performed by the sub-modules. Each sub-module needs a certain amount of time to perform its computation. The longest path determines the total time for the whole module.

Figure 1.5. Data flow graph of a circuit. The longest path determines the delay of the circuit.

To do the optimization, the trade relations need to be known. Since the design of the sub-module is not yet known, a prediction of the trade relations has to be made. Such a prediction can be made by making a number of sample designs, and interpolating the trade relations between the known values of the parameters. Alternatively, information about old designs can be stored or a prediction can be derived from some characteristic parameters.

Delay can be traded against area. The trade-off between the area and the delay, by using more hardware, is the subject of high level functional synthesis [63]. Timing constraints set by the data flow graph relate the delays of the circuits to each other. Delay can be traded against hardware by introducing parallelism at a high level or by duplicating logic to reduce the length of the critical path.

In this book we will not address the optimization and design problems arising from such an approach to timing. The possibility of giving a macro cell generator parameters for speed, power and testability has not been investigated. We will only consider the function of the circuit and the layout parameters. We believe however, that the methods indicated in this book are well suited for introducing such parameters.

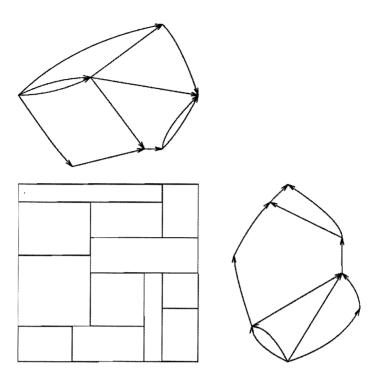

Figure 1.6. A rectangle dissection with its corresponding polar graphs.

The area of a chip is dissected into rectangular areas; a rectangular area is allocated for each circuit. A rectangle which is dissected by straight orthogonal lines is called a rectangle dissection. In a floor plan with rectangular circuits the width and the height of the circuits can be traded against each other. A partial order of the coordinates of the circuits is used to represent the relations between the width the different circuits. The graph representing this partial order is called the horizontal polar graph and denoted by  $\mathcal{P}_h(J_v,C)$ . A second, dual, (vertical) polar graph  $\mathcal{P}_v(J_h,C)$ , represents the relations between the heights. The topology of the rectangle dissection is determined by the polar graphs (see figure 1.6). The nodes  $J_v$  of the horizontal polar graph correspond to the vertical dissecting lines. The faces of the horizontal polar graph it is the other way around: the faces are the vertical lines and the nodes are the horizontal lines  $J_h$ . The edges of

each polar graph represent the rectangles of the rectangle dissection.

A trade relation, called *shape function*, specifies the trade-off of length and width for each circuit. No polynomial algorithm is known to determine the optimal trade-off in the general case [62]. When some restrictions are applied to either the polar graph or to the shape functions, polynomial algorithms become possible. In the next section and in chapter 3 some shape optimization algorithms will be described.

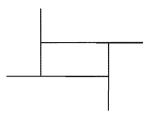

Figure 1.7. A slicing structure. The boxes within boxes indicate the hierarchy of slices.

The restriction to series parallel polar graphs is very effective. The rectangle dissections that have a series parallel polar graphs are called slicing structures. A slicing structure is a rectangle dissection that can be obtained by recursively dissecting rectangles into smaller rectangles by vertical and horizontal slicing lines. A slice is either an undissected rectangle or a rectangle dissected into two slices by a vertical or horizontal slicing line. This recursive definition indicates the hierarchical nature of the slicing structure. The slices are the modules of this hierarchy. The undissected rectangles represent the circuits, the primitive modules of the slicing hierarchy. A slicing structure can be

recognized by the property that all dissecting lines dissect a slice from one side to the other. Therefore it does not contain the 'wind mill' pattern:

#### 1.5 Example: shape optimization

In this section we will look at a simple algorithm for shape optimization for rectangular circuits [50]. It serves as an example of how the general predictor-adaptor paradigm can be translated into a concrete and straightforward algorithm. In this algorithm we will use some concepts that will play an important role in chapter 3.

The problem arises in the optimization of the aspect ratio of the circuits in a floor plan. We assume that the circuits have not yet been designed, so that they can take any aspect ratio, but have a fixed area. This assumption is consistent with top-down layout design. The rectangle dissection is already designed, the circuits are designed later. Only the area of the circuits is known, for instance by making a prediction based on the number of transistors or the number of nets in each circuit.

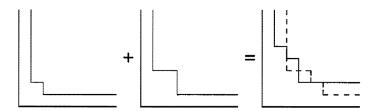

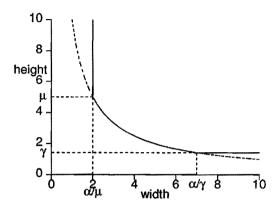

The flexibility of the circuits makes it possible to fill the available area completely. The problem is to find the optimal aspect ratios for the circuits, such that there is no wasted space between the circuits. The aspect ratio of the floor plan is given. The rectangle dissection is represented by a slicing structure. Each undissected slice is a circuit which has two parameters, w and h. The circuits are assumed to be completely flexible, only the product of wxh is fixed. The trade relation for the length and the width is a hyperbola. Because of the hierarchy and the flexibility of the circuits, an optimal solution is easy to find.

First, the areas of the compound slices are computed in a bottom-up order. This process is simple. The areas of the circuits are known. The

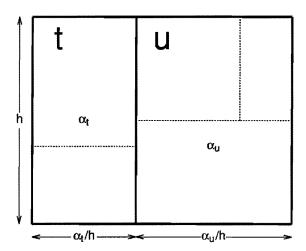

Figure 1.8. Shape assignment in a slicing floor plan. t and u are are slices that are separated by a slicing line (drawn) and they are decomposed themselves into sub-slices by further slicing lines (dashed). The optimal aspect ratio of each slice can simply be computed from the area of the slices and the dimensions of the floor plan.

area of a slice is the sum of the areas of its sub-slices. Finally the area of the floor plan is known. This process represents the bottom-up predictor. Information of the circuits is propagated up the hierarchy. This way global information about the design is gathered.

Once all slice areas are known the first global design decisions can be taken. The adaptor adapts the shapes of the slices in a top-down order. The first decision taken is the position of the first slicing line. This position follows directly from the shape of the floor plan and the area of the sub-slices.

Let the area of slice s be  $\alpha_s$ . Let slice s consist of two sub-slices t and u. The shape of slice s is  $w_s \times h_s$ . The shape of the sub-slices can be computed by  $h_t = h_s$  and  $w_t = \alpha_t/h_t$  if the slicing line is vertical. The shape of u can be computed in the same way. When the slicing line is horizontal  $h_t$  can be computed similarly.

By applying this method to all sub-slices, the shape assignment is done in a top-down order. The position of the slicing line determines the shapes of the sub-slices. The shape requirements are realized by translating them to requirements for the sub-slices, thereby moving the problems down the hierarchy. Since we assumed that the circuits are completely flexible, the problems can be solved here easiest.

In this algorithm we can see how the general concepts can be used explicitly in an algorithm for a specific problem. The hierarchy of slices and the flexibility of the rectangles made the problem much simpler. We saw how each slice was modeled by the height and width parameters and how they were related by a hyperbolic shape function.

#### 2. Building block layout

The conventional method of structured layout is building block layout. In this method the circuits are allocated a rectangular area. Because of this restriction they are also called *blocks*. This shape restriction is very common, and rarely a problem. Remember that in top-down design the blocks are designed after the construction of the floor plan, and that the shape of the blocks is to be adapted to the floor plan. There is no reason to make a flexible circuit any other shape than rectangular - rectangular is as good as any. The available area is dissected into rectangles. This dissection is represented by the polar graphs.

The layout problem is reduced to arranging the blocks and realizing the connections between them. In chapter 6 we will introduce another method for top-down layout design in which the primitive circuits are represented by unidimensional 'strips'. The building block method is more suitable for the layout of circuits that consist of complex subcircuits.

The circuits are connected by nets as specified by the net list. The building block circuit generator designs the layout of a circuit of rectangular blocks. It creates a rectangular layout, which can be used on a higher level in turn. We will assume that the area of the blocks and the area of the interconnections is disjunct: the interconnections are realized between the blocks. This assumption is reasonable if a small number of routing layers is available. When four or more layers are available, this assumption may not be reasonable any more.

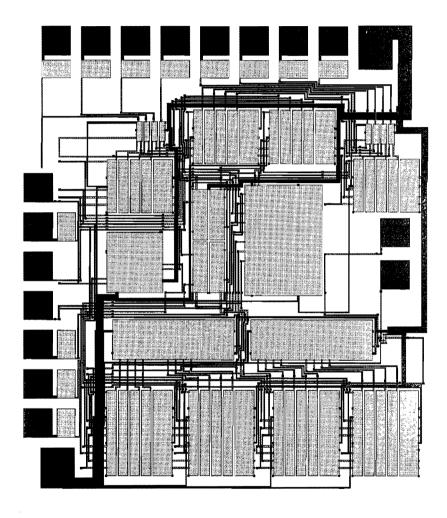

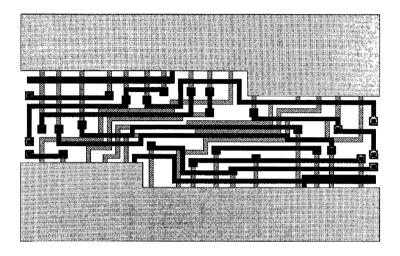

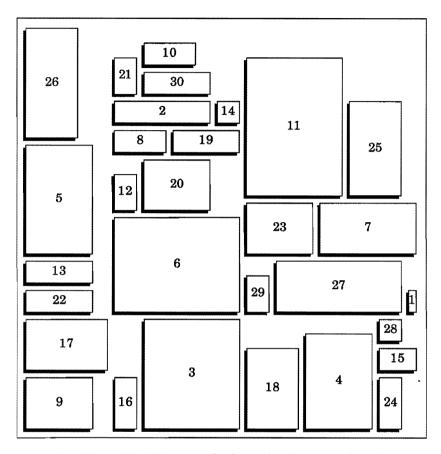

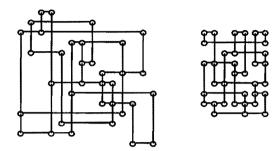

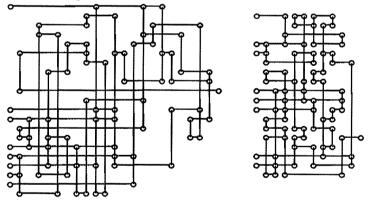

Figure 2.1. A building block layout.

The area for the interconnections is decomposed into *channels*. Each channel corresponds to a line  $j \in J$  in the rectangle dissection. The blocks on both sides of this line are moved apart to allow for the routing of the interconnections: each line is replaced by a rectangle that represents

the area of the channel. A channel can be seen as an 'interconnection block'.

The layout of the blocks is generated by other circuit generators. The building block circuit generator needs only to generate the layout of the interconnections.

This chapter serves as an example of the use of the predictor-adaptor paradigm to layout design and as a background for the remainder of the book. The generation of a building block layout proceeds in the following steps. First the relative positions of the blocks are determined. Then the nets are routed. From these first design decisions some parameters for the circuit generators are derived. Together these steps are called floor planning. Guided by the parameters, the circuit generators design the layout of the blocks. Finally the layout of the interconnections is generated and combined with the layout of the blocks.

#### 2.1 Floor planning

Floor planning was introduced by Preas and vanCleemput in [56]. They used a polar graph which was constructed by a branch and bound algorithm. In [32] a rectangle dissection was found by planarization of the interconnection graph and making a rectangular dual of this graph. Slicing was introduced in [64]. The approach followed here is based on the ideas of [51] in which a point configuration was sliced to get a slicing structure. Several software packages for floor planning have been developed, for instance [57,41,67].

The floor plan consists of a polar graph and its dual and a channel assignment which assigns nets to channels. The design decisions that are taken during the floor planning phase are the design of the polar graphs and the channel assignment.

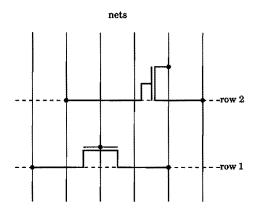

The design of the floor plan is done in several steps, which can be seen as a gradual refinement of the floor plan. The polar graphs, which give partial orders on the positions of the blocks, are determined first. Once the polar graph is known, a first prediction of the area allocation of the chip can be made, using the predictions for the shape functions of the blocks. This geometric information is used to determine the shortest route of each net.

The polar graph is restricted to a series parallel graph. In that case the rectangle dissection is a slicing structure. Using slicing structures has several advantages due to its hierarchical nature, such as: The use of a slicing structure avoids channel routing order conflicts [50]. A slicing structure facilitates the shape optimization [62, 52]. A slicing structure can be constructed by repeated slicing of a point configuration [51].

Since the shapes of the blocks have not been determined yet, the shape fitting problem does not play such an important role in floor planning. Therefore floor planning aims more at reducing the interconnection length. Shape fitting should be seen as a secondary objective. The slicing structure is designed in two steps [51]. In the first step the interconnections are taken into account. The decisions taken in the first step are refined further in the second step which takes the shape functions of the blocks into account.

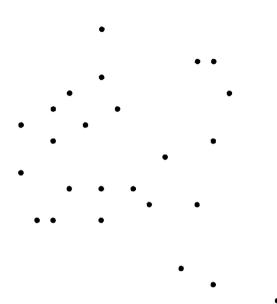

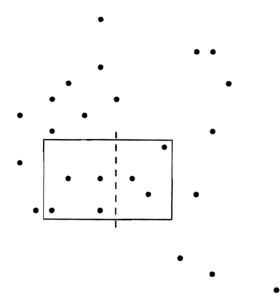

The first step in designing a floor plan is the design of a point configuration. In a point configuration, each circuit is assigned to a position in the plane. The circuits are represented by points, and the shape of the circuits is ignored. The point configuration should be regarded as an ideal placement that should be approximated as close as possible. The point configuration is usually designed with disregard of any shape information, often even with disregard of area information. The only kind of information that is used is the net list information.

Once the point configuration has been determined a slicing structure must be found that is consistent with this point configuration. The slicing structure is made by slicing the point configuration by straight orthogonal slicing lines. Any two circuits are separated by a slicing line during some stage of the slicing process. Exactly one of the two ordering relations in both dimensions is enforced by the slicing tree. So, for the purpose of slicing, the point configuration can be seen as two sequences of circuits. Slicing the point configuration means enforcing one of the two ordering between the groups of circuits that are separated by the slicing line.

The distance information in the point configuration may be interpreted as additional connectivity information. However, it is not obvious how this information can be used in the slicing process.

During the slicing the shapes of the circuits can be taken into account. An algorithm that finds the best slicing tree, given a point configuration and the shape functions of the circuits is described in

§ 3.3.

When the topology of the blocks is known, the routes of the nets can be determined. This is called global routing or channel assignment. The channel assignment assigns each net to a set of channel intersections.

After the slicing structure has been determined, the important design decisions have been made and the parameters for the circuits can be derived. From the slicing structure and the trade relations of the length and width parameters, we can derive the optimal shapes of the blocks. This problem is addressed in chapter 3. Also the optimal pin positions can be determined from this floor plan.

#### 2.2 The point configuration

A point configuration is the assignment of circuits to positions in the plane. Each circuit has two coordinates  $x_{c}$  and  $y_{c}$ . The distance  $d_{ij}$  between two circuits is

$$d_{ij} = \sqrt{(x_i - x_j)^2 + (y_i - y_j)^2}$$

(2.1)

The circuits C are connected by the nets N. The connections are represented by a bipartite graph  $\mathcal{N}(C \cup \{C\}, N, P)$ , in which the edges P are the circuit - net incidences, the pins. Each net has a so-called *net weight*  $w_n$  which indicates the relative importance of the net to be kept short. This weight is used in the various score functions used by the different algorithms. A net with weight 2 has the same influence as two nets with weight 1.

A number of numeric methods to construct the point configuration have been described in the literature. The *dutch metric* [51] translates net list information to distances between the circuits. In the dutch metric the distance between two circuits is defined to be

$$m_{ij} = 1 - \frac{\sum \{w_n \mid (i,n) \in P \land (j,n) \in P\}}{\sum \{w_n \mid (i,n) \in P \lor (j,n) \in P\}}$$

(2.2)

Two circuits that do not share any nets are placed at the maximum possible distance 1. Circuits that share all nets are placed at the minimum distance 0. This distance space is embeddable in a #C-1 dimensional euclidean space.

To reduce the number of dimensions to two, the method of [51] uses a Schoenberg projection [60] to project this multi dimensional point

Figure 2.2. The point configuration is a placement of points which represent the circuits in the plane.

configuration onto a plane. This method minimizes the distortion of the distances caused by the projection: it minimizes

$$\sum_{i,i\in C} (\mathsf{m}_{ij} - \mathsf{d}_{ij})^2 \tag{2.3}$$

The method of [30] tries to minimize the net length by minimizing

$$\sum_{i,i\in C} d_{ij}^2 \sum \{ w_n \mid (i,n) \in P \land (j,n) \in P \}$$

(2.4)

The minimization of this object function involves the calculation of the eigenvalues of a matrix.

The same problem is posed in [39], except that pin positions on the boundary are given. When given pin positions taken into account, the problem is reduced to solving a number of linear equations.

Equation (2.4) gives a bias for nets with many pins. Of course this problem could be alleviated by adjusting the net weights for multi-pin nets. But preferably, the connections should consist of two pin nets only. We already noted that connectivity is a more important

consideration in top-down design than shape fitting. It is therefore advisable to do the routing as early as possible. The ideal is to do routing before placement has been done.

Routing can be done before the construction of the point configuration by using the dutch metric. Using this distance metric, a shortest spanning tree can be determined for every net. The edges of the spanning tree represent two pin nets. The decomposition in two pin nets depends only on the structure of the net list, and not on the placement. Such a decomposed net structure is likely to give less deformation in the schoenberg projection method.

#### 2.3 Channel assignment

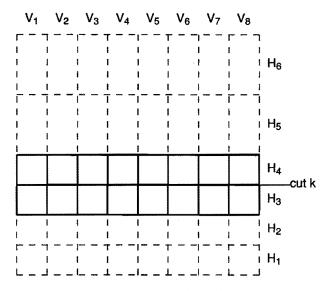

After the floor plan has been designed by calculating a point configuration and slicing, the topologies of the interconnections have to be determined. The channel assignment determines which channels are used by a net to make a connection. It is sometimes called global routing because it finds the rough routes of wires. After it is determined which wire uses which channel, the routing within the channels can be compacted. Using contour compaction track assignment is unnecessary.

The channel intersections are the set of the intersections between the horizontal and vertical channels. They are sometimes called the T-junctions. The channel intersections are denoted by the set  $V \subset J_h \times J_v$ .

The channel assignment is an assignment function  $\chi:N\to V^*$  which assigns to each net a set of channel intersections. The set of channel intersections of a net must be connected: there must be a path of intersections, going from channel to channel, connecting any pair of intersections in the set.

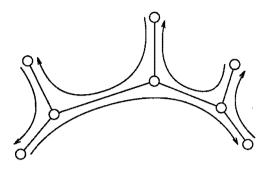

The routing model is a graph  $\mathcal{C}(V,E)$  of which the vertices V correspond to the channel intersections. Therefore this graph is called the *channel intersection graph*. Nodes that are neighbors in a channel are connected by an edge. Figure 2.3 shows an example of a channel intersection graph. The channel intersection graph is a planar graph. Note that the faces of the graph correspond to the circuits in the floor plan.

The length of an edge is the distance between the channel intersections. The distances in the routing model are not changed after

Figure 2.3. Example of a graph used as a global routing model. The drawn edges correspond to the edges of the channel intersection graph. The dashed edges are temporary edges that model the connections of a circuit.

a net has been routed. The sequence in which the nets are routed is therefore irrelevant.

The pins of the net are added to the graph as temporary nodes during the routing of the net. Temporary edges connect the temporary node to nodes that represent possible positions of the pin. A pin whose position is entirely unknown gets edges to all nodes surrounding the circuit. A pin whose position is exactly known only gets two edges. These two edges lead to nodes adjacent to the pin position. In figure 2.3 the temporary edges are indicated by dashed lines.

Some circuits allow a net to enter at different positions on its periphery. Making the length of the temporary edges small encourages routing through the circuit. Longer edges prohibit routing through the circuit.

Since the width of the channel is adapted, there is no limited channel capacity. We will not pay attention to the problem of controlling the

channel density. The main criterion for the wiring will be the length of the wires: all wires are to be kept as short as possible.

The routing problem is now to find the shortest connected subset of edges in the extended channel intersection graph that connect to the temporary nodes. This is known as the shortest steiner tree problem in graphs. A heuristic for the steiner tree problem is presented in chapter 4.

The steiner tree is a set of nodes and edges of the channel intersection graph. Only some of the nodes in the steiner tree indicate a transition from one channel to another. These nodes have orthogonal edges in the steiner tree. Only those channel intersections are included in the channel assignment of the net.

#### 2.4 The interfaces

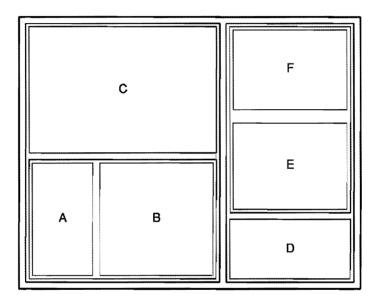

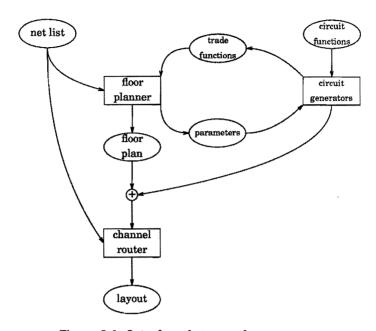

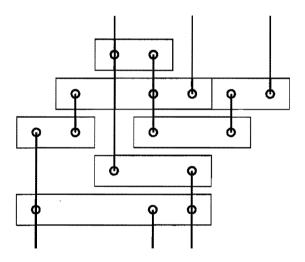

From the floor plan, as determined by the slicing structure and the channel assignment, parameters must be derived for the design of the circuits. Figure 2.4 gives an overview of the flow of the design data. The design is specified as a net list of interconnected circuits. The circuits also each have a description, which depends on the type of circuit. An essential feature of top-down design is the information exchange between the circuit generators and the floor planner.

The circuit generators start by reading the descriptions of the circuits they must design. In bottom-up design the circuit generators would immediately design these circuits. In a top-down design method the circuit generators first predict the capabilities they have for the parameters. For some parameters this can be specified in the form of trade relations.

Using the net list and the capabilities of the circuits, the floor planner designs a floor plan. This floor plan is represented as a slicing structure and as a channel assignment for the nets. The slicing structure determines the ordering of the circuits on the chip. The design parameters that can be derived from the floor plan are passed to the circuit generators. The circuit generators can then design the circuits accordingly. Once the circuits have been designed, the building block layout can be assembled and the masks for the connecting nets can be generated.

Figure 2.4. Interfaces between the programs.

We use the channel assignment to estimate the length of each wire and the widths of the channels. A statistical method for estimating the channel width has been proposed in [21]. The length of a wire can be used to estimate the capacitance of the wire. The output buffer driving the wires could be dimensioned to compensate this capacitance.

The channel width is not fixed; the width of the channel is determined by the number of wires that must be accommodated. The use of a slicing structure makes it easy to adapt the widths of the channels to match the requirements.

The width of a channel can be estimated from the routes found by the channel assignment. A lower bound for the width of the channel is the number of wires that must pass a certain point. The maximum number of wires that overlap at any point in the channel is called the *channel density*. Experience shows that this bound is rather sharp. After the channel assignment, shape optimization resizes the circuits according to widths of the channels.

A problem is that the topology of the channel intersection graph depends on the dimensions of the circuits and the widths of the channels. To determine the topology and distances in the channel intersection graph, the dimensions of the circuits must be known. It is therefore necessary to determine the optimal shapes of the circuits before the channel assignment can be done. It is advisable to redo the optimization after the channel assignment. Note, however, that the channel assignment, once determined is insensitive to topology changes in the channel intersections graph. The same nodes still exist in the graph, only the connecting edges have been changed. The channel assignment for a net is still valid.

The optimal shapes can be determined with the algorithm that is described in § 3.2. It may be a good idea to redo this optimization after the design of each circuit. When the predictions were inaccurate, it may be necessary to redesign some circuits.

Some blocks, like PLAs, may have limited flexibility and others may be designed beforehand. Of course, it is necessary to limit the number of fixed shape blocks. Another problem of fixed shape blocks is in the pin positions. A special heuristic is necessary to find a good orientation of the circuits. The pin positions can be determined once the orientation of the blocks is determined.

When all the circuit generators can produce the pins where they predicted that they would be, the channel assignment need not be redone. To avoid problems that may occur due to inconsistencies, the channel assignment is redone after all the circuits have be designed.

### 2.5 Mask generation

When the layout of the circuits has been designed, and the channel assignment of the nets is known, the layout of the routing can be generated. This is one of the most time consuming tasks in manual layout design. The mask generation of the interconnections is probably in any automatic layout design package the most time saving program.

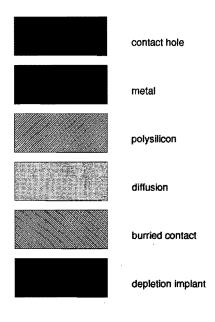

A layout is a set of patterns that completely specifies the geometry of the circuit. The term mask will be used for each pattern. To keep the mask generating algorithms simple, the mask patterns will be restricted to sets of iso-oriented rectangles.

To increase the yield when the circuit goes into production, patterns are required to satisfy certain rules, the *design rules*. Two classes of rules can be distinguished: structural rules and numeric rules. Structural rules enforce or prohibit certain combinations while numeric rules quantify the width of, and spacings between patterns in a mask or in a combination of masks. The numeric rules are almost exclusively specifications of lower bounds, because it is assumed that the layout design techniques will try to keep the total chip small.

The process of packing the layout elements as close as the design rules allow is called *compaction*. A channel allows for one-dimensional compaction because the positions of the pins of a channel are fixed but the channel width is not. One-dimensional compaction is a simpler problem then two-dimensional compaction.

Contour compaction [15] introduces jogs anywhere where this is advantageous. It takes maximum advantage of the design rules by using different rules on different layers. It allows variable width wires and takes advantage of irregular channel boundaries.

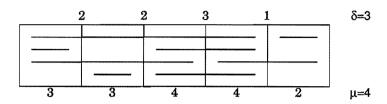

A number of channel routers that use contour compaction have been described [59,80,28]. However, contour compaction alone suffices to get good layouts. It makes conventional track assignment unnecessary, which simplifies the channel routing considerably.

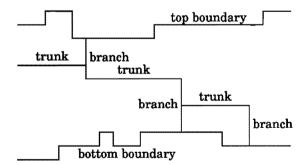

Figure 2.5. A routing channel with irregular boundaries. A net with 4 pins is decomposed into 2 pin sections. Each section has a trunk and two branches. The masks of a pair of branches to the same pin are superimposed.

The channel has two channel boundaries. We will assume that the channel is oriented horizontally, so there is a top and a bottom boundary. Wires can leave the channel at the open ends to the left and the right. Which nets have to leave and at which side is determined by the channel assignment. The pins on the boundary have known exact positions while the pins that leave the channel still have to be positioned.

Given the pins of a net, the net can be decomposed into one or more 2 pin segments. The global router ensures that there is never a net with only one pin. If there are several segments, the segments share a pin. Each pin connects at most to two segments.

Each two pin segment is realized by a horizontal piece called *trunk* and two vertical pieces called the *branches*. The vertical branches bring the wire into the channel. The horizontal trunk connects the branches together.

The compaction is done by maintaining two contours, one for each layer, that indicate the area occupied by previous trunks. A contour is a piecewise constant function, which gives the boundary between the area that is occupied by the wires and the free area. Only the trunks and their vias are considered during the compaction; the branches are added once the layout for the trunks is determined.

The contour is initialized with the shape of the bottom channel boundary. Trunks are processed one by one, and the channel is filled from the bottom to the top. The next trunk, with its associated vias, is placed against this contour, thereby using a minimum of space. The space used by this trunk and its vias, determined by the design rules, is added to the contour.

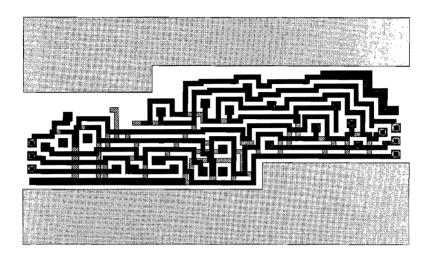

Figure 2.6. Routing after compaction phase.

As can be seen in figure 2.6 not all jogs that are generated this way are necessary to reduce the channel width. Each jog is believed to be a small reliability hazard due to electromigration. Also many jogs mean many rectangles in the layout. Wire straightening therefore increases the reliability of the chip and decreases the amount of disk space needed to store the layout.

Two passes are needed to get rid of unnecessary jogs. In the first compaction pass the width of the channel and the space available for each trunk is determined. All contours are saved, such that it will be known exactly what area can be used for each trunk in the second pass.

In the second pass the actual mask generation is done. The second pass starts at the top of the channel, and the trunks are compacted in the reverse order. Now there are two boundaries for each trunk, delimiting the area available on both sides. The straightening algorithm constructs a trunk with a minimum number of jogs that fits between the two contours.

Figure 2.7. Routing after straightening phase.

Because the pins are not restricted to grid positions, a branch may have more than one opposite branch. Therefore gridless channel routing introduces more vertical constraints. A problem is that there may be cycles in the vertical constraint graph. In [44] a simple but less conventional approach was used, which guarantees that there will be no cycles. This will guarantee that the algorithm generates a valid layout.

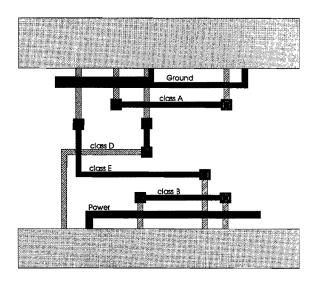

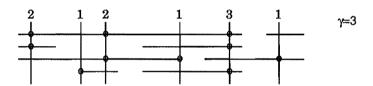

In the approach of [44] the two pin segments are divided into five classes, indicated by the letters A through E. Branches and trunks are realized in both layers. Figure 2.8 illustrates the different classes. The bottom layer is realized in polysilicon, the top layer is realized in metal.

Class C segments, that have pins in exactly opposite positions of the channel, are handled as class E or D segments. Power and ground lines are routed planarly. Therefore the power and ground lines are routed at the top and bottom of the channel. In [44] the branches at the top of the channel use another layer than the branches at the bottom. However, to be able to connect to power and ground on the metal layer it is unavoidable that the branches connect to the sides of the cells on the polysilicon layer. Therefore the classes D and E use an extra via hole to change layer.

Figure 2.8. Different classes of two pin segments.

The segments will be ordered from the bottom of the channel to the top of the channel. The classes can be ordered in the sequence B-E-D-A. Within the classes A and B there are no vertical constraints, and any order is possible. Within class D the segments can always be ordered on the position of the bottom pin from right to left. The segments of class E can be ordered from left to right on the position of the top pin. This always constitutes a valid order, in which the vertical constraints are satisfied.

The vertical constraints in the classes E and D tend to form very long chains. This causes trunk ordering algorithms similar to [76,8] to become ineffective. It is necessary to use contour compaction to reduce the channel width.

Table 2.1 compares the channel widths for two randomly generated channels and Deutsch's Difficult Example [14]. The channels have a large number of pins. Realistic channels in building block layouts mostly have far fewer pins. The channels were routed using Mead & Conway [46] design rules. Since our router does not have the concept of

tracks it is only possible to compare the width of the channel in lambda's. The pin positions were on a grid and the channel sides were straight. For comparison the last column is added which gives the density of the channel times 6. This could be the performance of a good track based router.

Table 2.1. Performance comparison for three Channels

| example   | gridless router<br>pin pitch |     | track router |

|-----------|------------------------------|-----|--------------|

|           | 5                            | 6   | 6            |

| random1   | 128                          | 120 | 132          |

| random2   | 82                           | 68  | 84           |

| Deutsch's | 144                          | 116 | 114          |

The results for Deutsch's Difficult Example are almost as good as those of a good track based router, and for random examples even better. In most practical floor plans the pin density is much lower, and compaction is more rewarding than track assignment techniques.

# 3. Joint shape optimization