# Integrated Schottky logic

*Citation for published version (APA):* Lohstroh, J. (1981). *Integrated Schottky logic*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Hogeschool Eindhoven. https://doi.org/10.6100/IR75257

DOI: 10.6100/IR75257

# Document status and date:

Published: 01/01/1981

# Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

## Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# INTEGRATED SCHOTTKY LOGIC

# **J.LOHSTROH**

DISSERTATIE DRUKKERIJ UDIDITO HELMOND TELEFOON 04920-23981

# INTEGRATED SCHOTTKY LOGIC

# INTEGRATED SCHOTTKY LOGIC

PROEFSCHRIFT

TER VERKRIJGING VAN DE GRAAD VAN DOCTOR IN DE TECHNISCHE WETENSCHAPPEN AAN DE TECHNISCHE HOGESCHOOL EINDHOVEN, OP GEZAG VAN DE RECTOR MAGNIFICUS, PROF. IR. J. ERKELENS, VOOR EEN COMMISSIE AANGEWEZEN DOOR HET COLLEGE VAN DEKANEN IN HET OPENBAAR TE VERDEDIGEN OP VRIJDAG 13 NOVEMBER 1981 TE 16.00 UUR

DOOR

# JAN LOHSTROH

**GEBOREN TE 'S-GRAVENHAGE**

# DIT PROEFSCHRIFT IS GOEDGEKEURD DOOR DE PROMOTOREN

# prof.dr. F.M. Klaassen

en

# prof.dr. H.J. de Man

Aan Yolanda en Tjitske

# Acknowledgment

The investigations described in this thesis were performed at the Philips Research Laboratories, Eindhoven, The Netherlands.

I am greatly indebted to the management of these laboratories for affording me the opportunity to publish the results of these investigations in their present form.

I should like to express my gratitude to all those who have contributed to this work in any way.

Personal acknowledgment is made to the following:

In the first place my thanks to J.D.P. v.d. Crommenacker who has worked with me enthusiastically since the start of the ISL-work in August 1976, he has done most of the layout and measuring work and he is coauthor of Sections 5 and 9.

Then I should like to thank R. Pluta for his stimulating response during his 1-year stay in our laboratories for his M.Sc.-graduation; he worked on oxide-isolated ISL modeling and he is coauthor of Sections 8, 10 and 13.

Gratitude is expressed to A.J. Linssen and N.C. de Troye who coauthored Sections 5 and 7 respectively.

I should like to thank D. Allison of the Signetics Corporation for processing the first ISLwafers and for his help with the experiments with higher doped substrates.

I should also like to thank R. Caduri, C.M. Hart, P.A.H. Hart, H. Ontrop, A. Slob and A.T. v. Zanten for many valuable discussions.

Thanks also to R. Treadway, D. Goddard, P. Lee, P. Scott and B. Loftis of the Signetics Corporation for their stimulating response and my appreciation also for their confidence in ISL by implementing it in their products.

Finally, I should like to thank Mrs. B. Brinkhaus for her excellent text-composing work and Mrs. P. Heesakkers (of Delta-H) for her skilful page-assembling work for this book.

Eindhoven, November 1981.

# Contents

| 1.       | GENERAL INTRODUCTION                                      |

|----------|-----------------------------------------------------------|

| 2.       | ASPECTS OF INTEGRATED SCHOTTKY LOGIC (ISL)                |

|          | AND COMPARISON WITH $l^2L$ AND STL                        |

| 2.I.     | Introduction                                              |

| 2.II.    | Comparison between bipolar and MOS-type circuits          |

| 2.III.   | Logic circuits for high speed bipolar VLSI                |

| 2.IV.    | Bipolar processes for ISL 8                               |

| 2.V.     | The original concept of ISL 8                             |

| 2.VI.    | Performance of pn-isolated ISL 11                         |

| 2.VII.   | Oxide-isolated ISL technologies 12                        |

| 2.VIII.  | Speed comparison of ISL and $I^2L$ 15                     |

| 2.IX.    | Propagation delay time of $I^2L$ at low current levels 17 |

| 2.X.     | Propagation delay times of ISL and STL at low and         |

|          | intermediate current levels 18                            |

| 2.XI.    | Fan-in and Fan-out aspects of ISL and STL 19              |

| 2.XII.   | Performance, temperature behaviour and first-order        |

|          | modeling of ISL                                           |

| 2.XIII.  | First-order modeling of oxide-isolated ISL 23             |

| 2.XIV.   | Static noise margins of logic circuits 24                 |

| 2.XV.    | Static noise margins of ISL, STL, $I^2L$ , and $SI^2L$ 27 |

| 2.XVI.   | Dynamic noise margins of logic circuits 31                |

| 2.XVII.  | Dynamic noise margins of ISL 32                           |

| 2.XVIII. | Temperature behaviour of the static noise                 |

|          | margins of ISL and STL 33                                 |

| 2.XIX.   | Applications of ISL 35                                    |

| 2.XX.    | References                                                |

| 3.      | DEVICES AND CIRCUITS FOR BIPOLAR (V)LSI             |

|---------|-----------------------------------------------------|

|         | J. Lohstroh, Proc. IEEE, vol 69, no. 7,             |

|         | pp. 812-826, July 1981 37                           |

| 3.I.    | Introduction                                        |

| 3.II.   | Comparison between bipolar and MOS-type circuits    |

| 3.III.  | General behaviour of switching speed and            |

|         | power-delay product of bipolar circuits             |

| 3.IV.   | The n-p-n transistors                               |

|         | A. SBC, CDI and 3D processes                        |

|         | B. VLSI process requirements                        |

|         | C. Oxide-isolation processes                        |

|         | D. Polysilicon processes                            |

|         | E. Influence of polysilicon on the emitter          |

|         | F. Up-diffused base processes                       |

|         | G. Short-channel JFET transistors (SIT)             |

| 3.V.    | The p-n-p tranisistors                              |

|         | A. Lateral p-n-p transistor types                   |

|         | B. Vertical p-n-p transistor types                  |

|         | C. Reverse operated vertical p-n-p transistor types |

| 3.VI.   | Schottky diodes and polysilicon diodes              |

|         | A. Schottky barrier diodes                          |

|         | B. Lateral polysilicon diodes                       |

| 3.VII.  | Resistors                                           |

|         | A. Diffused and ion-implanted resistors             |

|         | B. Polysilicon resistors                            |

| 3.VIII. | Logic circuits                                      |

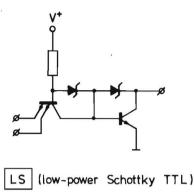

|         | A. Low-power Schottky TTL (LS)                      |

|         | B. Integrated Injection Logic (I <sup>2</sup> L)    |

|         | C. Schottky Transistor Logic (STL)                  |

|         | D. Integrated Schottky Logic (ISL)                  |

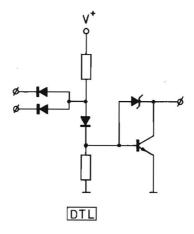

|         | E. Diode Transistor Logic (DTL)                     |

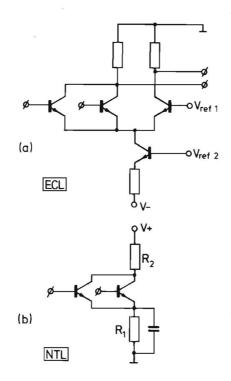

|         | F. Emitter Coupled Logic (ECL)                      |

|         | G. Non-threshold Logic (NTL)                        |

|         | H. Circuit/technology combinations comparison       |

| 3.IX.   | Conclusions                                         |

| 3.X.    | Acknowledgment                                      |

| 3.XI.   | References                                          |

| 4.      | ISL, A FAST AND DENSE LOW-POWER LOGIC, MADE IN                   |

|---------|------------------------------------------------------------------|

|         | A STANDARD SCHOTTKY PROCESS                                      |

|         | J. Lohstroh, IEEE J. Solid-State Circuits, vol. SC-14,           |

|         | no. 3, pp. 585-590, June 1979 65                                 |

| 4.I.    | Introduction                                                     |

| 4.II.   | Principle of Integrated Schottky Logic                           |

| 4.III.  | Current sources                                                  |

| 4.IV.   | Layout technique                                                 |

| 4.V.    | Processes and propagation delay measurements                     |

| 4.VI.   | Fan-out, Fan-in; speed comparison with I <sup>2</sup> L;         |

|         | absence of parasitic SCR-latching                                |

| 4.VII.  | Noise margins of ISL (comparsion with I <sup>2</sup> L)          |

| 4.VIII. | ISL in analog processes                                          |

| 4.IX.   | Advanced ISL proposals                                           |

| 4.X.    | Conclusions                                                      |

| 4.XI.   | Acknowledgment                                                   |

| 4.XII.  | References                                                       |

| _       |                                                                  |

| 5.      | OXIDE ISOLATED ISL TECHNOLOGIES                                  |

|         | J. Lohstroh, J.D.P. v.d. Crommenacker and A.J. Linssen,          |

|         | IEEE Electron Device Letters, vol. ED-2, no. 2,                  |

|         | pp. 30-31, Feb. 1981                                             |

| 5.I.    | Introduction and technologies                                    |

| 5.II.   | Conclusion                                                       |

| 5.III.  | References                                                       |

| 6.      | PERFORMANCE COMPARISON OF ISL AND I <sup>2</sup> L               |

|         | J. Lohstroh, IEEE ISSCC 1979, Digest of Technical                |

|         | Papers, pp. 48-49, Feb. 1979                                     |

| 6.I.    | Comparison                                                       |

| 6.II.   | Conclusion                                                       |

| 6.III.  | References                                                       |

| 7.      | PROPAGATION DELAY TIME OF I <sup>2</sup> L AT LOW CURRENT LEVELS |

|         | J. Lohstroh and N.C. de Troye, Electronics Letters,              |

|         | vol. 14, no. 22, pp. 705-706, Oct. 1979                          |

| 7.I.    | Calculation                                                      |

| 7.II.   | Reference                                                        |

|         |                                                                  |

| 8.       | PROPAGATION DELAY TIMES OF ISL AND STL                        |

|----------|---------------------------------------------------------------|

|          | J. Lohstroh and R.M. Pluta, submitted to                      |

|          | IEEE J. Solid -State Circuits                                 |

| 8.I.     | Introduction                                                  |

| 8.II.    | External and internal DC-voltage levels                       |

|          | A. ISL                                                        |

|          | <i>B. STL</i> 100                                             |

|          | C. Fan-in and/or fan-out larger than 1 100                    |

| 8.III.   | Low current level propagation delay times 100                 |

|          | A. General expression for the propagation delay               |

|          | <i>time for</i> $F_i = F_o = 1$                               |

|          | B. Propagation delay time starting from the                   |

|          | <i>DC-situation</i> ( $F_i = F_o = 1$ )                       |

|          | C. Propagation delay time in a ring-oscillator                |

|          | $(F_{i} = F_{o} = 1)$                                         |

|          | D. $Fan-out \ge 1$                                            |

| 21<br>21 | $E.  Fan-in \ge 1. \qquad 105$                                |

|          | F. Measures to obtain fan-in independent propagation          |

|          | delay times in ISL and STL 106                                |

| 8.IV.    | Propagation delay times at medium and high current levels 108 |

|          | A. ISL at high current levels with $F_i = F_o = 1$ 108        |

|          | B. ISL at medium current levels when $F_i = F_o = 1$ 112      |

|          | C. ISL at medium and high current levels when                 |

|          | $F_i \ge 1$ and $F_o \ge 1$                                   |

|          | D. STL 112                                                    |

| 8.V.     | Series resistances and wiring capacitances 113                |

|          | A. Series resistances in ISL 113                              |

|          | B. Series resistances in STL 114                              |

|          | C. Wiring capacitances in ISL and STL 114                     |

| 8.VI.    | ISL/STL comparison and measurements 114                       |

|          | A. Theoretical comparison 114                                 |

|          | B. Measurements, simulations and calculations 115             |

| 8.VII.   | Conclusions 117                                               |

| 8.VIII.  | References                                                    |

|          |                                                               |

|   | 9.       | PERFORMANCE, TEMPERATURE BEHAVIOUR AND                          |

|---|----------|-----------------------------------------------------------------|

|   |          | FIRST-ORDER MODELING OF ISL                                     |

|   |          | J. Lohstroh and J.D.P. v.d. Crommenacker, IEEE J. Solid-State   |

|   |          | Circuits, vol. SC-15, no. 3, pp. 269-276, June 1980 119         |

|   | 9.I.     | Introduction                                                    |

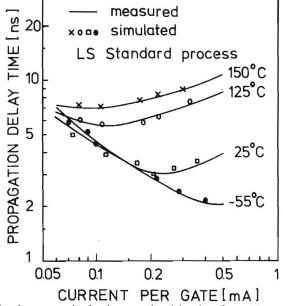

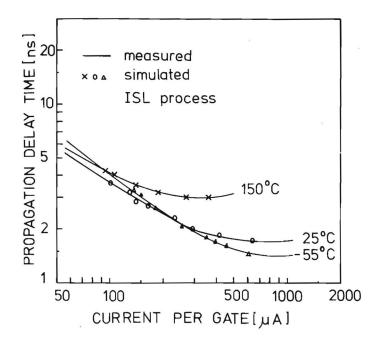

| ÷ | 9.II.    | Measurements and modeling of ISL in a standard LS process 120   |

|   | 9.III.   | Intrinsic and extrinsic behaviour versus temperature of ISL 126 |

|   |          | A. Intrinsic behaviour 126                                      |

|   |          | B. Extrinsic behaviour without junction capacitances            |

|   |          | for 200 µA/gate                                                 |

|   |          | C. Extrinsic behaviour at 200 µA/gate 129                       |

|   | 9.IV.    | Measurements and modeling of ISL in an improved                 |

|   | ,        | process (ISL process)                                           |

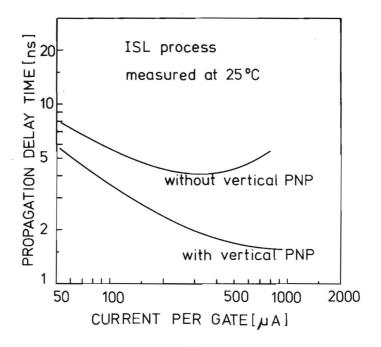

|   | 9.V.     | ISL performance with lateral p-n-p only 131                     |

|   | 9.VI.    | Conclusions                                                     |

|   | 9.VII.   | Acknowledgment                                                  |

|   | 9.VIII.  | References                                                      |

|   | 10.      | FIRST-ORDER MODELING OF OXIDE ISOLATED ISL                      |

|   | 10.      | J. Lohstroh and R.M. Pluta, submitted to                        |

|   |          | IEEE Trans. Electron Devices                                    |

|   | 10.I.    | Introduction                                                    |

|   | 10.II.   | Device structure                                                |

|   | 10.III.  | Modeling of the merged transistor part                          |

|   |          | A. Series resistances                                           |

|   |          | B. Transit times and transistor base-currents                   |

|   |          | C. Depletion capacitances                                       |

|   | 10.IV.   | Modeling of the Schottky diode part                             |

|   | 10.V.    | The complete model of an ISL gate                               |

|   | 10.VI.   | Temperature dependency of model parameters                      |

|   |          | A. Saturation currents of transistors and Schottky diodes 141   |

|   |          | B. Transit times of transistors and diodes                      |

|   |          | C. Depletion capacitance and built-in diffusion voltages 143    |

|   | ÷        | D. Current gains of transistors                                 |

|   |          | <i>E. Resistances</i>                                           |

|   | 10.VII.  | Measurements, analytical calculations and simulations 145       |

|   | 10.VIII. | Conclusions                                                     |

|   | 10.IX.   | Appendix                                                        |

|   |          |                                                                 |

.

| 10.X.    | References                                                      |

|----------|-----------------------------------------------------------------|

| 11.      | STATIC AND DYNAMIC NOISE MARGINS OF LOGIC CIRCUITS              |

|          | J. Lohstroh, IEEE J. Solid-State Circuits, vol. SC-14, no. 3,   |

|          | pp. 591-598, June 1979; also published in Nikei                 |

|          | Electronics, 4-28, pp. 124-143, 1980 (in Japanese) 149          |

| 11.I.    | Introduction                                                    |

| 11.II.   | Four basic noise sources 151                                    |

| 11.III.  | Worst-case static series-voltage noise margin 151               |

| 11.IV.   | Worst-case static parallel-current noise margin 154             |

| 11.V.    | Worst-case static margins for voltage noise in                  |

|          | ground- and power-supply lines                                  |

| 11.VI.   | Elucidation of the influence of static noise in a flip-flop 156 |

| 11.VII.  | Dynamic noise margins 159                                       |

| 11.VIII. | Energy noise margins                                            |

| 11.IX.   | Measured and computer-simulated noise margins of ISL 162        |

|          | A. Static noise margins                                         |

|          | B. Dynamic noise margins 166                                    |

| 11.X.    | Conclusions                                                     |

| 11.XI.   | Appendix I; Charging a capacitor with a pulsed voltage          |

|          | source and a series resistor                                    |

| 11.XII.  | Appendix II; Charging a resistor-shunted capacitor              |

|          | with a pulsed current source 170                                |

| 11.XIII. | Acknowledgment 171                                              |

| 11.XIV.  | References                                                      |

| 12.      | CALCULATION METHOD TO OBTAIN WORST-CASE                         |

|          | STATIC NOISE MARGINS OF LOGIC CIRCUITS                          |

|          | J. Lohstroh, Electronics Letters, vol. 16, no. 8,               |

|          | pp. 273-274, April 1980 173                                     |

| 12.I.    | Calculation 173                                                 |

| 12.II.   | References                                                      |

| 13.      | TEMPERATURE BEHAVIOUR OF THE STATIC NOISE                       |

|          | MARGINS OF ISL AND STL                                          |

|          | J. Lohstroh and R.M. Pluta, submitted to                        |

| 8        | IEEE J. Solid-State Circuits                                    |

| 13.I.    | Introduction                                                    |

|          |                                                                 |

| 13.II.     | Temperature coefficients of the voltage swings of                   |

|------------|---------------------------------------------------------------------|

|            | ISL and STL                                                         |

| ,          | A. ISL                                                              |

|            | <i>B. STL</i>                                                       |

| 13.III.    | The static noise margins; methods of determination 182              |

| 13.IV.     | First-order analytical expressions for the voltage swing            |

|            | and the worst-case ground-line voltage noise margins of             |

|            | simplified ISL and STL circuits with the most important             |

|            | series resistances included                                         |

|            | A. ISL without pull-up current                                      |

|            | B. ISL with pull-up current                                         |

|            | C. STL without pull-up current                                      |

|            | D. STL with pull-up current                                         |

| 13.V.      | DC models of oxide-isolated ISL and STL gates 190                   |

| 13.VI.     | Voltage swings and worst-case static ground-line voltage            |

|            | noise margins of oxide isolated ISL and STL at 100 $\mu A/gate$ 192 |

|            | A. ISL without pull-up current                                      |

|            | B. ISL with pull-up current                                         |

|            | C. STL without pull-up current                                      |

|            | D. STL with pull-up current                                         |

| 13.VII.    | Comparison, conclusions and discussion 195                          |

| 13.VIII.   | References                                                          |

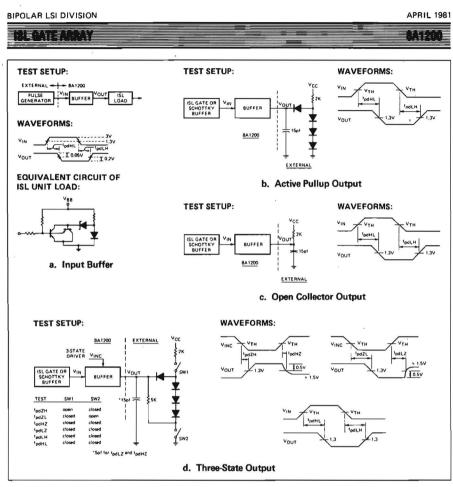

| APPENDIX A | ; ISL APPLICATIONS                                                  |

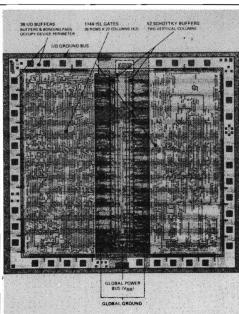

|            | A. The 3422A (256 bits shift register)                              |

| 2          | B. The OQ4100N1 (pipeline-multiplier)                               |

|            | C. The OQ0040 (counter chip)                                        |

| 1          | D. The ISL-CCL library and 8X60 (FIFO memory controller) 202        |

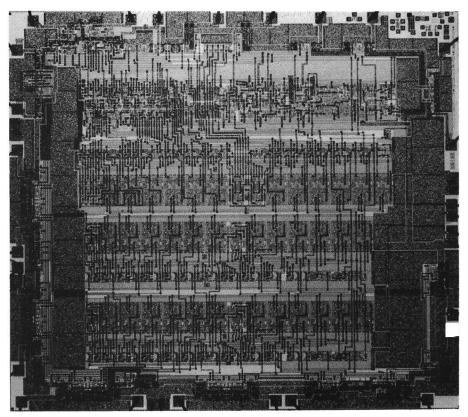

| )          | E. The 8A1200 (1200 gate-array) 203                                 |

|            | References                                                          |

| APPENDIX B | ; 8A1200 SPECIFICATIONS 207                                         |

|            |                                                                     |

| SUMMARY    |                                                                     |

|            |                                                                     |

| SAMENVATI  | 'ING                                                                |

| CURRICULU  | M VITAE                                                             |

# **General Introduction**

1

Twenty years after the introduction of the first integrated circuit (which contained a few transistors in combination with a few passive elements) silicon integrated circuit technology has reached a very high level of perfection, resulting in I.C.'s with 10.000 transistors and an equal number of passive elements made in processes with economical production yields.

The process development has still not reached saturation level; in the future the integration of even  $10^5 - 10^6$  and perhaps more transistors on a chip, known as VLSI (= Very Large Scale Integration) and ULSI (= Ultra Large Scale Integration) are expected. The factors responsible for this dramatic expansion are:

- a) continuing improvement in processes, partly due to the introduction of better chemical and physical processing steps, and partly due to elimination of first-order and second-order process variations; this is all made possible by expertise built up from the production of millions of I.C.'s (learning curve);

- b) continuing improvement in photolithography and etching techniques, which means that device sizes can be decreased, resulting in a better packing density of the circuitry;

- c) invention of new devices and circuits, which means that basic electronic functions can be performed with fewer or smaller basic elements (to improve the packing density) and/or at lower power dissipation level (which allows more functions on a chip).

Integrated Schottky Logic (ISL) is an example of the latter factor. It is a new bipolar logic concept that can be realized using existing processes. It combines device structures, which in fact were already known separately, with a very attractive type of logic gate which can be used for high speed VLSI.

This book discusses a large number of aspects of ISL, such as the original concept, its performance in different processes, switching speed (calculated and measured), first order modeling, its behaviour as a function of temperature, the noise margins as a func-

1

tion of temperature and its applications.

2

The next section entitled: "Aspects of Integrated Schottky Logic (ISL) and comparison with I<sup>2</sup>L and STL", is an extensive introductory discussion to the contents of the book; for detailed information reference should be made to the subsequent sections, where reprints of already published papers and not yet published papers are given. These papers include an overview article on "Devices and circuits for bipolar (V)LSI" (where bipolar circuits are compared with MOS circuits in general, and where bipolar circuit/ technology-combinations which satisfy VLSI requirements are discussed), and an article on "Static and dynamic noise margins of logic circuits" (where a general noise-margin test method is proposed, which is applicable to every type of logic circuit).

The subsections of section 2 and the corresponding section 3 to 12 are arranged in the following order: overview of devices and circuits for bipolar VLSI (section3), introduction to pn-isolated and oxide-isolated ISL (sections 4 and 5), comparison speed of ISL and  $I^2L$  (section 6), analytical expressions for propagation delay times (sections 7 and 8), modeling of pn-isolated and oxide-isolated ISL (sections 9 and 10), static and dynamic noise margins of logic circuits in general and of ISL in particular (sections 11 and 12), and the temperature behaviour of the static noise margins of ISL and STL (section 13). Appendix A discusses ISL applications and appendix B is a product specification of the 8A1200 ISL gate array. 2

# Aspects of Integrated Schottky Logic (ISL) and Comparison with I<sup>2</sup>L and STL

#### 2.I. Introduction

Silicon integrated circuits are fabricated using two main-stream technologies: bipolar and unipolar circuits. In the last group we find the MOSFET, MESFET and JFET circuits. Anno 1981 both technologies (bipolar and unipolar) circuits employ lithography techniques allowing minimum details of 2-3  $\mu$ m in standard production lines.

Production yields are high enough to obtain IC's with many thousands of transistors on an economical scale.

The two technologies differ in the electrical performance and packing density that can be obtained with the present 2-3  $\mu$ m lithography rules. Except for I<sup>2</sup>L, bipolar circuits, in general, exhibit higher speeds than unipolar circuits at the cost of a somewhat smaller packing density and/or a more complex technology, which means that the production yield of bipolar circuits per unit area tends to be lower than that of unipolar circuits. For this reason the minimum gate count in bipolar VLSI circuits is often taken to be a factor of two lower than the gate count in unipolar VLSI circuits (5000 and 10000 respectively).

## 2.II. Comparison between bipolar and MOS-type circuits

To obtain an electrical comparison between bipolar and MOS-type circuits the propagation delay times and power delay products will be discussed.

As explained in Section 3.II, the first order average propagation delay times for bipolar and MOS circuits are

$$t_{\rm d\,bipolar} \approx \frac{(C_{\rm j} + C_{\rm w})\Delta V}{i} + \frac{W_{\rm B}^2}{2\mu kT/q} \tag{1}$$

$$t_{\rm dMOS} \approx \frac{C_{\rm j}(W) + C_{\rm w}(W)}{(W/L)\mu C_{\rm ox} V_{\rm T}} + \frac{2L^2}{\mu V_{\rm T}}$$

(2)

3

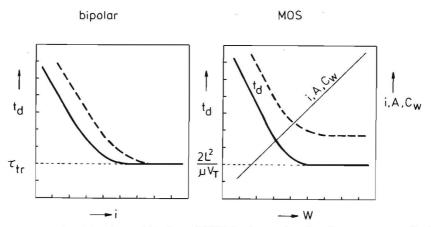

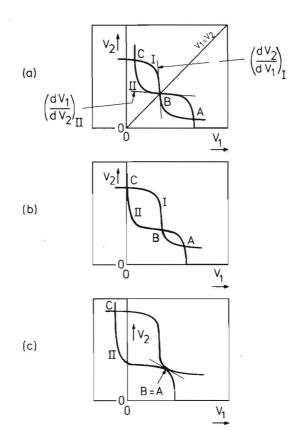

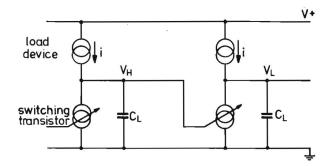

where  $C_j$  and  $C_w$  are junction and on-chip wiring capacitances,  $\Delta V$  the logic swing, *i* the current per gate,  $W_B$  the basewidth of the bipolar transistor, W the width of the MOS transistor, L the gate length of the MOS transistor,  $C_{ox}$  the gate oxide capacitance per unit square, and  $V_T$  the threshold voltage of the MOS enhancement driver transistor. Fig. 1 shows a graphical representation of (1) and (2). The essential difference between (1) and (2) is that in the bipolar case the current per gate i is easily increased (a factor of 10 for every 60 mV more base-emitter voltage at room temperature) without increasing the transistor size, due to the exponential characteristic of the transistor. This means that when no limiting effects occur due to series resistances, the bipolar propagation delay time can be minimized to the transit time (which is of the order of  $W_B^2/(2\mu kT/q)$  for a

Fig. 1. Propagation delay times of bipolar and MOS circuits as a function of current per gate (in the bipolar case) or transistor width (in the MOS case). The solid line is without on-chip wiring capacitance; the dashed line is with on-chip wiring capacitance  $C_w$ .

normal bipolar transistor) by increasing i.

As the first-order average propagation delay time in the MOS case is independent of the power supply voltage, the only way to increase the speed (and the current) is to increase the transistor W/L ratio as shown by (2), which means that W has to be increased in a given technology where L had already been minimized. Thus transistors with a larger minimum width have to be used, thereby increasing the packing density and causing larger junction capacitances and larger on-chip wiring capacitances (both  $C_j$  and  $C_w$ depend on W). This implies that it is impossible to improve the speed any further if  $C_w$ increases linearly with W [1], and if  $C_w$  increased more than linearly with W, the propagation delay time would even increase. MOS type of circuits are therefore less suitable for high speed VLSI [2].

In GaAs where the first-order mobility  $\mu$  (disregarding velocity saturation) is a factor of 5 higher than in silicon, smaller transistors can be used to obtain the same current. This gives a higher packing density and consequently a smaller  $C_w$ , and thus the speed may be about the same factor of 5 higher. The GaAs technology, however, is not yet considered mature enough for LSI and VLSI circuits and the advantages still cannot be utilized on an economical scale [3].

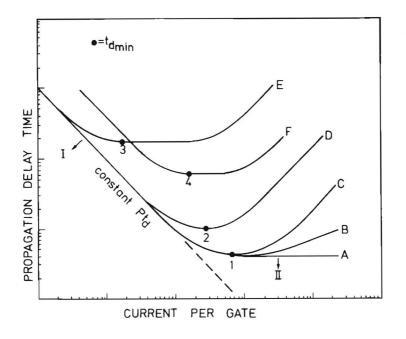

Note that Fig. 1 shows only qualitative first-order effects. The theoretical minimum propagation delay times are different for different types of transistors. In nonsaturated ECL circuits,  $\tau_{tr}$  of the normal operated n-p-n transistor can be as low as  $\tau_{tr} = W_B^2/(2\mu kT/q) = 20$  ps when the base width  $W_B$  is 0.3  $\mu$ m. In the I<sup>2</sup>L case where inverse operated n-p-n transistors are used  $\tau_{tr}$  can be as large as 10 ns. In ISL,  $\tau_{tr}$  is about 1.5 ns in the pn-isolated case and 250 ps in the oxide-isolated case. In MOS circuits with 3  $\mu$ m minimum gate length  $2L^2/\mu V_T$  is about 500 ps.

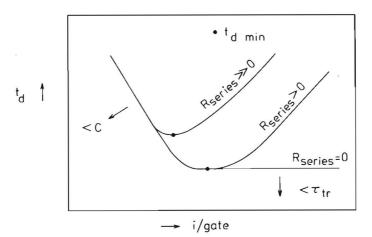

Another point to be made is that in practical bipolar circuits, including ISL, the theoretical minimum of the average propagation delay time is difficult to achieve due to series resistances (base series resistance, collector series resistance, Schottky diode series resistance) which limit peak currents which have to flow to charge and discharge capacitances (see Fig. 2). Also in MOS circuits the theoretical minimum of the propagation delay time is difficult to achieve due to the fact for instance that depletion loads in ED-logic do not behave as ideal current sources.

Fig. 2. Influence of series resistances on the propagation delay time of bipolar circuits.

So far only propagation delay times have been discussed. Another important figure of merit is the power-delay product  $P_{td} = iV^{+}t_{d}$  which would be  $V^{+}\Delta VC_{w}$ , if the on-chip wiring capacitances were dominant ( $V^{+}$  is the power supply voltage); see Section 3.II. For bipolar circuits the  $V^{+}\Delta V$  product can be minimized to 0.2 V<sup>2</sup> irrespective of transistor size. For MOS type of circuits the same value can be obtained, but this

makes only sense for scaled devices ( $L < 0.5 \ \mu$ m), otherwise the speed will be disappointingly low.

Thus the advantages of bipolar circuits over MOS circuits are that: a) optimum speed can be obtained with minimum size transistors (disregarding series resistances), b) small voltage swings are possible (due to the exponential characteristics), resulting in a relatively small speed degradation due to on-chip wiring capacitances, c)  $V^*$  and  $\Delta V$  can be minimized independently of transistor size.

In Integrated Schottky Logic (ISL) where minimum-size transistors are always used, the logic swing is as low as 200 mV, and using resistors as current sources instead of p-n-p transistors the power supply voltage is about 1.5 V, which means that the  $V^+\Delta V$  product is 0.3 V<sup>2</sup>; thus a low power-delay product is obtained (only 0.1 V<sup>2</sup> more than the minimum possible).

Note that in this sub-section (and in Section 3) bipolar and MOS gates are only compared for speed and power-delay product and not for many other important properties such as packing density, wiribility, suitability for dynamic storage etc.

For instance MOS circuits with polysilicon gates have 2½ effective interconnection layers when using 1 layer metal, whereas in bipolar circuits 2 layers metal are needed to obtain the same interconnect possibilities. Another point is for instance dynamic storage, which is extremely simple in MOS circuits and very difficult in bipolar circuits.

This all means that bipolar circuits may be faster (gate-wise), but that they miss a lot of convenient properties which are available in MOS circuits.

# 2.III. Logic circuits for high speed bipolar VLSI

Nowadays most medium-size chip packages do not allow a higher power dissipation than about 1 W, and therefore, for most VLSI circuits with more than 5000 gates per chip the maximum power dissipation per gate has to be smaller than 200  $\mu$ W.

Furthermore, with maximum chip areas of 25 mm<sup>2</sup>, packing densities better than 200 gates/mm<sup>2</sup> are required.

Section 3.VIII examines the question as to which logic circuit/technology combinations fulfil these requirements. Only the most important logic types such as LS,  $I^2L$ , STL, ISL, DTL, ECL, and NTL are considered.

The result of the comparison is that in oxide-isolated processes with 3  $\mu$ m minimum details, STL, ISL and I<sup>2</sup>L satisfy the VLSI requirements, with about 1 ns average propagation delay time for STL and ISL, and about 5 ns for I<sup>2</sup>L. ECL and DTL are VLSI candidates only in more sophisticated processes using polysilicon electrodes.

|                                                                           | pn – isolated<br>5 µm min. details - | oxide-isolated<br>3 µm min.details |

|---------------------------------------------------------------------------|--------------------------------------|------------------------------------|

| epithickness                                                              | 2.9 ± 0.3 µm                         | 1.2±0.05 µm                        |

| epithickness after<br>all processing steps                                | 2.4 ± 0.3 µm                         | 1.0 ±0.05 µm                       |

| <b>Se</b> pi                                                              | 0.3 Ωcm                              | 0.3 Ωcm                            |

| base × <sub>jB</sub><br>base sheet res                                    | 1.2 µm<br>200 גע                     | 0.5 µm<br>600 גע                   |

| emitter × <sub>jE</sub>                                                   | 0.8 jum                              | 0.25 µm                            |

| resistor × <sub>jR</sub><br>resistor sheet res.                           | 0.5 μm<br>2000 Ω/□                   | 0.5μm<br>2000 Ω/ロ                  |

| photoresist                                                               | neg./ contact<br>printing            | pos./optical<br>projection         |

| min. emitter<br>mask size                                                 | 5 × 8 µm²                            | 3×5 µm²                            |

| 1 <sup>st</sup> metal mask<br>width/spacing<br>2 <sup>nd</sup> metal mask | 5 µm/5 µm                            | 3 µm/5 µm                          |

| width/spacing                                                             | 10 µm / 14µm                         | m / 11 µm /5 µm                    |

| via's (mask)                                                              | 8 × 10 µm²                           | 5×7 µm <sup>2</sup>                |

| alignment<br>tolerance                                                    | 3 µm                                 | 1 µm                               |

Table 1. Most relevant process parameters of processes in which ISL has been made.

# 2.IV. Bipolar processes for ISL

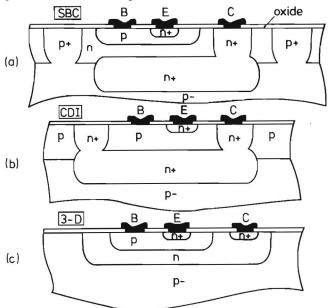

Section 3.IV-VII gives an extended survey of production and experimental processes for bipolar LSI and VLSI circuits. ISL has been made in existing production processes only. Initially, the pn-isolated SBC process (Standard Buried Collector) was used with a 3  $\mu$ m thick epitaxial layer and 5  $\mu$ m minimum dimensions; later an oxideisolated process was used with a 1.2  $\mu$ m thick epitaxial layer and 3  $\mu$ m minimum dimensions. Details of these processes are given in Section 8 and Section 10 respectively; table 1 lists the most important numbers.

In both processes Schottky diodes are made with PtNi-silicide (60% Pt and 40% Ni) with a barrier height of about 0.78 eV.

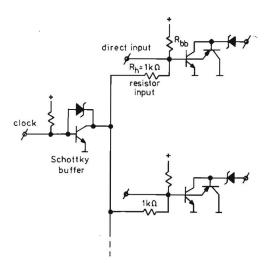

## 2.V. The original concept of ISL

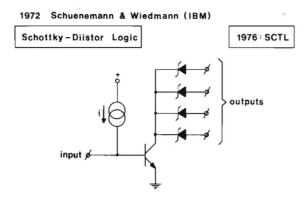

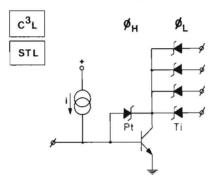

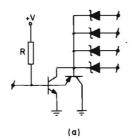

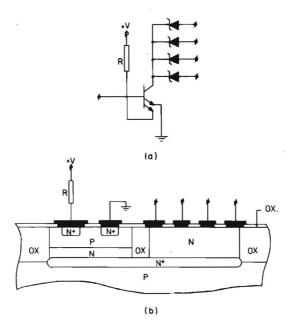

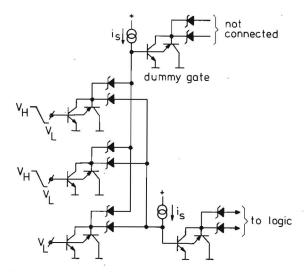

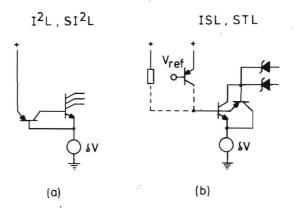

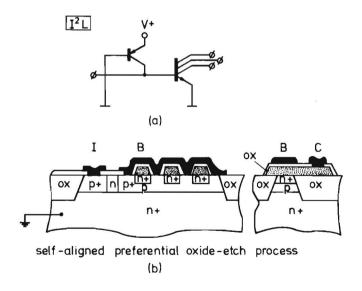

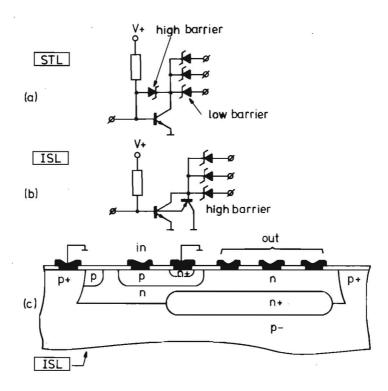

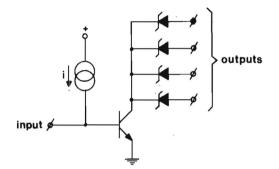

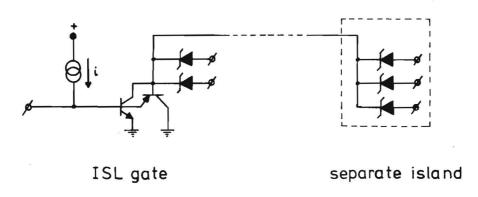

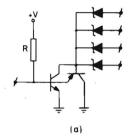

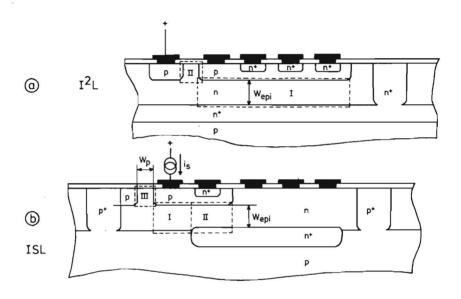

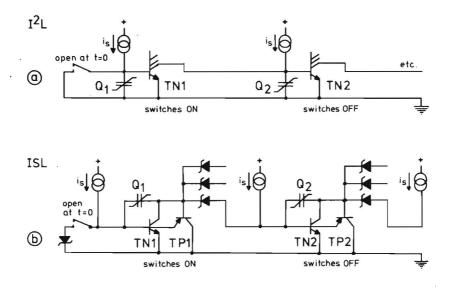

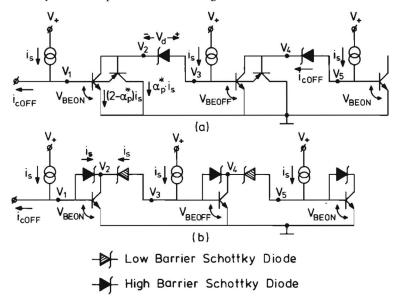

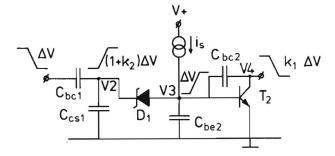

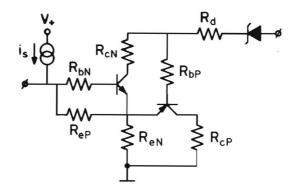

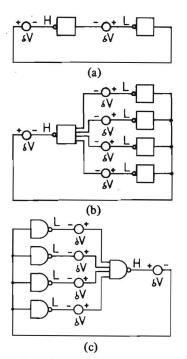

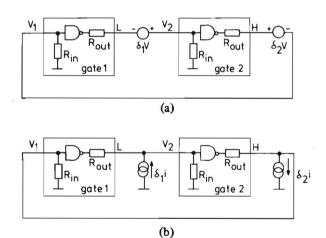

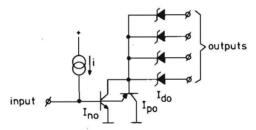

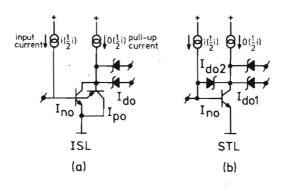

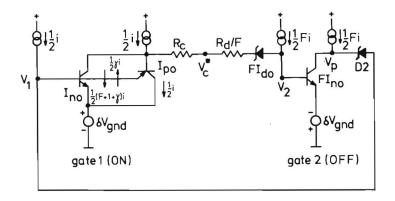

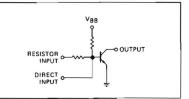

ISL was initiated to fill the gap between low-power Schottky TTL and I<sup>2</sup>L without changing the technological standard process, for those circuits where low-power Schottky TTL consumes too much power and takes up too much chip area, and when  $I^2L$  does not attain the required speed [4,5,6] (see Section 4). In fact, ISL is a compromise between Schottky-diistor logic [7] (also called Schottky Coupled Transistor Logic (SCTL) [8]) which is made in a process with one type of Schottky diode, and Schottky Transistor Logic [9] (also called Complementary Constant Current Logic  $(C^3L)$ [10]) which is made in a process with two types of Schottky diode. The electrical diagrams of Schottky-diistor logic, STL and ISL are shown in Fig. 3; all p-n-p transistors are used in the standard downwards mode. All these logic types are of the wired-AND type; they have one input and a multiple output. The disadvantage of Schottky-diistor logic is that it becomes heavily saturated which means that it is rather slow. STL, on the other hand, is Schottky clamped and consequently relatively fast, but has the disadvantage that the process in which it has to be made is much more complex due to the fact that two types of Schottky diodes have to be made with different barrier heights (a high barrier for the clamp diode and a low barrier for the output diodes) to obtain a reasonably large voltage swing.

In ISL the clamp action is provided by a p-n-p transistor (see Fig. 3); the n-p-n still goes into saturation, but as soon as the n-p-n base-collector junction is forward biased the superfluous base current is drained to ground by the p-n-p transistor which means that the n-p-n transistor goes less far into saturation.

The effectiveness of a p-n-p transistor as a fast clamp device depends mainly on the minority carrier storage in its base, hence the base width has to be small.

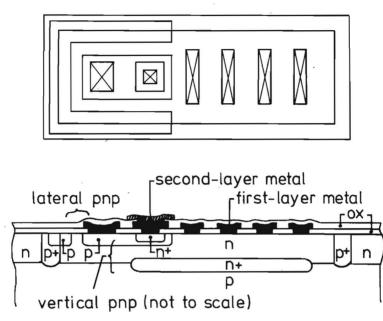

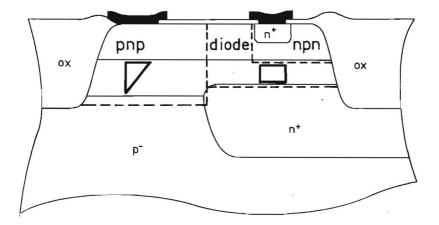

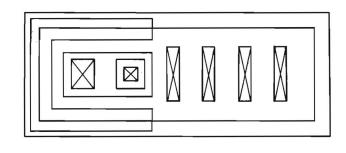

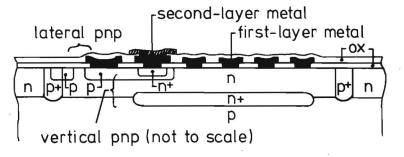

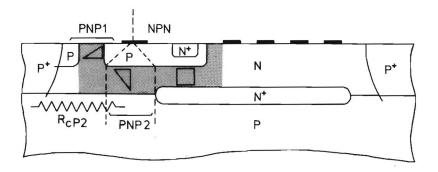

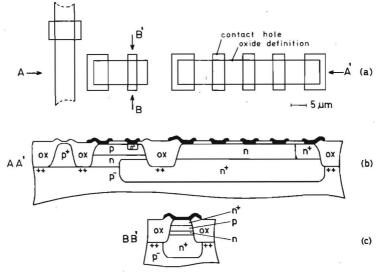

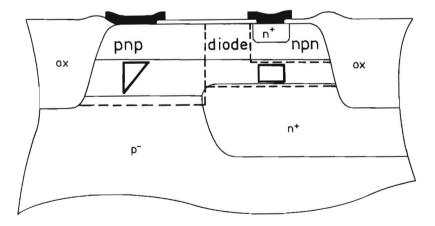

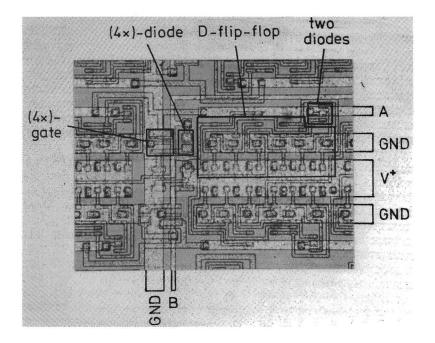

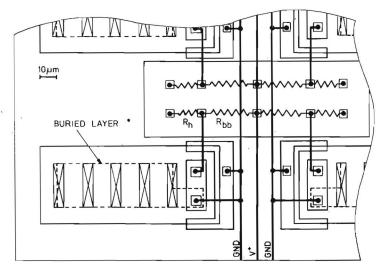

Fig. 4 shows a top view and cross section of an ISL gate made in a standard pnisolated process. A vertical clamp p-n-p is obtained by not extending the buried layer under the base-contact of the n-p-n transistor. The parasitic lateral p-n-p action to the

1975 Peltier (Motorola), Wiedmann&Berger (IBM)

Integrated Schottky Logic

Fig. 3. Circuit diagrams of Schottky-diistor logic or SCTL [7,8], STL or C<sup>3</sup>L [9,10], and ISL.

10 u

Fig. 4. Top view and cross-section of a pn-isolated ISL gate without current source; 5 µm minimum details are used.

isolation diffusion is inevitable in pn-isolated processes.

To reduce the minority carrier storage in these lateral areas, the lateral p-n-p base width is reduced by the application of a shallow isolation-diffusion overlapping p-ring at a minimum-detail distance around the p-base (5  $\mu$ m for instance).

The base thickness of the vertical p-n-p is determined by the thickness of the epitaxial layer; the thinner this epilayer, the faster the logic is.

A p-n-p clamp transistor has been proposed to control the saturation in an  $I^2L$  type of structure [11], but to implement a merged clamp p-n-p with an inverse operating n-p-n, requires a dramatic deviation from the standard process [11].

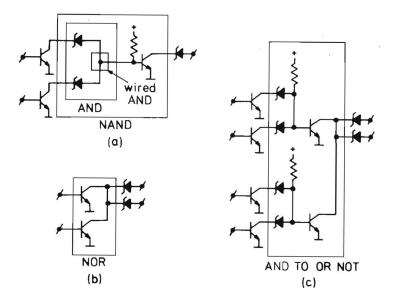

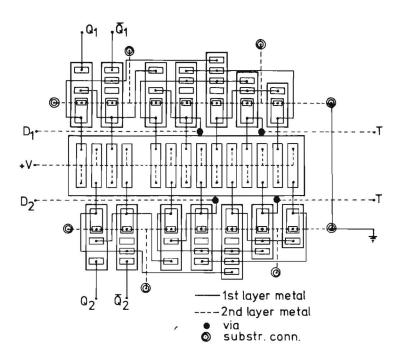

Although ISL is, in principle, a wired-AND type of gate (see Fig. 5(a)), the extra internal collector node (which does not exist in  $I^2L$ ) makes collector dotting possible to obtain NOR functions and also AND TO OR NOT functions (see Fig. 5(b,c)). Collector dotting is obtained either by placing more base areas in one collector island, or by interconnection of more collector islands with n<sup>+</sup> collector contacts and an interconnect wire.

Fig. 5. (a) Wired-AND construction to obtain AND and NAND functions, (b) collector dotting to obtain NOR functions, (c) combination of a and b to obtain AND TO OR NOT functions.

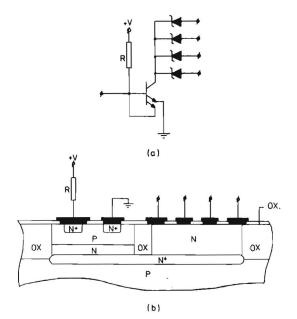

# 2.VI. Performance of pn-isolated ISL

As the n-p-n transistor in ISL is used in the normal (downward) mode, the current source cannot be merged with this transistor as in  $I^2L$  [12,13]. Either a separate transistor or a resistor in a separate island has to be made. This means that the packing density is about 30% lower than in I<sup>2</sup>L. The logic voltage swing is  $\Delta V = (kT/q) \ln(\alpha_{p-n-p}I_{d0}/I_{p0})$ , where  $I_{d0}$  and  $I_{p0}$  are the saturation currents of the Schottky diode and the p-n-p transistor respectively. In processes with an epilayer thickness of about 3 µm and PtNi-silicide diodes ( $\phi_B = 0.78$  eV) and using 5  $\mu$ m minimum details (see Fig. 4) a logic swing of 200 mV is obtained. With resistors as current sources, and washed emitters, a minimum average propagation delay time of 2.7 ns at 200 µA/gate is obtained (see Fig. 6). Despite a voltage swing which is about 500 mV smaller than that of  $I^2L$ , most of the ISL noise margins are larger than those of I<sup>2</sup>L. The main reasons, as explained in chapter 2.XV, are that the current source is a resistor instead of a saturated p-n-p transistor (this improves the power supply line and ground line noise margins) and that the current gain of the normal operating n-p-n is generally much higher than the current gain of the inverse operated n-p-n (this improves the parallel current noise margin). This makes the ISL a more "forgiving" circuit than I<sup>2</sup> L [4].

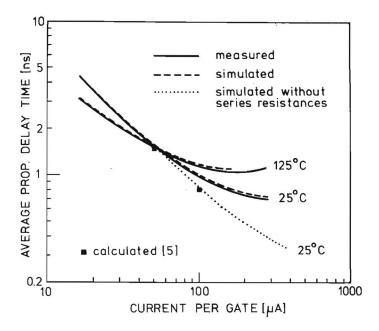

Fig. 6. Average propagation delay times of the ISL gate of Fig. 5. The epilayer thickness is 2.9  $\mu$ m; the current sources are ion-implanted resistors.

As the ISL gates are made in a standard buried collector process, they can easily be combined with  $I^2L$ , low-power Schottky TTL and ECL on the same chip. Even in analog processes with thicker epilayers, ISL has been demonstrated to have a 5 to 10 times better speed than  $I^2L$ .

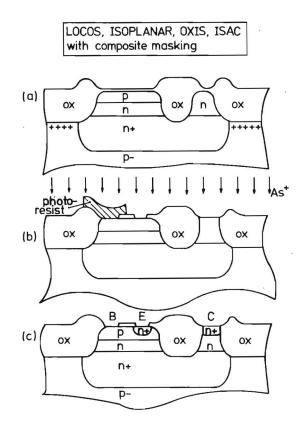

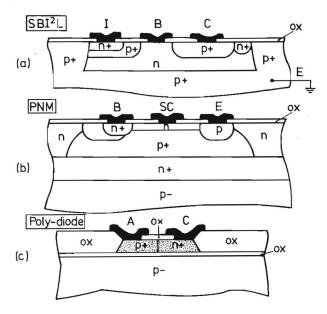

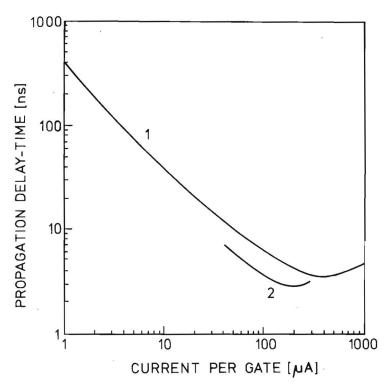

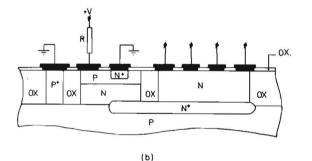

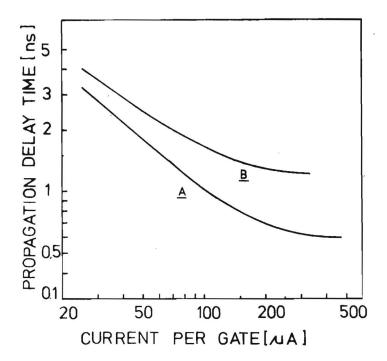

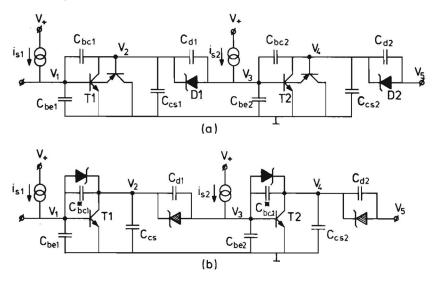

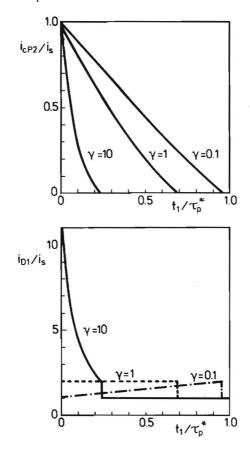

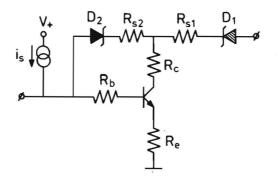

## 2.VII. Oxide-isolated ISL technologies

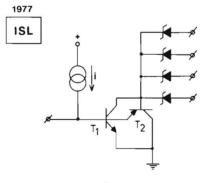

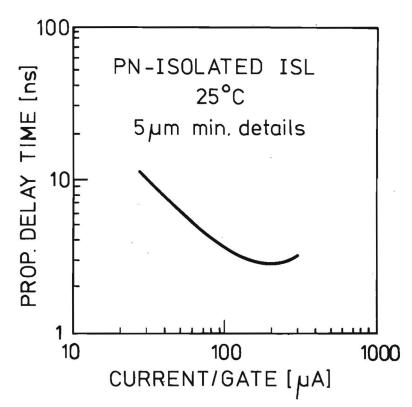

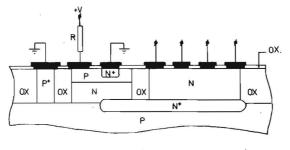

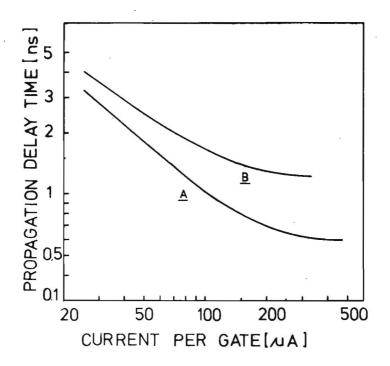

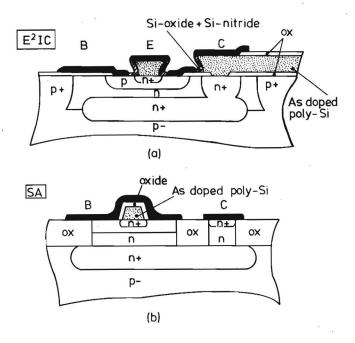

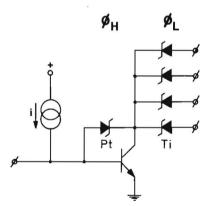

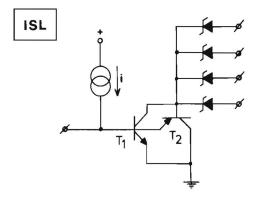

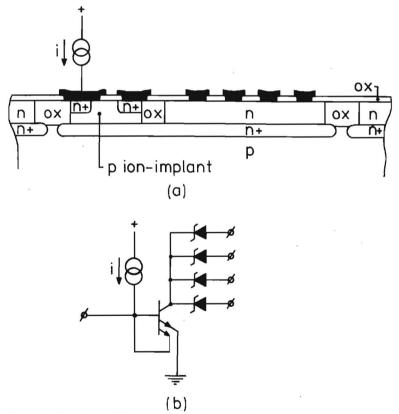

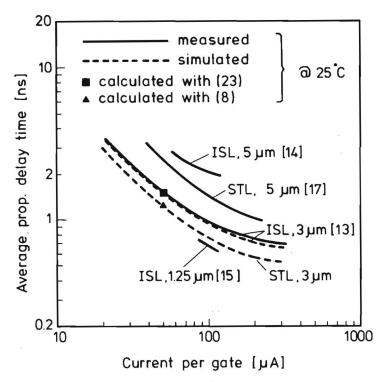

Using oxide isolation, ISL gates can be fabricated without the relatively slow lateral p-n-p transistor which is inevitable in pn-isolated processes. As shown in Section 5, the clamping action is provided either by a fast vertical p-n-p only, or a reverse operated n-p-n (see Fig. 7 and 8); a 1.2  $\mu$ m thick epilayer and 3  $\mu$ m min. dimensions are used. Fig. 9 shows  $t_{pd}$  as a function of current per gate for type A (vertical p-n-p clamp) and type B (reverse operated n-p-n clamp). Type A is the most successful one;  $t_{pd}$  is about 0.7 ns at a current level of 200  $\mu$ A/gate ( $t_{pd}D \approx 0.2$  pJ). The reason why type B is slower is due to the fact that the saturation current of the minimum size inverse n-p-n is about a factor of

Fig. 8. Oxide isolated ISL with reverse operated n-p-n clamp.

5 smaller than the saturation current of the vertical p-n-p. This means that the normal operated n-p-n becomes much more heavily saturated than with p-n-p clamping, causing much more hole storage in the n-epilayer underneath the base. The speed could be improved by increasing the size of the inverse n-p-n transistor, but the improvement may be small if the size of the total structure then needs to be increased (which would cause an increase in base-collector capacitance and an increase in island capacitance).

Using a small size vertical p-n-p clamp therefore ISL has been realized in a standard oxide-isolated process, featuring sub-nanosecond propagation delay times with sub-pico-joule speed-power products. This makes this type of logic very attractive for high speed VLSI. Oxide-isolated ISL has also been tested by others with 5  $\mu$ m details [14] and even 1.25  $\mu$ m details [15]; in the last case  $t_{pd} = 0.7$  ns at 100  $\mu$ A/gate was reported.

Fig. 9. Measured propagation delay times of oxide isolated ISL with vertical p-n-p clamp ( $\underline{A}$ ) and reverse operated n-p-n clamp ( $\underline{B}$ ).

### 2.VIII. Speed comparison of ISL and I<sup>2</sup>L

As already mentioned, the minimum average propagation delay time of ISL is a factor of 5 to 10 better than the speed which can be obtained with  $I^2L$  in the same process. This is explained in Section 6.

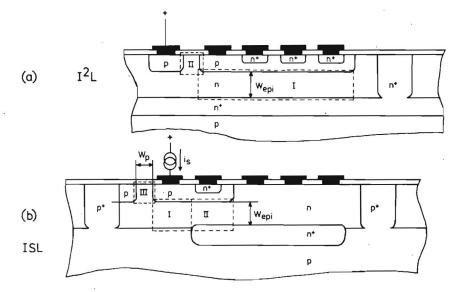

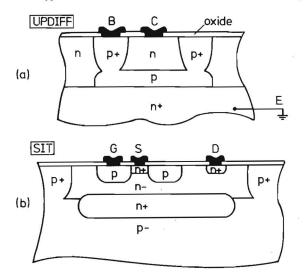

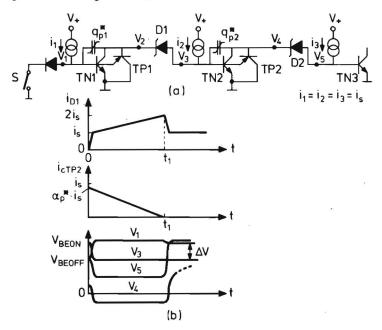

For comparison, ISL and  $I^2L$  gates are considered which are made in the same process with the same epilayer thickness and the same minimum dimensions, see Fig. 10.

Fig. 10. Cross-section of I<sup>2</sup>L (a) and ISL (b) made in the same pn-isolated process. Active charge will be found mainly in areas I and II (I<sup>2</sup>L) and I, II and III (ISL).

For small currents ISL will be faster than  $I^2L$  because of the smaller voltage swing (200 mV instead of 700 mV), whereas the junction capacitances are comparable.

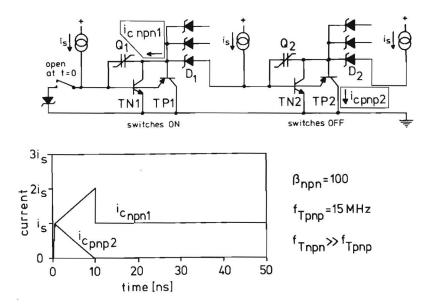

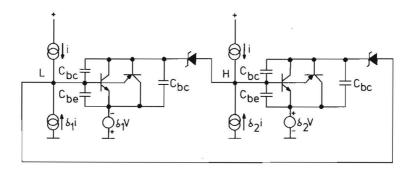

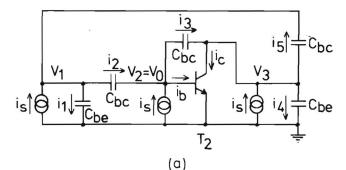

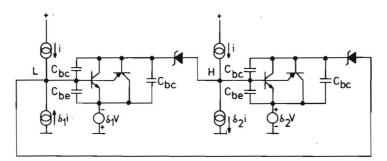

At high current levels, at maximum speed, the active charges dominate. It is characteristic of  $I^2L$  that the active charge is found mainly in the n-p-n emitter area (see Fig. 10(a)), whereas in ISL the active charge is found mainly in the n-p-n collector area (= p-n-p base) because of the saturation of the n-p-n (see Fig. 10(b)). These active charges can be represented by non-linear capacitances between base and emitter in  $I^2L$  and between base and collector in ISL (see fig. 11(a) and 12(a) respectively). As shown in Section 6, the ratio of the intrinsic current-independent average propagation delay times of  $I^2L$  and ISL is about  $2\sqrt{\beta_{upeff}} f_{T PNP} ISL/f_T NPN up I^2L$ .

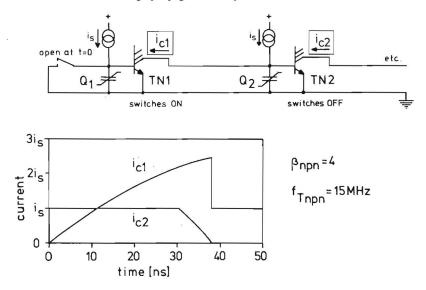

For processes where  $W_{epi}$  is 2  $\mu$ m,  $f_{T PNP ISL}$  and  $f_{T NPN up I^2L}$  are both about 15 MHz. Fig. 11(b) shows for this case the typical switching behaviour of  $I^2L$  when  $\beta_{up eff} = \beta = 4$  and  $f_{T NPN up I^2L} = 15$  MHz.

The transient behaviour of the currents illustrated is obtained with a computer simulation program. At t = 0 the switch is opened and TN1 starts to conduct. The collec-

tor cirrent of TN1 increases relatively slowly:  $i_{cl} = \beta i_{c1} [1 - \exp(-t2\pi f_T/\beta)]$ .

It takes a relatively long time to discharge  $Q_2$  due to the fact that TN2 is heavily saturated. After 30 ns TN2 is no longer saturated and it takes another 7 ns to completely switch OFF TN2. So the average propagation delay is 37/2 = 18.5 ns.

Fig. 11. Inverter chain made with I<sup>2</sup>L (a) and the behaviour of  $i_{c1}$  and  $i_{c2}$  as a function of time (b).

Fig. 12. Inverter chain made with ISL (a) and the behaviour of  $i_{cp-p_1}$  and  $i_{cp-p_2}$  as a function of time (b).

Fig. 12(b) shows the ISL case with  $f_{T PNP ISL} = 15$  MHz. We assume that

$f_{\rm T NPN} \gg f_{\rm T PNP}$ . In this case, shortly after t = 0, TN1 can sink any amount of current up to  $i_{\rm cmax} = \beta_{\rm n-p-n} i_{\rm s}$ . This maximum current will not be reached since the discharge path to remove  $Q_2$  goes through the fan-out diode D2 and is limited to  $i_{\rm s}$ .

This means that  $i_{c p-n-p2}$  decreases linearly  $(i_{c p-n-p2} = i_s (1-t2\pi f_{T PNP}))$  and  $i_{cn-p-n1}$  increases from  $i_s$  to  $2i_s$  with the same amount. The charge  $Q_2$  is thus removed in about 10 ns and so the average propagation delay time in this particular ISL-case is 5 ns (compare with 18.5 ns in the I<sup>2</sup>L case).

Measurements of  $I^2L$  and ISL made in the same process show about the same or an even larger factor in maximum speed, because in most cases  $f_{T NPN ISL} > f_{T NPN up I^2L}$ .

# 2.IX. Propagation delay time of I<sup>2</sup>L at low current levels

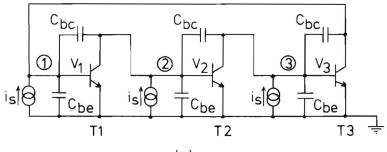

Before the propagation delay times of ISL and STL are calculated (for low and intermediate current levels), first the propagation delay time  $\overline{o}f I^2L$  at low current levels is calculated, because with its simple electrical diagram it gives a convenient introduction to the more complicated ISL/STL case.

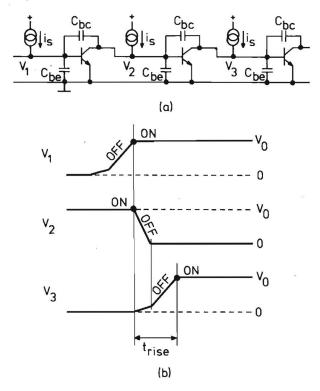

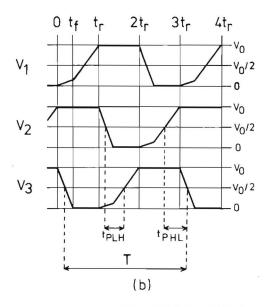

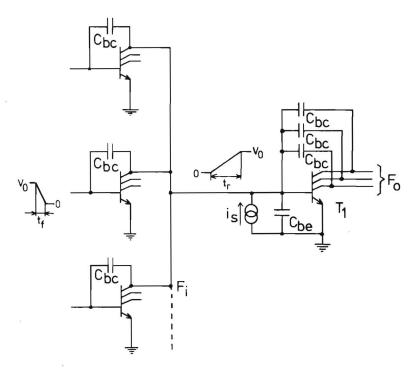

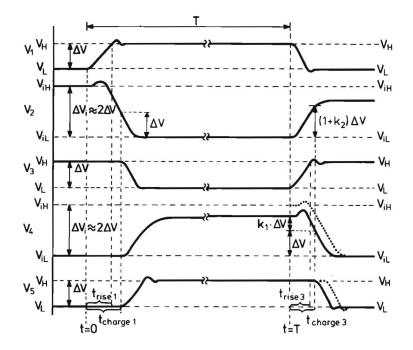

As shown in Section 7, the calculation of the  $I^2L$  case is relatively simple due to the low number of electrical nodes, see Fig. 13(a). For the calculation the following simplification is introduced: the transistor is assumed to be ON as soon as  $V_{be}$  reaches it maximum value  $V_{bemax} = V_0$ , and OFF when  $V_{be} < V_0$  (see Fig. 13(b)). This simplification is justified by the exponential current/voltage characteristic of the transistor, and also verified by computer simulations. It implies that  $V_3$  and  $V_5$  start to decrease and increase respectively at the same time when  $V_1$  reaches  $V_0$ ; this means that the average propagation delay time is equal to  $t_{rise}/2$  when  $t_{rise} > t_{fall}$  (see Fig. 13(b)). It is shown in Section 7 that  $t_{rise} > t_{fall}$  in a 3-stage ring oscillator when  $\beta_{eff} > 2$  and that  $t_{rise}$  is equal to  $(3C_{bc} + C_{be})V_0/i_s$ . In ring oscillators which have more than 3 stages  $\beta_{eff}$  is permitted to be somewhat lower than 2; with an infinite number of stages  $\beta_{eff}$  can be very close to 1.

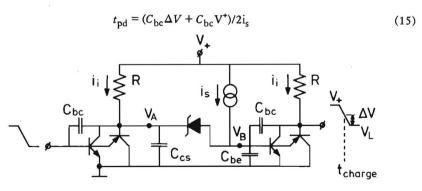

#### 2.X. Propagation delay times of ISL and STL at low and intermediate current levels

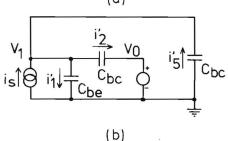

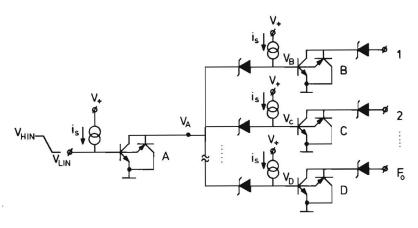

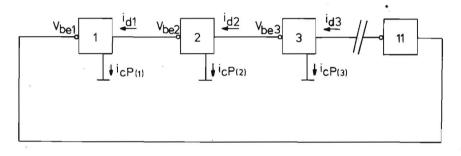

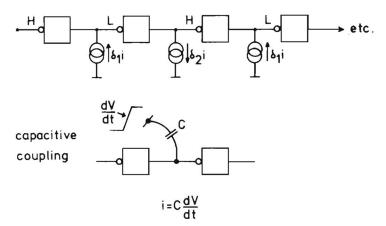

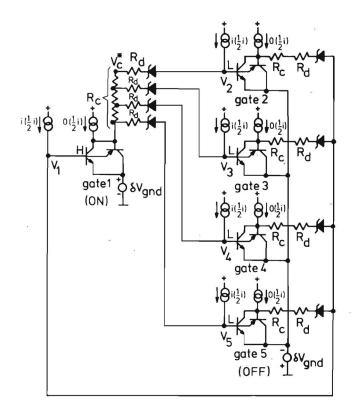

The calculation of the propagation delay times of ISL and STL at low current levels is more difficult than of  $I^2L$  due to the fact that ISL and STL have more electrical nodes than  $I^2L$  (compare Fig. 14 with Fig. 13(a)).

As shown in Section 8, the voltage swing at the internal nodes  $V_2$ ,  $V_4$ , etc. is twice as large as the voltage swing at the input/output nodes  $V_1$ ,  $V_3$ ,  $V_5$ , etc.

Here the propagation delay time is not determined only by  $t_{rise}$  of the input node, because  $V_5$  does not start to rise immediately after  $V_1$  has reched  $V_{bemax}$ , due to the fact that the internal node  $V_2$  first has to be discharged sufficiently to forward biase D1 and to switch OFF T2 ( $V_5$  starts to rise when  $V_3 < V_{bemax}$ ). The average propagation

Fig. 14. Chain of ISL inverters.

delay time is now determined as  $t_{charge}/2$  where  $t_{charge}$  is  $t_{rise}$  plus the times it takes to decrease the voltage of the next internal node to switch OFF the subsequent n-p-n transistor. As the internal node voltages do not reach their eventual DC-level, an exact expression for  $t_{charge}$  is difficult to derive. With empirical factors a reasonable approximation is obtained for instance for a 21-stage ring oscillator:

$t_{\text{charge}} = (4.0 C_{\text{bc}} + 1.3 C_{\text{cs}} + C_{\text{be}}) \Delta V/i_{\text{s}}$ , where  $\Delta V$  is the voltage swing.

As shown in Section 8, the average propagation delay times of ISL and STL are very similar at low current levels; at intermediate current levels, the intrinsic average propagation delay time of ISL being about  $\alpha^* \tau_p^*/2$  has to be added in the ISL case only ( $\alpha^*$  is the effective  $\alpha$  of the p-n-p transistor;  $\tau_p^*$  is the effective forward transit time of the p-n-p with the active charge stored in the n-p-n-collector added to the charge stored in the p-n-p base). At high current levels the propagation delay times of both ISL and STL are increased by series resistance effects. It is shown by calculation and measurements that, when compared in pn-isolated processes with 3  $\mu$ m epilayer, the speed difference, at intermediate and high current levels between ISL and STL can be quite large due to the relatively high value of  $\tau_p^*$ .

This high value of  $\tau_p^*$  (1.5 ns) is caused both by the relatively thick epilayer and by the presence of the relatively slow lateral p-n-p. In oxide isolated processes with a thinner epilayer,  $\tau_p^*$  is much smaller (250 ps), also because the lateral p-n-p, which is inevitable in pn-isolated processes, is fully eliminated. In an oxide isolated process with 3  $\mu$ m minimum details  $t_{pd}$  ISL and  $t_{pd}$  STL are about 0.95 ns and 0.75 ns respectively at 100  $\mu$ A/gate.

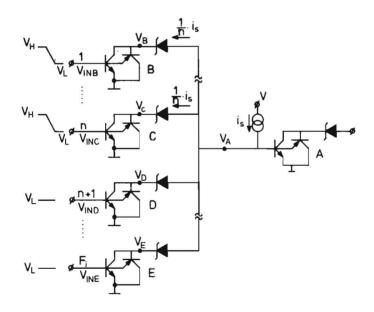

#### 2.XI. Fan-in and Fan-out aspects of ISL and STL

Both ISL and STL suffer from speed degradation due to fan-in. Fan-out, in general, has a speeding-up effect. In real logic circuits combinations always occur, and thus that speed degradation due to fan-in may be compensated or partly compensated by speed improvement due to fan-out. Nevertheless, critical paths are always found where speed degradation due to fan-in is dominant, so this determines the worst case situation. Fig. 15 shows the effect. Here the fan-in is  $F_i$ , and n gates switch OFF simultaneously. Now the current source  $i_s$  has to charge more than one base-collector capacitance ( $C_{be}$ ) and island capacitance ( $C_{cs}$ ). In Section 8 expressions are derived for  $t_{pd}$  where this fan-in effect is

Fig. 15. ISL situation with fan-in > 1. The current source has now to charge more capacitance if n input gates switch OFF simultaneously.

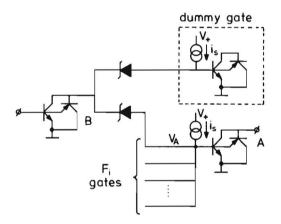

included. Measures of obtaining delay times that are independent of fan-in are also discussed. One of them is to use dummy gates as shown in Fig. 16. Here the speed improvement of fan-out is used to compensate a speed degradation of fan-in.

Fig. 16. A dummy gate is used to compensate the speed degradation due to fan-in.

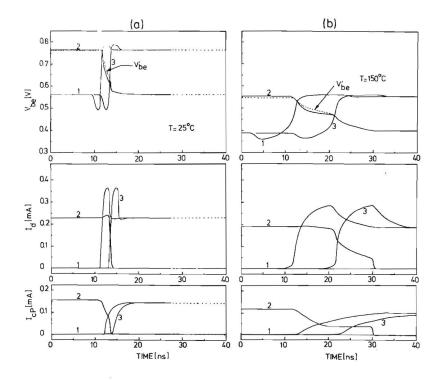

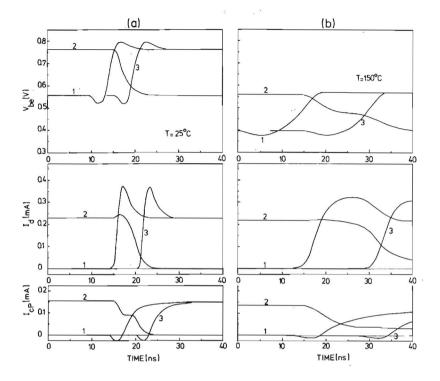

## 2.XII. Performance, temperature behaviour and first-order modeling of ISL

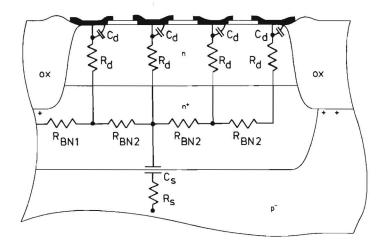

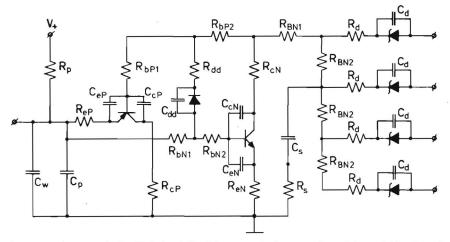

So far analytical expressions for the average propagation delay time have been derived, where series resistances and non-linearities of capacitances have been ignored. With an appropriate model and a circuit simulation program the more refined behaviour of the gate can be studied.

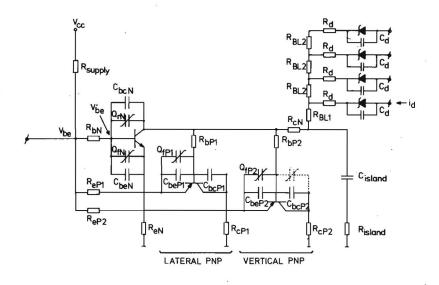

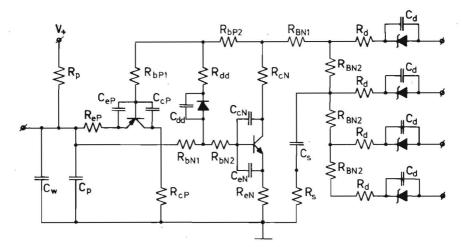

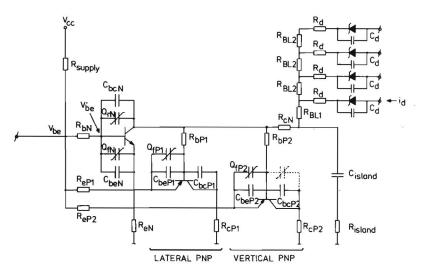

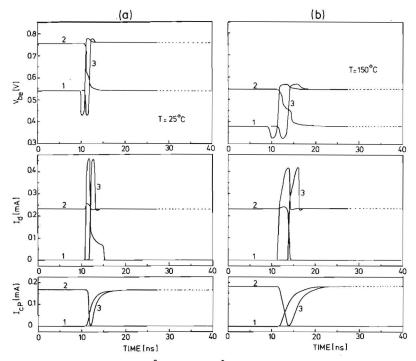

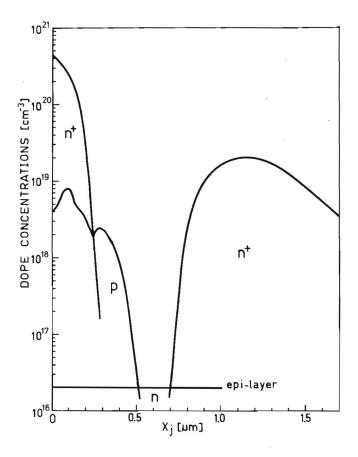

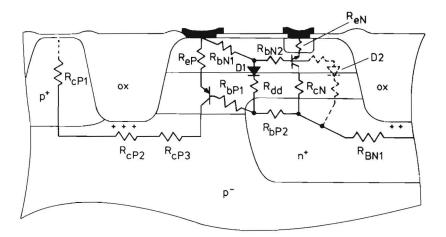

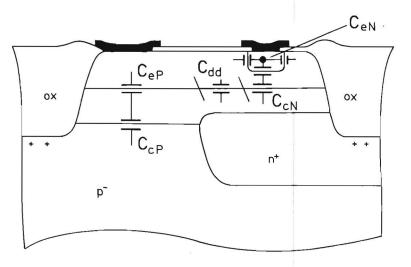

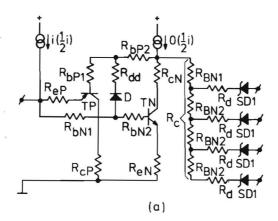

Fig. 17 shows a complete model of pn-isolated ISL, including all series resistances, junction capacitances and non-linear diffusion capacitances (minority carrier storage). The p-n-p is split into two parts, the lateral and the vertical one. Fig. 18 shows a to-scale cross section of the lateral p-n-p, the vertical p-n-p and n-p-n transistors. The depletion layers and hole distributions are indicated. Hole storage is found in three regions: in the base of the lateral p-n-p, in the base of the vertical p-n-p and in the collector of the n-p-n. The storage is calculated from all junction depths, and forward and reverse transit times for the n-p-n, and both p-n-p's are derived. Beta's of transistors are measured and capacitances are measured and/or calculated. In Section 9 it is shown, both by measurements and simulations, that the voltage swing decreases with increasing temperature due to the different temperature coefficients of the base-emitter voltage of the combined p-n-p's and of the anode-cathode voltage of the Schottky diodes. At room temperature the voltage swing is about 200 mV; at  $150^{\circ}$ C the swing is reduced to about 150 mV.

Fig. 17. Complete model of pn-isolated ISL.

Fig. 18. To-scale cross-section of a typical pn-isolated ISL gate. Minority carrier storage is indicated.

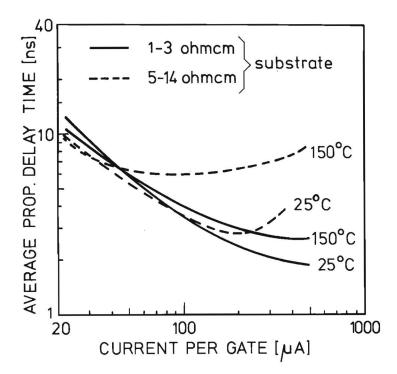

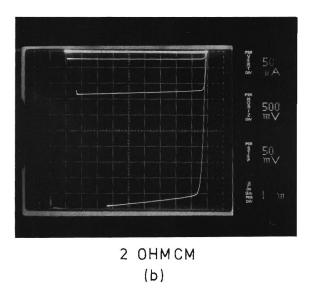

It is further evident from measurement that the vertical p-n-p has a very large collector series-resistance of 8 k $\Omega$  at room temperature when ISL is processed in the original low-power Schottky TTL process with a substrate resistivity of 5-14  $\Omega$ ·cm. Moreover, this resitance has a very high temperature coefficient which means that the series resistance increases to 16 k $\Omega$  at 150°C. The consequence is that, already at inter-

mediate current levels, the vertical p-n-p goes into saturation, causing a dramatic increase in the propagation delay time (see Fig. 19). The only way to get rid of this effect is to decrease the resistivity of the substrate below 5  $\Omega$  • cm at the cost of higher island capacitance of the n-p-n. Using the higher doped substrate (called ISL process) therefore the average propagation delay time at low current levels will be somewhat higher than in the LS-process, but the minimum  $t_{pd}$  is much lower, due to the elimination of the saturation of the vertical p-n-p (see Fig. 19). The intrinsic delay time being  $\tau_p^*/2$  is 750 ps. As explained in Section 9, all results are obtained with minimum design rules of 5  $\mu$ m causing a lateral p-n-p base width of 2.5  $\mu$ m. It may be asked whether a similar performance with a similar delay time could be obtained with a lateral p-n-p only. Of course this would be possible, but then the base width of the lateral p-n-p would have to be 0.7  $\mu$ m, which means that instead of 5  $\mu$ m, 2.8  $\mu$ m minimum details would have to be used in the same process. However, for standard production lines this value is much too small.

Fig. 19. Average propagation delay times of ISL made on a 5-14  $\Omega$ \*cm substrate (dashed lines) and on a 1-3  $\Omega$ \*cm substrate (solid lines).

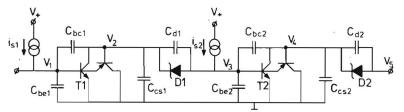

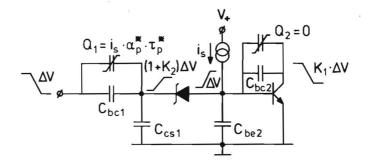

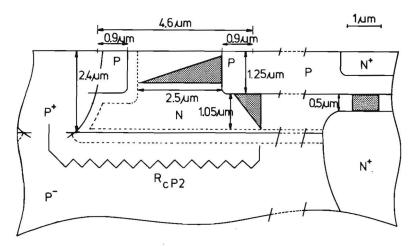

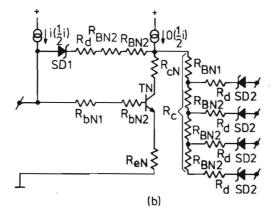

# 2.XIII. First-order modeling of oxide-isolated ISL

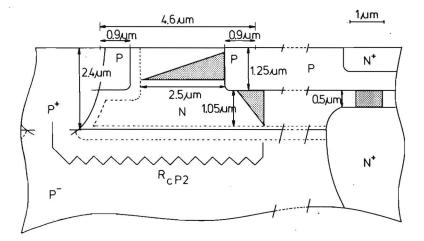

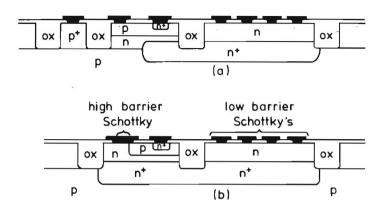

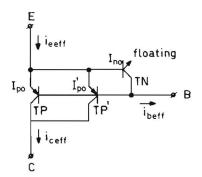

Oxide-isolated ISL, in the p-n-p clamped version, can be modeled in a similar way to pn-isolated ISL. As the lateral p-n-p does not exist, the most simple model would contain only one n-p-n transistor and one p-n-p transistor to model the merged n-p-n/p-n-p structure. However, in oxide isolated processes with a thin epilayer, a very shallow base diffusion (0.5  $\mu$ m) and a very shallow emitter (0.25  $\mu$ m), the base series resistance tends to be very high, especially in cases where the emitter is oxide-walled on two sides. This causes a relatively large voltage drop across this resistance and the base collector junction thus injects more holes outside the intrinsic n-p-n region than inside the intrinsic n-p-n region when the transistor goes into saturation. As a first-order approximation all hole injection is modeled by a diode, and the hole storage under the n-p-n is then assumed to occur as a result of lateral flow of holes (see Fig. 20). Fig. 21 shows the complete model derived in Section 10. All parameters for this model are obtained from measurements and calculations. Due to the p<sup>+</sup> channel stop in the process, the collector series resistance of the clamp p-n-p is relatively small (~ 1.5 k $\Omega$ ), which means that low doped substrates can be used. It is shown that, already at 100  $\mu$ A/gate, series resistances affect the propagation delay time seriously. Without series resistances  $t_{pd}$  would have been 0.8 ns instead of the measured value of 1 ns (at room temperature). Simulations have shown that the relatively high base-series-resistance of the n-p-n causes the largest speed degradation. Special attention is paid to all temperature coefficients of the device parameters, to obtain a good agreement with the measurements in the temperature range from 25°C to 125°C.

Fig. 20. Subdivision of the merged transistor structure in oxide-isolated ISL into a p-n-p, a diode and an n-p-n transistor. The hole storage under the base of the saturated n-p-n is associated with the diode. Hole storage is indicated for the p-n-p (triangle) and diode (box).

Fig. 21. Complete model of p-n-p clamped oxide-isolated ISL.

#### 2.XIV. Static noise margins of logic circuits

The noise margins of logic circuits are often the subject of confusion because there are different types of noise, and the worst case situations depend on fan-in, fan-out and the way the noise sources are applied.

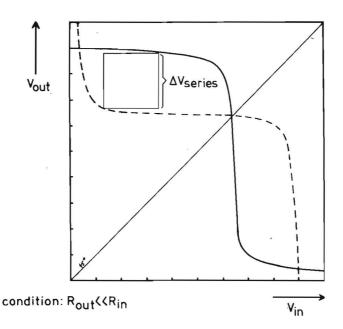

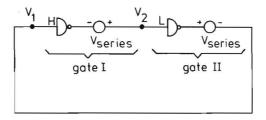

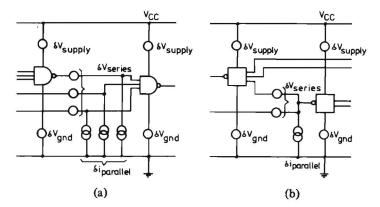

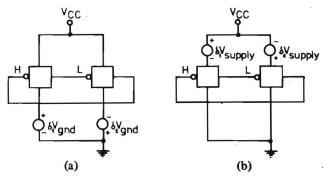

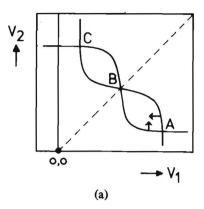

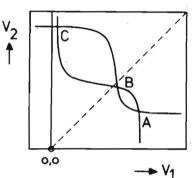

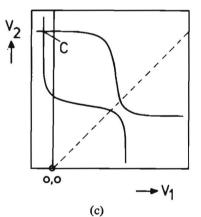

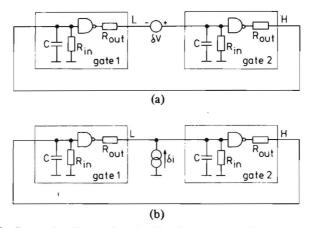

In Section 11 it is shown that four basic noise sources can be considered: series--voltage noise ( $\delta V_{\text{series}}$ ), parallel-current noise ( $\delta i$ ), voltage noise at the ground line ( $\delta V_{\text{gnd}}$ ) and voltage noise at the power-supply line ( $\delta V_{\text{supply}}$ ). When identical noise sources of opposite sign in the even and odd stages of an infinitely long chain put this chain on the very edge of switching to the wrong state, the amount of noise is considered the worst case noise margin  $\Delta$  ( $\Delta = \delta_{\text{max}}$ ). Instead of an infinitely long chain, a flip-flop (made with two inverters) can also provide the same result [16]. When the often disregarded condition that the output impedance of a gate is very much smaller than its input impedance ( $R_{\text{out}} \ll R_{\text{in}}$ ) is satisfied,  $\Delta V_{\text{series}}$  can be found using the maximum square method of the voltage transfer characteristics of the logic gate [16]; see Fig. 22.

To explain what happens in a flip-flop, Fig. 23 shows series voltage noise in a fan-in = fan-out = 1 flip-flop. It is assumed that  $R_{out} \ll R_{in}$ . When the noise sources are incorporated in gate 1 and gate 2, overall transfer characteristics can be obtained (for gate I and gate II respectively). Fig. 24(a) shows the two transfer characteristics when

$\delta V_{\text{series}} = 0$ . There are three states: two stable states where the small signal voltage loopgain  $A^* = (dV_2/dV_1)_I \cdot (dV_1/dV_2)_{II}$  is smaller than 1 (at cross points A and C) and a metastable state where  $A^* > 1$  (at cross point B). Let us assume that the flip-flop is in the stable state A and the noise amplitude starts to increase. In Fig. 24(b) the intermediate

Fig. 22. Determination of the worst-case series voltage noise margin  $\Delta V_{\text{series}}$  of an inverting gate, when  $R_{\text{out}} \ll R_{\text{in}}$ , by mirroring the voltage transfer characteristic and by finding the maximum square which fits between the characteristics [16].

Fig. 23. Flip-flop built up with two identical gates, disturbed by series voltage noise sources  $\delta V_{series}$ .

situation is shown where  $0 < \delta V_{series} < \Delta V_{series}$ ; the transfer characteristics are shifted but the flip-flop still remains at point A (at this point the loop gain has increased but is still smaller than 1). In Fig. 24(c) the noise margin  $\Delta V_{series}$  is reached; points A and B merge together (B = A) and at this point the loop gain is exactly 1. When  $\delta V_{series}$  is made larger than  $\Delta V_{series}$  the flip-flop switches to state C.

In cases where  $R_{out}$  is not much smaller than  $R_{in}$ , the voltage transfer characteristics have no relevance any more, because the output voltage depends now both on  $R_{out}$

Fig. 24. Transfer characteristics of the gates I and II of Fig. 23 for different values of  $\delta V_{\text{series}}$ ; (a)  $\delta V_{\text{series}} = 0$ , (b)  $0 < \delta V_{\text{series}} < \Delta V_{\text{series}}$  and (c)  $\delta V_{\text{series}} = \Delta V_{\text{series}}$ . In the last case the small signal voltage loop gain is 1.

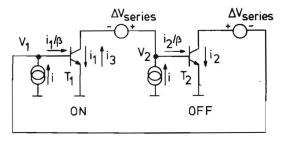

and  $R_{in}$ . In this case the noise margin can be found as the amount of noise which has to be applied to achieve a situation in which both small signal voltage and small signal current loopgains are equal to 1. This method is explained in Section 12 [17] where, as an example,  $\Delta V_{series}$  is calculated for  $I^2 L$  (fan-in = fan-out = 1).

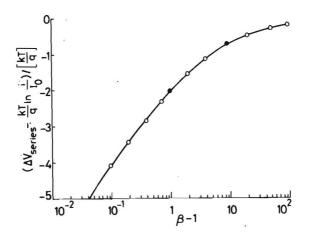

As a reaction to [17] Seevinck showed [18] that instead of a careful examination of the small signal loops and of assuming that current loopgain and voltage loopgain are 1, it is possible to calculate instead the condition for which the Jacobian of the complete set of Kirchoff equations is zero. This provides a more mathematical approach, but physically it is exactly the same, so both methods deliver exactly the same value for a particular noise margin. Only simple mathematical results are obtained when series resistances are ignored.  $I^2L$ ,  $SI^2L$ , ISL and STL circuits are then translinear circuits [19], and the noise margins are current independent.

When calculations are too difficult (which certainly is the case when all series resistances are included), computer simulations have to be carried out.

The best way is to carry out quasi-static transient simulations by increasing the noise sources slowly compared with the switching speed of the flip-flop, and detect the noise amplitude at which the flip-flop switches to the wrong state.

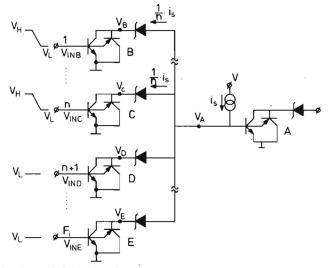

# 2.XV. Static noise margins of ISL, STL, I<sup>2</sup>L and SI<sup>2</sup>L

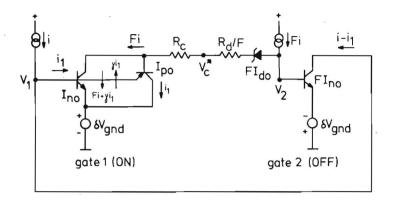

### A. ISL and STL

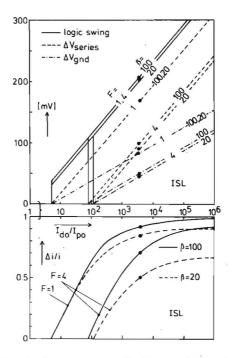

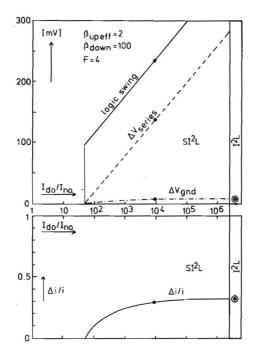

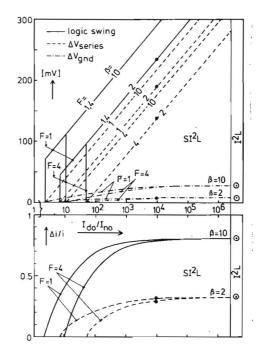

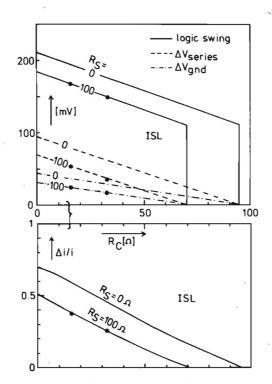

Fig. 25 shows the logic swing and the worst case room temperature static noise margins (simulated) of pn-isolated ISL with  $F_i = F_o = 4$ ,  $\beta_{fN} = 20$  and  $\alpha_p = 0.9$ . The results are obtained with an asymmetric flip-flop (see Section 11). The figure shows the logic swing,  $\Delta V_{series}$ ,  $\Delta V_{gnd}$  and  $\Delta i/i$  as a function of  $I_{do}/I_{po}$ . Stable flip-flop operation starts when  $I_{do}/I_{po} > 120$ ; the logic swing increases with increasing  $I_{do}/I_{po}$ .

Fig. 26 shows the same as Fig. 25, but this time for more parameter values ( $\beta_{\rm fN} = 20$  and 100,  $F_{\rm i} = F_{\rm o} = 1$  and 4) [20]. Measurements have been done for  $I_{\rm do}/I_{\rm po} = 4.10^3$ ; and they coincide with the simulations. As shown by Fig. 26,  $\Delta V_{\rm series}$  is about 100 mV

Fig. 25. Logic swing and worst-case room temperature static noise margins (simulated) of pn-isolated ISL with  $F_i = F_o = 4$ ,  $\beta_{\rm fN} = 20$  and  $\alpha_p = 0.9$  as a function of  $I_{\rm do}/I_{\rm po}$ .

Fig. 26. As Fig. 25, but also for the parameters  $F_i = F_o = 1$  and 4, and  $\beta_{fN} = 20$  and 100.

Fig. 27. Logic swing and worst-case room temperature static noise margins (simulated) of STL as a function of  $I_{do1}/I_{do2}$ .

smaller than the logic swing;  $\Delta V_{gnd}$  is about 50 mV smaller than half of the logic swing;  $\Delta i/i$  increases to  $(\beta_{fN} - F)/(\beta_{fN} + F)$  for large values of  $I_{do}/I_{po}$ . Fig. 27 shows the logic swing and noise margins of STL [20]. The curves are very similar to those of ISL; along the abscissa is  $I_{do1}/I_{do2}$  instead of  $I_{do}/I_{po}$ .

# B. $SI^2L$ and $I^2L$

Fig. 28 shows the logic swing,  $\Delta V_{\text{series}}$ ,  $\Delta V_{\text{gnd}}$  and  $\Delta i/i$  for  $\text{SI}^2 \text{L}$  [21] and  $\text{I}^2 \text{L}$  for the case where  $\beta_{\text{up}}$  eff = 2,  $\beta_{\text{down}}$  = 100 and  $F_i = F_o = 4$  at room temperature [20]. Along the abscissa are the saturation currents  $I_{\text{do}}/I_{\text{no}}$  for  $\text{SI}^2 \text{L}$ , where  $I_{\text{do}}$  is the saturation current of the Schottky diode and  $I_{\text{no}}$  the saturation current of the inverse operated n-p-n. A saturated p-n-p current source is used both for  $\text{SI}^2 \text{L}$  and  $\text{I}^2 \text{L}$ . The voltage swing and  $\Delta V_{\text{series}}$  of  $\text{I}^2 \text{L}$  are not indicated in Fig. 28 because those values (~ 700 mV and ~ 600 mV respectively) are outside the scale of this figure. Fig. 29 also shows  $F_i = F_o = 1$  and 4, and  $\beta_{\text{up}}$  eff = 2 and 10.

It has been suggested in the literature [12,22] that  $\Delta V_{\text{series}}$  would be equal to  $(kT/q)\ln\beta_{\text{up eff}}$ ; this is not true however.

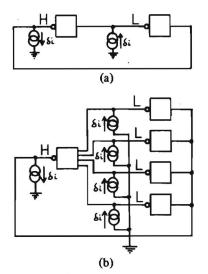

The ground line noise margin  $\Delta V_{\text{gnd}}$  is rather small due to the fact that the p-n-p current sources have their bases connected to ground, which implies that the current

Fig. 28. Logic swing and worst-case room temperature static noise margins (simulated) of SI<sup>2</sup>L and I<sup>2</sup>L for the case where  $\beta_{up}$  eff = 2,  $\beta_{down}$  = 100, and  $F_i = F_o$  = 4. The voltage swing and  $\Delta V_{series}$  of I<sup>2</sup>L (~ 700 mV and ~ 600 mV respectively) are outside the scale of this figure.

Fig. 29. As Fig. 28, but also for the parameters  $F_i = F_o = 1$  and 4, and  $\beta_{up}$  eff = 2 and 10.

Fig. 30. Ground line voltage noise in SI<sup>2</sup>L and I<sup>2</sup>L (a) and in ISL and STL (b). As SI<sup>2</sup>L and I<sup>2</sup>L have a p-n-p current source which is exponentially modulated by  $\delta V_{gnd}$ ,  $\Delta V_{gnd}$  is much smaller than in ISL and STL.

sources are exponentially modulated by  $\delta V_{gnd}$  (see Fig. 30(a)). In ISL and STL this modulation is not very effective (see Fig. 30(b)), so  $\Delta V_{gnd}$  and also  $\Delta V_{supply}$  will be essentially higher for ISL and STL.

For I<sup>2</sup>L,  $\Delta V_{\text{gnd}}$  is equal to ½  $(kT/q)\ln\beta_{\text{up eff}}$ , which is half the value given in [12] and [22].

The relative parallel current noise margin  $\Delta i/i$  increases with increasing voltage swing to a maximum value of  $\Delta i/i = (\beta_{up eff} - 1)/(\beta_{up eff} + 1)$ .

No separate computer simulations have been done to determine  $\Delta V_{supply}$ , because this value can directly be calculated from  $\Delta i/i$  as the power supply is only connected to the emitter of the p-n-p. Calculation shows that  $\Delta V_{supply} \approx (kT/q)\ln(1 + \Delta i/i)$ , which is 5 mV for  $\Delta i/i = 0.2$  for instance.

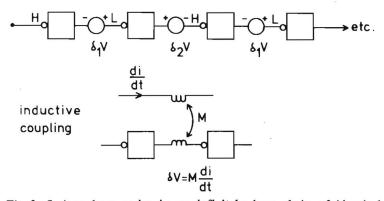

# 2.XVI. Dynamic noise margins of logic circuits

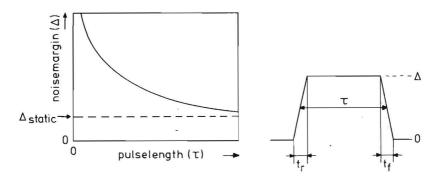

The static noise margins indicate the maximum DC noise amplitudes that can be withstood by the logic. This means that the noise may be present for an infinitely long time without bringing gates into the wrong state.

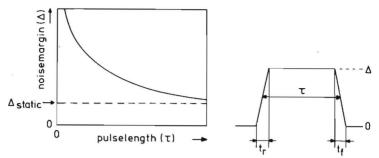

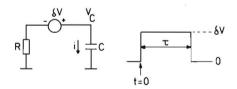

It is very well known that if the noise is present in pulse form, the noise amplitudes are allowed to be higher than the static margins, without affecting the proper logic states. Fig. 31 shows this phenomenon. For very long pulses the situation is quasi-static and the margins are determined by the static worst-case margins  $\Delta_{\text{static}}$ .

Fig. 31. General behaviour of the dynamic noise margins; amplitudes of noise pulses are allowed to be higher for short pulse widths. For very long pulses, the situation is quasi-static and the noise margins will reach their minima.

For short pulses the noise margins increase. The combination of the pulse length and amplitude now depend also on the switching speed of the gates.

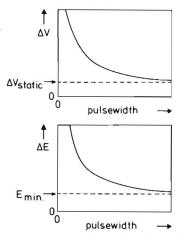

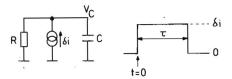

Section 11 gives a first-order explanation as to wat happens in a logic cirucit when series voltage noise and parallel current noise is applied in pulse-form. During such a pulse

31

energy is delivered to or sinked from (= negative delivery) the circuit to bring it into the wrong state. It appears that the energies in these noise pulses are generally different for series voltage noise sources and parallel current noise sources; it is impossible therefore to speak of a typical energy noise margin as a figure of merit. In general, the energy delivered by a series voltage noise pulse increases with decreasing pulse-width, and the energy delivered by a parallel current pulse decreases with decreasing pulse width; this has also been demonstrated with pulsed noise in ISL.

#### 2.XVII. Dynamic noise margins of ISL

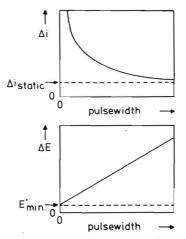

Fig. 32 shows four noise sources in an pn-isolated ISL flip-flop ( $F_i = F_o = 1$ ) without series resistances. These noise sources have been investigated separately for dynamic noise margins (the noise sources are not applied simultaneously, but separately).

Fig. 32. Four noise sources in an ISL flip-flop ( $F_i = F_o = 1$ ), which are investigated for the dynamic noise margins. The noise sources are not applied simultaneously.

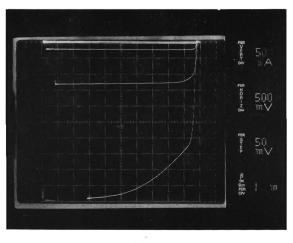

Fig. 33(a) shows computer simulated dynamic voltage noise margins and relative current noise margins as a function of pulse width for the four noise sources. Fig. 33(b) shows the energy content of the same noise pulses (energy noise margins). Indeed the energy in the voltage pulses increases with decreasing pulse width and the energy in current pulses decreases with decreasing pulse widths.

Fig. 33. Computer-simulated dynamic noise margins (a) and dynamic energy noise margins (b) of the ISL flip-flop of Fig. 32.

# 2.XVIII. Temperature behaviour of the static noise margins of ISL and STL

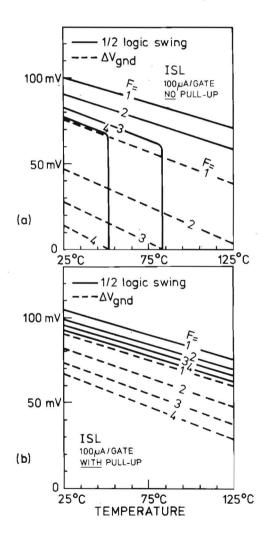

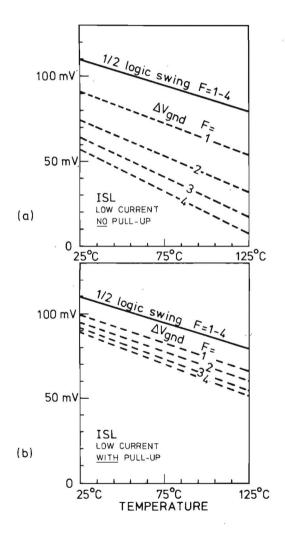

When, at room temperature, the voltage swings of ISL and STL are equal, then the room temperature values of the noise margins of ISL are a little better, due to the fact that in ISL the superfluous base-current of the saturated n-p-n transistor is sinked to ground (by the p-n-p transistor), whereas in STL this current has to flow through the n-p-n transistor. With a temperature increase, however, the noise margins of ISL are very soon smaller than those of STL, mainly because of the high negative temperature coefficient (- 0.6 mV/°C) of the voltage swing of ISL (as a first-order approximation the voltage swing of STL is independent of the temperature). Section 13 gives an analysis of the voltage swings of ISL and STL, and analytical expressions for the low-current worst-case static noise margins of ISL and STL. At high current levels series resistances can no longer be ignored and the noise margins are obtained with computer simulations.

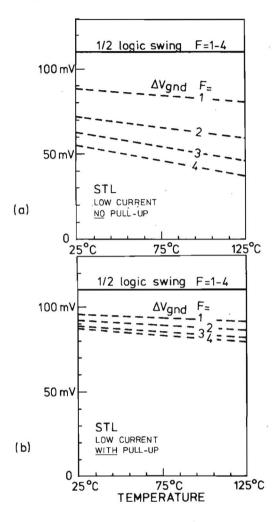

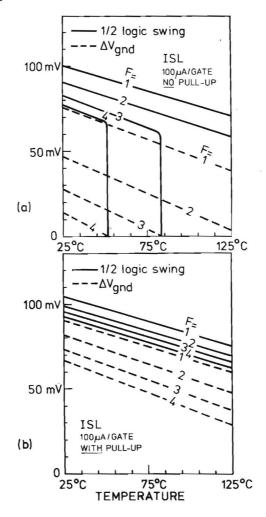

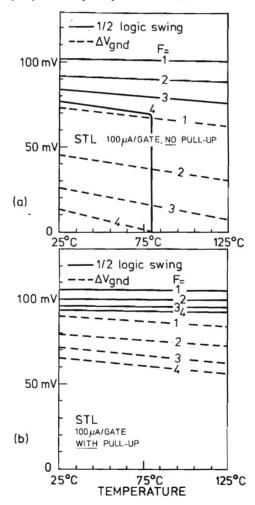

Fig. 34(a) shows half the voltage swing and the worst-case static ground-line voltage noise margins of oxide-isolated ISL at 100  $\mu$ A/gate with F = fan-in = fan-out as parameter, as a function of temperature. In this case the noise margin  $\Delta V_{\text{gnd}}$  for F = 4 is quite low and even negative for temperatures higher than 50°C. Fig. 34(b) shows similar results but this time with a gate input current of 50  $\mu$ A and an internal pull-up current of 50  $\mu$ A. It is obvious that the noise margins have been increased dramatically; for F = 4

Fig. 34. Half the voltage swing and the worst-case static ground-line voltage noise margins at 100  $\mu$ A/gate of oxide-isolated ISL without internal pull-up current (a) and with internal pull-up current (b), as a function of temperature, with F = fan-in = fan-out as parameter.

save operation is now possible up to 200°C. The noise margins of STL are always somewhat better due to the temperature-independent voltage swing, but without pull-up current  $\Delta V_{ond STL}$  is zero at 80°C for oxide-isolated STL at 100  $\mu$ A/gate; also for STL the application of an internal pull-up current improves the noise margins (see Section 13). Thus the application of internal pull-up currents improves the noise margins and decreases the propagation delay time depending on the fan-in (see Section 2.XI) of ISL and STL.

#### 2.XIX. Applications of ISL

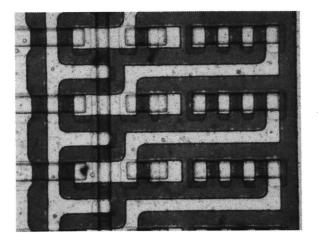

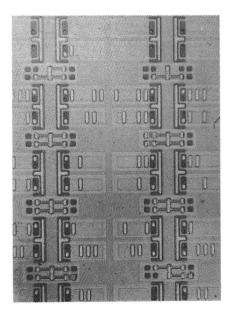

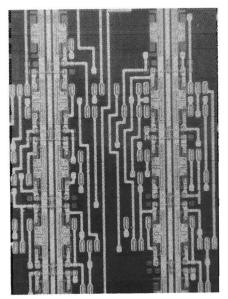

Until now all ISL applications have been made in a pn-isolated process with a 3  $\mu$ m epitaxial layer and 5  $\mu$ m minimum details.

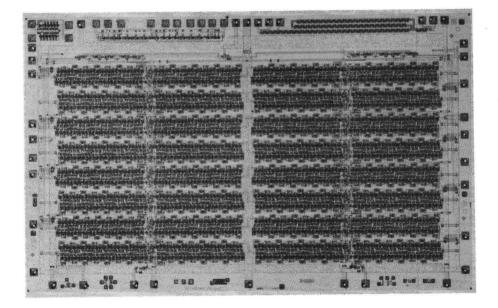

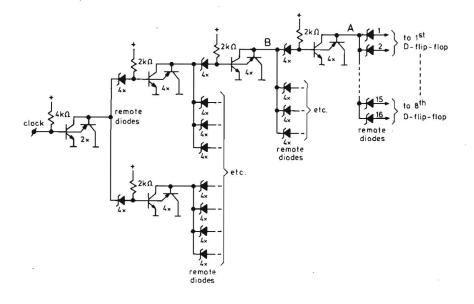

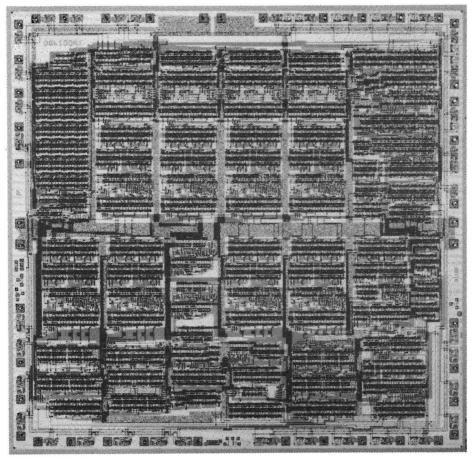

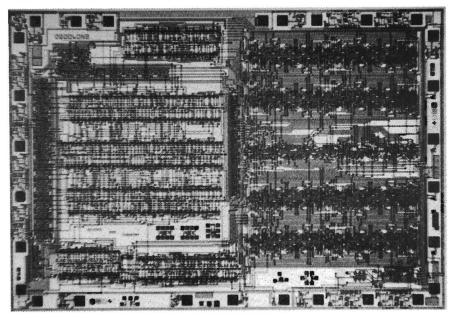

In appendix A some designs are discussed; a 256 bits shiftregister, a pipeline--multiplier, a counterchip (which combines ECL, I<sup>2</sup>L, ISL and TTL), a custom library called CCL (= Composite Cell Logic) with as example a FIFO memory controller and a 1200 gate array (8A1200).

Appendix B summarizes the main characteristics and specifications of the 8A1200 gate array.