## Transceiver architectures and sub-mW fast frequency-hopping synthesizers for ultra-low power WSNs

*Citation for published version (APA):* Lopelli, E. (2010). *Transceiver architectures and sub-mW fast frequency-hopping synthesizers for ultra-low power WSNs.* [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR657018

DOI: 10.6100/IR657018

#### Document status and date:

Published: 01/01/2010

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

## Transceiver Architectures and Sub-mW Fast Frequency-Hopping Synthesizers for Ultra-low Power WSNs

**Emanuele Lopelli**

Front cover: "Ultra-low power fast frequency-hopping synthesizer"

Back cover: "Ultra-low power frequency predistortion based transmitter RF front-end"

## Transceiver Architectures and Sub-mW Fast Frequency-Hopping Synthesizers for Ultra-low Power WSNs

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 20 januari 2010 om 16.00 uur

door

### Emanuele Lopelli

geboren te Bari, Italië

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. A.H.M. van Roermund

Copromotor: dr.ir. J.D. van der Tang

Emanuele Lopelli

Transceiver Architectures and Sub-mW Fast Frequency-Hopping Synthesizers for Ultralow Power WSNs / by Emanuele Lopelli. –A catalogue record is available from the Eindhoven University of Technology Library– ISBN: 978-90-386-2140-1 Subject headings: Frequency Hopping / Spread-Spectrum / Transmitter / Transceiver / Oscillator / Frequency synthesizer / Ultra-low power/ Wireless sensor networks.

> © Emanuele Lopelli 2010 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Anyone who has never made a mistake has never tried anything new.

Albert, Einstein

Dedicated to the numerous persons who contributed to this work Samenstelling promotiecommissie:

prof.dr.ir. A.C.P.M. Backx prof.dr.ir. A.H.M. van Roermund dr.ir. J.D. van der Tang prof.dr.ir. B. Nauta prof.dr.ir. J.R. Long prof.dr.ir. P.J.M. Baltus dr.ir. P.T.M. van Zeijl prof.dr.ir. E.R. Fledderus TU Eindhoven TU Eindhoven Broadcom Corporation TU Twente TU Delft TU Eindhoven Philips Research Laboratories TU Eindhoven

| 1 | Wire | eless Sensor Networks                  | 1  |

|---|------|----------------------------------------|----|

|   | 1.1  | Application field                      | 2  |

|   |      | 1.1.1 One-way link                     | 2  |

|   |      | 1.1.2 Two-way link                     | 4  |

|   | 1.2  | System requirements                    | 5  |

|   |      | 1.2.1 One-way link                     | 5  |

|   |      | 1.2.2 Two-way link                     | 6  |

|   | 1.3  | Energy scavenging techniques           | 7  |

|   |      |                                        | 10 |

|   |      |                                        | 10 |

|   | 1.4  |                                        | 11 |

|   |      |                                        | 11 |

|   |      |                                        | 12 |

|   |      | 1.4.3 Range and sensitivity            | 12 |

|   |      |                                        | 13 |

|   |      |                                        | 14 |

|   | 1.5  |                                        | 15 |

|   |      |                                        | 16 |

|   |      |                                        | 16 |

|   | 1.6  |                                        | 17 |

|   | 1.7  |                                        | 18 |

|   | 1.8  |                                        | 19 |

| 2 | Svs  | tem-Level and Architectural Trade-offs | 21 |

| - | 2.1  |                                        | 21 |

|   |      |                                        |    |

|   |                   | 2.1.1                                                                                                                                                         | Impulse radio transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                                                                                                                 |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 2.1.2                                                                                                                                                         | Back-scattering for Radio Frequency IDentification (RFID) ap-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

|   |                   |                                                                                                                                                               | plications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                                                                                                                                                                                 |

|   |                   | 2.1.3                                                                                                                                                         | Sub-sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                                                                                                 |

|   |                   | 2.1.4                                                                                                                                                         | Super-regenerative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                                                                                                                                                 |

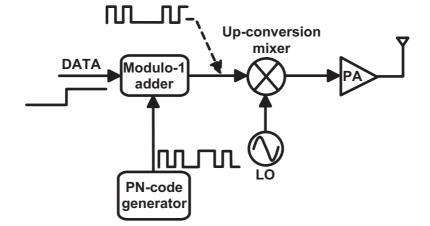

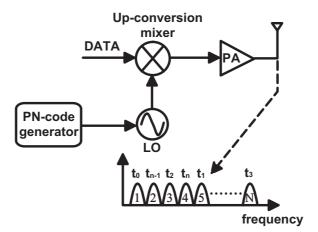

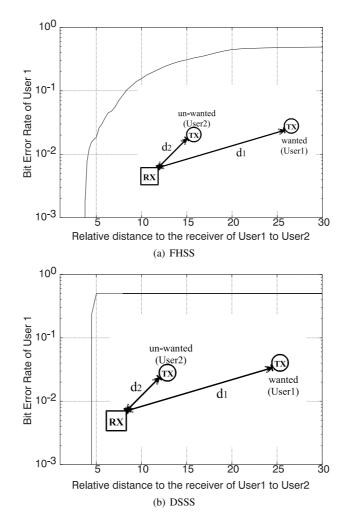

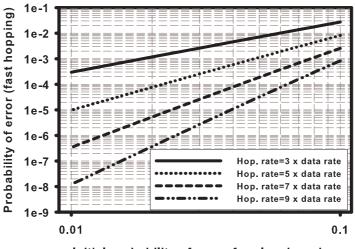

|   |                   | 2.1.5                                                                                                                                                         | Spread-spectrum systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                                                                                                                                                 |

|   | 2.2               | Optima                                                                                                                                                        | al Data-rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                                                                                                 |

|   |                   | 2.2.1                                                                                                                                                         | Constant duty-cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                                                                                                                                 |

|   |                   | 2.2.2                                                                                                                                                         | Constant time between two consecutive transmissions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                                                 |

|   | 2.3               |                                                                                                                                                               | nitter architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                                                                                                                                 |

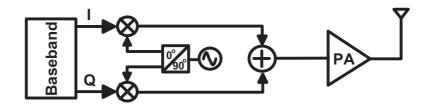

|   |                   | 2.3.1                                                                                                                                                         | Direct conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                                                                                                 |

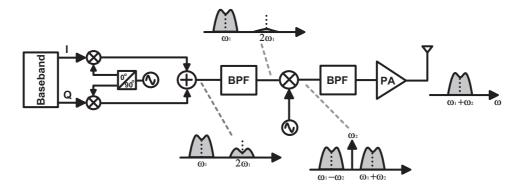

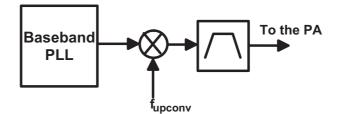

|   |                   | 2.3.2                                                                                                                                                         | Two-step conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                                                                                                                                 |

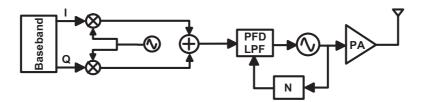

|   |                   | 2.3.3                                                                                                                                                         | Offset PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                                                                                                 |

|   | 2.4               |                                                                                                                                                               | ver architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43                                                                                                                                                                                 |

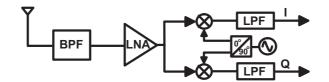

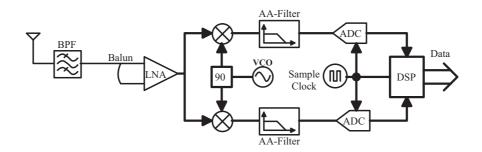

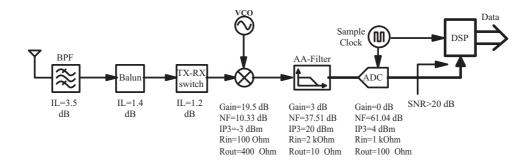

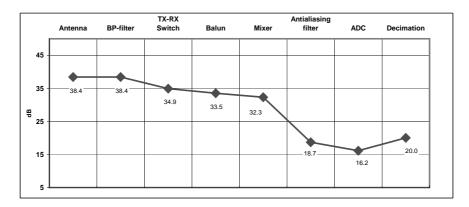

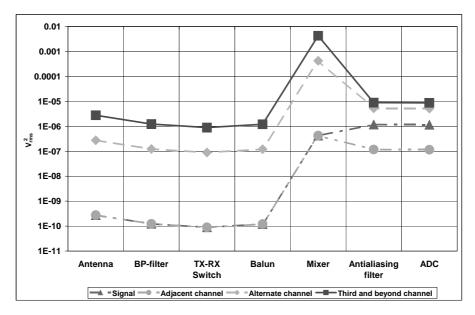

|   | 2.1               | 2.4.1                                                                                                                                                         | Zero-IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43                                                                                                                                                                                 |

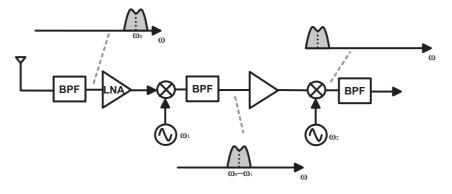

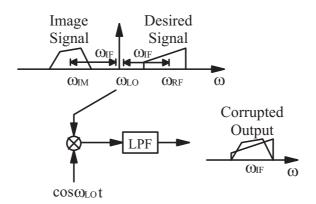

|   |                   | 2.4.2                                                                                                                                                         | Super-heterodyne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                                                                                                                                 |

|   |                   | 2.4.3                                                                                                                                                         | Low-IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                                                                                                                                 |

|   | 2.5               |                                                                                                                                                               | Isions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                                                                                                                                 |

|   | 2.5               | Concit                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40                                                                                                                                                                                 |

| 3 | FHS               | S Svst                                                                                                                                                        | ems: State-of-the-art and Power Trade-offs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                                 |

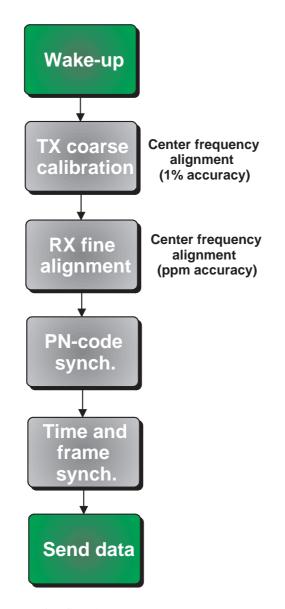

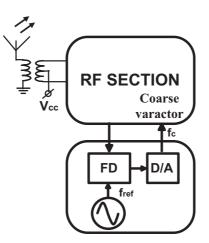

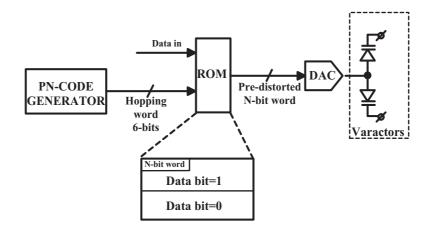

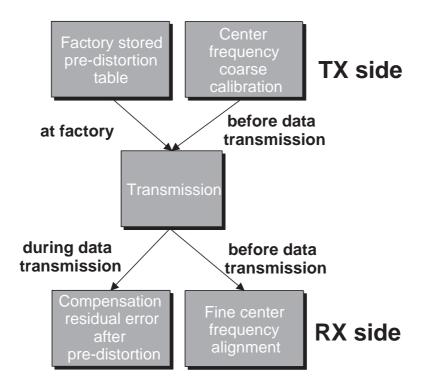

| - | 3.1               | -                                                                                                                                                             | ronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                                                                                                 |

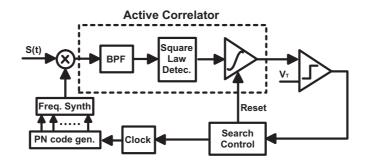

|   | 0.11              | 3.1.1                                                                                                                                                         | Stepped serial search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51                                                                                                                                                                                 |

|   |                   |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •••                                                                                                                                                                                |

|   |                   | 312                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                                                                                                                                                                 |

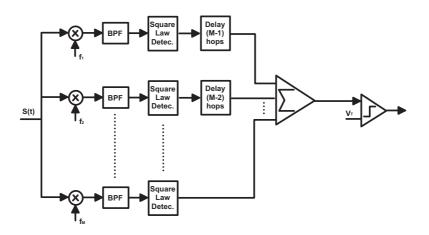

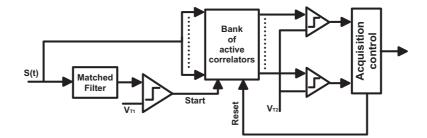

|   |                   | 3.1.2<br>3.1.3                                                                                                                                                | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52<br>53                                                                                                                                                                           |

|   |                   | 3.1.3                                                                                                                                                         | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                                                                                                 |

|   | 3.2               | 3.1.3<br>3.1.4                                                                                                                                                | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54                                                                                                                                                                           |

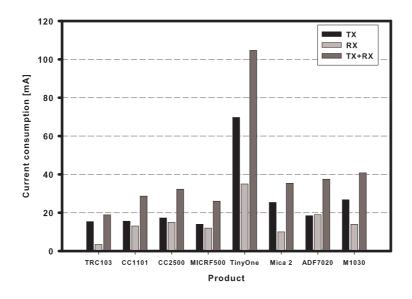

|   | 3.2<br>3.3        | 3.1.3<br>3.1.4<br>State-c                                                                                                                                     | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>56                                                                                                                                                                     |

|   | 3.3               | 3.1.3<br>3.1.4<br>State-c<br>Freque                                                                                                                           | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>56<br>59                                                                                                                                                               |

|   |                   | 3.1.3<br>3.1.4<br>State-c<br>Freque<br>Specifi                                                                                                                | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>56<br>59<br>59                                                                                                                                                         |

|   | 3.3               | 3.1.3<br>3.1.4<br>State-o<br>Freque<br>Specifi<br>3.4.1                                                                                                       | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>56<br>59<br>59<br>60                                                                                                                                                   |

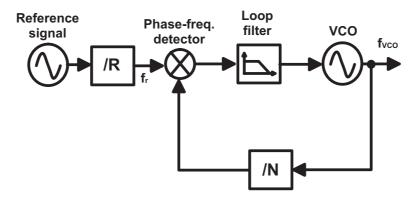

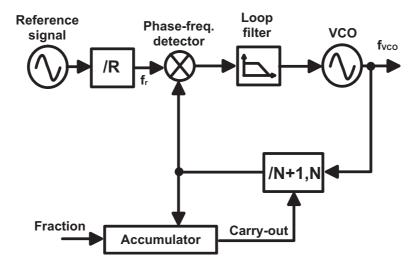

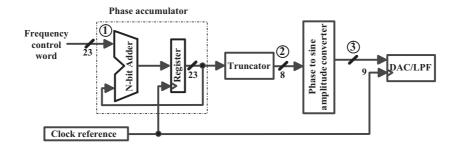

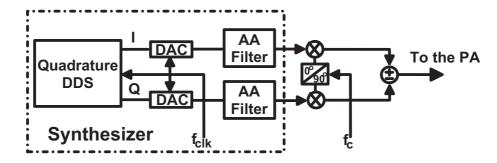

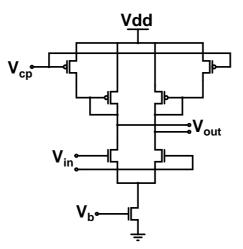

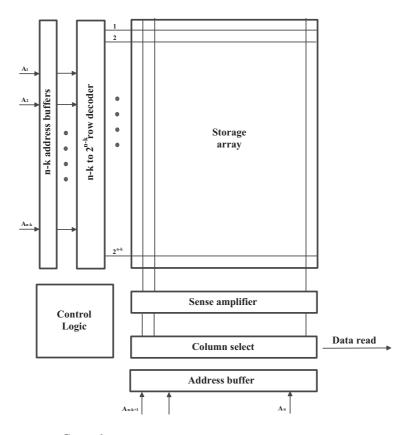

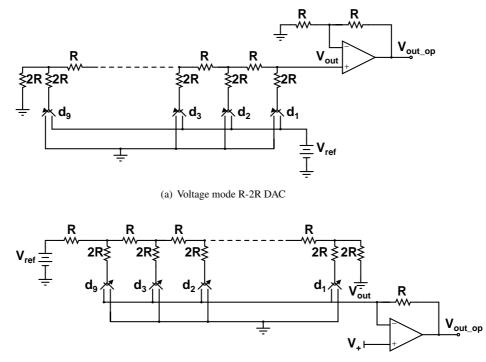

|   | 3.3<br>3.4        | 3.1.3<br>3.1.4<br>State-o<br>Freque<br>Specifi<br>3.4.1<br>3.4.2                                                                                              | Matched filter acquisitionTwo-level acquisitionAcquisition methods comparisonAcquisition methods comparisonof-the-art Frequency Hopping Spread Spectrum (FHSS) systemsency Hopping (FH) synthesizer architecturesications for ultra-low-power frequency-hopping synthesizersPhase-Locked Loop (PLL) basedDDFS based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53<br>54<br>56<br>59<br>59<br>60<br>63                                                                                                                                             |

|   | 3.3               | 3.1.3<br>3.1.4<br>State-of<br>Freque<br>Specifi<br>3.4.1<br>3.4.2<br>PLL po                                                                                   | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>56<br>59<br>59<br>60<br>63<br>67                                                                                                                                       |

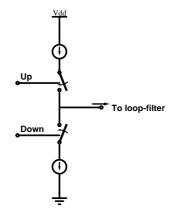

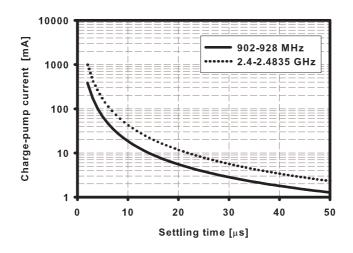

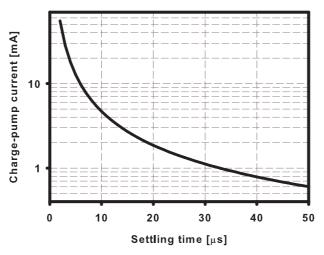

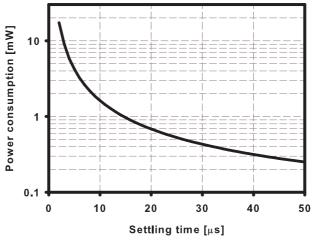

|   | 3.3<br>3.4        | 3.1.3<br>3.1.4<br>State-oc<br>Freque<br>Specifi<br>3.4.1<br>3.4.2<br>PLL po<br>3.5.1                                                                          | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>59<br>59<br>60<br>63<br>67<br>68                                                                                                                                       |

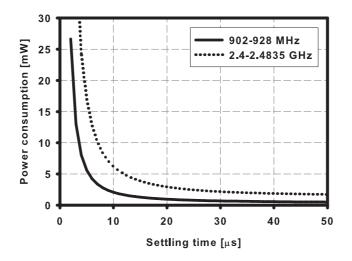

|   | 3.3<br>3.4        | 3.1.3<br>3.1.4<br>State-o<br>Freque<br>Specifi<br>3.4.1<br>3.4.2<br>PLL po<br>3.5.1<br>3.5.2                                                                  | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>59<br>59<br>60<br>63<br>67<br>68<br>70                                                                                                                                 |

|   | 3.3<br>3.4        | 3.1.3<br>3.1.4<br>State-of<br>Freque<br>Specifi<br>3.4.1<br>3.4.2<br>PLL po<br>3.5.1<br>3.5.2<br>3.5.3                                                        | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>59<br>59<br>60<br>63<br>67<br>68<br>70<br>70                                                                                                                           |

|   | 3.3<br>3.4        | 3.1.3<br>3.1.4<br>State-of<br>Freque<br>Specifi<br>3.4.1<br>3.4.2<br>PLL po<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                                               | Matched filter acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>54<br>59<br>59<br>60<br>63<br>67<br>68<br>70<br>70<br>70                                                                                                                     |