# Solar cell

Citation for published version (APA):

Dingemans, G., Engelhart, P., Kessels, W. M. M., & Wanka, S. (2010). Solar cell. (Patent No. WO2010070013).

## Document status and date:

Published: 24/06/2010

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

## Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

## Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 08. Feb. 2024

### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

## (43) International Publication Date 24 June 2010 (24.06.2010)

## (10) International Publication Number WO 2010/070013 A1

(51) International Patent Classification: H01L 31/0224 (2006.01)

(21) International Application Number:

PCT/EP2009/067340

(22) International Filing Date:

16 December 2009 (16.12.2009)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data: 102008055036.1 19 December 2008 (19.12.2008) DE

- (71) Applicant (for all designated States except US): Q-CELLS SE [DE/DE]; Sonnenallee 17-21, OT Thalheim, 06766 Bitterfeld-Wolfen (DE).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): ENGELHART, Peter Declarations under Rule 4.17: [DE/DE]; Wilhelmsplatz 8, 31785 Hameln (DE).

- (74) Agent: REININGER, Jan; adares Patent- und Rechtsanwälte, Reininger & Partner, Schumannstraße 2, 10117 Berlin (DE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ,

CA, CH, CL, CN, CO, CR, CU, CZ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

- as to the identity of the inventor (Rule 4.17(i))

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

#### Published:

with international search report (Art. 21(3))

(54) Title: SOLAR CELL

Fig. 1

(57) Abstract: A solar cell comprising a semiconductor layer (1), a collecting layer (6) for collecting free charge carriers from the semiconductor layer (1) and a buffer layer (3) which is arranged between the semiconductor layer (1) and the collecting layer (6), which buffer layer (3) is designed as a tunnel contact (31) between the semiconductor layer (1) and the collecting layer (6) is characterised in that the buffer layer (3) essentially comprises a material with a surface charge density of at least 10<sup>12</sup> cm<sup>-2</sup>, preferably of at least  $5 \times 10^{12}$  cm<sup>-2</sup>, more preferably of at least  $10^{13}$  cm<sup>-2</sup>.

,

- 1 -

PCT/EP2009/067340

Title:

WO 2010/070013

Solar cell

5 Description:

10

15

20

25

30

The invention relates to a solar cell with a tunnel contact.

The use of a tunnel layer system for contacting a solar cell is known. In this arrangement a tunnel layer is inserted between the emitter or base of the solar cell semiconductor and a metal layer that acts as a collecting layer for the charge carriers that tunnel through the tunnel layer. For example silicon oxide  $(SiO_2)$  is used as such a tunnel layer. It can at the same time be used to carry out surface passivation in that recombination-active surface states of the semiconductor are saturated. In solar cells that are formed based on a silicon the tunnel layer can be produced by means of thermal oxidation. However, an  $SiO_2$  layer is associated with a disadvantage in that adequate surface passivation with at the same time high tunnelling probability of the charge carriers in the metal layer is difficult to implement from the point of view of technology.

Furthermore, as a rule, in solar cells with a heterojunction, which comprises, for example, a crystalline layer and an amorphous layer, which as a rule is mostly doped, of a semiconductor, an additional layer is inserted between the two semiconductor layers in order to achieve surface passivation, in particular of the crystalline semiconductor layer. To this effect, as a rule, a thin, intrinsic, i.e. essentially doping-free, amorphous semiconductor layer is used. In this arrangement too, passivation, for example by means of an intrinsic amorphous silicon layer, is often insufficient, which results in a reduction in the efficiency of the solar cell. Furthermore, homogeneous layer deposition, for example by means of vapour-deposition from the gas phase, is technologically difficult to implement if at the same time a high tunnelling probability is to be achieved.

- 2 -

It is thus the object of the invention to provide a solar cell comprising a tunnel layer that is arranged between a semiconductor layer and a collecting layer, which solar cell is technologically easy to implement and moreover provides good efficiency.

PCT/EP2009/067340

According to the invention this object is met by a solar cell with the characteristics of claim 1. Advantageous embodiments of the invention are stated in the subordinate claims.

10

15

20

5

WO 2010/070013

The invention is based on the recognition that a buffer layer with a high surface charge density of at least  $10^{12}$  cm<sup>-2</sup>, preferably of at least  $5 \times 10^{12}$  cm<sup>-2</sup>, more preferably of at least  $10^{13}$  cm<sup>-2</sup>, is particularly well suited to form a tunnel contact and at the same time to ensure adequate surface passivation by means of field effect passivation. Moreover, the buffer layer, due to its high surface charge density, can induce an inversion layer or accumulation layer in a semiconductor layer situated underneath it. The surface charge density of the buffer layer can be either negative or positive. The intensity and type of the induced layer depends in particular on the polarity of the surface charge density, as well as on the material and any doping of the semiconductor layer. The electrical properties and the spatial expansion of the tunnel contact also depend on the electrical characteristics of the inversion layer or accumulation layer.

In this document the term "layer" can also refer to a layer-shaped structure that extends only over a limited region on the solar cell. In other words the semiconductor layer, collecting layer, buffer layer or the like can be limited to insular or strip-shaped regions on the solar cell. It is thus not necessary for the layers to essentially extend over the entire solar cell, which is usually planar.

Furthermore, the term "layer" need not necessarily relate to a planar or flat position; instead, conforming to an underlying structure, it may be curved or bent, for example it may be dish-shaped or cup-shaped in design.

- 3 -

A possible method for producing the solar cell comprises a step of providing the semiconductor layer, subsequent application of the buffer layer onto the semiconductor layer, and furthermore the application of the collecting layer onto the buffer layer. Additional application steps for applying intermediate layers or structuring steps may be provided. The semiconductor layer can be present in the form of a wafer, or can be vapour-deposited onto a substrate in a thin-film process. In the latter case the sequence of layer depositing can also be reversed so that, for example, at first a collecting layer is applied to a substrate or a superstrate, and subsequently the buffer layer and the semiconductor layer are vapour-deposited onto said collecting layer.

That the buffer layer is essentially made of a certain material means in particular that the buffer layer may comprise traces of other materials due to imperfections in the fabrication process, in the raw materials or the like.

15

20

10

5

According to an advantageous embodiment, the buffer layer is essentially made of a material with a negative surface charge density. Aluminium fluoride (AlF<sub>3</sub>) with a negative charge density of between approximately 10<sup>12</sup> and approximately 10<sup>13</sup> cm<sup>-2</sup> is one example of a material with negative surface charge density. Negative surface charge density provides an advantage in that the material is particularly suitable for contacting a p-type semiconductor layer, which, for example, in silicon-based photovoltaics is by far the most frequently-used conductive type for an absorber.

An expedient improvement provides for the buffer layer to essentially be made of aluminium oxide. With the use of a suitable application process or vapour-depositing process, aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) can be applied in a homogeneous layer thickness. Furthermore, such an aluminium oxide layer is particularly well suited for surface passivation. As a result of its high negative surface charge density, an inversion layer or accumulation layer induced in this manner further comprises good conductivity.

- 4 -

A preferred embodiment provides for the buffer layer to be formed without pinholes. In other words the buffer layer is essentially free of faults, and in particular does not contain any openings (pinholes) that extend through the thickness of the buffer layer.

5

10

15

20

25

30

According to an advantageous embodiment, the buffer layer has been applied by means of atomic layer deposition (ALD). By means of ALD, in which layer deposition of one atomic layer after another takes place, in particular thin layers can be produced without any defects. In this process the layer thickness can be controlled very precisely. In particular in the production of aluminium oxide layers, ALD results in buffer layers with very advantageous electronic characteristics.

Preferably, the buffer layer comprises a thickness ranging between 0.1 and 10 nanometres, preferably ranging between 1 and 3 nanometres. In particular in a thickness of between 1 and 3 nm, due to a sufficient number of bound charges, good passivation will result, at the same time with high tunnelling probability.

An advantageous improvement provides for the semiconductor layer to be made of a crystalline semiconductor. This can, for example, be a semiconductor wafer that serves as the starting point in the production of the solar cell.

An expedient embodiment provides for the semiconductor layer to be an n-type or p-type semiconductor layer. The semiconductor layer thus comprises base doping. Due to the buffer layer, furthermore an inversion layer or an accumulation layer underneath the buffer layer can be induced, wherein, for example, a buffer layer, depending on the signs of its surface charge density, in an n-type semiconductor layer induces an n<sup>+</sup>-type accumulation layer or a p-type inversion layer. Doping of the semiconductor layer can take place during its manufacture or subsequently by means of a diffusion step.

- 5 -

In this context it should be pointed out that the terms "n-type" or "p-type" denote that the semiconductor layer has been doped with a doping material in such a way that it forms an n-type or a p-type semiconductor. In the present document these terms are used synonymously with the terms "n-doped" and "p-doped".

According to a preferred embodiment, the semiconductor layer adjoining the buffer layer comprises a doping layer and/or an inversion layer or accumulation layer induced by means of the buffer layer. Both the doping layer and the inversion layer are suitable for generating band bending such that in the semiconductor, separation of charge carriers takes place, which charge carriers were generated by means of light incidence. In this arrangement, for example, the semiconductor layer can comprise base doping so that this layer together with the inversion layer induced therein forms a pn-junction.

15

20

10

5

As an alternative, such a pn-junction can already have been formed between the base-doped semiconductor layer and the doping layer. In this case the induced accumulation layer can be used to control the electronic characteristics of the tunnel contact, formed by means of the buffer layer, between the semiconductor layer and the collecting layer.

Expediently it is provided for the buffer layer to be designed as an antireflection layer (AR layer). An anti-reflection layer is used to reduce or entirely prevent back reflection of incident light impinging on the solar cell.

Consequently the efficiency of the solar cell is increased. The AR layer should preferably be effective for the wavelength range for which the solar cell is tailored, for example in that it is most sensitive in this range. This characteristic can be set by means of suitable selection of the material and of the layer thickness of the buffer layer.

30

25

A preferred improvement provides for the collecting layer to comprise a metal, a metal alloy and/or a transparent conductive material. Furthermore, the collecting layer can be structured, for example in order to form electrode

- 6 -

fingers by means of which the current generated in the solar cell can be tapped. The transparent conductive material is a material that is transparent to the wavelength spectrum for which the solar cell is designed, for example to the visible and/or infrared spectrum. Preferably the material is a transparent conductive oxide (TCO) such as indium tin oxide (ITO), zinc oxide or the like.

5

10

An advantageous embodiment provides for the collecting layer to comprise a semiconductor. In this case, over the collecting layer preferably a contact layer that is also structured is applied in order to accommodate the charge carriers that have tunnelled into the collecting layer. Advantageously it is provided for the collecting layer to be n-doped or p-doped. A layer comprising highly-doped polycrystalline silicon is one example of a collecting layer comprising semiconductors.

- An expedient embodiment provides for the collecting layer to comprise an amorphous semiconductor. For example this can be a heterojunction layer which comprises an amorphous or a microcrystalline semiconductor material, while the semiconductor layer that is arranged underneath the buffer layer is crystalline. Usually, for passivation purposes an intrinsic amorphous

semiconductor layer is inserted between these semiconductor layers with different crystal structures. A layer arrangement comprising crystalline silicon (c-Si) and amorphous or microcrystalline silicon (a-Si or μc-Si) is one example of a heterojunction.

- In the present embodiment the intrinsic amorphous semiconductor layer is replaced by the buffer layer so that a tunnel contact forms between the semiconductor layer and the heterojunction layer. Replacing the intrinsic amorphous semiconductor layer is associated with an advantage in that it is not necessary, as is normally the case, to find a compromise between V<sub>OC</sub>-gain (with V<sub>OC</sub> denoting the open circuit voltage) and fill factor losses (FF-losses) by means of setting the layer thickness of the intrinsic layer.

An expedient improvement provides for a contact layer made of a conductive material to be formed on the collecting layer. In this arrangement the contact layer can comprise a metal, a metal alloy and/or a transparent conductive material. Furthermore, the contact layer, which can be a front or a back contact, can be structured, for example in order to form finger-shaped contacts if applicable with busbars.

A preferred embodiment provides for a further buffer layer to be provided between the semiconductor layer and a further collecting layer, namely on a face of the semiconductor layer, which face points away from the buffer layer. Independently of the buffer layer and the collecting layer, the further buffer layer and the further collecting layer can comprise the embodiments described above and below in the context of said collecting layer. For example, the collecting layer can comprise a metal layer, while the further collecting layer forms a heterojunction with the semiconductor layer.

Below, the invention is explained with reference to the figures by means of exemplary embodiments. The following are shown in diagrammatic cross-sectional drawings:

20

5

10

15

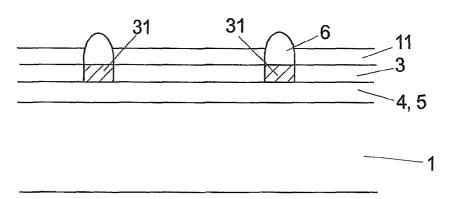

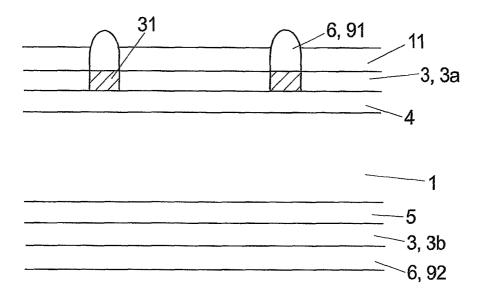

- Fig. 1 an embodiment of a solar cell comprising a buffer layer and a collecting layer designed as finger electrodes;

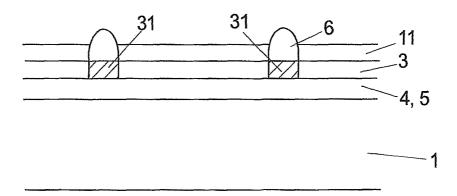

- Fig. 2 a further embodiment of the solar cell comprising a buffer layer and a continuous collecting layer;

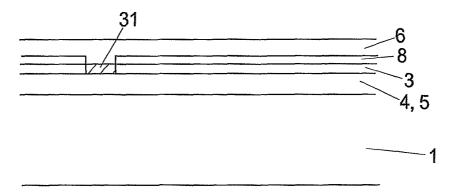

- 25 Fig. 3 a solar cell comprising a heterojunction, in which the buffer layer is incorporated;

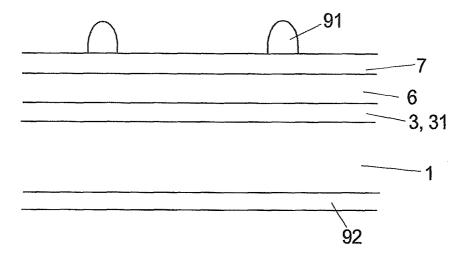

- Fig. 4 a solar cell comprising buffer layers arranged on both faces of the semiconductor layer;

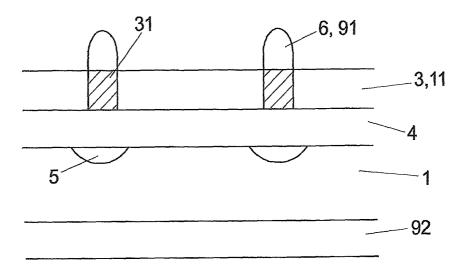

- Fig. 5 a further solar cell comprising a doping layer underneath the buffer layer;

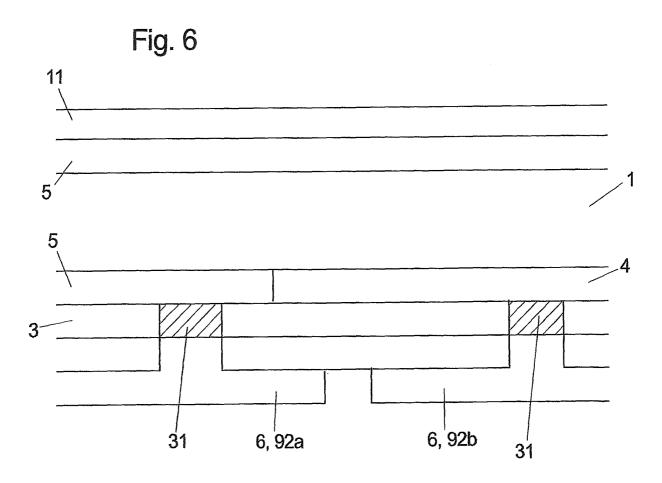

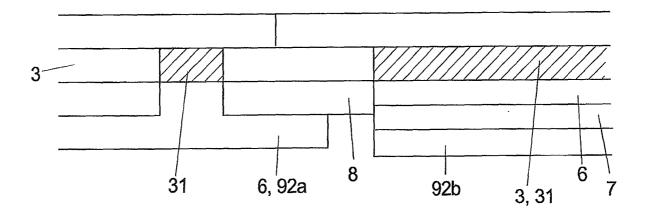

- Fig. 6 an embodiment of a back-contacted solar cell; and

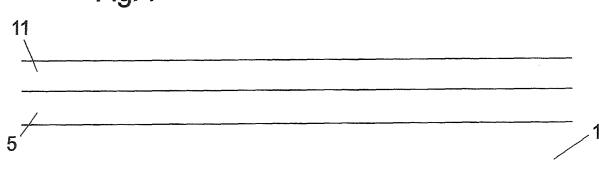

- Fig. 7 a further embodiment of a back-contacted solar cell.

- 8 -

Fig. 1 shows a solar cell comprising a semiconductor layer 1, a buffer layer 3 arranged thereon, and a collecting layer 6 vapour-deposited on the buffer layer 3. The collecting layer 6 is structured to form finger-shaped metal electrodes and is used to collect charge carriers that have been generated in the semiconductor layer by means of incident light. To this effect the electrically insulating buffer layer 3 forms tunnel contacts 31 between the semiconductor layer 1 and the collecting layer 6, through which the charge carriers tunnel into the collecting layer 6.

5

20

25

30

10 The buffer layer 3 is preferably an aluminium oxide layer that has been applied to the semiconductor layer 1 by means of atomic layer deposition (ADL). Thus a layer thickness is obtained which essentially stays the same over the entire buffer layer 3, with the atomic scale of said layer thickness in addition being precisely settable. In this manner the electronic characteristics of the tunnel contacts 31 can be precisely set. The tunnel contacts 31 are thus tunnel regions 31 in the buffer layer 3.

Directly underneath the buffer layer 3 a doping layer 5 is formed in the semiconductor layer 1 by means of diffusion. As an alternative, the doping layer 5 can have been applied to the semiconductor layer 1 by means of a vapour-deposition process. Due to the surface charge density of the buffer layer 3, instead of the doping layer 5 directly underneath the buffer layer 3 an inversion layer or accumulation layer 4 can be induced. For example, if the semiconductor layer 1 is n-doped, for example in the form of a base-doped semiconductor wafer, by means of a subsequent overcompensating diffusion process a p-doped doping layer 5 can be produced in order to obtain a pn-junction. As an alternative, the use of a suitable material, for example of aluminium oxide, for the buffer layer 3 can result in the buffer layer 3 inducing a p-doped inversion layer 4 in the semiconductor layer 1, thereby producing the pn-junction.

Furthermore, it is possible for the buffer layer 3 to produce in the semiconductor layer 1 an accumulation layer 4 that adjoins it. This is the case,

WO 2010/070013

- 9 -

PCT/EP2009/067340

for example, if the semiconductor layer 1 is p-doped and the buffer layer 3 comprises aluminium oxide, as a result of which a  $p^+$ -doped accumulation layer 4 is produced.

- Above the buffer layer 3 an anti-reflection layer 11 is arranged, which with the selection of a suitable refractive index and a suitable layer thickness is designed to minimise or avoid reflection of the incident light at least over a defined spectral region and angle of incidence region. The finger-shaped electrodes that form the collecting layer 6 are partly surrounded by the anti-reflection layer 11. Instead of the additional anti-reflection layer 11, with suitable selection of the material and of the layer thickness, the buffer layer 3 can be used as an anti-reflection layer.

- Fig. 2 shows a solar cell according to a further embodiment in which the

collecting layer 6 comprises a continuous layer, which without structure extends over a surface of a solar cell, which layer comprises a conductive material, for example metal. To ensure that the tunnel contact 31 between the inversion layer or accumulation layer 4 or doping layer 5 in the semiconductor layer 1 through the buffer layer 3 only forms locally rather than along the entire buffer layer 3, between the buffer layer 3 and the collecting layer 6 an insulation layer 8 is arranged which comprises an opening above the tunnel contact 31.

- Figs. 1 and 2 only show front contacting of the solar cell. In order to provide a

better overview the back surface contacts have been left out in these figures.

For example, it is possible for the collecting layers 3 shown in Figs 1 and 2 in

each case to form a front collecting layer 3 and a back collecting layer 3 of one

and the same solar cell.

- Fig. 3 shows a solar cell that is contacted on both sides, which solar cell comprises a heterojunction. The heterojunction forms between the semiconductor layer 1 and the collecting layer 6 between which the buffer layer 3 is arranged. For example, the collecting layer 6 can comprise

- 10 -

amorphous silicon, while the semiconductor layer 1 is formed from crystalline silicon. Essentially the entire buffer layer 3 acts as a tunnel layer 31. When compared to a conventional heterojunction with a crystalline semiconductor layer, an amorphous semiconductor layer and an intrinsic amorphous semiconductor layer arranged in between, in the present embodiment an alternative heterojunction is thus created.

With the use of ADL the layer thickness of a buffer layer 3 that, for example, comprises aluminium oxide can be precisely controlled. Buffer layers 3 that have been vapour-deposited in this way and that comprise a sufficiently high surface charge density furthermore result in very good surface passivation. Furthermore, here too, as already explained with reference to Figs. 1 and 2, an inversion layer or accumulation layer 4 (not shown) can form underneath the buffer layer 3 in the semiconductor layer 1.

15

20

10

5

On the collecting layer 6 a contact layer 7 is arranged which comprises, for example, a conductive transparent material. Finally, the solar cell comprises a front-surface electrode 91 and a back-surface electrode 92. While the front-surface electrode 91 is structured to form electrode fingers so that incident light can reach the solar cell through the contact layer 7 with only little shading, the back-surface electrode 92 is planar in shape. Above the back-surface electrode 92 the semiconductor layer 1 can additionally comprise a doping layer in order to improve ohmic contact between the semiconductor layer 1 and the back-surface electrode 92.

25

30

Fig. 4 shows a further solar cell that is contacted on both faces. On both faces of the semiconductor layer 1 this solar cell comprises a buffer layer 3. A front-surface buffer layer 3a is followed by an inversion layer or accumulation layer 4 that is induced in the semiconductor layer 1 as a result of the former, while a back-surface buffer layer 3b is formed on a doping layer 5. The collecting layers 6 associated with the buffer layers 3a, 3b are a structured front-surface electrode 91 and a back-surface electrode 92 that extends over the entire surface. Correspondingly, tunnel regions 31 that are delimited in area form in

- 11 -

the front-surface buffer layer 3a, while the back-surface buffer layer 3b essentially acts completely as a tunnel contact 31.

In a manner similar to that in the embodiment according to Fig. 1, here, too, an anti-reflection layer 11 is formed on the front-surface buffer layer 3a. In the front embodiment the inversion layer or accumulation layer 4 and the doping layer 5 can be exchanged, or the semiconductor layer 1 can on both sides comprise an inversion layer or accumulation layer 4 and/or a doping layer 5.

10

15

20

25

30

5

Fig. 5 shows a solar cell in which the semiconductor layer 1 on one face comprises both an inversion layer or accumulation layer 4 and a doping layer 5. For the formation of the doping layer 5 the semiconductor layer 1 is, however, only doped in those sections that are located underneath the finger-shaped front-surface electrode 91 and thus underneath the tunnel regions 31 that form between the collecting layer 6 and the semiconductor layer 1. While in the present embodiment the inversion layer or accumulation layer 4 is responsible for band bending and thus for charge carrier separation, with a suitable selection of their doping parameters such as, for example, doping type, doping intensity, doping depth and the like, the doping layer 5 serves partly or exclusively to improve the tunnel contact 31.

Fig. 6 shows a back-contacted solar cell that comprises a semiconductor layer 1 and on the back face comprises a buffer layer 3. The buffer layer 3 comprises an insulation layer 8 from a suitable electrically insulating material, on which insulation layer 8 a collecting layer 6 is arranged. The collecting layer 6 is divided into a back-surface base electrode 92a, and an back-surface emitter electrode 92b. The back-surface base electrode 92a is connected to a doping layer 5 by way of a tunnel contact 31 formed in the buffer layer 3. By way of a further tunnel contact 31 the back-surface emitter electrode 92b is connected to an inversion layer or accumulation layer 4 that is induced in the semiconductor layer 1 due to the surface charge of the buffer layer 3. The inversion layer or accumulation layer 4 thus forms the emitter in the solar cell.

- 12 -

In this embodiment, too, the inversion layer or accumulation layer 4 and the doping layer 5 can overlap.

Above the semiconductor layer 1 and thus on a face of light incidence of the solar cell there is a further doping layer 5, which is covered by an anti-reflection layer 11. Here, too, the doping layer 5 can have been replaced by an inversion layer or accumulation layer 4 which is induced by means of a buffer layer 3 arranged underneath the anti-reflection layer 11 (which buffer layer 3 in the present embodiment, however, only serves as an inversion layer).

10

15

5

Fig. 7 shows a further embodiment of a back-contacted solar cell. It differs from the solar cell shown in Fig. 6 in that the back-surface emitter electrode 92b is connected to the semiconductor layer 1 by way of a heterojunction similar to the one shown in Fig. 3. In this embodiment, too, the buffer layer 3 underneath the collecting layer 6 forms a tunnel contact 31 that expands in a planar manner.

# - 13 -

# List of reference characters:

| 1   | Semiconductor layer                  |

|-----|--------------------------------------|

| 3   | Buffer layer                         |

| 3a  | Front-surface buffer layer           |

| 3b  | Back-surface buffer layer            |

| 31  | Tunnel contact (tunnel region)       |

| 4   | Inversion layer (accumulation layer) |

| 5   | Doping layer                         |

| 5   | Collecting layer                     |

| 7   | Contact layer                        |

| 3   | Insulation layer                     |

| 91  | Front-surface electrode              |

| 92  | Back-surface electrode               |

| 92a | Back-surface base electrode          |

| 92b | Back-surface emitter electrode       |

| 11  | Anti-reflection layer                |

PCT/EP2009/067340

## Claims:

WO 2010/070013

- 1. A solar cell comprising a semiconductor layer (1), a collecting layer (6) for collecting free charge carriers from the semiconductor layer (1) and a buffer layer (3) which is arranged between the semiconductor layer (1) and the collecting layer (6), which buffer layer (3) is designed as a tunnel contact (31) between the semiconductor layer (1) and the collecting layer (6), characterised in that the buffer layer (3) is essentially made of a material with a surface charge density of at least 10<sup>12</sup> cm<sup>-2</sup>, preferably of at least 5x10<sup>12</sup> cm<sup>-2</sup>, more preferably of at least 10<sup>13</sup> cm<sup>-2</sup>.

- 2. The solar cell according to claim 1 or 2, characterised in that the buffer layer (3) is essentially made of a material with a negative surface charge density.

- 3. The solar cell according to claim 1 or 2, characterised in that the buffer layer (3) is essentially made of aluminium oxide.

- 4. The solar cell according to any one of the preceding claims, characterised in that the buffer layer (3) is formed without pinholes.

- 5. The solar cell according to any one of the preceding claims, characterised in that the buffer layer (3) has been applied by means of atomic layer deposition.

- 6. The solar cell according to any one of the preceding claims, characterised in that the buffer layer (3) comprises a thickness ranging between 0.1 and 10 nm, preferably ranging between 1 and 3 nm.

- 7. The solar cell according to any one of the preceding claims, characterised in that the semiconductor layer (1) is made of a crystalline semiconductor.

- 8. The solar cell according to any one of the preceding claims, characterised in that the semiconductor layer (1) is n-doped or p-doped.

- 9. The solar cell according to any one of the preceding claims, characterised in that the semiconductor layer (1), adjacent to the buffer layer (3) comprises a doping layer (5) and/or an inversion layer (4) or accumulation layer (4) induced by means of the buffer layer (3).

- 10. The solar cell according to any one of the preceding claims, characterised in that the buffer layer (3) is designed as an anti-reflection layer (11).

- 11. The solar cell according to any one of the preceding claims, characterised in that the collecting layer (6) comprises a metal, a metal alloy and/or a transparent conductive material.

- 12. The solar cell according to any one of claims 1 to 9, characterised in that the collecting layer (6) comprises a semiconductor.

- 13. The solar cell according to claim 11, characterised in that the collecting layer (6) comprises an amorphous semiconductor.

- 14. The solar cell according to claim 11 or 12, characterised in that the collecting layer (6) is n-doped or p-doped.

- 15. The solar cell according to any one of claims 11 to 13, characterised in that on the collecting layer (6) a contact layer (7) of a conductive material is formed.

- 16. The solar cell according to any one of the preceding claims, characterised in that on a face of the semiconductor layer (1), which face points away from the buffer layer (3a; 3b), a further buffer layer

- 16 -

(3b; 3a) is provided between the semiconductor layer (1) and a further collecting layer (3).

1/4

Fig.1

Fig.2

Fig.3

Fig.4

3/4 Fig.5

Fig. 7

# INTERNATIONAL SEARCH REPORT

International application No PCT/EP2009/067340

| A. CLASSI<br>INV.         | FICATION OF SUBJECT MATTER<br>H01L31/0224                                                                   |                                                                                                                                                 |                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                           | o International Patent Classification (IPC) or to both national class                                       | sification and IPC                                                                                                                              |                                               |

|                           | SEARCHED                                                                                                    |                                                                                                                                                 |                                               |

| H01L                      | ocumentation searched (classification system followed by classifi                                           |                                                                                                                                                 |                                               |

|                           | tion searched other than minimum documentation to the extent th                                             |                                                                                                                                                 |                                               |

| EPO-In                    | ata base consulted during the international search (name of data                                            | a base and, where practical, search terms used                                                                                                  | ŋ                                             |

| C. DOCUMI                 | ENTS CONSIDERED TO BE RELEVANT                                                                              |                                                                                                                                                 |                                               |

| Category*                 | Citation of document, with indication, where appropriate, of the                                            | e relevant passages                                                                                                                             | Relevant to claim No.                         |

| Х                         | US 2008/105299 A1 (KRASNOV ALE)<br>8 May 2008 (2008-05-08)                                                  | (EY [US])                                                                                                                                       | 1–15                                          |

| Υ                         | paragraphs [0014] - [0032]; fig                                                                             | gures 1,2                                                                                                                                       | 16                                            |

| X                         | US 4 253 881 A (HEZEL RUDOLF) 3 March 1981 (1981-03-03) column 4, line 50 - column 7, l figures 1-6         | line 14;                                                                                                                                        | 1-11,15                                       |

| Υ                         | US 5 009 719 A (YOSHIDA SUSUMU<br>23 April 1991 (1991-04-23)                                                | [JP])                                                                                                                                           | 16                                            |

| A                         | column 3, line 16 - column 6, l<br>figures 3,4                                                              | line 15;                                                                                                                                        | 1–15                                          |

| А                         | US 4 248 675 A (BOZLER CARL O E<br>3 February 1981 (1981-02-03)<br>the whole document<br>                   | ET AL)                                                                                                                                          | 1-16                                          |

|                           |                                                                                                             |                                                                                                                                                 |                                               |

| Furti                     | her documents are listed in the continuation of Box C.                                                      | X See patent family annex.                                                                                                                      | <u> </u>                                      |

| * Special c               | ategories of cited documents :                                                                              |                                                                                                                                                 |                                               |

|                           | ent defining the general state of the art which is not lered to be of particular relevance                  | "T" later document published after the integration or priority date and not in conflict with cited to understand the principle or the invention | the application but                           |

| E" earlier ("<br>filing d | document but published on or after the international late                                                   | "X" document of particular relevance; the cannot be considered novel or canno                                                                   | claimed invention                             |

| which                     | ent which may throw doubts on priority claim(s) or<br>is cited to establish the publication date of another | involve an inventive step when the do                                                                                                           | ocument is taken alone                        |

|                           | n or other special reason (as specified) ent referring to an oral disclosure, use, exhibition or            | cannot be considered to involve an ir<br>document is combined with one or m<br>ments, such combination being obvio                              | ventive step when the<br>ore other such docu- |

| "P" docume                | neans ent published prior to the international filing date but nan the priority date claimed                | in the art.  "&" document member of the same patent                                                                                             | •                                             |

| Date of the               | actual completion of the international search                                                               | Date of mailing of the international sea                                                                                                        | arch report                                   |

| 1.                        | 5 February 2010                                                                                             | 02/03/2010                                                                                                                                      |                                               |

| Name and n                | nailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL ~ 2280 HV Riliswijk     | Authorized officer                                                                                                                              |                                               |

|                           | Tel. (+31–70) 340–2040,<br>Fax: (+31–70) 340–3016                                                           | Boero, Mauro                                                                                                                                    |                                               |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/EP2009/067340

| Patent document cited in search report |    | Publication date | Patent family<br>member(s) |                                                                | Publication<br>date                                                |

|----------------------------------------|----|------------------|----------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|

| US 2008105299                          | A1 | 08-05-2008       | CA<br>EP<br>WO             | 2668103 A1<br>2092571 A1<br>2008057202 A1                      | 15-05-2008<br>26-08-2009<br>15-05-2008                             |

| US 4253881                             | A  | 03-03-1981       | AU<br>AU<br>FR<br>GB<br>IT | 524635 B2<br>5202279 A<br>2440081 A1<br>2034973 A<br>1125514 B | 23-09-1982<br>01-05-1980<br>23-05-1980<br>11-06-1980<br>14-05-1986 |

| US 5009719                             | Α  | 23-04-1991       | DE<br>JP                   | 4004559 A1<br>2218174 A                                        | 30-08-1990<br>30-08-1990                                           |

| US 4248675                             |    | 03-02-1981       | NONE                       |                                                                |                                                                    |