## Minimum power design of RF front ends

Citation for published version (APA):

Baltus, P. G. M. (2004). Minimum power design of RF front ends. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR580521

DOI:

10.6100/IR580521

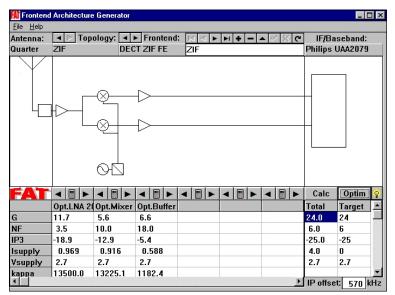

Document status and date:

Published: 01/01/2004

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Minimum Power Design of RF Front Ends

**Peter Baltus**

Cover: JWL Producties Eindhoven

# Minimum Power Design of RF Front Ends

# **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof. dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op 16 september 2004 om 16.00 uur

door

Petrus Gerardus Maria Baltus

geboren te Sittard

Dit proefschrift is goedgekeurd door de promotoren:

prof. dr. ir. A.H.M. van Roermund

en

prof. ir. A.M.J. Koonen

© Peter Baltus 2004

All rights reserved.

Reproduction in whole or in part is prohibited without the written consent of the copyright owner Printing: Printservice TU/e

# **Contents**

| List of syn | ıbols xi                                           |

|-------------|----------------------------------------------------|

| Ma          | in Symbols xi                                      |

| Sub         | scripts                                            |

| Abbreviat   | ions xiii                                          |

| 1 Introduc  | ction                                              |

|             | Trends in RF frequencies                           |

|             | Relevance of RF front ends                         |

|             | Relevance of low power                             |

|             | Relevance of fundamental limits                    |

|             | Thesis overview                                    |

| 2 Status ai | ıd trends                                          |

|             | State of the art in low power literature           |

|             | Trends in low power design                         |

|             | Trends in RF design methods                        |

| 3 Low pow   | ver problem                                        |

|             | Elementary operations and signal processing stages |

|             | Gain                                               |

| 0.2         | 3.2.1 Gain in long-range systems                   |

|             | 3.2.2 Gain in short-range systems                  |

| 3 3         | Frequency conversion                               |

|             | Frequency selectivity                              |

|             | Other operations                                   |

| 2.0         | 3.5.1 Other systems                                |

| 3.6         | Summary and conclusions                            |

| 1 A casa st | udy: the DECT front end                            |

|             | Introduction                                       |

|             | The DECT system                                    |

| 7,2         | 4.2.1 Frequency allocation                         |

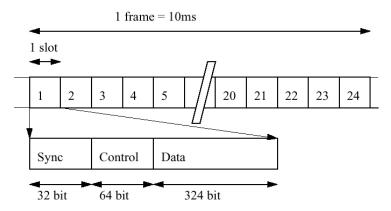

|             | 4.2.2 Time slot structure                          |

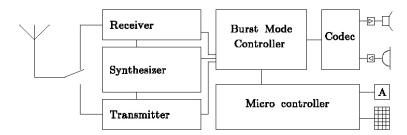

|             | 4.2.3 DECT transceiver architecture                |

|             | 4.2.4 Requirements                                 |

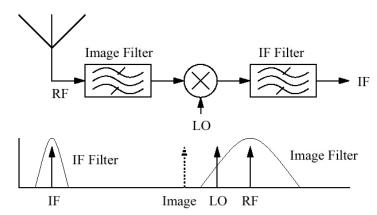

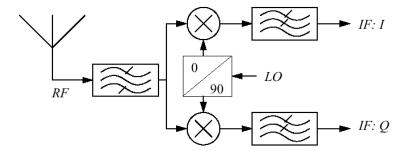

| 43          | Zero-IF receivers                                  |

| 7.5         | 4.3.1 Zero-IF receiver architecture                |

|             | 4.3.2 Advantages                                   |

|             | 4.3.3 Disadvantages                                |

|             | 4.3.4 Comparison                                   |

| ΔΛ          | Design                                             |

| 7. <b>7</b> | 4.4.1 Front End design                             |

|             | 4.4.2 Package                                      |

|             | 1.1.2 1 uonugo                                     |

Contents

|           | 4.4.3 Voltage-controlled low-noise amplifier                 | 49  |

|-----------|--------------------------------------------------------------|-----|

|           | 4.4.4 Mixers                                                 |     |

|           | 4.4.5 Phase shift circuit                                    |     |

|           | 4.4.6 IF circuit                                             | 57  |

| 4.5       | Implementation and results                                   |     |

|           | Summary and conclusions                                      |     |

|           |                                                              |     |

| 5 A minim | um-power design method                                       | 65  |

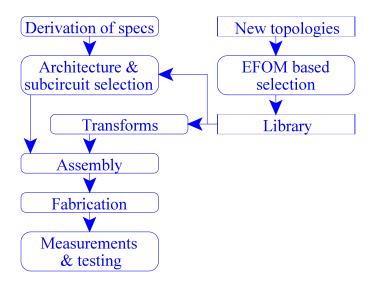

|           | Design flow                                                  |     |

|           | A SIT and EFOM based design procedure                        |     |

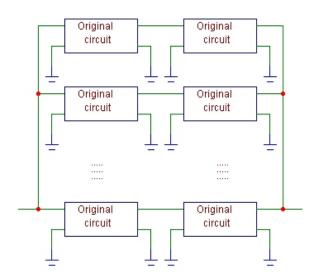

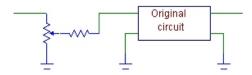

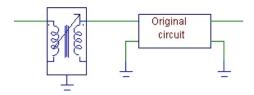

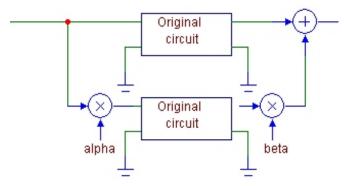

|           | Structure independent transforms (SITs)                      |     |

|           | 5.3.1 A set of structure independent transforms              |     |

|           | 5.3.2 Orthogonal SITs (OSITs)                                |     |

| 5 4       | Equivalent figures of merit (EFOMs)                          |     |

|           | Optimum distribution of gain, linearity and noise            |     |

| 5.5       | 5.5.1 General Problem                                        |     |

|           | 5.5.2 The solution for n=2                                   |     |

|           | 5.5.3 The General Solution                                   |     |

|           | 5.5.4 Discussion                                             |     |

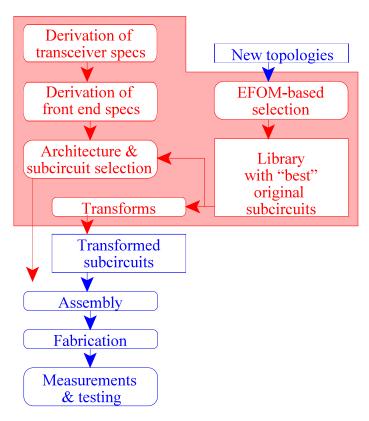

| 5.6       | A minimum-power front-end design procedure                   |     |

| 5.0       | 5.6.1 Derivation of transceiver specifications               |     |

|           | 5.6.2 Derivation of front end specifications                 |     |

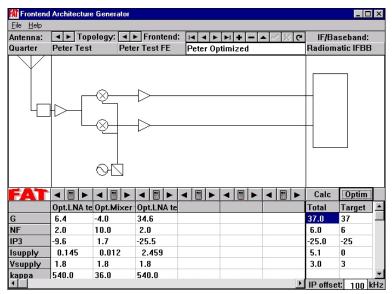

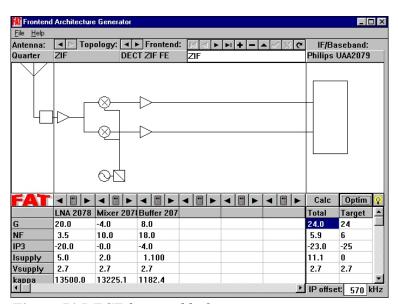

|           | 5.6.3 Architecture and subcircuit selection                  |     |

| 5 7       |                                                              |     |

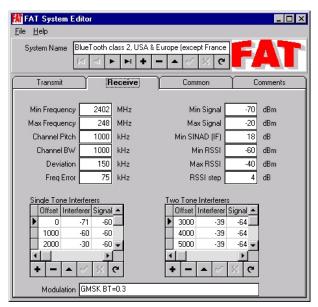

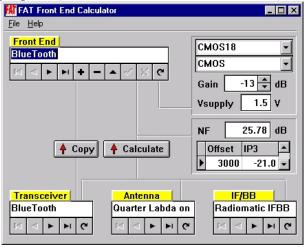

|           | A minimum-power front-end design tool                        |     |

|           | Summary and conclusions                                      |     |

| 3.9       | Summary and conclusions                                      | 100 |

| 6 Low nov | ver boundary conditions                                      | 111 |

| 6.1       | System                                                       | 111 |

| 0.1       | System                                                       |     |

|           | <u> •</u>                                                    |     |

|           | 6.1.2 Receiver sensitivity                                   |     |

|           | 6.1.3 Range                                                  |     |

|           | 6.1.4 Frequency                                              |     |

|           | 6.1.5 Antenna Gain                                           |     |

| ( 2       | 6.1.6 Antenna interface losses                               |     |

| 6.2       | Circuit                                                      |     |

|           | 6.2.1 Circuits for short-range systems                       |     |

|           | 6.2.2 Circuits for long-range systems                        |     |

| 6.3       | Technology                                                   |     |

|           | 6.3.1 A new FOM for the gain of active devices               |     |

|           | 6.3.2 An EFOM for active devices                             |     |

|           | 6.3.3 Influence of passive devices                           |     |

|           | 6.3.4 An optimized low-power IC process: Silicon on Anything |     |

| 6.4       | Summary and conclusions                                      | 135 |

|           |                                                              |     |

| -         | ver front end circuits                                       |     |

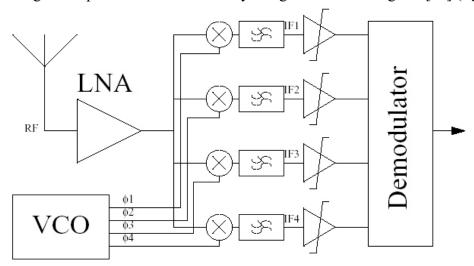

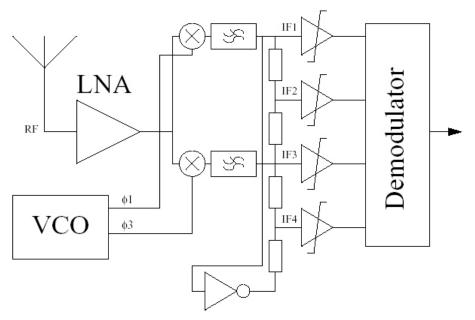

| 7.1       | Transceiver architecture                                     | 138 |

Page viii Contents

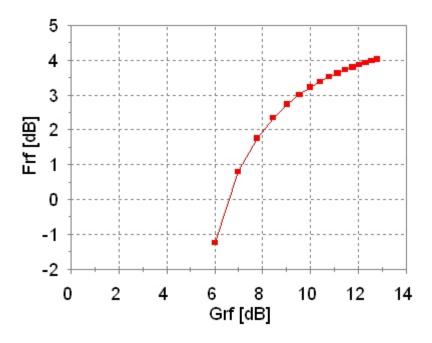

| 7.2        | Receiver front end                               | . 141 |

|------------|--------------------------------------------------|-------|

| 7.3        | IF and demodulator                               | . 145 |

| 7.4        | Summary and conclusions                          | . 149 |

|            | •                                                |       |

| 8 RF Platf | orms                                             | . 151 |

|            | Introduction                                     |       |

|            | RF Platform elements                             |       |

|            | Architecture and partitioning                    |       |

|            | Building block specification                     |       |

|            | Design method                                    |       |

|            | RF Platform Implementation                       |       |

|            | Summary and conclusions                          |       |

|            | •                                                |       |

| Conclusio  | ns                                               | . 165 |

| Red        | commendations for further research               | . 166 |

|            |                                                  |       |

|            | nication                                         |       |

| A.1        | Radio Communication                              | . 170 |

| A.2        | 2 Translating Messages into Radio Signals        | . 172 |

| A.3        | Sharing the radio channel                        | . 174 |

|            |                                                  |       |

|            | munication systems history                       |       |

|            | Cellular phone systems                           |       |

|            | Cordless phone systems                           |       |

|            | Wireless data                                    |       |

| B.4        | Telecommunication system parameters              | . 182 |

|            | DE C                                             | 105   |

|            | logy impact on RF performance                    |       |

| C.I        | IC Technology scaling                            |       |

|            | C.1.1 IC Device Types                            |       |

|            | C.1.2 Lateral devices                            |       |

| ~ •        | C.1.3 Vertical devices                           |       |

| C.2        | Other technology-induced performance limitations |       |

|            | C.2.1 Modeling problems                          |       |

|            | C.2.2 Inter-block interaction                    | . 194 |

| D C        | 4 J 41 . J. 0 14 .                               | 105   |

|            | t design methods & results                       |       |

|            | Automatic versus manual design methods           |       |

|            | 2 Iterative versus single-shot methods           |       |

|            | Algorithmic versus heuristic methods             |       |

|            | Model versus reality based methods               |       |

|            | Exact versus approximate methods                 |       |

|            | Explicit and implicit design methods             |       |

|            | Bottom-up versus top-down design methods         |       |

|            | Custom versus reuse design methods               |       |

| D.9        | Abstraction levels covered by design methods     | . 201 |

Contents Page ix

| E Limiting in zero-IF receivers                        | 203 |

|--------------------------------------------------------|-----|

| E.1 Problems with limiting in zero-IF receivers        |     |

| E.2 Existing solutions                                 |     |

| E.3 New solutions                                      |     |

| E.3.1 Low-complexity generation of multiple IF signals |     |

| E.3.2 Accurate reconstruction in superhet receivers    |     |

| E.3.3 Accurate reconstruction in zero-IF receivers     |     |

| F Solution of the general problem                      | 227 |

| G FAT transforms                                       | 235 |

| G.1 Deriving front end specifications                  | 239 |

| H Definitions & derivations                            | 243 |

| H.1 S-parameters for a complex source impedance        | 243 |

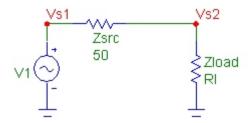

| H.2 Distortion                                         | 246 |

| H.2.1 IP3                                              | 246 |

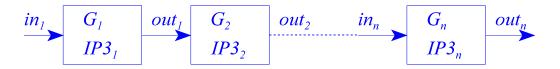

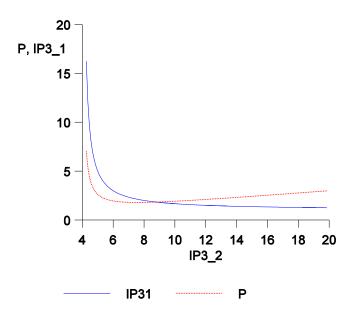

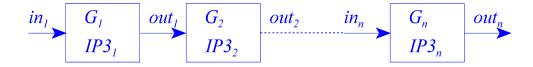

| H.2.2 IP3 of cascaded stages                           | 251 |

| References                                             | 257 |

| List of Publications and patents                       | 265 |

| Summary                                                | 269 |

| Samenvatting                                           | 271 |

| Acknowledgments                                        | 273 |

| Biography                                              | 277 |

| Biografie                                              | 279 |

Page x Contents

# List of symbols

## **Main Symbols**

T

Absolute temperature

```

Power linearity parameter; \kappa = P/(G IP3)

κ

C

Capacitance

f

Frequency

DR

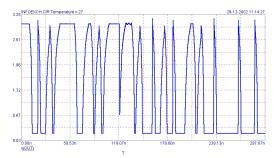

Dynamic range

DR_o

Dynamic range of the desired signal

DR_{i}

Dynamic range of the desired signal with a single interferer

Dynamic range of the desired signal with two interferers

DR,

F

Noise factor

G

Gain

G_{\mathfrak{p}}

Realized power gain, or power gain: P<sub>out,del</sub>/P<sub>in,del</sub>

G_{t}

Transducer power gain: P<sub>out,del</sub>/P<sub>in,av</sub>

G_{av}

Available power gain: P<sub>out,av</sub>/P<sub>in,av</sub>

Maximum power gain: Pout, av/Pin, del

G_{max}

G_{\nu}

Realized voltage gain; G = G_v / \zeta

Transconductance

gm

Ι

Current

HD2

Second-order harmonic power of the output signal

IP2

Second-order intercept input power

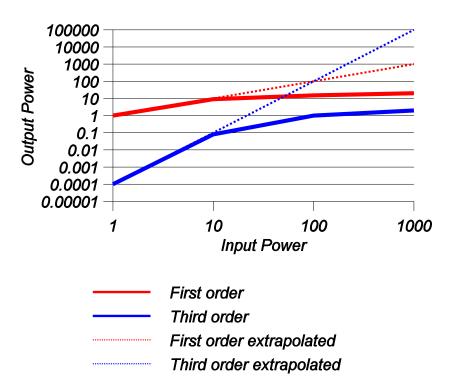

HD3

Third-order harmonic power of the output signal

IP3

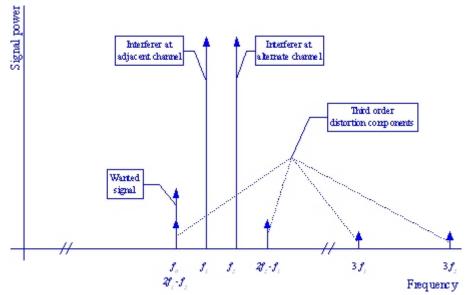

Third-order intercept input power

IP3_{o}

Third-order intercept input power measured for DC input signals

IP3_1

Third-order intercept input power measured for single-tone input signals

Third-order intercept input power measured for two-tone input signals

IP3,

IP3′

Third-order intercept single-tone input power measured for two-tone input signals

J

Current density

Boltzmann constant; k approximately equals 1.380658e-23

k

L

Length of a device, or inductance value

NF

Noise figure; NF = 10 \log(F)

Second-order intercept output power

OIP3

Third-order intercept output power

P

Power

PAE

Power added efficiency

R

Resistance

```

List of symbols Page xi

```

V VoltageW Width of a deviceVHD2 Second-order harm

```

VHD2 Second-order harmonic voltage of the output signal

VIP2 Second-order intercept input voltage

VHD3 Third-order harmonic voltage of the output signal

VIP3 Third-order intercept input voltage

Z Impedance

Ratio of load and source impedance,  $\zeta = Z_l/Z_{src}$

## **Subscripts**

```

available (as in available power)

av

del

delivered (as in delivered power)

if

if circuit

rf

rf circuit

running index, e.g. indicating the ith stage in a cascade

Ι

tot

input

in

out

output

running index for e.g. cascaded subcircuits

I

1

load

src

source

eff

effective

b

base

c

collector

emitter

e

base-collector

bc

be

base-emitter

collector-substrate

cs

dist

distortion component

fund

fundamental component (desired signal)

base

signal frequency component corresponding to the input frequency

third

signal frequency component corresponding to 3 times the input frequency

```

Page xii List of Symbols

# **Abbreviations**

AM Amplitude Modulation

AMPS Advanced Mobile Phone System

BT Bluetooth, a wireless personal area network standard

CDMA Code division multiple access

CDMAOne DSSS CDMA system, also called IS-95

CT0 Cordless Telephony System 0

CT1 Cordless Telephony System 1

CT2 Cordless Telephony System 2

DECT Digital European Cordless Telecommunications system

DCS Digital Communication System (GSM system in 1800MHz band)

DSSS Direct sequence spread spectrum

EDGE QPSK-based modulation for GSM with higher spectrum efficiency

EFOM Equivalent Figure of Merit

EMF Electromagnetic Electromagnetic Field

ETSI European Telecommunications Standardization Institute

FDMA Frequency division multiple access

FDD Frequency division duplex (also sometimes called "full duplex")

FHSS Frequency hopping spread spectrum

FM Frequency Modulation

FOM Figure of Merit

FSK Frequency Shift Keying

GFSK Gaussian Filtered Frequency Shift Keying

GPRS General Packet Radio Services, multislot packet service over GSM

GSM Global System for Mobile Communication

HSCSD High speed circuit switched data, multislot extension to GSM

IEEE 802.11 Family of WLAN standards

IEEE 802.11a WLAN standard for data rates up to 54Mbps

at RF frequencies between 5GHz and 6GHz

IEEE 802.11b WLAN standard for data rates up to 11Mbps

at RF frequencies between 2.4GHz and 2.5GHz

IEEE 802.11g WLAN standard for data rates up to 54Mbps

at RF frequencies between 2.4GHz and 2.5GHz

I-mode Web-like services across GSM and PDC systems IS-95 DSSS CDMA system, also called CDMAOne

ISDN Integrated Services Digital Network

LNA Low noise amplifier

MSK Minimum Shift Keying

NMT Nordic Mobile Telephony system

Abbreviations Page xiii

OFDM Orthogonal Frequency Division Multiplex

PCS Personal Communication System (used for GSM system in the

1900MHz band, as well as for IS-95 systems)

PDC Personal digital cellular, cellular phone system in Japan

PHP Personal Handy Phone system (Japan)

PHS Personal Handy System (Japan)

POTS Plain Old Telephony System (analog phone system)

PSK Phase shift keying

QPSK Quadrature phase shift keying

RF Radio Frequency

SDMA Space Division Multiple Access

SMS Short message service (short text messages over GSM)

TDMA Time division multiple access

TDD Time division duplex

UMTS Universal Mobile Telecommunications System, a standard for the

third generation cellular phone & data systems.

WAP Wireless application protocol, providing web-like services

across the GSM system

WAN Wide Area Network

WCDMA Wideband CDMA, 3G standard originated in Japan and now

unified with UMTS

WLAN Wireless Local Area Network

Page xiv Abbreviations

# Introduction

Communication, in all its guises, makes the difference between a number of lonesome individuals and a community. It enables cooperation and the development of cultures. In this sense, communication has played an essential role in the development of human civilization [1].

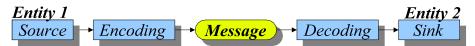

In recent times, electrical systems have been developed to support and augment communication. Among others, these systems allow communication across much greater distances than would normally be practical or even possible. The electrical systems that enable such communication are called telecommunication systems [2]. Telecommunication systems such as telephone, television and the Internet are changing the communication between people dramatically, and have a correspondingly big impact on communities, cultures and economies. This makes telecommunication systems a very relevant research topic. Consequently, many aspects of telecommunication systems are being studied all over the world.

Since the beginning of the previous century, propagation of electromagnetic (EM) waves through space has become a very popular basis for many telecommunication systems, since it allows electrical, but wireless, communication systems. Devices that use such EM wave propagation in the frequency range of approximately 10kHz to around 1THz are commonly called radios [4]. Since radios allow communication without having to build up a wired connection between the devices, they allow the mobile use of communication devices, for example in cars (figure 1). Even though mobile use is not quite impossible using wired connections [5], it is highly impractical.

Especially for mobile use, the energy consumption of the radio is very important, since most mobile devices depend on a battery for their operation. Their energy consumption then determines the amount of time that they can be used without replacing or recharging the battery, and thus the cost and convenience of using such a device. The time that a mobile device can be used without recharging is often split in the standby time

and the talk time. The standby time is the time in which the device is not actively communicating, but only monitoring the radio channel for any incoming calls. In this mode of operation, the rate at which the battery is discharged depends mostly on the receiver. The talk time is the time in which the device is actively communicating, and both the transmitter and receiver are active. In this mode of operation, the transceiver usually dominates the battery discharge rate.

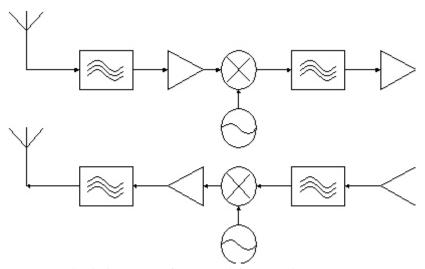

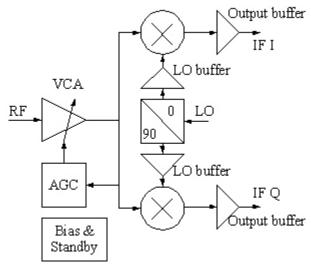

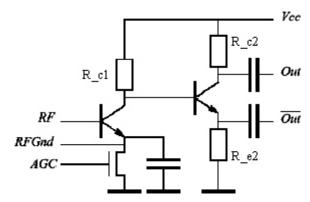

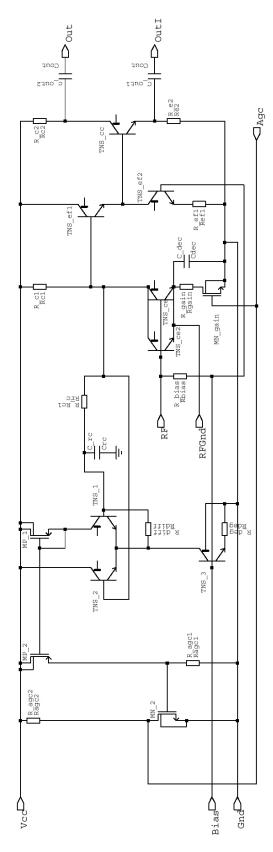

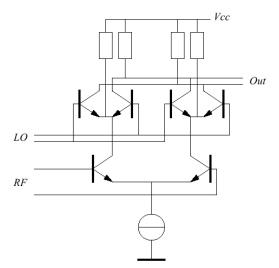

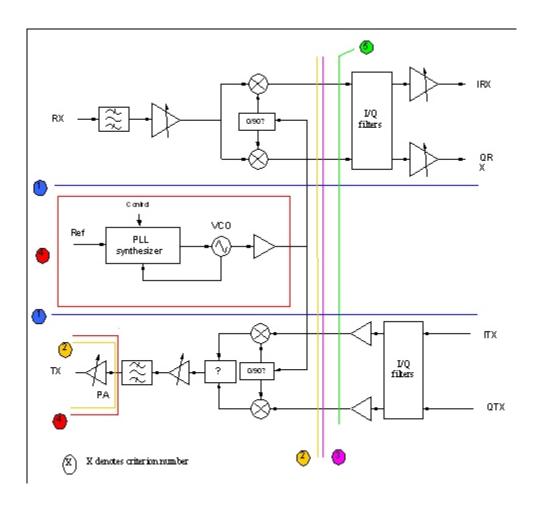

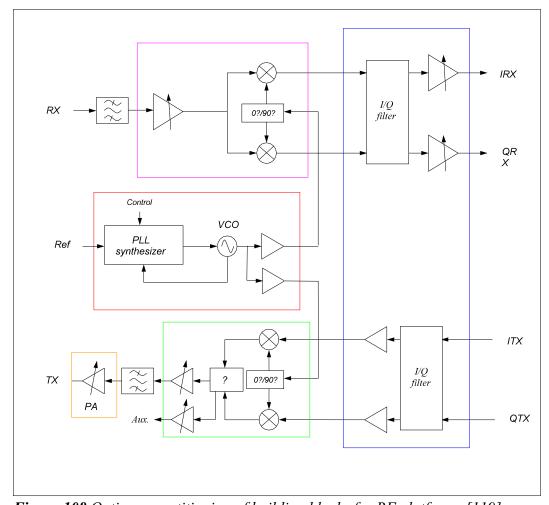

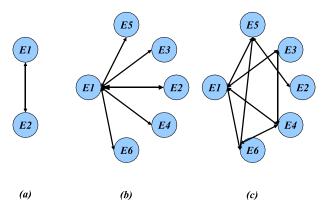

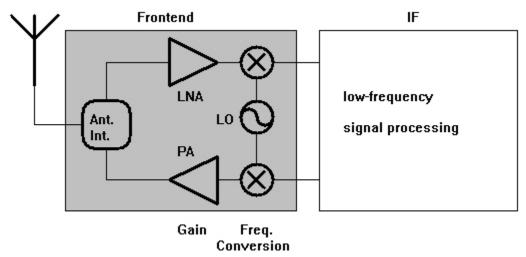

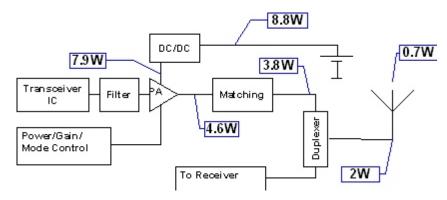

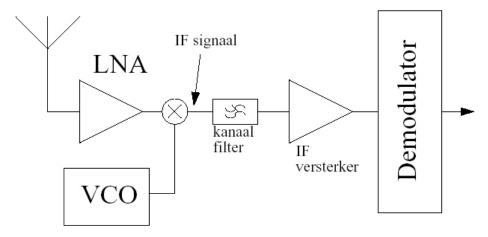

The radio frequency (RF) front end is the part of a radio that interfaces between messages in the form of electrical signals and the EM field (through the antenna), making it an essential part of any radio. A block diagram of a typical RF front end is shown in figure 3. Even though the complexity (in terms of number of components) of most RF front ends is small compared to other parts of modern radios and mobile devices, the RF front end is usually responsible for a significant part of the cost, performance and power consumption (both in terms of talk time and standby time) of the total radio.

*Figure 1* First mobile phone attempts (Copyright © 2003 Lucent Technologies [109])

Different telecommunication systems support different types of communication. For example, broadcast systems support uni-directional, point-to-multipoint communication, whereas cellular systems support bi-directional, point-to-point communication. The various types of communication and their messages, as well as the particular properties of radio communication, are discussed in more detail in appendix A.

Telecommunication systems are evolving quickly, and this has a significant impact on the requirements for RF front ends. The history of telecommunication systems and their properties is discussed in more detail in appendix B. The main trends, especially with respect to the radio frequencies, will be discussed in Section 1.1.

The variety of telecommunication systems results in widely varying requirements for RF front ends. This makes a completely general study of RF telecommunication front ends impractical. The context for this research is therefore limited to the current cellular, cordless, and wireless data systems. The relevance of the main topics of this thesis within this context, namely RF front ends, low power, and fundamental limits, will be discussed in the remainder of this chapter.

## 1.1 Trends in RF frequencies

In the past, the range of frequencies that could be used for new radio systems was limited at low frequencies by the availability of unused spectrum, and at high frequencies by the availability of relatively cheap technology in which the radio could be implemented.

With progress in technology, and increasing scarcity of free spectrum at lower frequencies, radio frequencies for wireless devices have increased. They are currently concentrated in the 1GHz to 2GHz region. Especially the explosive growth of the cellular phone, and the resulting move from bands below 1GHz to the 2GHz region, has been driving the development of cheap IC technologies with increased bandwidths.

This is currently changing: cellular and other wireless systems that need to work over longer distances will be limited by the decreasing link budget at high frequencies. In the radio transmission equation below (eq. 1),  $P_{RX}$  is the available signal power from the receive antenna,  $P_{TX}$  is the power applied to the transmit antenna,  $G_{RX}$  and  $G_{TX}$  are the gains of the receive and transmit antennas,  $\lambda$  is the wavelength, r is the distance between receive and transmit antenna, and  $\alpha$  is the propagation constant. This equation holds in the far field of the antennas, assuming that the polarizations of both antennas are perfectly matched.

The propagation constant  $\alpha$  depends on the environment of the antennas. In free space, this constant is 2. Inside buildings it varies between 1.81 and 5.22, and tends to be higher at higher frequencies [21], because the attenuation of walls increases with frequency.

$$P_{RX} = P_{TX} G_{RX} G_{TX} \left( \frac{\lambda}{4\pi r} \right)^{\alpha}$$

(1)

For omnidirectional antennas with constant gains, the link budget scales as (eq. 2):

$$\frac{P_{RX}}{P_{TX}} \sim \frac{1}{f^{\alpha}} \tag{2}$$

Increasing transmit power to make up for this reduction in the link budget is impractical in the frequency region above roughly 5GHz, especially for portable, battery-powered systems. Another solution would be the use of high-gain antennas, but since such antennas will also be highly directional, they are not practical for portable wireless devices, unless advanced beam-steering approaches are applied and a line-of-sight path is available.

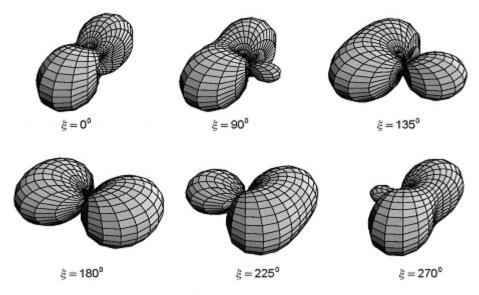

Since neither of these remedies is very practical, it seems likely that there will be a split in the frequency bands for short-range, mostly line-of-sight, high-bandwidth, high-bitrate connections, and long-range (including outdoors) connections that need to propagate in all directions and through walls and other objects. The essential distinction is in the frequency f, the propagation constant  $\alpha$ , and antenna gains  $G_{RX}$  and  $G_{TX}$ , but for practical purposes these systems will be referred to as long-range and short-range systems.

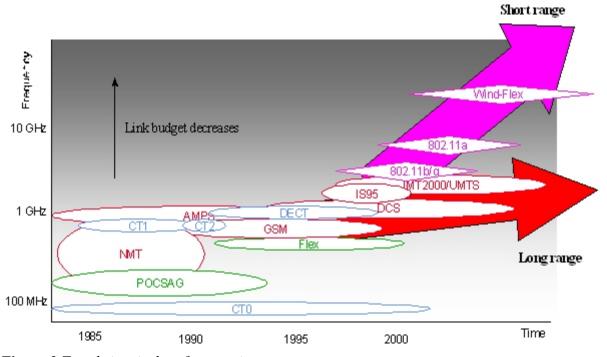

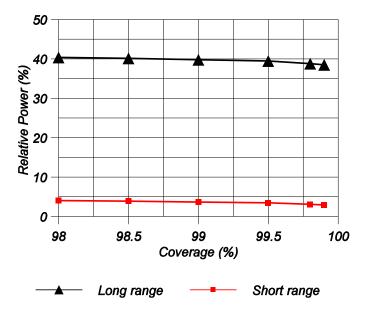

Short-range systems will continue to move to higher frequency bands to satisfy the need for increased bandwidths, whereas long-range systems will be limited to frequencies below 5GHz. These long-range systems will concentrate on efficient use of the increasingly scarce spectrum below 5GHz through efficient modulation schemes, efficient access mechanisms and adaptive use of the available resources. This split between short-distance, high-bandwidth systems and long-range systems is shown in fig. 2.

Front ends in long-range systems will require high linearity, low noise figures and high power efficiency for most efficient use and re-use of the spectrum. Since the frequencies in these systems will not increase significantly in the future, but the bandwidths of the devices in future IC technologies will continue to increase for many years to come, the power dissipation is typically limited by the dynamic range, rather than the frequency.

Front ends in high-bitrate, high-bandwidth, short-range systems will probably

Figure 2 Trends in wireless frequencies

continue to move to higher frequencies. The high bandwidths for these systems will only be available at increasingly high frequencies in e.g. the 5GHz and 17GHz bands. The power dissipation in front ends for these systems will be limited by the high frequencies at which the front-end circuits will need to operate. Such systems will have relaxed requirements for sensitivity and linearity compared to long-range systems, and these requirements will typically be met at the current levels that are needed to achieve the high frequency operation of the front-end circuits. Therefore, the power dissipation is typically limited by the operating frequency rather than the dynamic range.

This divergence of specifications can already be found in current systems such as the GSM cellular system (for long range) and the Bluetooth system (for short range). Specification parameters that are especially affected are sensitivity and linearity. Sensitivity is affected, among others, by the noise figure (NF) of the receiver. The noise figure of a circuit is defined as the ratio between the input-referred noise of that circuit, and the thermal noise from the source that provides the input signal. The relation between sensitivity and noise figure is discussed in more detail in Appendix G. Linearity is affected, among others, by the third order intercept point (IP3). IP3 is defined as the input power at which the extrapolated third-order output power equals the extrapolated power of the desired signal. This is discussed in more detailed in Section H.2, and the relation between IP3 and the effect of interferers is discussed in more detail in Appendix G. Table 1 shows the NF and IP3 requirements as defined by these standards.

|           | GSM     | Bluetooth |

|-----------|---------|-----------|

| Frequency | 950 MHZ | 2450 MHZ  |

| NF        | 9 dB    | 25 dB     |

| IP3       | -10 dBm | -21 dBm   |

**Table 1** Sensitivity and linearity specs for GSM (long-range) and Bluetooth (short-range) systems

This table shows that the smaller received signals and the stronger interferers that long-range systems need to work with translate as expected in lower noise figures and higher IP3 values. Please note that competitive implementations usually need to perform better than the performance set in a standard. Still, a significant difference between both types of systems remains. A more extensive overview of system parameters can be found in appendix B.4.

Future portable wireless devices will be able to set up both short-range, high-bitrate links and long-range connections, depending on the environment and the needs of the user. This can be achieved through the use of multiple standards in one device, e.g. Bluetooth and GSM, or through a single standard that supports different trade-offs between range and data rate, such as UMTS/IMT 2000. In such multi-mode devices, the properties of the transceiver front end will depend on the particular mode that the device is being operated in. The optimizations discussed in this thesis will apply to each of these modes. Although the methods proposed in this thesis can be applied to current systems, they might need to be adapted to deal with future systems based on very different approaches, such as time-domain ultra-wideband systems.

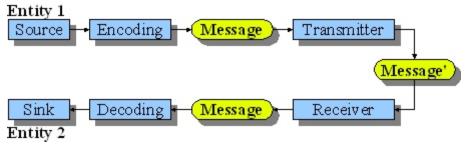

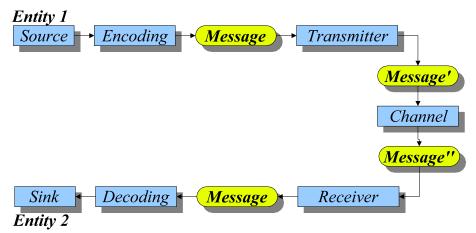

#### 1.2 Relevance of RF front ends

Communication is the process of exchanging information between two or more entities. In radio communication systems, this information is exchanged through electromagnetic signals. The translation of the messages into electromagnetic signals and vice versa is carried out in the transmitter and receiver parts of radio communication systems. An important part of the transmitter and receiver is the RF front end, which converts between the RF signals and the low or intermediate frequency signals. (see also appendix A)

An RF front end carries out three important signal processing steps, both in the transmitter and receiver signal path:

- 1. Frequency translation, in order to obtain a signal with a frequency appropriate for further transmission or processing;

- 2. Signal amplification, in order to obtain a signal with an amplitude appropriate for further transmission or processing;

- 3. Signal filtering, in order to remove unwanted signal components generated by other transceivers or by the signal-processing circuits in the transceiver itself.

A simple block diagram of a front end is shown in figure 3.

Figure 3 Block diagram of a typical front end

This block diagram shows that both gain and filtering are typically distributed throughout the front end. The frequency conversion, here shown in a single conversion step using mixers and local oscillator signals, can also be implemented as two or more conversion steps, since this can reduce the requirements on the performance of the individual filter, gain, and mixer blocks. A simple antenna interface is shown here, with separate, single, transmit and receive antennas. In practice, it is often desirable to share the antenna between transmitter and receiver, in order to save cost and space. This requires switches or duplex filters between the circuits and the antenna. In addition, many systems today

use multi-band radios, requiring multiple antennas or multiple antenna feeds, which in turn require extra switches or, in some cases, varicaps. Finally, antenna diversity is becoming more practical, but also more necessary, at higher frequencies, again creating the need for more antennas and related electronics.

The oscillators used for frequency conversion are often tunable to allow channel selection already in the front end of the radio, reducing the dynamic range requirements of the filters, IF amplifiers, and data converters. These tunable oscillators are typically controlled through a synthesizer loop, adding considerable complexity in terms of number of transistors to the front end.

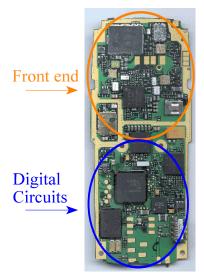

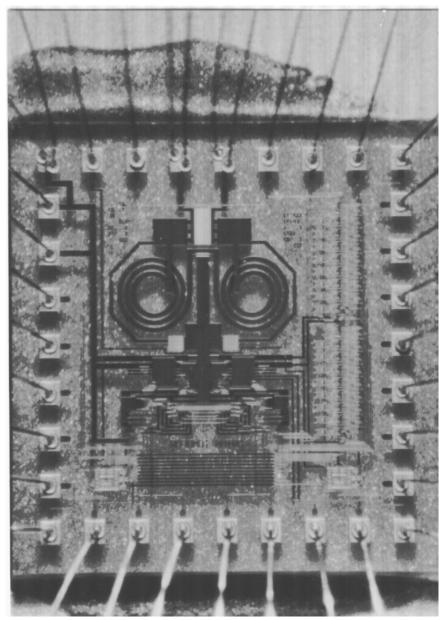

Even so, an RF front end consists of only a very limited number of active devices, often in the order of hundreds or thousands. The silicon area of the front end decreases with improvements in IC technology that cause devices to shrink in physical dimensions. Current RF front end ICs measure just a few square millimeters. Also, the desired functionality, and therefore the number of active devices, decreases with advanced transceiver architectures such as single-conversion receivers, and further digitization of the radio. Compared to the millions of transistors in the digital parts of a handset and the millions of bytes in the software, it might be assumed that the design of an RF front end is a trivial job, with little relevance for the overall handset. From such a viewpoint, it would be hard to justify any research in this area. Fortunately for RF researchers, the RF design problem is highly relevant. Figure 4 shows the inside of a modern cellular (GSM) terminal.

**Figure 4** Inside of a GSM handset

As can be seen in this picture, the front-end part contributes significantly to the size of the total handset. It also has considerable influence on other properties, such as power dissipation and bill of material. Depending on the system, and trade-offs in the design, the impact of the front end on the cost, size, and power dissipation of the total system can be between 10% and 50%. Finally, the quality of the signals, and therefore the accuracy of the messages, depends very much on the properties of the RF front end. This makes

## 1.3 Relevance of low power

RF front ends for the systems described in the previous chapters typically run from a battery that is often the largest and most expensive component in the device. The main design problem is to keep such devices small and cheap while achieving the desired functionality and performance.

The total power consumption is often dominated by the radio as much as by the digital circuits. This has an additional impact on size and cost through the battery size: in a typical cellular handset, up to 50% of the total power is consumed by the radio, both in transmit and in receive mode. Therefore, the RF front end has a major impact on achieving the design goals of a small and cheap phone. Much effort has already gone into reducing the power dissipation of RF front ends for this type of application, and significant improvements have been made over the past years [8]-[17]. Nevertheless, there seems to be no reason why, ultimately, the power dissipation should be constrained by other limits than the law of conservation of energy<sup>1</sup> and imperfections in implementation technology<sup>2</sup>.

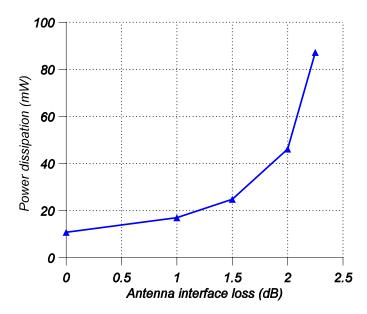

The efficiency of a circuit is defined as the ratio between the output power and the power consumed from the power supply. Transmitter efficiencies of over 40% are currently found in publications [18][19], suggesting that there is little room for improvement in this area. However, when taking into account losses in the antenna matching, filtering and switching circuits, and losses between battery and power amplifier, the overall efficiency quickly drops below 25%. Even worse, the best efficiencies are usually achieved for maximum power output levels. When power levels are decreased to more typical output levels, efficiencies often drop below 10%. In the future, we will see the emergence of more variable envelope modulation schemes, especially for the long-range systems, in order to use the available spectrum more efficiently. Also, in addition to FDMA and TDMA, CDMA will be used to allocate the available spectrum flexibly and efficiently. Variable envelope modulation schemes and CDMA access methods will increase the requirements for linearity, power control range, and accuracy of the power amplifier, resulting in overall efficiencies below 5% for output power levels 20dB or more below the maximum output power level [20]. Improved efficiency of the transmitter, at lower power levels, is therefore expected to become important. A higher efficiency of the antenna interface is likely to become even more important, since this affects performance at all power levels.

Page 8 Chapter 1: Introduction

<sup>&</sup>lt;sup>1</sup>The law of conservation of energy relates to electronic circuits, and thus to RF circuits, through the relation between power consumed from the power supply and signal inputs, and power delivered to signal outputs. The law of conservation of energy requires that, for any typical RF circuit that only exchanges energy with its environment through electrical signals and through heat dissipation, the sum of the average signal powers delivered at the output terminals is less than, or equal to, the sum of the average signal powers received at the inputs, and the power consumed from the power supply.

<sup>&</sup>lt;sup>2</sup>Although eliminating the imperfections in the implementation technology might be physically impossible.

The power dissipation of the receiver tends to be much lower than the power dissipation of the transmitter. However, since the receiver will usually be switched on for more extended periods of time than the transmitter, e.g. to check whether new calls or messages are coming in, or whether a hand-over to a different base station is needed, the power dissipation of the receiver is nevertheless very relevant.

Receiver front ends tend to consume power far in excess of the bound set by conservation of power. The output of a typical front end might drive a sigma delta analog-to-digital converter (ADC) with a real part of the input impedance of e.g.  $100k\Omega$ , at signal levels below 1Vpp. The maximum power delivered by the front end is then  $0.5V^2/100k\Omega=1.25\mu W$ . A well-optimized front end consumes around 50mW, resulting in an efficiency below 0.01% in best case conditions. For lower input signals, resulting in lower output power, the efficiency further decreases by several orders of magnitude. Since the power efficiency of current receiver front ends is this low, there should be many opportunities for power reduction.

#### 1.4 Relevance of fundamental limits

The complexity of RF circuits, when measured by the number of components, is much lower than the complexity of e.g. digital circuits. This is, of course, due to the simpler intended functionality of an RF front end circuit: it only needs to convert signals to an appropriate frequency and signal level, and filter, to some extent, some undesired signal components. Even so, the time required to develop an RF product is not proportionally shorter than that of a digital product, when taking the number of components as a reference. This has undoubtedly resulted in many debates in development groups, and in various approaches to improving the current RF IC design methods, which are sometimes perceived as inefficient and old-fashioned. Thus far, none of these approaches have resulted in RF IC development efficiencies comparable to digital IC design. Therefore, it is relevant to investigate the reasons for this lower efficiency, and to develop more efficient design methods, if possible.

Common design methods for RF front ends are based on experience, insight, and creativity of the designer. After the specifications for the product have been set, a first estimate of the distribution of gain, noise, linearity and selectivity for each of the subcircuits is made, based on experience with previous designs and/or simple calculations. The circuits are obtained from earlier designs, or from colleagues who have designed similar circuits in the past, and adapted to the new specifications. If no suitable circuits are available, they are developed from scratch.

Since the complexity of the desired functionality of an RF front end is rather low, this approach seems fairly obvious and is easy to carry out. However, mistakes made at this point in the development process can turn out to be very expensive ones indeed. They often require a redesign almost from scratch, or many iterations, to achieve acceptable results.

Subsequently, the subcircuits need to be designed and simulated. This is where an important difference between digital and RF IC design becomes relevant. RF front end circuits tend to work close to the limits of what can be achieved in a given technology, in terms of frequency, linearity and noise. In order to accurately predict the performance

of a circuit this close to the limits of a technology, one needs to take into account a large number of parasitic effects in the circuit and the package, such as parasitic capacitance, resistance, and inductance, of interconnect, as well as electrical and magnetic coupling of the interconnect and the package, crosstalk through the substrate, thermal effects, etc. Even for simple circuits, it is not practical to model and simulate all these parasitic effects, given the current state of computer hardware and software.

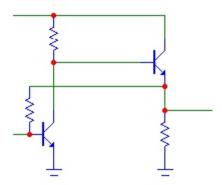

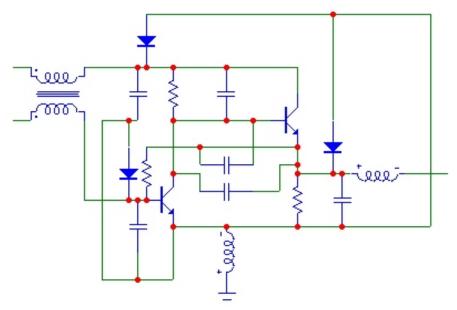

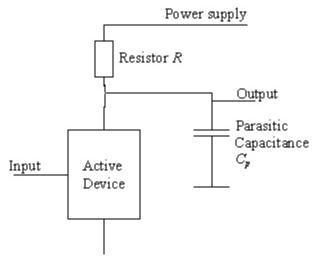

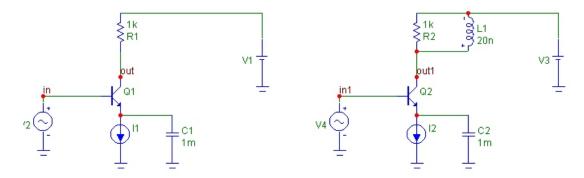

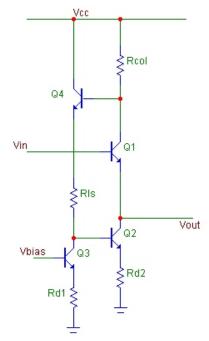

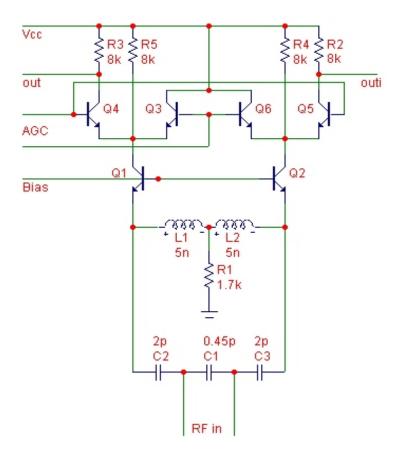

As a simplified example, figure 5 shows a circuit diagram of an amplifier as intended by the designer.

**Figure 5** Amplifier circuit as intended by the designer

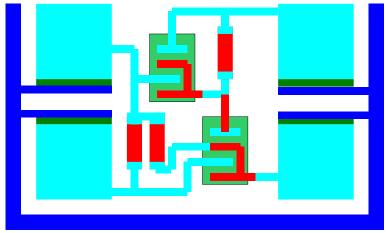

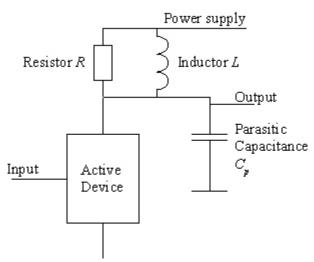

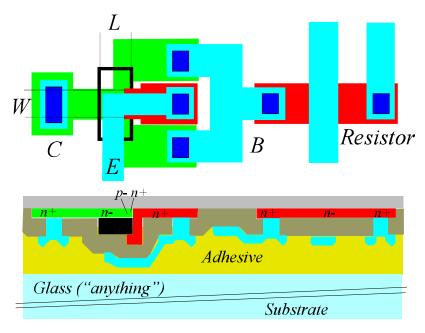

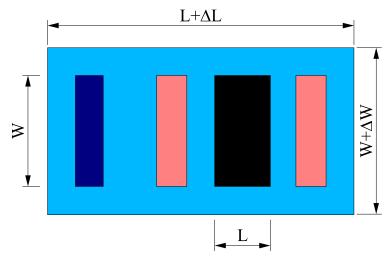

When this circuit is implemented on an IC, parasitic effects occur that are not taken into account in the schematic of figure 5 or in the models of the transistors and resistors. Figure 6 shows a simplified layout of this amplifier (in a simple, fictitious IC process): Using the layout and knowledge of the IC process, the parasitic effects in the circuit can

Figure 6 Layout of amplifier circuit

be calculated. In the schematic diagram of figure 7, a small subset of the most significant parasitic effects has been annotated.

Figure 7 Amplifier with some parasitic effects.

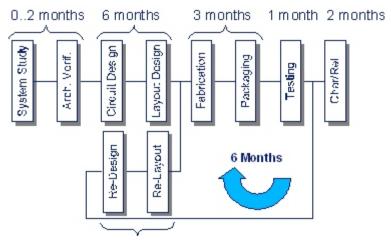

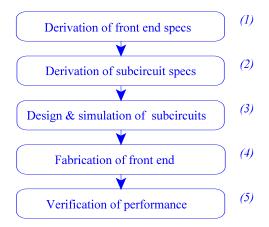

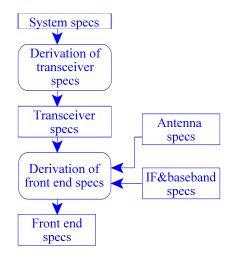

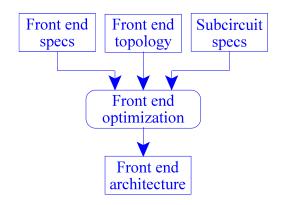

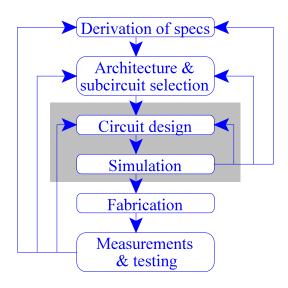

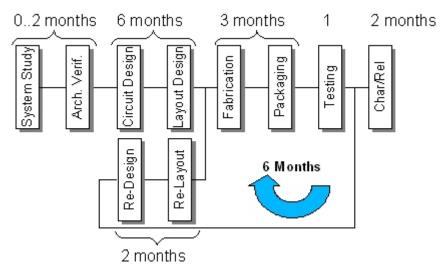

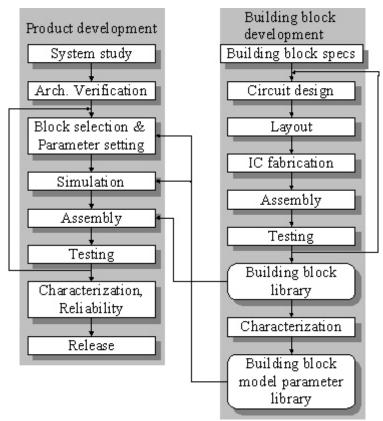

As can be seen in this simple example, making a selection of parasitic elements to be modeled and simulated is essential to keep the problem manageable and the results accurate. Except in the most simple cases, even experienced RF designers cannot always make the right selection on the first try, which leads to measurement results that differ significantly from the simulation results. As a consequence, several iterations through the IC fab are needed to achieve the desired circuit performance. This product development process is shown in the flowchart of figure 8. The times in the flowchart are indications only: they depend very much on the complexity of the product, the size of the development team, their experience, changes in specifications during the development, fab arrangements and performance, stability of the IC process, accuracy of the models, stability of the IC design tools, etc. In many cases, most of the product development time is spent in the iteration loop through fabrication.

Figure 8 IC design process

This process is basically an implementation of an algorithm that searches for the global minimum of a function P, which represents the cost as a function of all the design variables  $v_1, v_2, v_3, \ldots, v_n$ . In general, this cost includes all aspects of a circuit that need to be optimized, such as size, technology cost, number of external components that are required, etc. In this thesis, we will focus on the power dissipation, and therefore P will represent the power dissipation of the circuit. The design variables include not only the parameters of a circuit (such as transistor sizes, resistor values, power supply voltages, etc.), but also architectural choices, circuit topology selection, and other degrees of freedom in a design process that are not as easy to quantify as the circuit parameters. In principle, the global optimum can be found using a suitable algorithm and sufficient iterations in the design. In practice, however, RF product development projects often need to be completed in a (very) limited amount of time, reducing the number of iterations that can be carried out. Especially changes in the early choices of a design, such as the architecture, can result in the need to start the iteration loop all over again, and, consequently, in a considerable loss of time.

Thus far, there has been no systematic way to take power dissipation into account this early in the design process. This results in higher than desirable power dissipation of the final product, and/or a large increase in development time.

Fundamental limits, e.g. for power dissipation as a function of gain, linearity and noise, can help in the development process by giving an indication for the lowest possible power dissipation that can be achieved with a given technology for a required performance level. This insight can be used to develop efficient design methods for RF front ends with a power dissipation close to these fundamental limits. Following such design methods will greatly limit the time needed for designing minimum-power RF front ends.

#### 1.5 Thesis overview

This thesis will investigate the design of RF front ends for telecommunication systems that consume a minimum amount of power. The state of the art in low power design, especially with respect to design methods, achieved power dissipation, figures of merit, and trends, will be discussed in Chapter 2.

The problem of designing a minimum power RF front end starts with understanding the lower limits of power dissipation that can be achieved. These limits are imposed by physics and technology. In an RF front end, several different operations need to be carried out. The physics and technology imposed limits for each of these operations will be discussed in Chapter 3.

A traditional DECT RF front end is used as the basis for a discussion of low power design. Although this particular design is from 1993, the design approach is still representative for the way in which low power designs are currently carried out. For the remainder of this thesis it also provides some of the system background, and a benchmark for low power design. The DECT front end will be discussed in Chapter 4.

To design minimum power front ends, a new design method is needed. In Chapter 5, such a new design method will be introduced. It is based on a library of circuit

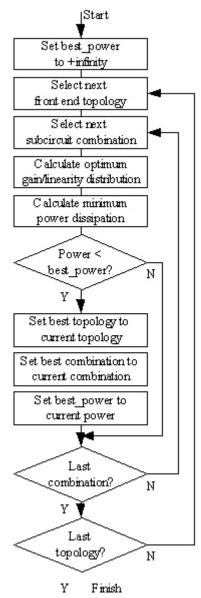

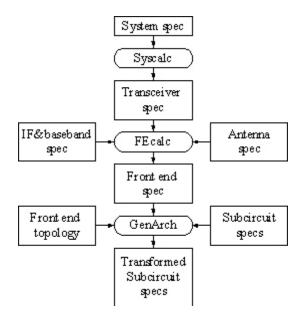

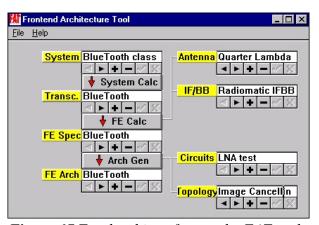

topologies that have been selected for the best low power performance. The selection, in turn, is based on a special figure of merit from the class of equivalent figures of merit, which will also be introduced in Chapter 5. Furthermore, a set of transforms that can be applied to any circuit will be developed. Such transforms are called "structure-independent transforms", or SITs. Using SITs, the optimum trade-off between the performance parameters of individual circuits within a front end can be determined. This optimum trade-off determines which transforms will be applied to the circuits from the library, in order to assemble a minimum power front end. A special tool has been developed to support this design method.

The design method can also be used to identify the boundary conditions at system, circuit and technology level that limit further power reduction. These boundary conditions, as well as the implications for the development of low-power systems, circuits, and devices, will be discussed in Chapter 6.

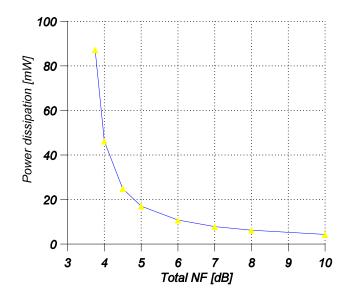

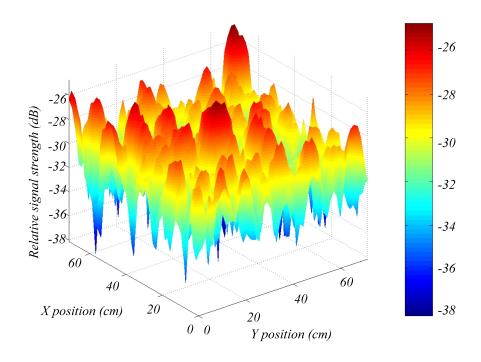

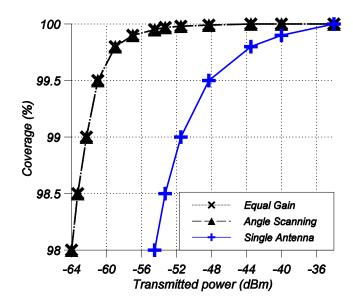

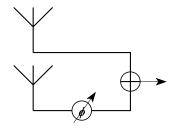

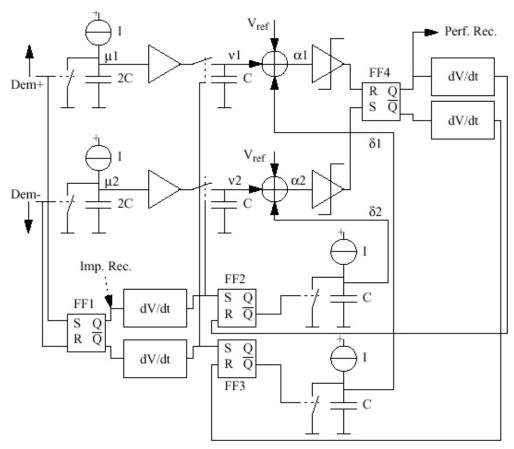

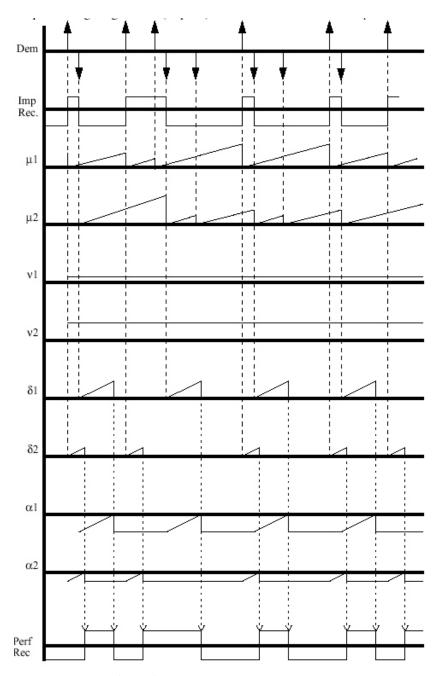

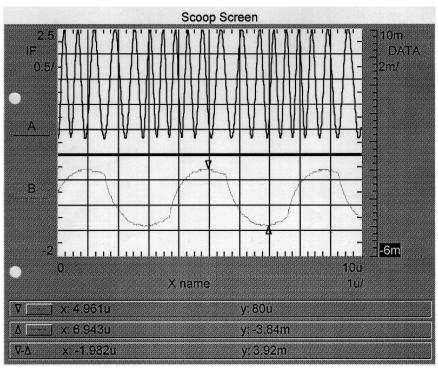

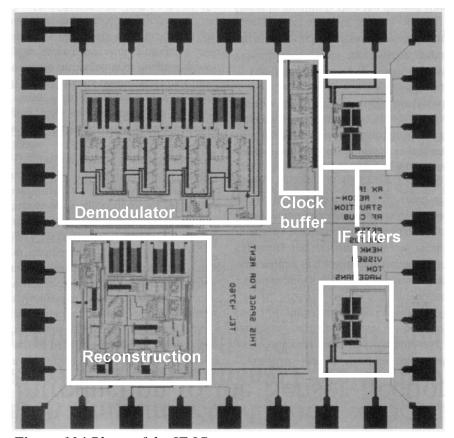

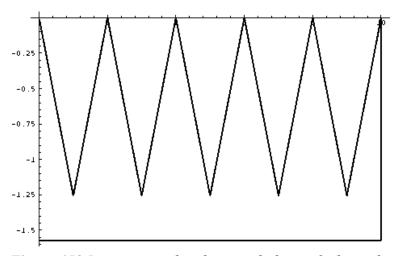

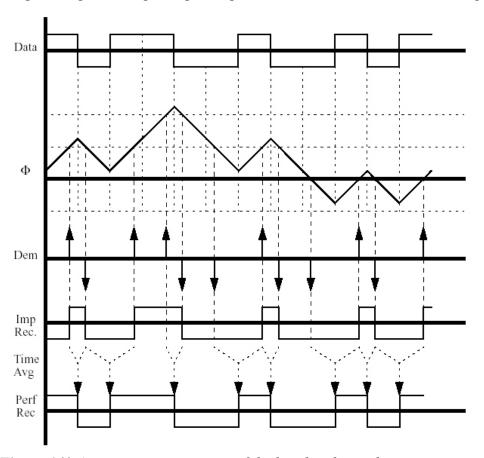

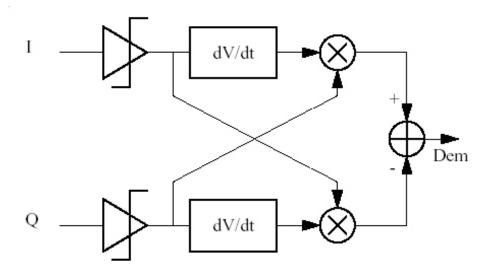

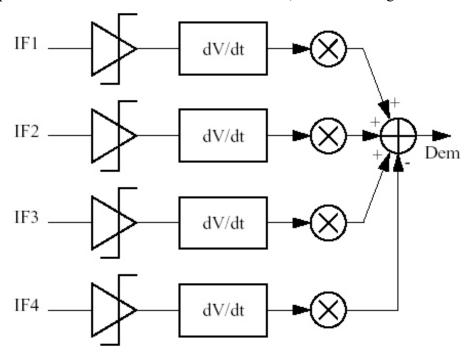

The application of several of the insights of this work to actual radio front-end circuits will be demonstrated in Chapter 7. The 3.5mW receiver includes a low-power RF front end with advanced antenna diversity, as well as a new low-power non-linear signal processing method for the IF signal. This new signal processing method is described in more detail in appendix E. It is based on the reconstruction of the phase trajectory of the received signal from the non-equidistant samples obtained from the transitions of the limiter outputs.

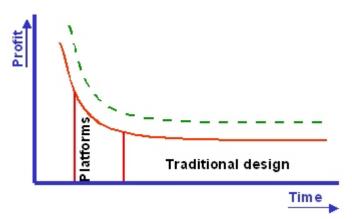

For many markets, the time-to-market is a very important consideration in addition to the power dissipation of the RF front end. One approach that is aimed at improving time-to-market is the use of a platform as the basis for new products. Chapter 8 discusses how a platform approach can be adapted to RF design, and how this can be combined with minimum power design.

The results of this research work is expected to help to improve the performance, reduce the power dissipation, and speed up the design of future RF front ends. Although this thesis focuses on RF front ends in wireless telecommunication systems, the results can be applied in a much wider range of systems and circuits, e.g. wired RF systems such as cable.

# Status and trends

Many RF design methods are currently being used, both in product development and in research. The variety is too large to allow an exhaustive treatment of all individual methods. Instead, they will be grouped in categories according to their main properties:

- Automatic design methods, as opposed to manual design methods

- Iterative design methods, as opposed to single-shot design methods

- Algorithmic design methods, as opposed to heuristic design methods

- Model-based design methods, as opposed to reality based methods

- Exact design methods, as opposed to approximate design methods

- Explicit design methods, as opposed to implicit design methods

- Bottom-up design methods, as opposed to top-down design methods

- Custom design methods, as opposed to reuse design methods

- Dedicated design methods, as opposed to general-purpose design methods

In addition, design methods might cover one, multiple, or all abstraction levels in a design. The differences between the design method categories are briefly explained in appendix D. In this section, the state of the art in low power design and design methods will be discussed in Section 2.1. Trends in low power design and RF design methods will be discussed in Sections 2.2 and 2.3.

## 2.1 State of the art in low power literature

Table 3 shows a small subset of the current design methods found in literature, categorized according to the classification system introduced in the previous section. It is obvious that even with this small subset of current design methods, all design method categories are already covered.

| Name                    | De        | le i rain i ii |          |             |             |           |       |         |       | Abs<br>leve | tract    | tion     | Literature<br>reference |                    |           |        |          |        |        |         |        |              |

|-------------------------|-----------|----------------|----------|-------------|-------------|-----------|-------|---------|-------|-------------|----------|----------|-------------------------|--------------------|-----------|--------|----------|--------|--------|---------|--------|--------------|

|                         | Automatic | Manual         | terative | Single-Shot | Algorithmic | Heuristic | Model | Reality | Exact | Approximate | Explicit | Implicit | Top Down                | Meet in the middle | Bottom up | Custom | Re-cycle | Re-use | System | Circuit | Layout |              |

| Custom design           |           | 1              | 1        |             |             | ✓         | 1     |         |       | 1           | 4        |          |                         |                    | 1         | 1      |          |        | 4      | 1       | 1      | [67]         |

| Adapt                   | 1         |                |          | /           | 1           |           | 1     |         | 1     |             | 1        |          | 1                       |                    |           | 1      | ✓        |        |        | ✓       |        | [64] [65]    |

| Trial and Error         |           | 1              | 1        |             |             | ✓         |       | ✓       |       | 1           |          | 1        |                         | 1                  |           | 1      |          |        | 1      | 1       | 1      |              |

| Module generators       | 1         |                |          | 1           | 1           |           | 1     |         |       | ✓           | 1        |          | 1                       |                    |           | 1      | ✓        |        |        |         | 1      | [68] [69]    |

| Augmented mod. Gen.     | 1         |                |          | 1           | 1           |           | 1     |         |       | 1           | 1        |          | 1                       |                    |           | 1      | 1        |        |        | 1       | 1      | [70]         |

| Exhaustive search       | 1         |                |          | 1           | 1           |           | 1     |         | 1     |             | 1        |          | 1                       |                    |           | 1      |          |        |        | 1       |        | [72][73][74] |

| Genetic algorithms      | 1         |                |          | 1           |             |           | 1     |         |       | 1           | 1        |          | 1                       |                    |           |        |          | 1      | 1      |         |        | [76]         |

| Analytical (receiver)   |           | 1              | 1        |             | 1           |           | 1     |         |       | 1           | 1        |          | 1                       |                    |           | 1      |          |        |        | 1       |        | [77]         |

| Large signal behavioral |           | 1              |          | 1           | 1           |           | 1     |         |       | 1           | 1        |          | 1                       |                    |           | 1      |          |        |        | 1       |        | [78]         |

| Analytical (mixer)      |           | 1              | 1        |             | 1           |           | 1     |         |       | 1           | 1        |          | 1                       |                    |           | 1      |          |        |        | 1       |        | [75]         |

Table 3: RF design methods and their classification

Of all current design methods, *custom design* is still the most popular. It is the main RF design method supported by the popular CAD tools such as Cadence from Cadence Design Systems (San Jose, CA, U.S.A.), and ADS from Agilent (Palo Alto, CA, U.S.A.).

The main drawbacks of custom design are:

- *low effectiveness*. It is not clear how much margin is left between the performance that has been achieved in a design, and the optimum performance that could be achieved within the given boundary conditions (specifications, technology). The results depend very much on the experience of the designer.

- *low efficiency*. The design is assembled from scratch in a (mostly) bottom-up approach, often requiring iterations across multiple abstraction levels (system, circuit, layout, hardware) to achieve the desired performance.

These drawbacks drive the research into alternative design methods which improve upon, or even eliminate, these shortcomings. Many of these alternative methods address only one or a few abstraction levels (system, circuit, layout, hardware), or can be applied only to specific subcircuits of an RF front end.

An ideal design method should cover all applicable abstraction levels, as well as all subcircuits of an RF front end, and achieve optimum performance in an effective and efficient way. Such a design method for low power RF front-end circuits does not yet exist, but will be developed in this thesis.

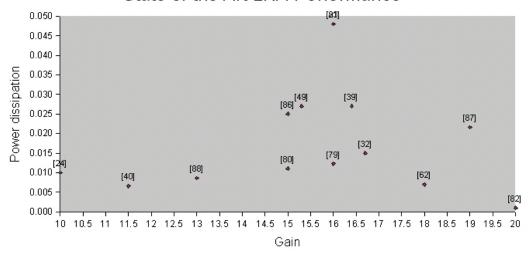

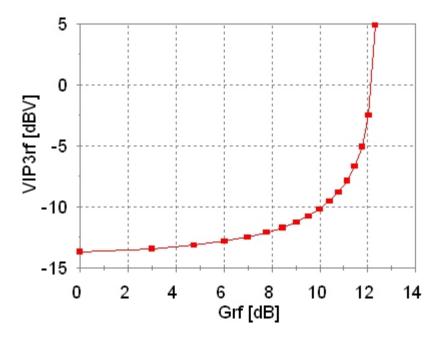

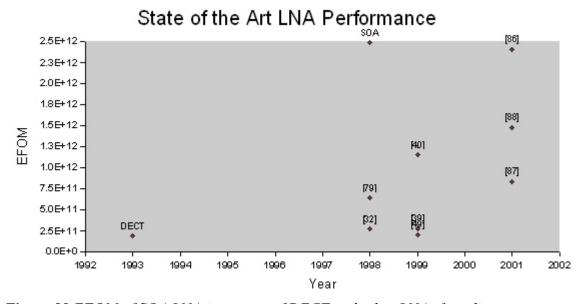

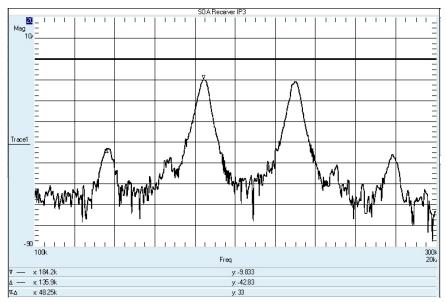

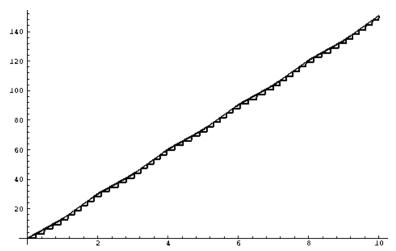

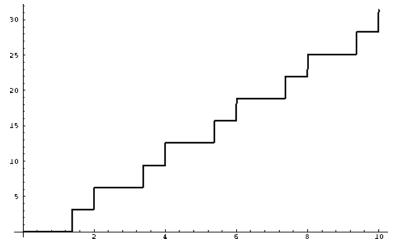

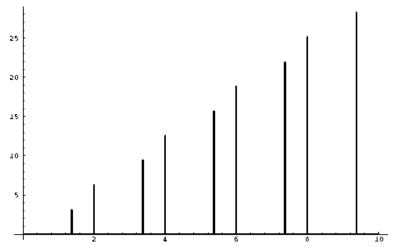

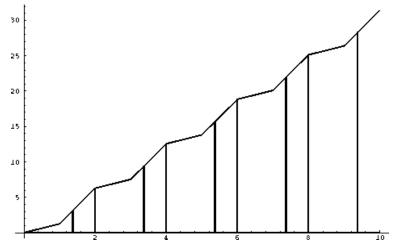

Figure 10 shows the gain and power dissipation of RF low-noise amplifiers as reported in recent literature. This figure is representative of the performance and power dissipation of other RF circuits: there is a wide variety in performance parameters and power dissipation of individual circuits.

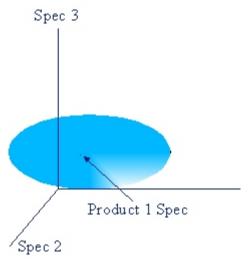

Comparing these numbers is difficult, however, since they relate to different circuit topologies, different implementation technologies, and different specifications for performance parameters such as noise, linearity, and bandwidth. A more accurate portrayal of current LNA performance would show the performance of these circuits in an *n*-dimensional space. The various dimensions would represent the relevant performance parameters, and points in this space would represent individual designs.

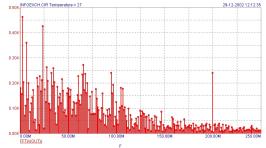

#### State of the Art LNA Performance

Figure 10 Power dissipation of recently published LNA circuits versus their gain

Since the number of relevant dimensions is significantly higher than 3, a drawing of such an n-dimensional space would not be very useful to most people. Instead, it is customary to map the points in this *n*-dimensional space onto a 1-dimensional space through a *figure of merit*.

A figure of merit, or FOM, is a function that maps any point from an *m*-dimensional space unequivocally onto a point in a 1-dimensional space. Since most FOMs do not take all performance parameters into account, *m* is usually smaller than *n*. This allows for easy identification of the relative performance of individual circuits, and therefore also of the "best" circuit. However, the relative position, and therefore the "best" circuit, depends on the FOM used for this mapping. Many different FOMs have been proposed in literature. Four examples from two publications are shown in table 4.

| Name | Function                 | Reference |

|------|--------------------------|-----------|

| FOM1 | Gain/(NF*Pdc)            | [84]      |

| FOM2 | Gain/Pdc                 | [84]      |

| FOM3 | $(IIP3/(F k T B))^{2/3}$ | [85]      |

| FOM4 | β Vip3²/ε                | [85]      |

**Table 4** Some figures of merit for amplifiers

Considering the variety in figures of merit, it would be natural to ask for the "correct", or "best", or "most fair" FOM. This question cannot be answered, since the relevance of different performance parameters depends on the boundary conditions of the system in which a circuit will be used. In some systems, such as hearing aids or pagers, power dissipation will be a dominant parameter, whereas in other systems, such as wireless data, linearity might be more important.

# 2.2 Trends in low power design

0.030

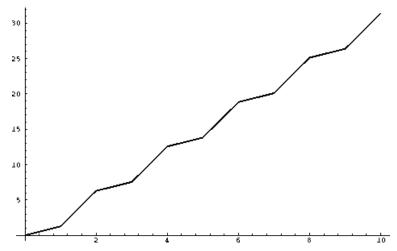

The large number of performance parameters, and the large number of FOMs, make it very difficult to distinguish any trends in RF power dissipation. In figure 11, the absolute power dissipation of recent LNAs has been plotted versus their publication year. This graph does not show any obvious trends.

# State of the Art LNA Performance 0.050 0.040

[89]

Power dissipation [87] [47] 0.020 [88] 0.010 [40] [82] 0.000 1998 1999 2000 2001 2002 1997 Year

Figure 11 Absolute power dissipation of recent LNAs over time

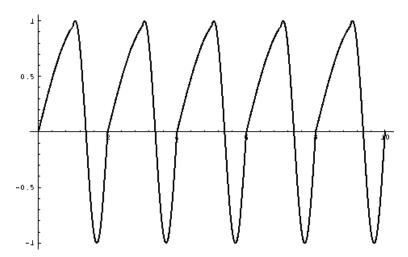

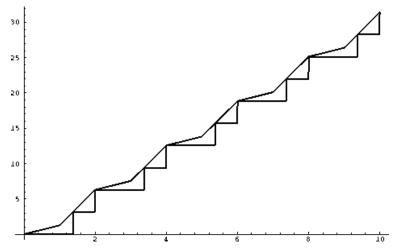

#### State of the Art LNA Performance 100000 [82] • 10000 [33] 1000 100 10-1998 1999 2000 2001 2002 1997 Year

Figure 12 FOM1 versus publication year of recent LNAs

This makes sense, since the large variation in other parameter values of LNAs probably hides any trends that might be present in these numbers. Therefore, plotting a FOM, rather than the absolute power dissipation, might make trends easier to identify. Figure 12 shows the FOM1 of recent LNAs versus publication year.

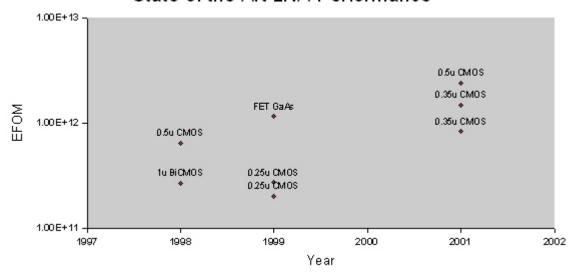

As with the absolute power dissipation, there seems to be no obvious trend in the performance of recent LNAs. By trying many FOMs, a FOM might be found that shows a clear trend. The interpretation of such a trend would be difficult, since the selection of this FOM would be rather arbitrary. Therefore, a specific class of FOMs is required that provides a basis for comparing low power performance of RF circuits in a less arbitrary way. Such a new class of FOMs will be introduced in Chapter 5. At that point the trends in power dissipation of RF circuits will be reconsidered, and a trend will be demonstrated using this new FOM.

## 2.3 Trends in RF design methods

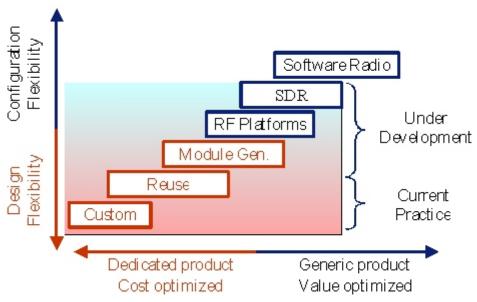

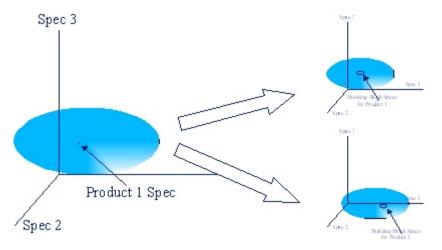

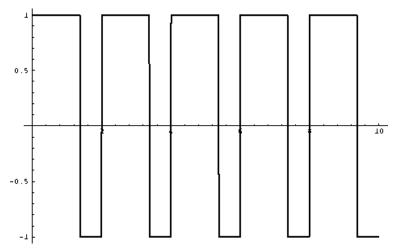

As mentioned in the previous section, the dominant design method for RF circuits is currently still custom design. Nevertheless, a push towards design methods with higher effectivity and efficiency can be detected in both literature and industry. Although the many different design methods that are being proposed initially seem very confusing, a trend can be distinguished from current methods that result in heavily cost-optimized, dedicated products, using all available degrees of freedom during the design stage, towards future methods that will result in more generic products with significant configuration flexibility. This trend can be represented in a graph depicting the trade-offs between design versus configuration flexibility, and cost versus value optimization [93] (fig. 13).

Figure 13 Trends in design methods

The methods that can be distinguished in this figure are:

- *full custom design*, the most popular design method at this moment, in which a product is optimized for low cost, and dedicated for a single application. Towards this end, all available degrees of freedom are used in the design of the product, and there is little, if any, flexibility in the configuration of the finished product.

- reuse, in which parts of a design, typically subcircuits, are not developed from scratch. Instead, they are more or less modified copies of parts of other, existing, designs. Pure reuse assumes no modification of the reused parts at all: the design is used "as is", without the need to even understand how it is constructed internally. This is still relatively rare in RF design. More often, the designs are modified, for example in order to work with other IC processes, or to achieve slightly different specifications. Such forms of reuse are often called "recycling". Recycling is closer to custom design than pure reuse, but for the purpose of this thesis, we consider them to be parts of the same category.

- *module generators*, in which (part of) a design is generated automatically, using an algorithm that takes the required specifications as an input, and that produces a representation of the design at a pre-defined abstraction level, often a schematic or layout. Module generators offer even less flexibility during the design phase, but also very little flexibility (if any) after fabrication.

- *RF platforms*, in which a product is built from pre-existing, configurable components that are assembled in a module or multi-die package. This is the first design method that offers significant configuration flexibility after fabrication; but it also offers very little flexibility during product development.

- *SDR*, or software-defined radio, in which the transceiver performance can be dynamically reconfigured during operation. This offers more configuration flexibility than RF platforms, since in RF platforms the configuration is mostly fixed during the assembly of the pre-fabricated blocks.

- *Software radio*, which offers the ultimate configuration flexibility by carrying out all signal processing in software.

These design methods will probably not be developed simultaneously. Instead, it seems likely that they will be developed over time from the bottom-left corner towards the topright corner.

Reuse and recycling is already being used in many designs, and is currently more formally organized in many companies. A next step will be the standardization of the format in which the reusable elements are stored and transferred. If such standardization is achieved between multiple companies, it will become practical to trade RF IP blocks. This also requires a better standardization of IC processes between companies, since otherwise the transfer of IP, even if it is in a well-standardized format, would be difficult. RF CMOS processes, based on standard digital CMOS processes, seem to be the most likely candidate to be used for this purpose.

Module generators and RF platforms are still in the advanced development stage, and are not widely used yet for product development. Software-defined radio and software radio are mostly still research projects.

Newer design methods will probably not replace older ones immediately. Instead, it seems likely that they will coexist for a long time, similar to the design method developments in e.g. digital design. Which design method will be used for a specific design in this timeframe will depend on the specific requirements with respect to the

parameters on the axes of fig. 13. Therefore, it seems likely that successive generations of one design will follow a reverse timeline compared to the development of the design methods. A first product generation might be designed using a method near the top-right corner, because the high configuration flexibility will enable fast time to market, without the need for a fully cost-optimized product. Later generations of the same product might be developed using design methods towards the lower-right corner, since the markets are likely to be larger and more mature by this time, requiring dedicated, cost-optimized product designs.

# Low power problem

Based on the background provided in the previous chapter, it is now possible to more accurately define the central research question of this thesis:

"What are the fundamental limits for the power dissipation of telecommunication front ends, and what design procedures can be followed that approach these limits and, at the same time, result in practical circuits?"

under the following boundary conditions:

- the "practical circuits" need to be competitive to existing circuits with respect to cost and performance;

- the design procedures should not take significantly more time and/or effort than current design procedures;

- the application area is limited to consumer telecommunication systems, such as cellular, cordless, and wireless data systems in the range of 1GHz to 5GHz;

- it should be possible to extend and/or generalize the design procedures to other RF design areas.

This chapter will focus on fundamental limits in RF low-power design. Two types of fundamental limits can be distinguished:

- 1. Fundamental limits imposed by physics

- 2. Fundamental limits imposed by technology

This distinction is relevant, since our understanding of the laws of physics tends to remain valid for long periods of time, whereas technology limits are improved upon on a regular basis in the semiconductors industry. Therefore, limits of RF circuit and system performance can be expected to improve in parallel with technology limits, and to approach limits imposed by physics in an asymptotic manner.

# 3.1 Elementary operations and signal processing stages

As discussed in the introduction to this thesis, an RF front end typically carries out three elementary operations:

- 1. frequency conversion

- 2. amplification

- 3. filtering

Architectures and systems that don't require some or all of these elementary operations are conceivable, but they generally don't require less power dissipation. For example, architectures that use analog-to-digital converters at RF frequencies may avoid the frequency conversion operation (at least in the analog domain), but the power dissipation of the analog-to-digital converter is almost always much higher than that of a mixer. Notable exceptions are direct-detection AM broadcast receivers and near-field transponders used for e.g. theft detection and road tolling.

To carry out the elementary operations, an RF front end consists of a cascade of signal-processing stages. Each stage carries out at least one of the operations, but there is no one-to-one mapping of signal-processing stage types and elementary operations. In the receiver part of the front end, the following signal processing stage types can usually be distinguished:

- amplifiers, such as low-noise amplifiers (LNA) and voltage-controlled amplifiers (VCA), providing the gain required to increase the antenna signals to levels more convenient for further processing, especially where this further processing adds a significant amount of noise to the signal;

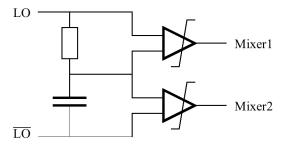

- mixer(s), which, in combination with oscillators and synthesizers, provide the frequency conversion (translation). Mixers are sometimes combined into pairs that mix the input signal with two independent local oscillator (LO) signals, often with the same frequency and 90° relative phase difference. Also, the frequency conversion is often carried out in several steps by cascaded mixing stages, usually with filters in between, such as in double-conversion superhet and sliding-IF architectures. In addition to frequency conversion, mixers often provide some gain as well;

- filter(s), providing frequency selectivity, and, in case of active filters often also gain. The transmitter part of the RF front end also includes filters, mixers and amplifiers. The amplifiers in this case are typically pre-drivers and power amplifiers rather than lownoise amplifiers, but the basic principle is the same.

Please note that, while the three elementary operations are orthogonal, the signal-processing stage types (amplifiers, filters and mixers) are independent but non-orthogonal combinations of the elementary operations, as shown in table 5.

|           | Gain | Frequency Conversion | Selectivity |  |

|-----------|------|----------------------|-------------|--|

| Amplifier | ✓    | ×                    | X           |  |

| Mixer     | ✓    | ✓                    | ×           |  |

| Filter    | ✓    | ×                    | ✓           |  |

**Table 5** Signal-processing stages and elementary operations

This table shows that all signal-processing stage types can have gain, but only the mixer can provide frequency conversion and only the filter can provide (significant) selectivity, since mixer and amplifier implementations on an RF IC are almost inevitably wideband.

In principle, it is possible to build up RF front-end circuits without amplifiers, since gain can also be obtained from mixer and filter circuits. This is not entirely unrealistic: for less demanding applications, receivers in which the mixer provides sufficient gain at sufficiently low noise levels are conceivable, although not necessarily practical (e.g. because of local oscillator leakage). Almost all current RF front-end circuits use a cascade in which all signal-processing stage types occur at least once.

To investigate the fundamental limits of power dissipation for RF front ends, the limits imposed by laws of physics and technology for each of the elementary operations will be discussed in the following sections. Since technology is constantly in development, scaling of IC technology and progress in related areas has to be taken into account (Appendix C). Subsequently, other elementary operations which are required for building a complete RF transceiver front end, but which are not usually considered part of RF IC design, will be discussed, as well as elementary operations needed for specific systems.

# 3.2 Gain

Gain stages have a fundamental lower limit in power dissipation that is imposed by the law of conservation of energy, which, in this case, can be formulated as:

$$\forall P_{in}: P_{supply} \ge P_{out} - P_{in} \tag{3}$$

or, in words: the power provided by the supply should at least make up for the difference between input and output power. Please note that the condition " $\forall P_{in}$ :" needs to be included to make this limit a property of the circuit itself, independent of the actual value of the input power.

Practical circuits often do not come close to this limit. Power amplifiers with low linearity requirements (for example, for constant-envelope signals) can have efficiencies in excess of 50%, but small signal amplifiers such as LNAs, in which the linearity is important, can have efficiencies below 0.000001%<sup>3</sup>. This already shows that there might be a lot of room for improvement of the power dissipation in mobile equipment.

One reason for low efficiencies is that all current active devices dissipate power, which is caused by the voltage drop across the device in combination with the output current. This is relevant for both long-range and short-range systems (Section 1.1).

<sup>&</sup>lt;sup>3</sup> This is based on a DECT LNA which will be discussed in Chapter 1. This LNA consumes 3.7mA at 3V, when generating (with an antenna signal at the -90dBm sensitivity level) an output signal of -70dBm, corresponding to PAE=9.01 10<sup>-9</sup>.

Another reason is that circuits often need to achieve a pre-defined RF performance with a given technology. Since these requirements are different for long-range and short-range systems, they will be investigated separately.

## 3.2.1 Gain in long-range systems

Long-range systems normally have strong requirements for linearity, since they are optimized for highest bandwidth efficiency. Even with ideal devices and interconnect, creating gain with low distortion will result in a reduction of the power added efficiency (PAE), for three reasons:

- 1. All known active devices (vacuum tubes, all kinds of bipolar and field effect transistors, MEMs) have a non-linear transfer function, resulting in distortion of the input signal.

- 2. Some active devices (e.g. bipolar transistors) do not have symmetric transfer functions for negative and positive output currents.

- 3. Parasitic non-linearities, such as the non-linear capacitors in and around active devices, cause additional distortion.

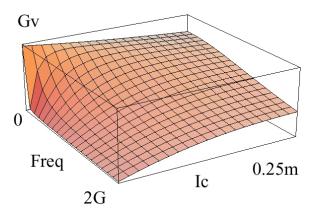

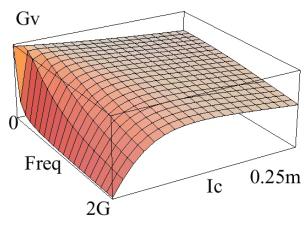

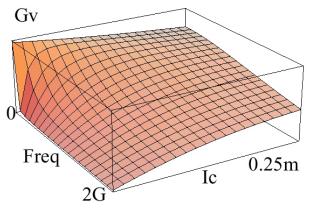

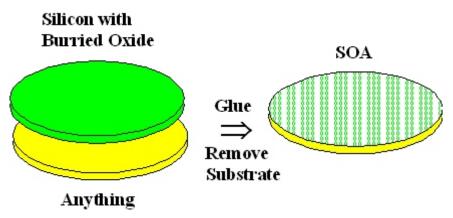

All three reasons are technology related, rather than imposed by laws of nature. However, not all three are equally likely to reduce in impact or even disappear with technological improvements. The parasitic non-linearities mentioned in number 3 usually decrease with new generations of an IC process. Number 1 and number 2 are caused by basic properties of the active device, and are therefore less likely to improve significantly in future IC process generations. All three effects can be reduced at the cost of power consumption: