## Periodic scheduling for cache-miss minimisation

#### Citation for published version (APA):

Clout, R. A. W. (2001). Periodic scheduling for cache-miss minimisation. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR549267

DOI: 10.6100/IR549267

#### Document status and date:

Published: 01/01/2001

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Periodic Scheduling for Cache-Miss Minimisation

## Periodic Scheduling for Cache-Miss Minimisation

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 27 augustus 2001 om 16.00 uur

door

#### Ramon Antoine Wiro Clout

geboren te Oosterhout

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. E.H.L. Aarts en prof.dr. M. Rem

Copromotor: dr.ir. W.F.J. Verhaegh

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Clout, Ramon Antoine Wiro.

Periodic Scheduling for Cache-Miss Minimisation / Ramon Antoine Wiro Clout. -Eindhoven: Eindhoven University of Technology Thesis Eindhoven. - With index, ref. - With summary in Dutch ISBN: 90-74445-49-7 Subject headings: scheduling, combinatorial optimisation, cache memory

> © Koninklijke Philips Electronics N.V. 2001 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

### Preface

This thesis is the result of many years of working in the field of cache optimisation. The research started as a graduation project for my computing science studies at Eindhoven University of Technology. Martin Rem and Frans Sijstermans, who supervised this project, encouraged me to continue the work as a Ph.D. student. The following years, that have not always been easy, have shown me the difficulties, but more importantly the beauty and satisfaction of doing research.

Many people have contributed to the results presented in this thesis. I wish to thank them.

First, I would like to thank my daily supervisor Wim Verhaegh. His warm and unique way of supporting this research has given me the strength to continue the work. Our constructive and pleasant discussions generated many of the ideas on which this thesis is based. It often proved that one hour of discussion generated several months of work.

I am very grateful to Emile Aarts for his continuous support. Besides providing an excellent working environment, he has taught me the importance of unambiguous and clear presentation of the work. I would like to thank Martin Rem for introducing me to this fascinating world, and for stressing that many results, however insignificant they may appear to me, are worth being reported upon.

The research has been carried out at the Philips Research Laboratories (Nat.Lab.) in Eindhoven. I have enjoyed working in this stimulating environment and owe thanks to many colleagues, especially to the members of the 'Algoritmenclub', for their open and constructive discussions. I am grateful to the management of the Nat.Lab. for giving me the opportunity to carry out the research described in this thesis.

Finally, I thank my family and friends for their support. My parents and sister I thank for giving me a safe home to return to. Ronald and Hans, you know what writing a thesis is all about. I would like to thank you for your support and friend-ship over the years. Arjan, Martijn, and Roy, the past years would not have been the same without our weekly 'kookclub' and our regular visits to the theatre and the swimming pool. I value these happenings highly.

Eindhoven, June 2001

Ramon Clout

## Contents

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

|   | 1.1  | Video signal processing                    | 1  |

|   | 1.2  | Processors                                 | 4  |

|   | 1.3  | Informal problem statement                 | 5  |

|   | 1.4  | Related work                               | 6  |

|   | 1.5  | Thesis outline                             | 8  |

| 2 | Con  | ceptual Model                              | 9  |

|   | 2.1  | Video algorithms                           | 9  |

|   | 2.2  | Caches                                     | 13 |

|   | 2.3  | Processor performance                      | 17 |

|   | 2.4  | Cache performance                          | 18 |

| 3 | For  | mal Model                                  | 21 |

|   | 3.1  | Multidimensional periodic operations       | 21 |

|   | 3.2  | Schedules                                  | 25 |

|   | 3.3  | Constraints                                | 27 |

|   | 3.4  | Objectives                                 | 28 |

|   | 3.5  | Formal problem statement                   | 31 |

|   | 3.6  | Special properties                         | 31 |

| 4 | Con  | nplexity Analysis                          | 35 |

|   | 4.1  | Computing the cost of a schedule           | 35 |

|   | 4.2  | Feasibility of a schedule                  | 43 |

|   | 4.3  | Multidimensional periodic cache scheduling | 47 |

|   | 4.4  | Discussion                                 | 54 |

| 5 | Sequ | uentialisability                           | 57 |

|   | 5.1  | Sequential programs                        | 57 |

|   | 5.2  | Sufficient conditions for compactness      | 62 |

|   | 5.3  | Discussion                                 | 72 |

| 6  | Cost   | Calculation                         | 75  |

|----|--------|-------------------------------------|-----|

|    | 6.1    | Decomposition                       | 75  |

|    | 6.2    | Reuse graphs                        | 81  |

|    | 6.3    | Reuse heuristics                    | 87  |

|    | 6.4    | Filling function                    | 110 |

|    | 6.5    | Counting cache misses               | 113 |

|    | 6.6    | Experiments                         | 114 |

|    | 6.7    | Discussion                          | 119 |

| 7  | Tow    | ards Global Cache-Miss Minimisation | 121 |

|    | 7.1    | Decomposition                       | 121 |

|    | 7.2    | Local search strategy               | 123 |

|    | 7.3    | Neighbourhoods                      | 124 |

|    | 7.4    | Incremental cost calculation        | 127 |

|    | 7.5    | Discussion                          | 129 |

| 8  | Con    | clusion                             | 131 |

| Bi | bliogr | aphy                                | 133 |

| Sy | mbol   | Index                               | 137 |

| Au | thor   | Index                               | 140 |

| Su | bject  | Index                               | 143 |

| Sa | menv   | atting                              | 145 |

| Cu | rricu  | lum Vitae                           | 147 |

viii

## Introduction

This thesis concerns the problem of periodic scheduling for cache-miss minimisation. Periodic scheduling refers to the problem of determining an order for a given set of operations that have to be executed repeatedly. Our interest in periodic scheduling originates from the field of digital video signal processing. More precisely, it originates from the problem of compiling a description of a video algorithm into code that can be executed by a general purpose processor, while optimising the use of the processor cache.

This chapter contains background information on the field of video signal processing in Section 1.1, and on processors in Section 1.2. In Section 1.3 we give an informal statement of the scheduling problem we consider. Next, Section 1.4 contains an overview of related work. The chapter ends with an outline of the thesis in Section 1.5.

#### 1.1 Video signal processing

Signal processing concerns the transformation of input streams into output streams. Applications of signal processing can be found in TV, radio, radar, medical diagnosis, and telecommunications. In these areas a shift takes place from analog systems to digital ones. This shift is enabled by advances in integrated circuit technology. Digital signal processing can be used for picture and sound enhancement, and for

#### Introduction

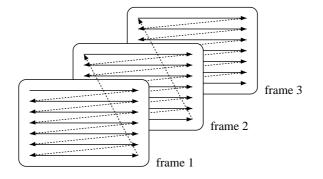

Figure 1.1. The scanning process for non-interlaced PAL.

new features that support applications such as video conferencing.

A digital video signal is obtained by sampling a moving picture that can be regarded to be continuous in time and space. By digitising an image in time, space, and amplitude, the image is represented in such a way that it can be handled by digital video signal processing algorithms. The spatial and temporal digitisation is referred to as *sampling*, the amplitude digitisation is referred to as *quantisation*.

*Frames* are still pictures that are the result of temporal sampling. Each frame consists of a number of *lines*, and each line consists of a number of *pixels*. The exact number of frames per second, lines per frame, and pixels per line depends on the video standard that is used. In the PAL standard, for example, we have 25 frames per second, 625 lines per frame, and 864 pixels per line, which gives a total of 13.5 million pixels per second. Out of these 625 lines only 576 are visible, and out of the 864 pixels only 720 are visible.

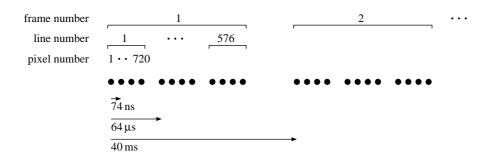

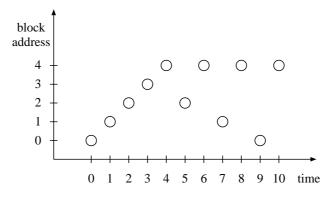

Spatial sampling is performed in order to map the two-dimensional spatial information into one-dimensional temporal information. For a non-interlaced version of the PAL standard the scanning process is shown in Figure 1.1. For each frame pixels are scanned from left to right, and lines are scanned from top to bottom. PAL video has 25 frames per second, which results in one frame every 40 ms. The time between successive lines is  $1/625 \cdot 40$  ms =  $64 \ \mu s$ , and the time between successive pixels  $1/864 \cdot 64 \ \mu s \approx 74$  ns. In Figure 1.2 this scanning process is depicted as a three-dimensional periodic arrival of visible pixels. The time between the last pixel of a line and the first pixel of the next line is called the *line blanking*, and is  $(864 - 720) \cdot 74$  ns  $\approx 9 \ \mu s$  for our example. This time can be used by a scanner to move to the beginning of the next line. Similarly, the *frame blanking* is the time between the last visible pixel of a frame, and the first pixel of the next frame.

After quantisation the pixels can be represented as integers, representing light intensity and colour. A video signal can thus be represented as a stream of integers.

#### 1.1 Video signal processing

Figure 1.2. Three-dimensional periodic arrival of visible pixels.

An algorithm that transforms such an input stream into an output stream is called a digital video signal processing algorithm, or *video algorithm*, for short.

The high sampling frequency, together with the number of operations a video algorithm requests per pixel results in a high computational demand. For example, a video algorithm that performs 100 operations per pixel on a stream of 13.5 million pixels per second results in a demand of over 1 billion operations per second. Until recently, only *application specific integrated circuits* (ASICs), which are tailored to performing dedicated tasks, and *programmable video signal processors*, which are heavily tailored towards video signal processing, were able to implement such video algorithms. Advances in processor technology have enabled the possibility of executing such algorithms on general purpose processors.

Application specific processors are inflexible in the sense that they are designed for one application only. The flexibility of video processors, and even more for general purpose processors enables the possibility of fast prototyping of new algorithms. The price for this flexibility is paid by a worse resource usage, which results in larger circuits and higher power consumption.

As examples of these approaches that have been developed at the Philips Research Laboratories we mention the Phideo design methodology [Van Meerbergen et al., 1995] which supports high-level synthesis of video algorithms into application specific circuits, such as the I.McIC MPEG2 video encoder [Van der Werf et al., 1997], and the VSP programming environment [Vissers et al., 1995] which supports code generation of video algorithms for programmable video signal processors. An example of a general purpose processor tailored towards video signal processing is the TriMedia processor [Slavenburg, Rathnam & Dijkstra, 1996]. This thesis focuses on methods for mapping video algorithms onto general purpose processors. In the next section we give characteristics of such processors, after which this mapping problem is stated informally.

#### **1.2 Processors**

As indicated above, speed of modern microprocessors has increased considerably in the past 20 years. Besides integrated circuit technology, the current performance of processors is largely due to exploitation of instruction level parallelism. This can be done in the following two ways. In the first place, pipelining is applied to let executions of operations overlap in time. Second, multi-issue processors allow simultaneous start of multiple operations per clock cycle. As operations can only be started if all input data are present and if sufficient resources are available, operations must be well ordered for an effective use of the processor. This scheduling process can be handled by a compiler, but can also be performed by the processor.

Unfortunately, the latency of the memory system, which is the time needed to retrieve data from memory, has not kept up with the speed of the processors. Hennessy & Patterson [1996] show that memory performance has increased with approximately 7% annually over the past 20 years. Processor performance on the other hand has increased with 35% per year until 1986 and with 55% per year in the past 14 years. This leads to a performance gap between processors and memory; processors are able to request data from memory faster than the memory is able to service these requests.

A way to reduce the gap between memory and processor performance is to insert a cache between the processor and the memory. Caches are fast but small pieces of memory located close to the processor that act as a buffer for data that are used frequently. In this way, the data requested by the processor can be delivered much faster. However, as the cache is small it cannot contain all the data that are needed during the execution of a program. If the processor requests data that are not available in the cache, we say that a *cache miss* occurs and the requested data must be fetched from memory, which takes a long time. Upon a cache miss, a cache must furthermore decide which data must be removed from the cache to facilitate storage of the new data. This process is called *cache replacement*. Cache replacement policy, as well as cache size are parameters that must be determined during the design of a processor.

General purpose processors are flexible in the sense that they can execute a great variety of programs efficiently. To this end, a cache should be targeted towards the set of programs that are likely to be executed on that processor. Much research has been done on the problem of designing a cache. Basically, there are two ways of approaching the design problem [Przybylski, 1990]. In order to make the common case fast, a set of representative applications is chosen for which the memory system is analysed using trace-driven simulations. A trace is a sequence of memory references that contains sufficient information for the computation of the cache hit rate, i.e., the fraction of the memory references that result in a hit in the cache. Another way of attacking the cache design problem is by analytical modelling of a cache. Analytical models give insight in the phenomena that determine the performance of a cache.

Processors use cache memory for both instruction and data references. Processors can have separate caches for instruction references and data references. Such caches are called *data caches* and *instruction caches*, respectively. *Unified caches* can contain both instructions and data. In this thesis we focus on data references and data caches only.

Complementary to the cache design problem is the problem of optimally using a cache for a given application, which is the problem we study in this thesis. Given a processor with a cache and a description of an algorithm in a programming language, it is the task of a compiler to translate the algorithm into object code for the processor in such a way that the scarce resources on the processor, in our case the cache, are used optimally.

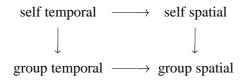

We divide the field of cache optimisation into two categories: local optimisations and global optimisations. Local optimisations deal with small parts of a program, typically one or two loop nests, whereas global optimisation considers a whole program. Local optimisations have the disadvantage that locally optimal solutions for each part of the program lead to sub-optimal solutions for the whole program. Next to these categories, we make a distinction in the level of detail in which we study the scheduling problem. A high level of detail is achieved by optimisation that considers every individual access to memory. Optimisation with a low level of detail considers arrays or sections of arrays rather than individual array elements. Again, optimising with a low level of detail may lead only to sub-optimal solutions. Therefore, this thesis focuses on global optimisation with a high level of detail.

#### **1.3 Informal problem statement**

For the scheduling problem subject to this thesis we assume that a cache and a video algorithm are given. Parameters that define a cache are, amongst others, cache size and replacement policy. As many video algorithms can be described by a set of operations that must be executed repeatedly, a video algorithm is represented as a series of nested loops. In this way, an execution of an operation of a video algorithm is uniquely identified by the corresponding values of its loop iterators. As a consequence, these operations also produce and consume data in a repetitive way, which is described using multidimensional arrays.

The order of execution of operations can now be defined by periods for every loop iterator, which denote the time between two consecutive iterations of the corresponding loop. Each operation is given a start time, indicating the moment in time at which the first execution takes place. In this thesis periods and start times are used only to give a partial order on the executions of the operations. During scheduling we must assign values to the periods and the start times of all operations. In addition to this *time assignment* we must also assign a memory position to every element of the multidimensional arrays, which is reflected in a so-called *address assignment*.

We consider two kinds of constraints. First, we have *precedence constraints*, which are due to data dependencies. Data dependencies express the relationship between production and consumption of data, and precedence constraints specify that consumption of data may only take place after the corresponding production. Second, we have *address constraints* that express that data may not be overwritten as long as they are not consumed. Hence, a memory location can only be reused after the previous data item has been consumed for the last time.

The objective for scheduling is minimisation of the number of processor cycles that are required for the execution of the schedule, i.e., a time assignment and an address assignment. As a cache miss results in a large number of processor cycles, we determine total execution time of a schedule by counting the total number of cache misses.

Informally, we state the scheduling problem as follows. Given a video algorithm and cache parameters, find a schedule, consisting of a time assignment and an address assignment, that satisfies the precedence constraints and address constraints, and that minimises the number of cache misses.

#### 1.4 Related work

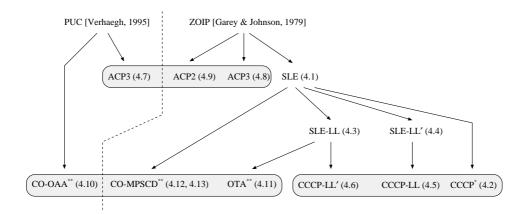

The discrete nature of the scheduling problem we consider allows for a formulation in terms of a combinatorial optimisation problem. For the theory of combinatorial optimisation we refer to Papadimitriou & Steiglitz [1982] and Schrijver [1986]. The computational complexity of many of these problems is studied by Garey & Johnson [1979] and Papadimitriou [1995].

In the area of off-line non-preemptive periodic scheduling, work has been done by Korst [1992] and De Kock [1999], who consider the mapping of video signal processing algorithms onto programmable video signal processors, and by Verhaegh [1995], who considers the problem of scheduling multidimensional periodic operations in high-level synthesis. Contrary to these approaches, where operations are scheduled on several processors, we restrict the scheduling problem to a single processor. For a general introduction to scheduling we refer to Pinedo [1995].

An early and thorough survey on the influence of various cache parameters is given by Smith [1982]. The specific topic of using trace-driven analysis is handled by Hill & Smith [1984]. Przybylski, Horowitz & Hennessy [1988], Przybylski

#### 1.4 Related work

[1990], and Smith & Goodman [1983] analyse caches using analytical models of typical workloads. These approaches, however, do not consider periodic operations.

Bacon, Graham & Sharp [1994] and Wolfe [1996] give overviews of compile time optimisations. They both give an overview of loop transformation techniques for cache optimisation. A general introduction on compilers is given by Aho, Sethi & Ullman [1986].

A well known compiler optimisation algorithm for caches, *blocking* or *tiling*, breaks computations for large arrays into several computations on sub-arrays. Techniques for finding tile sizes have been reported by Lam, Rothberg & Wolf [1991], Wolf & Lam [1991], Kennedy & McKinley [1992], and Coleman & McKinley [1995].

Other algorithms that rearrange loops are often included in source-to-source compilers. Kennedy & McKinley [1993] and Singhai & McKinley [1997] use *loop fusion* and *loop distribution* to enhance cache performance. McKinley, Carr & Tseng [1996] propose a compound optimisation algorithm that incorporates several loop reordering techniques. These optimisation approaches are all local optimisation techniques. Our global optimisation algorithm generalises these reordering techniques in terms of periods and start times in Chapter 7.

Another class of algorithms aims at optimising cache performance by taking the placement of data in memory into account. Recent work has been done by Panda & Dutt [1999], Strout, Carter, Ferrante & Simon [1998], Rivera & Tseng [1998], and Calder, Krintz, John & Austin [1998]. Topham & González [1999] propose randomness in the indexing function of the cache in order to eliminate cache conflicts. Combinations of loop transformations and data placement are given by Kandemir, Ramanujam & Choudhary [1999] and Manjikian & Abdelrahman [1997].

Gannon, Jalby & Gallivan [1988] present program transformation techniques for caches and local memories. Philbin, Edler, Anshus, Douglas & Li [1996] use fine-grained thread scheduling for cache optimisation. Schutte & Van Kempen [1997] propose cache optimisation algorithms for a class of image processing algorithms. The problem of optimising video algorithms for combined instruction cache performance and data cache performance is studied by Clout [1994].

Besides reordering memory accesses, the latency of fetching data from memory can be shortened by prefetching data. A hardware-controlled prefetching method is already mentioned by Smith [1982], who suggests considering the next line for prefetching upon a cache reference. Jouppi [1990] and Palacharla [1994] propose the addition of stream buffers to the cache that prefetch streams of subsequent cache blocks. Chen & Baer [1992] include *reference prediction tables* that store predictions for regular data accesses, and which generate prefetching requests.

Zucker, Flynn & Lee [1995] combine the use of a prediction table and stream buffers for multimedia applications, such as an MPEG2 decoder. Software controlled prefetching as proposed by Callahan, Kennedy & Porterfield [1991] and Mowry, Lam & Gupta [1992] assumes that the instruction set of a processor includes a *prefetch instruction*, which can be inserted by either a programmer or a compiler. A combination of software and hardware control for prefetching is given by Chen [1997] and Struik, Van der Wolf & Pimentel [1998]. The former approach synchronises the prefetching on the instruction addresses, the latter on the data addresses. In Chapter 6 of this thesis we come back to prefetching issues.

#### 1.5 Thesis outline

In this thesis we study the mapping of video algorithms onto processors with caches, where the objective is to minimise the execution time of a video algorithm on such a processor by minimising the number of cache misses. We aim at finding an appropriate model for video algorithms that allows for a global optimisation approach. Contrary to local optimisations, that only look at a limited number of loop nestings, our global approach treats all loops at once. Furthermore, we aim at analysing the complexity of our scheduling problem and at finding a solution approach to this problem. The thesis is organised as follows. In Chapter 2 we informally present the most important concepts that we use in this thesis. In Chapter 3 we give a formal model for video algorithms, a formal execution model for these algorithms (schedule), a model for caches, and a formal problem definition of the multidimensional periodic cache scheduling problem. Chapter 4 handles the formal complexity of this scheduling problem and some related sub-problems. As not all schedules allow for an efficient implementation on a single processor, we introduce in Chapter 5 some constraints on schedules that make an efficient implementation possible. In Chapter 6 we propose a method for efficiently estimating the number of cache misses for a given schedule and a given cache. This method is used in Chapter 7, where we give ingredients for a local search approach that is aimed at finding good schedules. We summarise the main results of this thesis in Chapter 8. Notes on notation used in this thesis can be found in the symbol index.

# 2

## Conceptual Model

In this chapter we present the concepts *video algorithms, caches,* and *cache per-formance*. These concepts are described in an informal way. A formal presentation is given in Chapter 3. Section 2.1 gives characteristics of video algorithms. In Section 2.2 we present the relevant cache terminology. In Section 2.3 we break down a measure for processor performance into several parts, which are discussed one by one. Section 2.4 discusses several ways of measuring the performance of a cache.

#### 2.1 Video algorithms

We aim at exploiting the repetitive nature of video algorithms. This nature exists both in the operations that must be performed for every pixel and in the storage of the pixels in memory. For every pixel on every video line of every video frame a similar action usually has to be performed. The memory is also accessed in a repetitive way, meaning that pixel information for the second pixel on the third video line of the first frame can usually be accessed in a similar way as the second pixel on the third video line of the seventh frame.

Hence, for video algorithms we use a formalism that can handle this repetition well. In this chapter we only give a flavour of this model by means of an example; in Chapter 3 it is formalised.

for

$$i := 0 \dots 2 \rightarrow$$

for  $j := 0 \dots 1 \rightarrow$

$Z[j][i+1] := \operatorname{sum}(Y[i][j], Z[j][i])$

for  $k := 0 \dots 1 \rightarrow$

$Z[k][0] := \operatorname{cpy}(Y[0][k])$

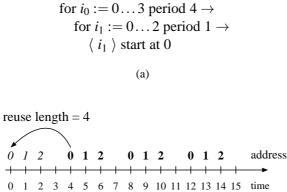

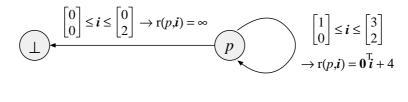

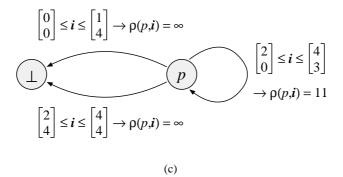

for  $i := 0 \dots 3 \rightarrow$

for  $j := 0 \dots 1 \rightarrow$

$Y[i][j] := \operatorname{avg}(X[3i+j], X[3i+j+1])$

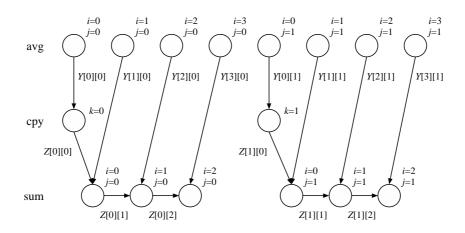

Figure 2.1. Example of a part of a video algorithm with nested loops and multidimensional arrays.

As video signals are periodic, their execution must also be periodic. Therefore we specify them as nested loops. In Figure 2.1, we give a set of operations that perform some calculations on an input array X. Here, we have three operations: operation 'sum' with two input arguments Y[i][j], Z[j][i] and one output argument Z[j][i+1], operation 'cpy', and operation 'avg'. The arguments of the operations are elements of multidimensional arrays, where the *index expressions*, for example 3i + j + 1, are affine expressions in the *loop iterators i* and *j*.

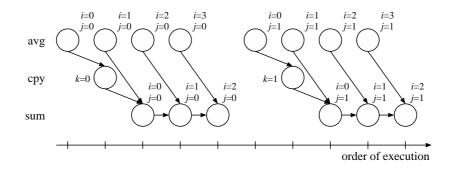

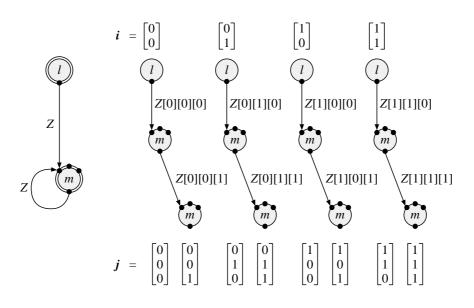

This program looks much like a program in an *imperative* programming language like Pascal or C, but there are marked differences. In Figure 2.1 there is no direct relationship between the syntactic order of loops and a *possible* order of execution of the operations. In general there are many valid orders, that are restricted only by data dependencies. These dependencies are implicit in the program and exist between each production and consumption of the same array element. In Figure 2.2 we have depicted all data dependencies for the example. Every data dependency induces a *precedence constraint* on the possible order of execution of operations, that is, every array element must be written before it can be read. A possible order of execution of the operations that meets all precedence constraints is given in Figure 2.3. This order is not complete as executions that appear above each other may be executed in arbitrary order. A compact representation of such partial orders is given in Chapter 3.

Another difference with imperative programming languages is the memory allocation. A memory allocation assigns a memory address to each element of each array. This allocation, which is implicit for many programming languages, has not been specified in the program above. For arrays in the programming language C, the mapping of array elements to memory locations is described by an address

Figure 2.2. Data dependencies for the example of Figure 2.1. Every circle represents an execution of an operation and is annotated with the values for the iterators. The data dependencies are denoted by arrows and annotated with the corresponding array elements.

Figure 2.3. A possible order of executions of operations where all precedence constraints are met. Executions that appear to the right of another execution must be performed later.

| Z[0][0] | ] Z[0][1] | Z[0][2] | Z[0][3] | Z[1][0] | <i>Z</i> [1][1] | <i>Z</i> [1][2] | Z[1][3 | ] array element |

|---------|-----------|---------|---------|---------|-----------------|-----------------|--------|-----------------|

| <br>    |           | +       | +       |         |                 |                 |        |                 |

| 100     | 110       | 120     | 130     | 140     | 150             | 160             | 170    | memory address  |

Figure 2.4. A possible memory assignment for a  $2 \times 4$  array *Z* with C-like storage. Array element Z[i][j] is placed at memory location 100 + 10(4i + j).

function a, which is given by

$$a(X[n_{N-1}]...[n_1][n_0]) = o(X) + s(X) \sum_{k=0}^{N-1} n_k \prod_{l=0}^{k-1} S_l,$$

for an  $S_{N-1} \times ... \times S_1 \times S_0$  array *X*, and s(X) being the size of one array element. The offset o(X) determines the location of array element X[0] ... [0][0] in memory. This position is usually chosen at compile time for global variables, or at run time for local variables or dynamically created variables. For example, a 2 × 4 array *Z* with array offset o(Z) = 100 and element size s(Z) = 10, is arranged in memory as depicted in Figure 2.4.

The above assignment method is called *row-major* storage, as the larger coefficients appear for the indices  $n_k$  with larger k. The opposite method, *column-major* storage, is used in the programming language Fortran.

In this thesis, we use a generalisation of such memory assignments, given by

$$a(X[n_{N-1}]...[n_1][n_0]) = o(X) + \sum_{k=0}^{N-1} n_k c_k(X),$$

where the *address offset* o(X) and *address coefficients*  $q_k(X)$  remain to be chosen. Here we must take care that array elements that are alive at the same time are not mapped onto the same memory address. The *lifetime* of an array element is defined as the interval between its production and its last consumption. Hence, we are looking for a memory assignment for all arrays in such a way that array elements with overlapping lifetimes are mapped onto different memory addresses. The order of the executions of operation 'sum' that we chose in Figure 2.3 allows that array elements Z[k][0], Z[k][1], and Z[k][2] are all mapped to the same memory address. Hence we can use a memory assignment  $a(Z[i][j]) = o(Z) + s(Z) \cdot (i + 0j) = o(Z) + s(Z)i$ . This memory assignment is possible as the lifetimes of these array elements do not overlap for the given order.

In this thesis we aim at methods for finding an execution order for all operations and a memory assignment for each array in such a way that the processor cache is used optimally. To this end, we first give an introduction to processor caches, and accompanying performance criteria.

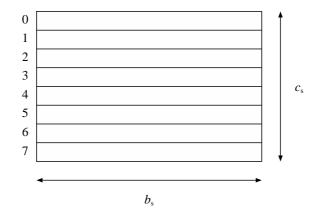

Figure 2.5. A cache is a memory consisting of blocks with block size  $b_s$ . The size of a cache, denoted by  $c_s$ , is expressed in the number of blocks.

#### 2.2 Caches

In this section we give an overview of caches. This overview is not intended to be complete; we limit ourselves to the relevant terminology. We closely follow the description of caches given by Hennessy & Patterson [1996].

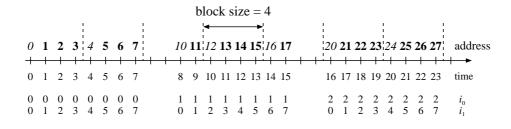

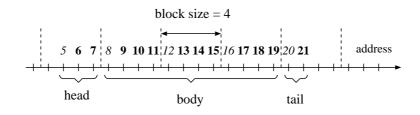

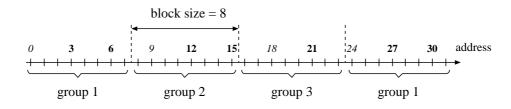

A cache is a fast but small piece of memory between processor and main memory that acts as a buffer for data that are used frequently. We say that a *cache miss* occurs if the processor requests a data item that is not available in the cache. The opposite, a request for a data item that is present in the cache, is called a *cache hit*. A *block* is the granularity for storing data in a cache, i.e., the amount of data that the cache requests from memory upon a cache miss. A cache hit or cache miss will consequently occur for an entire cache block. Figure 2.5 shows a cache with  $c_s$  cache blocks, every block having a size  $b_s$ . The unit of block size is the size of the smallest element that can be addressed in memory, usually a byte.

A cache is designed in such a way that it takes advantage of *locality of reference*. References to the same memory address tend not to be uniformly distributed over time, but instead, two references to the same memory address are likely to be executed close to each other in time. This kind of locality is called *temporal locality*. Also, if data items are close together in memory, they tend to be referenced close to each other in time. This is called *spatial locality*.

In order to exploit spatial locality, blocks usually consist of successive data items in memory. Hence, if a data item is requested from memory, a block of data is fetched, consisting of data items that are spatially close. When a processor requests data at memory address  $a \in \mathbb{Z}$ , the position within the corresponding block is called

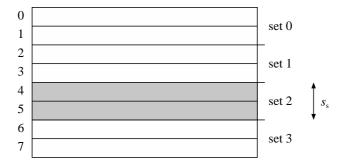

Figure 2.6. The positions within a cache where a block can be placed is restricted in set-associative caches. The size of each set, denoted by  $s_s$ , is also called the *associativity* of the cache. The number of sets, in this case four, is denoted by  $n_s$ .

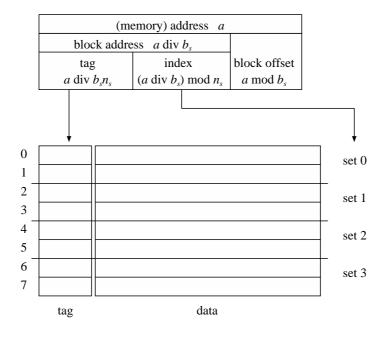

the *block offset*, and given by  $a \mod b_s$ , where  $b_s$  is the size of a single block. The *block address* equals  $a_b(a) = a \operatorname{div} b_s$ .

Now, there are four basic issues to be addressed in a cache design:

- Placement of a block in the cache.

- Finding a block in the cache.

- Replacement of a block upon a cache miss.

- Policies for writes to the cache.

**Placement of a block in the cache.** Often, there are restrictions on the position within a cache where a block can be placed. In Figure 2.6 the cache has been divided into four sets of equal size. Each memory block can only be placed in a predetermined set. It is common practice that a set is selected using low order bits of the block address; the set where address *a* is placed is given by its *index*  $s(a) = a_b(a) \mod n_s$ , where  $n_s$  is the number of sets in the cache. The number of blocks in each set is also called the associativity of the cache and is given by  $\S = \frac{c_s}{n_s}$ . A cache with set size  $s_s = 1$  is called a *direct mapped* cache, as the mapping of each memory block to a position within the cache is unique. A cache with only one set, with set size  $s_s = c_s$ , is called a *fully set-associative* cache. Here, every memory block can appear at every position in the cache. In general, caches with associativity *n* are called *n-way set-associative*. Caches with a higher degree of associativity usually result in fewer cache misses, but are more difficult to build in hardware [Hill, 1988].

**Finding a block in the cache.** In order to find out whether data requested by a processor is present in the cache, each cache block is tagged with its block address. As is depicted in Figure 2.7 we do not need to store the whole block address, as

2.2 Caches

Figure 2.7. Organisation of a 2-way set-associative cache.

a block can only appear in one set, and hence the index, i.e., the part of the block address that determines the set, does not have to be stored in the tag.

**Replacement of a block upon a cache miss.** Upon a cache miss, the cache must decide which block is removed from the cache. As a block can only appear in one set, a choice must be made between the blocks within this set. Several replacement algorithms have been presented in literature, which can be divided into two categories [Smith, 1982], being usage-based and non-usage-based algorithms. Usage-based replacement algorithms keep track of the use of blocks and select a victim for replacement based on this information. Non-usage-based algorithms choose a victim for replacement irrespective of the previously accessed blocks.

We give four examples of replacement algorithms, two usage-based (MIN and LRU), and two non-usage-based (Random and FIFO).

- *MIN.* The *MIN*-algorithm by Belady [1966] replaces the block that is used again the farthest into the future.

- *Least Recently Used (LRU).* The principle of locality tells that items that were accessed recently tend to be accessed again soon. Based on this principle, the most unlikely block to be accessed soon is the one that was accessed least recently.

- First In First Out (FIFO). Blocks are replaced cyclically. The cache block that

was least recently replaced, is the victim.

*Random.* Within the set a victim for replacement is chosen randomly.

The MIN-algorithm has been proved optimal with respect to the number of cache misses, but requires knowledge about the future and is therefore hard to implement. The hardware cost for LRU replacement increases with associativity and is often only approximated. Both FIFO and Random are easy to implement in hardware. As usage-based replacement usually performs better than non-usage-based replacement, and as LRU is widely used in modern processors, we focus on caches with LRU replacement.

**Policies for writes to the cache.** Upon a write it must be decided where the data item is modified. With *write through* data are changed in memory. Only if data already reside in cache, the contents of the cache are changed. As a consequence the data that are stored in the cache and the corresponding data in memory are always identical. This also means that upon a read miss, the block can simply be thrown out of the cache. *Write back*, on the other hand changes data in the cache only. Write back has the advantage that it generates fewer accesses to memory. In case of write back caches, blocks that have been changed in the cache, must be written back to memory, when they are replaced. An optimisation that is often used is the addition of a *dirty* bit to each cache block which registers whether data in the cache have been updated. Only if the dirty bit for a block has been set, the data must be written back to memory upon replacement of that block.

Furthermore, upon a write it must be decided whether to fetch data in case of a cache miss. The strategy where a block is fetched upon a write miss, is called *write allocate*. This strategy is common for write back caches, as subsequent writes to the same block are handled by the cache. The *no-write allocate* strategy changes the block only in memory. As all writes change memory in a write through cache, this is a common strategy for these caches.

Write through caches have the additional advantage that the content of the blocks that are present in the cache are equal to the contents of the corresponding blocks in memory. For multiprocessors that share memory it is important that all caches have the same copy of a memory block. This so-called *cache consistency* is implemented easier with write through caches.

In general write back caches handle writes faster than write through caches. Furthermore, if more writes to the same block result in hits, they will require only one write back.

As is explained in the next sections, we are mainly interested in finding an execution order and memory assignment that minimises the number of cache misses for a given program and a given cache. The cache parameters that are needed for measuring the number of cache misses are the cache size  $c_s$ , the associativity  $s_s$ , the block size  $b_s$ , and the replacement algorithm. In this thesis we focus on LRU caches with write back and write allocate policy.

#### 2.3 **Processor performance**

System performance optimisation involves optimal use of scarce resources, for example processors and memory. In our case we want to optimise the performance of a processor, where we use the term processor for a CPU and cache together. Hence it is worth taking a look at a measure of processor performance, being the time needed for the execution of a program, which is defined by Hennessy & Patterson [1996] as follows.

processor time =

$$\frac{\text{seconds}}{\text{program}} = \underbrace{\frac{\text{instructions}}{\text{program}}}_{1} \times \underbrace{\frac{\text{clock cycles}}{\text{instruction}}}_{2} \times \underbrace{\frac{\text{seconds}}{\text{clock cycle}}}_{3}$$

The number of instructions per program (1), also called the instruction path length or instruction count, is a measure for the amount of work that the processor has to perform. In the first place, the programmer is responsible for minimising this parameter. Optimising compilers can improve this, for example by removing redundant computations. This parameter is further influenced by the choice of instruction set. A processor with a small instruction set, for example RISC (Reduced Instruction Set Computer), will generally need more instructions than a processor that can execute complex instructions, such as CISC (Complex Instruction Set Computer). The last parameter, the number of seconds per clock cycle, is largely determined by the hardware technology.

Both parameter (1) and (3) fall outside the scope of this thesis. We zoom in on the average number of clock cycles per instruction (2), usually denoted by its abbreviation CPI, which can be split up [Przybylski, 1990] as follows.

$$\frac{\text{clock cycles}}{\text{instruction}} = \underbrace{\frac{\text{CPU cycles}}{\text{instruction}}}_{2a} + \underbrace{\frac{\text{references}}{\text{instruction}}}_{2b} \times \underbrace{\frac{\text{clock cycles}}{\text{reference}}}_{2c}$$

The average number of clock cycles per instruction consists of the average number of clock cycles that the CPU needs to execute an instruction and the average number of clock cycles that the cache needs for all memory references for the instruction. An important influence on the mean number of CPU clock cycles per instruction (CPI) is the architecture of the CPU. Modern CPUs allow the execution of multiple instructions in parallel. This level of instruction level parallelism (ILP) influences the CPI. As not all instructions require the same amount of clock cycles, the complexity of the instructions is another factor that affects the CPI.

|                    | (1) | (2a) | (2b) | ( <b>2c</b> ) | (3) |

|--------------------|-----|------|------|---------------|-----|

| instruction set    | *   | *    | *    |               |     |

| compiler           | *   | *    | *    | *             |     |

| CPU-architecture   |     | *    |      |               | *   |

| cache organisation |     |      |      | *             | *   |

Table 2.1. Influences on the various performance parameters discussed in Section 2.3, indicated with stars.

Parameters (2b) and (2c) constitute the time spent by the cache. The first factor, the average number of references per instruction, depends on the used compiler. For example, by storing data with short lifetimes in registers, the number of memory references can be decreased. The second factor, the average number of clock cycles per reference, depends on the organisation of the cache, and on the sequence of references that is fed to the cache. This sequence basically is an ordered list of memory addresses that are referenced. As explained in Section 2.1, both the order of the list and the addresses can be influenced by the compiler.

Table 2.1 lists all relevant parameters. This scheme lists influences on the various performance parameters. This table has been derived from Przybylski [1990], where we added the influence of a compiler on performance parameter (2c). Only the most important influences have been discussed in the text. In the next section we look more closely at performance parameter (2c), the average number of clock cycles per reference, or stated differently, the time spent by the processor cache for memory references. The focus in this thesis is on the influence of a compiler on this parameter.

#### 2.4 Cache performance

For a cache, the mean number of clock cycles per reference depends on the *miss rate*, i.e., the fraction of the memory references that cause a miss in the cache, as follows.

```

average time per reference = hit time + miss rate \times miss penalty,

```

where the *hit time* is the time required to fetch data from the cache, and the *miss penalty* is the additional time the cache needs to fetch this data from memory. In this thesis we assume that hit time and miss penalty are constants. In general neither of the two is constant. For example, processors that can issue multiple requests to the cache at the same time may suffer from conflicts in the cache, resulting in a variable hit time and variable miss penalty. Assuming that the cache hit time and the cache miss penalty are constants, minimisation of the average time per refer-

#### 2.4 Cache performance

ence for a video algorithm is equivalent to minimisation of the cache miss rate.

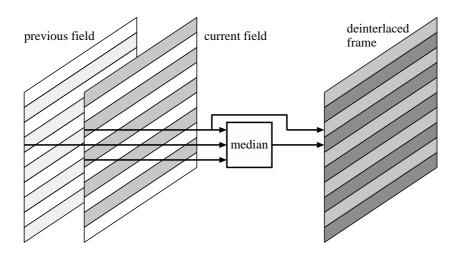

A method that is often used to measure the miss rate of a cache for an execution of a program is to perform a cache simulation. For a cache simulation one typically runs the program and registers which subsequent memory accesses take place. This information is sufficient to compute the number of cache misses. A disadvantage of cache simulation is the excessive execution times of such simulations. If we want to analyse a program with twice as many memory accesses, the cache simulation will take twice as long. As video signal processing algorithms usually generate many memory accesses, this will result in long simulation times.

For a PAL signal, for example, we have 720 visible pixels on 576 lines per video frame and 25 video frames per second. If we assume that we need one memory reference for each visible pixel, 10,368,000 memory accesses per second take place. A cache simulation for such an amount of accesses takes several minutes. For example, simulation of 10,000,000 memory accesses takes approximately 200 seconds on a Pentium processor running at 200 MHz.

An additional disadvantage of cache simulation is the difficulty to identify bottlenecks. As a simulation only reports the number of cache misses, it is hard to find the references in the original program that are responsible for the misses.

Another way of obtaining the number of cache misses is to analyse a program at source code level. Ghosh, Martonosi & Malik [1998] propose a method that generates so-called *cache miss equations* (CMEs) for every reference in a loop nest. Every solution for these equations represents a possible cache miss. Counting the number of solutions for a system of CMEs can then be performed using methods described by Clauss [1996]. From this the references with most misses can be identified. Unfortunately, at the moment CMEs do not allow for program analysis across loop nests.

Algorithms that optimise for cache performance at compile time often use approximations of the number of cache misses rather than the exact number. McKinley, Carr & Tseng [1996] use the number of distinct cache lines that a single loop nest accesses as an indication for the number of cache misses. Wolf & Lam [1991] use the number of memory accesses per iteration of a loop nest as a metric. Both estimations can be computed efficiently but work only for a single loop nest.

In Chapter 6 we give a method for the evaluation of the number of cache misses for a set of loop nests. We aim at a fast evaluation, that gives a good estimation of the number of caches misses. A precise count of the number of cache misses cannot be expected to be possible in reasonable time as is shown in Chapter 4. Nevertheless, the repetitiveness of video algorithms enables a compact description of the access sequence, which is used in Chapter 6 to estimate the number of cache misses effectively and efficiently.

# 3

### Formal Model

In this chapter we model video algorithms by means of multidimensional periodic operations in a *program graph*. A *schedule* that satisfies accompanying *constraints* determines a possible *execution* of a program graph. We give a formal *cache model* which we use to define the objective function of our scheduling problem, i.e., the number of cache misses. Throughout this chapter we use a model of multidimensional periodic operations based on the model presented by Verhaegh [1995].

The model in this chapter consists of three parts. In Section 3.1 we give a model of video algorithms that we want to optimise. Schedules are defined in Section 3.2, and feasibility of schedules is the topic of Section 3.3. The formal cache model is defined in Section 3.4. The problem is formulated in Section 3.5. Section 3.6 contains some special properties of program graphs and schedules.

#### 3.1 Multidimensional periodic operations

Usually, video algorithms are described using nested loops and multidimensional arrays. For an example see Figure 3.1, in which a matrix multiplication algorithm for  $50 \times 50$  matrices is given by two loop nests, of which the former initialises an array *Z* and the latter does the actual multiplication of arrays *X* and *Y* and stores the result in array *Z*. In a so-called *program graph* the statements in the inner loop are represented by *operations*. For the example of Figure 3.1 the program graph

operation *l*:

for

$$i_0 := 0 \dots 49 \rightarrow$$

for  $i_1 := 0 \dots 49 \rightarrow$

$Z[i_0][i_1][0] := 0$

operation *m*:

for  $i_0 := 0 \dots 49 \rightarrow$

for  $i_1 := 0 \dots 49 \rightarrow$

for  $i_2 := 0 \dots 49 \rightarrow$

$Z[i_0][i_1][i_2 + 1] := Z[i_0][i_1][i_2] + X[i_0][i_2] * Y[i_2][i_1]$

Figure 3.1. A program for matrix multiplication consisting of two loop nests.

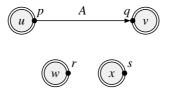

$$\begin{bmatrix} l \\ l \\ p \\ z \\ r \\ s \\ z \\ m \\ t \end{bmatrix} = \begin{bmatrix} 49 \\ 49 \\ 49 \end{bmatrix} \quad A(p) = \begin{bmatrix} 1 & 0 \\ 0 & 1 \\ 0 & 0 \end{bmatrix} \quad b(p) = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

$$A(r) = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 0 & 1 \end{bmatrix} \quad A(s) = \begin{bmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \end{bmatrix} \quad b(r) = b(s) = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix}$$

$$Z \\ m \\ t \\ T \\ m \\ t \end{bmatrix} \quad I(m) = \begin{bmatrix} 49 \\ 49 \\ 49 \\ 49 \end{bmatrix} \quad A(q), A(t) = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \quad b(q) = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} \quad b(t) = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix}$$

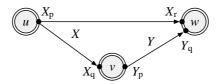

Figure 3.2. Program graph of the matrix multiplication example of Figure 3.1. The graph consists of two operations, denoted by a double circle, and annotated with their iterator bound vectors. The black dots represent ports of the operations, which are annotated with their index matrices and their index offset vectors. The meaning of the symbols is explained in the text.

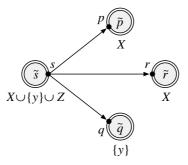

is depicted in Figure 3.2. Here, operation l corresponds to the assignment in the first loop nest, and operation m to the assignment in the second loop nest. In the program the array expressions are the arguments of the operations. The second loop nest in the example has three read arguments,  $Z[i_0][i_1][i_2]$ ,  $X[i_0][i_2]$ , and  $Y[i_2][i_1]$ , and one write argument,  $Z[i_0][i_1][i_2+1]$ . In the program graph these arguments are modelled by ports and denoted by black dots in the figure. In general an operation can have multiple read ports and multiple write ports. Operations without read ports or without write ports are the input and output ports of the program graph. A program graph is formally defined as follows.

**Definition 3.1 (program graph).** A program graph G is given by a 7-tuple

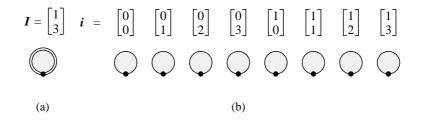

Figure 3.3. (a) An operation with two dimensions of repetition ( $\delta = 2$ ) and one port. (b) The individual executions of the operation are denoted by means of single circles.

#### (V, R, W, I, E, A, b), where

- V is a finite set of multidimensional operations,

- R(v) denotes a set of *operation read ports*, for each operation  $v \in V$ ,

- W(v) denotes a set of *operation write ports*, for each  $v \in V$ ,

- $I(v) \in \mathbb{N}^{\delta(v)}$  denotes an *iterator bound vector*, for each  $v \in V, A$

- $E \subseteq W \times R$  is a set of edges representing data dependencies, where  $W = \bigcup_{v \in V} W(v)$  and  $R = \bigcup_{v \in V} R(v)$ ,

- $A(p) \in \mathbb{Z}^{\alpha(p) \times \delta(v)}$  denotes an *index matrix*, for each  $v \in V$  and  $p \in P(v) = R(v) \cup W(v)$ ,

- $\boldsymbol{b}(p) \in \mathbb{Z}^{\alpha(p)}$  denotes an *index offset vector*, for each  $p \in P = R \cup W$ .

Here,  $\delta(v)$  denotes the number of loops by which operation v is enclosed, where the upper bounds of the loops are given by a vector I(v) with length  $\delta(v)$ . This means that in each loop  $k = 0, ..., \delta(v) - 1$  the iterator ranges from 0 to  $I_k(v)$ . For instance, operation l in the matrix multiplication example of Figure 3.1 has  $\delta(l) = 2$ surrounding loops and iterator bound vector  $I(l) = \begin{bmatrix} 49 & 49 \end{bmatrix}^T$ . An execution of an operation v can thus be characterised by a vector  $\mathbf{i} \in \mathbb{Z}^{\delta(v)}$ , with  $\mathbf{0} \le \mathbf{i} \le I(v)$ . The set of all iterator vectors for an operation v is called the *iterator space*, and denoted by  $\mathcal{I}(v) = \{\mathbf{i} \in \mathbb{Z}^{\delta(v)} \mid \mathbf{0} \le \mathbf{i} \le I(v)\}$ .

In Figure 3.3 all executions are depicted for an operation with iterator bound vector  $I = \begin{bmatrix} 1 & 3 \end{bmatrix}^T$ . An operation *v* without enclosing loops has dimension of repetition  $\delta(v) = 0$ . This operation has exactly one execution, which is denoted by the empty vector []. In the same way, we talk about executions of ports. The iterator space of a port  $p \in P(v)$  of an operation  $v \in V$  is given by  $\mathcal{I}(p) = \mathcal{I}(v)$

Figure 3.4. An example of data dependencies of the  $2 \times 2$  version of the matrix multiplication example of Figure 3.1, depicted by means of edges between port executions. The edges are labelled with the array elements associated with the dependencies.

and its dimension by  $\delta(p) = \delta(v)$ . The set of all executions of port p is denoted by  $\mathcal{E}(p) = \{ (p, \mathbf{i}) | \mathbf{i} \in \mathcal{I}(p) \}$ . We use  $\mathcal{E} = \bigcup_{p \in P} \mathcal{E}(p)$  for the set of all port executions.

Data consumption and data production of operations is described by ports. Each operation has a set of read ports, along which it reads data, and a set of write ports, on which it writes data. Data consumed or produced by an execution *i* of port *p* are described by an element of a multidimensional array with  $\alpha(p)$  dimensions. The array element that is accessed by execution *i* of port *p* is given by an *index vector*  $\mathbf{n}(p, \mathbf{i}) \in \mathbb{Z}^{\alpha(p)}$  as a linear expression in *i* by

$$\boldsymbol{n}(p, \boldsymbol{i}) = \boldsymbol{A}(p)\boldsymbol{i} + \boldsymbol{b}(p),$$

using the index matrix A(p) and index vector b(p). For instance, for port *s* of our matrix multiplication example of Figure 3.1 we have

$$\boldsymbol{n}(s, \boldsymbol{i}) = \boldsymbol{A}(s)\boldsymbol{i} + \boldsymbol{b}(s)$$

$$= \begin{bmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} i_0 \\ i_1 \\ i_2 \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

$$= \begin{bmatrix} i_2 \\ i_1 \end{bmatrix}.$$

#### 3.2 Schedules

In Figure 3.2 the index matrices and index offset vectors for all ports in the matrix multiplication example are given.

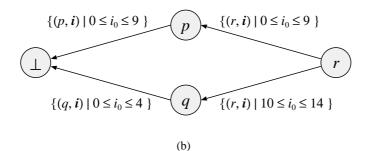

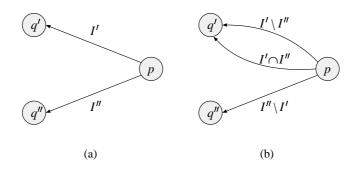

Data dependencies are described by edges between ports; the presence of an edge  $(p,q) \in E$  means that data produced by an execution *i* of write port *p* is consumed by an execution *j* of read port *q* if they refer to the same array element, i.e., n(p,i) = n(q,j). Figure 3.4 depicts all data dependences of the matrix multiplication example.

In order to identify which ports access same array, we introduce the notion of array clusters.

**Definition 3.2 (array clusters).** Two ports p and q are said to access the same array, denoted by  $p \bowtie q$ , if they are weakly connected in the program graph, i.e., there is a list of ports  $(p_0, ..., p_n)$ , with  $n \ge 0$ ,  $p_0 = p$ ,  $p_n = q$ , and

$$(p_i, p_{i+1}) \in E \lor (p_{i+1}, p_i) \in E,$$

for each i = 0, ..., n-1. Now, an array cluster  $A \subseteq P$  is defined as a set of weakly connected ports, i.e.,  $p \bowtie q$  for all  $p, q \in A$ , such that the set cannot be extended. The set of all array clusters is denoted by A.

In our matrix multiplication example of Figure 3.1 ports p, q, and t are weakly connected, so they form an array cluster  $\{p,q,t\}$ . Ports r and s are not connected to any other port. Hence for this example we have array clusters  $\mathcal{A} = \{\{p,q,t\}, \{r\}, \{s\}\}$ . These three clusters correspond to the arrays Z, X, and Y, respectively, in Figure 3.1.

In order to make data dependencies unique, we introduce a so-called *single-assignment* property, which is formally defined as follows.

**Definition 3.3 (single assignment).** An array  $A \in \mathcal{A}$  is said to have the singleassignment property if and only if for each  $p, q \in A \cap W$ , each execution  $i \in \mathcal{I}(p)$ , and each execution  $j \in \mathcal{I}(q)$  we have

$$\boldsymbol{n}(p, \boldsymbol{i}) = \boldsymbol{n}(q, \boldsymbol{j}) \Rightarrow p = q \land \boldsymbol{i} = \boldsymbol{j}.$$

The single-assignment property means that each array element may be written at most once.

#### 3.2 Schedules

So far we have not discussed the order of execution of operations, nor the actual memory positions for array elements. These are the decision variables of our scheduling problem. A schedule is defined by a *time assignment*, which gives a partial order on the execution of operations, and an *address assignment*, which

Figure 3.5. Two possible time assignments for operation *m* of the 2 × 2 variant of the matrix multiplication example of Figure 3.1. The first assignment has start time s(m) = 1 and period vector  $\boldsymbol{p}(m) = \begin{bmatrix} 7 & 3 & 1 \end{bmatrix}^{\mathrm{T}}$ , the second one has start time s(m) = 7 and period vector  $\boldsymbol{p}(m) = \begin{bmatrix} 4 & 1 & -7 \end{bmatrix}^{\mathrm{T}}$ .

gives a mapping of array elements onto actual memory locations, which are also called addresses.

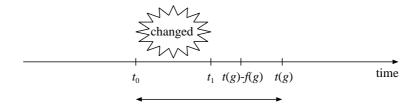

First we discuss the time assignment. In our model we use time only to define a partial order on the execution of operations. A time assignment, for instance, that assigns times 4 and 9 to two executions e and f of operations, respectively, merely demands that e is executed before f. If two executions e and f are assigned the same time, these executions are not ordered by the schedule. In this case e may be executed before f or the other way around.

A time assignment is defined as follows.

**Definition 3.4 (time assignment).** Given is a program graph (V, R, W, I, E, A, b). Then a time assignment  $\tau$  is a pair (p, s), where

- $p(v) \in \mathbb{Z}^{\delta(v)}$  denotes a *period vector*, for each operation  $v \in V$ , and

- $s(v) \in \mathbb{Z}$  denotes a *start time* for each operation  $v \in V$ .

The start time and period vector of an operation  $v \in V$  fix the time of execution *i* of operation *v* through the expression

$$t(v, \mathbf{i}) = \mathbf{p}^{\mathrm{T}}(v)\mathbf{i} + s(v).$$

The start time is the time at which execution i = 0 of operation v takes place. In general periods  $p_j$  may be negative. As a result, the start time of an operation can be different from the time at which the first execution of an operation takes place.

Two possible time assignments for the matrix multiplication example of Figure 3.1 are shown in Figure 3.5. For the first one, execution i of operation m takes

#### 3.3 Constraints

place at

$$t(m, \mathbf{i}) = \mathbf{p}^{\mathrm{T}}(m)\mathbf{i} + s(m) = \begin{bmatrix} 7 & 3 & 1 \end{bmatrix} \begin{bmatrix} i_0 \\ i_1 \\ i_2 \end{bmatrix} + 1 = 7i_0 + 3i_1 + i_2 + 1.$$

The time assignment also determines the order of execution of all ports. Each execution i of port  $p \in P(v)$  of operation v takes place at the same moment as execution i of the operation itself, i.e., t(p,i) = t(m,i). Therefore, we define p(p) = p(v) and s(p) = s(v) for all ports  $p \in P(v)$ .

Besides a time assignment we need a way to determine the address on which each array element is stored in memory.

**Definition 3.5 (address assignment).** Given a program graph (V, R, W, I, E, A, b), an address assignment  $\mu$  is a pair (c, o), where

- $c(A) \in \mathbb{Z}^{\alpha(A)}$  denotes an *address coefficient vector*, for each  $A \in \mathcal{A}$ , and

- $o(A) \in \mathbb{Z}$  denotes an *address offset*, for each  $A \in \mathcal{A}$ .

The address assignment  $\mu$  fixes the address of array element with index vector  $\boldsymbol{n}$  of array cluster  $A \in \mathcal{A}$  by

$$a(A, \boldsymbol{n}) = \boldsymbol{c}^{\mathrm{T}}(A)\boldsymbol{n} + o(A).$$

The address at which the data belonging to execution i of port  $p \in A$  is then given by

$$a(p, \mathbf{i}) = a(A, \mathbf{n}(p, \mathbf{i})) = \mathbf{c}^{\mathrm{T}}(A)\mathbf{n}(p, \mathbf{i}) + o(A).$$

**Definition 3.6 (schedule).** Given a program graph  $\mathcal{G}$ , a schedule  $\sigma = (\tau, \mu)$  is the combination of a time assignment  $\tau$  and an address assignment  $\mu$ .

#### 3.3 Constraints

Constraints on schedules are introduced as not all schedules are valid. Precedence constraints limit the possible time assignments by demanding that each execution of a write port that refers an array element takes place before all executions of read ports that refer the same array element.

**Definition 3.7 (precedence constraints).** Given are a program graph  $\mathcal{G} = (V, R, W, I, E, A, b)$  and a time assignment  $\tau = (p, s)$ . Then, for each execution *i* of a write port  $p \in W$ , and for each execution *j* of a read port  $q \in R$ , with  $(p,q) \in E$ , the precedence constraints specify that

$$\boldsymbol{n}(p, \boldsymbol{i}) = \boldsymbol{n}(q, \boldsymbol{j}) \Rightarrow t(p, \boldsymbol{i}) < t(q, \boldsymbol{j}).$$

A time assignment  $\tau$  is called a *feasible time assignment* with respect to a program graph  $\mathcal{G}$  if all precedence constraints are met. For the time assignments in Figure 3.5 the first assignment is feasible. The second one is infeasible as none of the precedence constraints for ports q and t are satisfied.

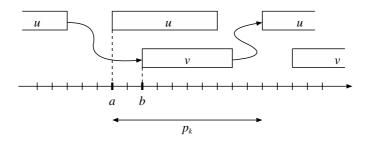

Next, we have address constraints, demanding that the memory location of an array element may be not overwritten during its lifetime. The lifetime of an array element is the time interval from the production until the last consumption. An address conflict for write ports p, r, and read port q occurs if there are executions of p and q that access the same array element, i.e., the same index vector of the same array, and the address belonging to that array element has been overwritten by an execution of r between the executions of p and q.

**Definition 3.8 (address constraints).** Given are a program graph  $\mathcal{G} = (V, R, W, I, E, A, b)$ , a feasible time assignment  $\tau = (p, s)$ , and an address assignment  $\mu = (c, o)$ . Then, for each execution *i* of a write port  $p \in W$ , and for each execution *j* of a read port  $q \in R$ , with  $(p,q) \in E$  and n(p,i) = n(q,j), the address constraints specify that for each execution *k* of a write port  $r \in W$

$$a(p, \mathbf{i}) = a(r, \mathbf{k}) \land t(p, \mathbf{i}) \le t(r, \mathbf{k}) < t(q, \mathbf{j}) \Rightarrow p = r \land \mathbf{i} = \mathbf{k}$$

if r and q belong to the same operation, or

$$a(p, \mathbf{i}) = a(r, \mathbf{k}) \land t(p, \mathbf{i}) \le t(r, \mathbf{k}) \le t(q, \mathbf{j}) \Rightarrow p = r \land \mathbf{i} = \mathbf{k}$$

if r and q belong to different operations.

We need stronger address constraints for the case where ports  $r \in W$  and  $q \in R$  belong to different operations, as at time  $t(r, \mathbf{k}) = t(q, \mathbf{j})$  executions  $\mathbf{j}$  of port q and  $\mathbf{k}$  of port r are not ordered. For the case where ports r and q belong to the same operation, we assume that for an execution of this operation the execution of read port q occurs before the execution of write port r, resulting in weaker address constraints.

The address constraint for ports p, q, and r with  $(p,q) \in E$  is denoted by  $(p \rightarrow q, r)$ . The address constraints for the matrix multiplication example of Figure 3.1 are  $(p \rightarrow q, p)$ ,  $(p \rightarrow q, t)$ ,  $(t \rightarrow q, p)$ , and  $(t \rightarrow q, t)$ .

An address assignment  $\mu$  is called a *feasible address assignment* with respect to a program graph  $\mathcal{G}$  and time assignment  $\tau$  if all address constraints are met.

A schedule  $(\tau, \mu)$  is called a *feasible schedule* with respect to a program graph  $\mathcal{G}$  if  $\tau$  is feasible with respect to  $\mathcal{G}$  and  $\mu$  is feasible with respect to  $\mathcal{G}$  and  $\tau$ .

#### 3.4 Objectives

The objective of our scheduling problem is to minimise the number of cache misses of a program. When computing the number of cache misses for an execution of a

#### 3.4 Objectives

schedule, we need knowledge about the size of the cache, the associativity, the block size, and the replacement policy. As LRU is the most effective replacement scheme in practice, we assume LRU replacement in the remainder of this chapter. The following definition of a cache together with a schedule contains sufficient information for determining the number of cache misses.

**Definition 3.9 (cache).** A cache C is a triple  $(c_s, s_s, b_s)$ , where

- $c_{s} \in \mathbb{N}_{+}$  denotes the size of the cache in blocks,

- s<sub>s</sub> ∈ N<sub>+</sub> with s<sub>s</sub> | c<sub>s</sub>, denotes the associativity, or, the size of each cache set in blocks,

- $b_s \in \mathbb{N}_+$  denotes the size of each *block* in bytes.

The number of sets of which a cache consists is given by  $n_s = \frac{c_s}{s_s}$ . An address *a* maps to set  $s(a) = a \mod n_s$ . The block address of an address *a* is  $a_b(a) = a \dim b_s$ .

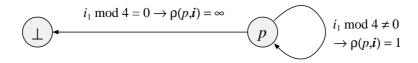

# 3.4.1 LRU cache model

We give a formal model of cache misses in a cache with LRU replacement. During the execution of a program, a CPU accesses an address a(e) for each execution  $e \in \mathcal{E}$  of a port.

A so-called *compulsory miss* for port execution  $e \in \mathcal{E}$  occurs if it is the first to access block address  $a_b(e)$ . To determine this, we define M(e) as the set of port executions that access block address  $a_b(e) = a(e) \operatorname{div} b_s$  and that execute before e, i.e.,

$$M(e) = \{ f \in \mathcal{E} \mid a_{\mathbf{b}}(f) = a_{\mathbf{b}}(e) \land t(f) < t(e) \}.$$

A compulsory miss for e occurs if no port executions access  $a_b(e)$  before e, i.e.,

$$comp(e) \Leftrightarrow M(e) = \emptyset.$$

(3.1)

If port execution *e* is the first port execution that accesses block address  $a_b(e)$ , and there is another port execution *f* that accesses  $a_b(e)$  at the same time t(f) = t(e), then both *e* and *f* will cause a compulsory miss in this cache model. Counting these misses twice can be avoided by assigning different times to these port executions.

A so-called *expiration miss* for port execution  $e \in \mathcal{E}$  in a fully set-associative cache occurs if there are too many port executions accessing block addresses different from  $a_b(e)$  between e and the *most recent* port execution preceding e accessing  $a_b(e)$ . We denote the time at which this port execution takes place by

$$m(e) = \max_{f \in M(e)} t(f).$$

The set of block addresses accessed between m(e) and t(e) is given by

$$Ac(e) = \{ a_{\mathbf{b}}(f) \mid f \in \mathcal{E} \land m(e) \le t(f) \le t(e) \}.$$

A port execution *e* causes an expiration miss in a fully set-associative cache if and only if *e* does not cause a compulsory miss and the set of block addresses between the previous access to  $a_b(e)$  and *e* itself exceeds the size of the cache, i.e.,  $|Ac(e)| > c_s$ . As port executions that take place at the same time are not ordered, we once again assume that all port executions  $f \in \mathcal{E}$  with t(f) = t(e) execute before *e*.

The treatment of an expiration miss in a *n*-way set-associative cache is analogous to treatment in the fully set-associative case, but now we are not interested in the accesses to the whole cache, but only in those to the set that *e* accesses, i.e., we consider the set

$$S(e) = \{a_{\mathsf{b}}(f) \mid f \in \mathcal{E} \land m(e) \le t(f) \le t(e) \land s(a(f)) = s(a(e))\}.$$

Port execution e causes an expiration miss if there is not enough room in the set that is accessed by e, i.e.,

$$ex(e) \Leftrightarrow \neg comp(e) \land |S(e)| > s_{s}.$$

(3.2)

As s(a(e)) = s(a(f)) for all executions *e* and *f* in the fully set-associative case, S(e) = Ac(e), and hence (3.2) is a general characterisation of expiration misses, irrespective of the associativity.

Every port execution causes either a hit or a miss in the cache. As a port execution cannot cause both a compulsory miss and an expiration miss, the total number of cache misses is the sum of the number of compulsory misses and the number of expiration misses, i.e.,

$$c_{\mathcal{G},\mathcal{C}}(\sigma) = |\{e \in \mathcal{E} \mid comp(e) \lor ex(e)\}| \\ = |\{e \in \mathcal{E} \mid comp(e)\}| + |\{e \in \mathcal{E} \mid ex(e)\}|.$$

The miss rate is the fraction of port executions that causes a miss, and is given by

$$\varphi_{\mathcal{G},\mathcal{C}}(\sigma) = \frac{c_{\mathcal{G},\mathcal{C}}(\sigma)}{|\mathcal{E}|}.$$

# 3.4.2 FIFO cache model

We can do the same exercise for caches employing a *least recently replaced* strategy. In literature this replacement scheme is referred to as FIFO.

As the occurrence of a miss depends on data being available in the cache, we are interested in knowing when data enter the cache. If a block address is accessed for the first time during the execution of a schedule, a compulsory miss is caused. Data will then remain in the cache up to the  $s_s^{th}$  miss after the data entered the cache. As before, we define

$$M(e) = \{ f \in \mathcal{E} \mid a_{\mathbf{b}}(f) = a_{\mathbf{b}}(e) \land t(f) < t(e) \},\$$

#### 3.5 Formal problem statement

and again a compulsory miss occurs if and only if  $M(e) = \emptyset$ .

For expiration misses we are interested in the moment the last miss on  $a_{b}(e)$  occurred, which is given by

$$l(e) = \max_{f \in M(e) \land miss(f)} t(f).$$

We then count the number of misses since the last miss, by considering the set

$$S(e) = \{ f \in \mathcal{E} \mid miss(f) \land l(e) \le t(f) < t(e) \land s(a(e)) = s(a(f)) \},\$$

and we derive that a miss occurrence is given by

$$miss(e) \Leftrightarrow M(e) = \emptyset \lor |S(e)| > s_s.$$

The definition for miss(e) is indeed a valid definition as miss(f) is used in the definition for f(e) and S(e) only for t(f) < t(e). The number of cache misses  $c_{\mathcal{G},\mathcal{C}}(\sigma)$  and miss rate  $\varphi_{\mathcal{G},\mathcal{C}}(\sigma)$  are defined in a similar way as we did for the LRU cache. In the remainder of this thesis the number of cache misses  $q_{\mathcal{G},\mathcal{C}}(\sigma)$  and the miss rate  $\varphi_{\mathcal{G},\mathcal{C}}(\sigma)$  refer to caches with LRU replacement, as LRU is more effective than FIFO [Chrobak & Noga, 1999].

#### **3.5** Formal problem statement

We now can define the problem that is studied in this thesis.

**Definition 3.10 (multidimensional periodic cache scheduling (MPCS)).** Given a program graph  $\mathcal{G}$  and a cache  $\mathcal{C}$ , find a feasible schedule  $\sigma$  for which  $c_{\mathcal{G},\mathcal{C}}(\sigma)$  is minimal.

# 3.6 Special properties

In this section special properties of program graphs and schedules are discussed that are often used in the remainder of this thesis.

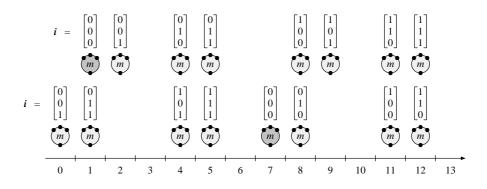

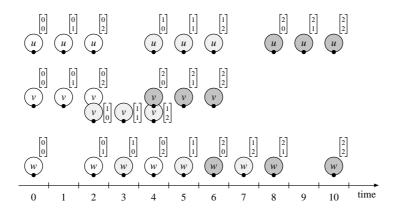

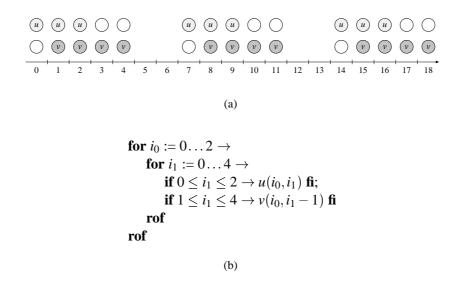

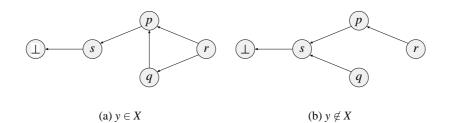

#### 3.6.1 Lexicographical executions

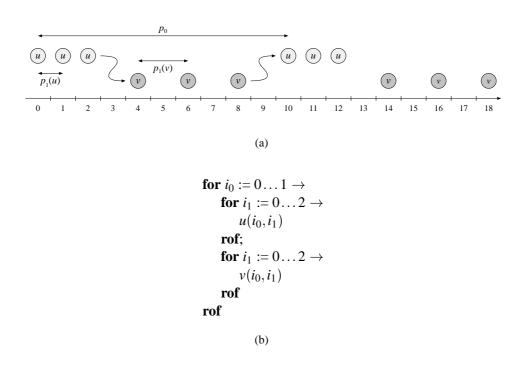

A loop nest is said to have lexicographical executions if the periods are ordered in such a way that all executions within an inner dimension take place in the period of an outer dimension. For weak lexicographical executions the first and last execution in an inner dimension of two successive executions of the outer dimension may take place at the same time. For an example see Figure 3.6, where operation u has lexicographical executions, operation v only has the weak lexicographical property, and w has no lexicographical property. In the following definition we formalise these properties.

**Definition 3.11 (lexicographical execution).** Given are an iterator bound vector  $I \in \mathbb{N}^{\delta}_{+}$  and a period vector  $p \in \mathbb{Z}^{\delta}$ . The iterator bound vector and period vector

Figure 3.6. Three operations u, v, and w with iterator bound vector  $I = \begin{bmatrix} 2 & 2 \end{bmatrix}^T$ , start time 0 and period vectors  $p(u) = \begin{bmatrix} 4 & 1 \end{bmatrix}^T$ ,  $p(v) = \begin{bmatrix} 2 & 1 \end{bmatrix}^T$ , and  $p(w) = \begin{bmatrix} 3 & 2 \end{bmatrix}^T$ . The executions of the outer dimension have been shaded differently.

are said to have the lexicographical execution property, denoted by lex(I, p), if and only if for all vectors  $i, j \in \mathbb{Z}^{\delta}$  with  $0 \le i, j \le I$  holds

$$i <_{\text{lex}} j \Leftrightarrow p^{\mathsf{T}} i < p^{\mathsf{T}} j$$

The vectors have the *weak* lexicographical property, denoted by wlex(I, p), if and only if for all vectors  $i, j \in \mathbb{Z}^{\delta}$  with  $0 \le i, j \le I$  holds

$$i \leq_{\text{lex}} j \Rightarrow p^{\mathsf{T}} i \leq p^{\mathsf{T}} j.$$