# Design, realisation and test of GaAs-based monolithic integrated X-band high-power amplifiers

Citation for published version (APA):

Hek, de, A. P. (2002). Design, realisation and test of GaAs-based monolithic integrated X-band high-power amplifiers. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Netherlands Organisation for Applied Scientific Research]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR556152

DOI:

10.6100/IR556152

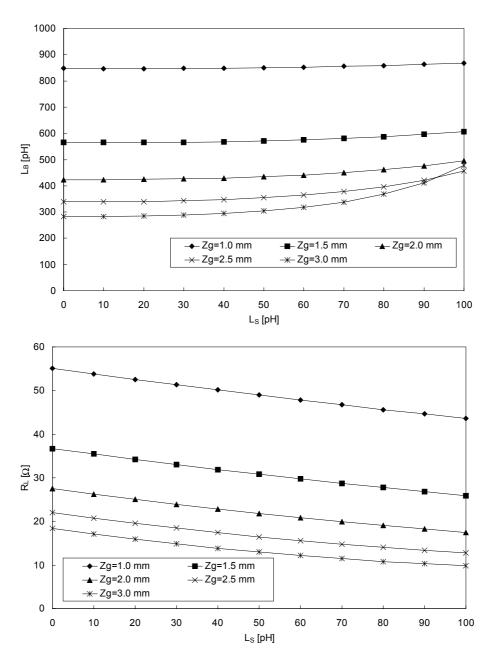

Document status and date:

Published: 01/01/2002

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

Design, Realisation and Test of GaAs-based Monolithic Integrated X-band High-Power Amplifiers

# Design, Realisation and Test of GaAs-based Monolithic Integrated X-band High-Power Amplifiers

# **PROEFONTWERP**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 2 juli 2002 om 16.00 uur

door

Andries Pieter de Hek

geboren te Hardinxveld Giessendam

De documentatie van het proefontwerp is goedgekeurd door de promotoren:

prof.Dr.-Ing. L.M.F. Kaufmann en prof.dr. P.J. Tasker

Copromotor:

prof. J.L. Tauritz, M.Sc.

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Hek, Andries P. de

Design, realisation and test of GaAs-based monolithic integrated X-band high-power amplifiers / by Andries P. de Hek. – Eindhoven : Technische Universiteit Eindhoven, 2002.

Proefontwerp. - ISBN 90-386-1920-0 NUR 959

Trefw.: microgolfversterker / geintegreerde schakelingen ; ontwerp / galliumarsenidetransistoren / vermogenstransistoren / microgolfmetingen. Subject headings: MMIC power amplifiers / integrated circuit design / gallium arsenide / power transistors / microwave measurement.

Copyright © 2002 by A.P. de Hek

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilised in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

Druk: Universiteitsdrukkerij Technische Universiteit Eindhoven

6 Contents

# **Contents**

| 1. | INTRO             | DDUCTION                                             | 10 |

|----|-------------------|------------------------------------------------------|----|

|    |                   | H-POWER AMPLIFIERS FOR PHASED-ARRAY RADAR            |    |

|    | 1.2 Prof          | BLEM, GOAL AND ORGANISATION                          |    |

|    | 1.2.1             | Problem and goal                                     |    |

|    | 1.2.2             | Organisation                                         |    |

|    | 1.3 Refe          | ERENCES                                              | 14 |

| 2. | COMP              | ONENTS                                               | 15 |

|    | 2.1 Intr          | ODUCTION                                             | 15 |

|    |                   | LIUM ARSENIDE                                        |    |

|    | 2.3 ACTI          | IVE COMPONENTS                                       | 17 |

|    | 2.3.1             | Introduction                                         |    |

|    | 2.3.2             | Metal Semiconductor Field Effect Transistor          |    |

|    | 2.3.3             | Heterojunction Field Effect Transistor               |    |

|    | 2.3.4             | Transistor Layout                                    |    |

|    |                   | SIVE COMPONENTS                                      |    |

|    | 2.4.1             | Microstrip line                                      |    |

|    | 2.4.2             | Microstrip discontinuities                           |    |

|    | 2.4.3             | Inductor                                             |    |

|    | 2.4.4             | Capacitor                                            |    |

|    | 2.4.5<br>2.4.6    | Viahole                                              |    |

|    |                   | VIABORE                                              |    |

|    |                   | CLUSIONS                                             |    |

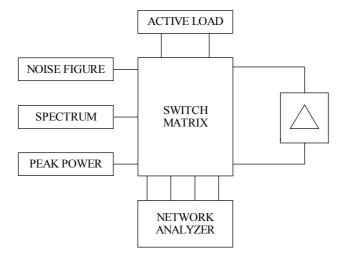

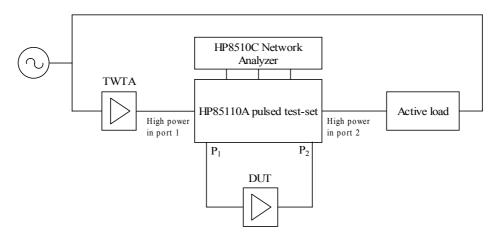

| •  |                   | POWER CHARACTERISATION SYSTEMS                       |    |

| 3. |                   |                                                      |    |

|    |                   | ODUCTION                                             |    |

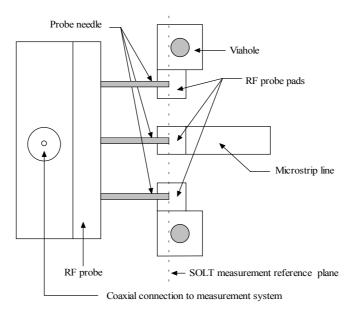

|    |                   | LL-SIGNAL MEASUREMENT SYSTEMS                        |    |

|    | 3.2.1             | Two-port S-parameter measurement system              |    |

|    | 3.2.2             | Three-port S-parameter measurement system            |    |

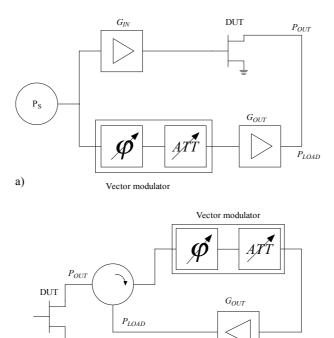

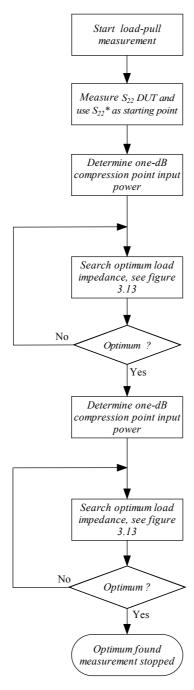

|    | 3.3 LARG<br>3.3.1 | GE-SIGNAL MEASUREMENT SYSTEM                         |    |

|    | 3.3.2             | Power measurement system                             |    |

|    | 3.3.2             | Load-pull measurement system                         |    |

|    | 3.3.3             |                                                      |    |

|    | 3.3.3             |                                                      |    |

|    |                   | CLUSIONS                                             |    |

|    |                   | ERENCES                                              |    |

| 4. | COMP              | ONENT MODELS                                         | 68 |

|    | 4.1 INTR          | ODUCTION                                             | 68 |

|    |                   | IVE COMPONENTS                                       |    |

|    | 4.2.1             | Transistor model extraction                          |    |

|    | 4.2.2             | EEFET3/EEHEMT1 large-signal transistor model results |    |

|    |                   | SIVE COMPONENTS                                      |    |

|    | 4.3.1             | Introduction                                         |    |

|    | 4.3.2             | Microstrip line                                      |    |

|    |                   | 1                                                    |    |

|    | 4.3.3    | Microstrip discontinuities                                         | 77  |

|----|----------|--------------------------------------------------------------------|-----|

|    | 4.3.3    | 3.1 45° microstrip bend                                            | 80  |

|    | 4.3.3    | 3.2 90° microstrip bend                                            | 81  |

|    | 4.3.3    | *                                                                  |     |

|    | 4.3.3    | 3.4 Microstrip crossing model                                      | 84  |

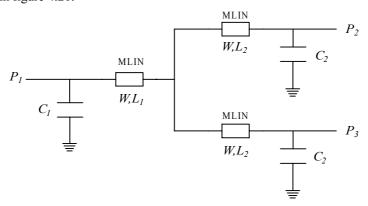

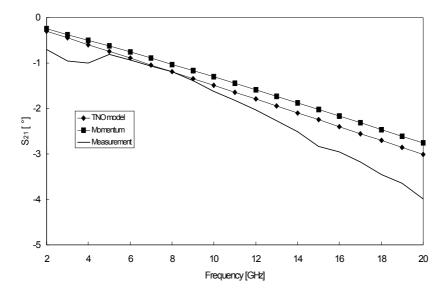

|    | 4.3.3    | 3.5 Symmetrical microstrip Y-junction model                        | 85  |

|    | 4.3.4    | Inductor                                                           | 87  |

|    | 4.3.5    | Capacitor                                                          | 88  |

|    | 4.3.6    | Resistor                                                           |     |

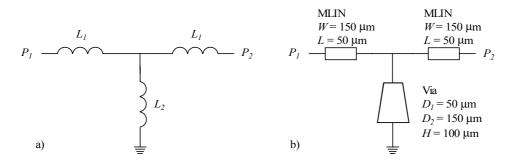

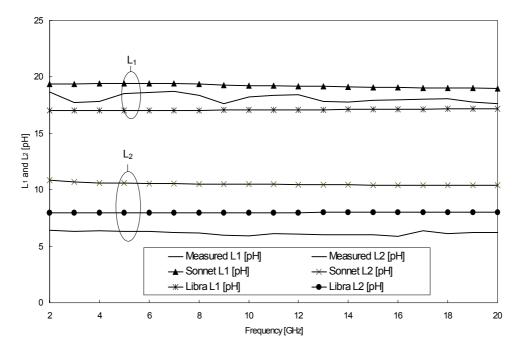

|    | 4.3.7    | Viahole                                                            |     |

|    |          | CLUSIONS                                                           |     |

|    | 4.5 Refi | ERENCES                                                            | 97  |

| 5. | HIGH-    | POWER AMPLIFIER TOPOLOGY AND TRANSISTOR CELL SIZE                  | 100 |

|    | 5.1 Intr | ODUCTION                                                           | 100 |

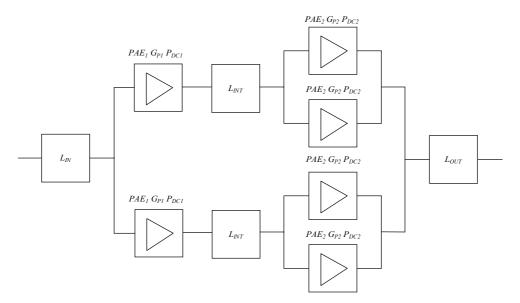

|    |          | LIFIER TOPOLOGY                                                    |     |

|    |          | NSISTOR SIZE AND LAYOUT                                            |     |

|    | 5.3.1    | Introduction                                                       |     |

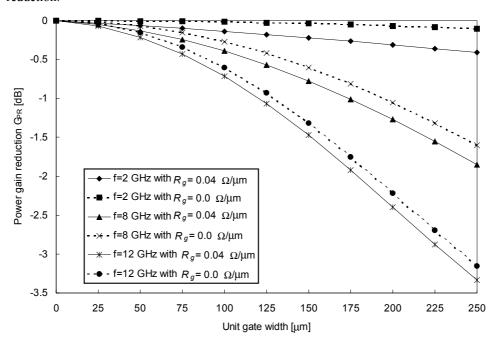

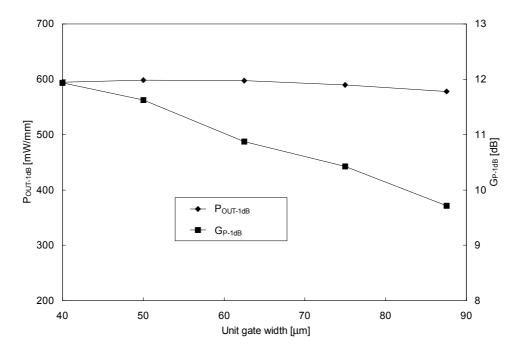

|    | 5.3.2    | Influence of unit gate width on transistor gain                    |     |

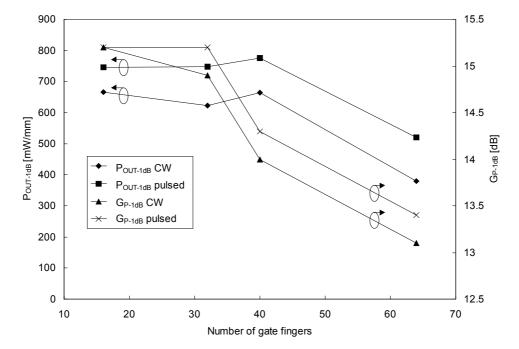

|    | 5.3.3    | Number of gate fingers.                                            |     |

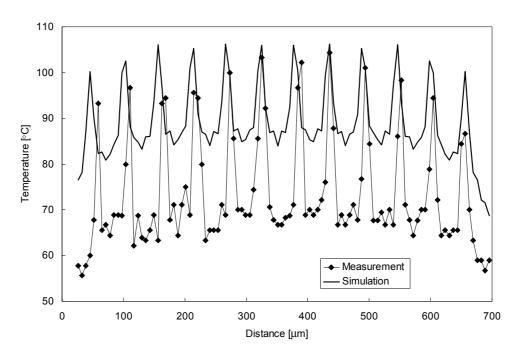

|    | 5.3.4    | Thermal analysis transistor                                        |     |

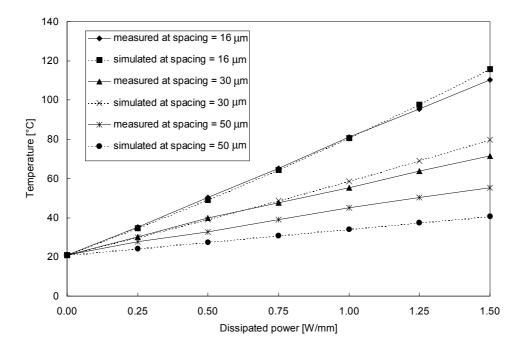

|    | 5.3.5    | Gate-to-gate spacing                                               |     |

|    |          | ECTION OPERATING CLASS AND DETERMINATION LOAD IMPEDANCE TRANSISTOR |     |

|    | 5.4.1    | Introduction                                                       |     |

|    | 5.4.2    | Selection operating class                                          |     |

|    | 5.4.3    | Determination optimum load impedance                               |     |

|    | 5.5 Reli | ABILITY IMPROVEMENT                                                |     |

|    |          | NSISTOR STABILITY ANALYSIS                                         |     |

|    |          | T TRANSISTOR CELLS USED IN AMPLIFIER DESIGNS                       |     |

|    | 5.7.1    | Selected unit transistor cell sizes                                | 143 |

|    | 5.7.2    | Stability unit transistor cells.                                   |     |

|    | 5.8 Con  | CLUSIONS                                                           | 147 |

|    | 5.9 Refi | ERENCES                                                            | 149 |

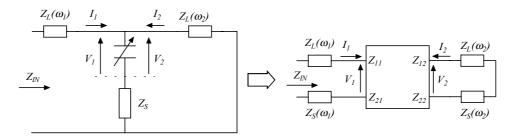

| 6. | HIGH-    | POWER AMPLIFIER DESIGN                                             | 153 |

| •• |          | ODUCTION                                                           |     |

|    |          | ODUCTION                                                           |     |

|    | 6.2.1    | Introduction                                                       |     |

|    | 6.2.2    | Wideband matching limitations                                      |     |

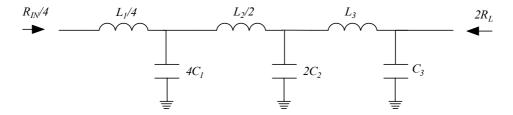

|    | 6.2.3    |                                                                    |     |

|    | 6.2.3    |                                                                    |     |

|    |          | 3.2 L-type matching networks                                       |     |

|    | 6.2.3    | **                                                                 |     |

|    | 6.2.3    |                                                                    |     |

|    | 6.2.3    | E                                                                  |     |

|    |          | CHING NETWORK DESIGN                                               |     |

|    | 6.3.1    | Introduction                                                       |     |

|    | 6.3.2    | Output-matching network design                                     |     |

|    | 6.3.3    | Interstage-matching network design                                 |     |

|    | 6.3.4    | Input-matching network design                                      |     |

|    |          | CUIT TO LAYOUT CONVERSION                                          |     |

|    |          |                                                                    |     |

8 Contents

|      | 6.5  |       | ALL HIGH-POWER AMPLIFIER SIMULATION                                        |       |

|------|------|-------|----------------------------------------------------------------------------|-------|

|      | 6.6  |       | NG CIRCUIT                                                                 |       |

|      | 6.7  |       | POWER AMPLIFIER STABILITY                                                  |       |

|      |      |       | Introduction                                                               |       |

|      |      |       | Low-frequency oscillations.                                                |       |

|      |      |       | Odd-mode oscillations                                                      |       |

|      |      |       | Parametric oscillations                                                    |       |

|      | 6.8  |       | LUSIONS                                                                    |       |

|      | 6.9  |       | RENCES                                                                     |       |

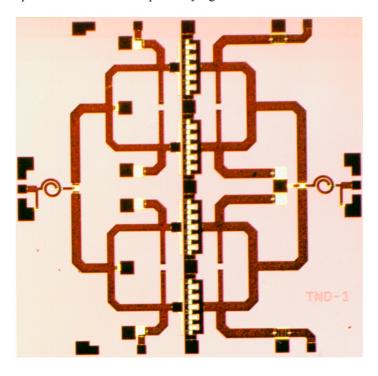

| 7.   | Н    | IGH-P | OWER AMPLIFIER RESULTS                                                     | 226   |

|      | 7.1  | INTRO | DUCTION                                                                    | 226   |

|      | 7.2  | MESI  | FET AMPLIFIER RESULTS.                                                     | 226   |

|      | 7.3  |       | AMPLIFIER RESULTS                                                          |       |

|      | 7.4  |       | ARISON WITH PUBLISHED X-BAND HPA RESULTS                                   |       |

|      | 7.5  |       | LUSIONS                                                                    |       |

|      | 7.6  | REFER | RENCES                                                                     | 243   |

| 8.   | C    | ONCL  | USIONS                                                                     | . 246 |

|      | 8.1  | INTRO | DUCTION                                                                    | 246   |

|      | 8.2  |       | IARY OF HIGH-POWER AMPLIFIER DESIGN PROCEDURE AND RESULTS                  |       |

|      | 8.3  |       | CABILITY OF TECHNIQUES AND MODELS TO OTHER APPLICATIONS                    |       |

|      | 8.4  | REFER | RENCES                                                                     | 252   |

| LI   | ST O | F SYN | 1BOLS                                                                      | 254   |

|      | om o | EAR   | ADELY ATIONS                                                               | 241   |

| LI   | SIU  | F ABE | BREVIATIONS                                                                | . 261 |

| Al   | PPEN | DIX A | PARAMETERS OF ELECTRICAL MODELS USED FOR HPA DESIGN                        | N 263 |

|      | A.1  | IN    | TRODUCTION                                                                 | 263   |

|      | A.2  | Mo    | DDEL PARAMETERS 45° MICROSTRIP BEND                                        | 263   |

|      | A.3  | Mo    | ODEL PARAMETERS 90° MICROSTRIP BEND                                        | 264   |

|      | A.4  |       | ODEL PARAMETERS SYMMETRICAL T-JUNCTION                                     |       |

|      | A.5  |       | DDEL PARAMETERS SYMMETRICAL MICROSTRIP CROSSING                            |       |

|      | A.6  |       | DDEL PARAMETERS Y-JUNCTION                                                 |       |

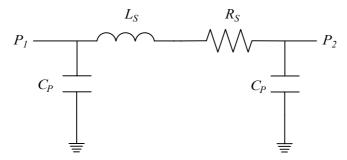

|      | A.7  |       | DDEL PARAMETERS OF AN INDUCTOR REALISED WITH THE HELP OF A MICROSTRIP LINE |       |

|      | A.8  |       | ODEL PARAMETERS OF A MIM CAPACITOR MODEL                                   |       |

|      | A.9  | RE    | FERENCES                                                                   | 273   |

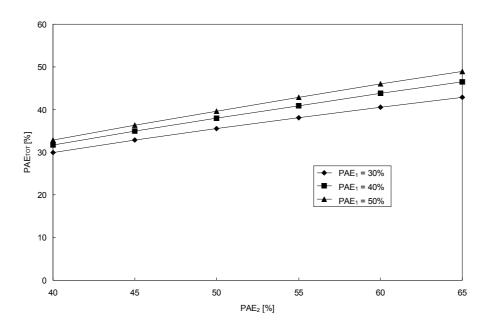

| Al   | PPEN | DIX B | POWER ADDED EFFICIENCY CALCULATIONS                                        | . 274 |

| ΑI   | PPEN | DIX C | TEMPERATURE COEFFICIENTS MESFET                                            | 280   |

|      | C.1  | Inn   | FRODUCTION                                                                 | 280   |

|      | C.1  |       | TERMINATION TEMPERATURE COEFFICIENTS                                       |       |

|      | C.3  |       | FERENCES                                                                   |       |

| Αl   |      | DIX D |                                                                            |       |

| - 44 |      | D     |                                                                            | 01    |

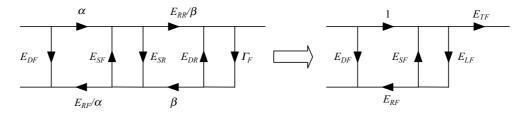

| Al   | PPEN | DIX E | N-PORT TO TWO-PORT NETWORK CONVERSION                                      | 288   |

| APPEN  | DIX F  | MODELLING OF THE LOAD AND SOURCE IMPEDANCE              | 291 |

|--------|--------|---------------------------------------------------------|-----|

| F.1    | Intr   | ODUCTION                                                | 291 |

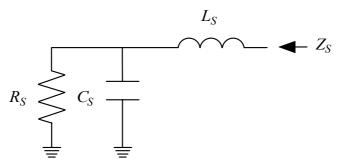

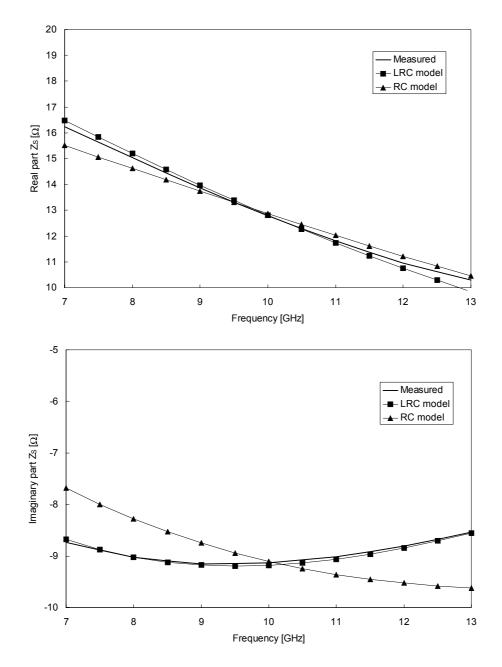

| F.2    | Mod    | ELLING OF SOURCE IMPEDANCE                              | 291 |

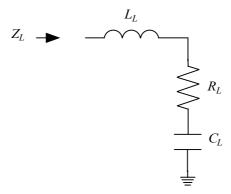

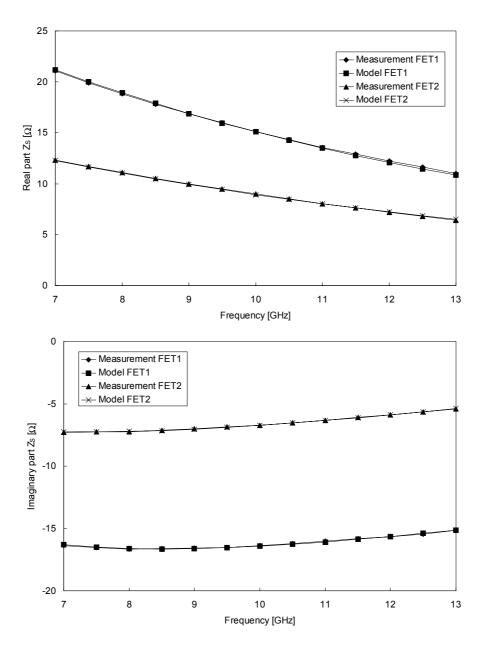

| F.3    | Mod    | ELLING OF LOAD IMPEDANCE                                | 294 |

| F.4    | Refe   | RENCES                                                  | 296 |

| APPEN  | DIX G  | CALCULATION OF THE DIMENSIONS OF THE LAYOUT             | 297 |

| G.1    | INTR   | DDUCTION                                                | 297 |

| G.2    | EQUA   | ATIONS FOR THE CALCULATION DIMENSIONS MATCHING ELEMENTS | 297 |

| G.3    | Refe   | RENCES                                                  | 300 |

| APPEN  | DIX H  | PARAMETRIC OSCILLATIONS                                 | 301 |

| H.1    | Intr   | DDUCTION                                                | 301 |

| H.2    | PARA   | METRIC OSCILLATION CONDITION                            | 301 |

| H.3    | Refe   | RENCES                                                  | 304 |

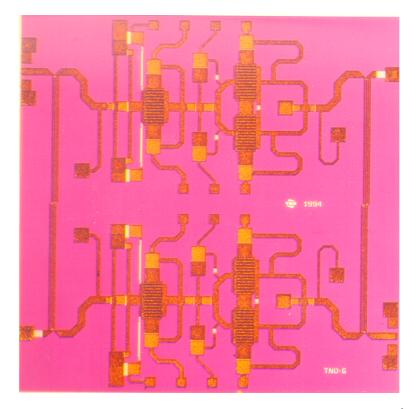

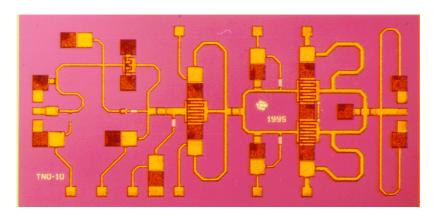

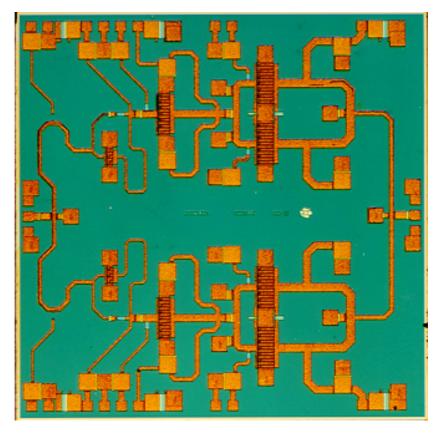

| APPEN  | DIX I  | OVERVIEW OF REALISED HIGH-POWER AMPLIFIERS              | 305 |

| I.1    | INTROD | JCTION                                                  | 305 |

| I.2    | OVERVI | EW MESFET AMPLIFIER DESIGNS                             | 305 |

| I.3    | Overvi | EW HFET DRIVER AMPLIFIER DESIGNS                        | 307 |

| APPEN  | DIX J  | SUMMARY X-BAND HPA RESULTS                              | 310 |

| LIST O | F PUBL | ICATIONS AND REPORTS                                    | 312 |

| SUMM   | ARY    |                                                         | 316 |

|        |        |                                                         |     |

| SAME   | NVAIII | NG                                                      | 318 |

| ACKN   | OWLED  | GEMENT                                                  | 321 |

| CURRI  | CULUM  | VITAE                                                   | 322 |

### 1. Introduction

The use of integrated microwave circuits, for both commercial and military applications, has come to full bloom during the last decade. Military applications, in particular phasedarray radar and Electronic Warfare systems, initially stimulated the development of Monolithic Microwave Integrated Circuits (MMICs). Nowadays, further development is mainly driven by the demands of the telecommunication market. Increased demand from the commercial sector has resulted in a further maturing of the existing technology based on MEtal Semiconductor Field Effect Transistors (MESFET). Other technologies based on Heterojunction Field Effect Transistors (HFET) and Heterojunction Bipolar Transistors (HBT) have also emerged during the last decade and are now available for commercial application. The main drive for the use of MMICs is their potential for cost and size reduction. Cost reduction results from the integration of several functions on a single chip. In addition, test and mounting costs are reduced and system reliability is improved. Improved performance is obtained because the on-chip and chip-to-chip component spread is minimal. The cost reduction that is possible through the application of MMICs makes the realisation of systems such as phased-array radar economically feasible; the size reduction makes them technologically feasible. The high-power amplifiers discussed in this thesis are mainly intended for application in phased-array radar antenna systems. For this reason first a short introduction regarding phased-array radar antennas and the Transmit Receive (TR) module, which is used for each antenna element, will be given.

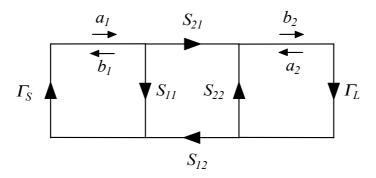

#### 1.1 High-power amplifiers for phased-array radar

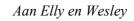

The development of phased-array radar originates from the increased demands upon radar systems. An example is the necessity to have multiple antenna beams simultaneously. One antenna beam is then for instance used for tracking a detected object while at the same time another beam is used for missile guidance. An active phased-array radar antenna consists of a number of antenna elements, which each have their own Transmit Receive module. The working principle of a linear phased-array antenna is visualised in figure 1.1. The antenna bundle is steered by giving each antenna element a different relative phase shift when compared to the other elements.

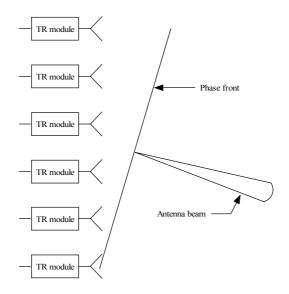

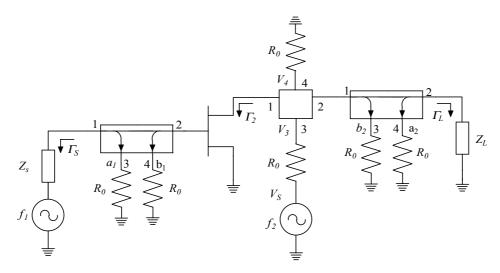

A phased-array antenna can consist of a few to several thousands of TR modules [1.1]. This large amount of TR modules requires the use of cheap highly integrated components to make the realisation of phased-array antennas economically feasible. The use of Monolithic Microwave Integrated Circuits (MMIC) is of vital importance for the realisation of this objective. In figure 1.2, the nowadays most commonly used components in a TR module are shown. The indicated phase shifter  $(\phi)$  and amplitude regulator (ATT) control the direction and the shape of the antenna pattern. The output power required to achieve a specified detection range is generated with the help of the depicted high-power amplifier (HPA).

Figure 1.1: Phased-array antenna principle.

Figure 1.2: Overview of MMICs used in TR module.

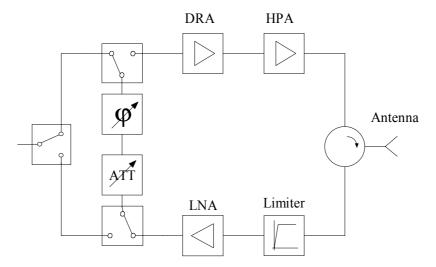

In the receive channel a low noise amplifier (LNA) is used to amplify the incoming radar signal. The TR module depicted in figure 1.2, shows the situation commonly encountered at the start of the work in 1992. The TR module topology foreseen for the near future is shown in figure 1.3. Most of the functions are integrated into one multi-function chip (MFC). Examples of such multi-function chips are described in literature [1.2, 1.3]. Probably the LNA and limiter will be integrated into one single chip.

Figure 1.3: TR module architecture for future phased-array radar systems [1.2, 1.3].

The high-power amplifier will be combined with the driver amplifier (DRA) onto a single chip. This indicates that a high-power amplifier is an important separate TR module component at this moment and will stay to be so in the foreseen future. The development of high-power amplifiers as a MMIC is the subject of this thesis. In the next section, the objectives of the work and content of this thesis will be discussed in detail.

#### 1.2 Problem, goal and organisation

#### 1.2.1 Problem and goal

The design of integrated microwave high-power amplifiers at X-band (8.0 - 12.4 GHz), that have both a broad bandwidth and a high efficiency, is the problem investigated in this thesis. These high-power amplifiers will be realised on GaAs wafers in two different transistor technologies, namely a MEtal Semiconductor Field Effect Transistor (MESFET) technology and a pseudomorphic Heterojunction Field Effect Transistor (HFET) technology.

At the start of the work described in this thesis:

- No procedure for the design of microwave integrated high-power amplifiers was available.

- No models for the transistors were available.

- The models for the passive components were inaccurate or even unavailable.

- No measurement systems were available for both the characterisation of high-power amplifiers and active and passive components including transistors, capacitors etc.

The primary goal pursued in this thesis therefore is, to give a systematic overview of all design steps that are necessary to realise a successful wideband high-efficiency microwave high-power amplifier. In addition, the component models and the measurement methods, developed in the scope of this thesis, which form an integral part of the design

methodology, are discussed. The final goal, which is pursued, is an investigation of the feasibility of the realisation of an X-band single chip combined driver and high-power amplifier.

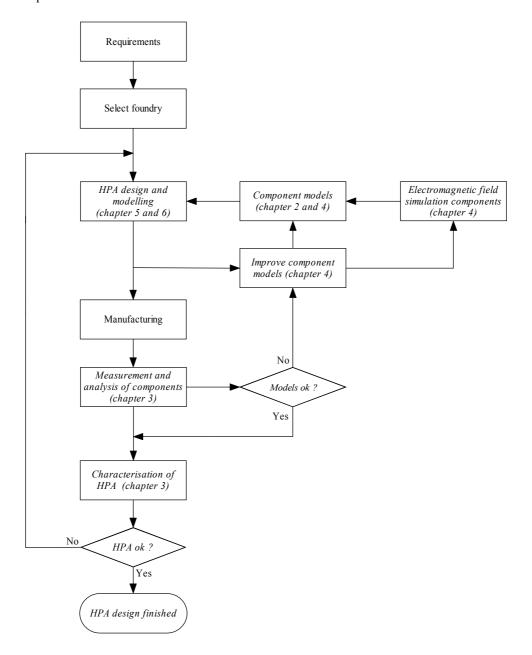

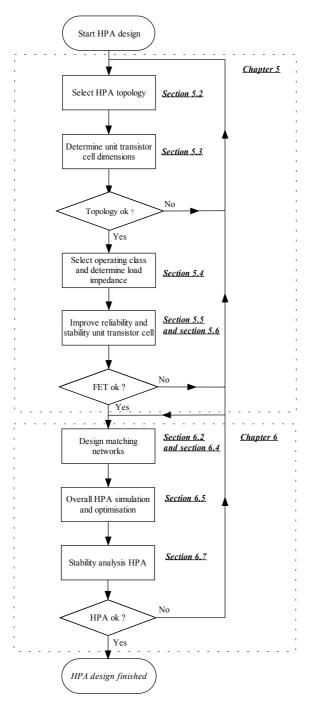

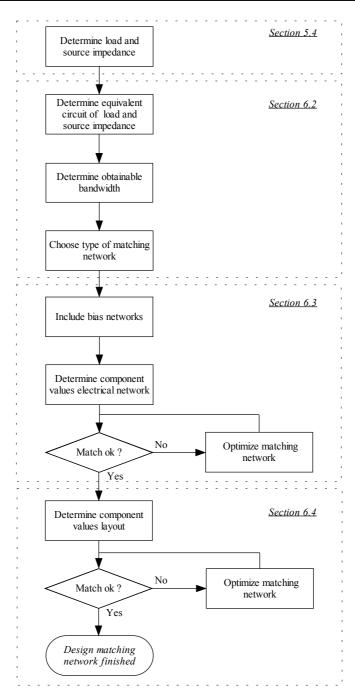

Figure 1.4: High-power amplifier design flow and the relevant chapter numbers.

#### 1.2.2 Organisation

An overview of the dominant factors for the design of high-power amplifiers is shown in figure 1.4. The subjects indicated in *italics* are discussed in detail in this thesis. The design always starts from a set of requirements. Based on the requirements, a foundry is selected that has a technology that is suited to realise the desired specification. After the foundry is selected, the actual high-power amplifier design starts. The procedures developed for the amplifier design will be discussed in detail in chapters 5 and 6. Essential inputs for the design are the active and passive components available in the given technology. In chapter 2 an overview is given of these available components along with their limitations when they are used for high-power amplifier design at X-band. This brings us to an important issue namely the necessity to include the effect of parasitic elements in the component models. The higher the frequency band of interest the more important this becomes. The models used are discussed in chapter 4. The information for both model development and verification comes from two different sources: electromagnetic field simulations and measurements. The measurement systems, developed in the scope of the work described in this thesis, are discussed in chapter 3. Information obtained with the help of these systems is used for component modelling and verification, but is also used for the design of the matching networks that are part of the high-power amplifier. The selection of the transistor layout, operating class and the influence of the selected transistor on the high-power amplifier are discussed in chapter 5. In chapter 6, the design of the high-power amplifiers is discussed. The measurement results of the realised high-power amplifiers are summarised in chapter 7. Finally in chapter 8 a number of conclusions and recommendations will be given.

#### 1.3 References

- [1.1] J. Bennett, K. Lewinski, P. Shearing, B. Velsher, J. van Houten and A. Tiesenga, "Quadpack X-band T/R Module for Active Phased Array Radar", *GAAS'98 Symposium Digest*, pp. 63-67, October 1998.

- [1.2] A. de Boer, M.W. van der Graaf, A.P. de Hek and T.C.B. Tieman, "A GaAs Multi-Function X-band MMIC for Space Based SAR Application with 7 bit Phase and Amplitude Control", *GAAS'98 Symposium Digest*, pp. 215-220, October 1998.

- [1.3] A. de Boer and K. Mouthaan, "GaAs Mixed Signal Multi-function X-band MMIC with 7 Bit Phase and Amplitude Control and Integrated Serial to Parallel Converter", *GAAS* "00 Symposium Digest, pp. 476-479, October 2000.

# 2. Components

#### 2.1 Introduction

To choose for the right technology is of vital importance for obtaining a good high-power amplifier performance. In this thesis, technology will be used interchangeably with process. The term technology covers the substrate material, the transistor layer stack, the passive components and the possible geometry of these components. The amplifiers discussed in this thesis are realised with the help of two different technologies. The first one is a MESFET technology, which is mature and already allows for the development of highpower amplifiers on a commercial basis. The second one is a HFET technology, which originally was less mature than the MESFET technology. The HFET technology used was optimised by the foundry during the work described in this thesis. This HFET technology makes the development of a combined driver and high-power amplifier on a single chip feasible. The HFET high-power amplifiers were realised on 3" wafers and the MESFET high-power amplifiers were realised on 4" wafers. Today the production of the MESFET process is using 6" wafers [2.1] and the HFET process 4" wafers, clearly demonstrating the rapid development of GaAs related processes. For the work described in this thesis, we had access to the DIOM20HP MESFET process of Infineon and the power HFET process of the Fraunhofer Gesellschaft-Institut für Angewandte Festkörperphysik (FhG-IAF). The choice for these two technologies was a sensible one at the start of the high-power amplifier design work in 1992. At that time, the alternative would have been a technology based on HBTs. However, at that time HBTs suffered from large reliability problems. Nowadays the situation is different and HBTs are an important option for every power amplifier application up to X-band as well. Above these frequencies, HFET technology is now the only viable option due to the available gain of HFETs. Industrial GaAs-based power HBT processes are available that have a reported Mean Time To Failure (MTTF) of more than 10<sup>6</sup> hours at 125 °C and a current density of 25 kA.cm<sup>-2</sup> [2.2]. The reliability of MESFET or HFET transistors is still better than before quoted MTTF for HBTs. For instance, Triquint quotes at a junction temperature of 150 °C a MTTF of more than 106 hours for their PHEMT process and more than 10<sup>8</sup> hours for their MESFET process.

In the remainder of this chapter, the active and passive components available in before mentioned technologies are discussed from a technology point of view. Where relevant also the limitations, such as the breakdown voltage of the transistor, are discussed. This chapter starts with the discussion of the used substrate material Gallium Arsenide (GaAs). The reasons why this substrate material is used are discussed, and a comparison is made with some other substrate materials that have potential for future high-power amplifier design. In section 2.3 and section 2.4 respectively, the active and passive components used for the amplifier design are discussed. The parameter extraction and device modelling of both the active and passive components is discussed in detail in chapter 4 after discussing the necessary measurement systems in chapter 3.

#### 2.2 Gallium Arsenide

The substrate material that is used for the amplifiers described in this thesis is GaAs. This substrate material has been the workhorse for the microwave industry for the development of MMICs, during the last decades. An important advantage of GaAs over Silicon (Si), which is commonly used at lower frequencies, is the fact that substrates as well as epitaxial layers can be made semi-insulating. This semi-insulating property is a prerequisite for monolithic integration of active and passive components and low-loss transmission lines. In table 2.1 the basic properties of GaAs, Silicon, Silicon Carbide (SiC) and Gallium Nitride (GaN) are compared at room temperature.

Table 2.1: Comparison of material properties [2.3]. For the breakdown field  $N_D = 1.10^{17}$  cm<sup>-3</sup> is taken into account. The electron and hole mobility is given for  $N_A = N_D = 1.10^{16}$  cm<sup>-3</sup>.

| Material | $\epsilon_{\rm r}$ | $E_G$ | Breakdown    | Electron            | Hole                | Saturation           | Thermal            |

|----------|--------------------|-------|--------------|---------------------|---------------------|----------------------|--------------------|

|          |                    | [eV]  | field        | mobility            | mobility            | velocity             | conductivity       |

|          |                    |       | $[V.m^{-1}]$ | $[m^2V^{-1}s^{-1}]$ | $[m^2V^{-1}s^{-1}]$ | [m.s <sup>-1</sup> ] | $[W.K^{-1}m^{-1}]$ |

| GaAs     | 12.8               | 1.43  | $65.10^6$    | 0.600               | 0.033               | $1.10^{5}$           | 46                 |

| Si       | 11.8               | 1.11  | $60.10^6$    | 0.135               | 0.045               | $1.10^{5}$           | 150                |

| 4H-SiC   | 9.7                | 3.20  | $35.10^7$    | 0.080               | 0.012               | $2.10^{5}$           | 490                |

| GaN      | 9.0                | 3.40  | $35.10^7$    | 0.100               | 0.030               | $15.10^4$            | 130                |

The materials GaN and SiC are added because they form interesting materials for future high-power amplifier designs. The first reason is their higher breakdown voltage, which gives a higher output power per occupied chip area and a second reason is the better thermal properties of the latter materials. At this moment in time they are, however, not an option to be considered in much detail in this thesis because these technologies are not yet available as a mature process. The thermal conductivity of GaAs is relatively poor when compared to the other materials listed in table 2.1. This is a point of concern for the development of the high-power amplifiers where a lot of heat is generated on a relatively small chip area. Because of this bad thermal conductivity, special countermeasures have to be made to reduce the gate finger temperature as much as possible. This will be discussed in more detail in chapter 5. Note that there is a direct relation between the reliability of the active devices and the temperature of the gate fingers [2.4]. Most failure mechanisms exhibited by semiconductors are due to the diffusion of atoms. Higher temperatures accelerate this diffusion process. The relation between reaction rate *R* and temperature is given by the Arrhenius equation [2.4]:

$$R = C \cdot e^{\frac{-E_a}{k \cdot T}} \,. \tag{2.1}$$

In this equation, C is a constant, K the Boltzmann constant, K the absolute temperature in K, and K is the activation energy K. The activation energy is a measure how effectively a failure mechanism utilises thermal energy. The effect of temperature variations can be described with the help of the acceleration factor,

$$AF = e^{\left(\frac{E_a}{k} \left(\frac{1}{T_0} - \frac{1}{T_A}\right)\right)}.$$

(2.2)

In this equation,  $T_{\theta}$  is the actual operating temperature and  $T_{A}$  is the accelerated temperature. The actual activation energies of the transistors used cannot be given here due to the non-disclosure agreements signed with the foundries. The maximum gate finger temperature that was considered to be acceptable by the foundries was approximately 125 °C. In the remainder of this section, the active and passive components, relevant for high-power amplifier design that can be realised on GaAs will be discussed.

## 2.3 Active components

#### 2.3.1 Introduction

In this section, the active components used in the high-power amplifier designs are discussed. In section 2.3.2 the working principle of the MESFET, which is used in most of the developed high-power amplifiers, is discussed. In this section also the figures of merit for high-power amplifier transistors, are discussed. The HFET is discussed in section 2.3.3. This section is concluded with a discussion of the various types of transistor layouts and their significance to high-power amplifier design in general will be highlighted.

# 2.3.2 Metal Semiconductor Field Effect Transistor

The MESFET has been the workhorse of the microwave industry during the last decades. This technology is mature and cheap compared to the HFET technology discussed in the next section. At this moment in time the realisation of high-power amplifiers based on MESFET technology is still attractive because it is a relatively cheap and well-proven technology.

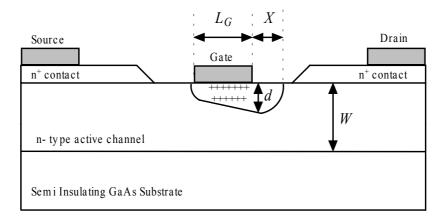

The MESFET technology used is the Self-Aligned Gate (SAG) DIOM20HP high-power technology of Infineon [2.5]. This technology allows the realisation of MMICs with a relatively small number of process steps. A simplified cross section of a MESFET is shown in figure 2.1; the space charge region is indicated beneath the gate contact.

Figure 2.1: Simplified cross section MESFET.

The MESFET consists of three metal electrodes that are connected to the active channel. The drain and source contacts to the active channel are made with the help of ohmic contacts. The current that flows from the drain to the source contact is controlled with the help of the voltage that is applied between the gate and the source electrode. The type of transistor used in this thesis is of the so-called depletion mode. This means that when no gate-source voltage is applied there still will flow a drain-source current. The gate contact is a Schottky barrier. This barrier forms a region beneath the gate that is completely free of charge carriers. Consequently, no current can flow through this region. This region can be further extended into the active channel by applying a more negative gate-source voltage. The voltage, at which the drain-source current ceases to flow through the active channel, is called the pinch-off voltage.

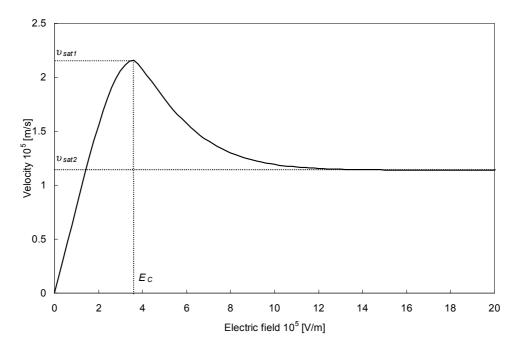

For the discussed MESFET, current saturation occurs for most drain-source voltages due to saturation of the electron drift velocity. The electron drift velocity as a function of the applied electric field E can be calculated with the help of the following equations [2.6]:

$$v(E) = \mu_0 \cdot E + \left(-2 \cdot \mu_0 \cdot E_C + 3 \cdot v_{sat1}\right) \cdot \frac{E^2}{E_C^2} + \left(\mu_0 \cdot E_C - 2 \cdot v_{sat1}\right) \cdot \frac{E^3}{E_C^3}, \quad (2.3)$$

when  $0 \le E \le E_C$  and,

$$v(E) = v_{sat2} + (v_{sat1} - v_{sat2}) \cdot e^{\left[-\alpha \left(\frac{E - E_C}{E_C}\right)^n\right]}, \tag{2.4}$$

if  $E > E_C$ . In this equation  $\mu_0$  is the low-field mobility,  $E_C$  the critical electric field,  $v_{sat1}$  the peak velocity and  $v_{sat2}$  the final saturation velocity,  $v_{sat2}$  is in the remainder of this thesis referenced to as  $v_{sat}$ . The factors  $\alpha$  and n are fitting factors, which model the transition of the low-field mobility region to the saturated velocity region. In table 2.2, some typical values for GaAs are listed [2.6, experiment 19].

Table 2.2: Parameters for GaAs at T = 300 K used in equations (2.3) and (2.4). The values of the listed parameters are taken from literature [2.6, experiment 19].

| $\mu_0  [\text{m}^2.\text{V}^{\text{-1}}.\text{s}^{\text{-1}}]$ | $E_C$ [V.m <sup>-1</sup> ] | $v_{sat1}$ [m.s <sup>-1</sup> ] | $v_{sat2}$ [m.s <sup>-1</sup> ] | α        | n       |

|-----------------------------------------------------------------|----------------------------|---------------------------------|---------------------------------|----------|---------|

| 0.75                                                            | $36.10^4$                  | $216.10^3$                      | $114.10^3$                      | 1.429759 | 1.26092 |

Equations (2.3) and (2.4) are used in combination with the numbers listed in table 2.2 to calculate the velocity as a function of the electric field as depicted in figure 2.2. The depicted results show a peak in the velocity at a low electric field  $E_C$ . For small gate lengths, the corresponding drain-source voltage is also low. At electric fields above  $E_C$  the electron-velocity saturates rapidly.

Figure 2.2: Velocity-electric field curve calculated for GaAs with the help of the numbers listed in table 2.2.

The active channel of the MESFET is formed with the help of n-type doped material. For high frequency transistors most of the time an n-type doping is used instead of p-type because n-type material has a higher saturation velocity than p-type material, see table 2.1.

This higher saturation velocity results in a higher cut-off frequency as can be seen from the following equation [2.7]:

$$f_T = \frac{v_{sat}}{2 \cdot \pi \cdot (L_G + X/2)}.$$

(2.5)

The cut-off frequency is defined as the frequency where the magnitude of the current gain of the transistor is reduced to one under the consideration that the output terminal of the transistor is short-circuited. In this equation (2.5), X is the extension of the space-charge layer into the gate-drain space as indicated in figure 2.1. This extension of the space-layer is bias dependent, as can be witnessed from [2.7]:

$$X \le \sqrt{\frac{2 \cdot \varepsilon_0 \cdot \varepsilon_r}{q \cdot N_D \cdot (V_{B0} - V_{GSI})}} \cdot (V_{B0} - V_{GDI}). \tag{2.6}$$

Consequently, also the cut-off frequency is bias dependent. Another important parameter that limits the highest operating frequency is the length of the gate  $L_G$  (figure 2.1), see equation (2.5) for the cut-off frequency of the intrinsic FET [2.7]. This equation shows that the cut-off frequency becomes higher when the gate length  $L_G$  becomes smaller. The gate length is 0.5  $\mu$ m for the DIOM20HP MESFETs. This results, ignoring parasitic or extrinsic FET elements, in a theoretical cut-off frequency of approximately 30 GHz. The parasitic elements of the transistor further reduce the cut-off frequency to approximately 12 GHz, see figure 2.4.

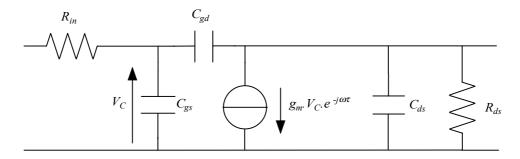

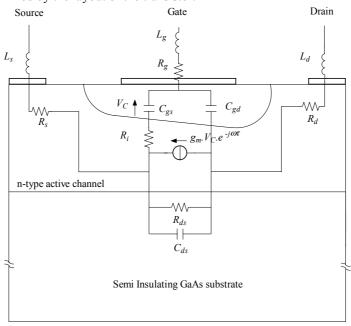

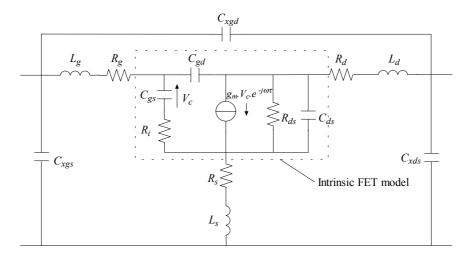

The cut-off frequency can also be written as a function of the equivalent circuit model parameters. A simplified model of an intrinsic FET is depicted in figure 2.3, a more detailed transistor model will be discussed in chapter 4.

Figure 2.3: Simplified intrinsic transistor model.

For this simplified intrinsic FET model, the cut-off frequency can be calculated with [2.7],

$$f_T = \frac{g_m}{2 \cdot \pi \cdot \left(C_{gs} + C_{gd}\right)}. (2.7)$$

The power gain  $G_P$  of a transistor is a very important figure of merit. The power gain of the simplified model depicted in figure 2.3 can be calculated as follows [2.7, page 223]:

$$G_{P} = \left(\frac{f_{T}}{f}\right)^{2} \cdot \frac{1}{R_{in}} \cdot \frac{|Z_{ds}|^{2} \cdot |Z_{L}|}{|Z_{ds} + Z_{L}|^{2}},$$

(2.8)

where  $C_{gd}$  is set to zero. This simplifies the calculations and avoids stability problems by enforcing a unilateral device. In this equation  $Z_{ds}$  is the parallel impedance of  $R_{ds}$  and  $C_{ds}$  and  $Z_L$  is the load impedance, which is applied to the transistor. From the equation for the power gain, it can be concluded that:

- The cut-off frequency of the transistor should be as high as possible to obtain a high power gain,

- The power gain of the transistors is reduced when the frequency is increased. The consequences of this gain reduction and methods to compensate for it will be discussed in detail in chapter 5 and 6. In the remainder of this thesis this gain reduction as a function of frequency is indicated with the term gain roll-off.

Another figure of merit, which is at least as important as the cut-off frequency, is the maximum frequency of oscillation  $f_{MAX}$ . This maximum frequency of oscillation is defined by the frequency where the power gain of the transistor becomes equal to unity. The maximum frequency of oscillation can be calculated with the following equation:

$$f_{MAX} = f_T \cdot \sqrt{\frac{n_L}{(1 + n_L)^2}} \cdot \sqrt{\frac{R_{ds}}{R_{in}}}, \qquad (2.9)$$

with  $n_L$  being the ratio between the value of the drain-source resistance and the real part of the load impedance  $(R_{ds}/R_L)$ . In this equation, it is assumed that the parallel capacitor  $C_{ds}$  is resonated out at the frequency of interest with the help of a parallel inductor. The maximum power gain under small-signal conditions is then obtained when the real part of the load impedance is taken equal to the drain-source resistance  $(R_{ds})$  of the transistor  $(n_L = 1)$ . Under large-signal conditions this is no longer the case because the real part of the load impedance is dictated by the output power required  $(n_L > 1)$ , see section 5.4. Therefore, under large-signal conditions the power gain and  $f_{MAX}$  will be lower than under small-signal conditions.

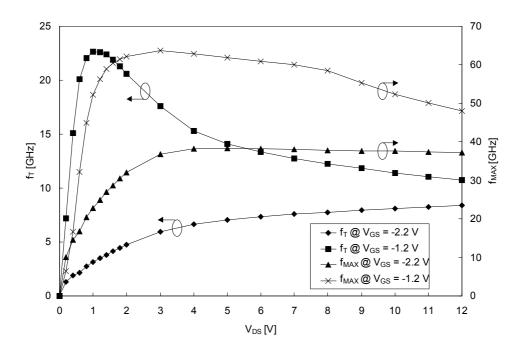

Equation (2.9) shows that the maximum frequency of oscillation is higher than the cut-off frequency. This is the case because in the saturated region  $R_{ds}$  is an order of magnitude larger than  $R_{in}$ . In practice,  $f_{MAX}/f_T$  is typically 1.5 to 2. The cut-off frequency and the maximum oscillation frequency of a MESFET, which has a total gate width of 1.5 mm and a gate length of 0.5  $\mu$ m, are depicted in figure 2.4. The cut-off frequency and the maximum

oscillation frequency are calculated with the help of the small-signal equivalent transistor model parameters.

Figure 2.4: Extracted  $f_T$  and  $f_{MAX}$  of a MESFET as a function of both the drain-source and gate-source voltages. The DIOM20HP transistor has a total gate width of 1.5 mm and a gate length of 0.5  $\mu$ m.

The results show that both  $f_T$  and  $f_{MAX}$  are bias dependent as already was concluded from equations (2.5) and (2.6). The cut-off frequency of the transistors discussed in this thesis (typical  $V_{DS} = 9$  V) is close to 12 GHz, which is also the high end of the desired frequency band. On the other hand, the maximum frequency of oscillation is much higher. Therefore, the transistors can still be used for the design of high-power amplifiers at X-band.

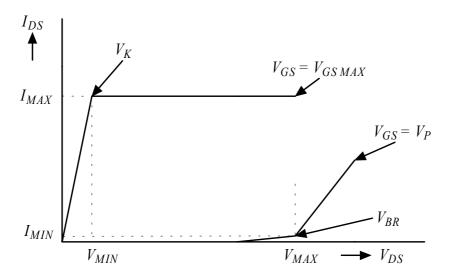

Important figures of merit of the used transistors are besides the gain, also the output power and power added efficiency. The idealised IV curves showing the factors that limit the output power are depicted in figure 2.5. The output power ( $P_{OUT}$ ) capability of the used transistor can be estimated with the help of the following equation:

$$P_{OUT} = \frac{(I_{MAX} - I_{MIN}) \cdot (V_{MAX} - V_{MIN})}{8}.$$

(2.10)

Figure 2.5: Idealised DC IV curves.

The following limiting factors for the output power are observed from the idealised DC IV curves. The maximum open channel current  $I_F$  limits the current swing, so  $I_{MAX} = I_F$ . For simplicity the minimum drain current  $I_{MIN}$  is considered to be zero. It is good to note that the maximum open channel current is considerably higher than  $I_{DSS}$ , which is some times used. According to [2.7] the maximum open channel current is given by:

$$I_F = q \cdot N_D \cdot Z_G \cdot v_{sat} \cdot (W - d_{min}). \tag{2.11}$$

From this equation, it can be seen that the maximum forward current  $I_F$  is determined by technology related parameters. These parameters are; the total gate width of the transistor  $Z_G$ , the doping density  $N_D$ , the saturation velocity  $v_{sat}$  of electrons in the n-doped GaAs, the channel thickness W and the minimum extension of the depletion region into the channel  $d_{min}$ , see also figure 2.1. In practice, a lower value has been used for the maximum current  $I_{MAX}$  because that current occurs at a gate-source voltage that is higher than the built-in potential of the Schottky diode. Consequently, a large gate current (> 10 mA per finger) starts to flow. This large gate current causes electron migration of the gate metal and results in a reduced reliability of the transistor. Therefore, the gate current per finger was limited for the used transistors to a maximum of 2 mA/finger, see also chapter 6. The resulting maximum drain current is found at a gate-source voltage that approximates the built-in potential of the Schottky diode ( $\approx 0.8 \text{ V}$ ).

The load impedances of the transistor should be chosen such that the voltage swing stays within the limits formed by the knee voltage  $V_K$  and the breakdown voltage  $V_{BR}$ . The knee voltage is determined by the value of the parasitic drain and source resistance, and the drain-source resistance in combination with the maximum current  $I_{MAX}$ . The knee voltage is given by the following equation:

$$V_K = (R_s + R_d + R_{ds}) \cdot I_{MAX} \,. \tag{2.12}$$

The voltage swing is limited for higher voltages by the breakdown voltage of the transistor. In equation (2.13) an expression is given for the breakdown voltage [2.7, page 169]:

$$V_{BR} = \frac{1}{2} \cdot \left( \frac{E_B \cdot L_G}{q \cdot N_D \cdot W} \cdot \left( \varepsilon_0 \cdot \varepsilon_r \cdot E_B - q \cdot N_D \cdot W \right) - \frac{q \cdot N_D \cdot W^2}{\varepsilon_0 \cdot \varepsilon_r} \right). \tag{2.13}$$

This simple expression shows the major influence of the material properties on the breakdown voltage. For instance when the doping density increases the breakdown voltage is reduced and the maximum drain current is increased. This kind of relation between the maximum drain current and the breakdown voltage is also observed for the technologies used in the discussed high-power amplifiers. Comparison of equation (2.11) and equation (2.13) shows that there exists a relation between the maximum drain current in the forward direction and the breakdown voltage. When the minimum voltage and current are assumed to be zero the following equation can be found for the output power:

$$P_{OUT} = \frac{1}{16} \cdot \left( \frac{E_B \cdot L_G}{q \cdot N_D \cdot W} \cdot \left( \varepsilon_0 \cdot \varepsilon_r \cdot E_B - q \cdot N_D \cdot W \right) - \frac{q \cdot N_D \cdot W^2}{\varepsilon_0 \cdot \varepsilon_r} \right) \cdot q \cdot N_D \cdot v_{sat} \cdot \left( W - d_{min} \right)$$

(2.14)

A logical choice for the drain voltage of a transistor would be the middle of the sum of the knee voltage and the breakdown voltage, see equation (2.15). Such a choice guarantees the maximum possible voltage swing without damaging the transistor,

$$V_{DS} = \left(\frac{V_K + V_{BR}}{2}\right). \tag{2.15}$$

Nevertheless this maximum drain voltage was not used for the high-power amplifier designs discussed in this thesis. The reason is the fact that the voltage, calculated with help of equation (2.15), is always higher than the drain voltage that was available from the system in which the amplifiers are used. For the power MESFETs discussed here, the drain to gate spacing is larger than the source to gate spacing. This is done to improve the breakdown voltage of the FET. The measured breakdown voltage under DC conditions is approximately 20 V. Note that the DC breakdown voltage for a MESFET or an HFET is not similar to the RF breakdown behaviour [2.8]. Under RF conditions, the carriers may not achieve sufficient energy to cause avalanche breakdown and therefore a higher breakdown voltage is obtained. For all discussed MESFET amplifiers a drain bias voltage of  $V_{DS} = 9 \text{ V}$  was used. Therefore, the breakdown voltage is not the limiting factor for the voltage swing but the knee voltage is. The knee voltage of the used MESFETs is 1.5 V, and the average measured drain current at  $V_{GS} = 0.8 \text{ V}$  is 365 mA/mm. These values suggest an output power

capability based on DC limits of 0.68 W/mm, output power density results measured under RF conditions will be discussed in chapter 5.

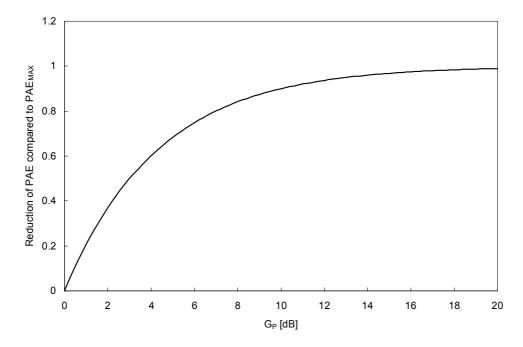

The last figures of merit, which need discussion, are the drain efficiency and the Power Added Efficiency (*PAE*) of the transistor. The drain efficiency is given by:

$$\eta_D = \frac{P_{OUT}}{P_{DC}} \,. \tag{2.16}$$

In this equation,  $P_{DC}$  is the dissipated DC power. A more relevant factor for describing the transistor efficiency is the power added efficiency (PAE), because the latter efficiency also considers the gain of the transistor. The power added efficiency is defined with the help of the following equation:

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}} = \frac{P_{OUT}}{P_{DC}} \cdot \left(1 - \frac{1}{G_P}\right). \tag{2.17}$$

This equation shows that the power added efficiency is directly related to the drain efficiency of the transistor and the power gain of the transistor.

Figure 2.6: Reduction of the PAE of a transistor compared to its maximum value  $(PAE_{MAX})$  as a function of the power gain.

In addition, it can be concluded that the power gain of the transistor ( $G_P$ ) should be as high as possible to obtain an as high as possible power added efficiency, see figure 2.6. In practice, a power gain below 10 dB is considered unacceptable in terms of power added efficiency reduction. The power gain of a single transistor has, in a multi-stage power amplifier, also influence on the overall power added efficiency of the amplifier. This influence is discussed in more detail in chapter 5.

Other relevant parameters that determine the transistor performance are the number of gate fingers and the width of these gate fingers. These parameters are discussed in more detail in chapter 5.

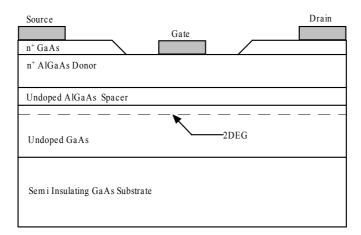

#### 2.3.3 Heterojunction Field Effect Transistor

For the design of advanced microwave power amplifiers, which can be used for the realisation of combined driver and high-power amplifiers, the HFET technology of FhG-IAF [2.9, 2.10] is used. A simplified cross section of a HFET is shown in figure 2.7. Note that in the literature many different names are encountered for the transistor type that is called HFET in this thesis, examples are High Electron Mobility Transistor (HEMT) and MOdulation Doped FET (MODFET).

Figure 2.7: Simplified cross section of a HFET.

The HFET technology used, has significant advantages over the MESFET technology presented in the previous section:

More power gain, 14 dB compared to 10 dB at 12 GHz, see chapter 5 for more details.

Due to this increased gain, there is less reduction of the power added efficiency and

fewer amplifier stages can be used to realise the combined driver and high-power

amplifier discussed in chapter 1.

More output power per gate width, values up to 0.9 W/mm have been measured at X-band compared to 0.7 W/mm for the MESFET technology, see chapter 5 for more details. Therefore, a higher output power can be realised at the same chip area with the HFET technology, as it will be demonstrated in chapter 7.

Above-mentioned factors make the realisation of a single chip high-power amplifier combined with a driver amplifier with the help of HFET technology possible.

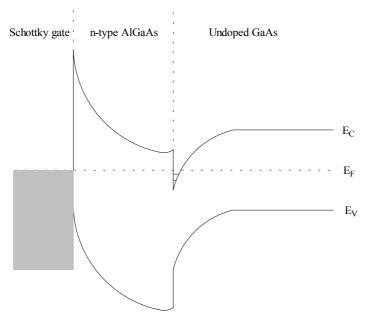

The HFET has, similar to the MESFET, three metal electrodes that respectively are called drain, source and gate. The contact to the active channel is made for the drain and the source with the help of an ohmic contact. The gate is realised with the help of a Schottky barrier. The better high frequency performance of a HFET when compared to a MESFET is due to the existence of a so-called two dimensional electron gas (2DEG). Figure 2.8 shows the energy-band diagram of an Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs heterojunction. Note that the bandgap is higher for Al<sub>x</sub>Ga<sub>1-x</sub>As compared to GaAs. This heterojunction is in thermal equilibrium when no external voltage is applied. The Al<sub>x</sub>Ga<sub>1-x</sub>As is doped n-type, while the GaAs is only lightly doped. To achieve thermal equilibrium electrons will flow from the wide-bandgap Al<sub>x</sub>Ga<sub>1-x</sub>As into the GaAs, forming an accumulation layer of electrons in the potential well adjacent to the interface. This accumulation layer is referred to as two-dimensional electron gas. The electrons have quantized energy levels in the plane perpendicular to the interface, in the other two directions the electrons are free to move. The 2DEG is an undoped region, therefore the electrons moving through this gas do not encounter ionised atoms, and therefore high electron mobility is obtained.

Figure 2.8: Energy band diagram HFET transistor, which is in thermodynamic equilibrium.

The available HFETs are of the depletion mode type. This means that current will flow through the active channel when no gate voltage is applied. The amount of current through the active channel can be controlled with the help of the voltage applied to the gate. Similar to the MESFET there exists a gate voltage denoted pinch-off voltage at which the current through the active channel is reduced to zero. In addition, current saturation will occur at higher drain-source voltages, due to the saturation of the electron velocity at higher field strengths. As in a MESFET, the current flow through a HFET can be controlled by applying a voltage between the gate and source of the transistor. However, in the case of a HFET, not the height of the active channel is varied, as it was the case for the MESFET but the electron density of the electron gas. When the undoped layer on top of the 2DEG is not sufficiently depleted, conduction through this layer will start to occur. The conduction through this layer is similar to the conduction in a MESFET. This so called parasitic MESFET has inferior transport characteristics when compared to the 2DEG and as a result the HFET performance is degraded as parasitic MESFET conduction starts to occur.

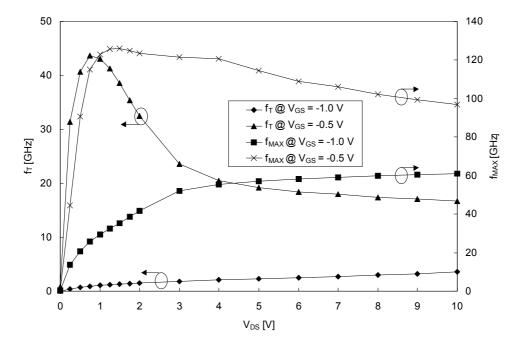

Figure 2.9: Extracted  $f_T$  and  $f_{MAX}$  of a HFET as a function of both the drain-source and gate-source voltages. The HFET has a total gate width of 1.44 mm and a gate length of 0.3  $\mu$ m.

The gate length of the HFETs used in this thesis is 0.3  $\mu$ m. An asymmetric source to gate and drain to gate spacing is used to improve the breakdown voltage. The gate-source spacing is 0.3  $\mu$ m and the drain-gate spacing is 0.9  $\mu$ m [2.10]. This large drain-gate spacing is used to improve the breakdown voltage of the HFET. The in this way realised breakdown voltage is > 20 V. For all HFET amplifiers a  $V_{DS} = 8$  V was used. The knee voltage of the

HFETs used is 1.25 V and the average measured drain current at  $V_{GS} = 0.8$  V is 526 mA/mm. The minimum drain current is assumed to be zero. These values suggest an output power capability based on DC limits of 0.89 W/mm, results measured under RF conditions will be discussed in chapter 5.

The cut-off frequency and the maximum frequency of oscillation of the HFET can be described with the same equivalent circuit that was used for the MESFET, see figure 2.3. The frequencies  $f_T$  and  $f_{MAX}$  extracted from measurements for a HFET with a total gate width of 1.44 mm and a gate length of 0.3  $\mu$ m are depicted in figure 2.9. The results show a similar bias dependency of the cut-off frequency and maximum oscillation frequency, as it was the case for the used MESFET. The absolute values, however, are significantly higher than was the case for the MESFET. This is quite logical taking into account the smaller gate length of the HFET of 0.3  $\mu$ m compared to the 0.5  $\mu$ m gate length of the MESFETs.

The layout of actual power transistors, which connects more than one gate finger in parallel, is more complex than is shown in this section. The layouts of the transistors used for the high-power amplifier design are discussed in the next section.

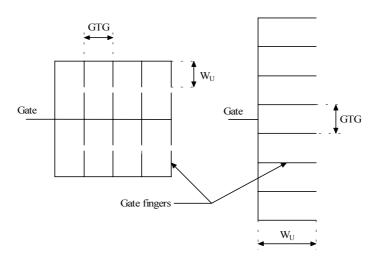

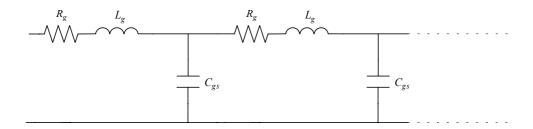

#### 2.3.4 Transistor Layout

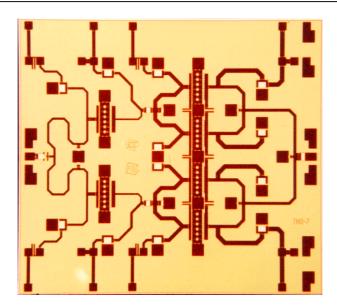

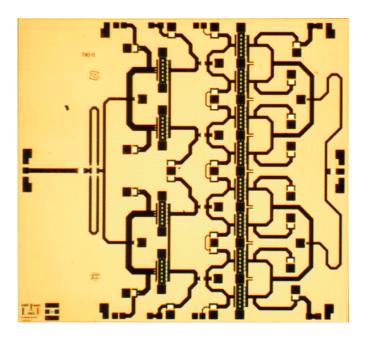

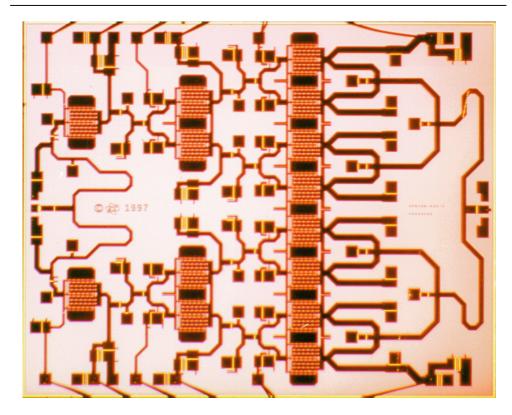

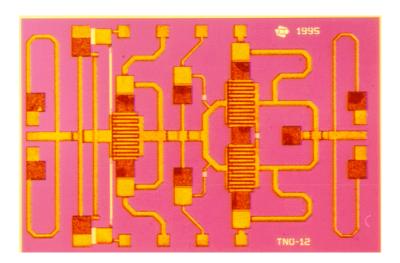

To form a power transistor several gate fingers have to be connected in parallel because the width of the gate finger should not be increased beyond 125  $\mu$ m for X-band transistors. Above this width, the gain of a transistor becomes unacceptably low. This gain reduction is discussed in more detail in chapter 5. Consequently, more gate fingers have to be connected in parallel to increase the output power of a transistor. The way these gate fingers can be connected in parallel is independent of the transistor type used, i.e. MESFET or HFET, or the foundry used. In fact, the transistor layout is an extra design freedom, which should be considered carefully. The transistor layouts used in the high-power amplifiers described in this thesis are shown in figure 2.10.

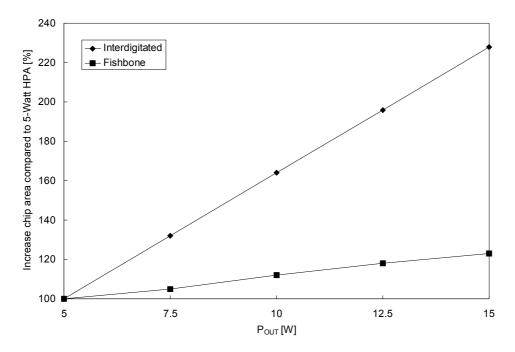

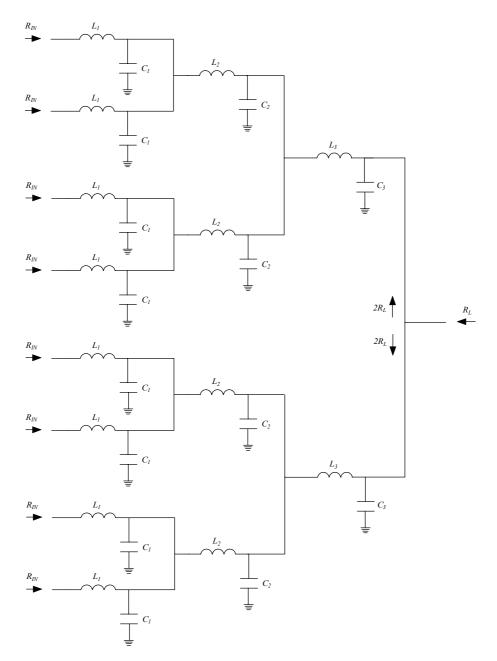

It turned out that the fishbone transistor layout gives the highest output power per chip area [2.11]. This is the case because for a large total gate width the fishbone layout results in a squarer layout of the transistor. In a high-power amplifier, a number of transistors must be used in parallel, as it will be discussed in chapter 5, to realise a required amount of output power. When more output power is required, the number of gate fingers in parallel must be increased. In the case of the interdigitated transistor, this will increase the height of the occupied chip area. Consequently, also the height of all matching networks is unnecessarily increased. This is not the case for the fishbone transistor layout where only the width of the bar of transistors that are placed parallel is increased. The width and height of the matching networks, see chapter 6, can stay at their minimal dimensions. The fishbone transistor has the additional advantage of higher gain. This is because more gate fingers with a smaller width are put in parallel than is the case for an interdigitated transistor of the same overall gate width. This is discussed along with the thermal details in much more detail in chapter 5.

Figure 2.10: Simplified schematic of gate finger connections for a 16 finger fishbone (left) and an 8 finger interdigitated (right) transistor layout. The indicated important parameters are the gate-to-gate spacing (GTG) and the unit gate width of one finger  $(W_U)$ .

Figure 2.11: Example of the increase in occupied chip area [2.11], when compared to a 5-Watt amplifier, as a function of the required output power.

An example of the chip area increase when going to a higher output power is depicted in figure 2.11. These results clearly show that transistors with a fishbone layout result in a smaller increase in occupied chip area than interdigitated transistor layouts.

Additional layout related factors that limit the performance of a transistor are:

- The minimum width of the gate, drain and source strips which is limited by the maximum current that is allowed to flow through a given microstrip line width.

- The maximum allowable channel temperature limits the spacing between the gate fingers. This is discussed in detail in section 5.3.5.

#### 2.4 Passive components

#### 2.4.1 Microstrip line

The interconnections between the different components can be realised with the help of various types of transmission lines. In figure 2.12, an overview is shown of the most commonly used transmission lines on a MMIC.

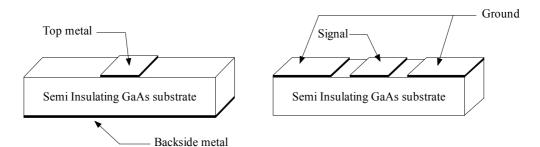

Figure 2.12: Overview of commonly encountered types of transmission lines on GaAs. The microstrip line is depicted left and the coplanar transmission line is depicted right.

Coplanar lines need fewer processing steps than microstrip lines due to the absence of wafer thinning, viahole etching, filling viahole with metal, and metallisation of the complete backside of the chip, which is necessary for a microstrip design. Therefore, a technology based on coplanar lines is potentially cheaper than one based on microstrip lines. At the start (1992) of the high-power amplifier design work, coplanar lines had the following disadvantages when compared to microstrip lines [2.12]:

Hardly any electrical models for coplanar transmission lines and discontinuities were available.

• Coplanar waveguide supports multiple modes, some of which may be excited at discontinuities. This increases the design risk.

- Coplanar structures are realised on thick substrates, typically  $>500 \mu m$ ; therefore, heat transfer becomes a problem for high-power amplifier designs, see also chapter 5.

- Coplanar lines exhibit somewhat higher losses than microstrip lines. A 1 mm long transmission line with a characteristic impedance of 50  $\Omega$ , a metal thickness of 5  $\mu$ m, and a centre conductor width of 68  $\mu$ m gives a loss of 0.054 dB for the microstrip line case and 0.066 dB for the coplanar line case [2.15].

Therefore, microstrip lines were chosen as transmission lines. In the for this work available MESFET process of Infineon and HFET process of FhG-IAF the microstrip lines are realised on  $100~\mu m$  thick GaAs substrates. The reasons for this thickness are:

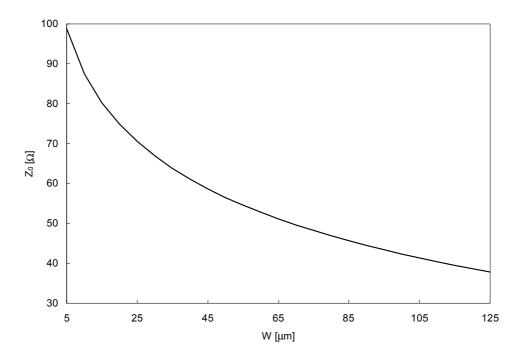

- The range of microstrip line impedances that can be realised with the help of small line widths,  $10-100~\mu m$ , is larger than is the case with thick wafers. Therefore, more compact MMICs can be realised. The microstrip line impedances depicted in figure 2.13 show that an impedance between 40 and 100  $\Omega$  can be realised on 100  $\mu m$  thick GaAs wafers.

- Lower inductance of the viahole to ground. This results for instance in a higher gain of

the transistors because there is less frequency dependent feedback caused by the

viaholes.

- The thermal properties are better.

The connection to ground is realised with the help of viaholes, see section 2.4.6.

Many of the disadvantages of the usage of coplanar lines mentioned before, have been resolved nowadays [2.13]. Cost savings up to 40% have been reported for a coplanar flip-chip high-power amplifier at X-band [2.14]. The heat is removed for the before mentioned high-power amplifier through the utilisation of thermal bumps at the sources of the used PHEMTs. Therefore in the future, coplanar transmission lines should be seriously reconsidered for high-power amplifier design. Nevertheless for the amplifiers discussed in this thesis only microstrip elements have been used.

The transmission line impedances, shown in figure 2.13, are calculated with the help of Linecalc [2.15]. The impedance levels are limited at the high end by the smallest line width that can be processed and at the low end by the occupied chip area, in practice line widths between 10 and 120  $\mu m$  are used.

The maximum current that can flow through a cross section of a microstrip line limits the use of microstrip lines, for high-power amplifier design. This is especially important for the microstrip lines that are used to supply the bias currents to the transistors. The amount of current that is allowed to flow, is for a given microstrip line width, determined by the thickness of the microstrip line metal. The metal thickness of the microstrip lines varies between 3 and 5  $\mu m$  for the used technologies. This results in current density per microstrip line width of 20 mA/ $\mu m$  for the lines directly on the GaAs and a value of 15 mA/ $\mu m$  for the airbridges.

Figure 2.13: Calculated characteristic microstrip line impedance as a function of the line width for a 100  $\mu$ m thick GaAs wafer [2.15]. The metal thickness of the microstrip line is 5  $\mu$ m.

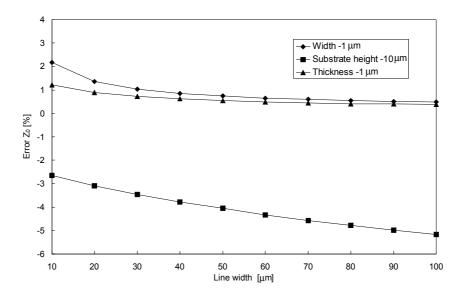

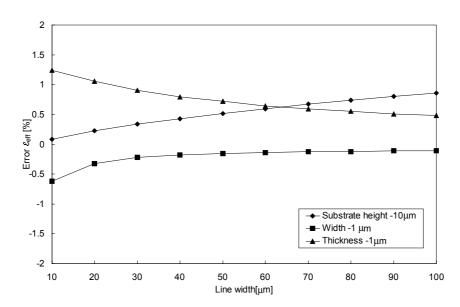

The characteristic impedance of the microstrip lines is influenced by process variations. The major process variations are:

- Variation of the thickness of the substrate. The GaAs substrates used have a nominal thickness of 100  $\mu$ m. For the variation of this thickness a value of  $\pm$  10  $\mu$ m is quoted.

- Variation of the line width. For the variation of the line width a value smaller than  $\pm$  1  $\mu$ m is assumed.

- Variation of the thickness of the line metal. For this, a maximum variation of  $\pm$  1  $\mu m$  is quoted.

These factors lead, besides variations in the characteristic impedance of the lines, also to variations of the effective dielectric constant of the transmission line. The results depicted in figures 2.14 and 2.15 show that the influence of process variations on the characteristic impedance of the line is considerably higher than the influence on the effective dielectric constant. In addition, it is show that for the relevant line widths (> 30  $\mu m$ ) the major influence on the characteristic impedance of the line is the substrate height. The error in the predicted impedance increases when the line width is increased. For a line width of 100  $\mu m$ , the maximum variation in the characteristic impedance is  $\pm$  6%. The maximum variation in the dielectric constant is  $\pm$  1.5%.

Figure 2.14: Influence of process variations on the characteristic impedance ( $Z_0$ ) transmission line, values are calculated at 10 GHz and a substrate thickness of 100  $\mu$ m and a metal thickness of 3  $\mu$ m.

Figure 2.15: Influence of process variations on the effective dielectric constant ( $\epsilon_{\rm eff}$ ) transmission line, values are calculated at 10 GHz and a substrate thickness of 100  $\mu$ m and a metal thickness of 3  $\mu$ m.

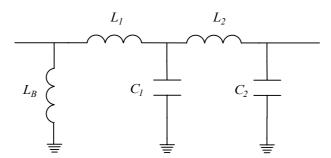

## 2.4.2 Microstrip discontinuities

Microstrip circuits generally require structures like bends, T-junctions, crosses etc., to form matching networks. These junctions result in discontinuities, which no longer can be ignored at X-band frequencies, and therefore accurate models are needed, see chapter 4. The use of the before mentioned junctions is limited by the maximum current that will flow through a given cross section as it is the case for the microstrip lines discussed in the previous section. In addition, the discontinuities are influenced by the same processing variations as the microstrip lines. For the discontinuities, equivalent circuit models mainly consisting of series inductors and parallel capacitors are used. These models will be discussed in detail in chapter 4. The parallel capacitors are mainly influenced by variations of the GaAs substrate. Therefore, a maximum variation of  $\pm$  10% can be expected for the parallel capacitor. The series inductors are influenced by variations in the characteristic impedance and the dielectric constant of the discontinuity, see section 4.3.4. For the series inductors, a maximum variation of  $\pm$  7% is expected.

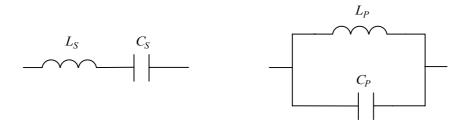

#### 2.4.3 Inductor

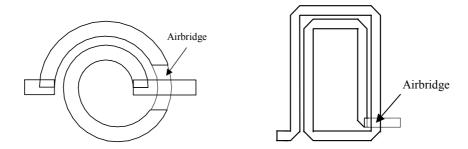

Inductors are available for application in MMICs. For low power MMICs most of the time spiral or square inductors are used, see figure 2.16.

Figure 2.16: Two possible layouts of inductors realisable on a MMIC.

Inductors are used in matching networks and for DC bias de-coupling. The application of spiral or square inductors in high-power amplifiers is problematic due to the high currents that will flow through relative small microstrip line widths. Inductors have line widths up to  $15~\mu m$ . Consequently the inductors can breakdown under high-power conditions. Therefore, only inductors that are realised with the help of microstrip lines have been used. The use of microstrip lines as inductor with the corresponding model is discussed in section 4.3.4.

The influence of process variations of inductors realised with the help of a microstrip line is the same as was quoted for the microstrip discontinuities discussed in the previous section.

## 2.4.4 Capacitor

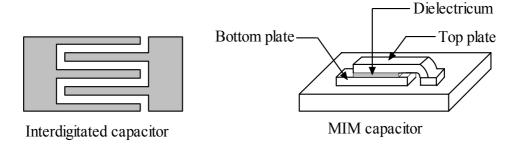

The availability of capacitors is crucial for the realisation of matching networks and DC decoupling networks. A capacitor can for instance be realised with the help of a parallel stub that is left open. Disadvantages of this method are the fact that only small capacitors can be realised in this way, only parallel capacitors can be realised and DC blocking is not possible. Therefore, this kind of capacitor is not used in the discussed high-power amplifier designs. There are two possibilities to realise lumped capacitors namely Metal Insulator Metal (MIM) capacitors and interdigitated capacitors. A picture of both types of capacitors is shown in figure 2.17.

Figure 2.17: Examples of possible layouts of an interdigitated (left) and a MIM capacitor (right).

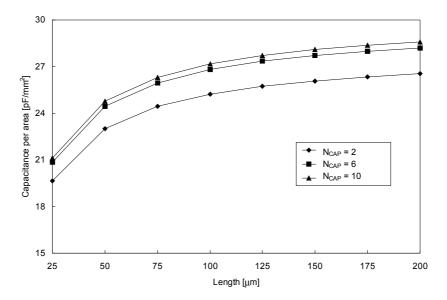

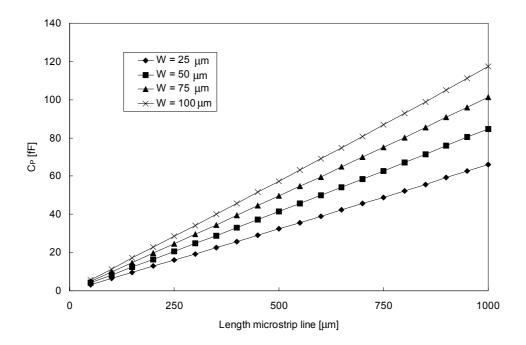

The interdigitated capacitor is based on the coupling between narrow microstrip lines. With the help of this type of capacitor, only small capacitance values can be realised [2.16]. Due to the low capacitance per area, as shown in figure 2.18, only capacitors < 0.5 pF can be realised. Therefore, this type of capacitor was not used in the discussed high-power amplifier designs. Recently an alternative planar capacitor based on a fractal has been described [2.17] which makes it possible to realise larger capacitance values per area than was possible until now.

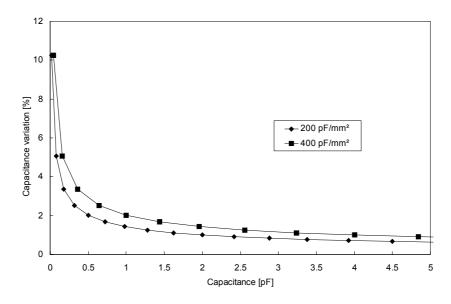

The capacitor type that is used for the discussed high-power amplifier designs is the MIM capacitor. This capacitor is formed with two metal plates on top of each other with a dielectric in between. This dielectric is also often used as a passivation layer to protect the MMIC. To be able to realise high capacitance values it is important to use an as thin as possible dielectric with a high permittivity. As dielectric often, Silicon Nitride ( $\mathrm{Si}_3\mathrm{N}_4$ ) or Silicon Oxide ( $\mathrm{SiO}_x$ ) is used. Typical values for the capacitance per area vary between 200 and 400 pF/mm². These values are considerably higher than the values shown in figure 2.18 for the interdigitated capacitors. In practice, capacitor values up to 5 pF have been realised for the discussed amplifier designs. Larger capacitance values would result in an unacceptable large occupied chip area.

Figure 2.18: Calculated capacitor value per area of an interdigitated capacitor as a function of the number fingers ( $N_{CAP}$ ) and the length of these fingers [2.16]. The width of each finger is 2  $\mu$ m and the spacing between the fingers is 2  $\mu$ m. The thickness of the metal is 0.8  $\mu$ m.

Figure 2.19: Capacitance variation as a function of the required MIM capacitance value for various capacitance values per area. For this calculation a square capacitor layout and a mask accuracy of  $\pm 0.5~\mu m$  is assumed.

The use of the MIM capacitors is limited by the breakdown behaviour of the dielectric layer. The maximum voltage, that means the sum of both DC and RF voltage, which can be applied to a capacitor is determined through the thickness of the dielectric layer times the electric breakdown field of the dielectric layer. Due to this limitation capacitors in series have sometimes been used in the output-matching network, see chapter 6 for more details.

The major processing related factors that influence the capacitance value per area are the height of the dielectric layer and the dielectric constant of this layer. A maximum variation between  $\pm$  10 – 15% is quoted for the capacitance per area. The value of a MIM capacitor is also influenced by the accuracy of the mask, which is used for the definition of the top plate of the capacitor. In figure 2.19, the influence of a variation of  $\pm$  0.5  $\mu$ m in the dimensions of the top plate of the capacitor is shown as a function of the required capacitor value. The results show that the accuracy decreases rapidly for capacitor values smaller than 0.4 pF. Therefore, only MIM capacitor values larger than 0.4 pF have been used in the amplifier designs discussed.

#### 2.4.5 Resistor

Resistors are used in the discussed power-amplifier designs in the stability improving networks and the slope compensation networks. The resistor is also used for control of the bias currents to improve the reliability of the transistors and to de-couple the influence of the bias circuit from the RF matching networks.

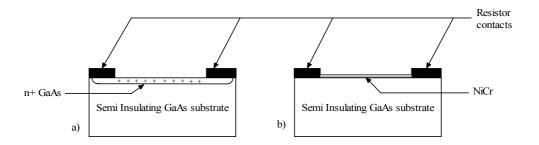

They can be implemented as implanted GaAs resistors or as deposited NiCr resistors. A cross section of both types of resistors is shown in figure 2.20.

Figure 2.20: Cross-section of a) an implanted GaAs and b) a NiCr resistor.

The usage of the NiCr resistors is limited by the maximum current that is allowed to flow through the resistor before electron-migration in the resistor metal begins to occur. The maximum current, which can flow through a given NiCr resistor width, is in the order of 0.4 mA/ $\mu$ m. The usage of the implanted resistors is limited by the electrical field strength where

the resistor becomes non-linear. This non-linear behaviour is caused by the saturation of the velocity of the electrons for a given electrical field strength. Consequently, the current will not further increase when the applied voltage is increased and the resistor stops acting as a linear resistor.

For the NiCr resistors an accuracy between  $\pm$  10 – 15% is quoted and for the GaAs resistors between  $\pm$  10 – 40%. The accuracy of the GaAs resistors is considerably lower than for NiCr resistors. Therefore, GaAs resistors have only been used when their absolute value is not critical, e.g. the 1 k $\Omega$  stabilisation resistors discussed in section 5.7.2. In the matching networks, only NiCr resistors have been used.

#### 2.4.6 Viahole

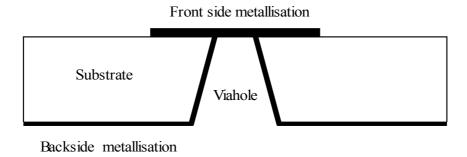

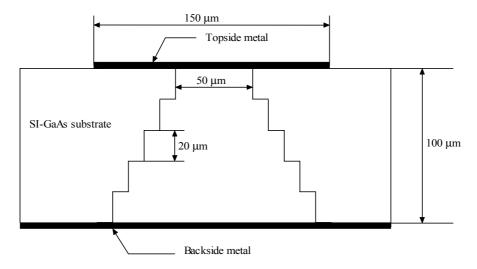

Viaholes are used to make electrical ground contacts for the electrical components used in the MMIC. This is of vital importance for the active devices used in a high-power amplifier because reduced inductance to ground will result in improved output power and gain. The viaholes used in conjunction with the active devices also act as thermal short circuits to the ground plane and as such reduce the temperature of the active devices. A viahole is etched through the substrate to the ground plane with its sidewalls covered with gold, see figure 2.21.

The use of viaholes is limited by the maximum current that is allowed to flow before electron migration starts to occur. For the used viahole, a value of several amperes is allowable and there is therefore no problem applying the viaholes in a high-power amplifier.

Figure 2.21: Cross section of a viahole.

The viahole can be modelled with the help of series inductors and a parallel inductor to ground, see section 4.3.7. The value of these inductors is mainly influenced by variation of the thickness of the GaAs substrate. Therefore, the parallel inductor to ground has a maximum variation of  $\pm$  10% and the series inductors of  $\pm$  7%.

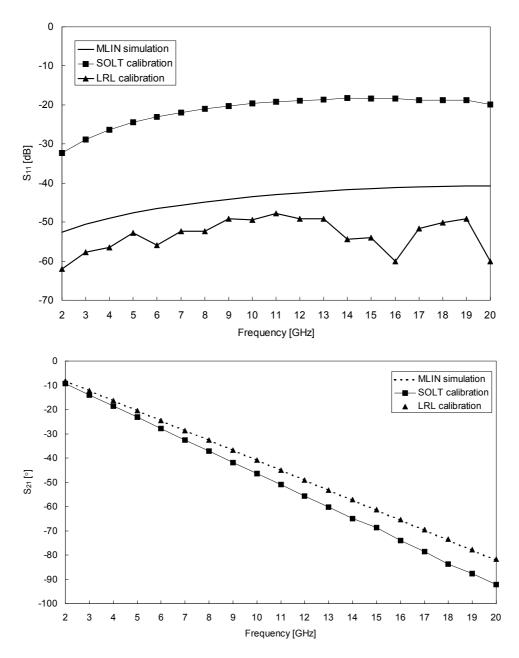

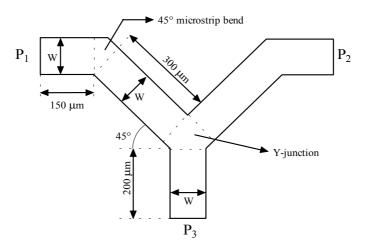

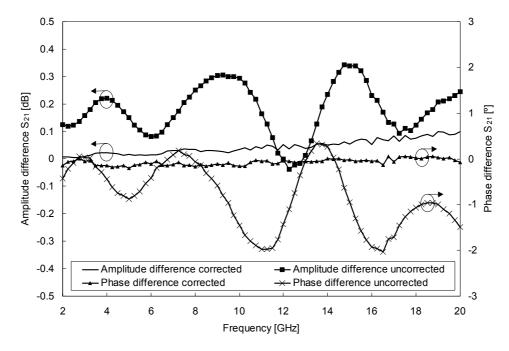

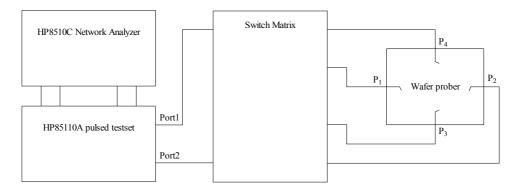

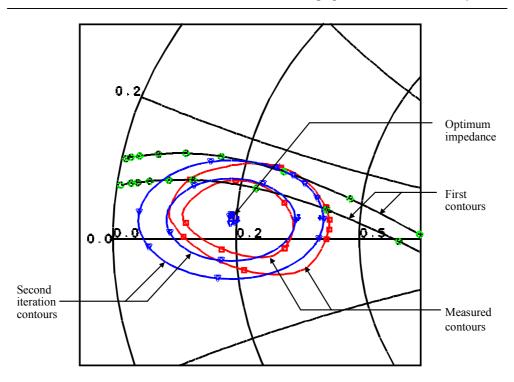

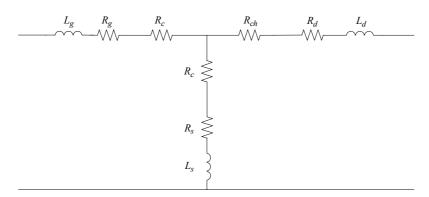

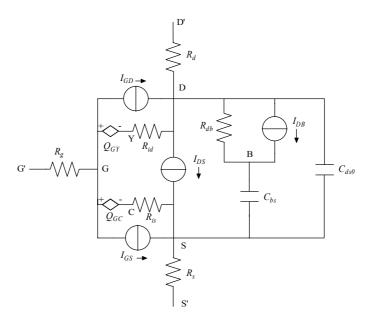

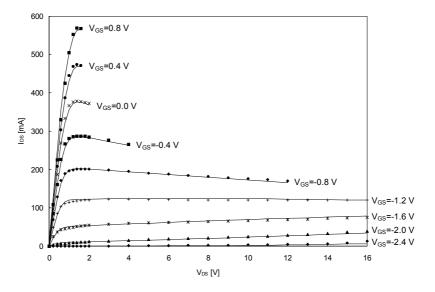

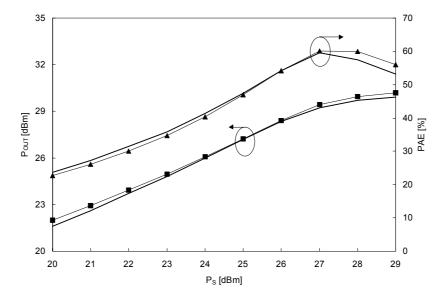

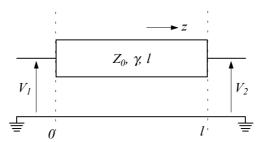

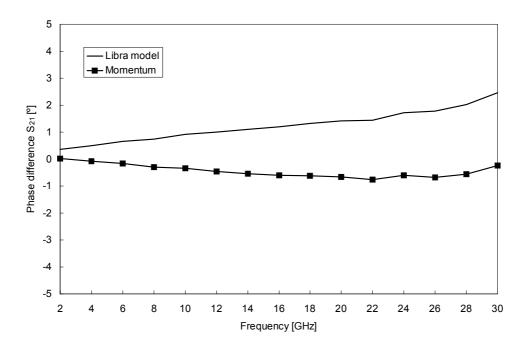

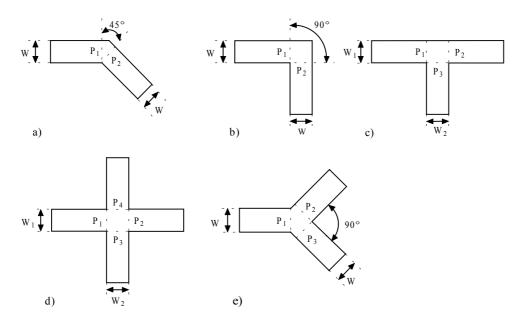

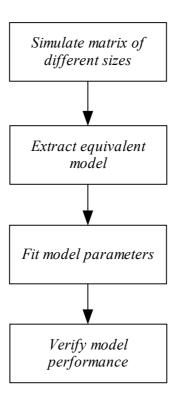

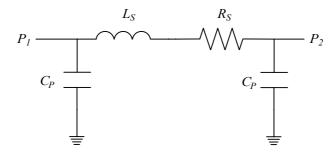

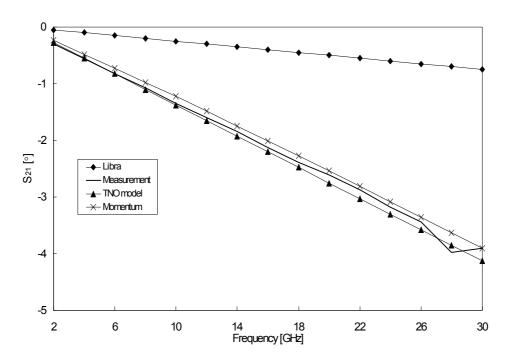

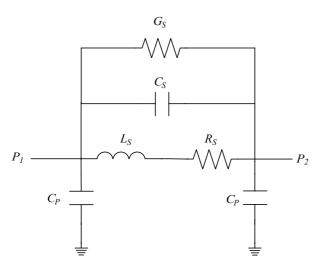

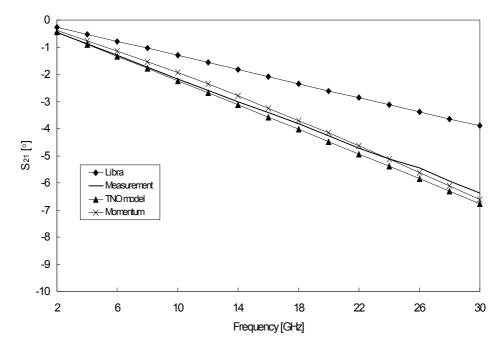

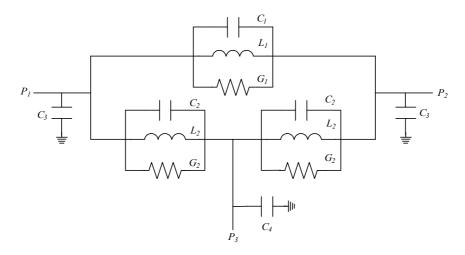

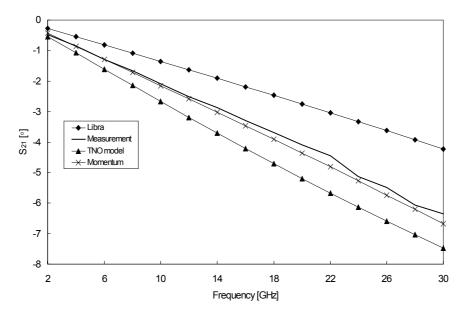

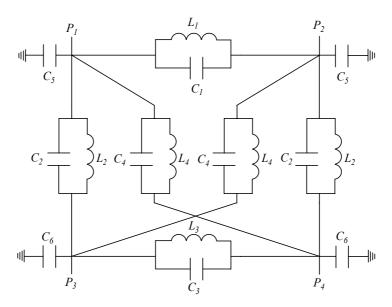

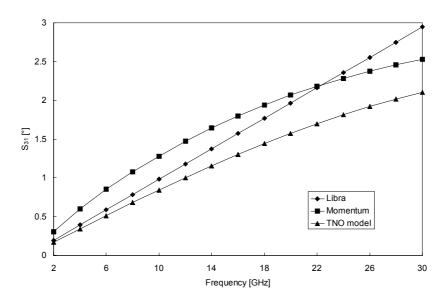

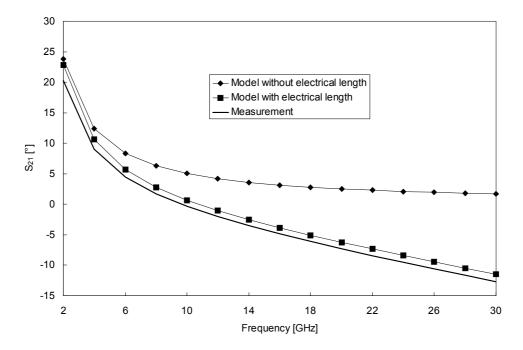

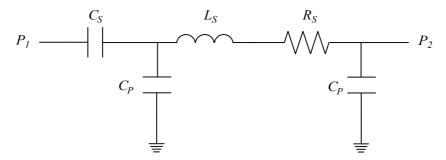

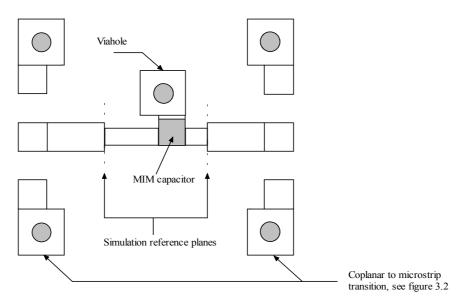

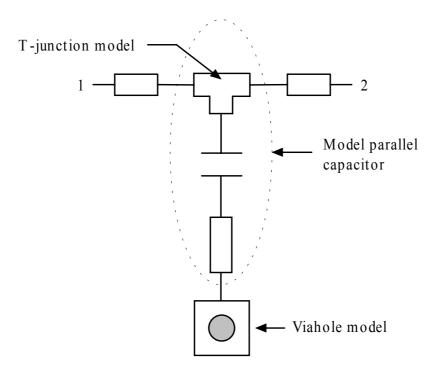

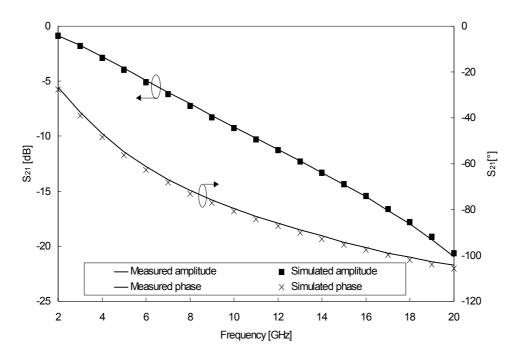

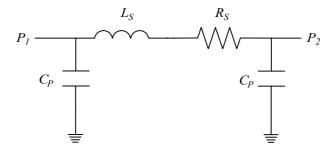

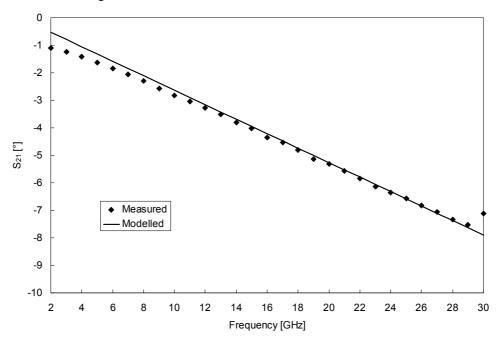

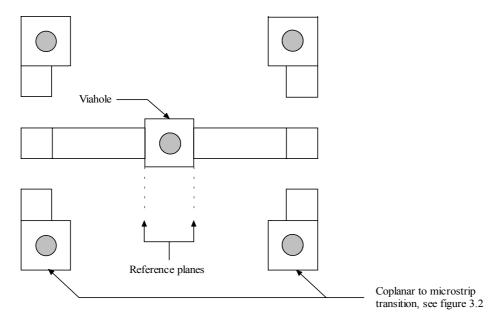

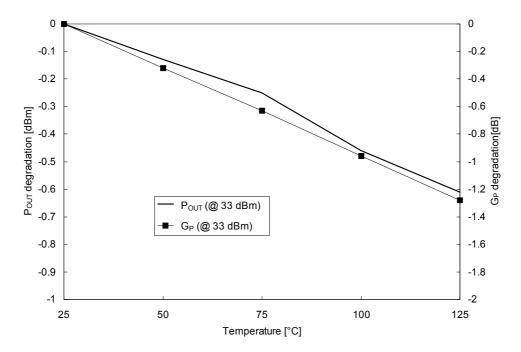

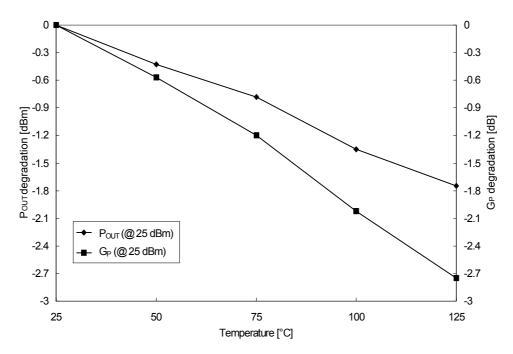

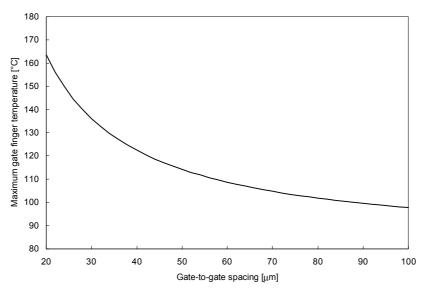

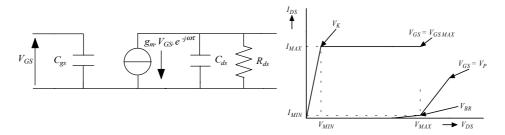

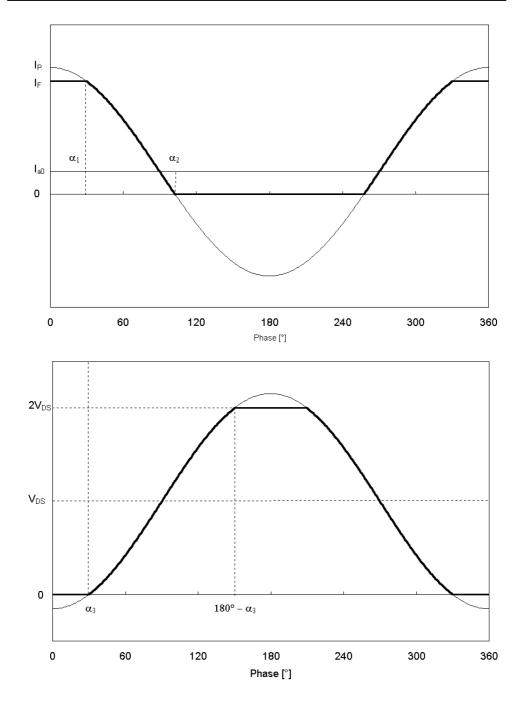

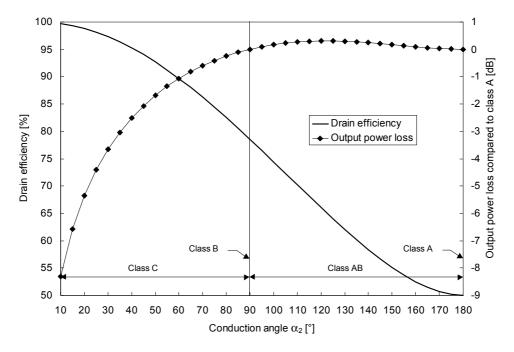

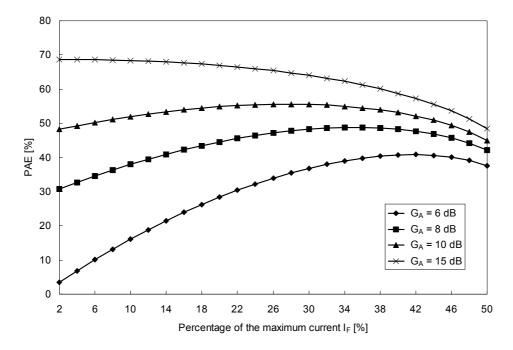

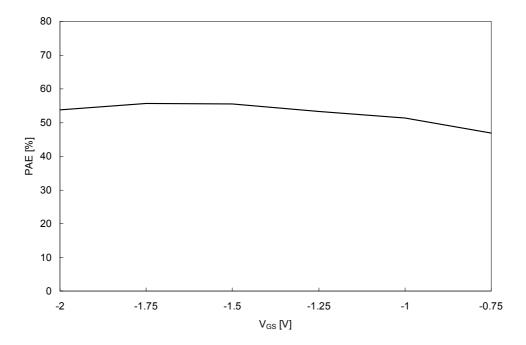

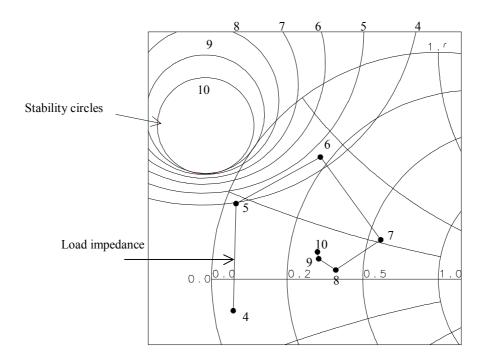

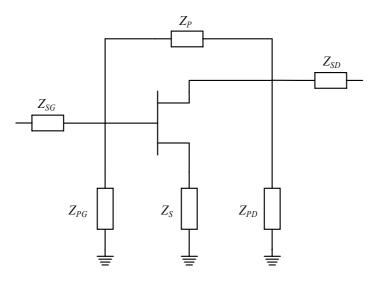

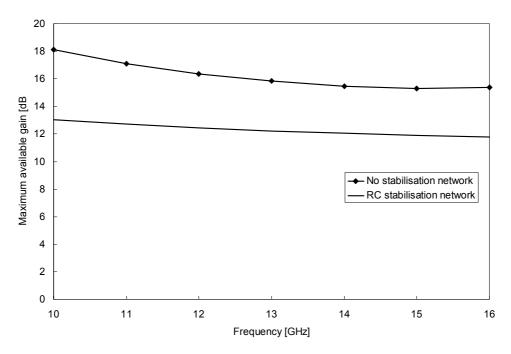

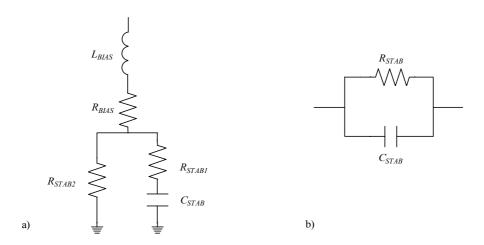

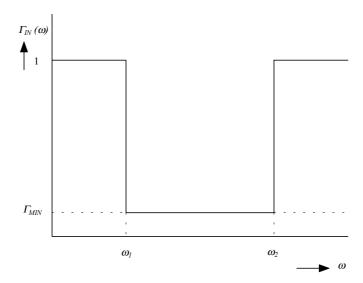

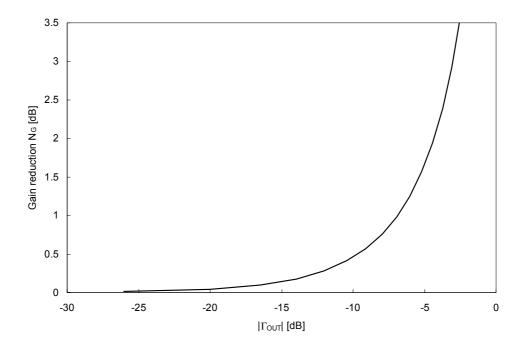

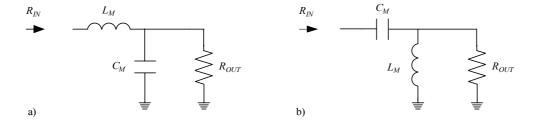

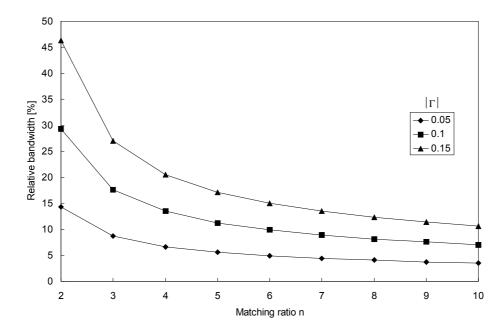

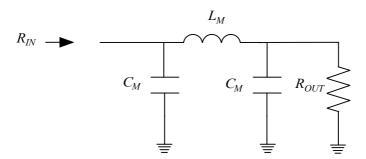

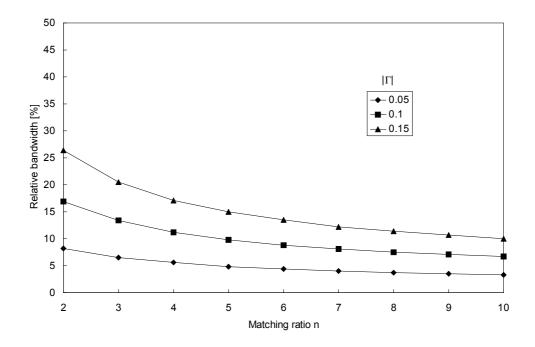

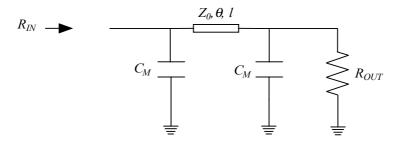

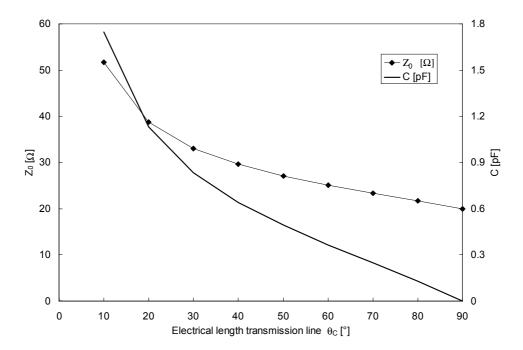

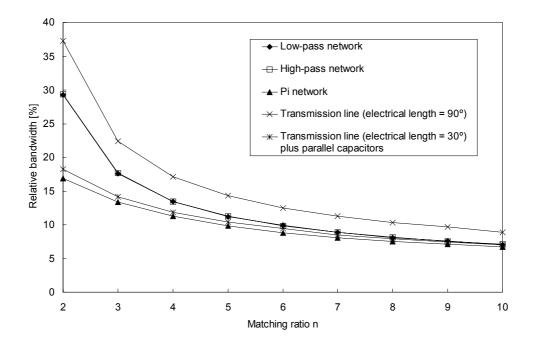

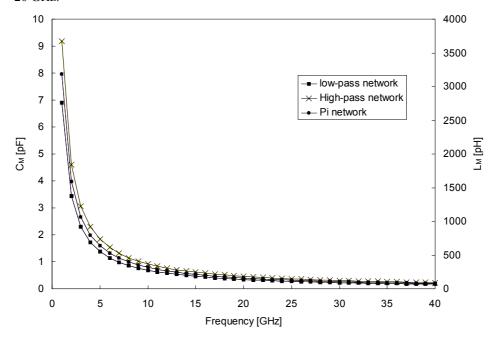

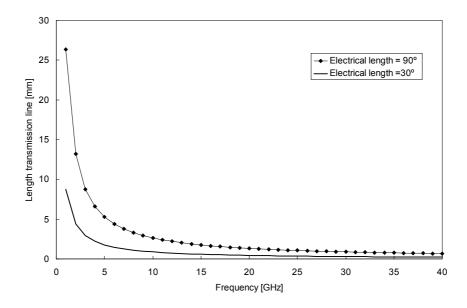

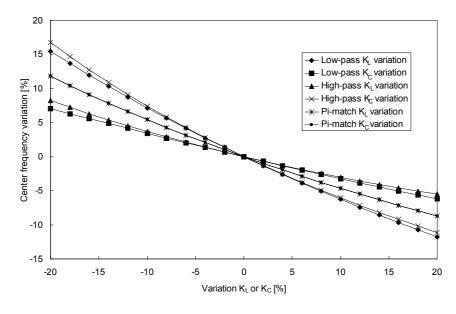

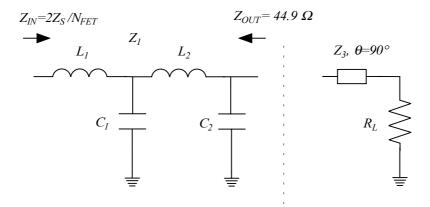

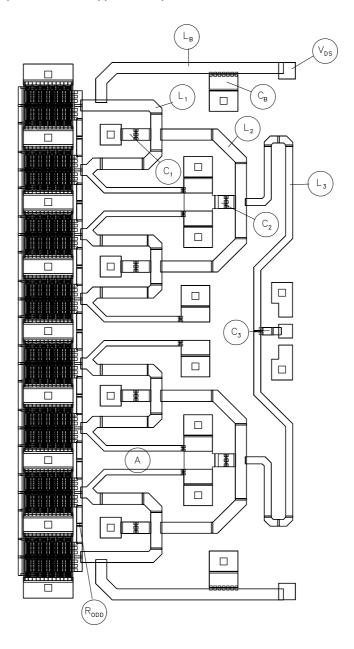

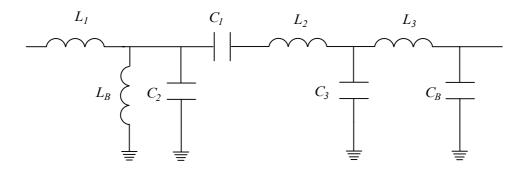

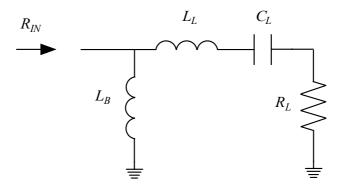

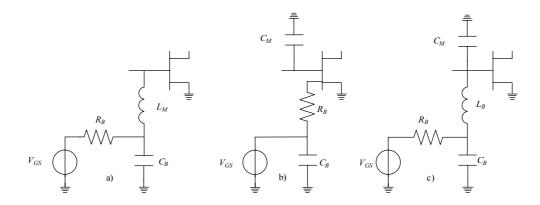

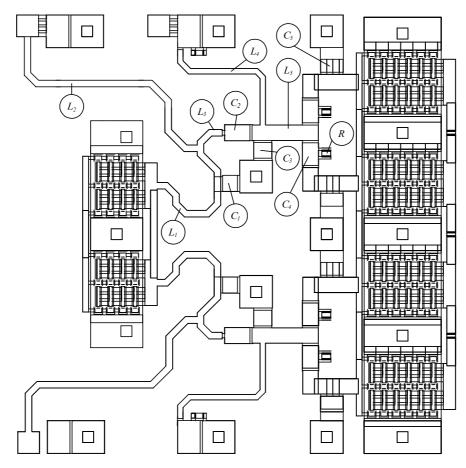

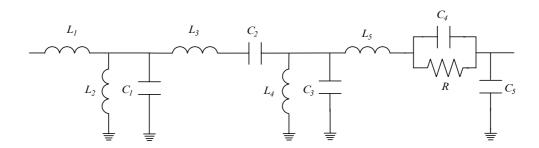

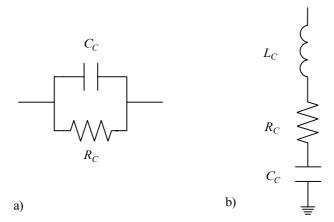

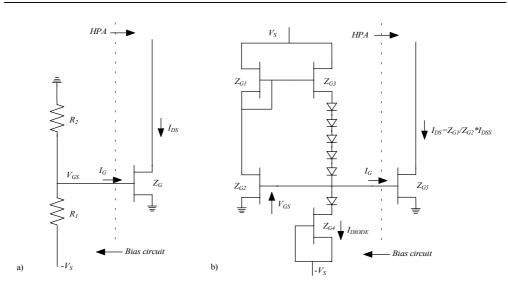

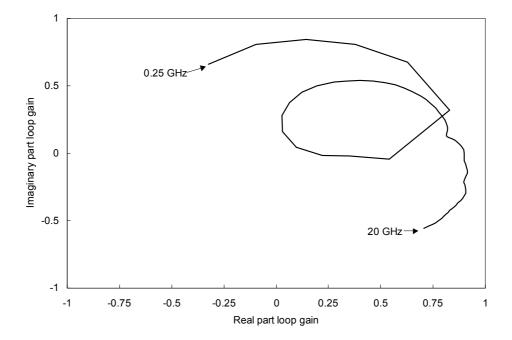

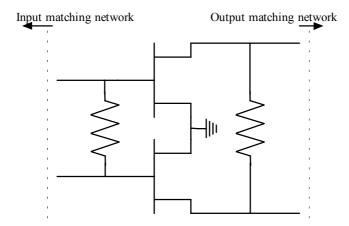

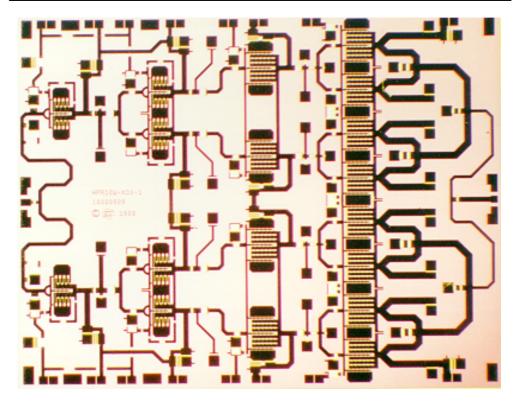

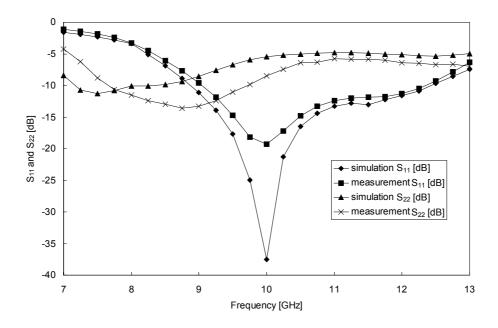

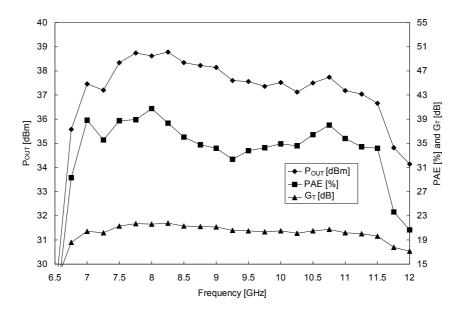

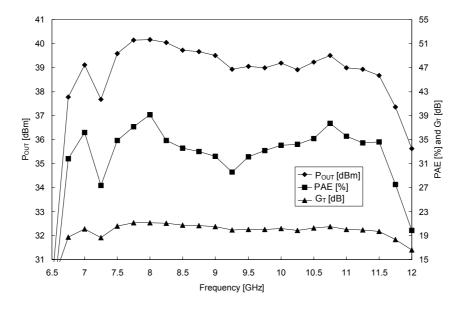

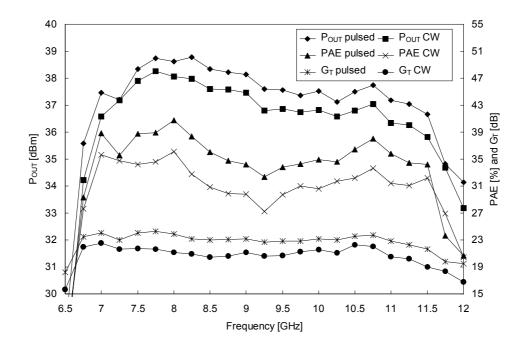

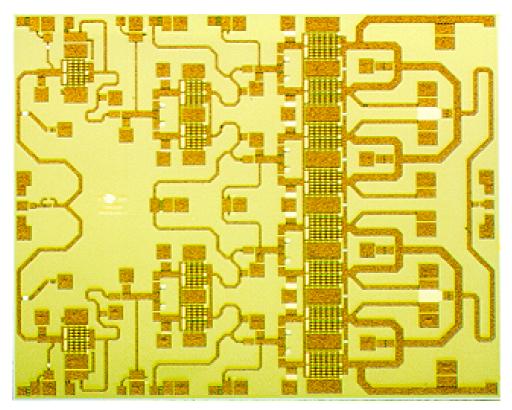

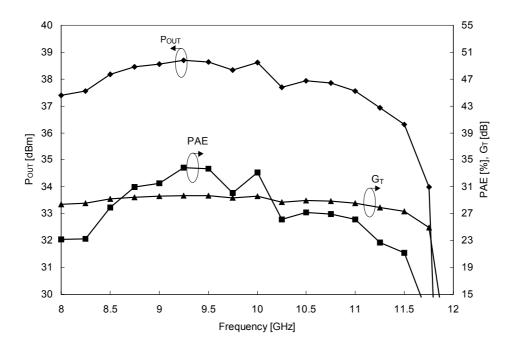

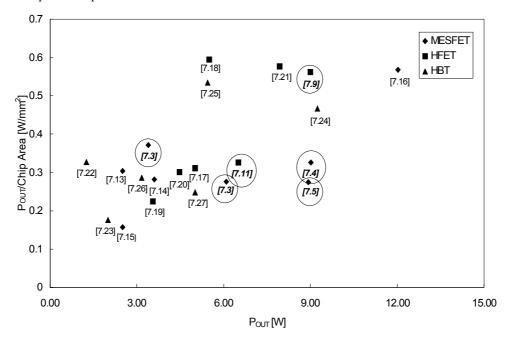

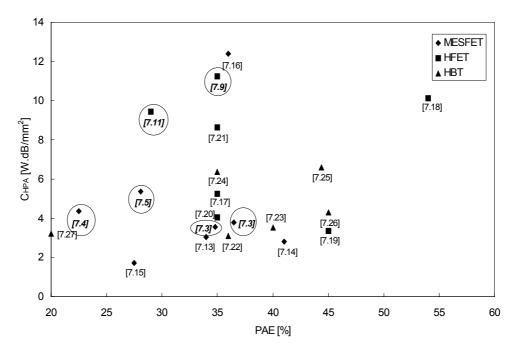

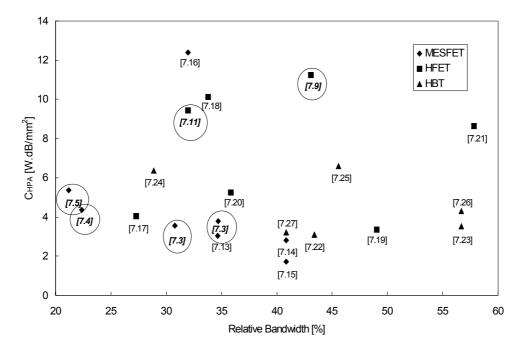

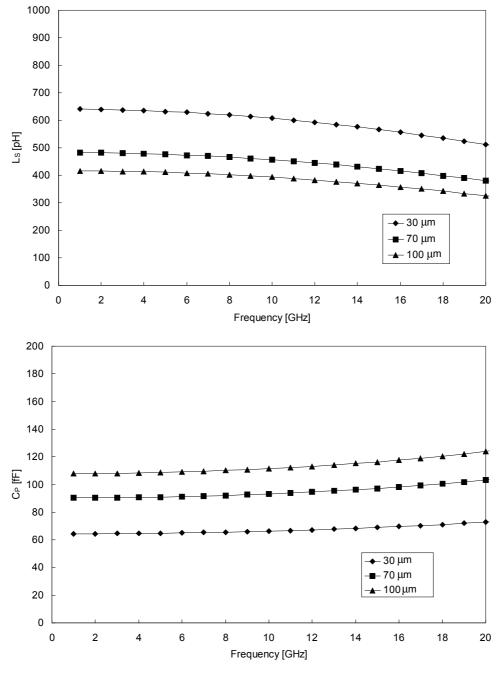

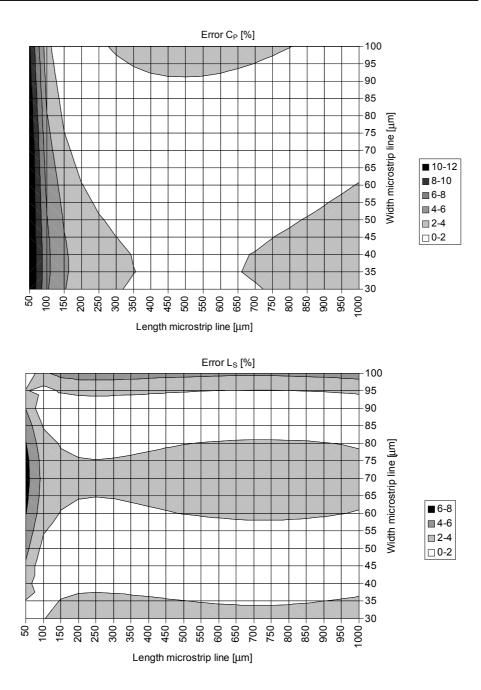

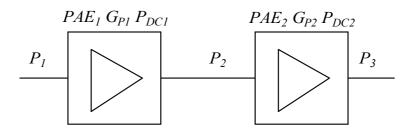

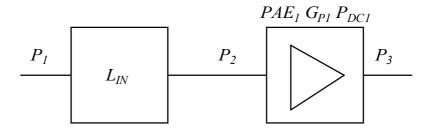

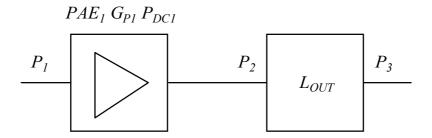

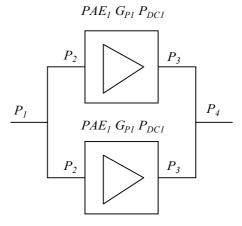

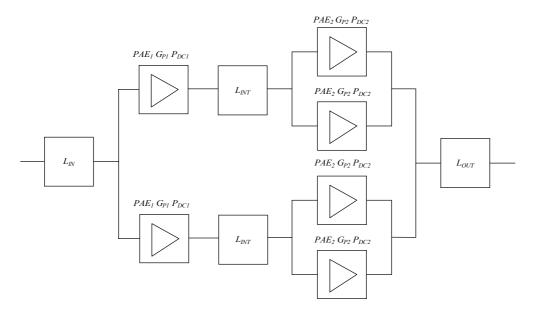

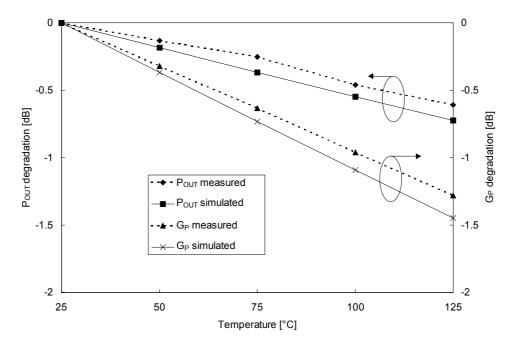

### 2.5 Conclusions