# Two and three terminal double barrier resonant tunneling devices

# Citation for published version (APA):

Lepsa, M. I. (1997). *Two and three terminal double barrier resonant tunneling devices*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR500621

DOI: 10.6100/IR500621

### Document status and date:

Published: 01/01/1997

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Two and Three Terminal Double Barrier Resonant Tunneling Devices

M.I. Lepsa

# Two and Three Terminal Double Barrier Resonant Tunneling Devices

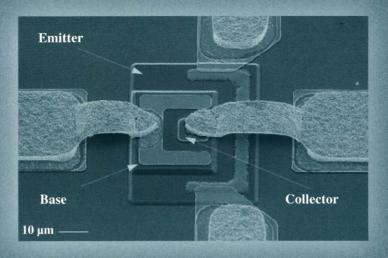

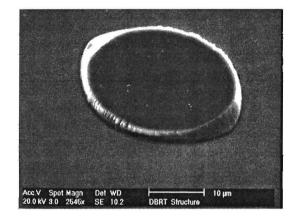

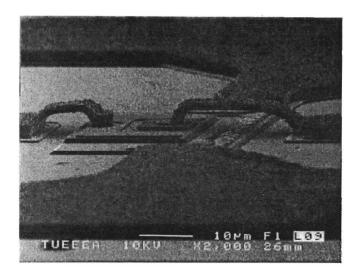

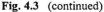

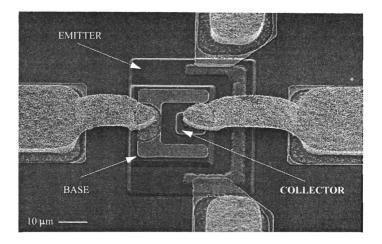

Front cover: SEM picture of a three terminal double barrier tunneling device.

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Lepsa, Mihail Ion

Two and three terminal double barrier resonant tunneling devices / by Mihail Ion Lepsa. -Eindhoven: Technische Universiteit Eindhoven, 1997. Proefschrift. - ISBN 90 - 386 - 0390 - 8 NUGI 832 Trefw.: halfgeleiders; tunneleffect / halfgeleidertechnologie / microgolfmetingen. Subject headings: resonant tunnelling devices / semiconductor technology / microwave measurement.

druk: Universiteitsdrukkerij

# Two and Three Terminal Double Barrier Resonant Tunneling Devices

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 12 november 1997 om 16.00 uur

door

# **Mihail Ion Lepsa**

geboren te Brasov, Roemenië

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.-Ing. L.M.F. Kaufmann en prof.dr. D. Lenstra

Copromotor: dr.ir. Th.G. van de Roer to Anca and our parents

.

#### Acknowledgements

This work has been carried out with the contribution and collaboration of many people. Gratefully I acknowledge support and friendship from the members of the Electronic Devices Group of Eindhoven University of Technology. I would like to thank prof. Dr. L. M. F. Kaufmann for giving me the opportunity to realize this work and for permanent help. I thank dr. ir. Th. G. Van de Roer, my copromotor, who has been alongside of me from the very beginning till the end. I acknowledge the critical reviewing of this work and fruitful discussions by prof. dr. D. Lenstra, my second promotor. I thank also drs. E. Smalbrugge for wonderful collaboration during device processing and ing. J. J. M. Kwaspen unstinted help in microwave measurements, from which I learned a lot and I still have to do.

I acknowledge the colaboration of W. C. van der Vleuten from Solid State Department of Eindhoven University for having grown the epitaxial structures. I wish to thank prof. Dr. rer. nat. F. J. Tegude for getting me support in partial processing of the three terminal DBRT devices at Duisburg University, Electronic Devices Department.

Acknowledgements are due to dr. C. Popescu from Research Institute of Material Physics, Bucharest, for permanent encouragement. I also thank dr. T. Stoica from the same institute for help in temperature dependent measurements and von Humboldt foundation for the equipment donation.

Finally I will not forget my family for their permanent support and especially Anca, Simina and Silvana for their patience during the work and preparation of this thesis.

# Contents

# 1. Introduction

| 1.1 Tunneling in Solids                                                | 1  |

|------------------------------------------------------------------------|----|

| 1.2 Resonant Tunneling in Quantum Structures                           | 3  |

| 1.3 Materials for Resonant Tunneling Structures                        | 4  |

| 1.4 Evolution of the Two and Three Terminal Resonant Tunneling Devices | 7  |

| 1.5 Outline of the Dissertation                                        | 12 |

| References                                                             | 13 |

# 2. Resonant Tunneling Device Physics

| 2.1 Introduction                                       | 16 |

|--------------------------------------------------------|----|

| 2.2 Principles of Resonant Tunneling                   | 16 |

| 2.2.1 Electronic States in a Double Barrier Structure  | 17 |

| 2.2.2 Coherent Resonant Tunneling                      | 20 |

| 2.2.3 Incoherent Resonant Tunneling                    | 23 |

| 2.3 Current Density                                    | 25 |

| 2.4 Band Bending under Bias Condition                  | 27 |

| 2.5 Quantum Well Charge Storage: Intrinsic Bistability | 28 |

| 2.6 Effects of the Band Nonparabolicity                | 29 |

| 2.7 Excess Valley Current                              | 30 |

| References                                             | 31 |

# 3. Technology

| 3.1 Introduction                                                       | 33 |

|------------------------------------------------------------------------|----|

| 3.2 General Processes                                                  | 34 |

| 3.2.1 Cleaning                                                         | 34 |

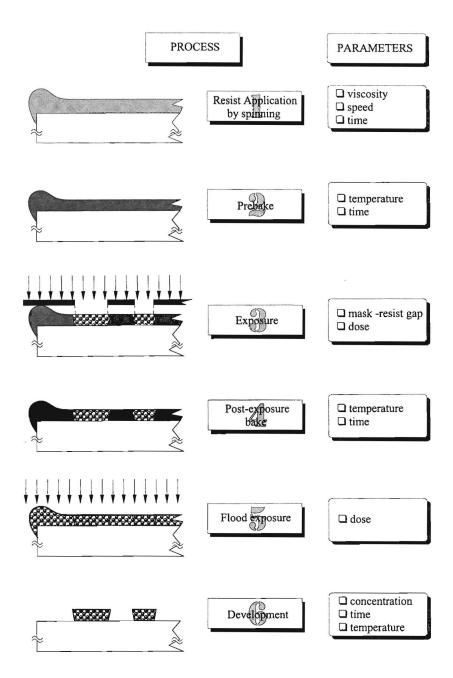

| 3.2.2 Photolithography                                                 | 36 |

| a) Direct Process Positive Resist Photolithography                     | 38 |

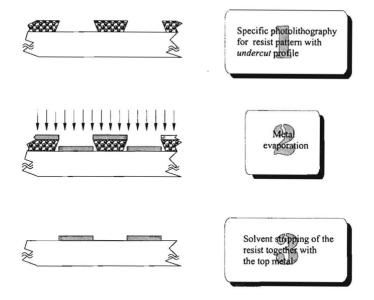

| b) Image Reversal Technique and Dual Image Photoresists                | 45 |

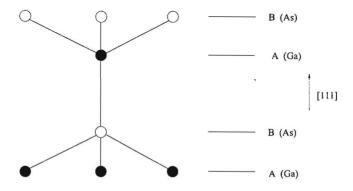

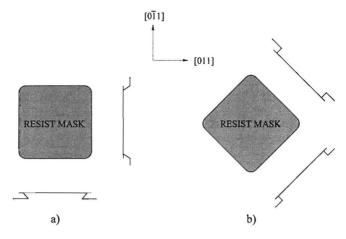

| 3.2.3 Wet Chemical Etching                                             | 49 |

| 3.2.4 Contacts                                                         | 55 |

| 3.3 Specific Processes                                                 | 63 |

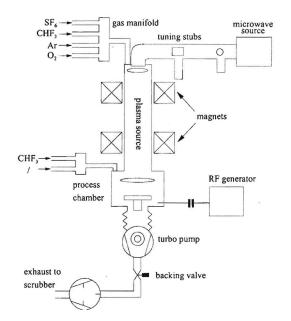

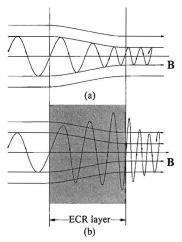

| 3.3.1 Thin Film Dielectric Deposition and Etching using Plasma Systems | 63 |

| 3.3.2 Selective Etching                                                | 69 |

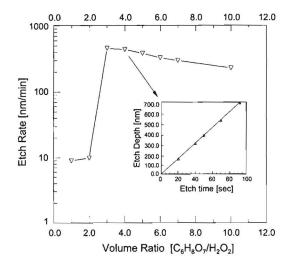

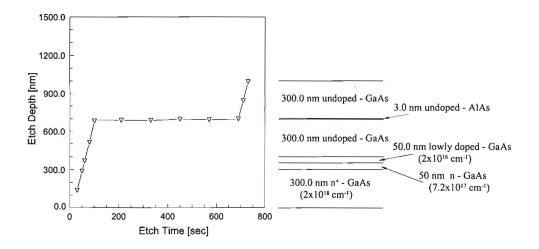

| a) Selective Wet Etching                                               | 70 |

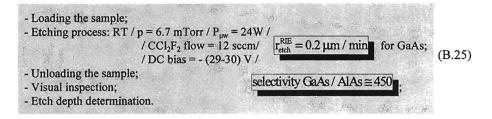

| b) Selective Dry Etching                                               | 73 |

|                                                                        |    |

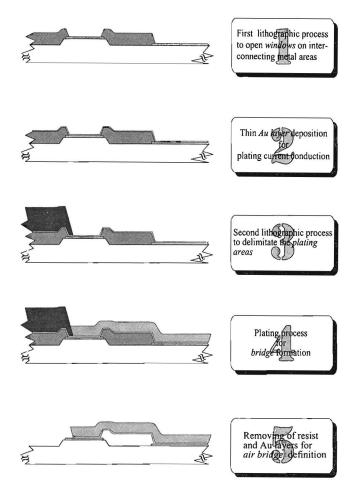

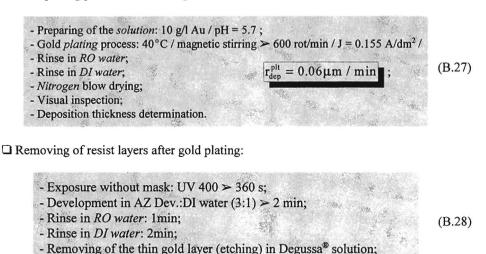

| 3.3.3 Gold Plating and Airbridge Fabrication | 73 |

|----------------------------------------------|----|

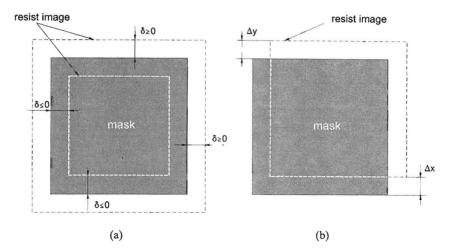

| 3.4 Design and Fabrication of Masks          | 78 |

| 3.5 Conclusions                              | 82 |

| References                                   | 83 |

# 4. Two Terminal DBRT Devices

|                                                       | s   |

|-------------------------------------------------------|-----|

| 4.1 Introduction                                      | 87  |

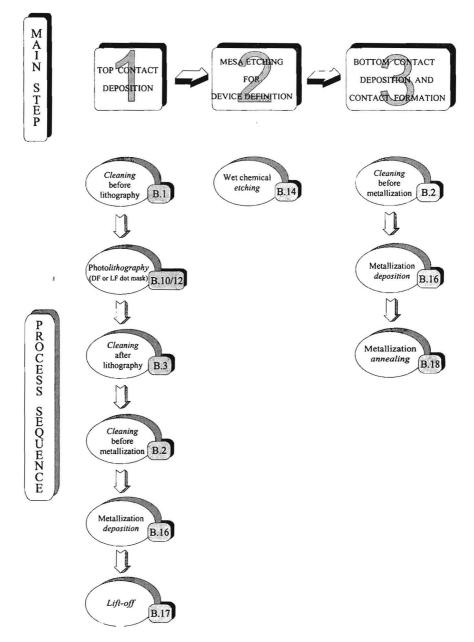

| 4.2 Device Fabrication                                | 88  |

| 4.3 Measurements                                      | 94  |

| 4.3.1 DC Measurements                                 | 94  |

| a) Room Temperature DC Measurements                   | 94  |

| b) Temperature Dependent DC Measurements              | 101 |

| 4.3.2 AC Measurements                                 | 103 |

| 4.4 Modeling                                          | 108 |

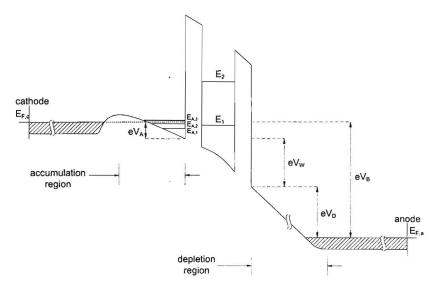

| 4.4.1 Model Description                               | 109 |

| a) The Accumulation Region                            | 109 |

| b) The Barrier Region                                 | 110 |

| c) The Depletion Region                               | 110 |

| d) Calculation of the Current-Voltage Characteristics | 110 |

| 4.4.2 Results                                         | 111 |

| 4.5 Conclusions                                       | 115 |

| References                                            | 115 |

|                                                       |     |

# 5. Three Terminal DBRT Devices

| 5.1 Introduction       | 117   |

|------------------------|-------|

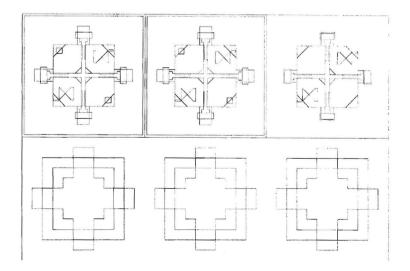

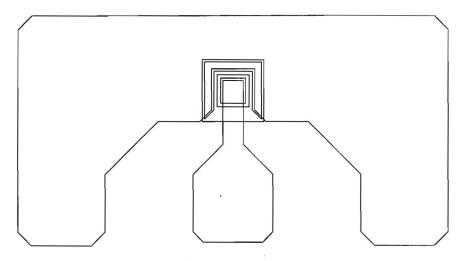

| 5.2 Mask Layout        | 118   |

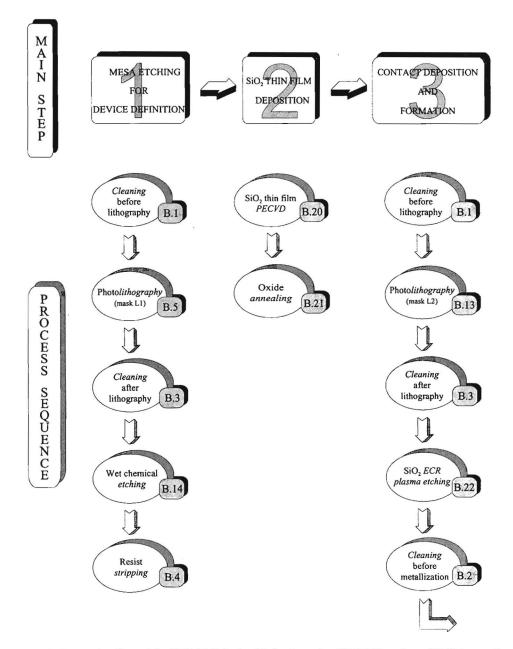

| 5.3 Device Fabrication | 119   |

| 5.4 Measurements       | 123   |

| 5.4.1 DC Measurements  | 123   |

| 5.4.2 AC Measurements  | 130   |

| 5.5 Conclusions        | 138   |

| References             | 139   |

| · · · ·                |       |

| Conclusions            | . 140 |

| Appendix A             | 143   |

| Appendix B             | 153   |

| Summary                | 166   |

| Samenvatting           | 168   |

| Curriculum Vitae       | 170   |

# 1

# Introduction

## 1.1 Tunneling in Solids

Tunneling is a quantum process in which a particle penetrates into and traverses a barrier region where the potential energy exceeds its initial, kinetic plus potential, energy. According to classical physics, conservation of the energy would not permit this to occur, the particle being totally reflected by the barrier. It is possible in quantum physics, where the particle wave function, and hence its probability density, is spread out over both the classically allowed and classically forbidden parts of the path. Wave functions penetrate from allowed regions into adjoining forbidden regions, for a limited distance, and this allows non-classical motions of the particle that can cross a sufficiently narrow barrier.

Historically the definition of the concept of tunneling and the observation of its experimental manifestations represented one of the early triumphs of the Schrödinger wave mechanics. After Oppenheimer in 1928 [1], used this prediction to describe the autoionization of excited states of atomic hydrogen in a strong electric field, other tunneling processes were conceived and investigated with important consequences in the fields of atomic, nuclear and solid state physics. They included the field emission or the escape of an electron from the surface of a metal into the vacuum in an externally high electric field (Fowler and Nordheim 1928 [2], Nordheim 1929 [3]); the penetration of a metal surface barrier by electrons in thermionic emission (Frenkel 1929 [4], Nordheim 1929 [3]); and the alpha decay of an atomic nucleus in which the alpha particle escapes by tunneling through a barrier of an atomic nucleus (Gamow 1928 [5], Gurney and Condon 1929 [6]). Soon afterwards it was proposed that the current flow between two conductors in electrical contact involved electron tunneling through a potential barrier at the interface (Frenkel 1930 [7]). A short time later the advent of the quantum theory of the (extrinsic) semiconductors (1931) permitted several tries to explain the rectification by metal semiconductor junctions (Schottky 1931 [8], Frenkel and Joffe 1932 [9], Wilson 1932 [10]) and construction of a model of "internal field emission" or interband tunneling as an explanation for the dielectric breakdown (Zener 1934 [11]). Unfortunately in both situations other mechanisms proved to have prevalence, the thermally activated charge transfer over the top of the metal semiconductor barrier in the first case and the hot electron effects such as impact ionization, avalanche, etc. in the second.

All these offered the theoretical basis for many phenomena characterized as being "tunneling

in solids". Nevertheless the experimental observation of most of these phenomena and their study using simple models occurred in the postwar era, when the material technology developed intensively. As a result of this technological progress another two important events were registered in the field, the invention of the p-n tunnel diode (Esaki 1957 [12]) and the discovery of the tunneling into superconductors (Giaever 1960 [13]). The first one represented the most convincing experimental evidence for tunneling in homogeneous, single-crystal material. The later led to the prediction and observation of weak coupling between superconductors (Josephson 1962 [14], 1963 [15]).

In general, in solids two categories of tunneling phenomena can be involved. Thus, one can speak about the elementary tunneling processes in atomic field, with "microscopic barrier", invoked to explain certain transport phenomena in the bulk semiconductors and also in molecular crystals. On the other hand there are the tunneling processes through macroscopic potential barriers or junctions (the interface of different materials). Concerning this aspect it is interesting to point out that most of the people in the field consider only the last category as referring to "tunneling phenomena in solids" [16, 17]. An explanation could be the great importance which the junction tunneling processes have for the electronic devices.

In their turn the junction tunneling processes also can be divided into two classes according to either the tunneling being in heterojunction systems, e.g. metal-insulator-metal, metalinsulator-semiconductor, supraconductor-insulator-supraconductor, Schottky junctions, etc., or in the same material (semiconductor) as interband tunneling.

A fundamental and difficult question to be asked about junction tunneling in a given system is "*what is the physical origin of the barrier potential*?". Although the answer to this question is obvious in the case of field ionization of atomic hydrogen (microscopic barrier), it ceases to be self-evident for external or internal field emission from a solid (macroscopic barrier). For systems that are in a self-binding state, the physical mechanisms responsible for the barrier potential are primarily the multitude of microscopic interactions that cause the self-binding, rather than a simple one-electron external potential like that due to a proton (ie. hydrogen nucleus). The simplest model of an interface or a tunnel junction is the "independent-electron" model in which the junction region is replaced by an external (one electron) potential. Prior to the discussion of tunneling into superconductors that involves collective-phenomena and thus a many-body approach, this model was exclusively considered in literature. The early applications of tunneling through junctions considered the free-electron model in which "de Broglie waves" were associated to the electrons.

After the development of the quantum theory of solids and in particular that of semiconductors, it was evident that the electron tunneling through junctions involves the relatively complex Bloch states. But to solve the Schrödinger equation even in the adiabatic approximation, in which the motion of the ions and electrons are separated, proved to be practically impossible. Two qualitatively different model simplifications of the Hamiltonian describing the junction have been studied. In the first an adequate treatment of the Coulomb electron-electron interactions is attempted at the expense of neglecting the electron-ion potential altogether by replacing it with a uniform positive background in each part of the junction. This is the so called "jellium" model and has been applied to evaluate the charge density at a metal-vacuum interface (Bardeen [18], Bennett and Duke [19]) and to describe bimetallic and metal-semiconductor contacts (Bennett and Duke [20]). In the second model simplification, an attempt

#### 1.2 Resonant Tunneling in Quantum Structures

is made to include the periodic component of electron-ion potential ab initio by using one electron states appropriate for the relevant periodic potential on each side of the interface, but permitting the charge distribution near the junction to introduce a slowly varying average potential determined by Poisson equation. This average potential is said "to bend the bands" near the interface. In its initial form this approach was developed to describe situations in which the local perturbing non-periodic potential is caused by impurities, electric fields, etc. and is known as the envelope function representation. Supplementary approximations in combination with this are the neglect of band bending in one part (usually the metal) of the junction and the use of WKB (Wentzel. Kramers. Brillouin) or semiclassical approximation, or the effective-mass approximation, depending on whether the junction is gradual or abrupt. The value at the interface of the shift of the energy zero (usually conduction band edge) in one electrode relative to another (which is primarily a consequence of the electron Coulomb interactions) is treated as a phenomenological parameter to be determined from experiment. The effective mass method was introduced by Ben Daniel and Duke [21] for the study of the metal-oxide-semimetal tunnel junctions and abrupt p-n tunnel diode. It consists of considering the description of the electron eigenstates by the envelope functions rather than using the full wave functions and using of appropriate boundary conditions for these to guarantee the probability current conservation. The abrupt-junction effective-mass and the gradual-junction WKB methods do not lead to identical expressions for the tunneling current. It is important to note the distinction between the two methods: the accurate treatment of the external potential at the expense of a quadratic approximation for the band energies which characterizes the effective-mass method and the accurate treatment of the band energies (in the classically forbidden region) at the expense of an approximate treatment of the external potential which characterizes the WKB method.

# **1.2 Resonant Tunneling in Quantum Structures**

Resonant tunneling is distinguished from the simple tunneling process by the presence within the classically forbidden region of the quasibound, or metastable, states of the tunneling particle.

The most typical situation is that one of the double barrier resonant tunneling which is involved in both nuclear and solid state phenomena. In the quantum theory textbook written by Bohm [22] in 1951, the double barrier problem was solved in the WKB approximation. He showed that, at certain energies, unity transmission resonances (resonant tunneling) occur for particles incident upon the structure. These energies correspond to quasibound states between the two barriers. Also the subject was treated by Kane [23] in a general presentation of the basic concepts of tunneling. In his approach Kane describes two methods for the determination of the tunneling probability in square barriers and square wells: the transfer matrix method that starts from the Ben Daniel and Duke's effective mass approximation and the transfer or tunneling Hamiltonian method, well known in the field of superconductivity but originated from the first tunneling approach of Oppenheimer. Later these became useful tools in the treatment of resonant tunneling in quantum heterostructures.

The extension of the double barrier resonant tunneling problem to the more general case of a periodic rectangular potential (Kronig-Penney), also presented in quatum mechanics textbooks [24], offered a simple model of the behaviour of electrons in a crystal lattice. The electron energy

#### 1 Introduction

spectrum along the periodic potential consists of continuous bands separated by forbidden gaps.

The advance of the epitaxial growth techniques, namely Molecular Beam Epitaxy (MBE) and Metal Organic Vapour Phase Epitaxy (MOVPE), made possible the growth of very pure and thin semiconductor layers (especially from III-V compounds) with accuracy up to one atomic layer. In this way it became possible to design and fabricate a large variety of structures characterized by manifestation of the quantum phenomena. Among them, naturally one can say, it was also the double barrier resonant tunneling (DBRT) structure. In conjunction with the interest manifested for the possible high speed microwave applications the DBRT diode became the most studied resonant tunneling device in the last decade.

The DBRT structure consists primary of two layers of semiconductor material, such as AlAs, embedded in another semiconductor having a smaller band gap, such as GaAs. The band diagram of this layer sequence represents a quantum well between two potential barriers. Two electron reservoir layers clad the basic structure resulting the DBRT diode.

In the study of resonant tunneling properties of the DBRT diode two main approaches have been developed. The first one, known as the coherent tunneling model, is based on the calculation of the transmission coefficient for the full structure as one coherent wave propagation, using the Kane's transfer-matrix method. The coherent tunneling description is a true wave-mechanical approach to tunneling: the resonance is due to multiple reflections of the electron waves in the well, whence the analogy with the Fabry-Perot interferometer in optics.

The second approach, the sequential-tunneling model, considers the tunneling as two separate and subsequent processes, from emitter to well and from well to collector. No coherence of the wave function is assumed in the description. The transmission coefficient is obtained using the transfer Hamiltonian method. In this method the Hamiltonian for the full double barrier structure is replaced by three Hamiltonians for each allowed region, separately. For each barrier a "transfer Hamiltonian" is considered which is treated as a first order perturbation in the perturbation theory and from this the transmission coefficient is calculated using the Fermi Golden Rule.

In addition to the two previous models, a third approach, using Wigner distribution functions has to be mentioned [25]. The Wigner distribution function is the Fourier-transformed density matrix in phase space. It is the closest parallel to the classical distribution function, that quantum mechanics can offer. Consequently, many results of classical transport theory can be transferred to a Wigner function based quantum transport theory. The usefulness of the Wigner representation consists in the fact that it permits the evaluation of the time evolution of the resonant tunneling phenomenon as well as the steady state situation.

The practical transposition of the physical situation described by the Kronig-Penney potential has been also possible due to the advanced epitaxial technics. The structures, named *superlattices*, have become both means for fundamental research in solid state physics and component parts of electronic devices.

# **1.3 Materials for Resonant Tunneling Structures**

As we have seen, the resonant tunneling process requires stacked thin semiconductor layers with different band gaps which, energetically speaking, give rise to at least a double barrier structure. The diversity of band alignments between III-V semiconductors suggests, at least in

#### 1.3 Materials for Resonant Tunneling Structures

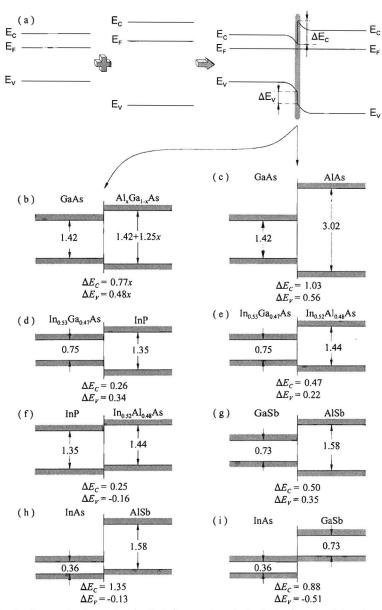

principle, that there are considerable number of possibilities to realize resonant tunneling structures from these materials. To illustrate this, Fig. 1.1 shows the best estimate of the band alignments for eight lattice- or nearly lattice-matched III-V compound heterojunctions. We specify that for a general heterojuction the band gap discontinuity is distributed between the valence and conduction bands. As seen in Fig. 1.1a the corresponding band "offsets",  $\Delta E_v$  and  $\Delta E_{c}$ , are abrupt discontinuities in the band edges at the heterojunction interface. Additionally, electrostatic band bending also occurs because of charge redistribution near the interface. The band bending changes (increasing usually) if the heterojunction is doped, but the band offsets is presumably to remain constant. In general, one speaks about an isotype junction if the same conductivity type is achieved on both sides of the junction (n-n or p-p) and an anisotype junction if the type of conductivity is opposite (n-p or p-n). The diagrams in Fig. 1.1, illustrating the band alignments for the different systems, show the behaviour of the  $E_{c}$  and  $E_{y}$  in the immediate vicinity of the heterojunction, that is they figure only the band offsets. According to the relative ordering of the band edge energies we can distinguish several types of band alignments [26]. The most common (and generally considered to be the "normal") alignment is the straddling configuration illustrated in the cases (b) [27], (c) [27], (d) [28], (e) [28] and (g) [29] of Fig. 3.1, in which the bandgaps of the two materials entirely overlap. Another situation is when the bandgaps are partial overlapped i.e., the conduction band of the smaller-gap material might lie above that of the larger-gap material, or its valence band might lie below that of the larger-gap material. Such a band alignment is called *staggered* and is known to occur in the cases (f) [30] and (h) [31] presented in Fig. 1.1. The staggering might become so extreme that the bandgaps cease to overlap. This situation is known as a *broken gap* alignment, being illustrated in Fig. 1.1i [29]. Another nomenclature, employed usually in describing superlattices, divides the band alignments in two main categories; type I and type II alignments. If the extrema of both the conduction and valence bands lie both in the same layers, the alignment is referred as type I. whereas if the band extrema are in different layers the alignment is type II. Comparing the two notations, one can easily observe that the type I alignments correspond to the straddling case and the type II alignments include both staggered and broken-gap situations.

Grown on a lattice-matched substrate, as GaAs, InP or GaSb, each of the above systems have been used to demonstrate the resonant tunneling phenomena in double barrier structures (see next section). This case, in which all the layers in and around the double barrier structure are made of materials having the same lattice constant as the substrate, is the most desirable from the point of view of the epitaxial growth of high quality materials. But, some other possibilities, using also not lattice-matched materials, have been successfully demonstrated. One of these is to lattice match the quantum well and cladding layers with the substrate but use a material having a different lattice constant in the barriers. If the barriers are sufficiently thin, their lattice will conform by compression or tension to surrounding layers in the lateral plane, and will deform in the opposite sense in the longitudinal axis. This is called a pseudomorphic match and the resulting layers have few defects (dislocations). Another possibility is to lattice match the barriers but use material of different lattice constant in all or part of the quantum well, or some portion of the cladding layers. Again, if the layers are sufficiently thin, a pseudomorphic match results.

Fig. 1.1 Conduction- and valence- band offsets in a semiconductor heterojunction (a) and experimentally determined band alignments for lattice-matched heterojunctins between group III-V semiconductors (b-i) [27]. Energies are indicated in electron volts. For GaAs/Al<sub>x</sub> Ga<sub>1-x</sub>As the case (b) illustrates the direct gap range and (c) the indirect gap corresponding to  $\Gamma$  minimum. Cases (b), (c), (d), (e), and (g) show straddling alignments, cases (f) and (h) are typical for staggered alignments, and case (i) corresponds to the broken-gap alignment.

# **1.4 Evolution of the Two and Three Terminal Resonant Tunneling Devices**

The history of the double barrier resonant tunneling (DBRT) diode or two terminal (2T) resonant tunneling device, identifies with the progress of the molecular beam epitaxy (MBE) technique. In 1974 Chang et al. [32] fabricated the first MBE grown DBRT structure that exhibited evidence of negative differential resistance (NDR) at low temperature. Following this pioneering result, most of the work in heterostructures centred around the development of the MBE, since it was clear that the quality of the materials in these structures would have to be improved in order to observe the NDR or any other quantum transport at room temperature. The primary structures studied during this time were single-heterojunction devices or quantum wells rather than resonant tunneling structures.

In 1983 Sollner et al. [33] used a cooled GaAs/AlGaAs double barrier structure to rectify 2.5 THz laser radiation. This pivotal experiment demonstrated that resonant tunneling was a very fast process and it spurred the development of improved materials. Within 3 years several groups have achieved a relative large room-temperature NDR effect, first in the GaAs/Al<sub>0.25</sub>Ga<sub>0.75</sub>As material [34] and shortly after that in the GaAs/AlAs system [35, 36]. After these first successful examples an intense research activity developed to increase the performances of the resonant tunneling structures and at the same time to study the physical phenomenon itself. Before other MBE material systems became available for quantum devices the field of resonant tunneling structures was already matured using almost exclusively the GaAs/Al<sub>x</sub>Ga<sub>1,x</sub>As system.

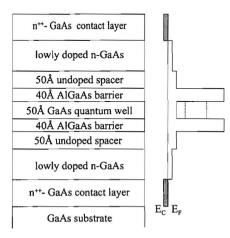

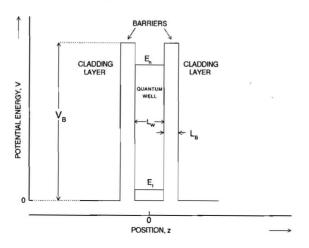

Fig. 1.2 illustrates schematically a typical electron resonant tunneling structure, where a GaAs quantum well is clad by two thin barrier layers of a material with a larger gap (e.g. AlGaAs). The contact layers are doped n-type for an electron tunneling device. Two other kinds of layers are inserted between the proper structure and the contacts: the undoped "spacer" layers and the lowly doped layers.

Fig. 1.2 Schematic illustration of the MBE-grown structure and the corresponding conduction band diagram for a typical n-type DBRT structure.

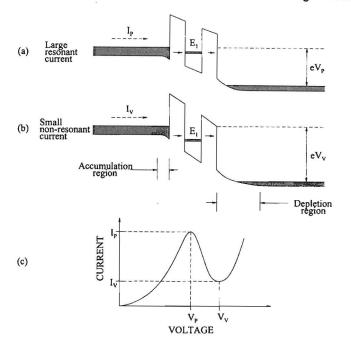

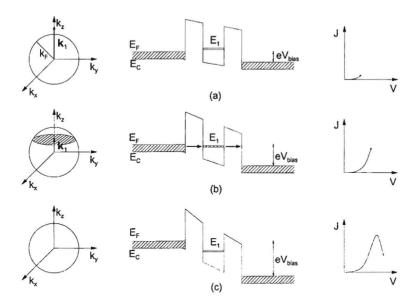

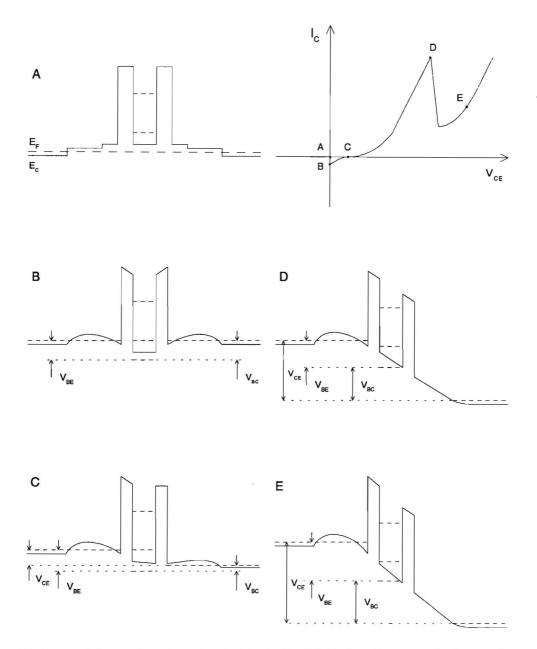

From the application point of view the quality of a DBRT diode is usually given by the peak current density  $J_p$  and the peak to valley current density ratio PVCR =  $J_p/J_v$ , where  $J_p$  and  $J_v$  are the peak and valley current densities, respectively, associated with the NDR region of the currentvoltage (I-V) characteristics (see Fig. 1.3). Other quantities of importance are the peak to valley voltage ratio PVVR =  $V_p/V_v$ , where  $V_p$  and  $V_v$  are the peak and valley voltages, respectively, and the available current density  $\Delta J \equiv J_p - J_v$ . For high speed operation the current density should be large ( $J_p \ge 10^5 \text{ A/cm}^2$ ) for the same reasons as in any other fast speed electronic device: high current density is required for fast charging and discharging of the device and circuit capacitance.  $\Delta J$  should be also as large as possible and  $\Delta V = V_v - V_p$  small. The PVCR of a double barrier structure is sensitive to relative magnitudes of a number of resonant, nonresonant, and parasitic currents. Some of the major contributions to the overall carrier transport in a DBRT diode include (a) resonant tunneling, (b) tunneling through a higher resonance level, (c) thermionic emission, (d) field-assisted tunneling, (e) tunneling through evanescent states, (f) inelastic tunneling, and (g) surface leakage current [37]. These processes are illustrated in Fig. 1.4.

The process of achieving a high PVCR represented in fact an "exercise" in enhancing the resonant tunneling current density while minimizing all nonresonant and parasitic contributions to the valley current. A number of factors that modify both resonant and nonresonant currents are due solely to specific MBE growth conditions. They refer to the quality of the layers and especially to the sharpness of the interfaces expressed by the so called interface roughness. Theoretical studies [38,39] have shown that scattering from interface roughness of the quantum well and barriers broadens the resonance leading to the decrease of the peak current. Unfortunately for the DBRT diode there is no technique to measure quantitatively the degree of interface roughness and to correlate it with the observed transport characteristics of the device. The "standard" quantum well characterization technique - the observation of the excitonic spectrum using photoluminescence (PL) - is not possible in this case because the high doping of the contact layers effectively masks the PL emission from the energy levels in the quantum well [40]. In this way the most sensitive characterization tool for the analysis of the structure of materials used in resonant tunneling applications has appeared to be the tunneling device itself.

Besides the optimization of the growth conditions, DBRT devices with improved performances resulted by altering the design characteristics of the structure. Among them the increase of the barrier height proved to be very important, modifying the Al concentration towards larger values, and the optimization of their width. The introduction of undoped "spacer" layers on the outer sides of the barrier layers was also beneficial for the device quality. Finally, the same positive influence had the use of lowly doped layers, interposed between the contact and spacer layers.

The first DBRT structure functioning at room-temperature had a GaAs quantum well and  $Al_{025}Ga_{0.75}As$  barriers without spacer and lowly doped layers [34]. With a  $J_p$  of  $1.6 \times 10^3$  A cm<sup>-2</sup> and a PVCR of 1.5 (8) at 300 K (77 K) its performances were relative modest. Increasing the Al mole fraction in the barriers to  $x \approx 0.4$  and introducing the spacer layers, useful PVCR at values of  $J_p$  up to about  $1 \times 10^4$  A cm<sup>-2</sup> resulted [41]. At higher values of  $J_p$  the PVCR is usually degraded by large thermionic current over the top of the barriers as well as the nonresonant tunneling current through the next quasilevel in the quantum well. Consequently, much better PVCR at high  $J_p$  offered the GaAs/AlAs structures [36]. In GaAs/AlAs DBRT diodes having  $J_p$  in the range from  $10^4$  to  $10^5$  A cm<sup>-2</sup>, the best observed room-temperature PVCRs are about 4.

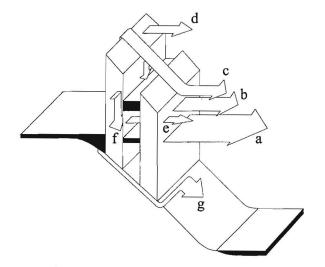

**Fig. 1.3** Schematic diagrams of the current flow through a DBRT diode at bias voltage near peak (a) and valley (b) points, and representative I-V characteristics showing the NDR region (c).

**Fig. 1.4** Contributions to the resonant and nonresonant currents in a DBRT diode: (a) resonant tunneling, (b) tunneling through a higher resonance level, (c) thermionic emission, (d) field-assisted tunneling, (e) tunneling through evanescent states, (f) inelastic tunneling, and (g) surface leakage current [37].

These results followed after systematic studies of the effects of the barrier thickness and composition in Al [41, 42] as well as of the spacer layer width [43, 44]. At higher peak density currents, the PVCR degrades significantly [45, 46], the best reported PVCR with  $J_p \ge 10^5$  A cm<sup>-2</sup> being 3.0 [47].

Several clever structures have been implemented to improve the PVCR of the GaAs DBRT diodes by lowering the valley current. In a first case, the spacer side AlAs barriers have been grown with  $Al_xGa_{1-x}As$  layers just outside to form "chair barriers" [48]. This has resulted in a DBRT diode having PVCR of 6.3 at room temperature [49]. Other structures contained an  $In_xGa_{1-x}As$  layer either as a prewell on the cathode side [50] or in place of the GaAs quantum well [44]. An improved PVCR resulted in both cases.

New material systems successful grown by MBE have been used also for DBRT structures. The indium based systems, InGaAs/InAlAs and InAs/AlSb are the most important but others like InAs/GaSb/AlSb arouse more and more interest.

The first useful DBRT diodes in the In containing system have been made from  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  materials [51], because both of these ternary alloys are lattice matched to InP substrates. The structure yielded a PVCR of 2.3 at room temperature. This was subsequently improved to about 7 at room temperature and 40 at 77K [52, 53]. Superior results have been obtained by replacing the  $In_{0.52}Al_{0.48}As$  barriers with pseudomorphic AlAs. The resulting DBRT diodes demonstrated an unprecedent PVCR of 14 at room temperature [54]. Further improvement followed with the achievement of a PVCR of 30 at room temperature in a DBRT structure having a thin InAs layer embedded in the  $In_{0.53}Ga_{0.47}As$  quantum well [55].

The primary reason for the superiority of the  $In_{0.53}Ga_{0.47}As/AlAs$  diodes over the GaAs/AlAs diodes has been attributed to the large separation between the  $\Gamma$  point conduction band minimum in the  $In_{0.53}Ga_{0.47}As$  and the X point conduction band point in the AlAs barrier [54]. In the GaAs/AlAs system this separation is much smaller and has been correlated with the contributions to the valley current in these diodes [56, 57].

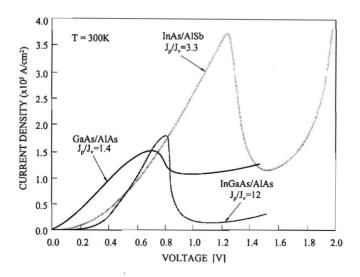

High quality DBRT diodes have been fabricated from the InAs/AlSb material system. The system has a staggered band offset in which the valence band edge of the AlSb lines up in the band gap of the InAs. This determines a significantly smaller barrier attenuation coefficient than is realized in GaAs/AlAs or  $In_{0.53}Ga_{0.47}As/AlAs$  structures having the same barrier thickness. The values of  $J_p \approx 3.7 \times 10^5$  A cm<sup>-2</sup> and PVCR  $\approx 3$  obtained for InAs/AlSb structures [58] are comparable with the best results achieved in the  $In_{0.53}Ga_{0.47}As/AlAs$  system and are considerably better than those of GaAs/AlAs DBRT diodes. For comparison Fig. 1.5 shows I-V curves of high- $J_p$  DBRT diodes made from different material systems [59].

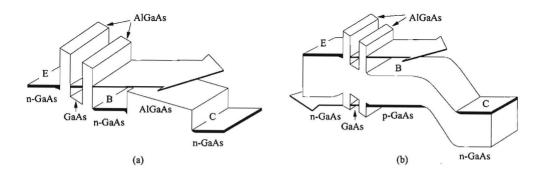

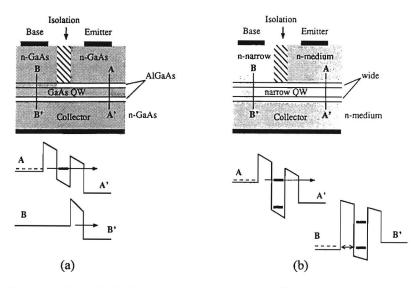

From the beginning the long range application of the resonant tunneling structures was their implementation in three terminal (3T) devices. A particularly powerful concept for achieving this has been to incorporate a DBRT structure into one or another junction or transport region of a bipolar, hot electron, or field effect transistor. In this implementation the primary operational parameters are those of the "traditional" device, with the tunneling features added to alter these characteristics. The most successful solutions in this approach proved to be the resonant tunneling hot electron transistor (RHET) and the resonant tunneling heterostructure bipolar transistor (RBT), with applications in logic circuits. The band structures and operation principle of an RHET and an RBT are shown in Fig. 1.6 [60].

The RHET evolved from a transistor with a wide base and no confinement [61, 62] to a

Fig. 1.5. Room temperature current density versus voltage curves for DBRT diodes made from three different material systems [60].

device with thin base (10nm) and hence confinement [63]. In this way a room temperature gain as high as 12 at a current density of  $1.3 \times 10^5$  A cm<sup>-2</sup> has been reached.

As an alternative at RHET several solutions of RBTs have been examined. The differences between them consists in the region of the bipolar transistor where the DBRT structure has been incorporated and the material system used. The best performances of such a transistor were obtained using InGaAs/InAlAs/InP system with the DBRT structure integrated in the emitter[64]: PVCR  $\approx$  70, J<sub>p</sub> > 10<sup>4</sup> A cm<sup>-2</sup> and the differential current gain at resonance of 19.

Another approach has been to make direct contact to the quantum well of a DBRT structure

Fig. 1.6 Band Structure and principle of operation illustration of an RHET (a) and RBT (b) [61].

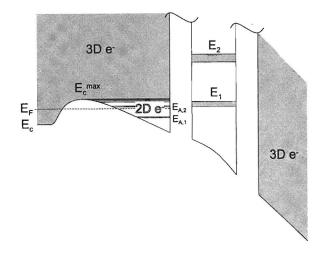

and thereby form a 3T device in which the quantum well base is two-dimensional (2D), with transport proceeding from three dimensional (3D) emitter to 2D base and then to 3D collector. In this way a separate control of the quantum well potential can be achieved. The primary challenge in this approach consists in the difficulty of exposing and making contact to such a thin layer (~ 5.0 nm) as the quantum well base. This technological obstacle conducted only to partial results in different laboratories [65-69].

After more than two decades, from the first DBRT structure, the resonant tunneling devices are a well defined and important part in the fast growing field of quantum devices.

# 1.5 Outline of the Dissertation

The goal of this dissertation is to study some physical aspects of 2T resonant tunneling devices and to propose a solution for a 3T resonant tunneling device with the base contact to the quantum well. To realize this, a comprehensive approach of the problems was developed, from the technological aspects of the device processing to the electrical measurements and then to modeling, with possible and inherent feed-back interconnections between them.

The second chapter gives an overview of the fundamental aspects of the resonant tunneling device physics. The actual understanding of the resonant tunneling process, with the two main approaches, coherent and incoherent tunneling, is exposed in detail, with the intention to give a unitary description of the phenomenon. The expression for the current density is derived and some important factors, which describe its behaviour with applied voltage, are discussed. The section offers the theoretical base for measurement interpretation and modeling presented in the next chapters.

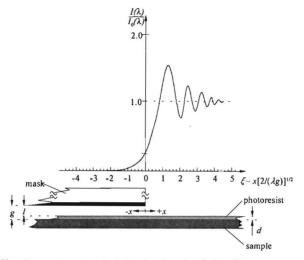

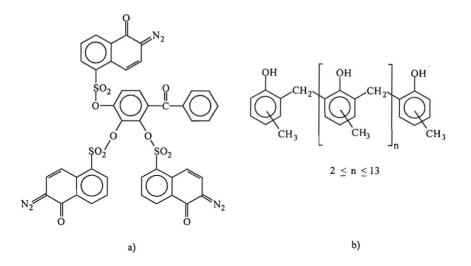

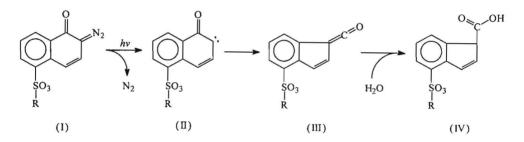

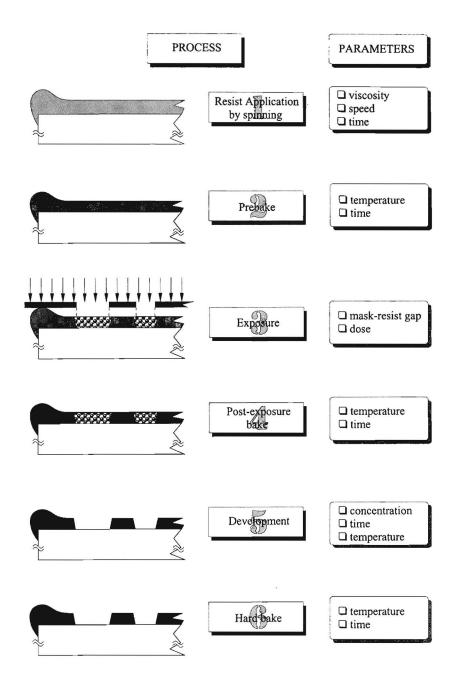

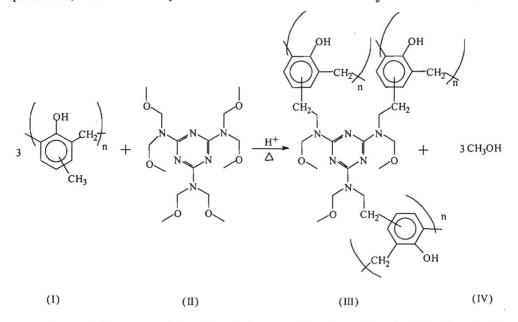

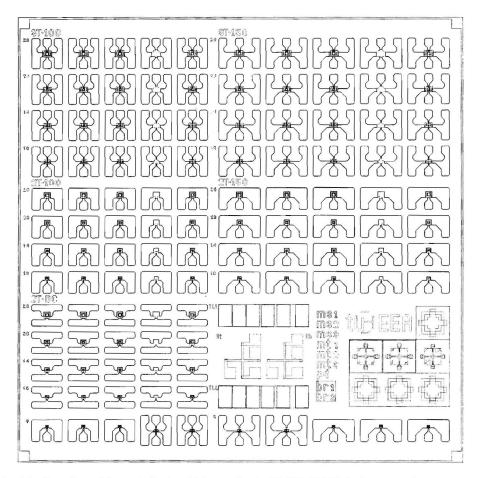

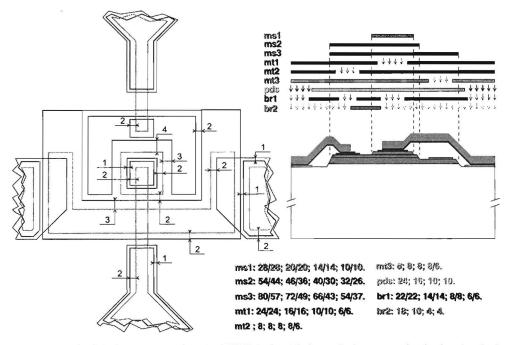

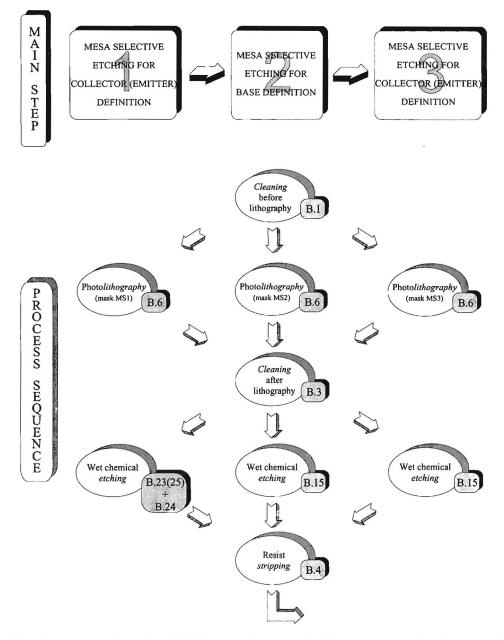

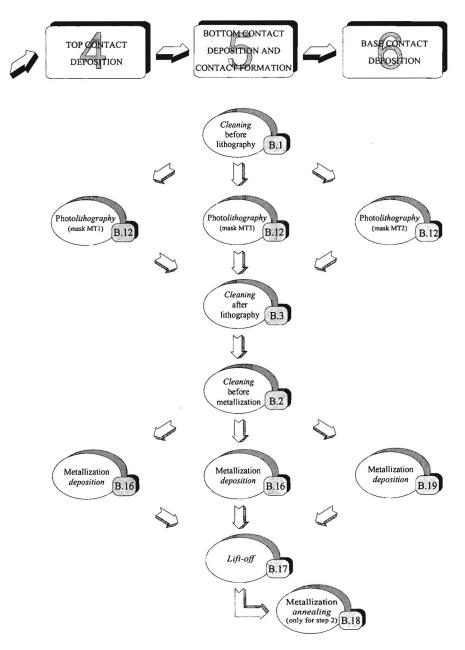

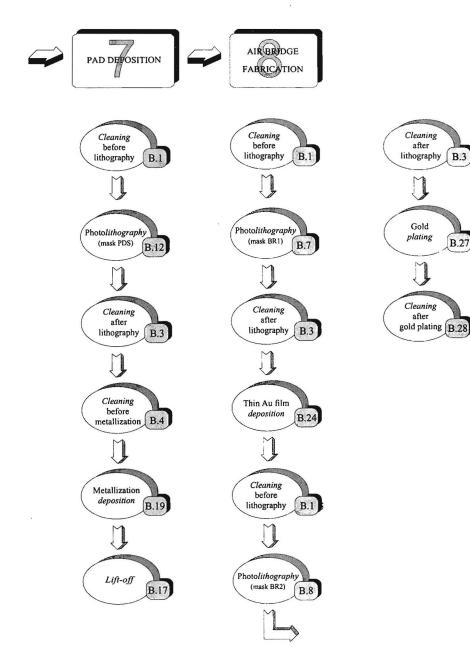

The technological processes involved in the fabrication of 2T and 3T resonant tunneling devices are presented in detail within chapter 3. Special attention is paid to the photolithography using both direct and dual image resists, wet chemical etching, selective etching of GaAs and AlGaAs, and gold plating for airbridge interconnections, which have been optimized for the specific design characteristics of the devices. The strategy of the mask design is also described.

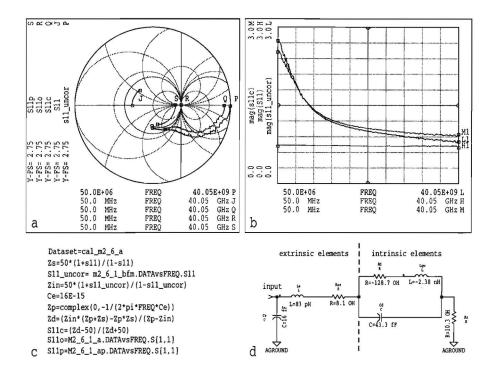

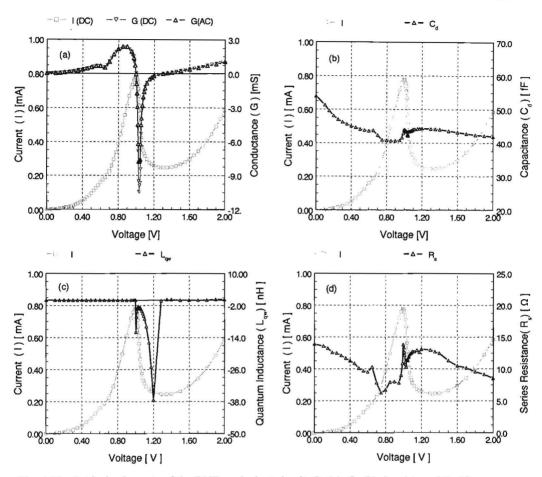

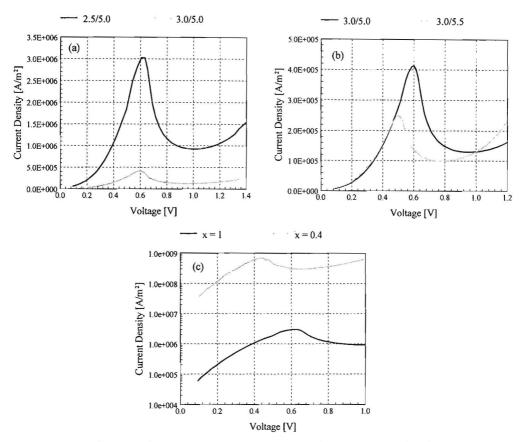

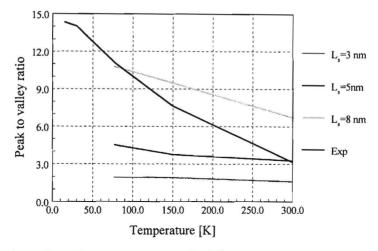

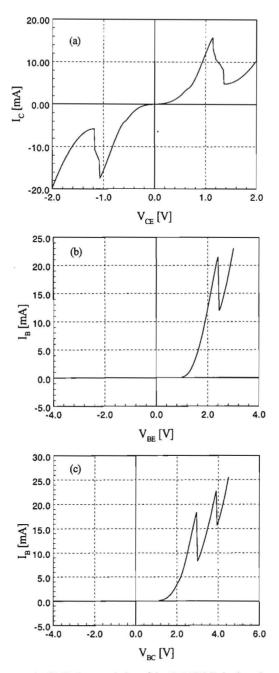

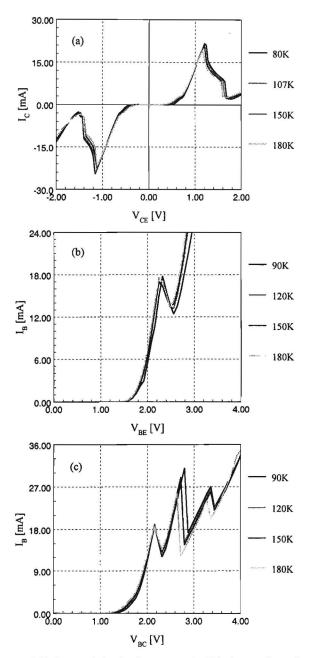

The next chapters present the devices studied in this thesis. The epitaxial structures necessary for device fabrication have been grown by MBE at the Solid State Physics department of Eindhoven University of Technology (EUT). Both 2T and 3T resonant tunneling devices described in the dissertation have been processed from structures using the available GaAs/AlGaAs material system. The processing has been accomplished using the clean room facilities of the Electronic Devices department of EUT. Chapter 4 deals with the 2T resonant tunneling devices. After the device fabrication description, the electrical measurements are presented and explained in detail, along several paragraphs. First, a comparative analysis of the room temperature DC results corresponding to the two types of processed devices, based on GaAs/Al<sub>0.4</sub>Ga<sub>0.6</sub>As and GaAs/AlAs materials, is carried out. Then, DC measurements versus temperature are interpreted in connection with possible tunneling mechanisms. Finally, accurate microwave measurements performed over the whole bias range of the device I-V characteristic are used to establish the proper equivalent-circuit of our DBRT structures and to extract the bias behaviour of the parameters associated to the circuit elements. The last part of the chapter is

#### References

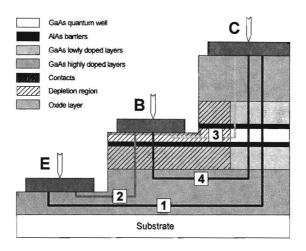

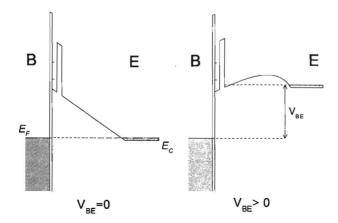

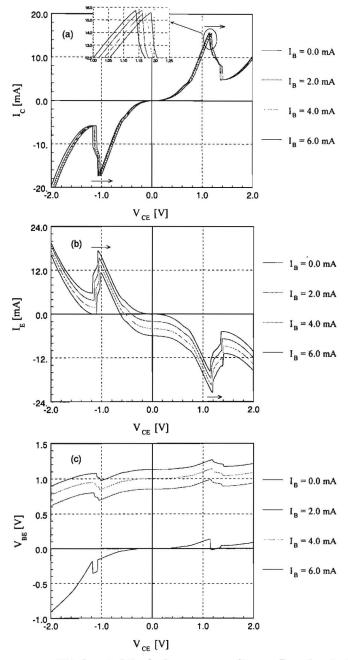

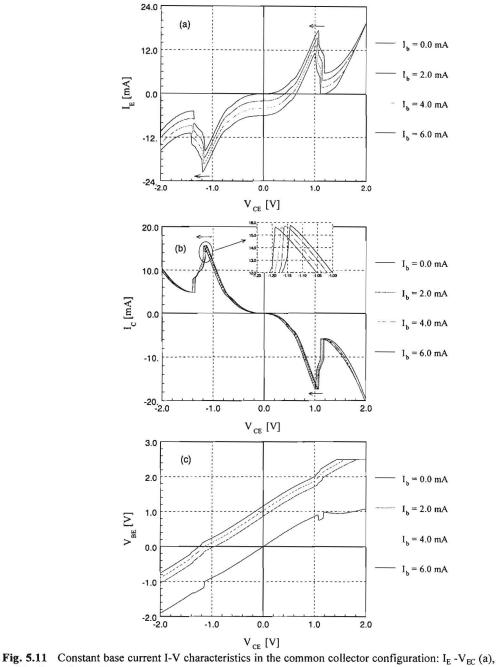

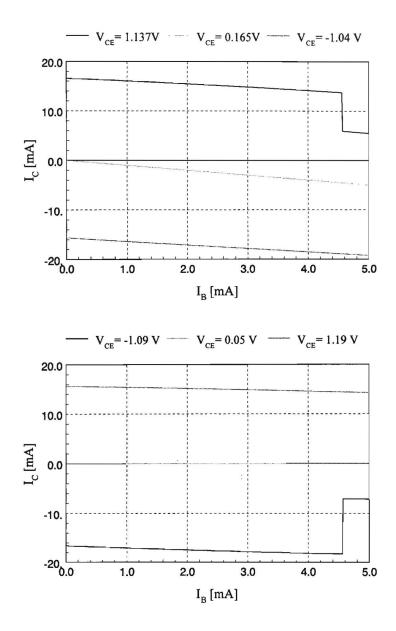

devoted to the device physical modeling of the I-V characteristic. Using an existing model, developed within the Electronic Devices Group in the last periode [70, 71], the DC behaviour of the 2T DBRT devices is described both qualitatively and quantitatively. Chapter 5 describes the fabrication and characterisation of the 3T DBRT devices. First, the technological solution to realize the device is exposed, with all the difficulties generated by the effort to contact such a thin layer as the quantum well. The mask layout designed especially for this aim is also described. Finally the DC and AC measurement results, that demonstrate the successful contacting of the quantum well, are discussed in connection with possible applications of this new device.

The last part summarises the work and gives an outlook on subsequent developments in the field of resonant tunneling devices described in this dissertation.

## References

- 1. J. R. Oppenheimer, Phys. Rev. 31, 66 (1928).

- 2. R. H. Fowler and L. W. Nordheim, Proc. Roy. Soc. A119, 173 (1928).

- 3. L. W. Nordheim, Phys. Z. 30, 177 (1929).

- 4. J. Frenkel, Einführug in die Wellenmechanik, Springer, Berlin, 1929.

- 5. G. Gamow, Z. Phys 51, 204 (1928).

- 6. R. W. Gurney and E. U. Condon, Phys. Rev. 33, 127 (1929).

- 7. J. Frenkel, Phys. Rev. 36, 1604 (1930).

- 8. W. Schottky, Phys. Z. 32, 833 (1931).

- 9. J. Frenkel and A. Joffe, Phys. Z. Sowjetunion 1, 60 (1932).

- 10. A. H. Wilson, Proc. Roy. Soc. A137, 487 (1932).

- 11. C. Zener, Proc. Roy. Soc. A145, 523 (1934).

- 12. L. Esaki, Phys. Rev. 109, 603 (1957).

- 13. I. Giavaer, Phys. Rev. Lett. 5, 147 (1960); 5, 464 (1960).

- 14. B. D. Josephson, Phys. Lett. 1, 251 (1962).

- 15. B. D. Josephson, Advan. Phys. 14, 419 (1963)

- 16. C. B. Duke, "Tunneling in Solids" Academic Press, New York, 1969.

- 17. E. Burnstein and S. Lundqvist eds., "Tunneling Phenomena in Solids" Plenum Press, 1969.

- 18. J. Bardeen, Phys. Rev. 49, 653 (1936).

- 19. A. J. Benett and C. B. Duke, Phys. Rev. 160, 541 (1967).

- 20. A. J. Benett and C. B. Duke, Phys. Rev. 162, 578 (1967).

- 21. D. J. Ben Daniel and C. B. Duke, Phys. Rev. 152, 683 (1966).

- 22. D. Bohm, "Quantum Theory", p. 283, Prentice-Hall, Engelwood Cliffs, N.Y., 1951.

- E. O. Kane, "Basic Concepts of Tunneling", in "Tunneling Phenomena in Solids", eds. E. Burnstein and S. Lundqvist, Plenum Press, New York, 1969.

- 24. E. Merzbacher, "Quantum Mechanics", p. 100, John Willey & Sons, New York, 1970.

- 25. W.R. Frensley, Phys. Rev. B 36, 1570 (1987).

- 26. H. Kroemer, Surface Sci. 132, 543 (1983).

- 27. E. T. Yu, J. O. McCaldin, and T. C. Mc.Gill, in "Solid State Physics, Advance in Research and Applications", eds. Ehrenreich and D. Turnbull, Academic Press, San Diego, CA,

Vol.46, p. 2, 1992.

- 28. J. R. Waldrop, E. A. Kraut, C. W. Farley, and R. W. Grant, J. Appl. Phys. 69, 372 (1991).

- 29. U. Cebulla, G. Tränkle, U. Ziem, A. Forchel, G. Griffiths, H. Kroemer, and S. Subbanna, *Phys. Rev. B* 37, 6278 (1988).

- 30. J. R. Waldrop, E. A. Kraut, C. W. Farley, and R. W. Grant, J. Vac. Sci. Technol. B8, 768 (1990).

- 31. A. Nakagawa, H. Kroemer, and J. H. English, Appl. Phys. Lett. 54, 1893 (1989).

- 32. L. L. Chang, L. Esaki, and R. Tsu, Appl. Phys. Lett. 24, 593 (1974).

- T. C. L. G. Sollner, W. D. Goodhue, P. E. Tannenwald, C. D. Parker, and D. D. Peck, *Appl. Phys. Lett.* 43, 588 (1983).

- 34. T. J. Shewchuk, P. C. Chapin, P. D. Coleman, W. Kopp, R. Fisher, and H. Morkoç, *Appl. Phys. Lett.* 46, 508 (1985).

- 35. M. Tsuchiya, H. Sakaki, and J. Yoshimo, Jpn. J. Appl. Phys. 24, L466 (1985).

- W. D. Goodhue, T. C. L. G. Sollner, H. Q. Lee, E. R. Brown, and B. A. Vojak, *Appl. Phys. Lett.* 49, 1086 (1986).

- R. D. Schnell, H. Tews, R. Neumann, A. Mitwalsky, R. Treichler, and G. Packeiser Inst. Phys. Conf. Ser. 106, 825, (1990).

- 38. H. C. Liu and D. D. Coon, J. Appl. Phys. 64, 6785 (1988).

- 39. H. C. Liu, J. Appl. Phys. 67, 593 (1990).

- 40. R. L. Tober, J. Pamulapati, J. E. Oh, and P. K. Bhattacharya, Appl. Phys. Lett. 53, 883 (1988).

- C.I. Huang, M. J. Paulus, C. A. Bozada, S. C. Dudley, K. R. Evans, C. E. Stutz, R. L. Jones, and M. E. Cheney, *Appl. Phys. Lett.* 51, 121 (1987).

- 42. J. Söderström and T. G. Anderson, Superlatt. Microstruct. 5, 109 (1989).

- S. Muto, T. Inata, H. Onishi, N. Yokoyama, and S. Hiyamizu, Jpn. J. Appl. Phys. 25, L577 (1986).

- 44. H. M. Yoo, S. M. Goodnick, and J. R. Arthur, Appl. Phys. Lett. 56, 84 (1990).

- 45. E. R. Brown, T. C. L. G. Sollner, C. D. Parker, W. D. Goodhue, and C. L. Chen, *Appl. Phys. Lett.* **55**, 1777 (1989).

- 46. S. K. Diamond, E. Ozbay, M. J. W. Rodwell, D. M. Bloom, Y.C. Pao, E. Wolak, and J. Harris, Jr., *IEEE Eletron Device Lett.* **10**, 104 (1989).

- 47. E. Ozbay, and D.M. Bloom, IEEE Eletron Device Lett. 12, 480 (1991).

- 48. P. Cheng and J. S. Harris, Appl. Phys. Lett. 56, 1676 (1990).

- 49. V. K. Reddy, A. J. Tso, and D. P. Neikirk, *Electron. Lett.* 26, 1742 (1990).

- 50. K. L. Lear, W. S. Lee, and J. S. Harris, IEEE Trans. Electron Devices 36, 2619 (1989).

- 51. T. Inata, S. Muto, Y. Nakata, T. Fujii, H. Ohnishi, and S. Hiyamizu, Jpn. J. Appl. Phys. 15, L983 (1986).

- 52. S. Sen, F. Capasso, A.L. Hutchinson, and A. Y. Cho, Electron. Lett. 23, 1229 (1987).

- 53. A. A. Lakhani, R. C. Potter, D. Beyea, H. H. Hier, E. Hempfling, L. Aina, and J. M. O'Connor, *Electron. Lett.* 24, 153 (1988).

- 54. T. Inata, S. Muto, Y. Nakata, T. Fujii, H. Ohnishi, and S. Hiyamizu, Jpn. J. Appl. Phys. 26, L1332 (1987).

- 55. T. P. E. Broekaert, W. Lee, and C. G. Fonstand, Appl. Phys. Lett. 53, 1545 (1988).

- 57. E. E. Mendez, W. I. Wang, E. Calleja, and C. E. T. Goncalves da Silva, Appl. Phys. Lett.

#### References

50, 1263 (1987).

- 57. A. R. Bonnefoi and T. C. McGill, Phys. Rev. B 37, 8754 (1988).

- 58. J. Söderström, E. R. Brown, C. D. Parker, L. J. Mahoney, and T. C. McGill, *Appl. Phys. Lett.* 58, 275 (1991).

- 59. E. R. Brown, "High-Speed Resonant-Tunneling Diodes", in *Heterostructures and Quantum Devices*, eds. N. G. Einspruch and W. R. Fresnley, Academic Press, San Diego, 1994.

- D. Lippens, L. De Saint Pol, R. Bouregba, P. Mounaix, and T. Vinchon, *Revue Phys. Appl.* 24, 17 (1989).

- 61. T. Mori, H. Ohnishi, K. Imamura, S. Muto, and N. Yokoyama, *Appl. Phys. Lett.* 49, 1779 (1986).

- 62. N. Yokoyama, K. Imamura, H. Ohnishi, T. Mori, S. Muto, and A. Shibatomi, *Solid-State Electronics* **31**, 577 (1988).

- 63. A. C. Seabaugh, Y.-C. Kao, J. Randall, W. Frensley, and A. Khatibzadeh, Jpn. J. Appl. Phys. 30, 921 (1991).

- 64. A. C. Seabaugh, E. A. Beam III, A. H. Taddiken, J. N.Randall, and Y.-C. Kao, *IEEE Electron Device Lett.* 14, 472 (1993).

- 65. U. K. Reddy, I. Mehdi, R. K. Mains and G.I. Haddad, Solid-State Electronics 32, 1377 (1989).

- 66. G. I. Haddad, R. K. Mains, U. K. Reddy, and J. R. East, Superlatt. Microstruct. 5, 437 (1989).

- M. A. Reed, W. R. Frensley, R. J. Matyi, J. N. Randall, and A. C. Seabaugh, *Appl. Phys. Lett.* 54, 1034 (1989).

- 68. A. C. Seabaugh, W. R. Frensley, J. N. Randall, M. A. Reed, D. L. Farrington, and R. J. Matyi, *IEEE Trans. Electron Devices* 36, 2328 (1989).

- 69. J. Genoe, Ph. D. Thesis, Leuven, 1994.

- 70. Th. G. van de Roer, "Modeling of Double Barrier Resonant Tunneling Diodes: D.C. and Noise Model", EUT Report 95-E-285, ISBN 90-6144-285-0, 1995.

- 71. A. M. P. J. Hendriks, W. Magnus, and T. G. van de Roer, *Solid-State Electronics* **39**, 703 (1996).

# 2

# **Physics of Resonant Tunneling**

## **2.1 Introduction**

In general, the specific properties of any electronic device are determined by one or several (not many) basic physical phenomena. As seen in the previous chapter the DBRT device characteristics originate in a quantum phenomenon, namely resonant tunneling. Consequently, the study and explanation of the behaviour of such devices need, at least for the active region, a quantum analysis. In this chapter main aspects of the DBRT device physics are introduced. The presentation is intended as a general picture of the actual understanding of the resonant tunneling phenomenon used in the context of a real device, which may constitute a theoretical base for the measurement interpretation and modeling from the next chapters. In this sense, first the physical principles of the DBRT are discussed from a point of view used in quantum mechanics to describe the resonant scattering phenomena [1]. This approach, usually named the Breit-Wigner formulation of DBRT, situates this phenomenon, specific for semiconductor heterostructure, in a general context and correlates the transmission probabilities with measurable physical quantities, namely the energy and life-time of the quasi-levels inside the structure and scattering times. Then, the most accessible quantity for the DBRT characterization, the current density, is introduced. At last, factors, such as band bending under bias conditions, quantum well charge storage, band nonparabolicity, scattering mechanisms, which influence the behaviour of the current density in a real DBRT device are presented and discussed.

## 2.2 Principles of Resonant Tunneling

The DBRT devices operate on physical principles that are shared by all resonant-tunneling structures. As we know the process of resonant tunneling implies the existence of metastable states in the potential barrier region. Thus, one can say that the fundamental requirement for this process to occur is quantization by spatial confinement. For the DBRT structures the presence of the quantum well between the two barriers ensures this condition. Each quasi-stationary state from the quantum well is characterized by an energy  $E_n$  and a lifetime  $\tau_n$  [1]. In the real case, when different scattering processes are involved, the condition for spatial quantization is

#### 2.2 Priniples of Resonant Tunneling

Fig. 2.1 Schematic diagram of the double barrier structure

$E_{n+1}-E_n \gg \hbar/\tau_s$  where  $\tau_s$  is the scattering time for an electron in the two dimensional subband associated with the  $n^{\text{th}}$  quasi-level. This is similar to the condition that applies to other types of quantization in solids. For example, magnetic quantization requires  $\omega_c \tau_s \gg 1$ , where  $\omega_c$  is the cyclotron angular frequency.

The spatial quantization ensures that the quasi-two dimensional states exist in the quantum well, but it does not specify the nature of the resonant tunneling that occurs through these states. The nature of the resonant tunneling is usually defined by the relative magnitudes of  $\tau_n$  and  $\tau_s$  [2, 3]. If  $\tau_n \ll \tau_s$  the resonant tunneling through the  $n^{\text{th}}$  state is said coherent, since under this condition the electron does not scatter during the process and thus the phase of the wave function at each point in space is continuous in time. If  $\tau_n \gg \tau_s$  the resonant tunneling is said to be incoherent, or sequential. In this case the wave function phase is partially randomized by the scattering events that occur in the double barrier structure.

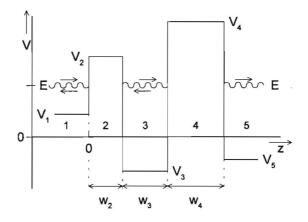

The basic principles of resonant tunneling are readily illustrated if one neglects both the complicating effects of compositional grading in the heterojunction and the electrostatic band bending. This means that we assume that the heterojunctions of the double barrier structure are perfectly abrupt and no externally voltage is applied. Such a situation is shown in Fig. 2.1. The potential energy difference, or band offset  $V_B$ , at the interfaces is some fraction of the difference in the bandgaps between the two materials. For thin barriers the band gaps for both quantum well and barrier materials are usually taken at the minimum  $\Gamma$ -point of the Brillouin zone [4].

#### 2.2.1 Electronic States in a Double Barrier Structure

The energies corresponding to the quasi-stationary states of the DBRT structure shown in Fig. 2.1 can be found based on the description of similar kind of states given in [1]. Within this description an electron placed in the well, in a quasi-stationary state moves inside the well for a considerable period of time  $\tau_n$  called the lifetime of the almost stationary state. The energy of this

#### 2 Physics of Resonant Tunneling

state is not discrete but broadened, whose "width" is related to the lifetime by  $\Gamma_n \sim \hbar/\tau_n$ (uncertainty principle for energy). In this conditions we have to look for solutions of the Schrödinger equation which represent outgoing waves outside the barrier region (at infinity). This corresponds to an electron finally leaving the quantum well by tunneling. Solving Schrödinger equation with such boundary conditions, a set of complex values of the energy are obtained, which can be written in the form  $\overline{E_n} = E_n - i\Gamma_n / 2$ . The physical significance of the complex energy values is in connection with the limited time spent by the electron inside the quantum well during the tunneling process. If we write the time factor of the wave function of the quasistationary state in the form  $e^{-(i/\hbar)\overline{E_n}t} = e^{-(i/\hbar)E_nt}e^{-[\Gamma_n/(2\hbar)]t}$ , then the probability of finding the electron "inside the system" (quantum well) decreases with time as  $e^{-(\Gamma_n/\hbar)t}$ . Thus  $\Gamma_n$  determines the lifetime  $\tau_n$  of the state.

In our case, we consider that the electron wave functions are solutions of the one-dimensional effective-mass Schrödinger equation [5, 6]:

$$\left[-\frac{\hbar^2}{2}\frac{\partial}{\partial z}\frac{1}{m^*(z)}\frac{\partial}{\partial z}+V(z)\right]\psi(z)=E\psi(z)$$

(2.1)

where  $\psi(z)$  is the envelope function,  $m^*(z)$  is the effective mass of the electron and V(z) is the potential energy at the conduction band minimum. As shown in Fig. 2.1, the origin of the coordinates z = 0 is taken as the centre of the quantum well and the structure is symmetric, V(z) = V(-z) and  $m^*(z) = m^*(-z)$ . We can restrict ourselves to the half-space z > 0 and consider for the quantum well the even eigenfunction. In this situation the wave functions for the different regions of the structure can be written as:

$$\psi(z) = \begin{cases} A\cos(\bar{k}z) & 0 < z < \frac{L_{W}}{2} \\ B\exp(\bar{\alpha}z) + C\exp(-\bar{\alpha}z) & \frac{L_{W}}{2} < z < \frac{L_{W}}{2} + L_{B} \\ D\exp(i\bar{k}z) & z > \frac{L_{W}}{2} + L_{B} \end{cases}$$

(2.2)

where

$$\overline{k} = \left(\frac{2m_{W}^{*}}{\hbar^{2}}\overline{E}\right)^{1/2},$$

and

$$\overline{\alpha} = \left[\frac{2m_B^*}{\hbar^2} \left(V_B - \overline{E}\right)\right]^{1/2},$$

are the wave vector in the quantum well and cladding layer regions and the barrier attenuation coefficient, respectively,  $m_{W}^{*}$  and  $m_{B}^{*}$  denote the corresponding electron effective masses, and  $L_{W}$  and  $L_{B}$  represent the quantum well and barrier widths, respectively. The energy  $\overline{E}$  as well as the wave vector  $\overline{k}$  and the attenuation coefficient  $\overline{\alpha}$  are complex.

In the effective-mass approximation the boundary conditions at the interfaces between different regions are: the continuity of  $\psi(z)$  and  $(1/m^*)d\psi/dz$  [5]. These connection rules express

#### 2.2 Priniples of Resonant Tunneling

the conservation of the probability density and current. Using the boudary conditions at  $z = L_W/2$  and  $z = L_W/2 + L_B$  we obtain a system of four homogenous equations for the constants *A*, *B*, *C* and *D*. These equations will have a nontrivial solution if we require the determinant of the coefficient matrix to vanish. This condition gives the following equation for the allowed wave vectors:

$$\left[\tan\left(\frac{\bar{k}L_{W}}{2}\right) + \bar{\gamma}\right][i + \bar{\gamma}]\exp(-2\bar{\alpha}L_{B}) = \left[\tan\left(\frac{\bar{k}L_{W}}{2}\right) - \bar{\gamma}\right][i - \bar{\gamma}], \quad (2.3)$$

where  $\overline{\gamma} = \frac{m_W^* \overline{\alpha}}{m_B^* \overline{k}}$ .

We recognize in (2.3) a transcendental equation, whose general solution requires numerical techniques. The roots  $\overline{k_n}$  have negative imaginary parts and the magnitudes of both real and imaginary parts increase with *n*. For each  $\overline{k_n}$  one can calculate the corresponding complex energy  $\overline{E_n}$  and extract from this the real energy,  $E_n = (\hbar^2 / 2m_W^*) \operatorname{Re}(\overline{k_n}^2)$  and the width,  $\Gamma_n = -(\hbar^2 / m_W^*) \operatorname{Im}(\overline{k_n}^2)$  of the resonant level.

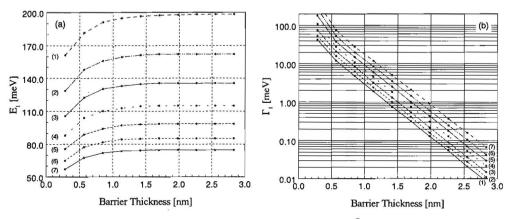

Fig. 2.2 shows the solution associated with the ground state for a number of GaAs-AlAs double barrier structures. It can be seen that for each case the real part  $E_1$  of the solution approaches the asymptotic value  $E_1^{\infty}$  for  $L_{\beta} \gg 1.5$  nm. The imaginary part  $\Gamma_1$  is exponential over the same range of  $L_{\beta}$ . From both curves it is possible thus to establish the cross-over from "thinbarrier" to "thick-barrier" behaviour. In the "thick-barrier" limit, when  $\alpha L_{\beta} \gg 1$ , with  $\alpha = \operatorname{Re} \overline{\alpha}$ , Eq. (2.3) reduces to the familiar bound-state eigen-value equation for an isolated quantum well, given as example in any quantum mechanics textbook,  $\tan(kL_w/2) = m_w^*\alpha/(m_{\beta}^*k)$ , where  $k = \left[(2m_w^*/\hbar^2)E\right]^{1/2}$  and  $\alpha = \left[(2m_{\beta}^*/\hbar^2)(V_{\beta}-E)\right]^{1/2}$ .

Fig. 2.2 (a) Quasi-bound-state energy  $E_1$  (real part of the complex energy  $\bar{E}_1$ ) in a GaAs quantum well as a function of the AlAs barrier thickness with quantum well width (integral number of monolayers ML of GaAs lattice at room temperature, ML = 0.565/2 nm) as a parameter: (1)  $L_W = 12$  ML, (2)  $L_W = 14$  ML, (3)  $L_W = 16$  ML, (4)  $L_W = 18$  ML, (5)  $L_W = 20$  ML, (6)  $L_W = 22$  ML, (7)  $L_W = 24$  ML. Each point on a curve represents an integral number of ML of AlAs lattice at room temperature (ML = 0.566/2 nm). (b) Quasibound state width  $\Gamma_1$  (imaginary part of the complex energy  $\bar{E}_1$ ) for the same parameters as in (a) [38].

#### 2.2.2 Coherent Resonant Tunneling

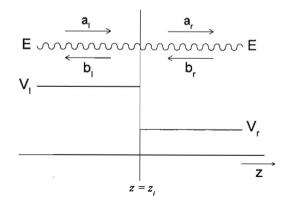

The interaction of the electron with the double barrier structure during the resonant tunneling process is described entirely by the transmission probability T(E). This quantity is the ratio of the outgoing probability current density on one side of the structure to the incoming probability current density on the opposite side. Within the effective-mass model T(E) is found assuming the same trial envelope functions as in the case of the quasi-bound states except that one cladding layer has an inward-going wave in addition to the outward wave. The most handy way to solve for T(E), under these conditions, is by considering the transmission (T) matrix approach. Appropriate for multiple heterostructures the procedure consists, in principal, in the following: for each interface of the structure, using the specific boundary conditions, the amplitudes of the waves on both sides are related to each other by a T-matrix; after this the T-matrix of the whole structure, defined in the same way, is obtained as a product of the previous elementary matrices; finally the transmission and reflection probabilities can be calculated using the elements of the total T-matrix. In the Appendix A, section A.1, T(E) is calculated in this way for a general double barrier structure, with the assumption of a piecewise constant potential. The result is:

$$T = \frac{T_{B_1} T_{B_2}}{1 + R_{B_1} R_{B_2} - 2\sqrt{R_{B_1} R_{B_2}} \cos\phi}$$

(2.4)

where  $T_{B_1,B_2}$  and  $R_{B_1,B_2}$  are the transmission and reflection probabilities, respectively, of the two barriers, and  $\phi$  is a phase angle.

The transmission probability has the same form as the optical transmission of a Fabry-Perot resonator, with sharp peaks at longitudinal energies corresponding to each quasi-bound level in the quantum well. Physically the behaviour of T(E) is the result of interference of the coherent electron wave function with itself, in the quantum well, by way of multiple reflections off the two barriers. For off-resonance energies the interference is destructive and the T(E) is very small, but for energies equal to the quantum well quasi-levels the interference is constructive resulting in the cancellation of the reflected wave outside the structure and enhancing of the transmitted one.

During resonant tunneling through a double barrier structure the electrons reside in one of the decaying quasi-stable states of the quantum well. This suggests that the process also can be described in the frame of the quantum scattering theory [1]. In such an approach at energies near the resonances the transmission probability T(E) can be expressed in the Breit-Wigner form permitting a direct correlation of the life time of the quasi-bound states,  $\tau_n$  with the full energetic width at half maximum of the transmission probability,  $\Gamma_n$  ( $\tau_n = \hbar/\Gamma_n$ ).

It can be shown that the transmission probability obtained using T-matrix formalism is reduced to the Breit-Wigner form at energies near the resonances [7]. This derivation offers an interesting insight into the physics of resonant tunneling and confirms the success of a Breit-Wigner formulation of the process [8]. Following [7], we establish this correspondence for the simple case of the symmetric double barrier structure (see Fig. 2.1).

The transmission probability T(E) is proportional with the square modulus of the transmission coefficient t(E) (see Appendix A, section A.1), which represents the ratio between the amplitude of the transmitted and incident wave. The transmission coefficient for a double barrier structure can be written as (see Appendix A, section A.1):

#### 2.2 Priniples of Resonant Tunneling

$$t(E) = \left[ M_{11}^{B_1} M_{11}^{B_2} + M_{12}^{B_1} M_{21}^{B_2} \right]^{-1},$$

(2.5)

where  $M_{11}^{B_1,B_2}, M_{12}^{B_1}$  and  $M_{21}^{B_2}$  are elements of the T-matrices corresponding to the two barriers. Making explicit the matrix elements, the above expression can be worked out and the transmission coeficient put in the following form (see Appendix A, sectionA.2):

$$t(E) = \left\{ \mathcal{Q} \frac{1}{\gamma} (1+i\gamma)(1-\frac{i}{\gamma}) \left[ L + 2\frac{1-i\gamma}{1+i\gamma} P \exp(-2\alpha L_B) + \left(\frac{1-i\gamma}{1+i\gamma}\right)^2 N \exp(-4\alpha L_B) \right] \right\}^{-1}, (2.6)$$

where

$$Q = \frac{\exp[ik(2\alpha L_B + L_W)]\exp(2\alpha L_B)}{8},$$

$$L = (\gamma^2 - 1)\sin(kL_W) + 2\gamma\cos(kL_W),$$

$$P = (\gamma^2 + 1)\sin(kL_W),$$

$$N = (\gamma^2 - 1)\sin(kL_W) - 2\gamma\cos(kL_W),$$

(2.7)

and  $\gamma = \frac{m_W^2 \alpha}{m_*^2 k}$ ;  $\alpha$ , k,  $L_W$  have the same meaning as in the previous section. We see that each  $E = \overline{E_n^0}^{0}$  where the part in square brackets of Eq. (2.6) vanishes is a pole of t(E). Because this expression contains imaginary terms, the poles  $\overline{E_n^0}$  of t(E) generally are complex, i.e. lie off the real axis in the complex E-plane. From the foregoing section we know that the energy values corresponding to quasi-stationary states in the quantum well are also complex, so we can associate them with the complex poles  $\overline{E_n^0}$  of t(E) and write:

$$\overline{E_n^0} = E_n - i\frac{\Gamma_n}{2} \tag{2.8}$$

where again  $E_n$  and  $\Gamma_n$  are positive.

The behaviour of t(E) at real incident energies E in the vicinity of  $\overline{E_n^0}$  describes quantitatively the resonant tunneling via the quasi-stable states associated with  $\overline{E_n^0}$ . This can be conveniently determined from the behaviour of the right side of Eq.(2.6) around its poles. As shown in the Appendix A, section A.2, such an analysis gives for the transmission coefficient, at real energies E near  $E_n$ , the expression:

$$t(E) = \mp i \exp\left[-ik(2L_B + L_W)\right] \exp(-i\eta) \frac{\frac{1}{2}\Gamma_n}{E - E_n + i\frac{\Gamma_n}{2}}$$

(2.9)

where  $\eta = \operatorname{arctg} \gamma$ . Further on , the transmission probability is obtined as:

$$T(E) = |t(E)|^{2} = \frac{\left(\frac{1}{2}\Gamma_{n}\right)^{2}}{(E - E_{n})^{2} + \left(\frac{\Gamma_{n}}{2}\right)^{2}}.$$

(2.10)

#### 2 Physics of Resonant Tunneling

Eq. (2.10) shows that the transmission probability through the double barrier structure has the accepted Breit-Wigner form [9] at energies near those corresponding to resonant tunneling. Also we can clearly see that  $\Gamma_n$  represents in fact the full width at half maximum of the transmission probability. It can be calculated using the following expression (see Appendix A, section A.2):

$$\Gamma_{n} = \frac{16\hbar^{2}k\gamma^{2}\exp(-2\alpha L_{B})}{m_{W}(1+\gamma^{2})\left[(1+\gamma^{2})L_{W} + \left(1+\frac{m_{B}}{m_{W}}\gamma^{2}\right)2\alpha^{-1}\right]}_{|E=E_{n}}.$$

(2.11)

From the equivalence between the width of the quasi-bound states and the full width at half maximum of the corresponding transmission probability results the direct correlation of the life time of the quasi-bound states,  $\tau_n$ , with the latter,  $\tau_n = \hbar/\Gamma_n$ .

For a general double barrier structure as that described in the Appendix A, section A1 the transmission probability can be also expressed, near resonances, in a Breit-Wigner form [7]:

$$T = \frac{\Gamma_n^{B_1} \Gamma_n^{B_2}}{\left(E - E_n\right)^2 + \frac{\Gamma_n^2}{4}},$$

(2.12)

where  $\Gamma_n = \Gamma_n^{B_1} + \Gamma_n^{B_2}$ , and  $\Gamma_n^{B_1}$ ,  $\Gamma_n^{B_2}$  are partial widths or transparencies associated with the transmission properties of the left and right barriers, respectively. For the case of constant effective mass along the double barrier structure the partial widths are estimated using the expression [7]:

$$\Gamma_{n}^{B_{1},B_{2}} = \left[ 8 \frac{\hbar^{2} k_{W}^{2}}{m^{*}} \frac{k_{L,R} \alpha_{B_{1},B_{2}}^{2}}{(L_{W} + \alpha_{B_{1}}^{-1} + \alpha_{B_{2}}^{-1})} \frac{\exp(-2\alpha_{B_{1},B_{2}} L_{B_{1},B_{2}})}{K_{B_{1},B_{2}}} \right]_{E=E_{n}},$$

(2.13)

where  $k_W$  is the wave vector in the quantum well,  $\alpha_{B_1,B_2}$  are the attenuation coefficients in the barriers,  $k_{L,R}$  are the wave vectors in the left and right cladding layers,  $K_{B_1,B_2} = \sqrt{2m^* V_{B_1,B_2}} / \hbar$ , and  $V_{B_1,B_2}$  are the heights of the two barriers. In the WKB approximation they take the simple form  $\Gamma_n^{B_1} = \hbar v_n T_{B_1}$  [3], where  $T_{B_1}$  are the transmission probabilities through barriers and  $v_n = 2L_W / v_n$  with  $L_W$  the width of the quantum well and  $v_n$  the velocity of carrier in the well at the resonant energy  $E_n$ .

The Breit-Wigner form of the transmission probability can be used in the estimating of the traversal time  $\tau_T$  for resonant tunneling. The expression for the traversal time of an electron wave packet through a barrier within flat-band conditions is given by [10]:

$$\tau_T(E^0) = \left(\frac{D}{v_g} + \hbar \frac{d\varphi}{dE}\right)_{E^0},\tag{2.14}$$

where D is the width of the barrier,  $v_g = \hbar^{-1} dE/dk$  is the group velocity in the region surrounding the barrier,  $\varphi$  is the phase angle of the transmission coefficient, and  $E^0 = (\hbar k^0)^2 / 2m^*$ , where  $k^0$  is the centre of the wave packet at the initial time. The first term in Eq. (2.14) is the transit time, and the second term is the quantum-mechanical phase time. This expression is derived under the assumption that the transmission coefficient varies only slightly over the range E that corresponds

#### 2.2 Priniples of Resonant Tunneling

to the width of the wave packet in k space. In double barrier structures this assumption is not usually valid. The traversal time in these structures is the sum of Eq. (2.14) (with  $D = 2L_B + L_W$ ) and correction terms that depend on the shape of the wave packet [11]. For a resonant wave packet (i.e.,  $E^0 = E_n$ ) the corrections vanish, yielding:

$$\tau_{T}^{n} = \left(\frac{2L_{B} + L_{W}}{v_{g}} + \hbar \frac{\frac{\Gamma_{n}}{2}}{\left(E - E_{n}\right)^{2} + \frac{\Gamma_{n}^{2}}{4}}\right)_{E^{0} = E_{n}} = \frac{2L_{B} + L_{w}}{v_{g}} + \frac{2\hbar}{\Gamma_{n}}.$$

(2.15)

We observe that the phase-time component is just twice  $\tau_n$ , as might be expected intuitively. As an electron traverses the double barrier structure, the probability density must first increase from zero to some maximum value and than decrease back to zero. Both the increase and the decrease occur with a characteristic time  $\tau_n$ .

In double barrier structures having thin barriers, the phase time usually exceeds the transit time by a large factor. For example, a GaAs-AlAs double barrier structure having 6ML-thick barriers and 16ML-thick quantum well has  $E_1 \approx 0.14 \text{ eV}$ ,  $v_g = \hbar k_1/m^* \approx 8 \times 10^7 \text{ cm s}^{-1}$  and  $\Gamma_1 \approx 1 \text{ meV}$ . Using Eq. (2.15) these values lead to a semiclassical transit time of 10 fs and a phase time of 1.3 ps. This estimate is comparable to the traversal times determined more accurately by numerical studies of the transmission of Gaussian wave packets through double barrier structures [12, 13].

#### 2.2.3 Incoherent Resonant Tunneling

As in any physical system, inelastic scattering that occurs in the double barrier structure changes the phase of the wave function and its coherence is lost. This should have an important effect on the transmission probability, since the sharp resonances that are characteristic for typical quasi-bound levels require a multiple-pass self-interference of the wave function in the quantum well. The most common models of the effect make use of the correspondence between the resonant tunneling in double barrier structures and the general theory of collisions already pointed out for the elastic case in the previous section [3, 14, 15].

We illustrate the influence of scattering on the transmission probability for the simple case of the symmetric double barrier structure. The presence of collision phenomena inside the quantum well can be taken into account assuming that the scattering potential has a small constant imaginary part i $\Gamma_s/2$  [1, 14, 16] which "absorbs" part of the incident electron flux and causes the breakdown of the unitarity of the total coherent probability (transmission plus reflexion). The "lost electrons" into the quantum well will tunnel out, forward or backward relative to the direction of incident flux, in a separate incoherent process. The probability of each of these events is correlated with the relative transparency of the corresponding barrier. For symmetric barriers these probabilities are equal.

In this picture the coherent transmission probability  $T_{coh}$  is expressed as [14, 15]:

$$T_{coh} = \frac{\left(\frac{1}{2}\Gamma_n\right)}{\left(E - E_n\right)^2 + \left(\frac{1}{2}\Gamma_T\right)^2},$$

(2.16)

#### 2 Physics of Resonant Tunneling

where  $\Gamma_T = \Gamma_n + \Gamma_s$ . We observe that this expression for  $T_{coh}$  is similar with Eq. (2.10) for the fully coherent case in which  $\Gamma_n$  in the denominator is replaced by the larger quantity  $\Gamma_T$ .

Alongside with the  $T_{coh}$  an incoherent transmission probability  $T_{incoh}$  can be calculated [14, 15]:

$$T_{incoh} = \frac{\frac{1}{4}\Gamma_n\Gamma_s}{\left(E - E_n\right)^2 + \left(\frac{1}{2}\Gamma_T\right)^2}.$$

(2.17)

Using Eqs. (2.16) and (2.17) the total transmission probability in the presence of scattering is given by:

$$T = T_{coh} + T_{incoh} = \frac{\frac{1}{4}\Gamma_{n}\Gamma_{T}}{\left(E - E_{n}\right)^{2} + \left(\frac{1}{2}\Gamma_{T}\right)^{2}}.$$

(2.18)

In the case of a general double barrier structure the Breit-Wigner form of the total transmission probability, including different collisions, has the expression [3]:

$$T = \frac{\Gamma_n^{B_1} \Gamma_n^{B_2}}{\Gamma_n^{B_1} + \Gamma_n^{B_2}} \frac{\Gamma_T}{\left(E - E_n\right)^2 + \left(\frac{1}{2}\Gamma_T\right)^2},$$

(2.19)

where  $\Gamma_T = (\Gamma_n^{B_1} + \Gamma_n^{B_2}) + \Gamma_s$ , with  $\Gamma_n^{B_1}$  and  $\Gamma_n^{B_2}$  being the partial width from the coherent resonant tunneling.

For any finite value of  $\Gamma_s$ , a given transmission resonance is broader than in the coherent limit, and the peak value of the transmission is less than unity.  $\Gamma_s$  can be related to the scattering time through the uncertainty principle,  $\Gamma_s \approx \hbar/\tau_s$ .

The Breit-Wigner approach does not apply to processes in which the scattering occurs in quanta of energy comparable to  $E_n$  in the quantum well. One of such processes is the scattering with longitudinal optical (LO) phonons. The LO phonons shift the elastic resonance and introduce inelastic transmission side bands separated by  $\hbar\omega_{LO}$  [17,18]. The transmission peak is reduced compared to the coherent case but with no additional broadening.

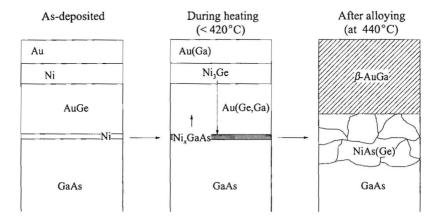

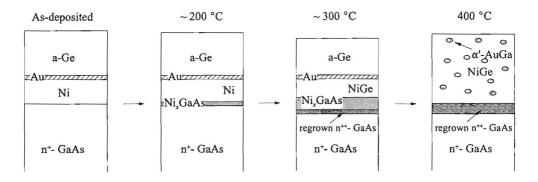

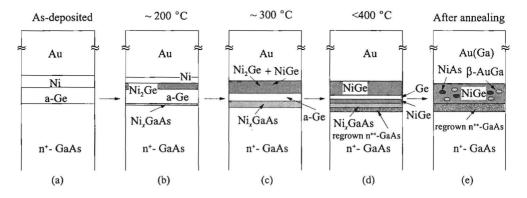

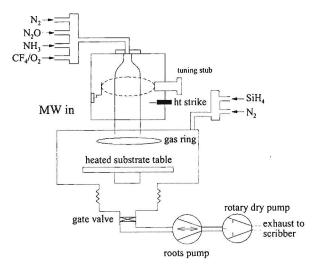

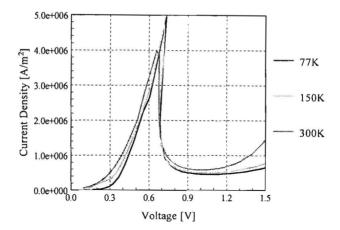

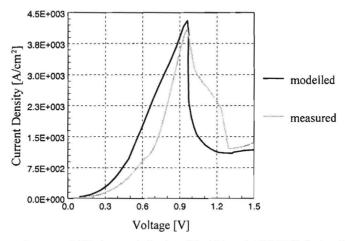

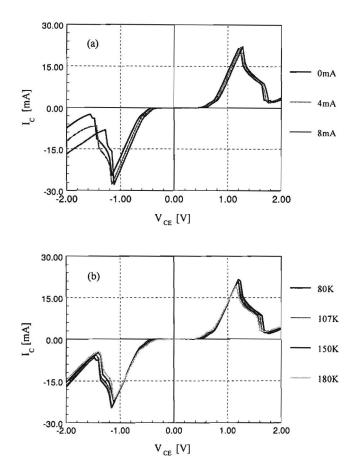

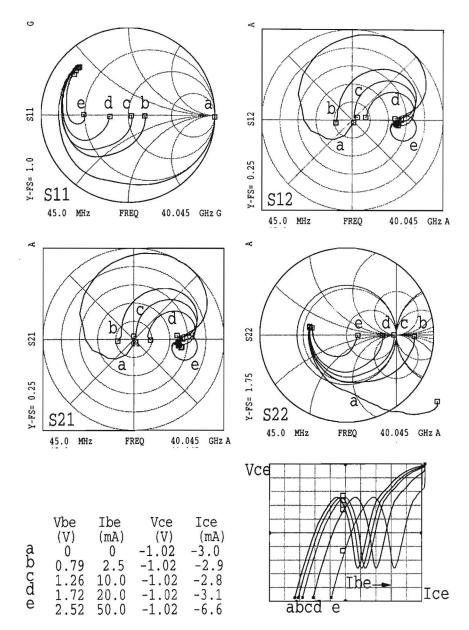

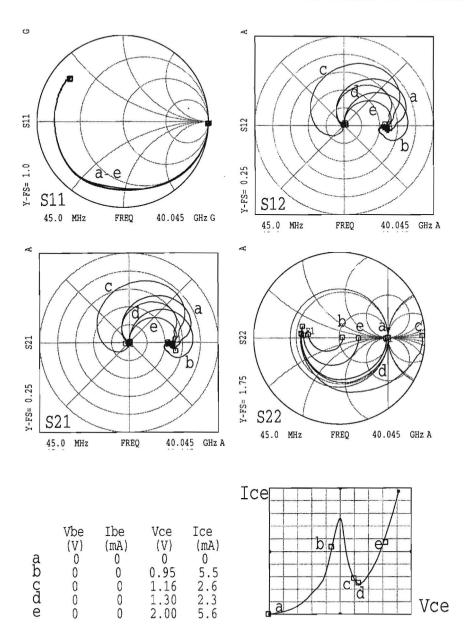

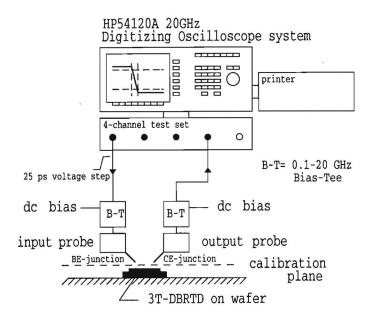

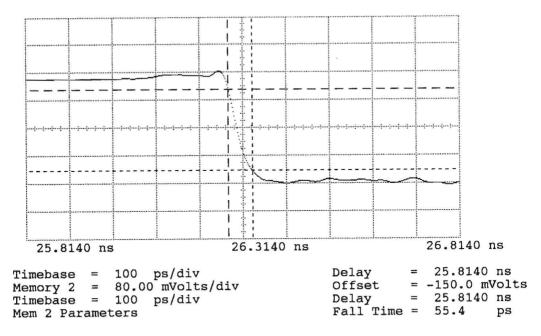

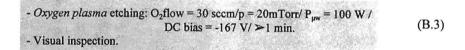

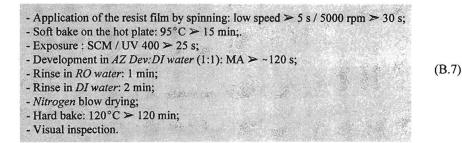

In both the Breit-Wigner and LO-phonon-mediated models the integrated transmission probability does not depend on the scattering parameter, i.e.,  $\Gamma_s$  and  $\hbar\omega_{LO}$ , respectively.