# RF-MEMS Switch Module in a $0.25~\mu m$ SiGe:C BiCMOS Process

vorgelegt von M.Sc. Mehmet Kaynak aus Antalya

von der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften Dr. -Ing.

genehmigte Dissertation

#### Promotionausschuss:

Vorsitzender: Prof. Dr.-Ing. Roland Thewes Berichter: Prof. Dr.rer.nat. Bernd Tillack

Berichter: Prof. Dr.-Ing. Hermann Schumacher

Berichter: Prof. Dr. Thomas Otto

Tag der wissenschaftlichen Aussprache: 26 February 2014

Berlin 2014 D 83 I lovingly dedicate this thesis to my beloved wife, Canan, who supported me each step of the way.

## Abstract

Wireless communication technologies have continuously advanced for both performance and frequency aspects, mainly for the frequencies up to 6 GHz. The results of Moore's law now also give the opportunity to design mm-wave circuits using advanced CMOS technologies. The introduction of SiGe into CMOS, providing high performance BiCMOS, has also enhanced both the frequency and the power performance figures. The current situation is that the active devices of both CMOS and BiCMOS technologies can provide performance figures competitive with III-V technologies while having still the advantage of low cost. However, similar competition cannot be pronounced for the passive components considering the low-resistive substrates of BiCMOS technologies. Moreover, both III-V and BiCMOS technologies have the lack of low-loss and low-power consumption, as well as highly linear switching and tuning components at mm-wave frequencies.

RF-MEMS switch technologies have been well-known with excellent RF-performance figures. The power consumption of electrostatic RF-MEMS switches is negligible and they can handle higher power levels compared to their semiconductor counterparts. However, RF-MEMS switches have been mostly demonstrated as standalone processes and have started to be used as commercial off-the-shelf (COTS) devices recently. The full system integration is typically done by a System-in-Package (SiP) approach. Although SiP is suitable for lower frequencies, the packaging parasitics limit the use of this approach for the mm-wave frequencies.

In this thesis, a fully BiCMOS embedded RF-MEMS switch for mm-wave applications is proposed. The design, the implementation and the experimental results of the switch are provided. The developed RF-MEMS switch is packaged using different packaging approaches. To actuate the RF-MEMS switch, an on-chip high voltage generation circuit is designed and characterized. The robustness and the reliability performance of the switch are also presented. Finally, the developed RF-MEMS switch is successfully demonstrated in re-configurable mm-wave circuits.

## Zusammenfassung

Drahtlose Kommunikationstechnologien im Frequenzbereich bis 6 GHz wurden in der Vergangenheit in Bezug auf Leistungsfaehigkeit und Frequenzbereich kontinuierlich verbessert. Aufgrund der Skalierung nach dem Mooreschen Gesetz koennen heutzutage mm-Wellen Schaltkreise in CMOS-Technologien hergestellt werden. Durch die Einfuehrung von SiGe zur Realisierung einer leistungsfaehigen BiCMOS-Technologie ebenfalls wurde eine Verbesserung Frequenzeigenschaften und Ausgangsleistungen erreicht, wodurch aktive CMOSoder BiCMOS-Bauelemente vergleichbare Leistungsparameter Technologien bei geringeren Kosten bereitstellen koennen. Bedingt durch das niederohmige Silizium-Substrat der BiCMOS-Technologie weisen vor allem passive Komponenten hoehere Verluste auf und weder III-V- noch BiCMOS-Technologien bieten hochlineare Schaltkomponenten mit geringen Verlusten und geringen Leistungsaufnahmen im mm-Wellen Bereich.

RF-MEMS Schalter sind bekannt fuer ihre ausgezeichneten HF-Eigenschaften. Die Leistungsaufnahme von elektrostatisch angetriebenen RF-MEMS Schaltern ist vernachlaessigbar und es koennen im Vergleich zu halbleiter-basierten Schaltern hoehere Leistungen verarbeitet werden. Nichtsdestotrotz wurden RF-MEMS Schalter hauptsaechlich als eigenstaendige Komponenten entwickelt. Zur Systemintegration wird meist ein System-in-Package (SiP) Ansatz angewandt, der fuer niedrige Frequenzen geeignet ist, aber bei mm-Wellenanwendungen durch parasitaere Verluste an seine Grenzen stoesst.

In dieser Arbeit wird ein in eine BiCMOS-Technologie integrierter RF-MEMS Schalter fuer mm-Wellen Anwendungen gezeigt. Das Design, die Integration und die experimentellen Ergebnisse sowie verschiedene Packaging-Konzepte werden beschrieben Zur Bereitstellung der hohen Auslenkungs-Spannungen wurde eine Ladungspumpe auf dem Chip integriert. Zum Schluss werden verschiedene, rekonfigurierbare mm-Wellen Schaltkreise zur Demonstration der Leistungsfaehigkeit des Schalters gezeigt.

## Acknowledgments

First and foremost, I would like to thank my supervisor, Prof. Bernd Tillack, for providing me the opportunity to work on RF-MEMS in IHP and giving me the freedom to develop my own ideas and strategy. I appreciate not only his brilliant technical support, but also support in all the other aspects of my life. I would also like to acknowledge Prof. Hermann Schumacher for his excellent technical support and exciting discussion on many different topics. I feel very lucky to be guided by these two professors both from the technical and personal aspects.

My gratitude goes to my colleague, Matthias Wietstruck, for his boundless support of RF-MEMS in IHP. His contribution to this thesis is much appreciated. I have had the pleasure to work with my very experienced colleagues Karl-Ernst Ehwald and Dieter Knoll and would like to thank them for very fruitful technical discussions. Special thanks go to Christine Richter who supports me for everything and shows me the friendly environment of IHP. I would also like to acknowledge my colleagues J. Drews, F. Koerndorfer, K. Schulz and Dr. R. Scholz for their support. Starting from the colleagues in RF-MEMS group of IHP, I appreciate the excellent support from Process Integration, Process Research, Clean Room and Electrical Characterization groups, as well as all the other colleagues in IHP. I would also like to thank my former colleagues from Sabanci University, Prof. Ibrahim Tekin and Prof. Yasar Gurbuz for their very valuable support.

A large part of my work has been carried out in the EU supported FLEXWIN and BMBF supported NANETT projects. I would like to acknowledge these projects and the partners. I especially would like to thank Dr. Volker Ziegler from EADS Innovation Works, Dr. Steffen Kurth from Fraunhofer ENAS and Katrin Kaletta from Fraunhofer IZM for their support. Finally, I would like to thank Dr. A. C. Ulusoy and Dr. G. Liu for their valuable support on the re-configurable circuit design part of the thesis. At last but not least, I would like to thank Dr. Fabio Coccetti from CNRS-LAAS for his extraordinary friendship during my studies. I feel lucky to have him both as a friend and an expert on RF-MEMS.

Finally and most importantly, I would like to express my deepest gratitude to my parents, Aysegul and Hasan Kaynak, and my wife Dr. Canan Baristiran Kaynak for continues encouragement, boundless support and unconditional love.

Mehmet Kaynak September, 2013

## **Table of Contents**

| 1 | Inti | odu   | ction                                                       | 1    |

|---|------|-------|-------------------------------------------------------------|------|

|   | 1.1  | Мо    | tivation and Objective                                      | 1    |

|   | 1.2  | SiG   | Ge BiCMOS Technologies for mm-wave ICs                      | 2    |

|   | 1.3  | RF    | -MEMS Switch Technologies                                   | 5    |

|   | 1.4  | Dis   | sertation Organization                                      | 16   |

| 2 | Tec  | hno   | logy                                                        | 17   |

|   | 2.1  | Int   | roduction                                                   | 17   |

|   | 2.2  | IHI   | P's 0.25 $\mu$ m SiGe:C BiCMOS Technologies                 | 18   |

|   | 2.3  | Str   | ess Control of the BiCMOS Metallization Layer Stack         | 20   |

|   | 2.4  | Pro   | ocess Integration of the MEMS Module                        | 22   |

|   | 2.5  | Coı   | nclusion                                                    | 26   |

| 3 | Mo   | delir | ng and Characterization                                     | 29   |

|   | 3.1  | Int   | roduction                                                   | 29   |

|   | 3.2  | Pro   | ocess Dependent Material Characterization                   | 30   |

|   | 3.2  | .1    | Extraction of Young's Modulus and Residual Stress           | 31   |

|   | 3.2  | .2    | Experimental Data: Topography Measurements                  | 37   |

|   | 3.3  | Ele   | ctromechanical Modeling                                     | 39   |

|   | 3.3  | .1    | FEM Model of the RF-MEMS Switch                             | 40   |

|   | 3.3  | .2    | Experimental Data: Low Frequency and Dynamic Measurements . | 42   |

|   | 3.4  | RF    | Modeling                                                    | 45   |

|   | 3.4  | .1    | EM Model of the RF-MEMS Switch                              | 46   |

|   | 3.4  | .2    | Experimental Data: S-Parameter Measurements                 | 58   |

|   | 3.5  | Coı   | nclusion                                                    | 60   |

| 4 | Pac  | kagi  | ing                                                         | 63   |

|   | 4 1  | Int   | roduction                                                   | . 63 |

|   | 4.2 | .2 Definition of Thermal Conditions for the Packaging Process |     |  |  |

|---|-----|---------------------------------------------------------------|-----|--|--|

|   | 4.3 | Cap-to-Wafer Packaging                                        | 69  |  |  |

|   | 4.4 | Wafer-to-Wafer Packaging                                      | 72  |  |  |

|   | 4.5 | Conclusion                                                    | 75  |  |  |

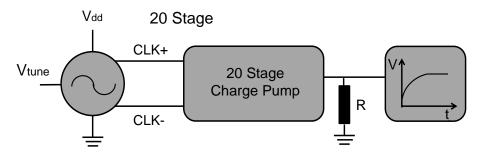

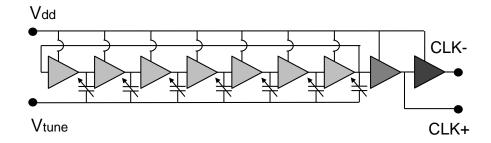

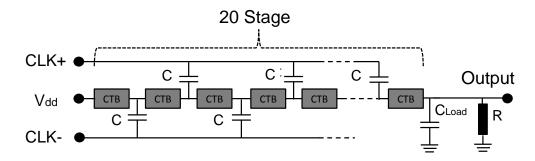

| 5 | On  | n-Chip High Voltage Generation                                | 77  |  |  |

|   | 5.1 | Introduction                                                  | 77  |  |  |

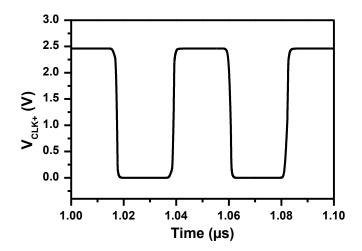

|   | 5.2 | High Voltage Generation Circuits and Sub-Blocks               | 78  |  |  |

|   | 5.3 | Simulation Results and Experimental Data                      | 81  |  |  |

|   | 5.4 | Conclusion                                                    | 86  |  |  |

| 6 | Rol | bustness and Reliability                                      | 89  |  |  |

|   | 6.1 | Introduction                                                  | 89  |  |  |

|   | 6.2 | Temperature Dependency                                        | 91  |  |  |

|   | 6.3 | Power Handling                                                | 93  |  |  |

|   | 6.3 | 3.1 Self-Actuation                                            | 93  |  |  |

|   | 6.3 | 3.2 Latching                                                  | 94  |  |  |

|   | 6.4 | Reliability                                                   | 96  |  |  |

|   | 6.5 | Conclusion.                                                   | 99  |  |  |

| 7 | Mn  | m-wave Design Examples                                        | 101 |  |  |

|   | 7.1 | Introduction                                                  | 101 |  |  |

|   | 7.2 | Passive Circuits                                              | 102 |  |  |

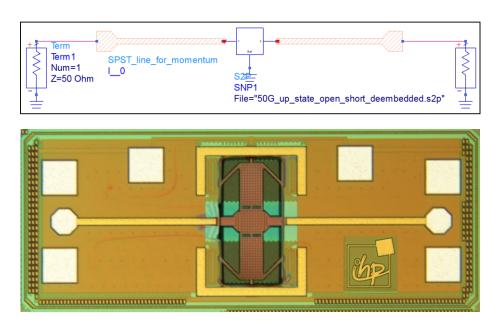

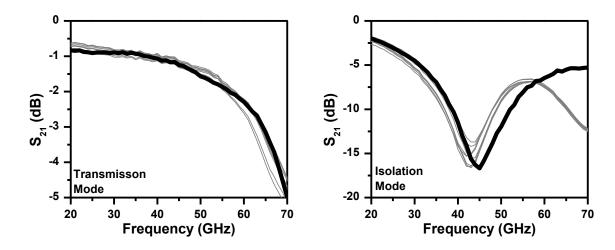

|   | 7.2 | 2.1 The Absorptive SPST                                       | 102 |  |  |

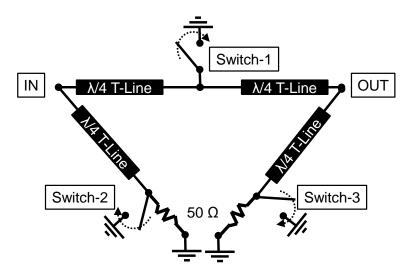

|   | 7.2 | 2.2 The SPDTs                                                 | 109 |  |  |

|   | 7.3 | Re-configurable Active Circuits                               | 110 |  |  |

|   | 7.3 | 3.1 The Dual Band mm-wave LNA                                 | 111 |  |  |

|   | 7.3 | 3.2 The Dual Band mm-wave VCO                                 | 112 |  |  |

|   | 7.4 | Conclusion                                                    | 116 |  |  |

| 8 | Cor | nclusions and Future Directions                               | 119 |  |  |

| 8.1 Ger      | neral Remarks                        | 119 |  |

|--------------|--------------------------------------|-----|--|

| 8.1.1        | Technology                           | 119 |  |

| 8.1.2        | Modeling and Characterization        | 120 |  |

| 8.1.3        | Packaging                            | 121 |  |

| 8.1.4        | On-Chip High Voltage Generation      | 122 |  |

| 8.1.5        | Robustness and Reliability           | 123 |  |

| 8.1.6        | Mm-wave Design Examples              | 125 |  |

| 8.2 Fut      | ture Directions                      | 125 |  |

| List of Abb  | previations                          | 129 |  |

| List of Figu | ıres                                 | 131 |  |

| List of Tab  | oles                                 | 139 |  |

| Bibliograph  | ny                                   | 141 |  |

| List of Pate | ents, Publications and Presentations | 151 |  |

| Patents.     |                                      | 151 |  |

| Publicati    | ons                                  | 151 |  |

| Presenta     | Presentations                        |     |  |

| Co-autho     | ored Publications                    | 155 |  |

## 1 Introduction

Chapter 1 starts with a general overview of the main motivation and the goal of the thesis. The latest developments and the state-of-the art of SiGe BiCMOS and RF-MEMS technologies are presented in sections 1.2 and 1.3, respectively. Chapter 1 is concluded with the organization of the thesis in section 1.4.

## 1.1 Motivation and Objective

During the past years, the rapid growth of the wireless communication market up to frequencies of 100 GHz and beyond has been the main driver for the development of multi-band RF front-end systems. However, RF communication and sensing systems are facing the demands of increased complexity, number of frequency bands and standards, as well as increased bandwidths and higher frequencies. The current solution of using multiple RF front-ends for different frequency bands may no longer be cost effective for the increasing number of bands. Especially when considering the increased demands on size and cost reduction, re-configurable or tunable systems are perhaps the only viable solution with respect to achieving further miniaturization and complex functionality. For such re-configurable systems, low loss, low power and highly linear switching/tuning components for building integrated adaptive RF circuits and front-ends are highly required. Nowadays, switches can be realized using different solid-state technologies, namely ferrite technologies and PIN diodes [1]. The former provide the lowest RF insertion losses but the devices are bulky and not cost effective. On the other hand, the latter provide low cost fabrication, but the insertion losses are relatively high and they consume significant power, thus are not suitable for low power or highly dense array applications.

RF-MEMS technologies are well known for their excellent RF properties, very low power consumption, wide bandwidths and IC compatibility [2]. Therefore, they are ideal components for realization of re-configurable RF circuits and systems. In addition, they are also considered as the key components to fulfill the beam steering and phase array antenna requirements of mm-wave applications [2, 3], such as imaging and sensor applications at 94, 120 and 140 GHz [4, 5]. For such high frequency

applications, a monolithic, embedded integration of the switch into a high-performance CMOS or BiCMOS platform would be advantageous over any heterogeneous integration with the basic IC process because it provides the shortest connection paths between the switch and the circuitry resulting in the lowest parasitics.

In this thesis, the main motivation is the need of the market for a high performance switching component at mm-wave frequencies. The objectives of the thesis can be summarized as follows:

- Integration of a high performance mm-wave packaged RF-MEMS switch technology into a SiGe BiCMOS process with minimum number of additional process steps and effort.

- No violation of qualified process specifications due to the additional or modified process steps of the RF-MEMS switch module.

- Electromechanical and electromagnetic (EM) optimization of the mm-wave RF-MEMS switch in order to achieve performance figures beyond state-of-the-art.

- Development of a low-loss, high throughput packaging process for the RF-MEMS switches without changing any specifications of the BiCMOS process.

- Study of the robustness and the reliability of the developed RF-MEMS switch.

- Use of the developed RF-MEMS switches in passive and active circuits.

## 1.2 SiGe BiCMOS Technologies for mm-wave ICs

Monolithic microwave integrated circuits (MMICs) have been dominated by III-V semiconductor technologies for a long time. While III-V semiconductor components continue to lead the way in terms of noise figure (NF) and maximum output power performances, an increasing number of Silicon based circuits appear in laboratories as well as in the marketplace. The introduction of the Silicon-Germanium (SiGe) Heterojunction-Bipolar-Transistor (HBT) in the late eighties was a major step. Since the BiCMOS processes can be achieved by adding only the bipolar part as a module to baseline CMOS, therefore it does not need a complete technology development. The true advantage of SiGe is the combination of SiGe HBT and CMOS, i.e. the SiGe HBT for analog/RF and ultrafast digital, CMOS for ultra-dense circuitry, memory, and certain analog primitives.

|                                | SiGe HBT |          | CMOS    |          | 400              | 90 nm                               |

|--------------------------------|----------|----------|---------|----------|------------------|-------------------------------------|

| Figure of merit                | Base     | Scaling  | Base    | Scaling  | (GFZ)            | 90 1111                             |

| f <sub>T</sub>                 | Good     | Improves | Good    | Improves | <u>5</u> 300     | SiGe BiCMOS                         |

| f <sub>MAX</sub>               | Good     | Improves | Good    | Improves | Ť                |                                     |

| NF <sub>MIN</sub>              | Good     | Improves | Good    | Improves | 250 260 200      | 0.13 μm 65 nm                       |

| 1/f noise                      | Good     | Neutral  | Neutral | Worsens  | 示 200            | <b>→</b> 0.5x                       |

| g <sub>M</sub> /g <sub>O</sub> | Good     | Improves | Poor    | Worsens  | ш <sub>450</sub> | 2.2x                                |

| g <sub>M</sub>                 | Good     | Improves | Poor    | Improves | E 150            | 0.18 μm RF CMOS 90 nm               |

| mismatch                       | Good     | Neutral  | Poor    | Worsens  | > 100            | .18 μm, 0.13 μm                     |

| linearity                      | Good     | Neutral  | Good    | Worsens  |                  | <mark>σ″</mark>                     |

| voltage headroom               | Neutral  | Neutral  | Poor    | Worsens  | nu               | 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 |

| breakdown voltage              | Good     | Neutral  | Poor    | Worsens  | U                | Relative Price                      |

Figure 1.1 The comparison of SiGe BiCMOS and CMOS processes for different performance figures (left). The relative cost comparison is also given for different technology nodes (right) [6].

Nowadays,  $f_{max}$  values of 300 GHz are commercially available, and HBTs with 500 GHz  $f_{max}$  are also provided as an early access [7]. Similar performance parameters can also be achieved by pure CMOS processes with 3 to 4 times smaller technology nodes; however, the cost of the process increases drastically. Furthermore, beyond the 90 nm technology node, the breakdown voltages rapidly decrease and the mask cost and gate leakage currents strongly increase. These limitations make BiCMOS still a powerful competitor to RFCMOS, especially for small to medium scale markets. Figure 1.1 summarizes the comparison between SiGe BiCMOS and pure CMOS technologies for base and scaling cases [6].

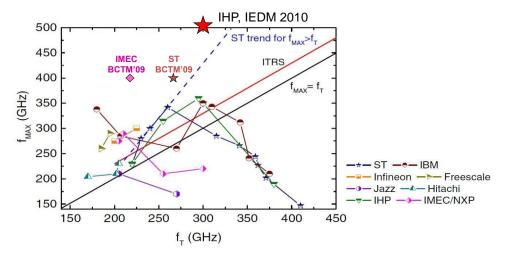

Despite the fact that there is an endless technology node improvement of pure CMOS technologies, SiGe BiCMOS technologies always find a market place due to their excellent performance parameters, such as high power handling and low noise figure. Automotive radar application at 77 GHz is now the most important market for SiGe and taking the market load from III-V technologies. Any mm-wave application over 60 GHz is also a potential market for SiGe since operation frequencies up to 600 GHz have already been demonstrated [8, 9]. However, the advantage of the higher level of integration of SiGe comes with a drawback of thermal issues since SiGe provides significant power in very small transistor footprint. The new phased array applications need several transceiver cores on a single chip; thus making the thermal management very challenging [10]. For those applications, SiGe technologies with higher  $f_{max}$  can provide significant benefit because the same performance can be achieved with much less power consumption which makes the thermal management easier. Figure 1.2 shows

the state-of-the-art SiGe technologies from different foundries [11]. 500 GHz  $f_{max}$  has been achieved by IHP in the DOTFIVE project [12, 13] and the research is still ongoing in the DOTSEVEN project which has a target  $f_{max}$  of 700 GHz [14].

Figure 1.2 The performance comparison of the state-of-the-art SiGe BiCMOS technologies provided by different foundries [11].

Increase of  $f_{max}$  has opened another potential market for SiGe BiCMOS technologies, namely the passive and active imaging systems at 94 and 140 GHz [15, 16, 17, 18]. The passive imaging systems at 94 GHz are mainly realized using InP and GaAs based technologies due to their excellent noise figure parameters. Passive imaging systems need very low noise amplifiers and noise figures of 2.5 to 3 dB can easily be achieved using these III-V technologies at these frequencies, with a drawback of high cost. However, the cost intensive III-V technologies are not the best candidates for multielement imaging systems. The increase of  $f_{max}$  values of SiGe HBTs also decreases the minimum noise figure and allows designing amplifiers with lower noise figures. The latest results show that LNAs at around 110 GHz with a noise figure of 4 dB can be achieved using a SiGe BiCMOS technology with an f<sub>max</sub> of 500 GHz [19]. Considering the additional analog/digital circuitry that can be integrated together with the LNA in BiCMOS and the potential increase of the number of elements in the system due to the lower cost per chip, SiGe technology is very promising for imaging applications at 94 and 140 GHz and can be a replacement of cost intensive III-V technologies in the near future.

As a conclusion, SiGe BiCMOS technologies are still very promising for many applications from radar to imaging systems as well as sensor applications at mm-wave frequencies. The active devices can provide very competitive performance against III-V technologies; however, this is not the case for the passive part. The low-resistive Silicon limits the quality factor of the transmission lines and inductors. Moreover, there is no real switching component in both CMOS and BiCMOS processes, especially beyond 60 GHz. Therefore, any additional module to BiCMOS which enhances the performance of the passive components or provides a switching component, can significantly improve the overall circuit and system performance. This would make the BiCMOS process more competitive against III-V or high-end CMOS technologies.

### 1.3 RF-MEMS Switch Technologies

#### - Types of Electrostatically Actuated RF-MEMS Switches

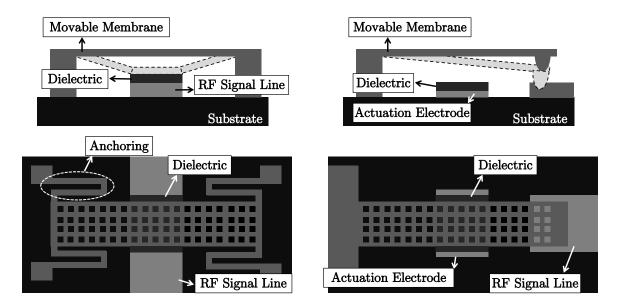

RF-MEMS switches can be summarized under two main categories considering the type of the contact; namely capacitive (Figure 1.3, left) and resistive (Figure 1.3, right).

Figure 1.3 Capacitive (left) and resistive (right) types of RF-MEMS switches.

In capacitive contact type of RF-MEMS switches, the RF signal is switched on and off by the help of low and high capacitance at the contact region. In up-state, the switch provides low capacitance which behaves like an open circuit for RF signal. However, in down state, the contact capacitance is high and it provides a series LC resonance, together with the movable membrane inductance. The most common actuation principle for the capacitive type of RF-MEMS switches is performed by applying a high voltage difference between the RF signal line and the movable membrane (Figure 1.3, left). The dielectric on top of the RF signal line is used in order to isolate the DC values of RF signal line and the movable membrane, as well as to achieve high capacitance at down-state. The typical circuit configuration to use the capacitive type of RF-MEMS switches is the shunt configuration; however, it can also be used in a series configuration.

The second type of RF-MEMS switch is the resistive type RF-MEMS switches (Figure 1.3, right). In resistive type RF-MEMS switches, the RF signal is switched on and off by having a low and high ohmic contacts. In up-state, the switch provides an open circuit between the movable membrane and the RF signal line. However, in down-state, the contact resistance is very low; thus the movable membrane and the RF signal line is shorted. The most common actuation principle for resistive type of RF-MEMS switches is the separated high voltage electrode, as given in Figure 1.3, right. The typical circuit configuration to use the resistive type RF-MEMS switch is the series configuration; however, it can also be used in a shunt configuration.

In general, the performance of the resistive type RF-MEMS switches is limited by the contact resistance, which is more significant at higher frequencies. On the other side, the down-state capacitance of the capacitive type RF-MEMS switches is the main limitation factor because in order to provide better short circuit at lower frequencies, higher capacitance values have to be achieved. Considering these facts, it can be concluded that the capacitive type RF-MEMS switches are more suitable for high frequency applications (i.e. > 40 GHz) while the resistive ones are more convenient at lower frequencies. Therefore, in this thesis capacitive type of RF-MEMS switch is chosen since the expected operating frequencies are at mm-waves frequencies.

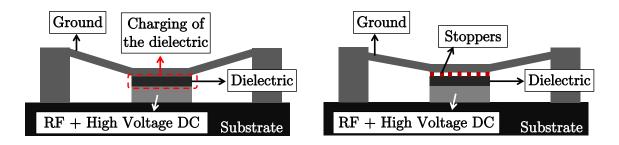

The main challenge of capacitive type RF-MEMS switches is the charging of the dielectric at the contact region. In most common approach, the high voltage is applied between the RF signal line and the movable membrane. The dielectric is charged under the applied high electric field and it causes stiction (Figure 1.4).

Figure 1.4 Charging of the dielectric in capacitive type of RF-MEMS switches (left) and method of "stoppers" to prevent stiction.

Stiction of the capacitive type RF-MEMS switches is known to be the most common failure mode. It is mainly related to the charging of the dielectric. However, many other conditions have also effect on stiction such as moisture, surface roughness or charging of the substrate. One of the common approaches to prevent stiction is using stoppers at the contact region. It apparently decreases the down-state capacitance; however, significantly minimize stiction probability due to two main reasons. Firstly, it increases the distance between the movable membrane and the RF signal line; thus decreases the force in between them at down-state. Secondly, the touching area at the contact region is smaller which reduces the stiction due to moisture. However, the charging of the dielectric still occurs and creates risk of stiction for high number of switching cycles.

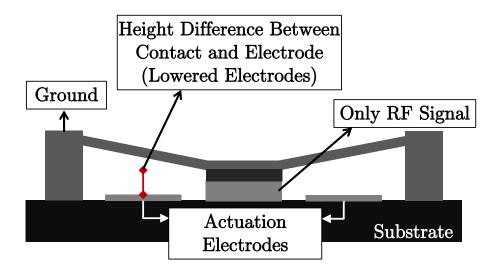

In order to achieve reliable capacitive type RF-MEMS switches, the charging of the dielectric needs to be minimized. One of the easiest methods to prevent charging of dielectric is using separated electrodes. With this technique, the applied high actuation voltage is completely isolated from the RF signal line where the contact occurs. However, the pull-in voltage of capacitive type of RF-MEMS switch, which means the minimum voltage required to move the membrane from up-state to down-state, increases. A further improvement is achieved if the actuation electrodes are placed lower elevation than the contact. In this case, the pull-in voltage again increases but the interaction between the high voltage electrodes and the movable membrane is minimized. The main bottleneck of applying these techniques is the requirement of larger area. The need of additional actuation electrodes significantly increases the required area on the chip. Figure 1.5 shows these two proposed techniques to prevent stiction. In this thesis, the configuration proposed in Figure 1.5, the capacitive type shunt RF-MEMS switch with separated and lowered electrodes is used.

Figure 1.5 The proposed RF-MEMS switch configuration for reliable operation: Capacitive type shunt RF-MEMS switch with separated and lowered actuation electrodes.

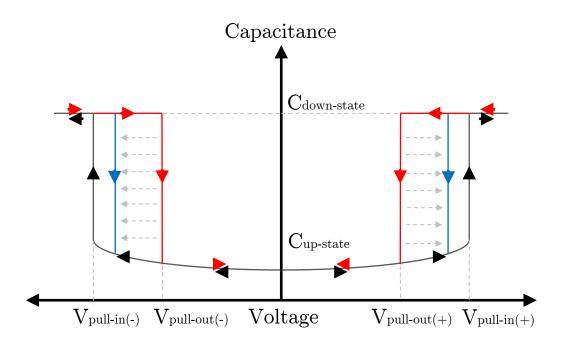

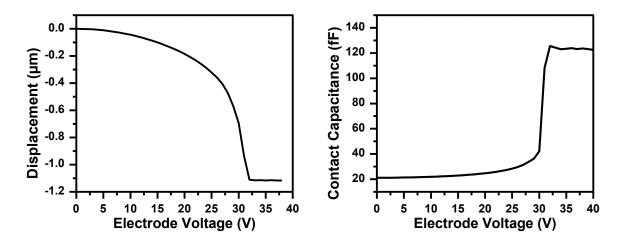

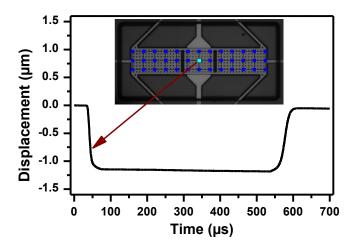

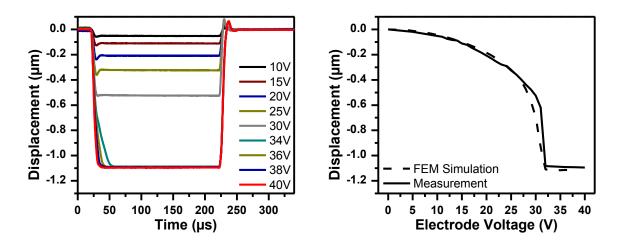

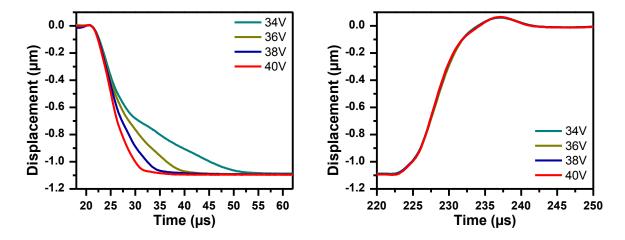

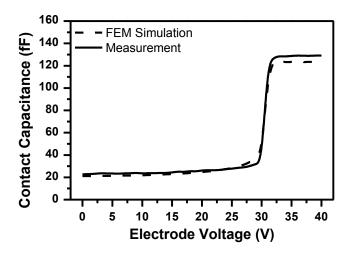

Figure 1.6 shows a typical capacitance versus voltage (C-V) curve of a capacitive type RF-MEMS switch. The switch provides an up-state capacitance ( $C_{up\text{-state}}$ ) when no electrode voltage is applied. When the voltage of actuation electrode is increased, the movable membrane starts to bend down and the contact capacitance starts to increase. After a specific voltage,  $V_{pull\text{-in}}$ , the membrane snaps down and the maximum capacitance,  $C_{down\text{-state}}$  is achieved. To release the movable membrane again, the electrode voltage is decreased and after a specific voltage,  $V_{pull\text{-out}}$ , the movable membrane releases and takes its initial up-state position. The dielectric charging phenomena can be easily observed by the help of C-V curve since the dielectric charging affects the  $V_{pull\text{-in}}$  and  $V_{pull\text{-out}}$ .

The voltage gap between the pull-in and pull-out voltages is an important parameter and strongly affected by the design of the switch. The proposed technique in this thesis (Figure 1.5) has the advantage of narrow gap between the pull-in and pull-out voltages, as can be seen by blue curve in Figure 1.6. First of all, the stiction due to the dielectric charging occurs at higher number of cycles compared to the red curve, which is a typical C-V curve of a capacitive type RF-MEMS switch. Secondly, as can be seen in Figure 1.6, the RF-MEMS switch cannot provide all the capacitances between up-state and down-state capacitances; thus cannot be used as a variable capacitor device. However, the proposed technique in this thesis provides wider range of available capacitances; hence allows the device use as a tunable capacitor.

Figure 1.6 A typical C-V curve of a capacitive type RF-MEMS switch. Red curve shows a typical release while the blue curve shows the release characteristics of the proposed technique in this thesis.

#### - Commercial RF-MEMS Switches

According to ITRS and EPoSS, RF-MEMS technologies have a crucial role for the development of tunable filters, matching networks and re-configurable transceiver ICs [20, 21]. In the US, RF-MEMS switch/tuner technologies have reached a high level of technical maturity. Companies such as Radant, WiSpry and MEMtronics are offering discrete packaged components up to 40 GHz [22, 23, 24]. Re-configurable impedance tuners enabled by RF-MEMS switched capacitors are commercialized by WiSpry for low cost, high volume antenna tuning networks in mobile phones [22]. Similar tuner products are also being developed by Cavendish Kinetics [25] and DelfMEMS [26]. Another very high performance and very reliable ohmic type of RF-MEMS switch is provided by OMRON [27].

Currently, the long-term reliability problems associated with RF-MEMS devices have been almost solved. However, packaging and reliability are still most challenging concerns for the commercialization of any new RF-MEMS device. The next section gives an overview of technology and material evaluation of capacitive type RF-MEMS switch technologies which have a significant impact on the way to commercialization.

#### - Technology and Materials Evolution of Capacitive Type RF-MEMS Switches

RF-MEMS technologies are much simpler and have a lower number of process steps than any CMOS or BiCMOS process. A state-of-the-art CMOS process can have more than 30 masks; however, most of the RF-MEMS processes have 5 to 10 masks in total only. Moreover, a typical CMOS process has 500 to 1000 process steps whereas it is below 100 for RF-MEMS. At first sight, the general impression about RF-MEMS development is quite optimistic. However, there are still many other challenges for RF-MEMS technologies that differ from CMOS processes.

CMOS processes have reached a mature and stable condition, so that the microelectronics community has already discriminated materials using the terms "CMOS compatible" and "CMOS incompatible". However, it is not the case for RF-MEMS technologies. As an example, all the aforementioned commercial RF-MEMS products use different materials, showing that there is no standard material combination providing the best performance for RF-MEMS devices.

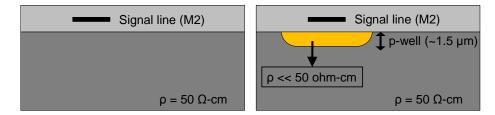

An RF-MEMS process development starts with the appropriate substrate choice. Many different materials can be used as the substrate material such as glass, ceramic, silicon or polymer. In between these materials, the most promising one is silicon due to the well-known processing techniques and the low cost. However, if the RF-MEMS process is to be integrated into a CMOS process, one of the main difficulties is the low resistivity of the silicon substrate. Different techniques have been proposed to prevent substrate losses. In [28], a simple technique of backside etching is proposed and applied in order to prevent this. Another way to diminish high substrate loss is making it more conductive and using it as a ground shield plane. It has been demonstrated by a highly doped region which can be realized using poly-silicon [29] or additional implantation steps [30]. Nevertheless, the first step before starting the process development should be the selection of the substrate with respect to the application frequency and the performance specifications.

The next important step is the selection of the MEMS processing technology. Both surface micromachining and bulk micromachining processing techniques have been successfully demonstrated in the literature. However, surface micromachining is by far the dominating one for RF-MEMS since it is the simplest way to obtain suspended membranes with small size. Bulk micromachining might be chosen if the size and the cost are not the first concerns [31, 32].

The actuation principle is a fundamental choice for RF-MEMS devices. In the literature electrostatic, piezoelectric, electrothermal and electromagnetic actuation principles have been studied. Most of the RF-MEMS switches use the electrostatic actuation principle since the required technology is simple and it provides fast switching speed as well as very low power consumption [33, 34]. Series type designs have been demonstrated in [35] up to 94 GHz by Bosch and in [36] by CNRS-IEMN using the electrostatic actuation principle.

Significant efforts have been spent to prevent dielectric charging of capacitive RF-MEMS switches and to decrease the pull-in voltage [37, 38]. One of the easiest techniques is the separation of the high voltage electrodes from the RF line to prevent the charging of the dielectric. However, results have shown that the separation of the high voltage electrodes increase the voltage requirement because the effective area for the actuation gets smaller. As a result, attempts have started to decrease the required voltage by reducing the stiffness of the membrane, as demonstrated in [39] and [40]. But, the reduced stiffness has caused reliability problems because the restoring force of the membrane also gets smaller; thus increasing the probability of stiction. These results have shown the strong trade-off between the pull-in voltage and the reliability.

On the other side, it is also shown that very stiff membranes have been affected by temperature effects. In [41], a fixed-fixed beam was demonstrated by Daimler-Chrysler but it was strongly influenced by temperature variations. A huge effort was spent on designing a stress compensated anchoring in [35, 42, 43]. In [43], a method of different thicknesses for anchoring and the membrane has also been shown with remarkable results. Consequently, an increase of the spring constant not only increases the required actuation voltage but also makes the switch more sensitive against temperature changes.

Besides complicated RF-MEMS process approaches, very simple processes have also been proposed and successfully demonstrated. In [44], curled up cantilevers have been shown with a very stable performance up to 120 °C by EADS. Actuation by using fringing electrostatic fields between the curled up fingers has been demonstrated in [45], by IMEC. Another promising approach is the application of bidirectional actuation which allows actuating the membrane from both top and bottom. By using this approach, the stiffness of the movable membrane can be decreased without any negative impact, as demonstrated in [46]; however, the process to realize such a device is relatively complex. The references [47, 48, 49, 50] can be given as examples for piezoelectric, electrothermal and electromagnetic actuation principles.

The selection of materials has also significant importance for the RF-MEMS devices. The choice for the RF signal line is relatively easy. Highly conductive metal with a thickness larger than the skin depth in the frequency range of interest can satisfy the requirements for the RF signal line. Most of the studies have been done using Al, Au or Cu. Power handling of Al and Au is limited due to electromigration, while Cu can offer higher conductivity and better electromigration stability.

The type of the dielectric material for the capacitive type of RF-MEMS switches is another important aspect since it strongly affects the unwanted charging of the dielectric during the operation. In general, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, AlN, Ta<sub>2</sub>O<sub>5</sub> and Al<sub>2</sub>O<sub>3</sub> are the materials that have been investigated as a dielectric material for capacitive type RF-MEMS switch. In addition, the type of the voltage polarity and the type of the substrate affect the charging of the dielectric, as studied in [51] and [52], respectively. Furthermore, the humidity has also effect on charging [53]. The different types of charging mechanisms have been extensively examined in [54] and [55]. Dielectric-less capacitive switches have also been proposed by [56] and [57].

Although the type of the material for the sacrificial layer looks not critical, it has a significant effect on the final reliability of the device and the yield of the process. Using photoresists as the sacrificial layer is the simplest and the cheapest technique but its dry removal leaves some residuals which degrade the performance and decrease the yield of the process. However, wet release has also some disadvantages since a CO<sub>2</sub> supercritical drying is necessary after the release process, which is a low throughput and cost intensive step. Beside photoresist, materials like silicon dioxide, poly-silicon, and copper have been also investigated as sacrificial layer. Electroplated copper is widely used by Intel [58], Teravicta [59], IBM [60] and Radant [61]. Oxides have also been used with wet and gas phase release techniques [62, 63, 64].

The last important selection is the material type of the movable membrane since it should exhibit large yield strength and low sensitivity to creep. Both oxides and metals can be used as the movable part of the switch. The simplest way is to use a metal such as Al, Au, Ni or Cu. However, using single layer metals for the membrane increases the influence of the temperature induced stress. Al alloys can provide very good mechanical properties but resistivity may increase due to the alloying [33]. As a result, the material of the movable membrane should be thick enough and have well defined stress. Thicker layers with higher conductivity have advantages both in mechanical and electrical respects. Multi-stack layers are also more robust against temperature variations if enough attention is given to the stress control.

In conclusion, there are many ways and different materials to realize RF-MEMS switches. However, the type of the process and the materials needs to be decided with respect to the specifications coming from the application. Therefore, the application has a strong effect on both selection of the materials and the process types.

#### - Integration of RF-MEMS into a CMOS/BiCMOS Platform

In the 1990s, sub-micron CMOS technologies have started to show up with limited RF performance. They provided high performance digital and logic; however, they were not fast enough for RF. The more common approach at that time was the System-in-Package (SiP) approach, which combines the best technologies for different parts of the system in a single package. SiP provided the best performance systems but the total cost and size was dominated by the packaging and integration. Starting with years 2000, the CMOS technology node has gone below 130 nm and then System-on-Chip (SoC) approach has started to be pronounced and dominated many applications. Since that time, RF front-end has still been following the digital and the logic part with the best available technology node. However, starting with 45 nm and below, the logic part of the systems has started to operate with very low V<sub>dd</sub>, which is not the best choice for RF front-ends. Furthermore, technology nodes such as 32 or 22 nm have been realized with many limitations in Back-End-off-Line (BEOL), making the RF designs more challenging. Now, heterogeneous integration is the new trend developed by chipset providers. Similar to SiP, it is again the combination of different technologies in a package/system with a very small footprint. It is almost the same approach as 20 years ago; however, the integration methods now are much more advanced which allows minimizing the overall size of the systems.

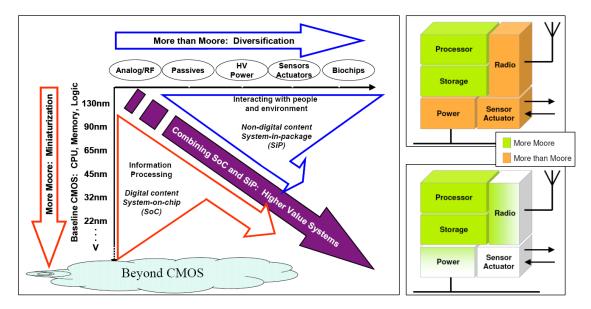

The incredible shrinking of CMOS, known as the "More Moore" approach is still the hottest and most challenging topic for the microelectronic industry, especially for the digital part of the system. On the other side, adding different functionalities to CMOS such as high voltage/power devices, sensors or actuators is known as the "More than Moore" approach. Next generation mobile systems are expected to provide not only more processing power, but also interaction with people and the environment. Following the More than Moore approach is one of the best choices to realize such smart systems together with the new heterogeneous integration platforms. Figure 1.7 shows different approaches from technology and system perspectives [20, 65].

Figure 1.7 "More Moore" and "More than Moore" approaches from the technology and system perspectives [20, 65].

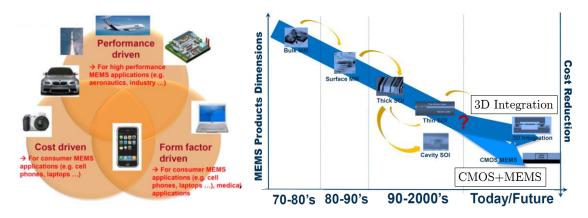

One of the main functionality modules which can be added to CMOS or BiCMOS platforms is the RF-MEMS switch module. As indicated in Figure 1.8 (left), there are three main drivers for the MEMS industry; namely the performance, cost and form factor. The type of the driver has a great importance for the process development. The decision for CMOS+MEMS integration or heterogeneous integration strongly depends on the driver type of the application; thus the size of the market. Figure 1.8 (right) shows that there should be a clear decision in terms of the integration scheme before starting the process development [66].

Figure 1.8 Main drivers of the MEMS industry (left) and the evaluation of the different processing and the integration techniques for MEMS processes [66].

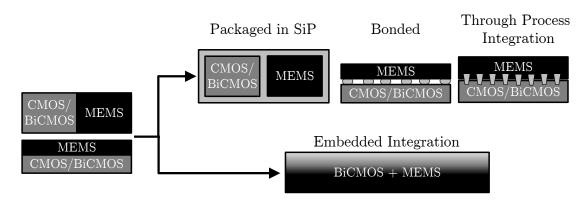

In the literature, several methods have been suggested to integrate MEMS components into semiconductor die using hybrid, monolithic, and post-processing techniques. The fabrication techniques in MEMS and semiconductor processes are similar but low throughput, difficult repeatability and low yield of MEMS processes make the combination very challenging. Moreover, the high yield requirement of CMOS processes which allows decreasing the cost are highly threatened by integrated MEMS devices. All these bottlenecks force the industry to use the heterogeneous integration techniques as an intermediate solution. In these days, chip stacking using Through-Silicon-Vias (TSVs) and interposer techniques have become popular to combine different dies together. Figure 1.9 summarizes the basic integration techniques of MEMS into a CMOS platform.

Figure 1.9 Different concepts for MEMS and IC integration.

Significant numbers of research works have been carried out to this date; however, most of them lacked real demonstration of monolithic integration of active circuits and RF-MEMS switches. So far, RF-MEMS together with active RF circuits have been realized mostly as hybrid circuits [67, 68, 69]. The X-band switched dual-path PAs and LNAs reported by the US Company Rockwell Scientific are the first real examples of a successful monolithic integration of active devices with RF-MEMS switches into a GaAs MMIC foundry process [70]. Many attempts have been also tried within the FP7 project MEMS-4-MMIC, utilizing prototype RF-MEMS switches on-chip integrated on the MMIC GaAs technology but the maturity of the developed technologies could not achieve commercialization levels [71, 72].

By using the hybrid and heterogeneous integration techniques, different products have already taken their place in the market. The interconnect losses from these integration methods are in an acceptable range for the frequencies up to 40 GHz. However, for the higher frequencies, interconnect losses become more important and define the overall system performance. Due to the significant effect of interconnect losses in interposer or chip stacking techniques, embedded integration of RF-MEMS components into the semiconductor technologies are necessary especially for mm-wave applications.

### 1.4 Dissertation Organization

In this thesis, the embedded integration of the capacitive RF-MEMS switch into a BiCMOS process is proposed for mm-wave applications. The fully embedded nature of integration helps to minimize the parasitic losses at mm-wave frequencies. Throughout the thesis, process integration, device simulation and characterization are described. Furthermore, packaging of the RF-MEMS switch, on-chip high voltage generation, robustness and reliability tests are also studied. Lastly, the developed module is demonstrated with different passive and active mm-wave circuit examples.

The thesis is organized as follows: In Chapter 2, the general introduction to technology is given and process integration of the RF-MEMS switch is detailed. In Chapter 3, the RF-MEMS switch modeling and characterization is studied with the experimental results and the performance figures. The requirements of the packaging process and two different packaging approaches are described in Chapter 4. In Chapter 5, the on-chip high voltage generation circuit design and the results are given. The robustness and reliability of the RF-MEMS switch is studied in Chapter 6. Finally, different circuit demonstrations realized by using the developed RF-MEMS switch are described in Chapter 7 and the thesis is concluded in Chapter 8 with general remarks and future directions.

## 2 Technology

#### 2.1 Introduction

RF-MEMS switch development requires stable process conditions. As extensively studied in Chapter 1, the demonstration of RF-MEMS devices is a big step, but considering the whole value chain, there is still much remaining work to replace any electronic component with an RF-MEMS counterpart. It should be emphasized that the first and the most important step is to have a stable process condition. Therefore, CMOS/BiCMOS processes can be very good candidates as a platform for RF-MEMS devices, since these processes are very mature and exhibit good yield. The only open point is the cost of these technology platforms, since CMOS cost drops sharply only if it is in mass production, i.e. > 10 M units per year due to the high mask costs.

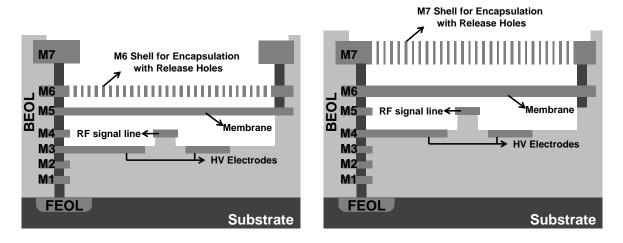

Currently, monolithic integration of an RF-MEMS device into a BiCMOS platform is done in two different ways: above-IC technique and BEOL integration. Both techniques have some advantages and limitations. In this thesis, the BEOL integration is chosen in order to minimize the parasitics and the cost of the fabrication

There is an obvious advantage of using CMOS platforms to build RF-MEMS devices but there are also some limitations. These platforms are optimized in order to increase the yield of the CMOS devices. Therefore, even the smallest change can degrade the yield. Most of the RF-MEMS devices can be built using the available metals and other layers of CMOS process, but the main limitation is the residual stress of these layers. In CMOS processes, the stress levels are optimized in order to compensate the complete stress of the full stack, including FEOL and BEOL. This is a physical limitation for RF-MEMS devices because they need suspended parts with low residual stress. Therefore, the main challenge is not only building an RF-MEMS device in CMOS but also keeping the CMOS process qualified maintaining high yield.

Chapter 2 provides a general overview of the used BiCMOS technology and the stress characterization of metallization layers in BEOL. It starts with a brief introduction of IHP's different technologies in 0.25 µm node in section 2.2. The stress control of the metal stacks and the integration scheme of the RF-MEMS switch into the BEOL of the BiCMOS process are given in sections 2.3 and 2.4, respectively. In

addition to the process flow of the MEMS module, the formation of the contact of the RF-MEMS switch is also given in section 2.4. Chapter 2 is concluded with some achievements and general remarks in section 2.5.

## 2.2 IHP's 0.25 $\mu$ m SiGe:C BiCMOS Technologies

The integration of the RF-MEMS switch has been done into the 0.25  $\mu m$  BiCMOS node. IHP's 0.25  $\mu m$  node has three main BiCMOS technologies, namely SGB25V, SG25H3 and SG25H1. SGB25V is the basic low cost technology and includes 3 different HBTs with maximum  $f_{max}$  of 95 GHz. SG25H3 technology offers HBTs with an  $f_{max}$  of up to 180 GHz while the highest performance SG25H1 offers HBTs with  $f_{max}$  values of 220 GHz. Table 2.1 summarizes the main performance parameters of the HBT transistors for the different 0.25  $\mu m$  technologies [7].

Table 2.1 Performance parameters of HBT transistors for different 0.25  $\mu m$  technologies of IHP [7].

| ${ m SGB25V}$                                          |                       |          |              |  |  |

|--------------------------------------------------------|-----------------------|----------|--------------|--|--|

|                                                        | High Performance      | Standard | High Voltage |  |  |

| $ m f_{max}~(GHz)$                                     | 95                    | 90       | 70           |  |  |

| $f_{t}$ (GHz)                                          | 75                    | 45       | 25           |  |  |

| BV <sub>CEO</sub> (V)                                  | 2.4                   | 4        | 7            |  |  |

|                                                        | $\operatorname{SG25}$ | 5H3      |              |  |  |

|                                                        | High Performance      | Standard | High Voltage |  |  |

| $ m f_{max}~(GHz)$                                     | 180                   | 140      | 80           |  |  |

| $f_{t}$ (GHz)                                          | 110                   | 45       | 30           |  |  |

| $\mathrm{BV}_{\mathrm{CEO}} \left( \mathrm{V} \right)$ | 7) 2.3 5              |          | 7            |  |  |

| SG25H1                                                 |                       |          |              |  |  |

|                                                        | High Per              | Standard |              |  |  |

| $ m f_{max}~(GHz)$                                     | 22                    | 190      |              |  |  |

| $f_{_{ m t}} \ ({ m GHz})$                             | 180                   |          | 190          |  |  |

| $BV_{CEO}(V)$                                          | 1.                    | 1.9      |              |  |  |

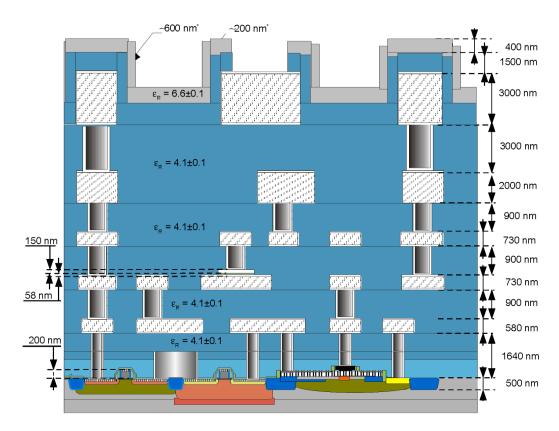

All 0.25  $\mu$ m BiCMOS technologies have 5 aluminum metallization layers in BEOL. Three thin metallization layers for digital signal routing and two thick metals with thicknesses of 2  $\mu$ m and 3  $\mu$ m for high-Q passive components are offered. A metalinsulator-metal (MIM) type of capacitor is also available between Metal2 (M2) and Metal3 (M3). The thin Si<sub>3</sub>N<sub>4</sub> dielectric layer with an approximate thickness of 55 nm is placed between M2 and M3 in order to achieve a high capacitance density of ~1.15 fF/ $\mu$ m<sup>2</sup>. All the available passive components and their performance parameters are given in Table 2.2.

Table 2.2 Performance parameters of different passive components in 0.25  $\mu m$  technologies offered by IHP [7].

| Passives                           |           |           |  |  |

|------------------------------------|-----------|-----------|--|--|

|                                    | SG25H1/H3 | SGB25V    |  |  |

| MIM Capacitor (fF/µm²)             | 1.15      | 1.15      |  |  |

| N+ Poly Resistor $(\Omega/\Box)$   | 210       | 210       |  |  |

| P+ Poly Resistor $(\Omega/\Box)$   | 280       | 310       |  |  |

| High Poly Resistor $(\Omega/\Box)$ | 1600      | 2000      |  |  |

| $ m Varactor~(C_{max}/C_{min})$    | 3         | 3         |  |  |

| Inductor Q @ 5 GHz                 | 18 (1 nH) | 18 (1 nH) |  |  |

SG25H1 and SG25H3 technologies offer the same BEOL while SGB25V technology has a slightly different BEOL than the others in terms of the metallization and the SiO<sub>2</sub> thicknesses. SG25H1 and SG25H3 technologies are chosen for the integration of RF-MEMS switch module considering the expected high frequency performance of the RF-MEMS switches because these two technologies can provide mm-wave circuits up to 100 GHz and above.

The cross section of the BEOL of the SG25H1/H3 technologies is seen in Figure 2.1. All the aluminum metallization layers are covered by TiN/Ti layers from both top and bottom sides as a barrier layer between the aluminum and  $SiO_2$ . The connection vias between different metallization layers are filled with tungsten and are isolated from the  $SiO_2$  by TiN. The  $SiO_2$  dielectric layer is used to isolate the metallization layers. The top passivation layer includes 1.5  $\mu$ m  $SiO_2$  and 400 nm  $Si_3N_4$ . The approximate thickness values of each layer are also indicated in Figure 2.1 [73].

Figure 2.1 Generic cross-section view of SG25H1/H3 BEOL [73].

## 2.3 Stress Control of the BiCMOS Metallization Layer Stack

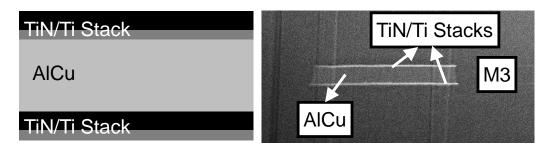

Multi-layer processes, such as BiCMOS, are optimized to control the total stress of the entire BEOL and FEOL layers. The stress in aluminum metallization layers is generally tensile which makes it challenging to be used for RF-MEMS applications. Although certain designs may benefit from such stress effects [74], uniformity over the wafer, reliability and repeatability remain problematic in case of such high residual stresses and prevent easy commercialization of RF-MEMS devices. Mechanical, electrical and RF performance parameters of an RF-MEMS switch are influenced by the residual stress of the movable membrane as well. Furthermore, the residual stress of the membrane has to be well controlled in order to have repeatable and reliable structures. Figure 2.2 shows the cross section of the M3 stack of the SG25H1/H3 BEOL.

Figure 2.2 Generic cross-section (left) and FIB cut (right) of the M3 layer in SG25H1/H3 BEOL.

${

m TiN/Ti}$  stacks are mainly used as barrier layer between aluminum and the  ${

m SiO_2}$  layers. The  ${

m TiN/Ti}$  stacks, with an effective Young's modulus of ~410 GPa, are much tougher than aluminum, therefore the total stress characteristics of the whole  ${

m TiN/Ti/AlCu/TiN/Ti}$  stack can be controlled by the  ${

m TiN/Ti}$  stacks. In this thesis, the bottom  ${

m TiN/Ti}$  stack is selected to control the overall stress gradient of M3.

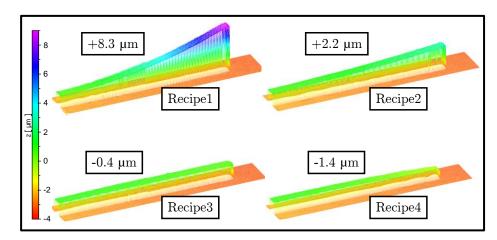

Figure 2.3 shows the measurements of four different cantilevers fixed from one side. The cantilevers were fabricated using 4 different recipes. The recipes are developed by changing the deposition conditions and the thickness of the TiN and Ti layers. The bending of the cantilevers was characterized by a White-Light Interferometer (WLI) in order to determine the type of the stress gradient. The numbers in each picture show the bending of the tip of the cantilever in z direction.

Figure 2.3 WLI measurements of 4 different cantilevers using four different recipes for the bottom TiN/Ti stack. The numbers in every picture show the bending of the tip of cantilever in z direction.

As seen in Figure 2.3, the stress gradient of the whole M3 stack can be controlled from tensile to compressive by using different recipes of bottom TiN/Ti stack. Note that the recipes used do not cause any violation of the original M3 process specifications, such as sheet resistance (Figure 2.4). In this work, Recipe3 was chosen to improve the reliability of the switch by decreasing the contact area when the switch is in the down-state. The preferred stress characteristic for improved reliability decreases the down-state capacitance. This is extensively studied in Chapter 3 by simulations and measurements.

### 2.4 Process Integration of the MEMS Module

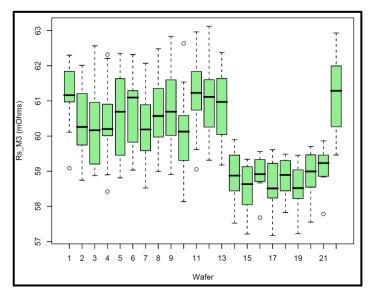

The RF-MEMS module integration starts after finalizing the BiCMOS process. As explained in the previous section, the BiCMOS process is finished with only a small modification of the M3 deposition recipe. This small change of the recipe slightly decreases the sheet resistance of M3. However, it should be noted that the achieved sheet resistance value is still in the specification limits of the process. Figure 2.4 shows the sheet resistance values of a production lot which has wafers for both Multi-Project-Wafer (MPW) production and MEMS process development.

Figure 2.4 Sheet resistance variation of M3 for different wafers in a lot. Wafers 1 to 13 and 24 are processed with standard recipe while wafers 14 to 21 are with Recipe3.

The wafers numbered from 1 to 13 and 24 are for MPW production and the standard M3 deposition recipe was used. The wafers numbered from 14 to 21 are the MEMS process wafers which use the special developed recipe for the stress control of M3. In Figure 2.4, it can be clearly seen that the sheet resistance of the MEMS wafers are slightly lower than for the MPW production wafers. However, the process specifications define the minimum sheet resistance for M3 to be 40 m $\Omega$ , and the maximum 70 m $\Omega$ . Therefore, it can be concluded that the small change of the M3 recipe does not significantly affect the M3 sheet resistance and the requirements of the process specifications are still fulfilled. Figure 2.5 shows the additional MEMS process flow to the BiCMOS process.

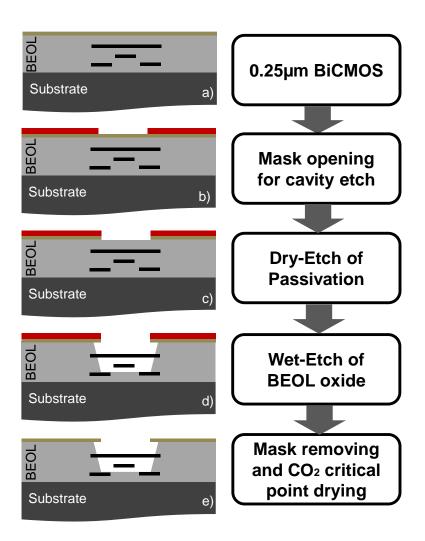

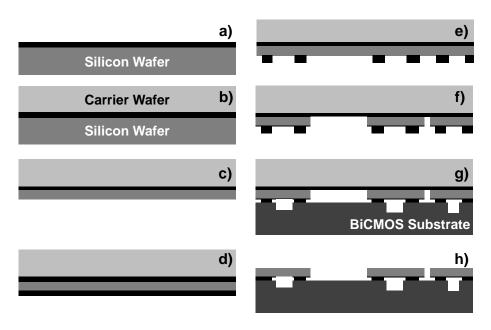

Figure 2.5 The complete process flow of RF-MEMS module added to 0.25  $\mu m$  BiCMOS technology [75].

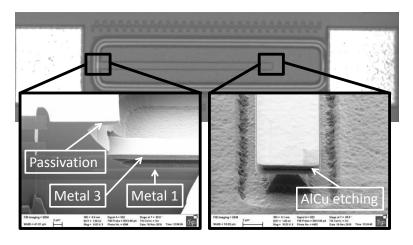

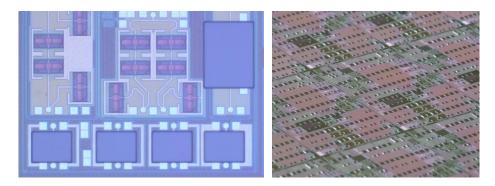

After finalizing the BiCMOS process (Figure 2.5a), a lithography step (Figure 2.5b) is followed by an RIE process step to remove the passivation of the RF-MEMS switch cavities (Figure 2.5c). This step also helps to decrease the time required for the wet etch release. After the dry etching of the passivation layer, the BEOL oxide is etched down to M1 using 10 % buffered HF solution (Figure 2.5d). The solution is mixed with glycerol in order to increase the selectivity to AlCu which helps to minimize the AlCu under-etch of M3. The wafer is cleaned and rinsed after the wet-etch. Finally, the CO<sub>2</sub> critical point drying step is applied to prevent unwanted stiction of the MEMS devices after the suspended membranes are released (Figure 2.5e). The process flow of the MEMS module integration adds only one extra mask to the BiCMOS flow [75]. The RF-MEMS module embedded in the BiCMOS process is completed on 200 mm (8-inch) wafer level.

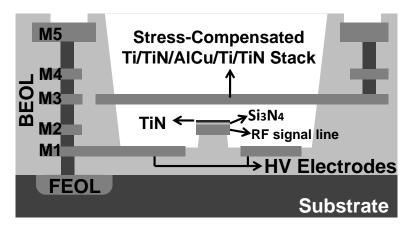

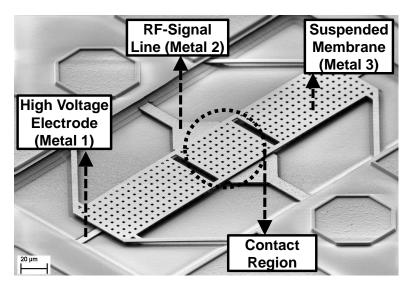

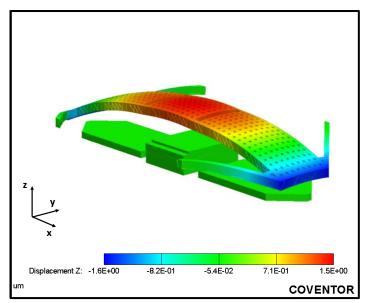

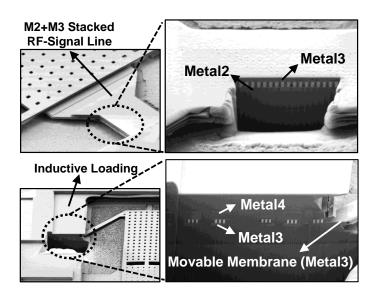

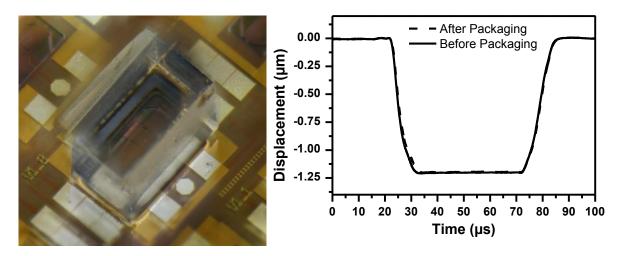

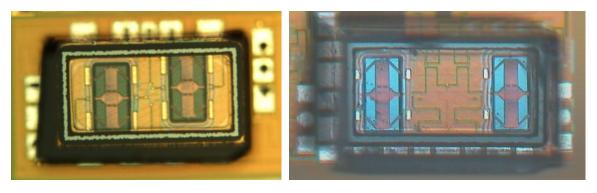

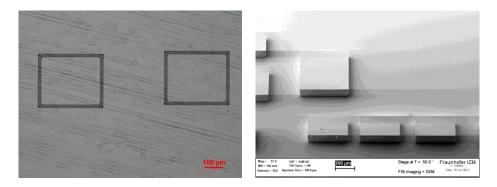

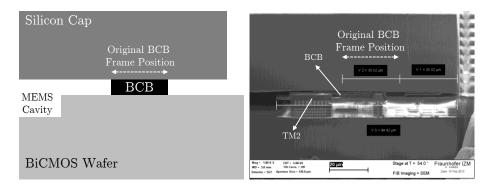

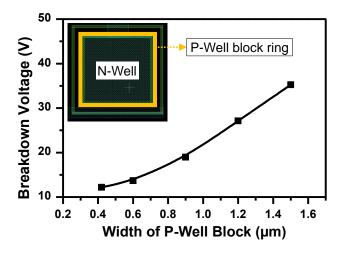

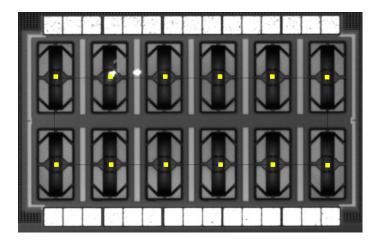

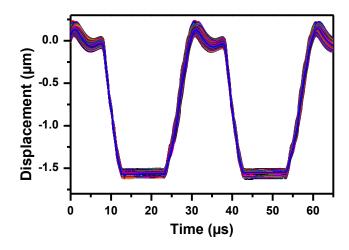

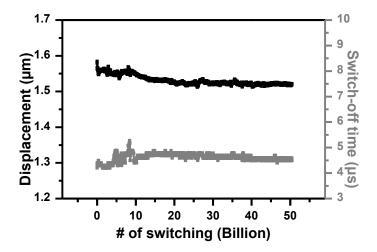

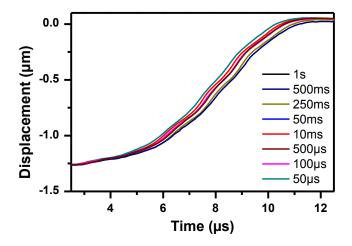

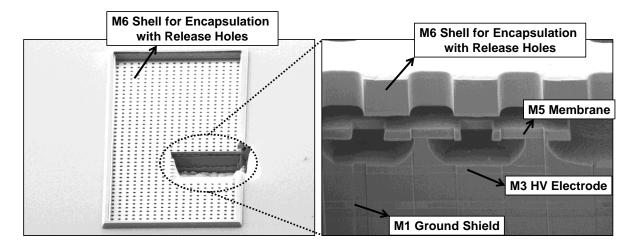

The capacitive type RF-MEMS switch is built between M1 and M3 layers of the BEOL using the developed RF-MEMS module process flow. High voltage electrodes are formed using M1 while M2 is used as the RF signal line. A thin  $Si_3N_4/TiN$  stack, which is a part of the BiCMOS MIM capacitor, forms the switch contact region and provides DC isolation between the movable membrane (M3) and the signal line (M2). This configuration also provides a height difference between the high voltage electrode and the signal line; hence the signal line serves simultaneously as a stopping layer for the switch membrane. The process integration scheme of the switch after applying the aforementioned RF-MEMS module is presented in Figure 2.6. Figure 2.7 shows SEM view of a fabricated RF-MEMS switch device [75].

Figure 2.6 Generic cross section of embedded RF-MEMS switch integration into the BEOL of BiCMOS technology [75].

Figure 2.7 SEM view of the RF-MEMS switch [75].

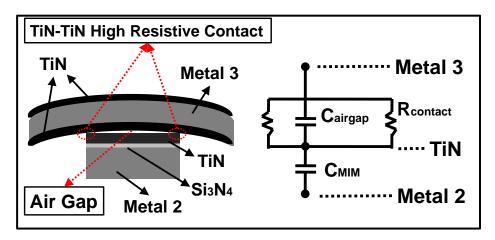

At down-state, the bottom TiN layer of M3 touches the TiN layer on top of the MIM dielectric (Figure 2.8). Due to the high contact resistance between the conductive TiN layers ( $\sim$ 4-5 K $\Omega$ ), the down-state capacitance is dominated by the air-gap capacitance that occurs in the contact area. The air-gap capacitance can be well controlled by optimizing the stress gradient of M3, as explained in previous sections. The MIM capacitor between the membrane and the signal line is used to achieve DC isolation only. The cross-section, as well as the RLC model of the contact region are given in Figure 2.8 for the down-state [76].

Figure 2.8 Cross-section of contact region for down-state (left). Lumped-element model of the contact when the membrane is in down-state (right) [76].

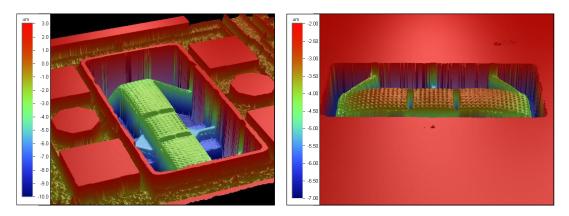

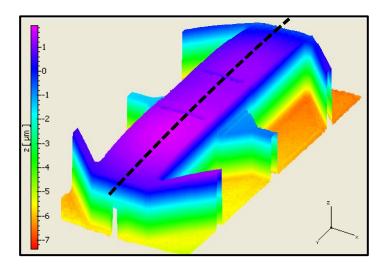

The WLI measurements of the RF-MEMS switch are depicted in Figure 2.9. Figure 2.9 (left) shows that the RF-MEMS switch is below the surface of the BiCMOS wafer. The slightly stressed membrane shape is also seen in Figure 2.9 (right) which helps to understand the phenomena in Figure 2.8. The z-level of the middle of the membrane is approximately 1.5 µm higher than the edge of the membrane, using the Recipe3.

Figure 2.9 WLI measurements of fabricated RF-MEMS switch. The RF-MEMS switch is below the surface of BiCMOS wafer (left). Slightly stressed membrane, middle part of the membrane is at higher z-level than the sides (right).

## 2.5 Conclusion

In Chapter 2, an introduction to the technology used in this thesis has been given. The underlying BiCMOS process has been detailed. The required changes in order to realize RF-MEMS devices in BiCMOS process has been explained by means of stress control of the metallization layers. Finally, the additional process steps and the process flow for the integration of the RF-MEMS switch into the BEOL of the BiCMOS process have been studied. The significant effect of the stress gradient of the movable membrane, especially at down-state, has been also detailed at the end of the chapter.

After the processing of every 200-mm wafer for the RF-MEMS devices, it is not surprising that most devices work perfectly on some parts of the wafer accompanied with non-functional ones on the other parts of the same wafer due to the non-uniform deposition and etch steps. However, the main issue is repeating the same process with similar device performance parameters from wafer to wafer and lot to lot, which can be defined as the first critical term for fabrication: *Repeatability*.

Over a 200-mm wafer, there can be many different types of stress gradients due to non0unifirm deposition and etch steps which strongly change the performance of the device over the wafer. This can be the main obstacle for industrialization of the process and causes the second critical term for fabrication: *Uniformity*.

The aforementioned uniformity issue over the wafer is always a bottleneck for the process engineers since the device performance can significantly change over wafer due the lack of good uniformity which decrease the number of good devices per wafer; hence increase the cost per device. This is the last critical term for fabrication: <u>Yield</u>.

To conclude Chapter 2, technology of an RF-MEMS device is the most important point and needs to be carefully planned before any RF-MEMS device development. Serious device developments can only be pronounced when these three important terms are started to be discussed; repeatability, uniformity and yield.

# 3 Modeling and Characterization

## 3.1 Introduction

While the RF-MEMS module integration explained in Chapter 2 provides functional RF-MEMS switch structures, a special design effort is necessary to obtain high performance parameters at mm-wave frequencies. The mechanically movable switch structures need to be optimized in mechanical, electrical and RF domains.

The mechanical domain is one of the most important domains and is closely related to the processing capabilities. First of all, mechanical simulations are more challenging than other simulation domains because the material properties required for mechanical simulations are not well known for every material and may significantly change depending on the process conditions [77]. The extraction of these parameters is not straightforward and needs stable process conditions and substantial effort.

The second simulation domain of RF-MEMS switches is the electrical domain. The electrical domain plays an important role in two different ways. The first is the electrical coupled mechanical (electromechanical) domain which needs to be modeled together with mechanical simulations. The second role of the electrical domain is to set the biasing conditions and the isolation of high actuation voltage from the radio frequency (RF) signal.

The last simulation domain required for optimizing an RF-MEMS device is the electromagnetic domain, where modeling is relatively easier and more straightforward by the help of mature EM simulators. However, one of the most important domains in this thesis is the electromagnetic domain due to the relatively large size of the RF-MEMS devices with respect to the other BiCMOS components such as transistors, capacitors and resistors.

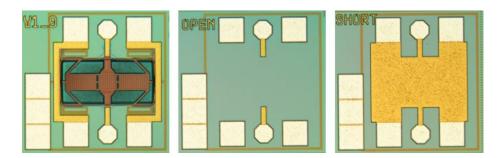

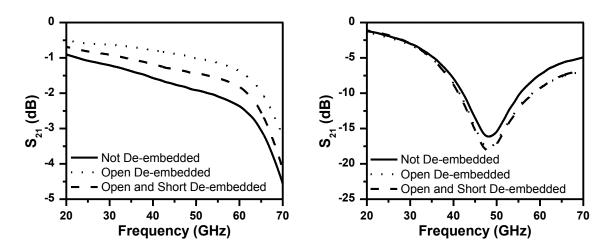

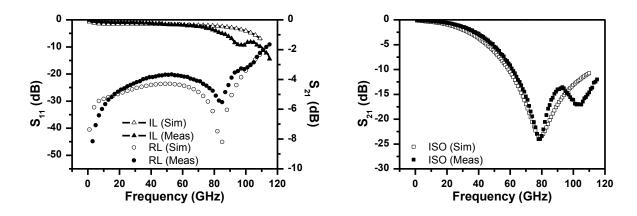

In addition to simulation and modeling, appropriate characterization methods need to be used to obtain accurate, reliable and time-efficient measurements. RF measurement techniques are well developed up to mm-wave frequencies by the help of Vector Network Analyzers (VNA). At mm-wave frequencies, special calibration and de-embedding techniques are required; however, many different techniques are

available and provided by VNA suppliers. Low frequency capacitance measurements, which have also importance in predicting the RF behavior, are also relatively easier. Using an impedance analyzer, capacitance values with an accuracy of around 1 fF can be detected [78]. The most challenging domain for characterization is the mechanical domain. Although well-established characterization techniques such as White-Light-Interferometer (WLI) and Laser-Doppler-Vibrometer (LDV) exist, they need special effort in order to characterize a specific RF-MEMS device.

Chapter 3 starts with the characterization of the material properties to provide accurate information for mechanical simulations. Section 3.3 gives the electromechanical modeling and optimizations. Measurements results of dynamic behavior and comparison of them with the simulated ones are also given in this section. RF modeling and characterization is given in section 3.4. Chapter 3 is concluded with section 3.5 in which general comments about the modeling, characterization and performance figures are given.

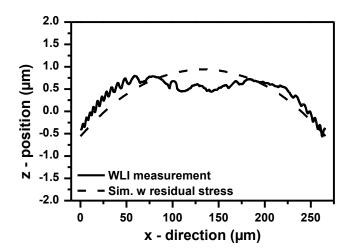

## 3.2 Process Dependent Material Characterization

In order to use the exact process parameters in FEM simulations, the Young's modulus and the residual stresses of the layers in the M3 stack are calculated by utilizing the measured frequency-response-functions (FRF) of cantilever test structures. FRF of different length cantilevers are extracted from the measurement results of mechanical responses using LDV (MSA-500, Polytec) [79]. After having the approximate Young's modulus values, the total residual stress of M3 is calculated and compared with the measurements done using an in-line wafer curvature method. Extracted material properties are inserted into the FEM solver in order to achieve a similar bended membrane shape as in measurements. A method to distinguish between the temperature-induced stress and the intrinsic stress is also presented. Finally, the measurement data of membrane topography taken from WLI is compared with the FEM model constructed by making use of the extracted process parameters.

## 3.2.1 Extraction of Young's Modulus and Residual Stress

#### - Determination of Young's Modulus

The knowledge of mechanical material parameters is mandatory for FEM simulators in order to develop RF-MEMS devices due to their influence on device performance and reliability [80]. Different types of methods like mechanical resonance, pull-down voltage and load-deflection method are proposed in the literature in order to estimate the mechanical material parameters [81, 82]. Out of these characterization methods, the determination of the specific mechanical material properties in this thesis is achieved using the method based on mechanical resonance and load-deflection method combined with FEM simulations and statistical methods.

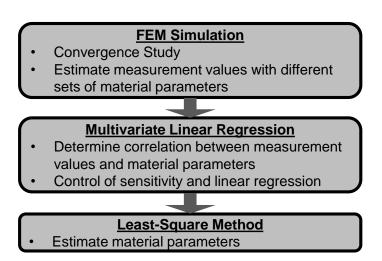

The mechanical resonance frequency and the load-dependent deflection of a mechanical system strongly depend on the material parameters, such as Young's modulus. These two main properties of the specific test structures are simulated using an FEM solver. A multivariate linear regression (MLR) is used to determine a correlation between measurement and simulations of the related material parameters. The method is resulting in different sets of material parameters which show the lowest deviation to measurement results. The proposed calculation method is schematically represented in Figure 3.1.

Figure 3.1 The estimation flow for Young's modulus and residual stress [83].

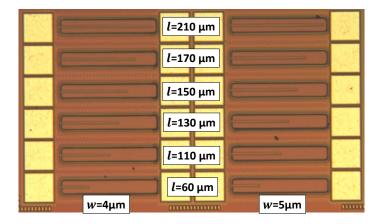

As given in Chapter 2, the movable part of the RF-MEMS switch is realized using the M3 layer of the BiCMOS BEOL stack. M3 consists of a TiN/Ti/AlCu/TiN/Ti material stack. TiN/Ti stacks are used as a barrier and adhesion layer between AlCu and the BEOL SiO<sub>2</sub> whereas AlCu (99.5 % Al) is used as the main conductive part of M3. The mechanical properties of the suspended M3 layer are mainly dominated by the Young's modulus of TiN, AlCu and the residual stresses of these layers. Total residual stress in a thin film is a combination of temperature-induced stress and intrinsic stress [84]. Temperature-induced stress is a result of cooling down from deposition temperature to room temperature during the process. Intrinsic stress is mainly determined by crystallographic defects and the grain boundaries [85]. The material parameters are strongly affected by the type of deposition and the deposition conditions, e.g., temperature and pressure. The estimation of Young's modulus and residual stress are done with different types of structures using the method given in Figure 3.1. In order to determine the Young's modulus, clamped beams with different lengths and widths are fabricated and measured (Figure 3.2).

Figure 3.2 Fabricated clamped beams with different lengths and widths for the estimation of Young's modulus with different widths and lengths [83].

The FRF of a simple clamped beam depends on the Young's modulus. The first eigenfrequency can be calculated by equation (3.1) and shows a dependency on the length (l), the thickness (t), the material density  $(\rho)$  and the Young's modulus (E).

$$f_r = \frac{1}{2\pi * l^2} * \sqrt{\frac{4*E*t^2}{\rho}} \tag{3.1}$$

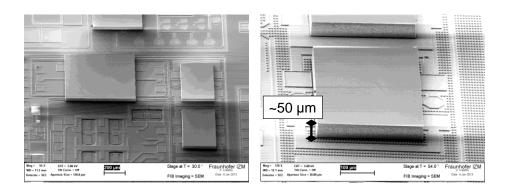

The fabricated test structures are investigated by Focused-Ion-Beam (FIB) to consider process specific characteristics like under etching of the cavity mask (lateral etch of SiO<sub>2</sub>) and unwanted etching of AlCu (Figure 3.3). The FEM simulations are very sensitive to these geometry changes, therefore the exact dimensions of fabricated structure have to be used for the simulations.

Figure 3.3 FIB cut of the clamped beam showing lateral under-etch and AlCu etch [83].

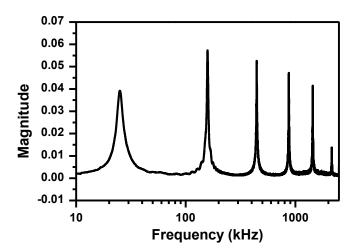

FRF is independent from residual stress and therefore it is defined by geometry and the effective Young's modulus of the metal stack only. The FRF is detected by electrostatic actuation with a noise-like broadband signal and observing the mechanical response with the LDV. The FRF of a 210 µm beam is shown in Figure 3.4 as an example and provides 6 detectable eigenfrequencies at the maximum frequency value of 2.5 MHz. Due to the low actuation amplitude the total displacement is too small. Considering the large distance between M1 and M3, no influence of squeeze-film damping is expected. Otherwise, damping may introduce a shift of the FRF leading to a significant measurement and calculation error.

Figure 3.4 FRF graph of a 210  $\mu m$  clamped beam shows the first 6 eigenfrequencies [83].

The calculated "coefficient-of-determination", which indicates how well the simulated results fit to the measurements, is higher than 0.998 for every eigenfrequency, showing that the linear type of multivariate regression is suitable. The most accurate results of the least-square method with lowest deviation to measurement are shown in Table 3.1.

Table 3.1 Results for determination of Young's modulus [83].

| $E_{AlCu}\left(GPa\right)$ | $\mathrm{E}_{\mathrm{TiN}}\left(\mathrm{GPa} ight)$ | Maximum Deviation $f_{1-6}$ |

|----------------------------|-----------------------------------------------------|-----------------------------|

| 65                         | 410                                                 | 3.0 %                       |

The Young's modulus of 65 GPa for AlCu and 410 GPa for TiN are in a very good agreement with the literature [86, 87] and the simulated FRF with the estimated material properties shows a small deviation of 3 % compared to the measured FRF. For further analysis of the residual stress, the achieved Young's moduli are applied to RF-MEMS switch structure to analyze the residual stress characteristics of the AlCu and TiN layers in the next section.

#### - Determination of Residual Stress

Residual stress in suspended structures results in membranes bent up or down and strongly influences the performance of the switch. Strong residual stress in thin layers is not only limiting the mechanical performance, but also resulting in poor electrical and RF performance. Furthermore, reliability of the RF-MEMS switch is also affected by the residual stress considering the change of the restoring force of the membrane. By knowing the approximate residual stress, design optimization time can be significantly reduced and the yield of the process can also be increased by optimizing the process flow less sensitive to the residual stress variations.

The residual stress in the suspended membrane is the result of temperature-induced stress during the fabrication process steps and the intrinsic stress of the different layers. The total residual stress of a single layer can be extracted using wafer curvature method. However, the measured stress out of wafer curvature method is the combination of temperature-induced stress and the intrinsic stress.

In order to distinguish between these two different kinds of stress, firstly the aforementioned calculation method in Figure 3.1 is used to estimate the total residual stress. The MLR shows a high sensitivity to residual stress but it has to be considered that the "coefficient-of-determination" varies for different locations in x-direction. Only points with a high "coefficient-of-determination" have been taken into account. The most accurate results of the least-square method out of all calculations are given in Table 3.2. The extracted results from simulations of single layers are in good agreement with in-line stress measurements using wafer curvature method. Characterization of stand-alone layers using wafer curvature method is only possible for the bottom TiN and AlCu layers. Residual stress values in Table 3.2 are used in FEM simulations to obtain the initial stressed case of the membrane.

Table 3.2 Calculated and measured results of residual stress for different layers [83].

| Layer      | Residual Stress (MPa)<br>(Calculation) | Residual Stress (MPa) (Wafer Curvature Measurements) |

|------------|----------------------------------------|------------------------------------------------------|

| TiN-Top    | - 514 (compressive)                    | -                                                    |

| AlCu       | 494 (tensile)                          | 432 (tensile)                                        |

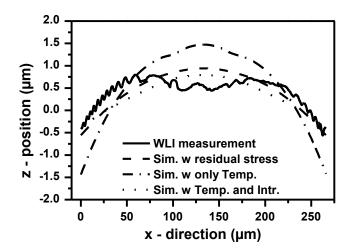

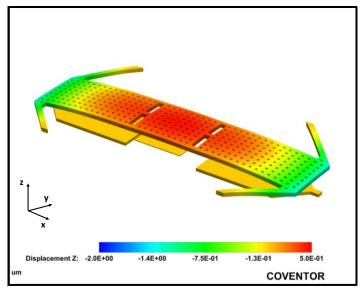

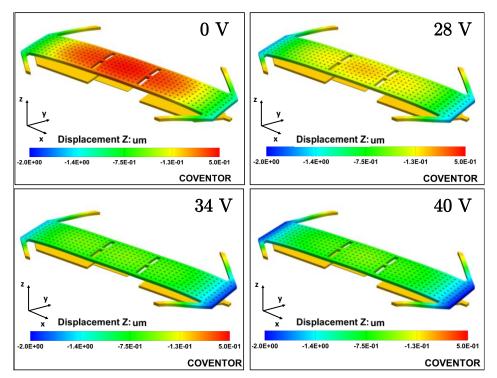

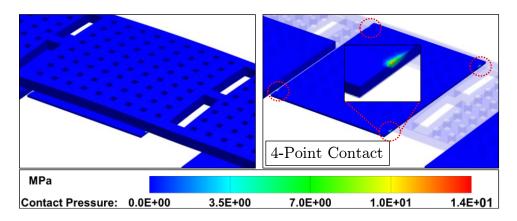

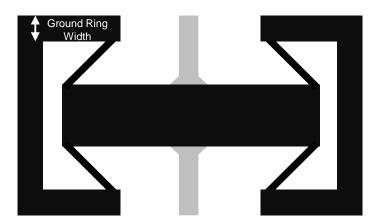

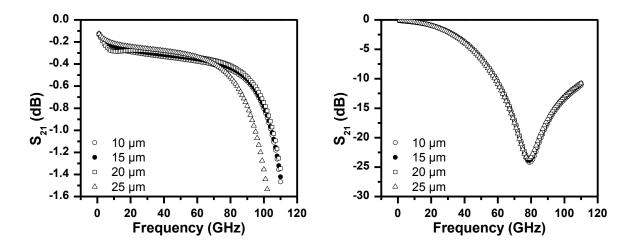

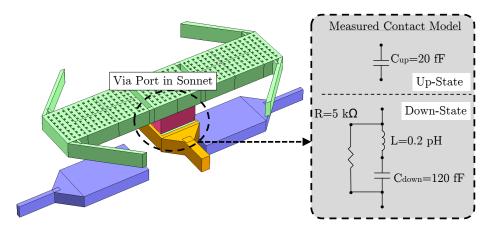

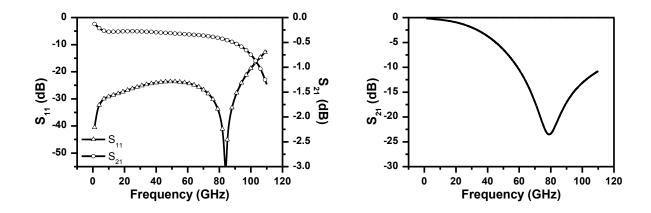

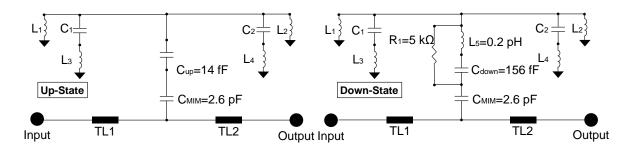

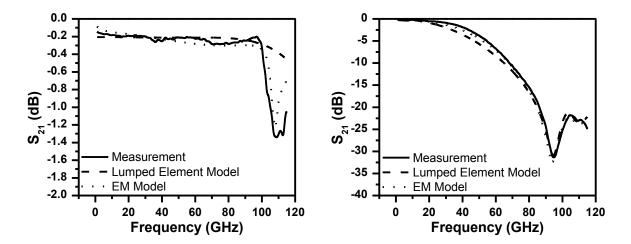

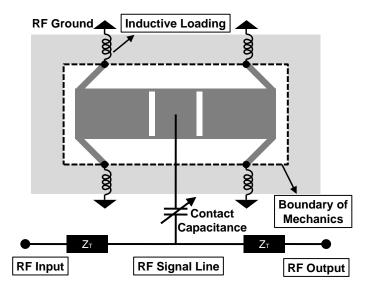

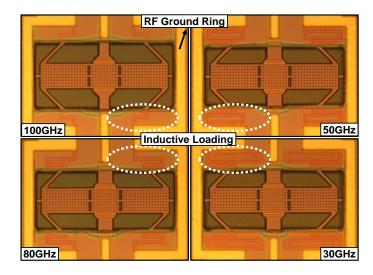

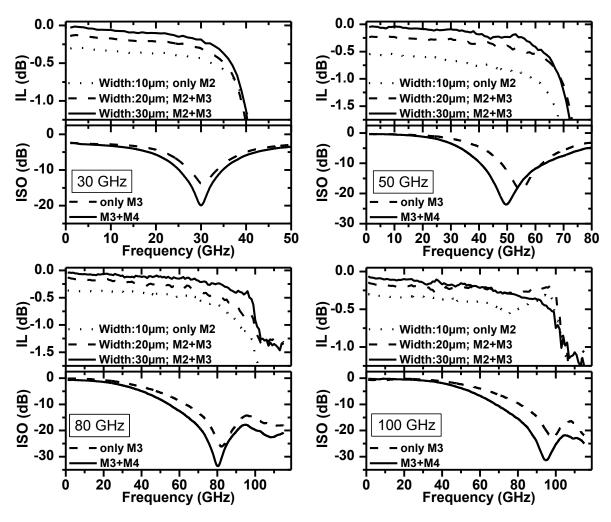

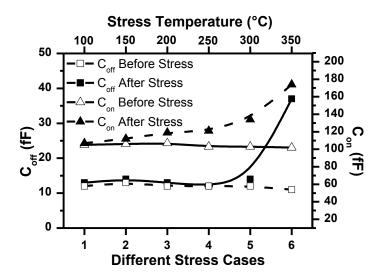

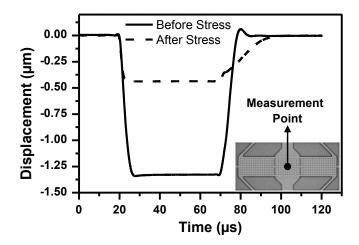

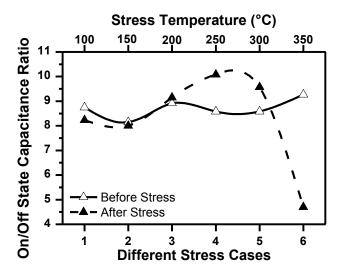

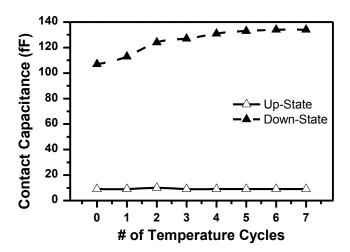

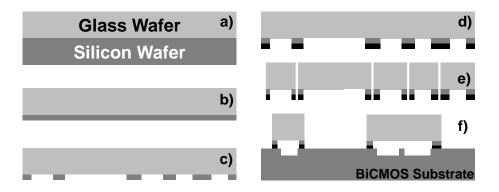

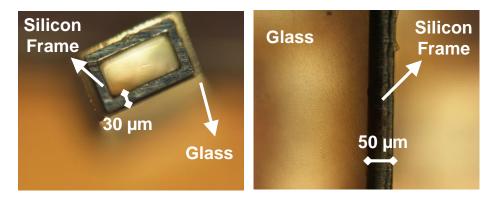

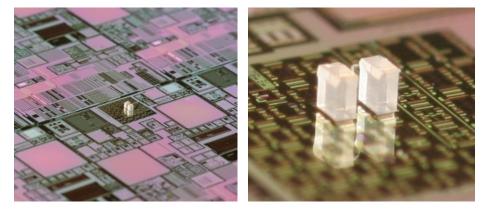

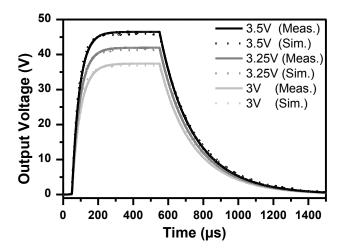

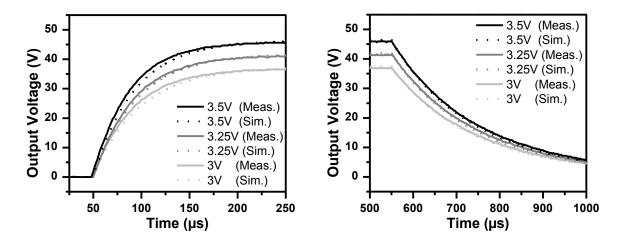

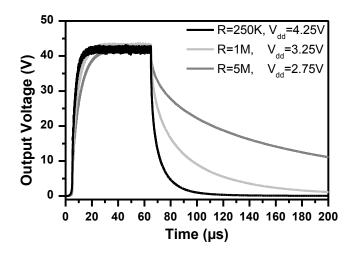

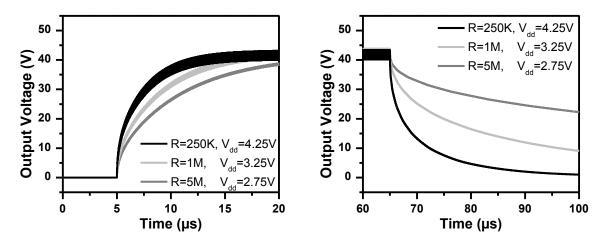

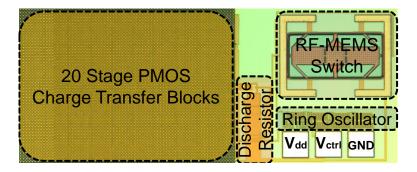

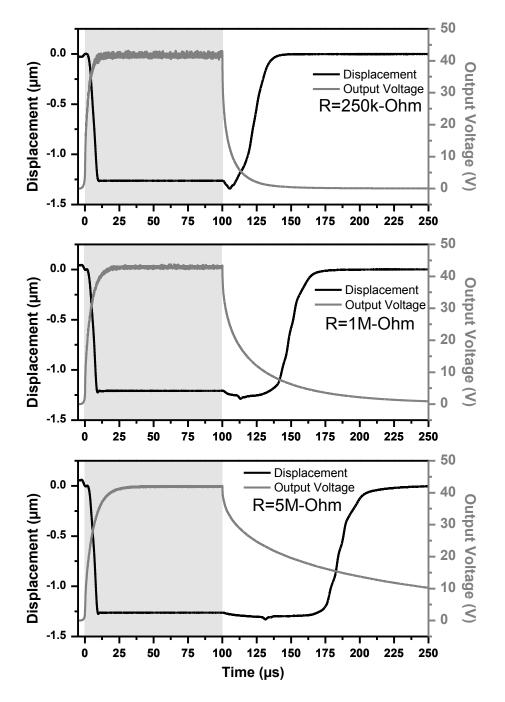

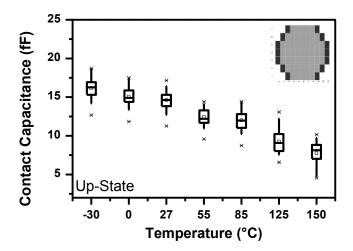

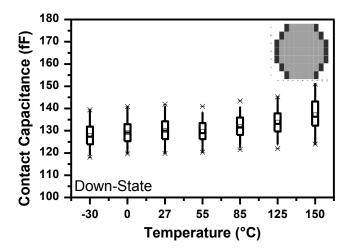

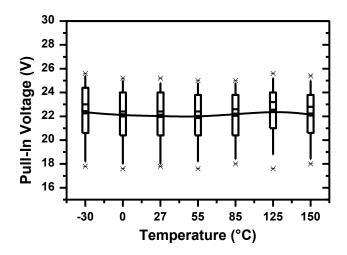

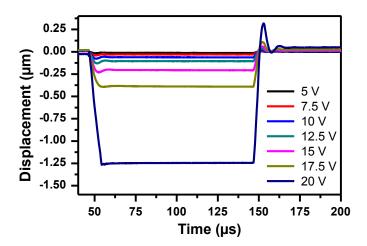

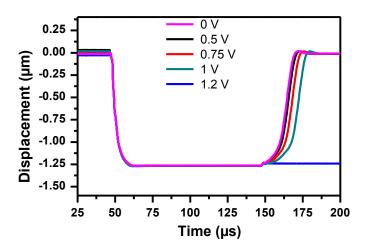

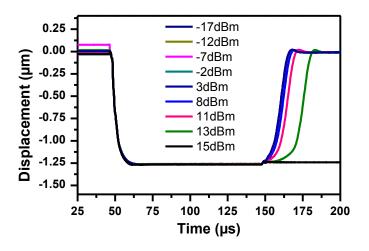

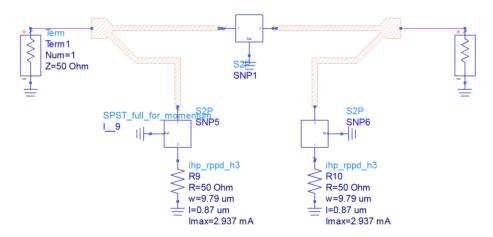

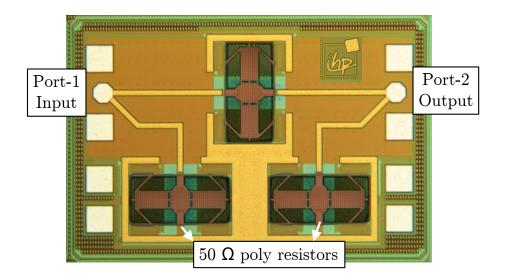

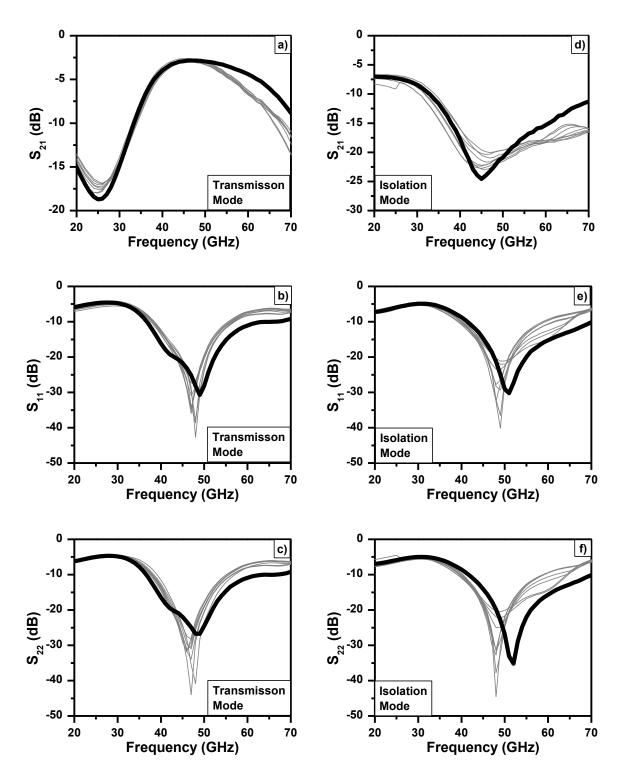

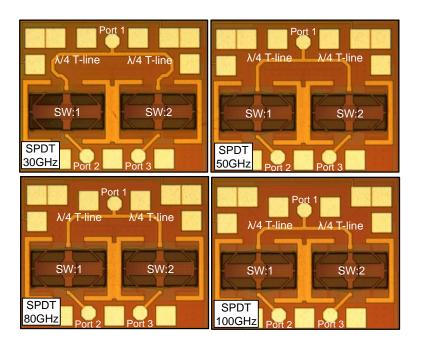

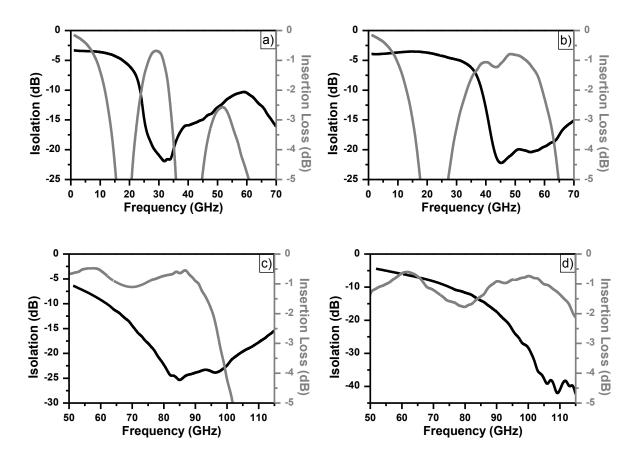

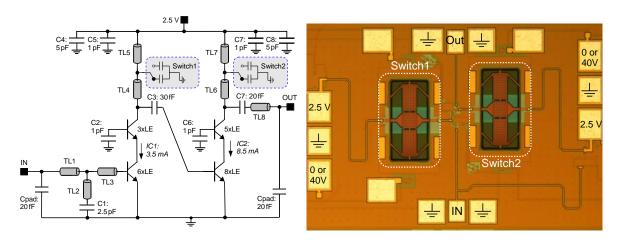

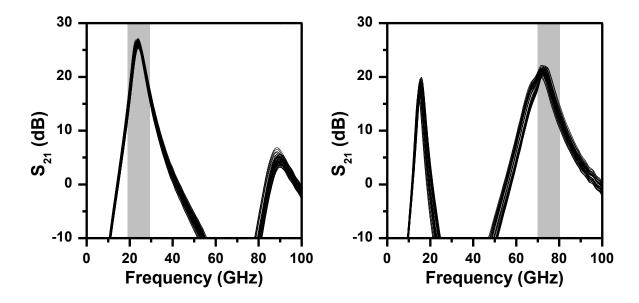

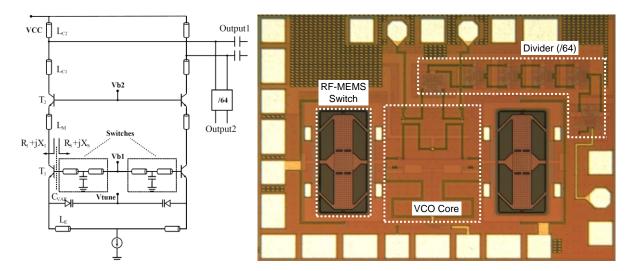

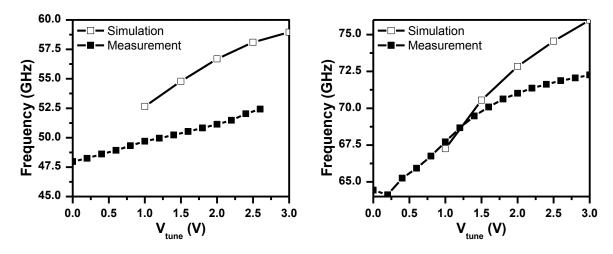

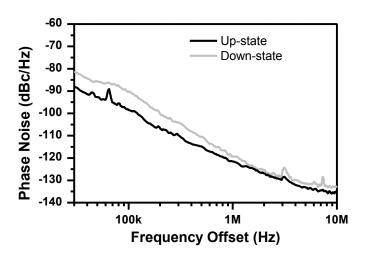

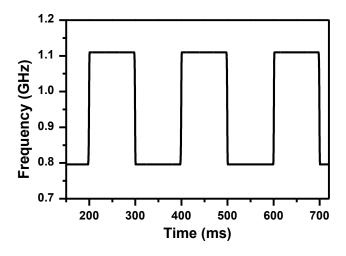

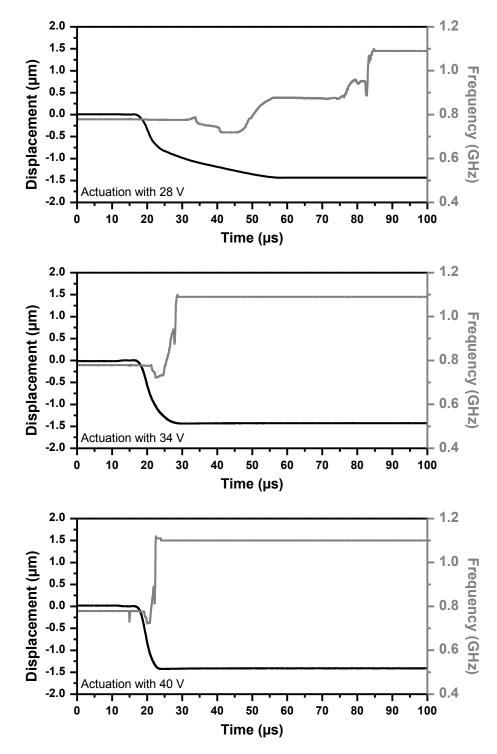

| TiN-Bottom | -964 (compressive)                     | - 860 (compressive)                                  |