# Small-Area SAR ADCs With a Compact Unit-Length DAC Layout

## Citation for published version (APA):

Li, H., Shen, Y., Cantatore, E., & Harpe, P. (2022). Small-Area SAR ADCs With a Compact Unit-Length DAC Layout. *IEEE Transactions on Circuits and Systems II: Express Briefs, 69*(10), 4038-4042. Article 9805764. https://doi.org/10.1109/TCSII.2022.3186064

Document license: Unspecified

DOI: 10.1109/TCSII.2022.3186064

### Document status and date:

Published: 01/10/2022

### Document Version:

Accepted manuscript including changes made at the peer-review stage

### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Small-Area SAR ADCs With a Compact Unit-Length DAC Layout

Hanyue Li, Graduate Student Member, IEEE, Yuting Shen, Graduate Student Member, IEEE, Eugenio Cantatore, Fellow, IEEE, and Pieter Harpe, Senior Member, IEEE

Abstract—This paper presents four small-area SAR ADCs with a resolution from 8 to 11 bits. Two area-saving techniques are utilized. First, the DAC layout is implemented with custom designed unit-length capacitors, which are optimized for each resolution to minimize the chip area. Second, dynamic logic is applied to the 8-bit design to further reduce the number of transistors and save area. Fabricated in 65 nm CMOS, the 8/9/10/11-bit SAR ADCs only occupy  $20 \times 21 \ \mu m$ ,  $20 \times 36 \ \mu m$ ,  $36 \times 36 \ \mu m$  and  $36 \times 36 \ \mu m$ , respectively. At 10 MHz sampling rate, their measured ENOB is 7.5, 8.3, 9.1 and 9.8 bits with an SFDR of 65.4 dB, 67.4 dB, 78.0 dB and 76.5 dB, respectively. Compared to prior-art, these designs achieve the smallest areas for the achieved ENOBs.

*Index Terms*—SAR ADC, small area, area efficiency, unit length, DAC layout, dynamic logic.

### I. INTRODUCTION

**O** VER the past two decades, the power efficiency of analog-to-digital converters (ADC) has improved more than  $1000 \times$  thanks to various circuit and architecture innovations [1], [2]. Among ADCs, the successive-approximation-register (SAR) ADC is a key contributor owing to its simple structure and compatibility to new technologies. Besides power consumption, the area efficiency can also be of great importance for emerging applications like neural recording, ultrasound imaging and image sensing where an ADC array is needed [3], [4]. Small-area SAR ADCs can be a well-suited choice for these application scenarios.

Typically, the area of a charge redistribution SAR ADC [5] is dominated by the switched-capacitor digital-to-analog converter (DAC). Due to the binary scaled DAC structure, the total DAC capacitance grows exponentially with increased resolution. The size of the DAC array is determined mainly by three factors: kT/C sampling noise, mismatch requirements and minimum physical size constraints [2]. Among these, the kT/C sampling noise is regarded as the fundamental limit in most designs, as mismatch could be calibrated, and physical size depends on technology. Table I summarizes the required DAC capacitance in a differential SAR ADC for different resolutions when only kT/C noise is considered. It is assumed

Digital Object Identifier xxxx.

TABLE I Capacitor Size for Different SAR ADC Resolutions

| # bits N | $C_{\rm DAC}~({\rm pF})$ | $C_{\rm u}~({\rm aF})$ | # bits N | $C_{\rm DAC}~({\rm pF})$ | $C_{\rm u}~({\rm aF})$ |

|----------|--------------------------|------------------------|----------|--------------------------|------------------------|

| 8        | 0.0016                   | 6                      | 12       | 0.4                      | 102                    |

| 9        | 0.0065                   | 13                     | 13       | 1.7                      | 203                    |

| 10       | 0.026                    | 25                     | 14       | 6.7                      | 407                    |

| 11       | 0.1                      | 51                     | 15       | 26.7                     | 814                    |

\*  $C_{\text{DAC}}$  is the DAC capacitance per side.  $C_{\text{u}}$  is the unit capacitance.  $C_{\text{DAC}} = 2^N C_{\text{u}}$ .

that for an *N*-bit ADC,  $2^N$  DAC unit capacitors are needed per side. The kT/C noise power is set to be equal to the quantization noise, and the reference voltage  $V_{\text{REF}}$  is 1 V. As can be seen, on the one hand, the DAC capacitance can reach a few pF for high-resolution SAR ADCs. In this case, ADC area reduction can be achieved by oversampling [6] or sampling noise cancellation techniques [7]. On the other hand, for low-resolution SAR ADCs, the required unit capacitor is so small that it is often overdesigned due to practical physical size limitations, leading to unnecessary area cost. Therefore, this paper aims to optimize the area of SAR ADCs with a resolution from 8 to 11 bits. Note that the thermal noise limited minimum capacitance decreases with  $V_{\text{REF}}$ , so this area optimization is particularly important at higher  $V_{\text{REF}}$ .

Different solutions have been proposed in literature to reduce the chip area for low-resolution SAR ADCs. A bridge capacitor can be used with a compact layout as in [8], but it requires a careful examination of the parasitics. A charge injection cell [9] eliminates the necessity for binary-scaled capacitors, but it requires a high frequency synchronous clock for the internal logic control [10]. MOS transistors have also been used as capacitors in the DAC [11], but its area is still limited by the minimum transistor size provided by the technology. Custom designed capacitors are widely used because they can realize unit capacitors below 1 fF. A unitelement-based layout approach can be found in [12], [13] and [14], but the DAC interconnections can still occupy substantial area [13]. Recently, a unit-length-based layout is proposed [4], and it has reduced the area of a 10-bit SAR ADC to  $36 \times 36$  $\mu$ m in 65 nm CMOS. This work is based on the same unitlength DAC layout principle, but expands it to achieve even better area efficiency for the 8, 9 and 11-bit SAR ADCs.

This paper is organized as follows. Section II describes the proposed compact DAC layout structure. Section III details

This paragraph of the first footnote will contain the date on which you submitted your paper for review, which is populated by IEEE. This work is supported by the Dutch Research Council (NWO) under Grant 16594. (*Corresponding author: Hanyue Li.*)

The authors are with the Department of Electrical Engineering, Eindhoven University of Technology, 5600 MB Eindhoven, The Netherlands (e-mail: h.li2@tue.nl).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

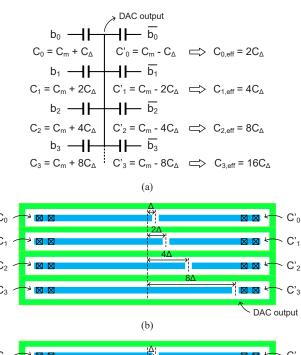

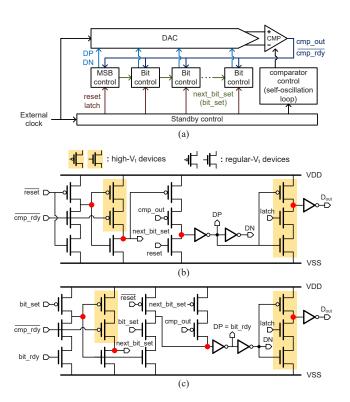

Fig. 1. (a) DAC schematic. (b) Original unit-length DAC layout in [4]. (c) Modified unit-length DAC layout. A 4-bit DAC is shown for simplicity.

the dynamic logic for the 8-bit ADC. Section IV presents the measurement results and Section V draws conclusions.

### II. UNIT-LENGTH DAC LAYOUT

A conventional charge-redistribution SAR ADC utilizes a binary-scaled capacitive DAC, where the unit cell in the DAC array is implemented as a single capacitor. Instead, in the unit-length DAC [4], each unit cell consists of two capacitors driven by opposite control bits, as shown in Fig. 1(a) and Fig. 1(b). In this way, the effective DAC unit cell is formed by the difference between a "positive" capacitor ( $C_0$ ) and a "negative" capacitor ( $C'_0$ ), e.g.  $C_{0,\text{eff}} = C_0 - C'_0 = 2C_{\Delta}$ . The accuracy of the DAC capacitors is then determined by the relative length difference ( $\Delta$ ,  $2\Delta$ ,  $4\Delta$ , etc.) of metal strips instead of their absolute length value. This unit-length configuration greatly reduces the number of unit cells in the DAC array while maintaining 10-bit linearity without calibration [4].

This unit-length DAC layout can be further simplified to provide even lower unit capacitance and smaller area for a SAR ADC with lower resolution. Fig. 1(c) shows the proposed DAC layout. The green metal strips between two adjacent unit cells are removed, and two DAC bits are merged into a single enclosed structure. In this way, the DAC capacitor is formed by the single-side coupling capacitor between the DAC bottom

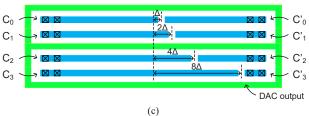

Fig. 2. Dimension of the unit-length DAC layout in (a) 10-bit and 11-bit ADCs, and in (b) 8-bit and 9-bit ADCs.

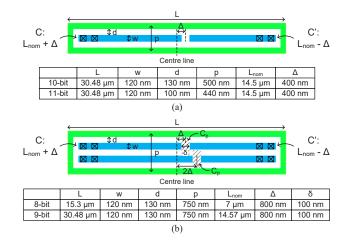

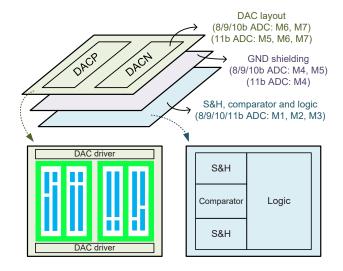

Fig. 3. ADC layout floorplan.

plate (blue strips) and the DAC top plate (green strips), which halves the minimum  $C_{\Delta}$  compared to the original layout in Fig. 1(b). With the same number of bits, this modified layout can also save about 25% DAC area compared to the original one. Both the reduction of capacitance and area are beneficial, especially for low-resolution SAR ADCs (Table I).

Despite the compactness of the proposed layout, a drawback is the undesired coupling capacitance  $C_p$  between the DAC bottom plate and the opposite top plate, as shown in Fig. 2(b). This parasitic capacitance  $C_p$  exists only for either C or C', thus it cannot be cancelled by subtracting C' from C during the SAR conversion. This causes systematic non-linearity for the converter. To minimize its effect, the distance between the two confronting blue metal strips [ $\delta$  in Fig. 2(b)] is set to the minimum allowed space. In practice, the DAC least significant bits (LSBs) are implemented with unit-length layout cells and the DAC most significant bits (MSBs) are built with unary layout cells [4], so the  $C_p$ -induced non-linearity will only affect LSB mismatch. The proposed layout is used in the 8bit and 9-bit SAR ADCs, where lower accuracy is acceptable and reduced capacitor values and area are preferred. Based on parasitic extraction,  $C_p$  is about 12 aF, and it causes a systematic error of 0.2 LSB INL and 0.2 LSB DNL for both the 8-bit and 9-bit ADCs. The exact capacitor dimensions in Fig. 2 are determined by two aspects: firstly, the experimental results in [4] were used to estimate which dimensions can achieve acceptable matching. Secondly, the dimensions were minimized as much as possible to fit in the overall ADC area.

The 10-bit ADC is the same as in [4] as a reference design. The original DAC layout in Fig. 1(b) is adopted in the 11-bit ADC. To meet the more stringent kT/C noise requirement in an 11-bit ADC, the capacitance density is increased by using the minimum spacing between DAC plates [d in Fig. 2(a)] and stacking 3 rather than 2 metal layers. This approach results in minimal area but is sub-optimal for matching. As an alternative, one could investigate to use less stacked metals and instead increase the L,  $\Delta$ , d, p and w dimensions (Fig. 2) to improve matching while maintaining a small total capacitance value, at the cost of increased chip area. The DAC layout is placed on top of the other blocks, as shown in Fig. 3 [4]. For the 8, 9 and 10-bit ADCs, the DAC layout is composed of metal 6 (M6) and metal 7 (M7), and metal 1 (M1) to metal 3 (M3) are used for wiring the circuitry. Metal 4 (M4) and metal 5 (M5) are used as shielding layers. For the 11-bit ADC, three metal layers (M5 to M7) are stacked to form the DAC, which leaves only one metal layer (M4) for shielding.

### **III. DYNAMIC LOGIC**

The DAC layout area scales exponentially with resolution, but the logic area only scales linearly. For the 10-bit ADC in [4], standard-cell-based logic is used and that fits well in the space under the DAC layout. However, in an 8-bit ADC layout, the DAC can be scaled to only a quarter of the original design in [4], while the logic area has only shrunk by 20%. In this case, the digital logic can be the bottleneck in the whole ADC area scaling. To further reduce the logic area, dynamic logic [13] is used in the 8-bit ADC because it requires less transistors than the standard-cell-based logic.

The overall logic diagram is shown in Fig. 4(a). A conventional DAC switching scheme [5] is used in this design, so the MSB control logic (Fig. 4(b)) is slightly different from the other bits (Fig. 4(c)). After the input is sampled on the DAC, the *reset* signal goes low and this triggers the MSB comparison. After one bit is resolved, the next\_bit\_set (namely, bit\_set in the next bit control stage) goes high to enable the next bit DAC toggling. When all the 8 bits are available, reset goes high to reset the DAC, and a latch pulse is generated for the data read-out. The control logic state information is stored on the internal nodes, denoted as red dots in Fig. 4. These nodes can be floating during part of the conversion process. In [13], additional capacitors were added to safely maintain the state. This work removes those capacitors and uses high- $V_t$  transistors for the critical nodes to save area. This approach shows stable digital functionality over PVT variations. Moreover, compared to [13], one redundant transistor connected to  $cmp_rdy$  is removed to simplify the design.

A double-tail dynamic comparator [15] is used in the 10bit and 11-bit ADCs, while a simpler StrongARM latch [16] is chosen for the 8-bit and 9-bit ADCs thanks to the relaxed noise requirement at lower resolutions. The sampling switch is implemented as an NMOS switch with a boosted clock for all the four ADCs. The DAC capacitance per side is 55 fF, 107 fF, 250 fF and 690 fF, for the 8/9/10/11-bit designs, respectively.

### **IV. MEASUREMENT RESULTS**

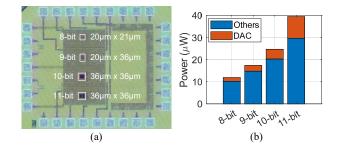

All four designs are fabricated in a single 65 nm CMOS test chip, where the 10-bit ADC is a copy from [4] as a reference design. Fig. 5(a) shows the die photo. The proposed 8, 9 and 11-bit ADCs occupy an area of only  $20 \times 21 \ \mu m$ ,  $20 \times 36 \ \mu m$  and  $36 \times 36 \ \mu m$ , respectively. Fig. 5(b) shows the power breakdown of each ADC. For low-resolution SAR ADCs, the DAC power is only a small fraction of the total ADC power, while digital power can become dominant.

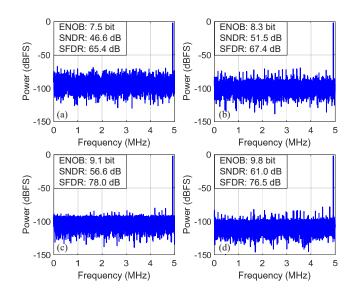

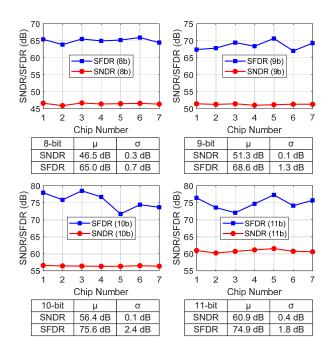

Fig. 6 shows the measured spectrum for all four ADCs at Nyquist input frequency. The sampling rate is 10 MS/s. The

Fig. 4. (a) Overall logic diagram. (b) MSB control block and (c) control block for other bits.

Fig. 5. (a) Die photo with all four ADCs. (b) Power breakdown.

Fig. 6. Measured spectrum of (a) 8-bit, (b) 9-bit, (c) 10-bit and (d) 11-bit ADCs.

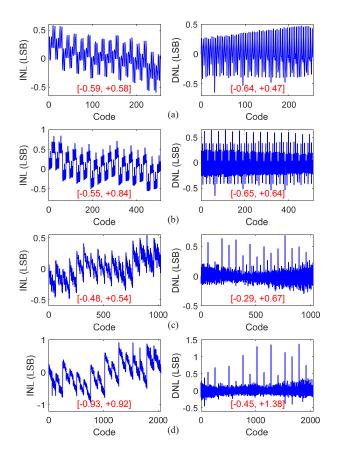

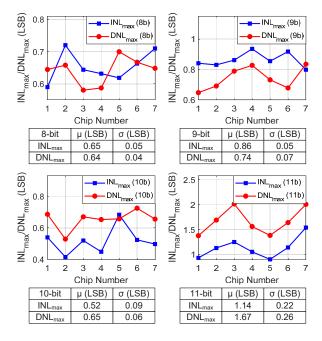

Fig. 7. Measured INL and DNL of (a) 8-bit, (b) 9-bit, (c) 10-bit and (d) 11-bit ADCs.

measured effective-number-of-bits (ENOB) of the four ADCs are 7.5, 8.3, 9.1, and 9.8 bits, and the measured spurious-freedynamic-range (SFDR) results are 65.4 dB, 67.4 dB, 78.0 dB and 76.5 dB, respectively. Fig. 7 shows the measured integral non-linearity (INL) and differential non-linearity (DNL) performance. For the 8-bit and 9-bit designs, the systematic

Fig. 8. Measured SNDR and SFDR of 7 samples.

Fig. 9. Measured INL and DNL of 7 samples.

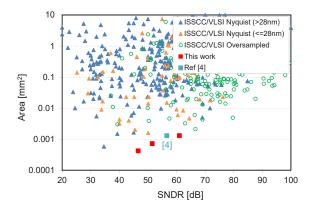

errors are caused by the parasitic  $C_p$ . For the 11-bit design, the linearity is limited by the intrinsic matching of the unitlength layout. Fig. 8 and Fig. 9 show the performance spread over 7 measured chips, which indicates consistent results. Fig. 10 benchmarks this work with other designs from [1]. Thanks to the different optimization strategies for each resolution, this work features the smallest area for each design when compared to other designs with similar signal-to-noise-and-distortionratio (SNDR), despite using a relatively old 65 nm technology. Compared to the original 10-bit design, the area of the 8-bit and 9-bit ADC scales down by 68% and 44%, respectively. With the same area cost as [4], the 11-bit ADC achieves 4.4

| Reference                         | [12]                       | [13]                       | [14]                       | [10]                        | [11]   | This work          |         |        |        |

|-----------------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|--------|--------------------|---------|--------|--------|

| Technology (nm)                   | 130                        | 90                         | 20                         | 65                          | 130    | 65                 |         |        |        |

| Supply (V)                        | 1.2                        | 1                          | 1                          | 1.2                         | 0.6    | 1                  |         |        |        |

| F <sub>sample</sub> (MHz)         | 50                         | 10.24                      | 320                        | 100                         | 1      | 10                 |         |        |        |

| Resolution (bit)                  | 10                         | 8                          | 10                         | 9                           | 9      | 8                  | 9       | 10 [4] | 11     |

| DAC<br>implementation             | Unit-<br>element<br>layout | Unit-<br>element<br>layout | Unit-<br>element<br>layout | Charge<br>injection<br>cell | MOSCAP | Unit-length layout |         |        |        |

| ENOB (bit)                        | 9.18                       | 7.77                       | 9.2                        | 7.5                         | 8.48   | 7.5                | 8.3     | 9.1    | 9.8    |

| SNDR (dB)                         | 57.0                       | 48.5                       | 57.1                       | 47.0                        | 52.76  | 46.6               | 51.5    | 56.6   | 61.0   |

| SFDR (dB)                         | 65.9                       | 61.8                       | 78.1                       | 62                          | 71.01  | 65.4               | 67.4    | 78.0   | 76.5   |

| Power (µW)                        | 826                        | 26.3                       | 1520                       | 4000                        | 2.78   | 11.9               | 17.4    | 24.7   | 39.5   |

| FoM <sub>W</sub> (fJ/convstep)    | 28.5                       | 11.8                       | 8.1                        | 219                         | 7.8    | 6.8                | 5.7     | 4.5    | 4.3    |

| Area (mm <sup>2</sup> )           | 0.052                      | 0.055                      | 0.0012                     | 0.02                        | 0.046  | 0.00042            | 0.00072 | 0.0013 | 0.0013 |

| Normalized area ( $\times 10^6$ ) | 3.08                       | 6.79                       | 3.00                       | 4.73                        | 2.72   | 0.10               | 0.17    | 0.31   | 0.31   |

TABLE II Benchmark With Other Works

$FoM_W = Power / (2^{ENOB} \times F_{sample})$

Normalized area = Area / feature size<sup>2</sup>

Fig. 10. ADC area benchmark, data from [1].

dB higher SNDR. Table II shows the benchmark table with other SAR ADC designs. This work shows a clear advantage in chip area when compared to other SAR ADCs implemented with different DAC structures.

### V. CONCLUSION

The unit-length DAC layout facilitates substantial area reduction in SAR ADCs. This work extends its usage to SAR ADCs with 8 to 11-bit resolution. A modified unitlength layout is proposed to build compact 8-bit and 9-bit ADCs, while more metal layers are stacked and spacing is minimized to get higher capacitance density for the 11-bit ADC. Moreover, dynamic logic is used for the 8-bit SAR ADC to further reduce the digital logic area. Thanks to these techniques, the designs in this work show state-of-the-art area efficiency.

### REFERENCES

- B. Murmann, "ADC Performance Survey 1997-2021," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

- [2] P. Harpe, H. Li and Y. Shen, "Low-power SAR ADCs: trends, examples and future," in *Proc. 45th Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2019, pp. 25–28.

- [3] D. De Dorigo *et al.*, "Fully immersible subcortical neural probes with modular architecture and a delta-sigma ADC integrated under each electrode for parallel readout of 144 recording sites," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3111–3125, Nov. 2018.

- [4] P. Harpe, "A compact 10-b SAR ADC with unit-length capacitors and a passive FIR filter," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 636–645, Mar. 2019.

- [5] J. L. McCreary and P. R. Gray, "All-MOS charge redistribution analogto-digital conversion techniques. I," *IEEE J. Solid-State Circuits*, vol. 10, no. 6, pp. 371–379, Dec. 1975.

- [6] P. Harpe, E. Cantatore and A. van Roermund, "An oversampled 12/14b SAR ADC with noise reduction and linearity enhancements achieving up to 79.1dB SNDR," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 194–195.

- [7] J. Liu, X. Tang, W. Zhao, L. Shen and N. Sun, "A 13-bit 0.005-mm<sup>2</sup> 40-MS/s SAR ADC with kT/C noise cancellation," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3260–3270, Dec. 2020.

- [8] C. Chan, Y. Zhu, S. Sin, S. U and R. P. Martins, "A 3.8mW 8b 1GS/s 2b/cycle interleaving SAR ADC with compact DAC structure," in *Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits)*, Jun. 2012, pp. 86–87.

- [9] K. D. Choo, J. Bell and M. P. Flynn, "Area-efficient 1GS/s 6b SAR ADC with charge-injection-cell-based DAC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 460–461.

- [10] M. Runge, D. Schmeck, P. Scholz, G. Boeck and F. Gerfers, "A 0.02mm<sup>2</sup> 9-bit 100-MS/s charge-injection cell based SAR-ADC in 65-nm LP CMOS," in *Proc. 44th Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2018, pp. 26–29.

- [11] T. Rabuske and J. Fernandes, "A SAR ADC with a MOSCAP-DAC," *IEEE J. Solid-State Circuits*, vol. 51, no. 6, pp. 1410–1422, Jun. 2016.

- [12] C. Liu, S. Chang, G. Huang and Y. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, Apr. 2010.

- [13] P. J. A. Harpe *et al.*, "A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1585–1595, Jul. 2011.

- [14] C. Liu, C. Kuo and Y. Lin, "A 10 bit 320 MS/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2645–2654, Nov. 2015.

- [15] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. A. M. Klumperink and B. Nauta, "A 10-bit charge-redistribution ADC consuming 1.9 μW at 1 MS/s," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1007–1015, May 2010.

- [16] B. Razavi, "The StrongARM latch [A circuit for all seasons]," IEEE Solid-State Circuits Magazine, vol. 7, no. 2, pp. 12–17, Spring 2015.