### Spectral Steady-State Analysis of Inverters With Temperature-Dependent Losses Using Harmonic Balance

*Citation for published version (APA):* Weiler, P., Vermulst, B., Lemmen, E., & Wijnands, K. (2022). Spectral Steady-State Analysis of Inverters With Temperature-Dependent Losses Using Harmonic Balance. IEEE Open Journal of Power Electronics, 3, 824-833. https://doi.org/10.1109/OJPEL.2022.3218282

Document license:

CC BY

DOI:

10.1109/OJPEL.2022.3218282

Document status and date:

Published: 01/01/2022

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04 Oct 2023

Received 18 September 2022; revised 21 October 2022; accepted 23 October 2022. Date of publication 31 October 2022; date of current version 16 November 2022. The review of this article was arranged by Associate Editor Vito Giuseppe Monopoli.

Digital Object Identifier 10.1109/OJPEL.2022.3218282

# Spectral Steady-State Analysis of Inverters With Temperature-Dependent Losses Using Harmonic Balance

PELLE WEILER <sup>1</sup> (Graduate Student Member, IEEE), BAS VERMULST <sup>1</sup> (Member, IEEE), ERIK LEMMEN <sup>1</sup>, AND KORNEEL WIJNANDS <sup>1</sup> (Member, IEEE)

<sup>1</sup>Electromechanics and Power Electronics Group, Eindhoven University of Technology, 5600 MB Eindhoven, Netherlands

<sup>2</sup>Electrical Energy Systems Group, Eindhoven University of Technology, 5600 MB Eindhoven, Netherlands

CORRESPONDING AUTHOR: PELLE WEILER (e-mail: b.p.weiler@tue.nl)

This work is part of the Project Next Generation of Ultrahigh Precision Power Amplifiers of the Research Programme High Tech Systems en Materials (HTSM), which was supported by the Dutch Research Council (NWO) under Project 10023393.

ABSTRACT Accurate calculation of semiconductor losses and temperature is the foundation of any design methodology for a power electronic converter. Computation accuracy and speed play a vital role if a large set of parameters needs to be considered. Averaged loss models often neglect the temperature dependence of transistors, leading to fast, but inaccurate results. In contrast, iterative methods and simulation tools, which can include temperature dependence, take significantly longer to compute, but yield more precise results. This paper presents a best of both worlds approach, by using the harmonic balance method to obtain the steady-state solution for any inverter topology including temperature dependent conduction and switching losses. The proposed method solves for the discrete Fourier series of the device temperature, by expressing the temperature dependence and operating parameters in the frequency domain. The set of equations for each coefficient is solved by a single matrix inversion, resulting in very fast computation for steady-state temperature cycles. The steady-state operation of over one thousand possible inverter designs is calculated within less than one minute, matching iterative simulation in device temperature, conduction and switching losses, at a fraction of the computation time. In addition, the method shows good agreement with temperature measurements of a three-phase silicon-carbide inverter.

**INDEX TERMS** Harmonic analysis, power converter, losses, power system simulation.

#### I. INTRODUCTION

Optimization of power electronic converters often aims at multiple goals, such as efficiency, power density, lifetime of components or cost [1], [2]. This procedure often starts with a large number of potential operating parameters and components, in order to meet the desired specifications. For each set of parameters, the losses and performance of the converter components are either calculated based on averaged states or iterated in time for more precise results [3] [4]. Usually, averaged models are much faster than iterative ones, but iterative solutions can include non-linear effects often neglected in averaged models [5]. Depending on the severity of the non-linearity, iterative simulation might be the only commonly available option towards correct results.

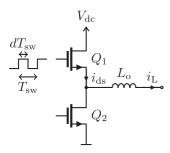

In case of power electronic devices, such as silicon or silicon-carbide (SiC) MOSFETs, accurate calculation of the total device losses is severely impeded by the temperature dependence of both conduction and switching losses [6], [7]. The temperature dependent losses can either be obtained through device characterization [8], or analytic modelling [9]. Given the half-bridge inverter in Fig. 1, each transistor experiences a temperature swing because of varying load conditions during each ac cycle. Because the device losses depend on temperature, an algebraic loop is formed: As the device heats up, the losses increase, which in turn further increases the temperature [4]. The convergence of this loop depends on the output frequency of the inverter as well as the thermal interface of the device. Given proper thermal design, the

FIGURE 1. Pulse-width modulated half-bridge.

device will reach a periodic steady-state within the allowed operating parameters, after a certain number of cycles. Once in steady-state, the device temperature alternates between a constant minimum and maximum. In this steady-state, the average device losses determine the operating efficiency of the inverter. Furthermore, the temperature swing experienced by the transistor is relevant for lifetime estimation, as thermal expansion of the device, and subsequent bond-wire lift-off or solder-cracks are dominant failure mechanisms in power converters [10]. With non-linearity affecting efficiency and lifetime, precise models and tools are crucial for correct optimization.

One state-of-the-art tool for simulating non-linear thermal behaviour is PLECS [11] [12]. Starting from a given initial condition, it solves the differential equations for all system-states step by step. To do this, PLECS describes the circuit as a set of state-space matrices denoting the change in electric quantities of all passive components, for all possible switching states of semiconductors. To reduce the matrix size and accelerate computation, PLECS can decouple parts of circuits where possible. More detailed information is given in [13]. While PLECS is faster than traditional time-based simulation, a search through a vast solution space still takes a significant amount of time, as several thermal cycles need to be simulated per parameter set until a steady state can be determined.

This paper presents a closed-form solution for the periodic junction-temperature and losses of devices in a power electronic converter including temperature dependence. The method is based on harmonic balance, which thus far, has been applied in power electronics for calculation of distortion caused by non-linear loads [14]. However, the methodology can be adapted to include the non-linearity of losses in calculation of the device temperature. The solution is obtained through a single matrix inversion, making the proposed method orders of magnitude faster than any time-based iterative calculation. To include second-order temperature dependencies, the method can be applied twice to further increase the accuracy. The derivation of the proposed method is covered step-by-step in Section II. Afterwards, a potential use case is demonstrated in Section III. Here, the operating point of a three-phase grid-inverter is calculated for over 1000 possible parameter combinations. The results of the proposed method are compared to simulation done in PLECS, both in accuracy as well as computation speed. In Section IV, the proposed method is compared to measurements on a three-phase SiC inverter. Finally, Section V concludes the paper.

## II. TEMPERATURE CALCULATION USING HARMONIC BALANCE

Harmonic balance has been used in circuit simulation to deal with non-linear components in otherwise linear networks [15]. The underlying assumption for harmonic balance is that a given input frequency only produces responses that can be expressed as integer multiples of itself. This allows to express all waveforms in the circuit as discrete Fourier series, and solve the response of each coefficient to the given input frequency. Because harmonic balance works in the frequency domain, differential equations from the time domain transform into algebraic operations. The resulting set of equations can be solved using standard solving methods.

#### A. POWER TRANSISTOR IN THE FREQUENCY DOMAIN

The basis for the presented method is the equation for the junction temperature of a device  $T_j(t)$ , given varying conduction losses  $P_c(t)$  and switching energies  $E_{\rm on}(t)$ ,  $E_{\rm off}(t)$  over time. The device is cooled by a thermal network with a given thermal impulse response  $z_{\rm th}(t)$ , connected to the ambient temperature  $T_0$ . The device's junction temperature is given by

$$T_i(t) = T_0(t) + z_{th}(t) * (P_c(t) + f_{sw}[E_{on}(t) + E_{off}(t)]), (1)$$

where '\*' represents a convolution between the thermal impulse response  $z_{\text{th}}(t)$  and the losses in the transistor. Transformed to the frequency domain, the convolution becomes a multiplication of the thermal impedance  $Z_{\text{th}}(j\omega)$  and the loss spectrum, leading to the temperature spectrum

$$T_{\rm i}(j\omega) = T_0(j\omega) + Z_{\rm th}(j\omega) \left( P_{\rm c}(j\omega) + f_{\rm sw} E_{\rm sw}(j\omega) \right). \tag{2}$$

The goal is to obtain the discrete Fourier series of the device temperature

$$T_{j}(t) = \sum_{k=-N}^{N} T_{j}[k] e^{jk\omega_{0}t}, \quad T_{j}[k] = T_{j}(j\omega_{0} k),$$

(3)

where each component corresponds to the temperature spectrum at discrete frequencies  $\omega_0 \, k$ . The underlying assumption is that any sinusoidal current will only cause harmonics at integer multiples of its own frequency. This assumption allows to express each Fourier coefficient of the temperature as a linear combination of the dissipated power and thermal impedance. Only a finite set of N coefficients needs to be considered, as the devices thermal network acts as a low pass and higher frequency coefficients will inevitably tend towards zero. The procedure will produce a system of linear equations for this finite set of coefficients, involving the thermal network, conduction losses and switching losses of the device. By modelling each of these in the frequency domain, including their temperature dependence, a solution for the device temperature can be obtained.

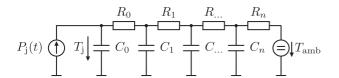

FIGURE 2. Cauer network used to model the thermal path from the device junction to ambient.

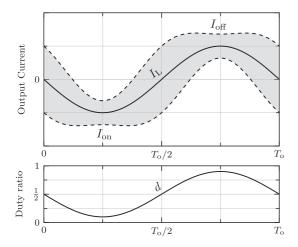

**FIGURE 3.** Inductor current during a fundamental cycle. The current ripple is centred around the load current  $I_L$  and stays between an envelope of  $I_\Delta$ , dictated by the supply voltage, output inductance, switching frequency and duty ratio.

#### **B. VECTOR NOTATION OF DISCRETE FOURIER SERIES**

To solve the set of linear equations, the discrete Fourier coefficients of each series are written as a vector

$$\vec{T}_{\mathbf{j}} = \begin{pmatrix} \dots & T_{\mathbf{j}}[-1] & T_{\mathbf{j}}[0] & T_{\mathbf{j}}[1] & \dots \end{pmatrix}^{T},$$

(4)

such that the center element corresponds to the average component at zero frequency. Components to the right correspond to positive k and components to the left to negative k. The same representation can be used for other quantities of the inverter, such as the thermal impedance  $\vec{Z}_{th}$  or the device losses  $\vec{P_c}$  and  $\vec{E_{sw}}$ .

Using this vector notation, and by writing the thermal impedance as a diagonal matrix of the discrete coefficients  $\mathbf{Z}_{th} = \text{diag}(\vec{Z_{th}})$ , the discrete form of (2) can be written as

$$\vec{T_j} = \vec{T_0} + \mathbf{Z_{th}} \left[ \vec{P_c}(T_j) + f_{sw} \vec{E_{sw}}(T_j) \right]. \tag{5}$$

#### C. THERMAL NETWORK

Each transistor has a thermal path from junction to ambient, which determines the thermal response to the power dissipated in the junction. A Cauer network can be used to model this path, as depicted in Fig. 2. Each of the consecutive

RC elements can model individual layers within the device or external layers, such as the electric insulation from the device to the heatsink or the heatsink's resistance to ambient temperature. As described in [16], the transfer function of this network can be expressed as

$$Z_{\text{th}}(j\omega) = \frac{1}{j\omega C_0 + \frac{1}{R_0 + \frac{1}{j\omega C_1 + \frac{1}{R_1 + \cdots}}}}.$$

(6)

#### D. CONDUCTION LOSSES

The basis calculation of the conduction losses is a two-dimensional lookup table  $V_{\rm ds}(i_{\rm ds},T_{\rm j})$ , which returns the device forward voltage for a given temperature and load current. The table is used to obtain the losses for ambient temperature through direct evaluation, and to model a temperature dependent component through fitting of an arbitrary curve. For simplicity of the loss calculation, the device temperature is assumed to be constant within one switching cycle, which is reasonable given that typical switching frequencies are significantly above the thermal networks cut-off frequency. To begin, the device current is expressed as the sum of the modulated output current  $I_{\rm L}$  and the superimposed current ripple, as depicted in Fig. 3. The load current can be of arbitrary shape, controlled by the modulating the duty ratio d(t) of the half-bridge. This duty ratio is expressed as

$$d(t) = \frac{T_{\rm on}(t)}{T_{\rm sw}},\tag{7}$$

where  $T_{\rm on}(t)$  is the timespan during which the device is conducting current and  $T_{\rm sw}$  is the switching period. The amplitude of the current ripple can now be written as

$$I_{\Delta}(t) = \frac{T_{\text{sw}}}{2L_{\text{o}}} d(t) (V_{\text{dc}} - v_{\text{o}}(t)).$$

(8)

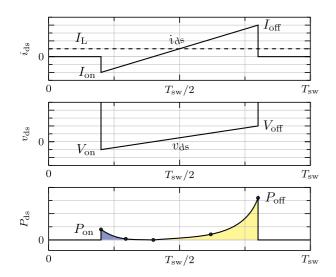

Within one switching cycle, as depicted in Fig. 4, the device current at turn-on and turn-off can be expressed as  $I_{on}$  =  $I_{\rm L}-I_{\Delta}$  and  $I_{\rm off}=I_{\rm L}+I_{\Delta}$ . At first, the conduction losses at ambient temperature are obtained from the device's look-up table by integrating the voltage current product. The current  $i_{\rm ds}$  is known from the operating parameters of the inverter, and the voltage is obtained by evaluating the look-up table  $V_{\rm ds}(i_{\rm ds},T_0)$  at ambient temperature  $T_0$ , as shown in Fig. 3(a). The integral is found using Simpson's rule, which gives an exact solution for polynomials provided single values at the beginning, center and end of the conduction interval. The calculation is done in two individual sections, to account for a potential zero crossing of the current, as indicated in Fig. 4, marked in blue and yellow. Either one becomes zero if both turn-on and turn-off current are above or below zero. The total losses at ambient are given in (9) at the bottom of this page.

$$P_{c,0}(t) = \begin{cases} \frac{I_{\text{on}}(t)}{6} [V_{\text{ds}}(I_{\text{on}}(t), T_0) + 2V_{\text{ds}}(\frac{I_{\text{on}}(t)}{2}, T_0)] + \frac{I_{\text{off}}(t)}{6} [2V_{\text{ds}}(\frac{I_{\text{off}}(t)}{2}, T_0) + V_{\text{ds}}(I_{\text{off}}(t), T_0)], I_{\text{on}} < 0 < I_{\text{off}} \\ \frac{1}{6} [I_{\text{on}}V_{\text{ds}}(I_{\text{on}}, T_0) + 4I_{\text{L}}V_{\text{ds}}(I_{\text{L}}, T_0) + I_{\text{off}}V_{\text{ds}}(I_{\text{off}}, T_0)], I_{\text{on}} < I_{\text{off}} < 0 \quad or \quad 0 > I_{\text{on}} > I_{\text{off}} \end{cases}$$

$$(9)$$

826 VOLUME 3, 2022

FIGURE 4. Conduction interval of the high-side switch. During the on-state, both device current and voltage increase. The conduction losses are obtained through multiplication of the two quantities. By splitting the conduction losses at the zero crossing, the average loss can be calculated from the mid and end points of the polynomial using Simpson's integration rule.

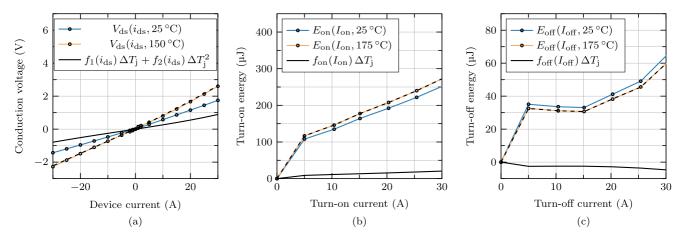

To now include the temperature dependence, the lookup table is fitted to a second-order temperature-dependent polynomial, with arbitrary functions  $f_n(i_{ds})$  for the known device current, such that

$$V_{\rm ds}(i_{\rm ds}, T_{\rm j}) = V_{\rm ds}(i_{\rm ds}, T_{\rm 0}) + f_{\rm 1}(i_{\rm ds}) \Delta T_{\rm j} + f_{\rm 2}(i_{\rm ds}) \Delta T_{\rm j}^2,$$

(10)

where  $\Delta T_{\rm j} = T_{\rm j} - T_{\rm 0}$ . Analogue to (9), the linear and quadratic dependencies can be formulated as  $P_{\rm c,1}$  and  $P_{\rm c,2}$ , proportional to the linear or square of the temperature. The conduction losses can then be expressed as

$$P_{c}(t) = P_{c,0}(t) + P_{c,1}(t) \Delta T_{i}(t) + P_{c,2}(t) \Delta T_{i}(t)^{2}.$$

(11)

From this expression in the time domain, the spectrum of the conduction losses can be obtained through a Fourier transform, yielding

$$P_{c}(j\omega) = P_{c,0}(j\omega) + [P_{c,1}(j\omega) + P_{c,2}(j\omega) * \Delta T_{j}(j\omega)] * \Delta T_{j}(j\omega).$$

(12)

Using the vector notation described in subsection II-B, the coefficients of the conduction loss spectrum can be formulated as

$$\vec{P_{\rm c}} = \vec{P_{\rm c,0}} + \vec{P_{\rm c,T}} \, \vec{\Delta T_{\rm j}},\tag{13}$$

where  $P_{c,T}$  is a Toeplitz matrix<sup>1</sup> built from

$$P_{\rm c,T}(j\omega) = P_{\rm c,1}(j\omega) + P_{\rm c,2}(j\omega) * \Delta T_{\rm i}(j\omega). \tag{14}$$

Multiplication of a vector with a Toeplitz matrix carries out the convolution of two discrete Fourier series.  $P_{c,T}$  still contains the unknown junction temperature resulting from the

second-order terms. This issue is addressed by assuming  $\vec{T}_{\rm j} = \vec{T}_{\rm 0}$  for the initial calculation of  $P_{\rm c,T}$  and  $\vec{T}_{\rm j}$ , and a subsequent second iteration with the resulting  $\vec{T}_{\rm j}$ . Further iteration is possible to improve the results, but little benefit is found for more than two iterations.

#### E. SWITCHING LOSSES

The switching losses are the sum of the switching energy dissipated in the device each switching cycle at turn-on and turn-off. Again, due to the low pass behaviour of thermal network, the nearly impulse-like switching energy can be averaged over one cycle, yielding

$$P_{\rm sw}(t) = f_{\rm sw} (E_{\rm on}(t) + E_{\rm off}(t)).$$

(15)

For brevity, this section only covers the derivation of the turnon losses  $E_{\rm on}(t)$ . The turn-off losses  $E_{\rm on}(t)$  are obtained using the same methodology and the resulting model is included.

The turn-on losses depend on the device current at the beginning of the conduction interval, previously established as  $I_{\text{on}}$ . Depending on the direction of this current, the device will either experience a hard-switched commutation, dissipating a significant amount of energy, or a soft commutation with little to no energy loss.

PLECS deals with this behaviour through a look-up table  $E_{\rm on}(I_{\rm on},T_{\rm j})$  and interpolation between the discrete values. The PLECS loss model for a MOSFET is depicted in Fig. 5(b). For the calculation with harmonic balance, similar as with the conduction losses, the turn-on losses are formulated as an ambient component  $E_{\rm on,0}=E_{\rm on}(I_{\rm on},T_{\rm 0})$ , obtained directly through the loss table, and a part with linear temperature dependence  $E_{\rm on,T}=f_{\rm on}(I_{\rm on})\Delta T_{\rm j}$ . The arbitrary function  $f_{\rm on}(I_{\rm on})$  is chosen, such that

$$E_{\text{on}}(I_{\text{on}}, T_{j}) = E_{\text{on}}(I_{\text{on}}, T_{0}) + B_{\text{on}}(I_{\text{on}}) f_{\text{on}}(I_{\text{on}}) \Delta T_{j}.$$

(16)

As most loss models have zero losses for soft-commutation, the fit  $f_{\rm on}(I_{\rm on})$  only needs to be correct for positive turn-on currents. To eliminate the wrong values when  $f_{\rm on}$  is evaluated at negative turn-on currents, the resulting energy is multiplied with a boolean function

$$B_{\rm on}(I_{\rm on}) = \begin{cases} 1, & \text{for } I_{\rm on} \ge 0\\ 0, & \text{otherwise} \end{cases}, \tag{17}$$

blanking any values when the inverter is operating in softcommutation.

The turn-on losses over time can then be expressed as

$$E_{\text{on}}(t) = E_{\text{on},0}(t) + E_{\text{on},T}(t) \Delta T_{i}(t),$$

(18)

which can be transformed into the frequency domain as

$$E_{\rm on}(j\omega) = E_{\rm on,0}(j\omega) + E_{\rm on,T}(j\omega) * \Delta T_{\rm i}(j\omega). \tag{19}$$

Same as with the conduction losses, the vector form of the turn-on loss spectrum is obtained by construction of a Toeplitz matrix  $E_{\text{on,T}}$  from the temperature dependent spectrum  $E_{\text{on,T}}(j\omega)$ , resulting in

$$\vec{E_{\text{on}}} = \vec{E_{\text{on},0}} + \vec{E_{\text{on},T}} \, \vec{\Delta T_{\text{i}}}. \tag{20}$$

<sup>&</sup>lt;sup>1</sup>A Toeplitz matrix *A* is constructed from a vector  $\vec{a}$  by  $A_{i,j} = a_{i-j}$ .

FIGURE 5. Device-loss look-up-table from the device manufacturer (blue, yellow) and fitted loss-model(black) for (a) conduction voltage, (b) turn-on energy and (c) turn-off energy at 700 V. The fitting functions are evaluated at a  $\Delta T_j$  of 125 °C for the conduction voltage and 150 °C for the turn-on and turn-off energies. When added to the table values of 25 °C, they match the look-up tables at 150 °C and 175 °C respectively (dashed lines). The switching loss fits are only valid for positive device currents. For correct calculation of the switching losses over the fundamental period, the polynomial is multiplied with a boolean function which is zero at times of negative device current, to eliminate the invalid fitting functions.

The same steps can be followed to obtain the expression

$$\vec{E_{\text{off}}} = \vec{E_{\text{off,0}}} + \vec{E_{\text{off,T}}} \, \vec{\Delta T_{\text{i}}}, \tag{21}$$

for the turn-off losses, using the turn-off current  $I_{\rm off}$ , its corresponding look-up table and boolean function  $B_{\rm off}$ . With all loss components modelled in vector format, the initial equation for the junction temperature is solved.

#### F. SOLVING FOR THE JUNCTION TEMPERATURE

Using the vector notation, (2) can be rewritten using the conduction losses (13), turn-on (20) and turn-off losses (21), resulting in

$$\vec{T_{j}} = \vec{T_{0}} + \mathbf{Z_{th}} \left[ \vec{P_{c,0}} + \mathbf{P_{c,T}} \Delta \vec{T_{j}} + f_{sw} \left( \vec{E_{on,0}} + \mathbf{E_{on,T}} \Delta \vec{T_{j}} + \vec{E_{off,0}} + \mathbf{E_{off,T}} \Delta \vec{T_{j}} \right) \right].$$

(22)

The terms proportional to  $\Delta \vec{T_{\rm j}}$  can be collected and  $T_0$  subtracted to obtain

$$\Delta \vec{T}_{j} = \vec{T}_{j} - \vec{T}_{0} = \mathbf{Z}_{th} \left( \vec{P}_{c,0} + f_{sw}(\vec{E}_{on,0} + \vec{E}_{off,0}) \right) + \mathbf{Z}_{th} \left( \mathbf{P}_{c,T} + f_{sw}(\mathbf{E}_{on,T} + \mathbf{E}_{off,T}) \right) \Delta \vec{T}_{j}.$$

(23)

Subsequent subtraction and inversion of these terms yield

$$\Delta \vec{T}_{j} = \left[ \boldsymbol{I} - \boldsymbol{Z}_{th} \left( \boldsymbol{P}_{c,T} + f_{sw}(\boldsymbol{E}_{on,T} + \boldsymbol{E}_{off,T}) \right) \right]^{-1}$$

$$\boldsymbol{Z}_{th} \left( \vec{P}_{c,0} + f_{sw}(\vec{E}_{on,0} + \vec{E}_{off,0}) \right), \tag{24}$$

the solution for the increase in junction temperature.

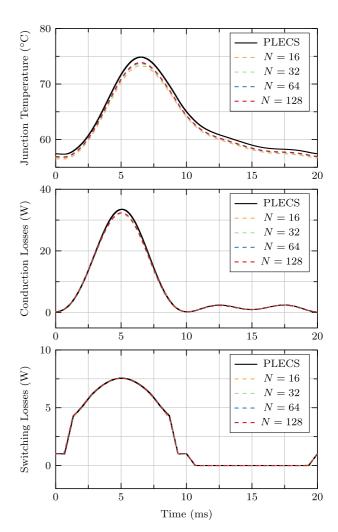

Fig. 6 shows the obtained temperature and losses for the high-side switch of the inverter specified in Table 1 and the fitting functions for the transistor are shown in Table 2. The results from harmonic balance are compared against a reference simulation in PLECS. Both files for simulation and

FIGURE 6. Results obtained with harmonic balance (dashed lines) compared to simulation in PLECS (solid line). N denotes the number of harmonics used for harmonic balance, where the first harmonic corresponds to the fundamental of the output current.

828 VOLUME 3, 2022

**TABLE 1. Inverter Parameters**

| Parameter                  | Symbol                 | Value                                |

|----------------------------|------------------------|--------------------------------------|

| Switching frequency        | $f_{ m sw}$            | $30\mathrm{kHz}$                     |

| Output frequency           | $f_{\mathrm{o}}$       | $50\mathrm{Hz}$                      |

| Supply voltage             | $V_{ m dc}$            | $700\mathrm{V}$                      |

| Grid voltage               | $V_{\mathrm{grid}}$    | $230\mathrm{Vrms}$                   |

| Transistors                | $Q_1, Q_2$             | C3M0065100K                          |

| Output current             | $I_{ m o}$             | $16\mathrm{Arms}$                    |

| Output inductor            | $L_{\rm o}$            | $600\mu\mathrm{H}$                   |

| Ambient temperature        | $T_0$                  | 40 °C                                |

| External thermal interface | $R_{ m th}, C_{ m th}$ | $1 \frac{K}{W}$ , $0.05 \frac{J}{K}$ |

TABLE 2. Polynomial Fits for the Losses of a SiC Transistor (C3M0065100 K)

$$\begin{split} f_1(i_{\rm ds}) &= 26.82 \, \frac{\mu \rm J}{\rm A} \, i_{\rm ds} 319.45 \, \frac{\rm nJ}{\rm A^2} \, i_{\rm ds}^2 + 23.23 \, \frac{\rm nJ}{\rm A^3} \, i_{\rm ds}^3 \\ f_2(i_{\rm ds}) &= 1.41 \, \frac{\mu \rm J}{\rm A^3} \, i_{\rm ds} + 0.96 \, \frac{\rm pJ}{\rm A^4} \, i_{\rm ds}^4 \\ f_{\rm on}(I_{\rm on}) &= 37.4 \, \frac{\rm nJ}{\sqrt{\rm A}} \, I_{\rm on}^{0.5} - 5.77 \, \frac{\rm nJ}{\rm A} \, I_{\rm on} + 0.15 \, \frac{\rm nJ}{\rm A^2} \, I_{\rm on}^2 - 1.15 \, \frac{\rm pJ}{\rm A^3} \, I_{\rm on}^3 \\ f_{\rm off}(I_{\rm off}) &= -17 \, \frac{\mu \rm J}{\sqrt{\rm A}} \, I_{\rm off}^{0.5} + 4.7 \, \frac{\mu \rm J}{\rm A} \, I_{\rm off} - 0.1 \, \frac{\rm nJ}{\rm A^2} \, I_{\rm off}^2 + 0.42 \, \frac{\rm pJ}{\rm A^3} \, I_{\rm off}^3 \end{split}$$

calculation are uploaded in conjunction with this paper [18]. The PLECS simulation requires an active PLECS standalone license, the harmonic balance method is implemented in python3, which is open source. The semiconductor loss models are available at the manufacturer's website.

Already a very low number of harmonics N=16 yields good accuracy in power losses and temperature. For a higher number of harmonics the calculated temperature approaches the shape of the simulated reference, but at a slight offset. The difference in average temperature can be explained by the slightly lower peak conduction losses. Still, the rest of the curve matches well with simulation results. The switching losses also show very good agreement, with a slight improvement at larger N for the discontinuous sections, where the device enters soft-commutation. To show how the proposed method can be used for fast evaluation and design of inverters, the next section will explore a multitude of operating points for a three-phase inverter, again using PLECS as reference, for both accuracy as well as computation time.

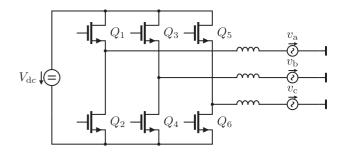

## III. DESIGN SPACE EXPLORATION OF A THREE-PHASE SPWM GRID INVERTER

To demonstrate the speed and accuracy of the proposed method, a three-phase grid-inverter, as depicted in Fig. 7, is analysed by search through a vast design space. This space, given in Table 3, spans different load currents, switching frequencies, as well as different filter sizes, yielding a total of 1014 possible combinations. As an application example, the load current is stepped through the profile of the European Efficiency for solar inverters, given by

$$\eta_{\text{euro}} = 0.03\eta_{5\%} + 0.06\eta_{10\%} + 0.13\eta_{15\%}

+ 0.10\eta_{30\%} + 0.48\eta_{50\%} + 0.20\eta_{100\%},$$

(25)

FIGURE 7. Bi-directional three-phase grid-inverter.

**TABLE 3.** Design Space and Runtime of Simulation

| Parameter                        | Symbol           | Value                                    | Steps |

|----------------------------------|------------------|------------------------------------------|-------|

| Line frequency                   | $f_{ m g}$       | 50 Hz -                                  |       |

| Line voltage                     | $v_{\rm a,b,c}$  | 230 VAC -                                |       |

| Ambient temperature              | $T_{ m amb}$     | 40 °C -                                  |       |

| Supply voltage                   | $V_{ m dc}$      | $700\mathrm{V}$                          |       |

| Switching frequency              | $f_{ m sw}$      | $10\mathrm{kHz}$ to $70\mathrm{kHz}$     | 13    |

| Line current                     | $I_{ m o,rms}$   | 0.8 A/1.6 A/3.2 A                        |       |

|                                  |                  | $4.8\mathrm{A/8}\mathrm{A/16}\mathrm{A}$ | 0     |

| Output Inductor                  | $L_{\mathrm{o}}$ | 400 μH to 1000 μH 13                     |       |

| Transistors                      | $Q_{16}$         | C3M0065100K                              | -     |

| Total number of simulations      |                  | 1014                                     |       |

| Runtime PLECS                    |                  | $18 \min  23  \mathrm{s}$                |       |

| Runtime Harm. Balance $(N = 32)$ |                  | $0 \min 11 s$                            |       |

| Runtime Harm. Balance $(N = 64)$ |                  | $0\mathrm{min}\ 25\mathrm{s}$            |       |

| Runtime Harm. Balance (N = 128)  |                  | $1 \min 10 s$                            |       |

where  $\eta_{xx}$  is the inverter efficiency at the indicated percentage of maximum load current. For simplicity, the inductive component is treated as lossless, but its impact on the semi-conductor losses is considered.

The results obtained through harmonic balance are compared to simulations done in with the PLECS, serving as reference for state-of-the-art steady-state-solvers. Both the harmonic balance method and PLECS use the same look-up table for the device losses, available from the device manufacturer. Thus any discrepancy can be entirely addressed to the proposed method.

For now, both simulation and calculation do not include dead-time, which can become a noticeable contributor to losses at higher switching frequencies [19]. Next to additional losses, dead-time leads to distortion in the output voltage of the inverter [20], which would result in different current ripple and modulation of the device, hindering a direct comparison between calculation and simulation.

#### A. SIMULATION AND CALCULATION SETUP

Within PLECS, the steady-state analysis tool is used to obtain the device temperature and losses of a single grid cycle. For a fair comparison, both PLECS and the harmonic balance method are run on the same machine (Intel Core i5-7500), as single threaded applications. In a practical scenario, paralleled

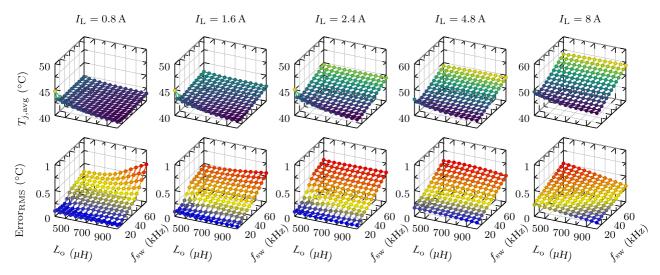

FIGURE 8. Calculation results over one grid cycle in a three phase grid-tied inverter, obtained using harmonic balance (N=128). The load current ranges from 0.8 A to 8 A. Each upper plot displays the average device temperature over one grid cycle, the lower plots show the rms error over the entire period between the calculated waveform and simulation in PLECS.

computation time of both methods. To evaluate each method's computation time, and not the machine's disk speed, both methods are run without saving of the time domain waveforms, as this significantly affects the time spent by each method. Moreover, the time PLECS takes is extremely dependent on tolerances and other settings. Thus, PLECS is kept at the default parameters preset after installation. The analysis settings and scripts are included within the attached model files.

#### B. RESULTS

The runtime of each program is listed in Table 3, with PLECS taking 18 min 23 s to analyze all 1014 possible circuit variations. In contrast, harmonic balance run at N=32 harmonics finishes after 11 s. For slightly higher accuracy, the number of harmonics can be increased to N=128, which leads to a computation time of 1 min 10 s, still considerably faster than PLECS.

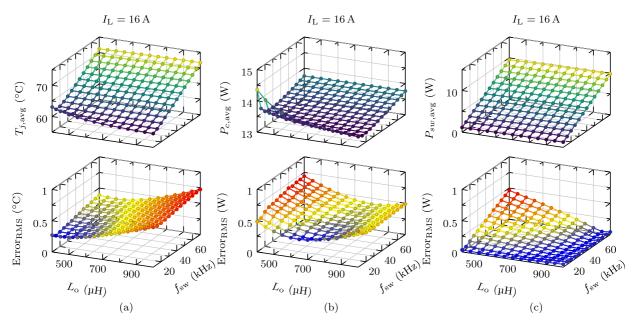

The calculation results are shown in Fig. 8. The upper set of plots show the average junction temperature for load currents from 0.8 A to 8 A over one fundamental cycle obtained with harmonic balance. To quantify how close the calculation is to simulation, the plots below show the rms error in temperature, calculated by

$$\text{Error}_{\text{RMS}} = \sqrt{\frac{1}{T_0} \int_0^{T_0} (T_{\text{j,PLECS}}(t) - T_{\text{j,Harm.Balance}})^2 dt}.$$

For all operating points, the error stays well below 1 °C. Fig. 9 shows the temperature, conduction and switching losses at a load current of 16 A and their respective rms error to PLECS. Again, the error stays below 1 °C and 1 W respectively. At low inductance and low switching frequency, the high current ripple leads to increased conduction losses. Increasing the

**TABLE 4. Setup Parameters**

| Parameter                    | Symbol           | Value                               |

|------------------------------|------------------|-------------------------------------|

| Switching frequency          | $f_{ m sw}$      | $10\mathrm{kHz}$                    |

| Output frequency             | $f_{\mathrm{o}}$ | $50\mathrm{Hz}$                     |

| Supply voltage               | $V_{ m dc}$      | $400\mathrm{V}$                     |

| Output inductor              | $L_{\mathrm{o}}$ | $5\mathrm{mH}$                      |

| Dead-time                    | $T_{\rm d}$      | $1\mu \mathrm{s}$                   |

| Rms output current           | $I_{ m o,rms}$   | $5\mathrm{A}$ to $10\mathrm{A}$     |

| Load cycle frequency         | $f_{ m pulse}$   | $0.1\mathrm{Hz}$                    |

| Load resistance              | $R_{\rm load}$   | $10\Omega$                          |

| Ambient Temperature          | $T_0$            | $25^{\circ}\mathrm{C}$              |

| Heatsink thermal resistance  | $R_{ m th,ca}$   | $1.1 \frac{\mathrm{K}}{\mathrm{W}}$ |

| Heatsink thermal capacitance | $C_{ m th,ca}$   | $7.7\frac{\ddot{J}}{K}$             |

|                              |                  |                                     |

switching frequency reduces the conduction losses at first, at a cost of increased switching losses. By further increasing the switching frequency, the feedback effect mentioned in section I sets in: The conduction losses begin to rise, as the increased switching losses heat the device, resulting in higher on-state resistance, and thus larger conduction losses.

For real-world verification, the following section will compare the proposed harmonic balance method to a three-phase inverter, where the junction-temperature of each device can obtained through a high-resolution measurement of the drain-source voltage during conduction.

#### IV. EXPERIMENTAL RESULTS

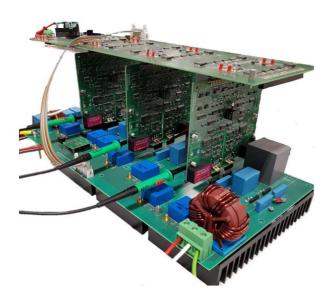

The harmonic-balance method is further validated by experiment with a 400 V three-phase SiC inverter, depicted in Fig. 10. The setup parameters are listed in Table 4. The temperature of the transistors is obtained by measurement of the drain-source voltage during conduction. The detailed setup is described in [21]. The measurement is limited by a

830 VOLUME 3, 2022

(26)

FIGURE 9. Calculation results over one grid cycle in a three phase grid-tied inverter, obtained using harmonic balance (N=128), at a load current of 16 A. The upper plots depict the average quantity over one grid cycle and the lower plots the respective rms error to PLECS for (a) junction-temperature, (b) conduction losses, and (c) switching losses.

FIGURE 10. Experimental setup for measuring junction temperature swing. Three-phase inverter with clamping circuits to measure the drain-source voltage during conduction.

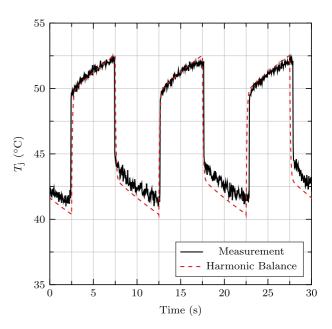

clamp circuit to obtain sufficient resolution. In combination with a measurement of the load current, the device temperature is obtained through a look-up table. To cycle the device temperature, the inverter supplies a 50 Hz sinusoidal load current with varying amplitude to a 10  $\Omega$  resistive load. The amplitude is stepped from 5 A to 10 A in 5 s intervals. The resulting temperature cycle is depicted in Fig. 11, alongside the calculation using harmonic balance. Due to the vast difference in load cycle and output frequency, the matrices become immense and calculation for one cycle takes

FIGURE 11. Measured temperature cycle compared to calculation using harmonic balance. The calculation result has an offset and amplitude error of about 0.5 °C. Due to imprecise timing of the load pulse generated by the microcontroller, the pulse duration slightly deviates from the programmed 5 s interval. As a result, the early pulses slightly overshoot the calculated response, as the device has less time to cool down. The delayed pulses, on the other hand, undershoot the calculated response, as the device is given slightly more time to cool down.

several seconds. The matrices now contain frequency components up to several 100 Hz at a step size of 100 mHz, which significantly slows down the matrix inversion. Still, the calculation shows good agreement with the measured device temperature. The mismatch between measurement and

calculation is within of 2 °C. Next to possible discrepancies between device and the manufacturer's loss model, the neglect of dead-time losses does affect the calculation result.

#### V. CONCLUSION

The calculation of device temperature using harmonic balance offers a fast, precise alternative to iterative steady-state solvers, which includes temperature dependence and saturation effects. The results match simulations obtained with commercial state-of-the-art steady-state solvers. Furthermore, good agreement is shown between calculation and measurement results of a 400 V three-phase SiC inverter. The steady state is calculated given a temperature dependent look-up table for the device losses available from the manufacturer, as well as the device current and duty ratio. For well known topologies, these operating parameters are easily written analytically. Otherwise, harmonic balance could serve as an addition to steady-state solvers, producing a solution after the device operating parameters are obtained through a first simulation cycle.

Several aspects of the presented method can be improved for more accurate results and universal application. As previously addressed, dead-time was omitted to simplify the analytic description of the inverter's output voltage and to limit potential error sources. For future work, dead-time losses need to be added as a term proportional to the switching frequency, including load current and temperature dependence. Furthermore, the conduction losses are calculated assuming a triangular output current, as is the case for PWM inverters or buck/boost converters. To extend application of the harmonic-balance calculation method to other topologies, different load current shapes have to be modelled, such as sinusoidal waveforms for resonant converters, or trapezoidal waveforms for active-bridge converters.

In combination with analytic loss models such as [9], it could enable fast, fully analytic evaluation of a power stage solely from the transistor datasheet. Next to thermal design of the inverter, the obtained temperature cycles can serve as input for life-time estimations [22]. State-of-the-art calculation methods for inductor and capacitor losses could be added to optimize the complete system [23], [24]. Beyond design of inverters, a possible application of harmonic balance could be over-temperature protection. Given that harmonic balance only requires standard matrix functions, it could be implemented on capable DSPs used to control the inverter. As the calculation produces the inverter's steady-state response, the controller could predict over-temperature of the transistors, before their thermal network reaches the undesired operating point and limit the load current to prevent this.

Harmonic balance performs best at small timescales, such as 50 Hz to 60 Hz grid cycles, up to several seconds for step responses of the thermal network, due to the required matrix inversion. For longer periods, such as drive cycles for electric vehicle inverters, the system matrix becomes extremely large, as it would contain frequency components in the kHz range

for the load current, down to components in the mHz range for the driving profile. As the computation time for matrix inversion grows exponentially with size, iterative methods would become the faster option. Further research is necessary to see if simplified, reduced timescale models would provide sufficient accuracy.

#### REFERENCES

- [1] M. Mirjafari and R. S. Balog, "Survey of modelling techniques used in optimisation of power electronic components," *IET Power Electron.*, vol. 7, no. 5, pp. 1192–1203, 2014. [Online]. Available: https:// ietresearch.onlinelibrary.wiley.com/doi/abs/10.1049/iet-pel.2013.0321

- [2] R. Barrera-Cárdenas and M. Molinas, "9 modelling of power electronic components for evaluation of efficiency, power density and power-to-mass ratio of offshore wind power converters," in *Offshore Wind Farms*, C. Ng and L. Ran, Eds. Sawston, U.K.: Woodhead Publishing, 2016, pp. 193–261. [Online]. Available:https://www.sciencedirect.com/science/article/pii/B978008100779200009X

- [3] T. Bruckner and S. Bernet, "Estimation and measurement of junction temperatures in a three-level voltage source converter," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 3–12, Jan. 2007.

- [4] N. Langmaack, T. Schobre, and M. Henke, "Fast and universal semiconductor loss calculation method," in *Proc. IEEE 13th Int. Conf. Power Electron. Drive Syst.*, 2019, pp. 1–4.

- [5] Y. Yang et al., "A fast and accurate thermal-electrical coupled model for sic traction inverter," in *Proc. IEEE Transp. Electrific. Conf. Expo*, 2021, pp. 496–501.

- [6] Z. Yang et al., "Resolving loss discrepancy between calculation and measurement in a 4.5 kw gan-based inverter," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2019, pp. 4409–4414.

- [7] J. Kolar, H. Ertl, and F. Zach, "Influence of the modulation method on the conduction and switching losses of a pwm converter system," in *Proc. Conf. Rec. IEEE Ind. Appl. Soc. Annu. Meeting*, 1990, pp. 502– 512.

- [8] G. Engelmann, M. Laumen, J. Gottschlich, K. Oberdieck, and R. W. De Doncker, "Temperature-controlled power semiconductor characterization using thermoelectric coolers," *IEEE Trans. Ind. Appl.*, vol. 54, no. 3, pp. 2598–2605, May/Jun. 2018.

- [9] M. Haider, S. Fuchs, G. Zulauf, D. Bortis, J. W. Kolar, and Y. Ono, "Analytical loss model for three-phase 1200V SiC MOSFET inverter drive system utilizing miller capacitor-based DV/DT-limitation," *IEEE Open J. Power Electron.*, vol. 3, pp. 93–104, 2022.

- [10] C. H. van der Broeck, L. A. Ruppert, R. D. Lorenz, and R. W. De Doncker, "Methodology for active thermal cycle reduction of power electronic modules," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 8213–8229, Aug. 2019.

- [11] J. Alimeling and W. Hammer, "Plecs-piece-wise linear electrical circuit simulation for simulink," in *Proc. IEEE Int. Conf. Power Electron. Drive Syst.*, 1999, vol. 1, pp. 355–360.

- [12] P. Górecki and D. Wojciechowski, "Accurate computation of IGBT junction temperature in PLECS," *IEEE Trans. Electron Devices*, vol. 67, no. 7, pp. 2865–2871, Jul. 2020.

[13] Plexim, "Model optimization," 2022. Accessed: Oct. 20, 2022. [On-

- [13] Plexim, "Model optimization," 2022. Accessed: Oct. 20, 2022. [Online]. Available: https://www.plexim.com/sites/default/files/tutorials/ model\_optimization.pdf

- [14] J. Lu, "Harmonic balance methods used in power electronics and distributed energy system," in *Proc. IEEE Int. Power Electron. Appl. Conf. Expo.*, 2018, pp. 1–6.

- [15] P. Feldmann, B. Melville, and D. Long, "Efficient frequency domain analysis of large nonlinear analog circuits," in *Proc. Custom Integr. Circuits Conf.*, 1996, pp. 461–464.

- [16] T. C. Fry, "The use of continued fractions in the design of electrical networks," *Bull. Amer. Math. Soc.*, vol. 35, no. 4, pp. 463–498, 1929. [Online]. Available: https://doi.org/10.1090/S0002-9904-1929-04747-5

- [17] P. Weiler, "Python implementation of harmonic balance algorithm," Sep. 2022. [Online]. Available: https://gitlab.tue.nl/epe/harmonic-balance

- [18] P. Weiler, B. Vermulst, E. Lemmen, and K. Wijnands, "Steady-state temperature calculation of transistors using harmonic balance," 2022. [Online]. Available: https://codeocean.com/capsule/0453273/tree/v1

832 VOLUME 3, 2022

- [19] A. Acquaviva, A. Rodionov, A. Kersten, T. Thiringer, and Y. Liu, "Analytical conduction loss calculation of a mosfet three-phase inverter accounting for the reverse conduction and the blanking time," *IEEE Trans. Ind. Electron.*, vol. 68, no. 8, pp. 6682–6691, Aug. 2021.

- [20] Q. Yu, E. Lemmen, and B. Vermulst, "A numerical method for calculating the output spectrum of an h-bridge inverter with dead-time based on switching mode analysis," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2019, pp. 2245–2251.

- [21] L. Wang, B. Vermulst, J. Duarte, and H. Huisman, "Thermal stress reduction of power mosfet in electric drive application with dynamic gate driving strategy," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2021, pp. 720–727.

- [22] F. Hoffmann, N. Kaminski, and S. Schmitt, "Comparison of the power cycling performance of silicon and silicon carbide power devices in a baseplate less module package at different temperature swings," in *Proc.* 33rd Int. Symp. Power Semicond. Devices ICs, 2021, pp. 175–178.

- [23] P. Papamanolis, T. Guillod, F. Krismer, and J. W. Kolar, "Minimum loss operation and optimal design of high-frequency inductors for defined core and litz wire," *IEEE Open J. Power Electron.*, vol. 1, pp. 469–487, 2020.

- [24] D. Menzi, M. Heller, and J. W. Kolar, "iGSE-C<sub>x</sub> A new normalized steinmetz model for class II multilayer ceramic capacitors," *IEEE Open J. Power Electron.*, vol. 2, pp. 138–144, 2021.

**PELLE WEILER** (Graduate Student Member, IEEE) received the M.Sc degree from RWTH Aachen, Aachen, Germany, in 2018. He is currently working toward the Ph.D. degree with the Electromechanics and Power Electronics Group, Eindhoven University of Technology, Eindhoven, The Netherlands. His main research interests include power electronics with a focus on high-precision applications, wide-bandgap semiconductors, and high frequency magnetics.

BAS VERMULST (Member, IEEE) received the M.Sc. and Ph.D. degrees from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 2012 and 2016, respectively. He is currently an Assistant Professor with the Electromechanics and Power Electronics Group, Eindhoven University of Technology. He has also been employed for several years as an Engineer and System Architect with high-tech industries around Eindhoven. His main research interests include power electronics and control, high-frequency switched mode power supplies, high-precision applications, and automotives

**ERIK LEMMEN** received the B.Eng. degree (cum laude) in electrical engineering from the Fontys University of Applied Sciences, Eindhoven, The Netherlands, in 2009, and the M.Sc. and Ph.D. degrees (cum laude) in power electronics from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 2013 and 2017, respectively. He is currently a Development Engineer and System Architect with the high-tech Industry in Eindhoven, and also as a part-time Research Assistant with the Electromechanics and Power Electronics Group, Eindhoven University of Technology. His research interests include multilevel topologies, redundancy in power converters, and modular converter structures.

KORNEEL WIJNANDS (Member, IEEE) received the M.Sc. degree in electrical engineering from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 1994. In 1994, he joined Prodrive Technologies B.V., where he started to work on the development of power electronics and control. He is currently a Senior Electronics Architect with Prodrive Technologies B.V., Son, The Netherlands. In 2009, he became a part-time Assistant Professor with the Electromechanics and Power Electronics Group, Eindhoven University of Technology, where he has been a Full Professor since 2017. He is currently a part-time Professor with the Electrical Energy Systems Group, Eindhoven University of Technology. His research interests include high precision amplifiers and smart grid electronics.