### Characterization and Acceleration of High Performance **Compute Workloads**

Citation for published version (APA):

Corda, S. (2022). Characterization and Acceleration of High Performance Compute Workloads. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Eindhoven University of Technology.

#### Document status and date:

Published: 19/12/2022

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

#### Characterization and Acceleration of High Performance Compute Workloads

#### THESIS

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op maandag 19 december 2022 om 11:00 uur

door

Stefano Corda

geboren te Moncalieri, Italië

Dit proefschrift is goedgekeurd door de promotor en de samenstelling van de commissie is als volgt:

Voorzitter: prof.dr.ir. A. M. J. Koonen Promotoren: prof.dr. H. Corporaal

prof.dr.ir. A. Kumar (Technische Universität Dresden)

Copromotor: dr.ir. R. Jordans

Promotiecommissieleden: dr.ir. A.B.J. Kokkeler (University of Twente)

prof.dr.ing. D. Goehringer (Technische Universität Dresden)

prof.dr.ir. P.H.N. de With

Adviseur: dr. J. Romein (ASTRON)

dr. A.J. Awan (Ericsson)

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# Characterization and Acceleration of High Performance Compute Workloads

Stefano Corda

#### Doctorate committee:

prof.dr. H. Corporaal prof.dr.ir. A. Kumar dr.ir. R. Jordans prof.dr.ir. A. M. J. Koonen prof.dr.ir. D. Göhringer prof.dr.ir. A. B. J. Kokkeler prof.dr.ir. P.H.N. de With dr. J. R. Romein dr. A. J. Awan

Eindhoven University of Technology,  $1^{st}$  promotor Dresden Technical University,  $2^{nd}$  promotor Eindhoven University of Technology copromotor Eindhoven University of Technology, chairman Dresden Technical University University of Twente Eindhoven University of Technology ASTRON Ericsson Sweden

This work was supported in part by the European Commission by the Horizon 2020 Program for the Project "Near-Memory Computing (NeMeCo)" through the Marie Sklodowska-Curie Innovative Training Networks European Industrial Doctorate under Project 676240.

#### © Copyright 2022, Stefano Corda

All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

ISBN: 978-90-386-5633-5

A catologue record is available from the Eindhoven University of Technology Library.

## Acknowledgements

This doctoral thesis finally concludes a long period of studies and research. The Ph.D. journey improved me both professionally and personally. This section acknowledges those who supported and helped me directly and indirectly during my Ph.D.

I am deeply grateful to my supervisors, Henk, Akash, and Roel, for their invaluable advice, continuous support, and patience during my Ph.D. study. Thanks Henk, for the rigorous feedback on papers and for teaching me how to conduct impactful research. I am grateful to Akash for allowing me to join his research group and supporting me in writing funding proposals. Thanks Roel, for your precious guidance and assistance in supervising Master' students, which I would also like to thank.

I would like to thank the Committee for reading the thesis and providing valuable feedback to improve the quality of the manuscript.

This work was only possible with inspiring and brilliant collaborators. I am grateful to Ahsan for providing his immense knowledge of application profiling and hardware. I had the pleasure of collaborating with researchers at ASTRON over these years: Albert-Jan, John, and Bram. Thanks you all for your support and, in particular, Bram for the innumerable long discussions on IDG and HPC. Special thanks to my colleagues at the Electronics System Group, the Parse, and the Nemeco team at TU/e and the Processor Design Chair at Dresden Technical University for providing an enjoyable working environment.

A big thanks to my family, in-law family, and friends for the support and blessing. I would like to express my deepest gratitude to my parents, Pia and Antonello. Thanks for growing me with the desire to learn and improve myself. Thanks also for your love and support during all my life steps and studies.

Above all, I would like to thank my loving wife, Ilenia, for always supporting me throughout all moments of my Ph.D and encouraging me to do my best on every occasion. Knowing that you were at my side made everything easier. Thanks for your patience when I was stressed, for the free time spent on this thesis, and for making sacrifices while living in different countries. I am deeply grateful for your being my partner for 10 years and for many more yet to come.

i

### Abstract

Modern big-data workloads have demanding performance requirements. This leads to compute and memory bottlenecks. These applications comprise, among others, radio-astronomical imaging, machine learning and bioinformatics algorithms. For instance, the future generation of radio-telescopes, such as the Square Kilometre Array (SKA), will have to process a massive quantity of data (in the order of Terabytes per second per antenna) using high-performance computing systems (in the order of Exaflop per second) with high energy efficiency.

With the demise of Dennard scaling and slowing down of Moore's law, computing performance is hitting a plateau. Furthermore, the improvements in memory and processor technology have grown at different speeds, infamously termed the memory wall. These challenges make it difficult to meet the requirements of such demanding applications.

A promising solution to bridge this gap is represented by High-Performance Computing (HPC), which uses modern architectures such as multi-core CPUs, GPUs, and FPGAs to accelerate workloads by optimizing the code to exploit performance close to their limits. Furthermore, among today's emerging computing paradigms, Near-Memory Computing (NMC) rises. NMC is a data-centric computation approach that performs the computation near the memory, avoids data movements that characterize classical compute-centric systems, and potentially is a candidate for high-performance computing.

With the advent of numerous emerging computing systems, it has become crucial to characterize applications for highlighting performance bottlenecks and optimization opportunities. Moreover, algorithm optimization and acceleration are key factors for providing high performance on modern computing systems. However, contemporary workloads do not perform equally on different systems, e.g., GPUs and FPGAs. This leads to a careful selection of application-domain architectures and optimizations. To overcome the abovementioned issue, we need to investigate application characterization techniques aided with machine learning for efficient offloading decisions and optimize the performance bottlenecks in radio-astronomical imaging applications on heterogeneous architectures.

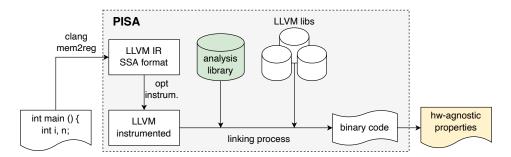

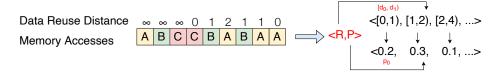

The thesis focuses on providing key contributions toward application profiling and optimization for high-performance computing systems. It extends the state-of-the-art Platform-Independent Software Analysis (PISA) with metrics concerning memory and parallelism relevant to NMC. The metrics include memory entropy, spatial locality, data-level, and basic-block-level parallelism. By profiling a set

of representative applications and correlating the metrics with the application's performance on a simulated NMC system, it demonstrates these additional metrics improve state-of-the-art tools in identifying applications suitable for NMC architectures.

Since hardware-independent analysis is expensive in terms of computation time and resources, the thesis suggests employing an ensemble machine learning model together with hardware-dependent application analysis, which reduces the prediction time up to 3 orders of magnitude compared with the state-of-the-art.

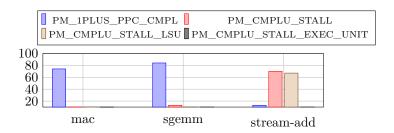

While the previous contributions employ the benchmark methodology, the thesis also focuses on the real-world use case of radio-astronomical imaging, where CPI (Clock Per Instruction) breakdown analysis on modern CPUs identifies large 2D FFTs and Gridder to be a performance bottleneck. It presents an NMC accelerator for 2D FFT computation and shows its implementation on FPGA outperforms the CPU counterpart and performs comparably to a high-end GPU. To improve the performance of Gridder, it exploits reduced precision acceleration contrary to the usual practice of employing high-precision computations in radio astronomy imaging. Reduced-precision analysis shows that precision must be selected carefully. It presents the first reduced precision accelerator for Gridder, employing custom floating-point data types on FPGA. The prototype outperforms a CPU and keeps up with a GPU with similar peak performance and lithography technology.

To summarize, the thesis's contributions are: 1) PISA-NMC, a hardware-agnostic tool to characterize applications with metrics directed towards near-memory computing; 2) NMPO, an ensemble machine learning framework for offloading prediction on NMC systems; 3) an evaluation of modern HPC architectures, including NMC, for accelerating radio-astronomical large 2D FFTs; and 4) an in-depth reduced precision analysis and the first custom floating-point accelerator for radio-astronomical imaging. Together, these contributions push the state-of-the-art of application characterization and architectural optimization forwards, focusing on real-world applications such as radio-astronomical imaging.

# Contents

| Acknowledgements |      |              |                                                              |    |  |  |  |  |  |

|------------------|------|--------------|--------------------------------------------------------------|----|--|--|--|--|--|

| 1                | Intr | Introduction |                                                              |    |  |  |  |  |  |

|                  | 1.1  | Challe       | enges                                                        | 2  |  |  |  |  |  |

|                  | 1.2  |              | em Statement                                                 | 4  |  |  |  |  |  |

|                  | 1.3  |              | s contributions                                              | 5  |  |  |  |  |  |

|                  | 1.4  |              | s structure                                                  | 6  |  |  |  |  |  |

| <b>2</b>         | Bac  | kgroui       | $\operatorname{nd}$                                          | 9  |  |  |  |  |  |

|                  | 2.1  | High I       | Performance Computing Systems                                | 9  |  |  |  |  |  |

|                  |      | 2.1.1        | Central Processing Units                                     | 12 |  |  |  |  |  |

|                  |      | 2.1.2        | Graphical Processing Units                                   | 13 |  |  |  |  |  |

|                  |      | 2.1.3        | Field Programmable Gate Arrays                               | 15 |  |  |  |  |  |

|                  |      | 2.1.4        | Near Memory Computing                                        | 16 |  |  |  |  |  |

|                  | 2.2  | Applie       | cation characterization                                      | 17 |  |  |  |  |  |

|                  |      | 2.2.1        | Goals                                                        | 17 |  |  |  |  |  |

|                  |      | 2.2.2        | Taxonomy                                                     | 20 |  |  |  |  |  |

|                  |      | 2.2.3        | State of the art                                             | 21 |  |  |  |  |  |

|                  | 2.3  | Radio-       | -astronomical imaging                                        | 23 |  |  |  |  |  |

|                  |      | 2.3.1        | Interferometry and Imaging                                   | 23 |  |  |  |  |  |

|                  |      | 2.3.2        | Image-Domain Gridding                                        | 24 |  |  |  |  |  |

|                  |      | 2.3.3        | Deconvolution                                                | 25 |  |  |  |  |  |

| 3                | Plat | tform-       | Independent Software Analysis                                | 29 |  |  |  |  |  |

|                  | 3.1  | Platfo       | rm-Independent Software Analysis                             | 30 |  |  |  |  |  |

|                  |      | 3.1.1        | LLVM framework                                               | 30 |  |  |  |  |  |

|                  |      | 3.1.2        | PISA Tool                                                    | 30 |  |  |  |  |  |

|                  | 3.2  | Metric       | CS                                                           | 32 |  |  |  |  |  |

|                  |      | 3.2.1        | Memory entropy                                               | 32 |  |  |  |  |  |

|                  |      | 3.2.2        | Data reuse distance for multiple cache-line size and spatial |    |  |  |  |  |  |

|                  |      |              | locality                                                     | 33 |  |  |  |  |  |

|                  |      | 3.2.3        | Data level parallelism                                       | 34 |  |  |  |  |  |

|                  |      | 3.2.4        | •                                                            | 35 |  |  |  |  |  |

|                  | 3.3  | Result       |                                                              | 37 |  |  |  |  |  |

#### CONTENTS

|          |     | 3.3.1 System in use                                            |

|----------|-----|----------------------------------------------------------------|

|          |     | 3.3.2 Applications evaluation on NMC system                    |

|          |     | 3.3.3 Hardware agnostic characterization                       |

|          |     | 3.3.4 Correlation between NMC Metrics and NMC Performance . 41 |

|          | 3.4 | Related Work                                                   |

|          | 3.5 | Summary and conclusions                                        |

| 4        | Ens | emble machine learning for NMC offloading 47                   |

|          | 4.1 | Background                                                     |

|          |     | 4.1.1 Application characterization                             |

|          |     | 4.1.2 NMC simulation                                           |

|          |     | 4.1.3 Ensemble machine learning 50                             |

|          | 4.2 | Framework                                                      |

|          |     | 4.2.1 NMPO                                                     |

|          |     | 4.2.2 Experimental Setup                                       |

|          | 4.3 | Experimental Results and evaluation                            |

|          | 1.0 | 4.3.1 Application profiling                                    |

|          |     | 4.3.2 Application offloading                                   |

|          | 4.4 | Related Work                                                   |

|          | 4.5 | Summary and conclusions                                        |

|          |     |                                                                |

| <b>5</b> | Lar | ge 2D FFT radio-astronomy 65                                   |

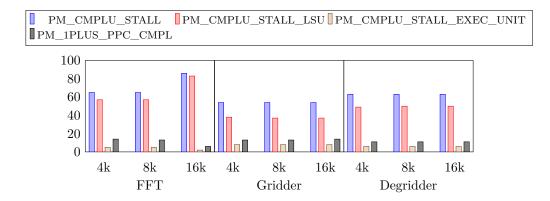

|          | 5.1 | CPI Breakdown Analysis                                         |

|          | 5.2 | Methodology                                                    |

|          |     | 5.2.1 System in use                                            |

|          |     | 5.2.2 Tools and Software                                       |

|          | 5.3 | Results                                                        |

|          |     | 5.3.1 Application Characterization 71                          |

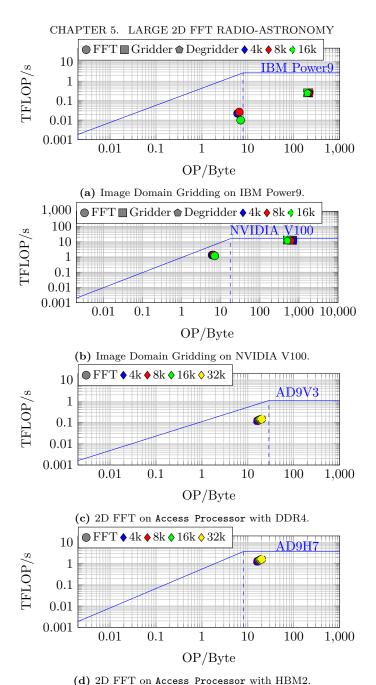

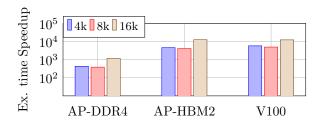

|          |     | 5.3.2 Offloading on NMC Systems                                |

|          | 5.4 | Related work                                                   |

|          |     | 5.4.1 Application Characterization                             |

|          |     | 5.4.2 Large 2D FFT acceleration                                |

|          | 5.5 | Summary and conclusions                                        |

| 6        | Rec | luced-Precision Acceleration of Radio-Astronomical Imaging     |

|          |     | Reconfigurable Hardware 79                                     |

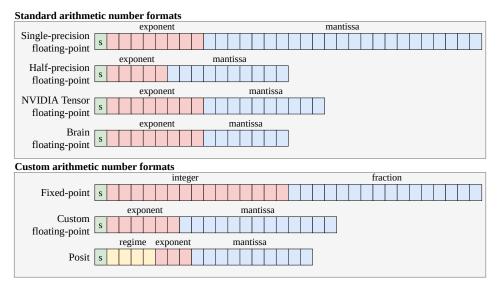

|          | 6.1 | Reduced precision                                              |

|          |     | 6.1.1 Data types                                               |

|          |     | 6.1.2 Reduced precision tools                                  |

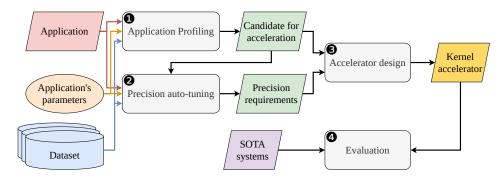

|          | 6.2 | Methodology                                                    |

|          |     | 6.2.1 Application Profiling                                    |

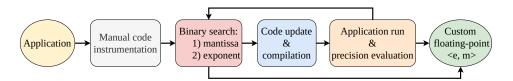

|          |     | 6.2.2 Precision auto-tuning                                    |

|          |     | 6.2.3 Accelerator design                                       |

|          |     | 6.2.4 Evaluation with state-of-the-art architectures 90        |

#### CONTENTS

|              | 6.3             | Analys  | sis                                                        | . 91  |

|--------------|-----------------|---------|------------------------------------------------------------|-------|

|              |                 | 6.3.1   | Bottleneck analysis                                        | . 92  |

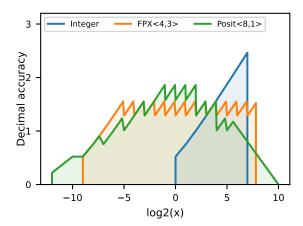

|              |                 | 6.3.2   | Data types exploration                                     | . 92  |

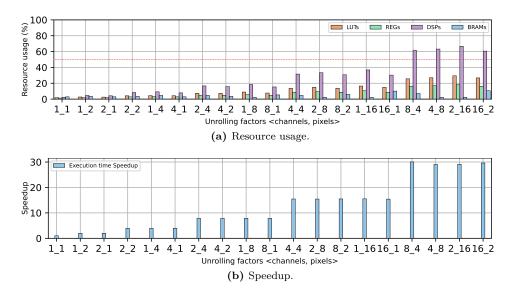

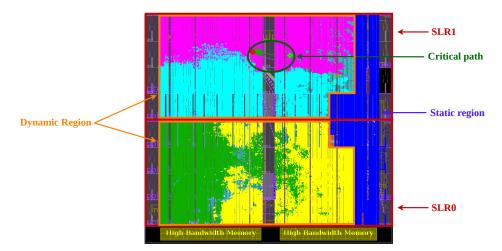

|              | 6.4             | Custor  | m Precision Accelerator Architecture                       | . 95  |

|              |                 | 6.4.1   | Gridding accelerator                                       | . 96  |

|              |                 | 6.4.2   | Cosine/sine Lookup Table and reduced precision             | . 98  |

|              |                 | 6.4.3   | Reduced precision                                          | . 98  |

|              |                 | 6.4.4   | Device-specific considerations                             | . 99  |

|              |                 | 6.4.5   | Design points                                              | . 102 |

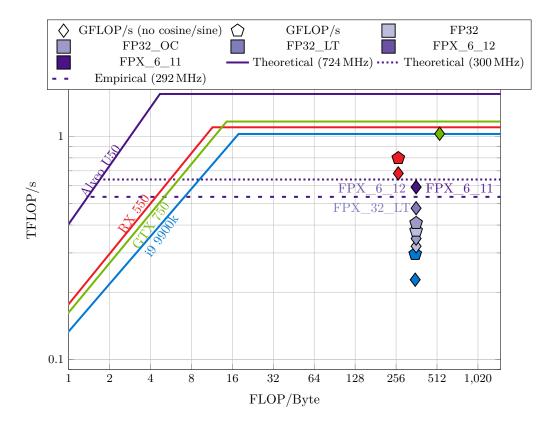

|              | 6.5             | Evalua  | ation and discussion                                       | . 103 |

|              |                 | 6.5.1   | Area usage                                                 | . 103 |

|              |                 | 6.5.2   | Performance                                                |       |

|              |                 | 6.5.3   | Lessons learned                                            | . 106 |

|              | 6.6             | Relate  | d work                                                     |       |

|              |                 | 6.6.1   | Radio-astronomy acceleration                               |       |

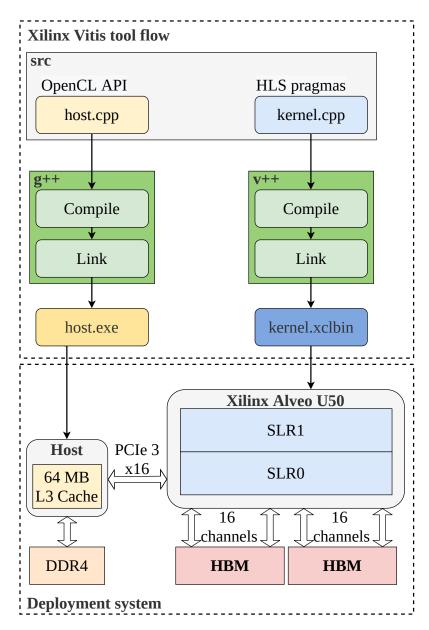

|              |                 | 6.6.2   | Xilinx Vitis                                               | . 109 |

|              | 6.7             | Summ    | ary and conclusions                                        | . 110 |

| 7            | Con             | clusio  | as                                                         | 113   |

|              | 7.1             | Summ    | ary                                                        | . 113 |

|              |                 | 7.1.1   | Application profiling and offloading                       | . 113 |

|              |                 | 7.1.2   | Novel hardware architectures for radio-astronomical imagin | g 115 |

|              | 7.2             | HPC h   | nardware trends                                            | . 116 |

|              | 7.3             | Future  | e work                                                     | . 118 |

| Bi           | bliog           | raphy   |                                                            | 123   |

| A            | HLS             | 6 custo | om floating-point library comparison                       | 141   |

| В            | $\mathbf{List}$ | of Pu   | blications                                                 | 145   |

| $\mathbf{C}$ | $\mathbf{CV}$   |         |                                                            | 147   |

# Introduction

Modern scientific applications have high-performance requirements. Workloads are from disparate field such as machine learning [1], genomics [2], hydrodynamics [3], radio-astronomy [4], etc. Radio-astronomy algorithms represent a noteworthy example. Indeed, the Square Kilometre Array (SKA) [5], which is in the first construction phase during this decade, will be the biggest radio-telescope in the world, with thousands of antennas and hosted in South Africa and Australia. A subset of tasks of the SKA is focused on extracting real-time information of transients, in other words detecting interesting objects in the sky like pulsar, and imaging the digitized signal of the sky in images. A radio-telescope of such dimension will produce a large amount of data traffic in the order of TeraBytes/s, and each computing facility will have to provide computing capabilities in the order of ExaFLOP/s [6].

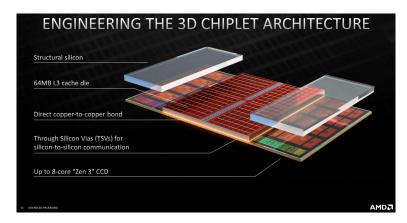

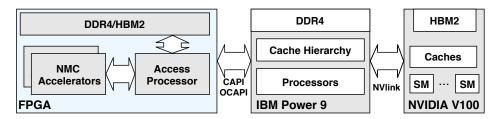

To accommodate such high-performance requirements, innovative approaches need to be researched. Moreover, hardware limitations raise in the past years. In particular, memory technology could not keep up with processing elements technology in terms of speed and energy consumption; this problem is typically called the Memory Wall [7]. In addition, chip manufacturers have difficulties in following Moore's [8] and Dennard's [9] Laws. Indeed, it is not anymore possible to shrink the size of transistors like in the past. To overcome these issues, new technologies and computational paradigms have been proposed. For instance, new 3D stacked memories such as High Bandwidth Memory (HBM) [10] and Hybrid Memory Cube (HMC) [11] are employed in current GPUs, and FPGAs generation [12,13]. These innovations are slowly affecting also the CPU architectures; for example the new AMD's 3D-V cache (see Figure 1.1). Indeed, 3D memory technology

allows to have large caches with faster interconnect to the cores. Thanks to these new technologies, computational paradigms such as Near-Memory Computing (NMC) [14] have re-gained interest.

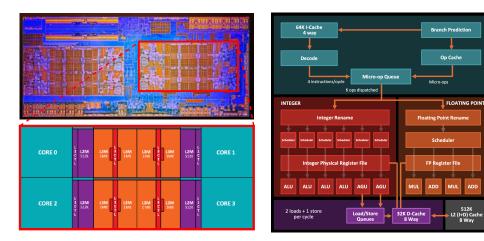

Figure 1.1: AMD 3D-V Cache technology [15, 16]. The CPU shown is equipped with 3D stacked L3 cache providing higher memory density and lower latency compared to traditional 2D-cache-equipped CPUs.

The trend of modern computing systems is directed towards heterogeneity. This simply means that supercomputers will consist of different nodes with different resource inter- and intra- nodes. Indeed, certain applications are better suited for certain architecture, such as CPUs [17] and GPUs [18]. Most of the future machines will host domain-specific accelerators, which are basically optimized for specific algorithms. The acquisitions of Altera and Xilinx by respectively Intel [19], and AMD [20] make FPGAs break into the HPC world, delivering promising competitive platforms for scientific computation with respect to GPUs. From one side, heterogeneity allows optimal hardware for the considered application. On the other, it complicates and creates challenges in characterizing workloads, optimizing them for the specific architectures, on which architecture they should be offloaded to, etc. In particular, the challenges regarding application characterization, offloading and optimization on the domain-specif accelerator will be treated in Section 1.1. Then we present the thesis' problem statement in Section 1.2, contributions in Section 1.3 and the thesis structure in Section 1.4.

#### 1.1 Challenges

The complexity of modern algorithms and computing systems will present difficult challenges to researchers and developers. In particular, here we present the challenges related to application characterization and offloading and the optimization on domain-specific accelerators.

#### Application characterization and offloading

One of the most difficult challenges is characterizing applications and deciding if and where to offload them to maximize performance. Heterogeneity makes this even more complex. Indeed, profiling and characterizing applications is not standardized, and many tools and characterization metrics have been proposed in the past decades. Furthermore, this becomes even more complex if the target is a future architecture, which can only be simulated [21].

A fair amount of research has been spent on abstracting application characterization from hardware details and focusing only on application properties [22, 23]. However, when targeting novel computation paradigms, new metrics needs to be researched to detect application hotspots that can take advantage of new hardware features. Indeed, this is still an open challenge for paradigms such as near-memory computing [14].

Application characterization should provide enough information to select the most profitable hardware for a specific application. While automatic methodologies such as compilers, which determine application hotspot and provide code optimization, have been introduced [24], they effectively work on simple and standard micro-kernels such as linear algebra (BLAS). Nonetheless, modern workloads contain non-standard computations, which are difficult to detect automatically. Therefore, possible solutions to determine offloading decisions are analyzing profiling results to determine the most relevant characterization metrics or machine-learning prediction model to determine offloading choices [21].

#### Domain-specific optimization

To accommodate the above mentioned high-performance requirements, powerful machines need to be developed and alternative computing approaches must be researched. Undoubtedly, modern supercomputers can achieve ExaFLOP/s performance but consume a large amount of energy.

Table 1.1 shows the first 5 positions of the TOP500 list [25]. The execution of HPCG [26] on the most powerful top500 supercomputers achieve less than 5% of their peak performance. The waste of power consumption of these machines could be used to sustain the energy demand of a small city [27].

With new architectures entering the domain, such as FPGAs, it becomes even more critical to understand how different platforms behave and can be employed to obtain the best performance in terms of time to solution, but more importantly, energy efficiency.

To achieve this goal, a good knowledge of how the computing architectures are designed is needed. Moreover, to achieve even higher performance and lower energy, a trade-off on the result quality may also be taken into account, e.g., by exploiting approximate computing [28]. However, as we will discuss in *Chapter 6* it strictly depends on applications and datasets. Indeed, radio-astronomical

**Table 1.1:** Latest (November 2022) results of the 5 faster supercomputers from top500 list [25]. Frontier is the first machine that surpasses the ExaFlop in raw performance. The table also reports the fraction of peak performance achieved by running HPCG [26], a standard benchmark to assess performance on supercomputers: most of the supercomputers are below 5%.

| Rank | System   | Rpeak (PFLOP/s) | Power (MW) | HPCG % |

|------|----------|-----------------|------------|--------|

| 1    | Frontier | 1685.65         | 21.10      | 1.00   |

| 2    | Fugaku   | 537.21          | 29.90      | 3.62   |

| 3    | LUMI     | 428.70          | 2.94       | 1.10   |

| 4    | Leonardo | 255.75          | 7.44       | 1.47   |

| 5    | Summit   | 200.79          | 10.10      | 1.97   |

imaging applications typically need high precision, which may vary slightly based on the datasets.

#### 1.2 Problem Statement

With the rising of modern real-world applications in various domains such as radio astronomy, genomics, artificial intelligence, and hydrodynamics that have demanding computational and memory requirements, it is crucial to understand which architecture can better support them and how to optimize them for specific hardware.

Indeed, it is challenging to determine which application sections, typically named kernels, should be offloaded to accelerators. This can be done in very different ways, and it is usually challenging for emerging technologies. More precisely, with the advent of new technologies such as High Bandwidth Memory (HBM) and Hybrid Memory Cube (HMC), new architectures and computational paradigms have been proposed. An example is near-memory computing which shifts the computation near the memory, avoiding the movement through the cache hierarchy. Additionally, competing architectures such as GPU and FPGA recently support this particular technology. This makes it difficult to understand when an architecture is beneficial and when to offload particular kernels.

Even though modern compilers can optimize particularly well applications code for multiple platforms, they are often limited to a few well-known kernels such as linear algebra (BLAS) [29]. However, modern applications in radio astronomical imaging and hydrodynamics include linear-algebra kernels and uncommon computations such as sine/cosine and floating-point operations with particular patterns. It is challenging to map and optimize these computational tasks to new accelerator architectures. Indeed, typically for every architecture, it is usually necessary to

employ specific code grammar to obtain high-performance code, e.g., CUDA for NVIDIA GPUs, Xilinx High-Level Synthesis Pragmas for Xilinx FPGAs.

More precisely, we need to understand which application characterization methodology would provide sufficient information to make offloading decisions on heterogeneous high-performance computing systems. Furthermore, can machine learning improve the above-mentioned offloading decisions? After determining bottlenecks and taking offloading decisions, which accelerators and optimization can maximize the computing and energy efficiency of real-world applications such as radio-astronomical imaging?

#### 1.3 Thesis contributions

This thesis provides techniques and demonstrations of application characterization and optimization by targeting both emerging and state-of-the-art high-performance systems and real-world workloads such as radio-astronomical imaging. We show how application profiling techniques can be used efficiently to detect possible application bottlenecks and individuate appealing optimization for improving performance.

This thesis makes the following four contributions:

- 1. Platform-Independent Software Analysis for Near-Memory Computing, is a hardware-independent tool capable of detecting application features related to data and memory parallelism. With this tool, we extend the application characterization possibilities for emerging computational paradigms such as near-memory computing, and we show its relationship with near-memory computing performance (Chapter 3) [30, 31].

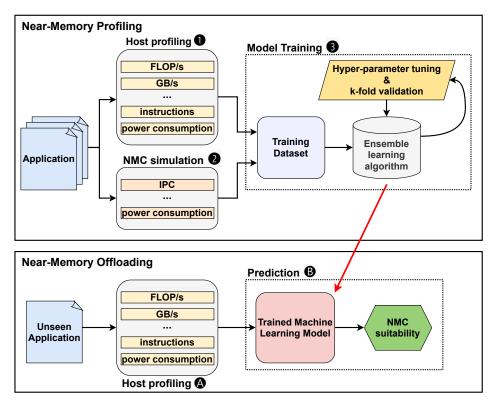

- 2. Emerging high-performance computational paradigm typically employs expensive simulation to understand the suitability for offloading. While machine learning can reduce the amount of hardware simulation to the training set, the current state-of-the-art uses costly hardware-independent characterization to predict NMC offloading suitability. The Near Memory computing Profiling and Offloading framework demonstrates that the offloading suitability prediction can drastically benefit from using hardware-dependent characterization (Chapter 4) [32].

- 3. Modern radio-telescope will need to deal with large datasets for detailed sky images. This introduces a bottleneck in the radio-astronomical imaging pipeline: the two-dimensional Fast Fourier Transform. We propose a detailed application characterization and evaluation on state-of-the-art systems including near-memory computing (*Chapter 5*) [33].

- 4. Radio-astronomical imaging requires high-performance and energy-efficient computing. Reduced precision is a technique that employs reduced precision

data types to improve application performance and saving energy. In this context, we propose for the first time an in-depth reduced-precision analysis and custom accelerator for this application domain. We also provide guidelines for optimizing applications on In Xilinx Vitis targeting Xilinx Alveo FPGAs and important lessons learned ( $Chapter\ 6$ ) [34].

To summarize, this thesis provides mechanisms and methodologies to ease application profiling to detect application hotspots. Moreover, we evaluate different state-of-the-art architectures showing advantages and disadvantages in modern scientific computing, with a particular focus on radio-astronomical imaging workloads.

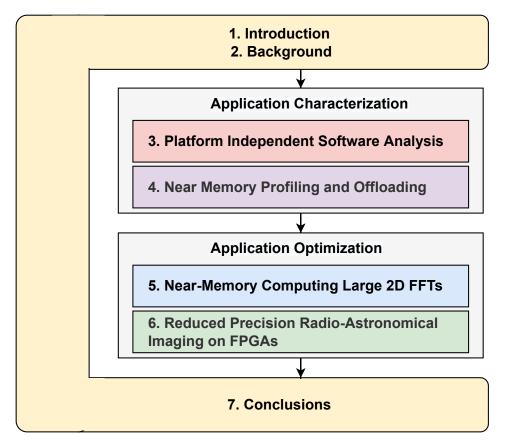

#### 1.4 Thesis structure

As depicted from *Figure 1.2*, the thesis is built on top of a skeleton (yellow area) containing Introduction, Background, and Conclusions. The main contributions are categorized in two macro-area (gray boxes): Application Characterization and Application Optimization.

In the following paragraphs, we detail the thesis structure per chapter:

Chapter 2: discusses the background information required to understand the thesis' contributions. We start by highlighting the main computing paradigm employed in this thesis. Then, we introduce the primary methodologies for application characterization. The chapter concludes with a thorough background of Radio-Astronomical Imaging algorithms, a real-world application with high-performance requirements we employ in the thesis.

Chapter 3: introduces the platform-independent software analysis tool for characterizing near-memory computing features. It discusses the novel memory and data parallelism metrics that we add to the original tool to enrich the application characterization. Then, we demonstrate the correlation of using these metrics with near-memory computing performance by employing the principal component analysis and near-memory computing simulation.

Chapter 4: introduces the Near-Memory computing Profiling and Offloading (NMPO) framework. NMPO is an ensemble machine learning model trained with near-memory computing simulation and hardware-dependent characterization data to predict near-memory computing suitability of unseen applications. NMPO promises to be faster than the state-of-the-art, especially in the prediction phase by employing hardware-dependent characterization, which typically has reduced overhead compared to hardware-independent techniques.

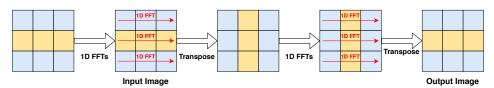

Chapter 5: presents a specific Radio-Astronomical Imaging use case. Indeed, radio-astronomers will need to process high-resolution images to detect smaller

and hidden space objects in the coming years. Two-dimensional Fast Fourier Transform becomes a critical bottleneck with increased image size. In this chapter, we characterize the 2D FFT by employing hardware-dependent methodologies.

Figure 1.2: Graphical representation of the thesis structure. The thesis develops on two macro-topics: application characterization and application optimization. Each topic has its own contributions and they are linked across the body of the thesis.

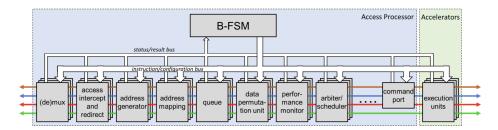

Then, we evaluate its performance on high-performance architectures, including a Near-Memory Computing system based on the Access Processor concept and realized on an FPGA.

Chapter 6: shows an in-depth analysis by using hardware-dependent tools of one state-of-the-art radio-astronomical imager. More precisely, we focus on determining the main application bottleneck. To the best of our knowledge, this

#### CHAPTER 1. INTRODUCTION

is the first time that the application tolerance to reduced-precision data types is evaluated. Then, we propose the first reduced-precision Image-Domain Gridding accelerator on FPGA. The chapter concludes with an evaluation of the prototypes presented with state-of-the-art architectures such as CPUs and GPUs.

**Chapter 7:** summarizes the thesis contributions and gives an overview on potential future works.

# Background

In order to understand this thesis some background information can help the reader. This chapter starts by describing the main computing systems studied and employed for this work (2.1). Application characterization techniques are reported in 2.2 and this chapter concludes with describing the most significant use case of this thesis: radio-astronomical imaging (2.3).

#### 2.1 High Performance Computing Systems

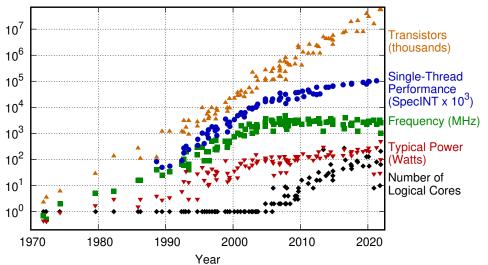

Modern scientific applications need High-Performance Computing in order to execute efficiently with sufficient performance. In the past decades, we have witnessed a rapid evolution in computer architecture. Especially, the CPU (Central Processing Unit), usually considered as the "heart" of a computing systems (HPC servers, laptops, smartphones, domestic devices, etc.) has deeply changed in the past years. Indeed, as shown in Figure 2.1, from 1970s there has been an exponential improvement in terms of frequency, number of transistors and single-thread performance. This behaviour was driven by the so-called Moore's Law [8] and Dennard's scaling Law [9]. The first one claims that the number of transistors doubles approximately every two years, while the second one states that the performance per watt double every 18 months.

However, at the beginning of the 21th century these two laws started to slow down and not be completely valid anymore [36]. Indeed, *Figure 2.1* shows that in the past two decades the number of transistor is still doubling at a lower speed, about every 18-24 months. A similar trend affects Dennard's scaling. In fact, starting

#### 50 Years of Microprocessor Trend Data

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

Figure 2.1: 50 years processors trend [35]: number of transistors, single-thread performance, frequency, power consumption and number of logical cores. The figure show how the number of transistor is increasing over time. This is true for the number of logical cores starting from the early 2000s. Contrariwise, the other trends are reaching a plateau.

from the early 2000s frequency and single-thread improvement started to reach a plateau. Typical high frequency values for today's CPU are in the range of 4 to 5 GHz. However, these values can typically be achieved by a single core at a time. Nevertheless, new solutions started to be introduced. As can be depicted from *Figure 2.1* around 2005, CPUs with multiple core started appearing on the market increasing the complexity of modern CPUs but providing higher performance for

modern applications.

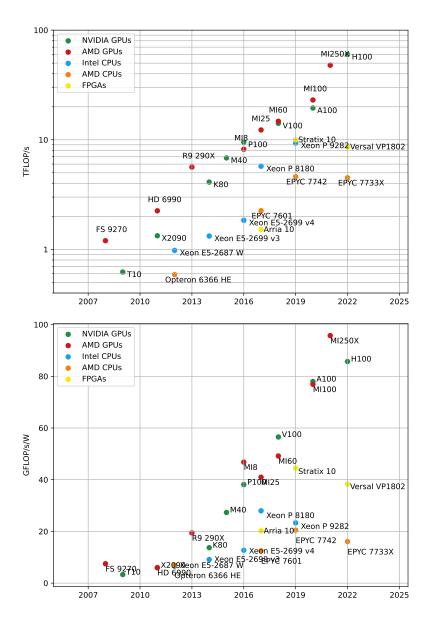

To accommodate the requirements of modern and performance demanding workloads, in the past two decades alternative architectures such as Graphical Processing Units (GPU) and Field-Programmable Gates Arrays (FPGAs) have been produced. In particular, these new architectures have usually higher peak performance in terms of operations per second and bytes per second at the cost of being less general purpose [37]. Indeed, these architectures work perfectly with embarrassingly parallel algorithms and typically provide better energy efficiency.

Figure 2.2: The top figure shows the theoretical peak performance expressed in TFLOP/s for different computing architectures in the past decade. NVIDIA GPUs are reported in green and AMD GPUs in red; they show the higher values of TFLOP/s. Other architectures such as CPU and FPGAs show lower performance; they are reported in blue (Intel CPUs), orange (AMD CPUs) and yellow (FPGAs). The bottom figure presents the theoretical energy efficiency (GFLOP/s/W) of the same architectures. Usually GPUs and FPGAs are far more energy efficient than CPUs.

11

For completeness, we show in Figure 2.2 the trend over the years of the most common computing architectures (CPUs, GPUs and FPGAs) in terms of performance (TFLOP/s) and energy efficiency (GFLOP/s/W). Overall, the improvement is exponential. GPUs usually can provide the highest throughput and energy efficiency compared to the other systems.

#### 2.1.1 Central Processing Units

A Central Processing Unit (CPU) is a key element in today's computing systems. A CPU typically consists of a small number of high-performance cores, often are in the range of 2-64 and can reach frequencies around 4-5 GHz. Usually a cache hierarchy is integrated in the CPU package. Cache memory is faster but smaller than the main memory where the application and operating system data usually resides. Cache memory temporarily stores frequently used instructions and data enabling quicker processing on the CPU cores. In most cases, the main memory uses Dynamic Random Access Memory (DRAM), which is commonly located outside the CPU package. However, this is not true for the recently released Apple M1 and M2 chips [38], where the CPU and main memory are placed in the same chip. CPU's cores usually consist of an instruction pipeline including Arithmetic Logic Units (ALU) and Registers for processing operations. Modern CPU's cores support vector operations and multi-threaded execution, therefore increasing the level of parallelism and complexity.

**Figure 2.3:** AMD zen2 architecture. On the left, the upper figure is the layout of an 8 cores CPU, the bottom figure is a zoomed representation of a CCX section of the 8 core CPU. On the right side, the pipelined representation of a zen2 core [39].

A layout of a relatively recent CPU is showed in *Figure 2.3*. On the left, the upper image shows the layout of 8 cores AMD CPU with zen2 architecture. Modern CPU

architectures pack a number of resources such as caches and cores in a modular fashion. The bottom image on the left side shows the layout of an AMD CCX (CPU Core Complex). It contains 4 large cores with each a L2 private cache, a shared L3 cache. Note that this may differ across vendors and architecture generations.

The right side of *Figure 2.3* depicts the structure of a modern CPU core: L1 and L2 private caches, ALUs for integer and floating-point (red and orange), pipeline queues. To maximize performance, CPUs implement pipelined designs [40] in order to increase the computation throughput. The pipeline stages can be recognized in in the upper part of the core scheme: instruction decode from the instruction cache, micro-op queue, ALU execution, etc.

#### 2.1.2 Graphical Processing Units

Graphical Processing Units (GPUs) were designed mainly for graphic tasks such as gaming and video rendering. Twenty years ago, GPUs were complicated to program for scientific computation and were mainly employed for applications with operations on image-like data structures [41]. Only with the advent of high-level programming models supporting common programming languages, such as C/C++, GPUs became popular for scientific workloads. In 2007 NVIDIA released a C-like language for GPUs, the so-called CUDA (Computed-Unified-Device-Architecture) [42]. A few years later, competitors such as AMD and Intel proposed OpenCL [41], which, compared to CUDA, is not vendor-specific.

GPU architectures have specific features that make them profitable for certain workloads compared to CPUs. GPUs usually come with fast memory soldered on the same board and are significantly faster than the CPU's main memory (called global memory). Modern GPUs are equipped with GDDR6X, or HBM2. While GDDR memory is placed on the PCB and spread around the processor, the HBM memory is located on the GPU itself and the different stacked dies communicate via microbumps and through-silicone vias (TSV). They can achieve a peak bandwidth in the order of TB/s [13]. Another key difference with CPUs is that GPU have more cores at lower frequencies: current high-end GPUs, such as the NVIDIA A100, have more than ten thousand processing elements. Each processing element has a private memory. It also includes units for floatingpoint (single and double precision) computations (FPU) and other units based on the model. For instance, modern NVIDIA GPUs have Special Functional Units (SFU) for transcendental operations such as sine and cosine [44]. They may also include tensor cores [45], for AI workloads, which are incredibly efficient in computing matrix multiply and accumulate. Most modern GPUs also support mixed-precision computation, including data types not commonly supported by CPUs, such as Brain Floating Point and Half Precision.

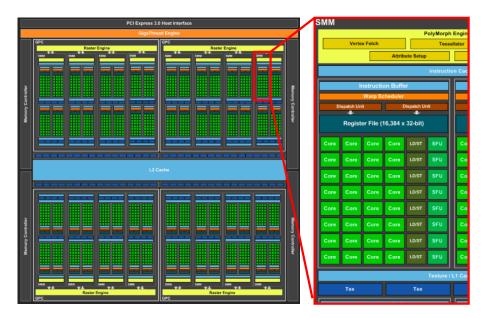

As shown in *Figure 2.4*, GPU processing elements are organized in clusters, so called Streaming Multiprocessor (SM) or Shader Engines depending on the vendor terminology. Inside an SM, the cores share an L1 memory, also called shared

Figure 2.4: Schematic of an NVIDIA Tesla V100 GPU [43]. On the left, the overall architecture with global memory, L2 caches and GPCs (Graphic Processing Clusters). On the right, a zoomed view of a Streaming Multiprocessor (SM). We can distinguish cores, SFUs (Special Function Units), Load/Store units, etc.

memory. SMs are grouped in GPCs (Graphic Processing Clusters) and access a common  $\rm L2$  cache.

Although modern GPUs are programmable in a high-level language, their programming model is different from the ones (like C/C++) used for CPUs. GPU computation exploits many threads for parallel operations. The operations are typically defined as a Grid consisting of Thread blocks. Each thread block hosts a group of threads (warps or wavefronts) [42].

```

void vecAdd(double *a, double *b, double *c, int SIZE)

pragma omp parallel for for (int i = 0; i < SIZE; i++){

c[i] = a[i] + b[i];

}

}

"""

plobal___ void vecAdd(double *a, double *c, int SIZE)

int id = blockIdx.x*blockDim.x+ threadIdx.x;

if (id < n)

c[id] = a[id] + b[id];

```

**Listing 2.1:** Vector addition in C++.

Listing 2.2: Vector addition in CUDA.

These features are explicit in the programming model. For instance, in *Listing* 2.1 we show an example of vector addition on CPU, where the parallelism is

inferred with an OpenMP pragma. To exploit GPUs parallelism, the code is written differently (see *Listing 2.2*). The first difference that can be noticed is that there is no for loop. The computation is split into different Thread Blocks, which a single Streaming Multiprocessor executes. Each Thread Block consists of different Threads that are offloaded to the SM's processing elements. These two dimensions (Thread Blocks and Threads) are specified by the kernel call in the host (CPU) code by using angular brackets: vecAdd<ThreadBlocks, Threads>(a, b, c, SIZE).

#### 2.1.3 Field Programmable Gate Arrays

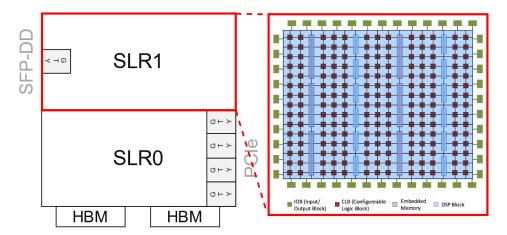

Field-Programmable Gate Arrays (FPGAs) are integrated circuits (IC) that consist of multiple programmable block and interconnect (Tile in  $Figure\ 2.5$ ) that can be programmed to execute specific computations.

Figure 2.5: FPGA architecture. Modern FPGAs are composed by multiple Super Logic Regions (SRL) to compete with GPUs. They also support high-speed connections such as GTY and SFP-DD.

In the case of Xilinx FPGAs, each block contains Configurable Logic Blocks (CLB) with LUTs (lookup tables) and FFs (flip flops) to generate logic circuits and small memories. Modern FPGAs also have DSP (digital signal processing) units, specially optimized for multiply and accumulate operations, and on-chip memories (BRAM, URAM, etc.) for storing high-re-used data or buffering inputs/outputs. The blocks mentioned above are programmed and connected to form digital functions. With the recent advancement in FPGA technology, they can easily perform numeric computations in floating-point and customizable/arbitrary precision arithmetic. This makes FPGAs appealing over architectures like CPUs and GPUs that support a set of pre-defined data types. FPGAs were programmed in the past

with relatively low-level Hardware Description Languages (HDLs), such as Verilog and VHDL. To avoid this time-expensive and tedious work, FPGAs vendors such as Xilinx and Intel support High-Level Synthesis Tools allowing programming FPGAs with High-Level Languages such as C++ and python. Moreover, vendors make available high-level APIs (Application Program Interface), which usually are usually based on OpenCL, to easily program and offload computation on the FPGAs.

However, the hardware generation (implementation), which provides the configuration, called bitstream, still requires several hours. Another important feature of FPGA devices is re-configurability. More precisely, it is possible to re-configure the programmable logic on at the run-time to support different computations or adapt the hardware to dynamic requirements. These features make FPGAs attractive candidates for High-Performance Computing and possible competitors with GPUs.

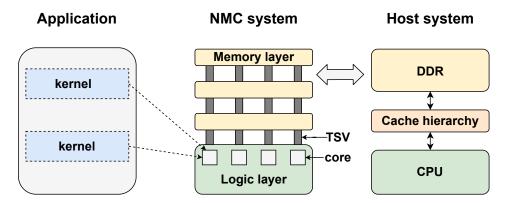

#### 2.1.4 Near Memory Computing

Differently from traditional computing architectures such as CPUs, near-memory computing (NMC) processes data near the main memory, in certain cases near storage memory, thereby avoiding the classical data movement throughout the cache hierarchy, which usually causes memory bottlenecks and increase the power consumption. First NMC ideas date back to 1970 [46]. However, given the hardware limitations at that time, the first prototypes started appearing not before early 1990s [47–49]. Vector IRAM (VIRAM) [50] is an example. Researchers developed a vector processor with an on-chip embedded DRAM (eDRAM) to exploit data parallelism in multimedia applications. This solution did not reach the market, although the results were quite promising.

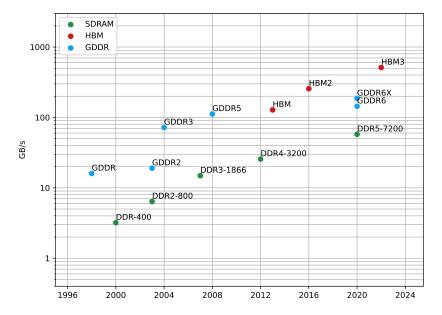

Recently, two key factors make NMC regain attention: the rising number of data-intensive applications and the memory technology improvement (see  $Figure\ 2.6$ ). More precisely, we are continuously witnessing an unstoppable increase of data requirements for applications in diverse fields such as health, social media, radio astronomy, etc. [51].

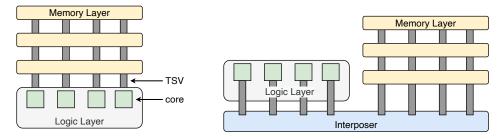

Three-dimensional stacked memory is one of the most important reasons of the NMC regained visibility. This technology can be used in 2.5D and 3D stacking configuration with the logic layer. In *Figure 2.7* we show an example of 3D stacking where memory layers and logic layers communicate with through-silicon via's (TSVs) reducing memory access latency, power consumption and enable high memory bandwidth [52]. In the case of 2.5D, mostly used in commercial solution (GPUs, FPGAs), the 3D-stacked memory communicate with the logic layer with an interposer, thus not being stacked. Example of 3D-stacked memory technologies are HBM (High Bandwidth Memory) [11] and HMC (Hybrid Memory Cube) [10].

Near-memory computing approaches have been studied and categorized by Singh et al. [14]. Briefly, NMC systems can be very different. The main parameter

Figure 2.6: Memory bandwidth trend of the most employed memory technology in HPC. In green SDRAM, typically used for CPUs; in blue GDDR, which is employed in GPUs. HBM is in red; it is used in high-end GPUs and FPGAs, but also in novel architectures such as NMC.

that varies in NMC systems is the main memory: HBM [53, 54], HMC [21] storage. Furthermore, there is an heterogeneous landscape in the state-of-theart of processing approaches: simple cores [21], fixed functions [55], etc. Moreover, since producing near-memory computing systems is costly, most of the research validation experiments are carried out with simulators [21, 56–58].

#### 2.2 Application characterization

Application characterization typically refers to the methodologies employed to collect performance-critical metrics in current and emerging applications. This is a challenging and crucial task, especially with continuously evolving hardware and software. Indeed, application characterization tools are fundamental when co-designing the hardware and software for modern workloads.

#### 2.2.1 Goals

Based on the characterization methodology, the achievable goals could be different. We summarize the most relevant ones as follows:

Figure 2.7: On the left an example of Near-Memory Computing (NMC) architecture with a 3D-stacked chip. The 3D-stacked memory is connected to the compute units or cores, placed on the logic layer, with through-silicon via's (TSVs). On the right, an example of 2.5D NMC architecture: the logica layer is connected to the memory layer with through-silicon via's (TSVs) through a layer called interposer.

Application hot spots: according to Amdahl's Law [8], reported in *Equation* 2.1, the speedup strictly depends on the critical hot spot that can be parallelized or accelerated. Therefore, finding application hot spots guarantee to optimize those application portions that will return a performance improvement:

$$S_{latency}(s) = \frac{1}{(1-p) + \frac{p}{s}}$$

(2.1)

where p is the application portion that can be parallelized and s is the section that must run sequentially.

This is usually achieved by individuating workload's critical sections that are frequently repeated over time, and that can be parallelized. First attempts date back late 1960's when IBM developed a monitoring device to profile CPU execution [59]. In the past 60 years, a large number of tools have been developed and proposed for this purpose, such as callgraph analysis tools [60,61] or hardware proprietary tools [62–64].

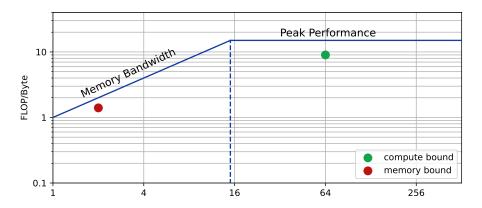

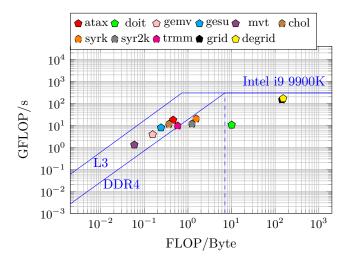

Hardware bottleneck: it is crucial to understand where the application stalls on specific hardware architecture. Indeed, new hardware generation may introduce a difference in their design that may impact the performance of pre-existing software. This is crucial to understand the current hardware's limitations and decide to either change architecture or, if possible, adapt the software to match it. Many tools capable of extracting hardware counters, such as Intel VTune [64], NVIDIA Nsight Compute [62], are available nowadays. Often these tools integrate the roofline model or can output the necessary metric to draw it. The roofline model is a widely employed performance model to assess achieved performance and hardware bottleneck [65].

The roofline model (see Figure 2.8) can be drawn for almost all the computing architectures such as CPUs, GPUs, and FPGAs. The key information that is needed for a basic roofline model are the peak compute and memory roofs. These are typically computed theoretically or empirically [66]. In the example, in Figure 2.8, the horizontal line represents the peak performance of the considered architecture, and it is usually expressed in floating-point operations per second (FLOP/s). The diagonal line represents the peak memory bandwidth.

Figure 2.8: Example of roofline model. The blue lines represent the architecture limits in terms of peak performance and memory bandwidth. The roofline model is helpful in distinguishing memory and compute-bound applications (see the green and red dots).

The roofline model shows on the y-axis the application achieved performance and on the x-axis the arithmetic intensity (FLOP/Byte). Arithmetic intensity is usually the factor that makes an application memory or compute bound. Indeed, if the application is underneath the compute roofs, it is compute bound, otherwise it is memory bound.

Application intrinsic analysis: the design-space exploration of emerging and future systems necessitates application characterization in terms of intrinsic application features. Indeed, it is crucial to understand application-related characteristics such as Instruction-Level Parallelism, Memory Entropy, and Task-Level Parallelism to efficiently design the system mentioned above. The information extracted is usually employed to build an architectural model or performance model to predict application performance on unavailable or to be designed computing systems [67].

Adaptiveness: Modern compiler such as LLVM Clang [68] embed a large variety of analysis tools in their toolchain to be able to identify bottlenecks such as race conditions [69] or detecting particular code patterns [24,70] that can be optimized by the compiler itself. Run-time managers represent another example. They are

typically software routines that run parallel with applications on a system and employ application profiling to determine stalls or offloading opportunities. This is usually done by analyzing the application performance, and hardware utilization to adapt on-the-fly the application offloading, e.g., by dynamically adapting the task scheduling [71, 72].

#### 2.2.2 Taxonomy

The numerous profiling and characterization tools that have been proposed over the years can be distinguished by their features.

- Hardware dependency: the profiling may only include the code analysis (hardware independent) or can in addition take into consideration hardware features (hardware dependent).

- Metrics: collected metrics can be really different among characterization tools. Common metrics are execution time, floating-point operation per second (FLOP/s), arithmetic intensity (FLOP/Byte), energy efficiency, Instruction-Level-Parallelism (ILP), etc.

- Application stage: analysis can be done at different application stages: source code, compilation time, and run-time.

- **Granularity:** profiling tools can work at different granularity starting from coarse grain such as event-based profilers to fine-grained such as profiling at instruction level.

Applications can be analyzed with different approaches. Often a mixture of methodologies can be applied:

- Event-based: this technique triggers the analysis based on software events such as function calls, class load or unload, etc [64].

- Statistical: the profiler collects information by sampling data. Perf, a profiler utility available in the Linux kernel, [73] or PAPI (Performance Application Profiling Interface) are able to collect hardware counter measurements at a certain sampling frequency.

- Instrumentation: the aim of this method is to inject additional instructions to collect application information. This technique usually reduces the applications performance. Instrumentation can be done in different ways:

1) the user can manually add instructions to the application code, e.g., PAPI [74]; 2) a tool can automatically instrument the source code [75] or the compiler intermediate representation; 3) other approaches perform the instrumentation at binary level [76] or at run-time.

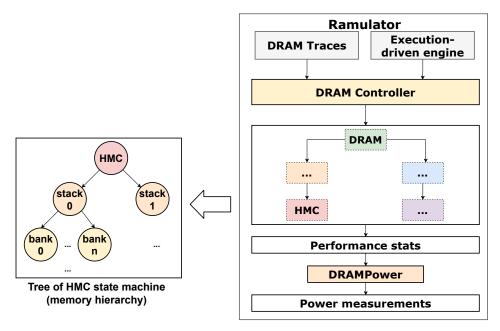

- Simulation: the application dynamically runs under an instruction set simulator (ISS), a simulation model capable of reproducing an architecture behavior. This is typically coded in high-level languages such as C++. Simulators can model entire systems or specific components. For instance, Ramulator [77] and DRAMSim3 [78] are cycle-accurate memory simulators. Gem5 [79] and Zsim [80] are employed to emulate the behaviour of CPUs, while GPGPUsim [81] models GPUs execution.

- Analytical models: are typically quantitative and less precise, compared to, e.g., simulator, estimation based on a set of mathematical equations. They quickly estimate the application performance based on collected application properties and hardware features. In this context, e.g., Gysi et al. [82] propose a fast analytical model of fully associative caches, based on static analysis using the LLVM compiler framework, that outperforms cache simulators by several order of magnitude with an error below 0.6%.

#### 2.2.3 State of the art

In this thesis, we mainly focus on the difference between hardware-independent and hardware-dependent analysis tools. Moreover, while the first ones can be more accurate and helpful for unavailable hardware, the second ones are easier to use and quicker. We summarize the most relevant state-of-the-art approaches and tools in the following paragraphs.

Hardware independent analysis A hardware-independent analysis can be done both statically and dynamically. For instance, Jordans et al. [83] analyzed the processor parallelism using a static analysis of the LLVM's IR, which is the Intermediate Representation employed by the LLVM compiler. This work aimed to estimate the level of parallelism in a workload and propose optimization strategies focused on VLIW architectures. Another static approach was proposed by Eusse et al. [84]. They used the LLVM framework to perform a pre-architectural performance estimation coupling high-level synthesis (HLS) to shorten design times.

On the other hand, dynamic analysis can collect the difference when changing the workload's problem size. Cabezas [85] proposed a tool that can extract different features from workloads but has many limitations: the compiler community no longer supports the used LLVM interpreter, and the target applications should be single threaded. Another tool has been developed by Shao et al. [22]. It can extract interesting metrics such as memory entropy and branch entropy. However, this tool has some limitations: it is based on the IDJIT IR (just-intime compilation) that has compatibility problems with OpenMP and MPI, thus being limited to sequential applications. Vector Fabrics [86] developed several commercial LLVM-based tools. For instance, based on dynamic analysis, Vector Fabrics' Pareon Profile tool was used to explore opportunities and bottlenecks for

#### CHAPTER 2. BACKGROUND

parallel execution of C/C + + code; Vector Fabrics' Pareon Verify, which uses dynamic analysis to find bugs in C/C + + application code.

One of the most recent hardware agnostic tools is PISA (Platform-Independent Software Analysis) for workload characterization was presented by Anghel et al. [23]. PISA can analyze multi-threaded applications supporting the OpenMP and the MPI standards.

Hardware dependent analysis As mentioned above, hardware-dependent analysis dates back to the late 1960s [59]. Over the years, additional tools have been researched. For instance Tjaden et al. [87] propose instruction-level parallelism (ILP) estimation. They took into account: memory accesses, data registers, operand availability, and procedural dependency. Later, Theobald et al. [88] improved the ILP estimation by analyzing instruction traces and including the effects of various memory reuse policies and long-latency operations.

Then, in 1982 Graham et al. [89] introduced *gprof*, an improvement of the existing Unix-prof tool. Its novelty was the utilization of a call graph to analyze both the time spent on methods and their impact. *Gprof* generated an overhead of about 30% compared to the normal execution.

Hoste et al. [90,91] developed a tool based on ATOM/Pin [92]. This tool performs code instrumentation based on which it can extract ISA-dependent metrics.

Caparros et al. [93] proposed a tool that profiles the binary execution dynamically. They estimated: instruction-level parallelism, thread-level parallelism, potential data-level parallelism, and inter-task data movement. However, this tool was limited by the influence of the architecture characteristics, and they could analyze only single-thread code.

Another work was done by Ferdman et al. [94], using x86 architectures, they tried to analyze a benchmark suite for the cloud. They showed, for certain applications, an over-provisioning of the memory bandwidth and low memory-level parallelism. However, they used hardware performance counters, and this limits the analysis to the employed hardware, especially for micro-architecture features such as cache size, issue width, etc.

Nowadays, a large number of commercial target-dependent tools are available. One of the most common ones [95] is included in Linux OS, and it is called *perf*. Using the available performance counters *perf* can extract interesting information, e.g., cache miss, rate and CPU utilization. The *nvprof* (*NVIDIA*) profiling tool [62] is specialized on GPU workload analysis. It can extract a timeline of CUDA-related activities on both CPU and GPU, including kernel execution, memory transfers, CUDA API calls, and events, or metrics for CUDA kernels.

Also, Intel has developed some interesting analysis tools; such as 1) Intel VTune Amplifier [64] that can extract a wide range of analysis metrics about CPU, Memory, and GPU; this is based on the work of Yasin et al. [96]. It is easy to use, and the overhead added to the application is very low; 2) Intel Advisor Roofline [97] that can plot a roofline model of the analyzed application allowing

memory and compute boundedness analysis.

#### 2.3 Radio-astronomical imaging

An important use case is represented by radio-astronomical imaging. Indeed, applications of this field are fundamental to answer important questions such as: how do galaxies and planets form? are we alone in the universe?

These problems have high-performance requirements. For instance, the Square Kilometre Array (SKA) radio-telescope will be the largest radio-telescope in the world hosted in Australia and South Africa. The first construction phase of SKA will finish before the 2030. The processing facilities that the SKA consortium is planning to build for the low and mid frequencies consist of large Science Data Processors. Each of them has a peak performance in the order of 6.50 PFLOP/s, and a thermal design power in the order of 125 MW [4].

We introduce interferometry and imaging in *Section 2.3.1*. Then we highlight some details about the Image Domain Gridding (see *Section 2.3.2* and Deconvolution algorithms (see *Section 2.3.3*.

#### 2.3.1 Interferometry and Imaging

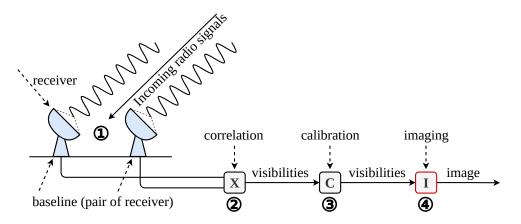

Figure 2.9: Radio astronomy image acquisition: the incoming radio signals are digitized and then correlated and calibrated before the imaging step is executed. We focus on the imaging step, which is highlighted in red.

A radio telescope detects electromagnetic waves that originate from radio sources in the universe. The signals are used, among other things, to construct a map of the sky containing the positions, intensity, and polarization of the sources.

Radio telescopes such as LOFAR (Low Frequency ARray) [98] and SKA1-Low [5] are comprised of many (small) dipole antennas that measure two orthogonal polarizations of the radio sources, while other radio telescopes, such as the VLA [99], MeerKAT [100] and SKA1-Mid [101], are based on an array of dishes. As shown in Figure 2.9, a station consists of multiple antennas, for which the signals for every distinct frequency channel are combined. The signals of a pair of stations (called a baseline) are multiplied and integrated (correlation ②) for a short period of time (in the order of seconds), thus producing a single visibility (a 2x2 matrix). The data that the telescope produces (the visibilities) is, therefore, a three-dimensional matrix (with indices number of baselines, frequency channels and correlations). The relation between visibilities and sky brightness is given by a measurement equation; see [102] for complete details.

The visibilities are first calibrated (3) and next used to reconstruct the sky brightness in the observation direction using an imaging step (4) [103].

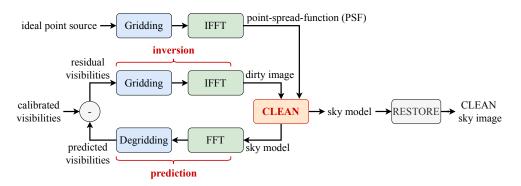

This thesis mainly focuses on ①. The imaging step (see Figure 2.10) starts with an empty sky model and it consists of an iterative process: 1) the inversion step is used to produce a dirty image; 2) one or more bright sources are detected in this image by a deconvolution algorithm such as CLEAN (see also Section 2.3.3); 3) a model image is created, which contains all of the sources in the sky model; 4) visibilities corresponding to this model image are predicted; 5) subtracting the predicted visibilities from the measured (and calibrated) visibilities yields residual visibilities. This process subtracts strong sources from the measurements, which mask the more interesting weak sources. This step is repeated until the sky model converges. Finally, the sky model is used to create the sky image.

The inversion and prediction steps comprise of 2D FFT and a gridding or degridding step. The gridding and degridding steps are typically the most compute-intensive image processing steps. To attain high-quality sky images, they need to correct for Direction-Independent Effects (the curvature of the earth, W-Term correction) and Direction-Dependent Effects (such as ionospheric effects, A-Term correction). The W-Term can be corrected by applying a convolution kernel to every visibility. The required convolution kernel could be huge, depending on parameters such as the field-of-view and distance between receivers. A-Term correction requires these convolution kernels to be different for every receiver and change over time according to changes in the Direction-Independent effects. These properties make imaging with correction for W-Terms and A-Terms particularly challenging.

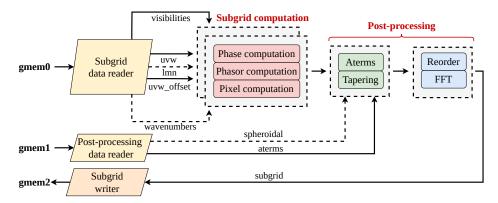

#### 2.3.2 Image-Domain Gridding

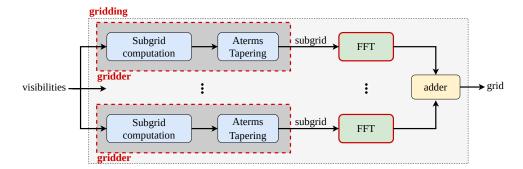

Image-Domaing Gridding (IDG) is a state-of-the-art algorithm for both gridding and degridding [105]. IDG performs both W-correction and A-correction in the image domain, avoiding large convolutions functions. The algorithm performs gridding and degridding using subgrids, which represent low-resolution sky im-

Figure 2.10: High-level schematic of the radio-astronomical imaging step. The three main phases inversion, prediction and deconvolution (or CLEAN), are highlighted in red. The critical computations are typically the inversion and the prediction steps, which include Gridding/Degridding and 2D Fast Fourier Transforms. We included the point-spread-function (PSF) computation, which is an inversion step with an all-ones matrix of visibilities and it is used during the CLEAN.

ages for a subset of visibilities. This approach exposes a lot of parallelism (subgrids can be processed in parallel), which makes it highly efficient on parallel hardware such as GPUs [4]. In IDG, gridding comprises three steps: 1) visibilities are gridded onto subgrids; 2) subgrids are Fourier transformed; 3) subgrids are added to the larger final grid. IDG degridding comprises these steps in reverse order. Refer to [4,105] for all the details on this algorithm and a formal derivation. Image-Domain Gridding performs much better [106] than classical gridding/degridding algorithms, such as W-projection [107] or AW-projection [108]. It also employs W-terms to solve artifacts around sources away from the phase center in wide-field imaging. Moreover, IDG image quality is higher than W-projection because IDG, like AW-projection, corrects for DDEs (direction-dependent effects, also called the A-terms), but the computational costs for such DDE corrections are much lower for IDG than for AW-projection [4]. IDG also has higher per-visibility accuracy compared to the other algorithms [105].

#### 2.3.3 Deconvolution

The objective of a CLEAN (or deconvolution) algorithm is to detect sky sources by iteratively finding the brightest peaks in a dirty image and fitting a sky model. In  $Figure\ 2.12$  we show an example of a dirty image and the corresponding image after a deconvolution algorithm has been applied. The CLEAN image shows lower noise compared to the dirty image.

Many CLEAN algorithms have been proposed in the literature. We briefly de-

Figure 2.11: Gridding high-level representation. It consists of multiple gridder computations (subgrid computation and tapering) and FFTs that process the input visibilities into subgrids. Then the subgrids are processed by the adder to obtain a grid. The gridder and FFT, red boxes, are the focus of this and the related work [104].

scribe the commonly used CLEAN algorithms in radio-astronomical imaging:

**Högbom**: it is the simplest CLEAN algorithm. After the dirty image is generated from the imaging step (gridding and IFFT), the Högbom CLEAN tries to remove the noise in the image. This is done iteratively, looking for the maximum value in the image. Then, the algorithm subtracts the Point Spread Function (PSF), which is a function dependent on the telescope used. It is computed like the dirty image using as input a Visibility array with values equal to 1, multiplied by a gain factor. After a certain number of iterations or when a certain threshold (e.g.,  $3\sigma$  of the standard deviation) is reached the algorithm stops. This algorithm does not include the prediction step.

Clark [109]: it is an improvement of the previously described algorithm, adds a feedback loop and tries to remove alias errors. It is possible to distinguish between major and minor iterations in this case. The minor iterations are represented by the peak search, similar to Högbom (the CLEAN box in *Figure 2.10*). Then, the model image is Fourier transformed and subtracted from the dirty image. This is the so-called major iteration.

Cotton-Schwab [110] and Multiscale [111, 112]: are the most employed and modern CLEAN algorithms, they have in common the prediction phase, thus including the degridding algorithm. Here the subtraction is done at the visibilities level reducing the pixelation error. More precisely, for these algorithms, a major iteration consists of an entire iteration to transform the data from the visibility domain to the image domain (inversion). The major iterations are executed until a threshold is reached, e.g., until 80% of the flux (which is a power density measure)

#### CHAPTER 2. BACKGROUND

Figure 2.12: Comparison between dirty image (left) and CLEAN image (right) applying Cotton-Schwab algorithm. The CLEAN image has reduced noise, e.g. rotation lines around the image(visible especially at the corners).

is removed from the dirty image during the minor iterations. The Multiscale algorithm operates on a set of residual images obtained by convolving the dirty image with different scale sizes. The peak subtraction step is performed on all the scaled imaged, and only the subtracted components are stored in the CLEAN component table. After being scaled, positioned, and convolved, the final image is obtained by adding the components. It decreases the effects of the pedestal of uncleaned flux and strong sidelobes present in the dirty beam (or Point-Spread Function), which are referred to as "clean bow", around bright resolved structures and has better convergence properties [113].

We employ in our analysis work, presented in *Chapter 6*, the Cotton-Schwab algorithm, which is available in the state-of-the-art imager WSClean [114].

# 3

### Platform-Independent Software Analysis

Application characterization is typically employed to determinate application bottlenecks and understand application features to select which kernel must be optimized and the most suitable optimization or hardware. Thus, profiling applications is a critical task to reach the goal of high performance and high energy efficiency. Emerging computing architectures such as near-memory computing (NMC) promise high performance for specific applications by reducing the data movement between CPU and memory. However, detecting such applications is not a trivial task.

This chapter presents an extension of the Platform-Independent Software Analysis (PISA) tool based on the LLVM framwork (see Section 3.1) with NMC related metrics such as memory entropy, spatial locality, data-level, and basic-block-level parallelism that are described in Section 3.2. By profiling a set of representative applications and correlating the metrics with the application's performance on a simulated NMC system, we verify the importance of those metrics. We demonstrate which metrics help identify applications suitable for NMC architectures (see Section 3.3). Finally, we present in Section 3.4 the related work and in Section 3.5 the conclusions.

This chapter is based on: S. Corda et al., "Memory and Parallelism Analysis Using a Platform-Independent Approach", SCOPES 2019 and S.Corda et al., "Platform Independent Software Analysis for Near Memory Computing", DSD 2019

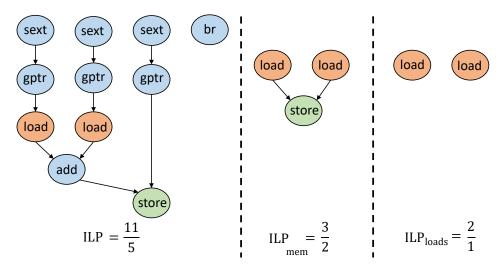

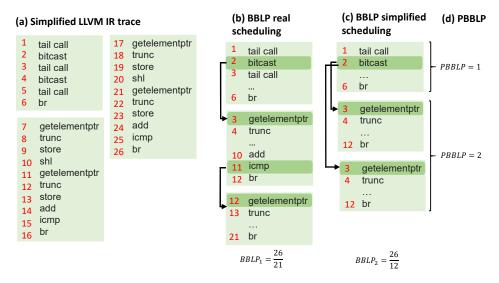

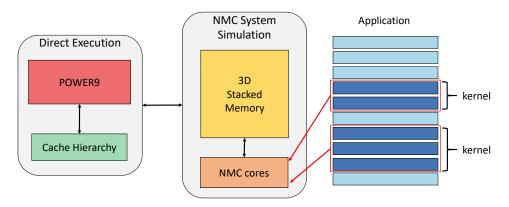

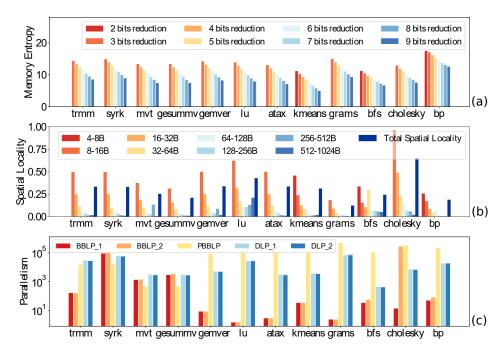

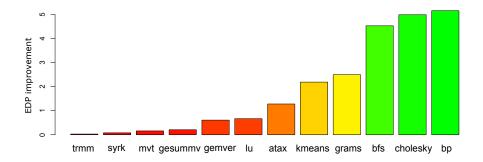

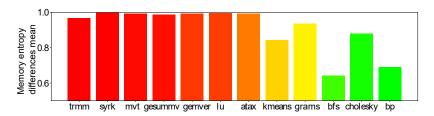

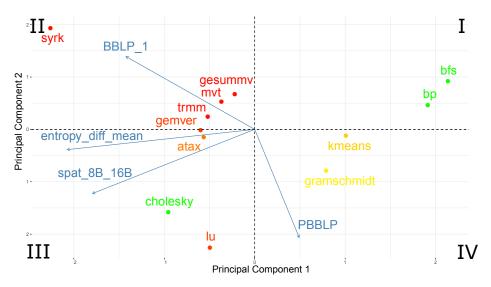

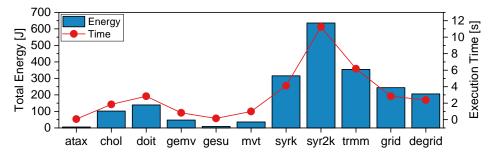

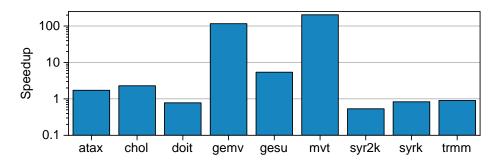

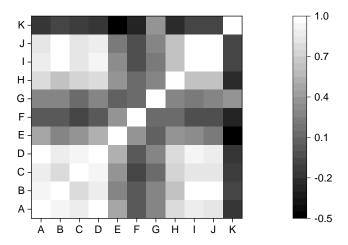

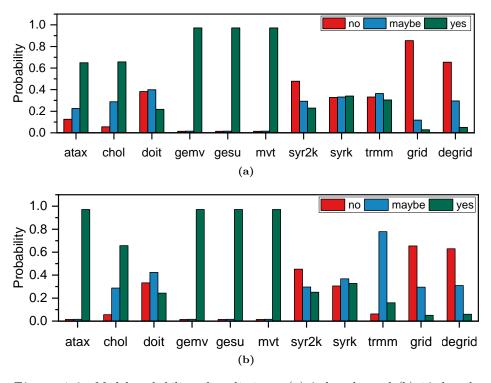

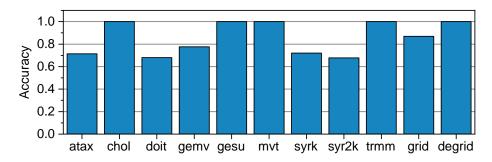

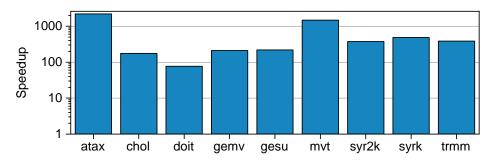

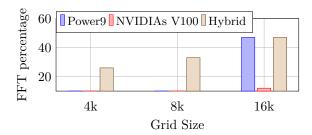

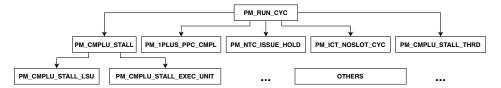

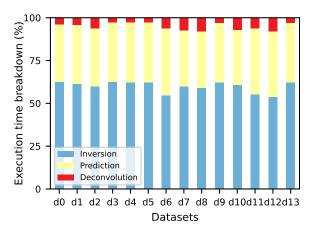

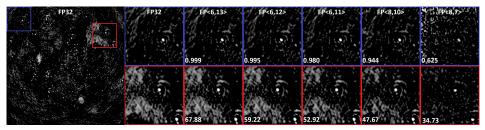

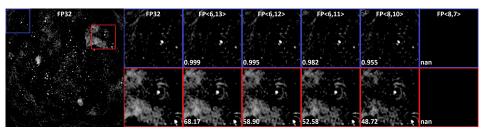

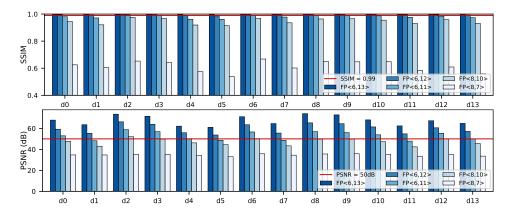

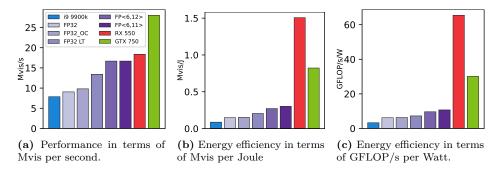

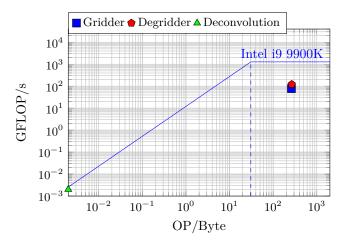

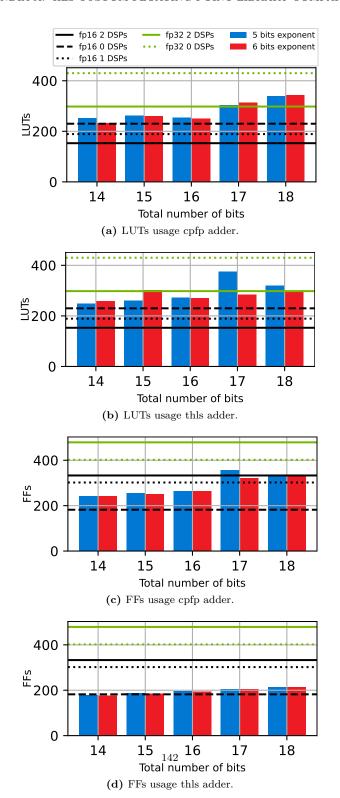

#### 3.1 Platform-Independent Software Analysis