# Polar coding for optical wireless communication

Citation for published version (APA):

Zheng, H. (2020). Polar coding for optical wireless communication. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven.

#### Document status and date:

Published: 15/12/2020

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 08. Feb. 2024

# Polar Coding for Optical Wireless Communication

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op donderdag 15 december 2020 om 16.00 uur

door

Haotian Zheng

geboren te Hubei, China

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

Voorzitter: prof.dr.ing. A.J.M. Pemen Promotor: prof.ir. A.M.J. Koonen

Co-promotor: dr.ir. Z. Cao

dr.ir. A. Balatsoukas Stimming

Leden: prof.dr. M. Karlsson (Chalmers University of Technology)

prof.dr.ir. F.M.J. Willems dr. C.M. Okonkwo

dr. S.A. Hashemi (Stanford University)

Het onderzoek of ontwerp dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

A catalogue record is available from the Eindhoven University of Technology Library.

ISBN: 978-90-386-5185-9

NUR: 959

Title: Polar Coding for Optical Wireless Communication

Author: Haotian Zheng

Eindhoven University of Technology, 2020.

$Keywords: Optical \ wireless \ communication \ / \ Polar \ Codes \ / \ Complexity-adjustable \ decoder \ / \ Interframe \ polar \ coding \ / \ Fast \ successive \ cancellation \ decoder \ / \ Hardware \ implementation \ / \ Infrared \ light \ communication$

Copyright © 2020 Haotian Zheng

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written consent of the author.

Typeset using LATEX, printed in The Netherlands.

#### **SUMMARY**

The demand for wireless communications is growing rapidly. It is expected that before 2030 not only almost all inhabitants of the earth will carry at least one personal wireless device, but that also 50 billion autonomous devices will have a wireless connection to the Internet of Things (IoT). The rapid growth of wireless traffic has introduced immense pressure on the limited radio frequency spectrum and the opening-up of new radio spectrum alone cannot bear this heavy burden. Optical wireless communication (OWC), using a carrier in the optical spectrum, promises to become a key alternative as a complementary solution to mitigate the pressure on the scarce radio spectrum and to realize high-speed wireless communication. Compared to radio communications, OWC using optical beams offers a number of unique advantages: license-free huge bandwidth, physical security, improved privacy, electromagnetic interference immunity, and high energy efficiency because each light beam can be targeted to the intended user individually at the time he needs it. An OWC system is mainly deployed in indoor scenarios as a supplement to radio techniques to help dealing with the tremendous indoor data traffic volume. High reliability, high speed and low power are three main requirements of an OWC system and also great challenges for its signal processing modules. Amongst the baseband signal processing units, the channel coding units, especially the decoder, are key components to achieve the above requirements. Proposed by Arıkan in 2008, polar codes have received a great deal of attention from both academia and industry in the past few years to the extent that they have been selected to be included in the channel codes adopted by the 5th Generation Wireless Communications Standard (5G). They have the advantages of good error-correction performance without error floor, no random-like construction or iterative decoding, and flexible code rate. However, being the most commonly used decoder of polar codes in practice, the successive cancellation list (SCL) decoder suffers from high complexity and high latency induced by its inherent principle. What's more, it has a bottleneck in error-correction performance at the short code length which is preferred by a latency-stringent communication system like OWC.

This Ph.D. research is aiming to design polar coding schemes with high error-correction performance, low latency and low computational complexity, especially advanced polar decoders, as a means to help realize high-reliability, high-speed and low-power OWC systems. The research results are multi-faceted, including theoretical innovations, hardware implementations and experimental demonstrations.

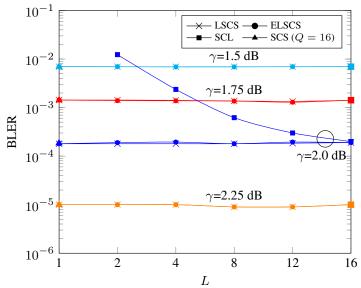

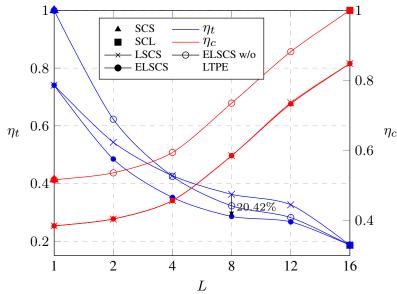

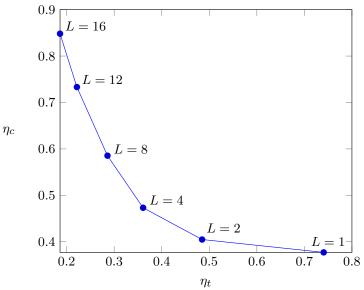

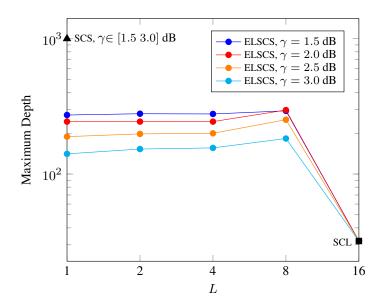

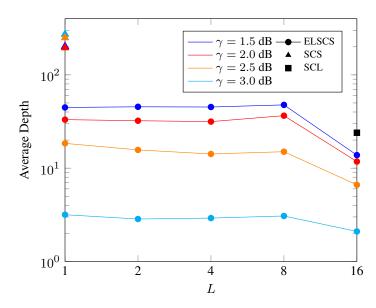

To combat the high computational complexity, we first identify the defects in the principle of an SCL decoder and also investigate another decoder with different principle and complementary performance, called successive cancellation stack (SCS) decoder. Then we combine the advantages of both decoders to create the list-aided successive cancellation stack (LSCS) decoder. It is a multi-mode decoder viii Contents

which can make a flexible trade-off between the computational and time complexity, corresponding to energy and latency costs respectively, by adjusting its working mode, while maintaining a constant error-correction performance. Taking advantage of this property, we can choose different modes of the LSCS algorithm to meet different application requirements at a low computational complexity. Besides, an enhanced version of LSCS is also proposed to improve resource utilization and further reduce time complexity.

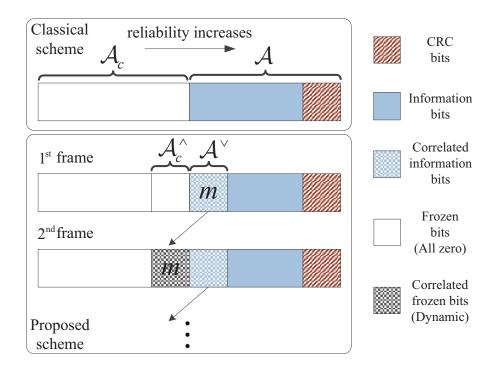

In order to address the bottleneck in error-correction performance at short code length, we jumped out of the conventional research idea focusing on improving the decoding performance of each separate frame. A novel inter-frame related polar coding is proposed which creates associations between two adjacent frames in a clever way by sharing some mutual information. Based on the proposed encoding scheme, a simple and efficient decoder is designed which makes use of this mutual information to execute re-decoding for decoding failed frames, thus increasing the average probability of successful decoding. Compared to the conventional polar coding, the performance improvement is significant even at short and moderate code lengths, while the increment in memory requirements and average computational complexity is negligible.

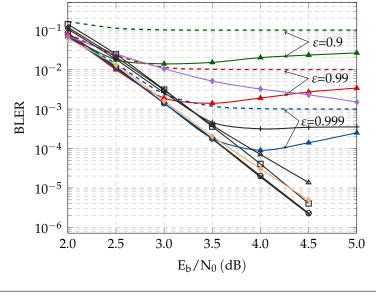

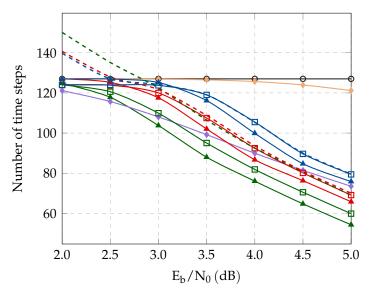

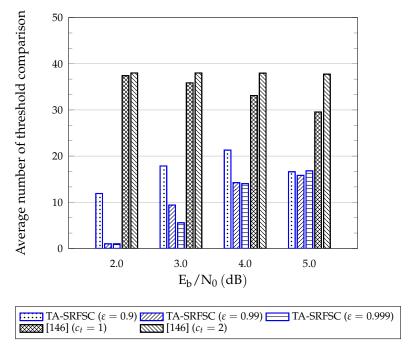

In order to overcome the high latency incurred by sequential bit-by-bit decoding nature of the successive cancellation decoder, many efforts have gone into the research of fast simplified successive cancellation decoders employing different special node types corresponding to codes with special frozen bit patterns. A fast multi-bit processor is designed for each node type considering their specific code structure, thus reducing the total latency. The current research trend is to discover more and more special node types and equip the fast SC decoder with their dedicated processor. However, we try to find the common point of those special nodes and come up with a generalized node type, called sequence repetition (SR) node, and almost all existing nodes are special cases of this one. Furthermore, we prove an important property of an SR node which enables the design of a fast decoder with the highest parallelism and lowest decoding latency ever, using only one processor. In addition, for general nodes outside the class of SR nodes, a threshold-based hard-decision-aided (TA) scheme is introduced to speed up their decoding process, especially under good channel conditions. Unlike existing TA schemes whose effect on performance is unpredictable, we derive the threshold value that guarantees a given error-correction performance in the proposed scheme theoretically.

In consideration for practical implementation, a hardware architecture that exploits the proposed SR node has been designed and specified for the 5G polar codes. At the end of this thesis, the first polar-coded modulation based infrared light communication system is experimentally demonstrated.

# **CONTENTS**

| Su | ımma  | nry                                                                  | vii  |

|----|-------|----------------------------------------------------------------------|------|

| Li | st of | Abbreviations                                                        | xiii |

| 1  | Intr  | oduction                                                             | 1    |

|    | 1.1   | Optical wireless communication                                       | 1    |

|    | 1.2   | Channel coding in OWC                                                | 4    |

|    |       | 1.2.1 Role of channel coding in OWC                                  | 4    |

|    |       | 1.2.2 Channel codes classification                                   | 5    |

|    |       | 1.2.3 Reported work on channel codes in OWC                          | 6    |

|    | 1.3   | Polar Codes: challenges and motivation                               | 8    |

|    |       | 1.3.1 Brief introduction of polar codes                              | 8    |

|    |       | 1.3.2 Challenges in polar codes                                      | 10   |

|    | 1.4   | Outline and contributions of the thesis                              | 12   |

| 2  | A R   | eview of Polar Codes                                                 | 15   |

|    | 2.1   | The theory of channel coding                                         | 15   |

|    |       | 2.1.1 Channel model and capacity                                     | 15   |

|    |       | 2.1.2 Channel coding                                                 | 17   |

|    | 2.2   | Polar Codes                                                          | 18   |

|    |       | 2.2.1 Channel polarization                                           | 19   |

|    |       | 2.2.2 Polar codes construction                                       | 23   |

|    |       | 2.2.3 Polar encoding and decoding                                    | 25   |

|    | 2.3   | Summary                                                              | 35   |

| 3  | Cha   | nnel Coding Requirements for Optical Wireless Communications         | 37   |

|    | 3.1   | Typical optical wireless communication system                        | 38   |

|    | 3.2   | Channel properties                                                   | 39   |

|    | 3.3   | Requirements on channel coding                                       | 40   |

| 4  | Con   | nplexity-Adjustable SC Decoding of Polar Codes                       | 43   |

|    | 4.1   | Introduction                                                         | 43   |

|    | 4.2   | SCL and SCS decoding algorithms                                      | 45   |

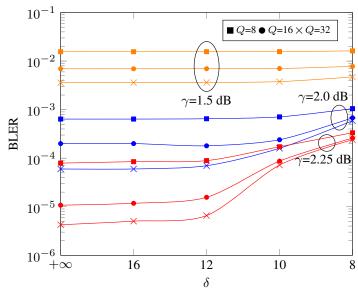

|    | 4.3   | LLR-threshold based path extension scheme                            | 47   |

|    | 4.4   | List-aided successive cancellation stack decoding algorithm          | 51   |

|    | 4.5   | Enhanced list-aided successive cancellation stack decoding algorithm | 54   |

|    | 4.6   | Numerical results                                                    | 57   |

|    | 4.7   | Conclusion                                                           | 62   |

Contents

| 5 | Hig      | h Error-Correction Performance Decoder of Polar Codes               | 63  |

|---|----------|---------------------------------------------------------------------|-----|

|   | 5.1      |                                                                     | 63  |

|   | 5.2      | Inter-frame polar coding                                            | 64  |

|   |          | 5.2.1 Inter-frame correlated encoding scheme                        | 64  |

|   |          | 5.2.2 Inter-frame assisted decoding scheme                          | 65  |

|   | 5.3      | Complexity analysis                                                 | 69  |

|   | 5.4      | Simulation results                                                  | 69  |

|   | 5.5      | Conclusion                                                          | 72  |

| 6 | Fast     | Successive-Cancellation Decoder of Polar Codes                      | 73  |

| Ŭ | 6.1      | Introduction                                                        | 73  |

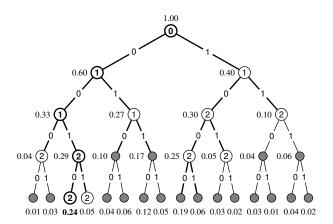

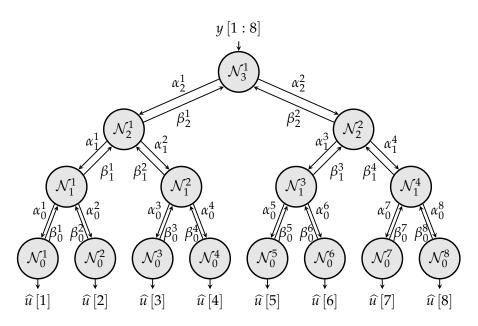

|   | 6.2      | Binary tree representation and fast SC decoding                     | 75  |

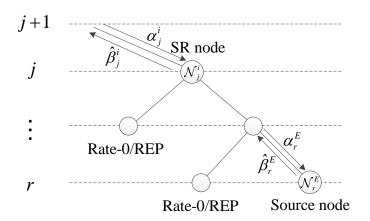

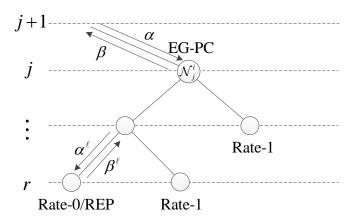

|   | 6.3      | Fast SC decoding with sequence repetition nodes                     | 77  |

|   | 0.0      | 6.3.1 Sequence repetition (SR) node                                 | 77  |

|   |          | 6.3.2 Source node                                                   | 78  |

|   |          |                                                                     | 80  |

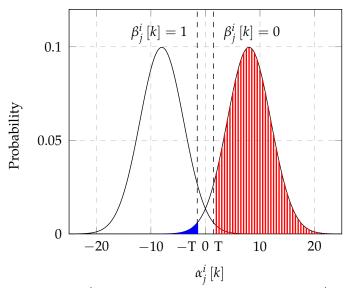

|   |          | 1 1                                                                 | 81  |

|   | 6.1      | 0                                                                   | 82  |

|   | 6.4      | Hard-decision-aided fast SC decoding with sequence repetition nodes |     |

|   |          | 6.4.1 Proposed threshold-based hard-decision-aided scheme           | 83  |

|   | <i>(</i> | 6.4.2 Multi-stage decoding                                          | 86  |

|   | 6.5      | Decoding latency                                                    | 87  |

|   |          | 6.5.1 No resource limitation                                        | 87  |

|   |          | 6.5.2 With hardware resource constraints                            | 89  |

|   | 6.6      | Results and comparison                                              | 89  |

|   | 6.7      | Conclusion                                                          | 95  |

| 7 |          | dware Implementation of Decoder for Polar Codes                     | 97  |

|   | 7.1      | Introduction                                                        | 97  |

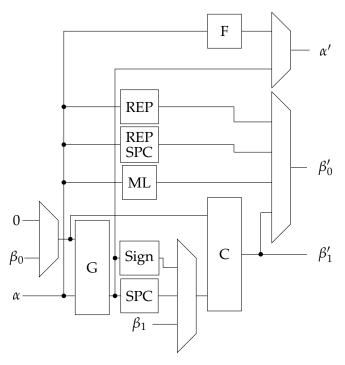

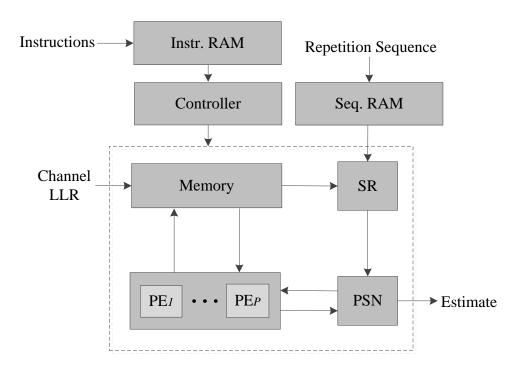

|   | 7.2      | Architecture of SRFSC decoder                                       | 98  |

|   |          | 7.2.1 Memory, processing, and PSN modules                           | 99  |

|   |          | 7.2.2 Controller module                                             | 99  |

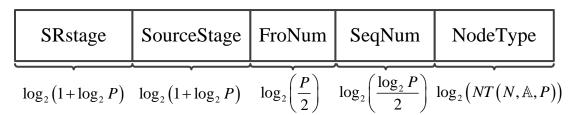

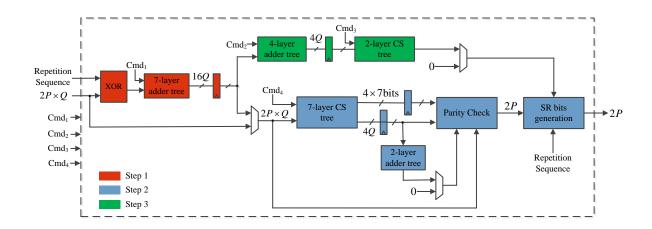

|   |          | 7.2.3 SR module                                                     | 101 |

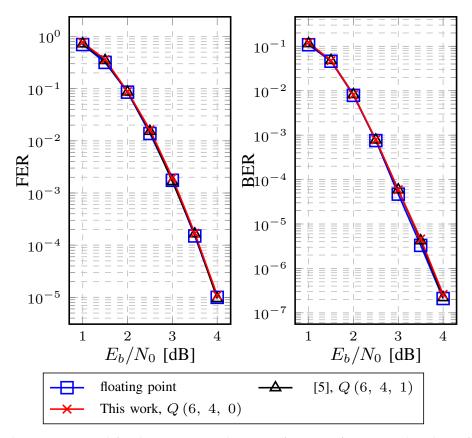

|   | 7.3      | Implementation results                                              | 103 |

|   | 7.4      | Conclusion                                                          | 104 |

| 8 | Opt      | ical Wireless Communication System Validation of Polar Codes        | 107 |

|   | 8.1      |                                                                     | 107 |

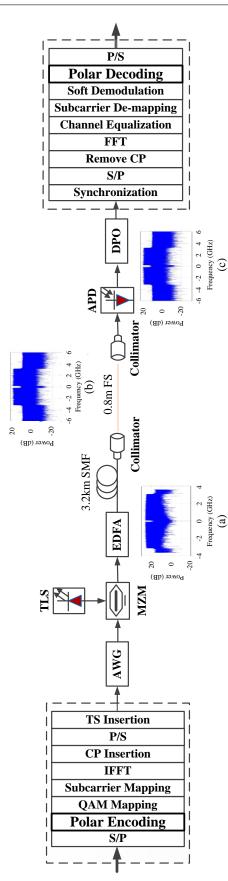

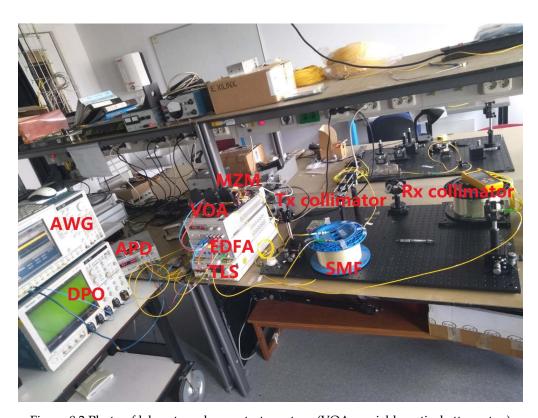

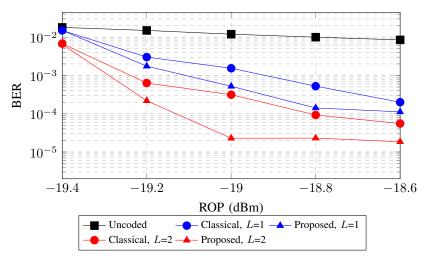

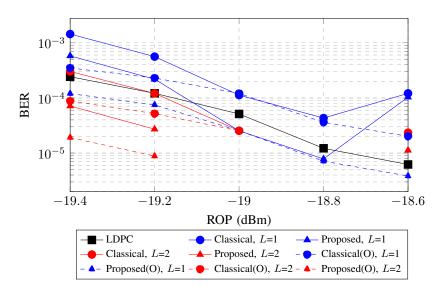

|   | 8.2      |                                                                     | 108 |

|   |          | 1                                                                   | 108 |

|   | 8.3      |                                                                     | 110 |

|   | 8.4      | 1                                                                   | 114 |

| 9 | Sur      | nmary and Future Work                                               | 115 |

| , | 9.1      |                                                                     | 115 |

|   | ~ · I    |                                                                     | 0   |

|          | •  |

|----------|----|

| Contents | Y1 |

| Contents | A1 |

| 9.2     | Futur   | e work                                     | 117 |

|---------|---------|--------------------------------------------|-----|

|         | 9.2.1   | Complexity                                 | 117 |

|         | 9.2.2   | Error-correction performance               | 117 |

|         | 9.2.3   | Latency                                    | 118 |

|         | 9.2.4   | Experiment                                 | 118 |

|         | 9.2.5   | Polar codes using MIMO and NOMA techniques | 118 |

|         | 9.2.6   | Other challenges                           | 119 |

| Refere  | nces    |                                            | 121 |

| List of | publica | ations                                     | 137 |

### LIST OF ABBREVIATIONS

Fifth Generation

One Dimensional

Two Dimensional

Three Dimensional

ALU Arithmetic Logic Unit

AWGN Additive White Gaussian Noise AWGR Arrayed Waveguide Grating Router

APD Avalanche Photodiode BEC Binary Erasure Channel

BER Bit Error Rate

BCH Bose-Chaudhary-Hocquenhem

BIPCM Bit-Interleaved Polar-Coded Modulation B-DMC Binary Discrete Memoryless Channel

BP Belief Propagation

BPSK Binary Phase Shift Keying

BLER Block Error Rate CLK Clock Cycle

CAPEX Capital Expenditures

CC Convolutional Code

CS Compensation Symbol

CWC Constant Weight Code

CDMA Code Division Multiple Access

CRC Cyclic Redundancy Check

CS Compare-and-Select

CMOS Complementary Metal Oxide Semiconductor

DE Density Evolution DMT Discrete Multitone

DMC Discrete Memoryless Channel

DC Direct Current

DPO Digital Phosphor Oscilloscope

ECC Error-Correction Code

eMBB Enhanced Mobile Broadband EDFA Erbium-Doped Fiber Amplifier FEC Forward Error Correction

FSC Fast Successive Cancellation FoV Field-of-View

FPGA Field Programmable Gate Array

FS Free-Space

GA Gaussian Approximation

GFSC Generalized Fast Successive Cancellation

ILC Infrared Light Communication

BS-ILC Beam-Steered Infrared Light Communication

IrDA Infrared Data Association ISI Intersymbol Interference

IM/DD Intensity Modulation with Direct Detection

IFA Inter-Frame Assisted

IFFT Inverse Fast Fourier Transform

LLR Log-Likelihood Ratio LED Light Emitting Diode

LOS Line-of-Sight LD Laser Diode

LDPC Low Density Parity Check

LR Likelihood Ratio

LSCS List-aided Successive Cancellation Stack LTPE LLR-Threshold based Path Extension

LUT Look Up Table

ML Maximum Likelihood MAP Maximum A Posteriori

MIMO Multiple Input Multiple Output

MCU Metric Computation Unit

MD Mobile Device

MZM Mach Zehnder Modulator

MMF Multimode Fiber

MRFB Most Reliable Frozen Bit

MUUB Most Unreliable Unfrozen Bit

NRZ Non-Return-to-Zero

NOMA Non-Orthogonal Multiple Access NSPC Non-Systematic Polar Codes OWC Optical Wireless Communications

OFDM Orthogonal Frequency Division Multiplexing

OOK On-Off Keying

OCT Orthogonal Circulant Matrix Transform

OXC Optical Crossconnect

CCC Central Communication Controller

PIN P-type/intrinsic/n-type Diode

PAM Pulse-Amplitude Modulation

PPM Pulse-Position-Modulation

PDF Probability Density Function

PM Path Metric

PE Processing Element PSN Partial Sum Network List of Abbreviations xv

PRA Pencil-Radiating Antenna

PRBS Pseudo-Random Binary Sequence

PSN Partial Sum Network

P/S Parallel to Serial

QC Quasi-Cyclic

QAM Quadrature-Amplitude Modulation

RPM Relative Path Metric RGB Red+Green+Blue RF Radio Frequency RLL Run Length Limited

RM Reed-Muller REP Repetition

RAM Random Access Memory

RCPC Rate-compatible Punctured Convolutional

ROP Received Optical Power

SC Successive Cancellation

SCL Successive Cancellation List

SCS Successive Cancellation Stack

**SCAN** Soft Cancellation SR Sequence Repetition **SNR** Signal-to-Noise Ratio **SMPC** Systematic Polar Codes **SPC** Single Parity Check SM Sign and Magnitude Single-Mode Fiber **SMF SRFSC** SR Node-Based Fast SC

S/P Serial to Parallel

TA Threshold-Based Hard-Decision-Aided

TIA Transimpedance Amplifier

TB Transport Block

TLS Tunable Laser Source

TS Training Sequence

UVC Ultraviolet Communication

URLLC Ultra-Reliable Low-Latency Communication

VLC Visible Light Communication VOA Variable Optical Attenuator

WDM Wavelength Division Multiplexing

### **INTRODUCTION**

# 1.1 Optical wireless communication

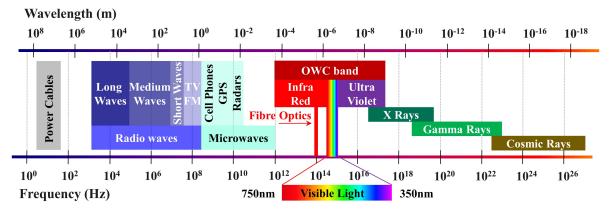

Communication via light has been a convenient and low-cost way of exchanging information without the need of a guided channel since the ancient years. The historical forms include beacon fires, smoke, ship flags and semaphores. In 1880, Alexander Graham Bell invented the photophone, the world's first telephone system transmitting voice over a visible light wave [1], which is a prototype of modern optical wireless communication. However, the concept of modern optical wireless communications (OWC) contains carriers covering the whole optical band, which includes not only the most commonly used visible light but also infrared and ultraviolet [2] as shown in Figure 1.1.

Figure 1.1 OWC in electromagnetic spectrum from [3].

The success of radio communications made the optical communication systems almost forgotten in the first half of the twentieth century. Things turned around after the middle of the twentieth century, when radio communication systems came into saturation in capacity mainly due to the depletion of radio spectrum resources. A surge of interest was drawn to the data transmission adopting carriers in the optical spectrum, and the invention of laser [4] and Light Emitting Diodes (LEDs) [5, 6] have accelerated this trend. In 1962, MIT Lincoln Labs built an experimental OWC link using GaAs LED and was able to transmit TV signals over a distance of 48 km. The first laser link to handle commercial traffic was built in Japan by Nippon Electric Company around 1970, with a distance of 14 km [7]. Although many trials of long distance OWC were conducted using different types of lasers and modulation schemes [8], the results were in general disappointing due to large

| Property            | OWC                  | RF Communications      |

|---------------------|----------------------|------------------------|

| Transmitter         | Mainly LED, Laser    | RF antenna             |

| Receiver            | Mainly PIN, APD      | RF antenna             |

| Bandwidth regulated | No                   | Yes                    |

| Data rate           | Low-High             | Low-Medium             |

| Scenario            | Mainly Indoor        | Indoor and outdoor     |

| Penetration         | Weak                 | Strong                 |

| Mobility            | Limited              | High                   |

| Power consumption   | Low                  | Medium                 |

| Dominant noise      | Background light     | All electrical devices |

| Multipath fading    | No                   | Yes                    |

| Security            | High                 | Low                    |

| Health safety       | Potential eye hazard | No obvious hazard      |

Table 1.1 Comparison between OWC and RF communication systems

(PIN: p-type/intrinsic/n-type diode; APD: avalanche photodiode.)

divergence of laser beams and the inability to cope with atmospheric effects, such as air turbulence, rain, fog. With the development of low-loss fiber optics in the 1970s, they became the obvious choice for long distance optical transmission and shifted the focus away from OWC systems. Nevertheless, OWC is still a strong competitor to the "last mile solution" both for indoor and outdoor communications. The latest transmission rate record is 8.9 Tbit/s offered by 2D steerable infrared beams with a reach beyond 2.5 m shown in [9]. OWC offers a number of unique advantages over its Radio Frequency (RF) counterpart, such as a much wider unregulated bandwidth for high data rate, secure connectivity, absence of electromagnetic interference, low latency. A general comparison between OWC technologies and RF communications is listed in Table 1.1.

Amongst the three OWC technologies: visible light communication (VLC), infrared light communication (ILC) and ultraviolet communication (UVC), VLC and ILC are most attractive as they can provide high-capacity wireless communication solution for the massive indoor data traffic volume. VLC has a spectrum range between 400 nm (750THz) and 700 nm (430THz), and may operate on the existing lighting infrastructure. Since it uses LEDs as the transmission source typically, VLC was driven by the progress of LED for solid state lighting. Visible light from an LED traffic signal head was modulated for audio broadcast in an early experiment by Pang et al in 1999 [10]. Tanaka and Komine proposed VLC using white LED in 2001 and 2004, respectively [11, 12]. The use of Red+Blue+Green (RGB) LEDs in VLC system enabled the introduction of Wavelength Division Multiplexing (WDM) technology, which demonstrated a 3.22 Gbps transmission over more than 25 cm distance in 2013 [13]. Compared to prementioned LEDs with a bandwidth on the order of 10 MHz, the current µLED and Resonant-Cavity (RC)-LED have a band-

width of approximately 100 MHz. In [14], they were employed to achieve a data rate of 11.2 Gbps over 1.5 m reach. In addition, advanced modulation techniques like Orthogonal Frequency Division Multiplexing (OFDM) [15] and Discrete Multitone (DMT) modulation format [16] were investigated to apply to VLC systems to boost the transmission rate.

OWC operating in the infrared (IR) spectrum commonly centers at 850 nm (353 THz), 1310 nm (229 THz) and 1550 nm (193THz). Indoor infrared communication was first proposed by F.R.Gfeller and U.Bapst in 1979, operating at 950 nm and achieving 1 Mbps [17]. The Infrared Data Association (IrDA) standard was formed in 1993, thereafter the standard was widely adopted for short range communication. In 2010, the European Community project OMEGA demonstrated a bi-directional OWC one-dimensional (1D) system operated at 1.25 Gbps at Non-Return-to-Zero (NRZ) On-Off-Keying (OOK) format [18]. More recently, OWC systems based on narrow infrared beam steering was reported in the Beam-steered Reconfigurable Optical-Wireless System for Energy-efficient communication (BROWSE) Advanced Grant project [19], led by Professor Ton Koonen from Eindhoven University of Technology. In these systems, a passive diffractive module is used to steer each beam two-dimensionally by just changing its wavelength remotely in the associated transmitter. The 2D beam steering with two crossed gratings was first proposed in [19–21], which established a point-to-point high capacity link. Its directivity enables a high SNR, which leads to high data rates and power efficiency. A speed of 42.8 Gb/s can be achieved, 100 times faster than current wireless networks generally achieve [22, 23]. However, the realization of beam steering using two crossed gratings requires highly-efficient gratings with low polarization dependency and careful highly stable mechanical adjustment of these gratings. As an alternative approach, 2D beam steering with high port-count arrayed waveguide grating router (AWGR) modules which are readily available commercially was proposed in [9]. This setup offers similar performance (up to 35Gbit/s NRZ-OOK and 112Gbit/s PAM-4 per beam), but is easier to assemble and requires less alignment effort. Building on this high-capacity IR beam-steered OWC system, a novel device localization concept was further introduced [24]. It only requires a simple fully passive function at the user device by means of a passive retroreflector based on an optical corner cube (CC) since a CC reflects light rays in the same direction as they came from. Compared to VLC, infrared light communication (ILC) using beams with wavelengths  $\lambda > 1400$ nm can have much higher emission powers, up to 10 dBm allowed by eye safety standards. Moreover, the use of IR laser instead of LED leads to a narrow beam, thus high bandwidth transmission can be achieved. BS-ILC can access up to 20.9 THz bandwidth in the 1460-1625 nm range by employing the well-established S+C+L band fiber-optic communication technologies. As concluded in [25], VLC systems may be preferred regarding capital expenditures (CAPEX) due to their lower infrastructure costs, whereas BS-ILC systems may be more beneficial regarding operating expenditures (OPEX) due to their lower energy consumption, as well as due to their higher energy efficiency, capacity density and higher privacy.

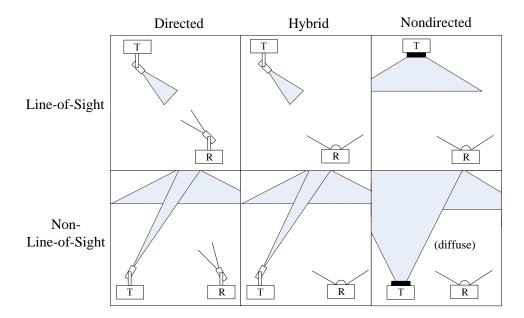

Figure 1.2 Classification of OWC links according to the degree of directionality of the transmitter and receiver and whether there exists a LoS path between them [7].

In terms of practical system implementation, an overview of different link configurations for indoor optical wireless systems is shown in Figure 1.2. Links are classified by two criteria. First, the degree of directionality of the transmitter and receiver. Directed links employ directional transmitters and receivers, while nondirected links employ wide-angle transmitters and receivers. In comparison, a directed link has a higher power efficiency and a nondirected link is more convenient for mobile devices. A hybrid link is a combination of the two forms. The second criterion is whether there exists an uninterrupted line-of-sight (LoS) path between the transmitter and receiver. LoS link is susceptible to blockage and shadowing but provides a higher link power budget. Non-LoS links mainly rely upon reflection of the light from diffusely reflecting surface, thus has a better link robustness and ease of use. In BS-ILC systems, advanced localization technology helps to track the position of device and maintain the connection of mobile users. And the severe impact of blockage is solved by handover between different transmitters.

# 1.2 Channel coding in OWC

## 1.2.1 Role of channel coding in OWC

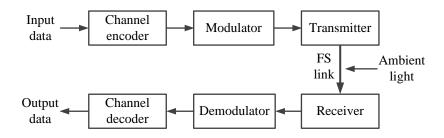

Basically there are two types of coding. 1, Source coding: to code the information of a source as efficiently as possible (e.g. data compression). 2, Channel coding: to code the transmitted data such that it is as robust as possible against transmission errors. This thesis is about channel coding. For an OWC system with noise caused by ambient light, channel coding with forward error correction (FEC) are vital

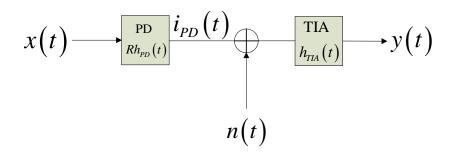

Figure 1.3 Schematic diagram of OWC system.

components to improve communication reliability, which can be described by a quantifiable and intuitive metric, called the bit error rate (BER). The most simple channel coding scheme is the repetition code. The encoder makes multiple copies of blocks of the data. For example, for a system whose uncoded BER is  $P_e$ , a single bit a is copied three times and sent as aaa. The decoder will choose the bit value that happened most frequently as the estimate of a. Hence, the estimate is correct if either no copies of a are in error or if one copy of a is in error and the probability of correct estimate is

$$P_{c,\text{coded}} = (1 - P_e)^3 + 3(1 - P_e)^2 P_e = 1 - 3P_e^2 + 2P_e^3.$$

(1.1)

It can be verified that  $P_{e, \text{coded}} = 1 - P_{c, \text{coded}} < P_e$  for any  $P_e \in [0, 0.5)$ , which means the repetition code improves the BER of the system. The performance improvement is obtained at the cost of extra bits. As a result of this data redundancy, the ratio between the number of the information bits and the transmitted bits, called code rate, is reduced. Generally, a lower code rate can bring better performance. What is of the highest concern is the maximum code rate for a reliable communication. This question is answered by Shannon in his seminal work [26]. He proved that reliable transmission is possible at any rate that is strictly smaller than the capacity of the channel, which is detailed in Chapter 2. However, random codes used by Shannon in the proof are not practical.

#### 1.2.2 Channel codes classification

There has been a great deal of effort in the search for optimal yet practical (i.e., easily implementable) channel codes [27]. Classical algebraic block codes encode messages into blocks, such as Hamming codes, Reed-Muller codes, Reed-Solomon codes and BCH (Bose-Chaudhary-Hocquenhem) codes, whose aim is to find specific codes that maximize the minimum Hamming distance [28]. More recently, convolutional codes have been invented that get very close to Shannon's capacity limit [29]. The convolution codes do not encode in blocks, instead they read and transmit bits continuously, where transmitted bits are a linear combination of previous source bits. Similar codes including Turbo codes [30, 31], Low Density Parity Check (LDPC)

codes [32, 33], etc., are called probabilistic codes since they were more directly inspired by Shannon's probabilistic approach to coding. Unlike algebraic coding, probabilistic coding is more concerned with finding classes of codes that optimize average performance. In general, algebraic codes have lower encoding/decoding complexity than probabilistic codes, while, probabilistic codes like Turbo and LDPC have much better error-correction performance, even capacity-approaching in some specific cases [34]. LDPC codes are selected to be included as a coding scheme for the 5th Generation of Wireless Communications Standard (5G) [35]. The latest breakthrough in channel coding came with Arikan's polar codes [36], which are provably capacity-achieving over a very wide range of transmission channels. Polar codes have advantages over the probabilistic codes in the sense of having no random-like construction, low-complexity encoding, good error-correction performance without error floor and flexible code rate. Currently, polar codes are selected as the coding scheme for the control link in Enhanced Mobile Broadband (eMBB) channel of the 5G standard which requires codes of short lengths.

### 1.2.3 Reported work on channel codes in OWC

The IEEE 802.15.7 standard for VLC [37, 38] introduces two FEC coding schemes, Reed-Solomon (RS) codes and convolutional codes (CC). An adaptive RS code based orthogonal frequency division multiplexing (OFDM) scheme has been proposed to optimize the tradeoff between BER and data rate in VLC system [39-42]. LDPCcoded VLC systems were first demonstrated in [43], supporting a date rate over 1Gbps. VLC systems to mitigate the influence of interference in LED arrays using LDPC were studied in [44]. Recently, a class of protograph based low-density paritycheck (P-LDPC) codes was employed in RGB-LED-based VLC system to improve system performance [45]. Since a VLC systems need to take illumination demand into consideration, dimming control and flicker is a challenging problem for a VLC system that needs variable controlled dimming. The number and distribution of zeros and ones in the transmitted bits must be appropriately arranged for providing target dimming levels. In the IEEE VLC standard, the dimming function is provided via run length limited (RLL) codes [46–48] and compensation symbols (CS) for OOK modulation. The standard does not consider modification of FEC codes according to dimming support. Different error-correction schemes with dimming control have been proposed for VLC systems to achieve reliable data transmission while also providing the flicker-free operation and good dimming control. FEC schemes based on modified Reed-Muller (RM) codes were designed for dimming support in VLC systems in [49, 50]. Another coding scheme based on rate-compatible punctured convolutional (RCPC) code was introduced for providing simple dimming control solution [51]. The punctured bits in the codeword are replaced with compensation symbols generated by dimming controller to achieve the target dimming level. In [52], the proposed turbo coded system employs puncturing and scrambling techniques to match the Hamming weight of codewords with targeted dimming rates. Based on Quasi-cyclic (QC) LDPC codes, an adaptive FEC scheme was proposed

in [53] to efficiently adjust dimming values in VLC systems. The previous works focused on the modification of FECs. Joint FEC-RLL coding solutions were pioneered in [54], where a concatenation of an outer RS code and an inner RLL code was proposed. The serial concatenation of convolutional codes and Miller codes was explored in [55]. A new coding scheme for dimmable VLC systems based on serial concatenation of columnscaled (CS) low-density parity-check (LDPC) codes and constant weight codes (CWCs) was proposed in [56], whose coding rates are not constrained by the dimming range as error control and dimming control are decoupled.

The design of error-correction codes for ILC does not need to consider dimming control since infrared light is invisible. The Advanced Infrared (AIr) standard by the Infrared Data Association (IrDA) proposed a rate-adaptive transmission scheme based on variable-rate repetition coding, providing robust links at data rates between 250 kb/s and 4 Mb/s by using pulse-position modulation (PPM). Additionally, the HHH(1, 13) modulation scheme, based on run-length limited (RLL) coding, has been also proposed by the IrDA in the Very Fast Infrared (VFIr) standard for data transfer of 16 Mb/s, but operating over line-of-sight links of up to 1 m. Rate-compatible punctured convolutional codes (RCPC) and adaptive pulse position modulation (PPM) were applied to indoor infrared wireless communication systems to achieve high bit rate and realise communications even under bad channel conditions with limited transmitter power [57–59]. The concatenation of an outer punctured convolutional code and an inner repetition code was proposed in [58, 60] for indoor infared wireless communication systems. Its code rate varies adaptively depending on channel conditions to achieve the required BER at the expense of bit rate. A RCPC coding scheme with a modified puncturing matrix was studied in [61], which achieves better bit-error rate results than conventional RCPC and convolutional coding schemes. Turbo code was first adopted in infrared wireless communication in [62], where iterative maximum a posteriori probability (MAP) decoding of Turbo coded OOK and Turbo coded binary PPM (BPPM) were presented. It was confirmed in [63] that turbo coding is very effective to improve the throughput-delay performance of an infrared Code Division Multiple Access (CDMA) network. A power-variable rate-adaptive low-density parity-check (LDPC)-coded OFDM scheme was used to deal with bandwidth limitations of indoor infrared links, supporting a high-speed optical signal (40 Gb/s and beyond) to an end-user [64].

Polar codes have only been applied to OWC systems in recent years. Polar codes with list+cyclic redundancy check (CRC) decoding were shown to outperform state-of-the-art LDPC codes in short block lengths, and shorter FEC codes are preferred for latency-stringent systems such as short-reach OWC [65]. In [66], based on polar codes, an efficient and flicker-free FEC coding scheme for dimmable VLC was proposed to increase the transmission efficiency and simplify the coding

structure. The coding gain<sup>1</sup> of the proposed scheme is about 4.6 dB and 1.4 dB higher than that of the RS codes-based scheme and the LDPC codes-based scheme, respectively. Wang and Kim have studied the joint design of polar codes and RLL codes in detail [67–69]. They also proposed a modified likelihood ratio (LR) for decoding of polar codes for mitigating intersymbol interference (ISI), which is a major impairment in visible light communication [70]. A recent study proposed an efficient construction of flicker-free polar codes to tackle the issue of flickering in VLC, which outperforms most state-of-the-art schemes in terms of error correction performance and implementation complexity [71]. The bit-interleaved polar-coded modulation (BIPCM) scheme based on orthogonal circulant matrix transform (OCT) precoding was proposed and experimentally demonstrated for a 256-QAM OFDM-VLC system, achieving a net data rate of 343 Mb/s over 80-cm free-space transmission with a BER below  $10^{-3}$  [72]. The applications of polar codes into Multiple Input Multiple Output (MIMO)-OFDM and non-orthogonal multiple access (NOMA)-enabled VLC systems were further studied in [73, 74]. In [75], a secure coding scheme based on polar codes was proposed to simultaneously achieve physical-layer security and transmission reliability for indoor VLC systems under Wyner's wiretap model. So far, the application of polar codes in ILC systems has not been reported.

# 1.3 Polar Codes: challenges and motivation

## 1.3.1 Brief introduction of polar codes

Polar codes are proposed based on the method called channel polarization. Channel polarization refers to the fact that it is possible to synthesize, out of N independent copies of a given binary discrete memoryless channel (B-DMC), a second set of N binary-input channels such that, as N tends to infinity the capacity of these synthetic virtual channels polarizes to either 0 or 1. One can only send information through those virtual channels with capacity near 1. The remaining virtual channels transmit fixed values known to both the sender and receiver in advance. Codes constructed on the basis of this idea are called polar codes. We will give a detailed review on the theory of polar codes in Chapter 2. As the first provably capacity-achieving codes with low complexity, polar codes have received extensive attention since their inception. Unlike other codes, polar codes are constructed given a specific channel type or channel condition. For the example of a given additive white Gaussian noise (AWGN) channel, polar codes should be optimized point-by-point in the given SNR range in order to achieve the optimal performance at each SNR. Despite the fact that code construction is channel dependent, the encoder structure is universal, following the recursive structure of channel transformation shown in Chapter 2. As for the decoding of polar codes, there are many types of decoders with different principles

<sup>&</sup>lt;sup>1</sup>In coding theory and related engineering problems, coding gain is the measure in the difference between the signal-to-noise ratio (SNR) levels between the uncoded system and coded system required to reach the same bit error rate (BER) levels when used with the error correction code.

and they directly determine the error-correction performance given a specific code construction. Thus, decoders are the research focus of polar codes.

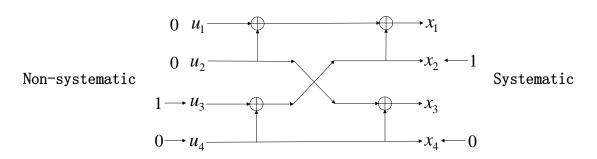

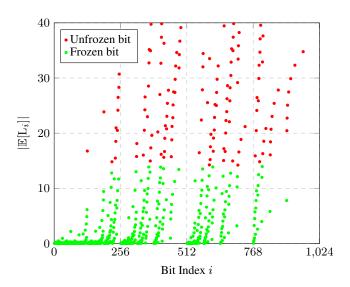

Construction and Encoding of Polar Codes: In his seminal paper [36] Arikan proposed a recursive calculation algorithm based on Bhattacharyya parameters to do channel-reliability evaluation and code construction for binary erasure channel (BEC). For more general channels, Arıkan proposed a Monte Carlo based approach which is universal but time-consuming. Mori and Tanaka proposed the use of density evolution (DE) tools for tracing the probability density function (PDF) of log-likelihood ratios (LLRs) used in the decoding of polar codes [76, 77]. However, its computational complexity is high in practical applications. Different approximation schemes have been taken to simplify the calculations [78–80]. The most practical way is called Gaussian approximation (GA), which enables one to compute only the expected value of LLRs using a recursive formula in the AWGN channel, thus drastically reducing the complexity [79]. However, when the code length is long (2<sup>14</sup> and above code length), the conventional approximate GA which uses a two-segment approximation function is not accurate, resulting in a catastrophic performance loss. New principles to design the GA approximation functions for polar codes were proposed in [81]. After code construction, the encoding can be executed using a recursive structure to obtain the codeword. Polar codes in their standard form are non-systematic codes, in other words, the information bits do not appear as part of the codeword transparently. Systematic polar encoding whose codeword contains information bits was proposed in [82], which offers significant advantages in terms of bit error rate performance with respect to conventional non-systematic counterpart. Efficient algorithms for systematic polar encoding were introduced in

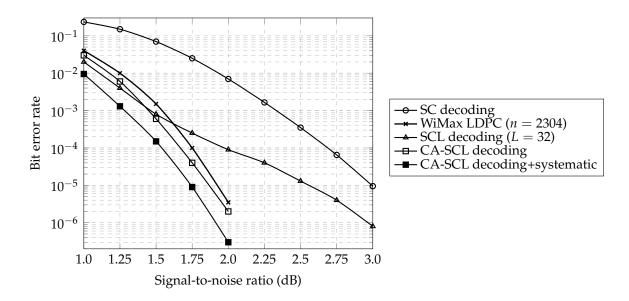

**Decoding of Polar Codes**: It has been proved in [36] that polar codes with successive cancellation (SC) decoding can achieve the capacity of B-DMCs. Nevertheless, the performance of SC decoding for finite code length is not ideal. As an enhanced version of SC, successive cancellation list (SCL) decoding approaches the performance of maximum likelihood (ML) decoding when the list size is large [84]. With the help of cyclic redundancy check (CRC), CRC-aided SCL (CA-SCL) [85] decoding provides a performance beyond the ML performance for SCL without CRC and can outperform LDPC codes at short and moderate code length [65]. Thus, CA-SCL decoding has become the standard benchmark in the research of polar decoders. Aimed at the high complexity problem of SCL decoding, successive cancellation stack (SCS) [86] and successive cancellation flip (SCF) [87] decoding were proposed, which can effectively reduce the computational complexity. But as a tradeoff for complexity reduction, SCS decoding requires a longer decoding latency and larger memory, and SCF decoding has a worse error-correction performance. To overcome the sequential bit-by-bit decoding problem of SC and SCL decoding, simplified fast SC/SCL decoding is proposed, which speeds up the decoding process by making multi-bit decision at some special nodes corresponding to constituent codes with special frozen bit patterns [88–93]. Other decoding algorithms include belief propagation (BP) decoding [94, 95], sphere decoding [96, 97], ordered statistic decoding [98] and soft cancellation (SCAN) decoding [99].

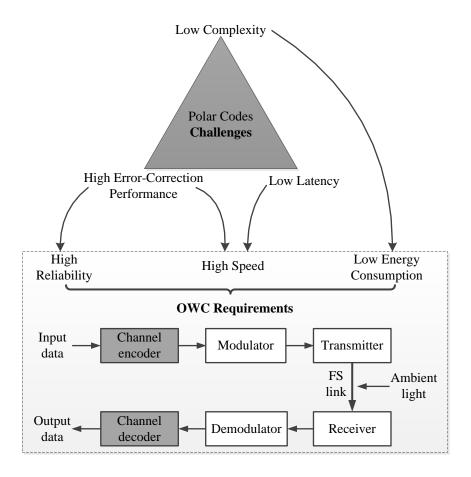

### 1.3.2 Challenges in polar codes

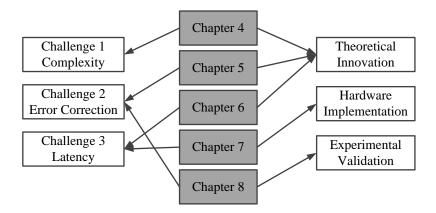

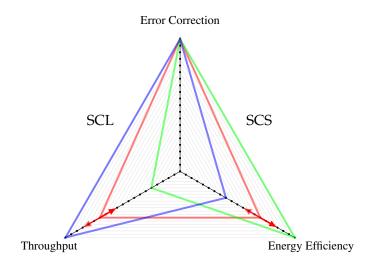

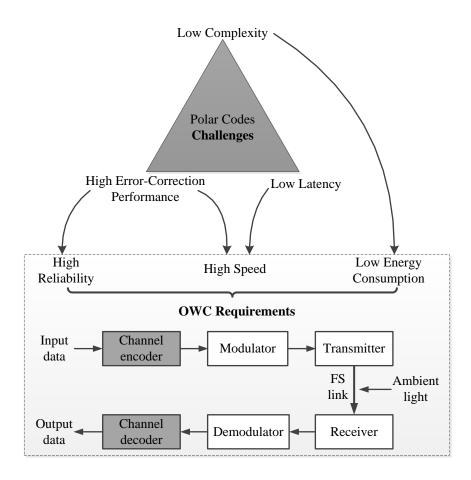

Despite the effort and interest for polar codes both in academic and industrial communities, there are still some challenges that need to be addressed to enable its use in high-reliability, high-speed and low-power OWC system, which are shown in Figure 1.4. The three challenges of polar codes correspond to the three requirements of OWC system. Note that in addition to low latency, high error-correction performance is also important to achieve the high-speed demand in the sense that polar codes with higher error-correction performance enable the use of a higher code rate or higher order modulation format given a target BER, thus boosting the transmission speed. The three challenges are analyzed in detail as follows:

Figure 1.4 Challenges in Polar Codes.

#### **Challenge 1: Complexity**

CA-SCL decoder is currently the most commonly used decoder with a very good error-correction performance. This is mainly due to a parallel search of list size *L* decoding paths, which also causes a large computational complexity. Moreover, the complexity remains constant, even if the noise is low enough for the use of a simpler SC decoder. The high computational complexity leads to a high power consumption, which is not friendly for a mobile device. As one of the few decoders with similar error-correction performance to CA-SCL decoder, a CA-SCS decoder has a much lower complexity than CA-SCL decoder. Moreover, its complexity is channel adaptive, close to that of SC decoder when the channel condition is good. However, the vital disadvantage of high decoding latency hinders its use in latency-sensitive applications. We can observe that it is difficult for a decoder to have the best performance in all metrics such as error-correction, latency and complexity. Hence, the question is how to deal with the tradeoff between metrics and achieve the requirement of a diverse set of applications with as low complexity as possible.

#### **Challenge 2: Error-correction performance**

Polar codes take advantage of the polarization phenomenon by only transmitting information bits through the polarized subchannels with the highest capacity. However, for a practical finite codeword length, especially at short code length, there is a non-negligible fraction of subchannels whose capacity is not fully polarized. The information transmitted through such subchannels is unreliable. This problem limits the error-correction performance of finite length polar codes. The concatenation of polar codes with other codes is considered as an effective way to deal with the partial polarization problem [100–102]. CA-SCL decoding is an example which concatenates polar codes with CRC [85, 84]. The shortcomings of this scheme are a reduction of code rate and longer code length due to concatenation. Another way to improve the error-correction performance is to exploit the benefits of long codes through spatial coupling [103–105]. Theoretically, an infinite long codeword chain can be constructed by coupling an infinite number of finite length code blocks in a certain structure. Spatially coupled codes can achieve considerable coding gains over uncoupled counterparts while maintaining the decoding complexity in a reasonably low level by using windowed decoders [106, 107]. In this scheme, coupled information is shared by several consecutive code blocks in the same codeword. Hence, the effective code rate of the information coupled polar codes is reduced [108, 109]. Existing solutions all lead to a long code length and reduced code rate. However, for a latency-constrained system, such as indoor short-reach OWC system, short code length is required to maintain a low decoding latency. So a challenge is to improve the error-correction performance of polar code with short code length without sacrificing the code rate.

#### Challenge 3: Latency

Conventional SC/SCL decoding implies sequential bit-by-bit decoding, which leads to a high decoding latency. Belief propagation (BP) decoding can be used instead of sequential decoding to reduce latency by parallelizing the decoding process using iterative receivers. However, the overall decoding complexity is high since it is proportional to the number of iterations. What is more, there is a gap between the error-correction performance of BP decoder and CA-SCL decoder. Another simple but efficient way is to make multi-bit parallel decoding at some special node types corresponding to constituent codes with special frozen bit patterns, which is called fast simplified SC/SCL decoding [88–93]. It exploits the characteristic of each special node type and designs their dedicated fast decoders. Although the nature of sequential decoding is not changed, fast SC/SCL decoding can provide a significant latency reduction with negligible performance loss compared to conventional SC/SCL decoding. However, an important problem is that there exist too many special node types, and a separate decoder for each of them will put a heavy burden on the hardware implementation. In addition, we are still on the way of finding a new special node with higher parallelism that can be exploited in decoding, thus further reducing the latency.

#### 1.4 Outline and contributions of the thesis

The main aim of the dissertation is to address the three key challenges mentioned before and design polar coding with high error-correction performance, low latency and low computational complexity for high-reliability, high-speed and low-power wireless communication systems, especially indoor OWC systems. This thesis first provides treatment of these challenges from algorithm level and theoretical perspective. Hardware implementation and experiment demonstration are then presented to further expand the research and build a bridge between theory and practice. The research work carried out in this thesis has led to several contributions in this field. They are categorized in the coming chapters and sections, according to the challenges each contribution addresses, as follows:

Chapter 2 presents an overview of polar codes. We start from the theory of channel coding, followed by the channel polarization theory, which explains why polar codes can achieve channel capacity when the block length tends to infinity. Then we move on to practical design of polar codes, including code construction, encoding and decoding schemes of polar codes in finite block length regime.

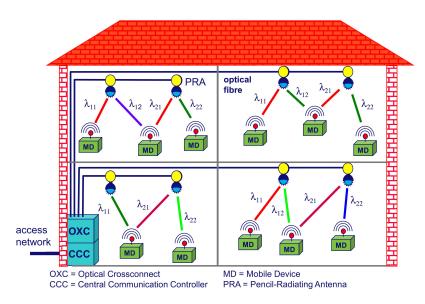

Chapter 3 introduces the optical wireless communication system, to be more specific, the one using pencil beams, employed in the BROWSE project to implement an indoor communication network [19]. Its channel properties and requirements on channel coding are analyzed and discussed in detail.

Chapter 4 proposes a complexity-adjustable successive cancellation decoder called enhanced list-aided successive cancellation stack (LSCS) decoder to meet

Figure 1.5 Challenges and their relations addressed in this thesis.

different application requirements at a low computational complexity. It firstly studies the LLR characteristics of the correct path in the decoding process. Exploiting the characteristics, an LLR-threshold based path extension scheme is designed to reduce the memory consumption of stack decoding. By employing both the ideas of SCL and SCS decoding, a novel LSCS decoding is introduced, which can provide a flexible tradeoff between time complexity and computational complexity. Moreover, LSCS decoding is improved to obtain an enhanced version to further decrease the time complexity.

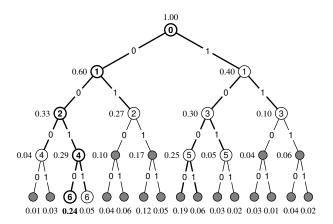

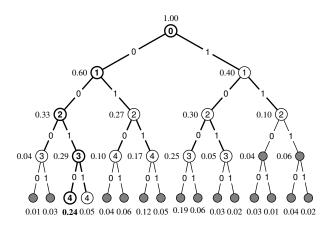

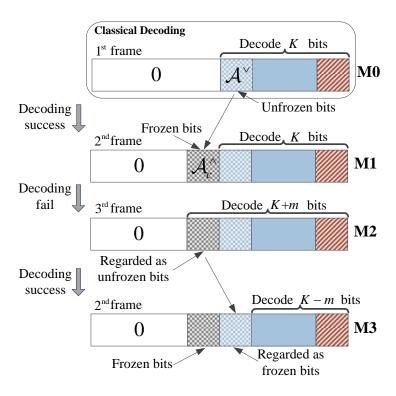

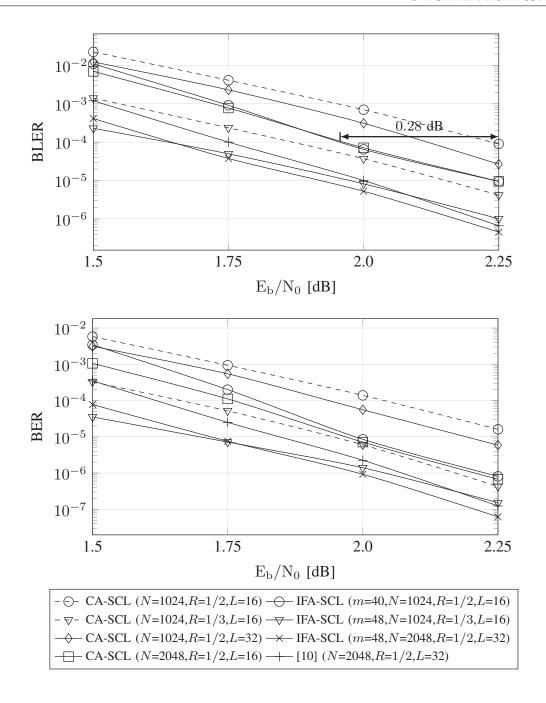

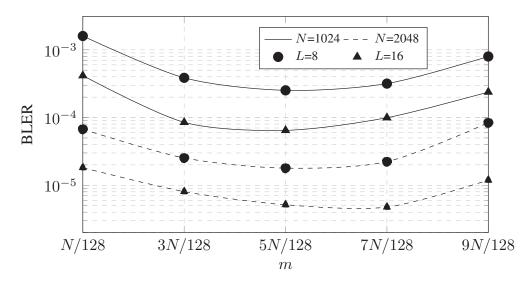

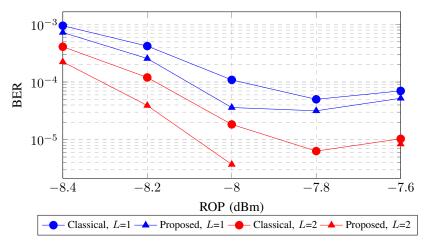

Chapter 5 presents a new inter-frame correlated polar coding scheme to improve the error-correction performance of polar codes. Two consecutive frames are correlated-encoded in the sense that the frozen bits of the second frame partially depend on the unfrozen bits of the first frame. Using this new encoding scheme, a novel decoding scheme is investigated, where consecutive frames can assist each other by performing a re-decoding on a decoding failed frame with the help of the shared information. Simulation results show that the proposed polar codes can yield a significant performance improvement compared to classical polar codes with negligible extra memory and complexity.

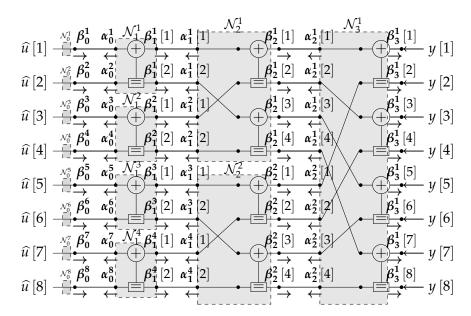

Chapter 6 proposes a fast decoding algorithm based on a new class of sequence repetition (SR) node to reduce the decoding latency. The concept of sequence repetition node and the accompanying concepts of the repetition sequence and the source node are firstly presented. Most existing special node types are special cases of the proposed sequence repetition node. Moreover, an important property of the SR node is proven that enables the design of an efficient fast decoder of the SR node. In addition, for general nodes outside the class of SR, a threshold-based hard-decision-aided scheme is introduced to speed up their decoding process. The threshold value that guarantees a given error-correction performance in the proposed scheme is derived theoretically. Both numerical simulation and hardware implementation results in terms of decoding latency are provided.

Chapter 7 presents the first FPGA implementation of the SR-node-based fast SC decoder. A dedicated architecture for the SR node processor is designed and an instruction structure is given. Moreover, the proposed architecture is specified for a 5G polar code with code length 1024 and three code rates 1/4, 1/2, 3/4, and 64 processing elements. The FPGA implementation results including both resource consumption and decoding latency are provided and compared with previous works.

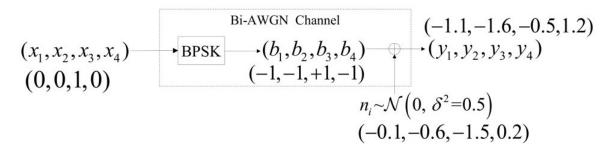

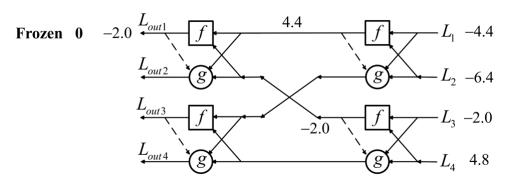

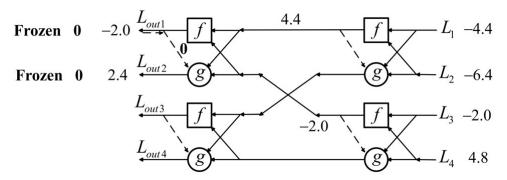

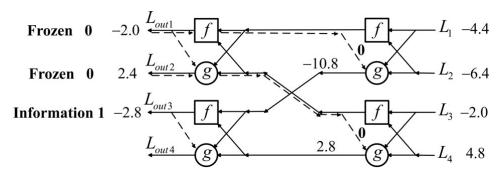

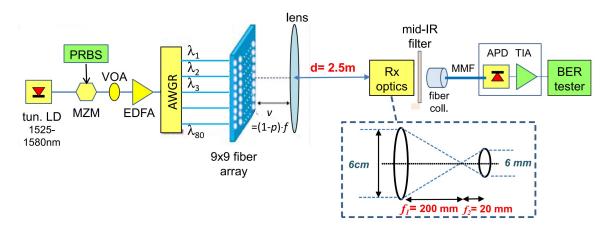

**Chapter 8** experimentally demonstrates the first polar coded modulation based infrared light communication system. A Monte Carlo method is proposed to jointly design an inter-frame related polar code with 16-ary quadrature-amplitude modulation (16-QAM) and orthogonal frequency-division multiplexing (OFDM). The indoor transmission of 9.6 Gbit/s 16-QAM OFDM signal is experimentally achieved over a 3.2 km single-mode fiber and 0.8 m free space with no errors over 10<sup>7</sup> bits.

Finally, **Chapter 9** summarizes the main contributions of this thesis. The possible areas for improvements and the potentially interesting open problems for future research are also discussed.

# A REVIEW OF POLAR CODES

# 2.1 The theory of channel coding

In real-world communication systems, the sent data will be corrupted by the noisy and dispersive channel. To recover the original data, an efficient way is to add redundant bits in the data before transmission, which is called channel coding [110]. The fraction of information bits to all transmitted bits is defined as the code rate of channel coding. A good channel coding scheme has a high code rate (as close as possible to 1) and low probability of error. Two important questions that follow are: First, the maximum code rate at which information bits can be transmitted reliably over a noisy channel. Second, a practical channel coding scheme which can achieve the maximum code rate. The remaining part of this chapter will address these two questions.

### 2.1.1 Channel model and capacity

Consider a channel W with input alphabet  $\mathcal{X}$  and output alphabet  $\mathcal{Y}$ , a transition probability function W(y|x),  $x \in \mathcal{X}$ ,  $y \in \mathcal{Y}$  is used to model channel W mathematically. W(y|x) is defined as the probability of observing y when x is sent. Throughout the thesis, we will focus on discrete memoryless channels (DMCs), defined as follows.

**Definition 2.1.1.** In a discrete memoryless channel (DMC), denoted by  $W: \mathcal{X} \to \mathcal{Y}, \mathcal{X}$  and  $\mathcal{Y}$  are two finite sets, i.e.  $|\mathcal{X}|$ ,  $|\mathcal{Y}| < \infty$ . The output  $y_k \in \mathcal{Y}$  at time k only depends on the input  $x_k \in \mathcal{X}$  at time k and not on the behaviour of the channel in the past time slots, i.e. let  $x_j^i$  denote  $\{x_j, \dots, x_i\}$ , the probability of observing  $y_k$  when  $x_1^k$  is sent and  $y_1^{k-1}$  is observed is

$$W(y_k|x_1^k, y_1^{k-1}) = W(y_k|x_k), \ \forall k \in \{1, 2, \dots\}.$$

(2.1)

Note that if a DMC is used without feedback, there is

$$W\left(y_1^k|x_1^k\right) = \prod_{i=1}^k W\left(y_i|x_i\right), \ \forall k \in \{1, 2, \dots\}.$$

(2.2)

If the input alphabet  $\mathcal{X}$  is always  $\{0,1\}$ , the DMC is denoted as a binary-input discrete memoryless channel (B-DMC). A B-DMC is said to be symmetric if there exists a permutation  $\pi$  of the output alphabet  $\mathcal{Y}$  such that 1)  $\pi^{-1} = \pi$ . and 2)

$p(y|1) = p(\pi(y)|0)$ . Throughout this thesis, symmetric B-DMCs are used without feedback.

Before introducing the channel capacity, we first explain three fundamental concepts: entropy, conditional entropy and mutual information.

a) Entropy: The entropy of a random variable  $X \sim p(x)$  is defined as

$$H(X) = -\sum_{x \in \mathcal{X}} p(x) \log_2 p(x), \qquad (2.3)$$

where p(x),  $x \in \mathcal{X}$  is the probability distribution function of X. This is a measure of the uncertainty in X.

b) Conditional entropy: The conditional of a random variable X given another random variable Y, where  $(X,Y) \sim p(x,y)$ ,  $x \in \mathcal{X}$ ,  $y \in \mathcal{Y}$  is defined as

$$H(X|Y) = \sum_{y \in \mathcal{Y}} p(y) \log_2 H(X|Y = y) = -\sum_{y \in \mathcal{Y}} p(y) \sum_{x \in \mathcal{X}} p(x|y) \log_2 p(x|y). \quad (2.4)$$

This is a measure of the uncertainty in *X* conditioned on knowing *Y*.

c) Mutual information: The mutual information between two random variables  $(X,Y) \sim p(x,y)$ ,  $x \in \mathcal{X}$ ,  $y \in \mathcal{Y}$  is defined as

$$I(X;Y) = H(X) - H(X|Y) = \sum_{x \in \mathcal{X}, y \in \mathcal{Y}} p(x,y) \log_2 \frac{p(x,y)}{p(x) p(y)}.$$

(2.5)

This is a measure of the amount of information about X revealed by the knowledge of Y.

**Definition 2.1.2.** *The mutual information* I(X;Y) *of a DMC*  $W: \mathcal{X} \to \mathcal{Y}$  *and input distribution* p(x) *is defined as*

$$I(X;Y) = \sum_{x \in \mathcal{X}} \sum_{y \in \mathcal{Y}} p(x) W(y|x) \log_2 \frac{W(y|x)}{\sum_{x' \in \mathcal{X}} W(y|x') p(x')}.$$

(2.6)

Based on the above concepts, the channel capacity is defined as follows.

**Definition 2.1.3.** *The channel capacity of a DMC W* :  $\mathcal{X} \to \mathcal{Y}$  *is defined as*

$$C = \max_{p(x)} I(X;Y), \qquad (2.7)$$

where the maximum is over the set of all input probability distribution p(x).

As we will see below, the channel capacity plays a fundamental role in channel coding.

### 2.1.2 Channel coding

Unless the channel has no noise and dispersion, the data transmitted over the channel may be corrupted. To cope with the possible error incurred during transmission, channel coding is an effective solution. We first give the definition related to channel codes.

**Definition 2.1.4.** An (N, M) code for a discrete memoryless channel with input alphabet  $\mathcal{X}$  and output alphabet  $\mathcal{Y}$  is defined by an encoding function

$$f: \{1, 2, \cdots, M\} \to \mathcal{X}^N, \tag{2.8}$$

and a decoding function

$$g: \mathcal{Y}^N \to \{1, 2, \cdots, M\}, \tag{2.9}$$

where N is the block length of the codeword.  $\mathcal{M} = \{1, 2, \dots, M\}$  is the message set.  $f(1), f(2), \dots, f(M)$  are the codewords. The set of all codewords forms the codebook.

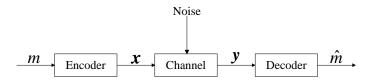

Figure 2.1 The communication system with channel coding.

In Figure 2.1, message m is randomly chosen from the message set  $\mathcal{M}$ . Thus,  $x_1^N = f(m)$  and the estimate  $\widehat{m} = g(y_1^N)$ .

**Definition 2.1.5.** *For all*  $1 \le m \le M$ *, let*

$$\lambda_m = W\left\{g\left(y_1^N\right) \neq m | x_1^N = f\left(m\right)\right\} \tag{2.10}$$

be the conditional probability of error given that the message is m.

**Definition 2.1.6.** The maximal probability of error of an (N, M) code is defined as

$$\lambda_{max} = \max_{m} \lambda_{m}. \tag{2.11}$$

**Definition 2.1.7.** The average probability of error of an (N, M) code is defined as

$$P_{e} = \frac{1}{M} \sum_{m \in M} W\left(g\left(y_{1}^{N}\right) \neq m | x_{1}^{N} = f\left(m\right)\right) = \frac{1}{M} \sum_{m=1}^{M} \lambda_{m}.$$

(2.12)

18 2.2 Polar Codes

Therefore,

$$P_e \le \max_{m} \lambda_m = \lambda_{\max}. \tag{2.13}$$

**Definition 2.1.8.** *The rate of an* (N, M) *channel code is defined as*

$$R = \frac{\log_2 M}{N} \text{ bits per transmission,}$$

(2.14)

*R* is the ratio between how many bits of message are transmitted and how many bits are used for encoding.

**Definition 2.1.9.** A code rate R is achievable for a discrete memoryless channel if, for all n, there exists an (N, M) code with  $M = 2^{NR}$  such that  $\lambda_{max} \xrightarrow{N \to \infty} 0$ .

The operational capacity of a channel is the supremum over all achievable rates for the channel. In the landmark work [26], Shannon proved the noisy channel coding theorem which shows that the operational capacity is equal to the channel capacity for any discrete memoryless channel.

**Theorem 2.1.1.** For any DMC, if  $R \le C$ , then R is achievable. Conversely, if R > C, it is not achievable.

The proof of achievability in the first part is in two steps. It first shows the existence of a sequence of codes that can transmit  $M=2^{NR+1}$  messages (rate  $R+\frac{1}{N}$ ) where the average probability of error  $P_e$  goes to zero. Then, by removing the  $\frac{M}{2}$  messages with the worst probabilities of error, it constructs a new sequence of codes that transmit  $\frac{M}{2}=2^{NR}$  messages (rate R) where the maximal probability of error  $\lambda_{max}$  goes to zero. For the converse part, the proof shows that, for an arbitrary sequence of codes with rate R>C,  $P_e$  does not converge to 0. Since  $\lambda_{max}>P_e$ , it also does not converge to 0. Therefore, the rate R is not achievable in this case.

The channel coding theorem proves the existence of codes that enables the information transmission at rates below capacity with an arbitrary small probability of error if the code length is large enough. However, the random codes used by Shannon are not practical. Hence, from the day this theorem was published, the search for the optimal and practical codes has been ongoing.

### 2.2 Polar Codes

Polar codes are channel codes proposed by Arıkan in 2008 [36]. They are designed on the basis of the channel polarization phenomenon and are the first provable

capacity-achieving channel codes with affordable encoding/decoding complexity. This section will illustrate the theory of channel polarization first, followed by the construction of polar codes and finally the encoding and decoding schemes of polar codes.

### 2.2.1 Channel polarization

We write  $W: \mathcal{X} \to \mathcal{Y}$  to denote a B-DMC with transition probabilities W(y|x),  $x \in \mathcal{X}$ ,  $y \in \mathcal{Y}$  and  $\mathcal{X} \in \{0,1\}$ . When using the input letters in  $\mathcal{X}$  with equal probability, the mutual information expression in (2.6) can be reshaped as follows

$$I(W) = \sum_{x \in \mathcal{X}} \sum_{y \in \mathcal{Y}} \frac{1}{2} W(y|x) \log_2 \frac{W(y|x)}{\frac{1}{2} W(y|0) + \frac{1}{2} W(y|1)},$$

(2.15)

$I\left(W\right)$  is defined as the symmetric capacity. When W is a symmetric channel,  $I\left(W\right)$  is the highest rate at which reliable communication is possible across W, that is, it equals the Shannon capacity.

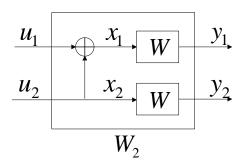

Figure 2.2 The channel  $W_2$ .

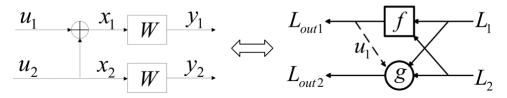

The operation of channel polarization is called channel transformation consisting of a channel combining phase and a channel splitting phase. Figure 2.2 shows the first level of the channel transformation. Two independent copies of W are combined and channel  $W_2: \mathcal{X}^2 \to \mathcal{Y}^2$  is obtained with the transition probabilities.

$$W_2(y_1, y_2|u_1, u_2) = W(y_1|u_1 \oplus u_2) W(y_2|u_2). \tag{2.16}$$

$W_2$  is then split into two synthesized subchannels  $W_2^{(1)}$  and  $W_2^{(2)}$  as below.

$$W_2^{(1)}\left(y_1^2|u_1\right) = \sum_{u_2 \in \mathcal{X}} \frac{1}{2} W_2\left(y_1^2|u_1^2\right) = \sum_{u_2 \in \mathcal{X}} \frac{1}{2} W\left(y_1|u_1 \oplus u_2\right) W\left(y_2|u_2\right). \tag{2.17}$$

2.2 Polar Codes

$$W_2^{(2)}\left(y_1^2, u_1|u_2\right) = \frac{1}{2}W_2\left(y_1^2|u_1^2\right) = \frac{1}{2}W\left(y_1|u_1 \oplus u_2\right)W\left(y_2|u_2\right). \tag{2.18}$$

$W_2^{(1)}$  can be viewed as a synthesized channel with input  $u_1$  and output  $y_1^2$ .  $W_2^{(2)}$  can be viewed as a synthesized channel with input  $u_2$  and output  $y_1^2$ ,  $u_1$ . The symmetric capacities of the channels before and after channel transformation have the following relationships.

**Theorem 2.2.1.** *Suppose*  $(W, W) \mapsto (W_2^{(1)}, W_2^{(2)})$ , *then*

$$I(W_2^{(1)}) + I(W_2^{(2)}) = 2I(W),$$

(2.19)

$$I(W_2^{(1)}) \le I(W) \le I(W_2^{(2)}).$$

(2.20)

This theorem [36] shows: after a single step of channel transformation, W is transformed into  $W_2^{(1)}$  and  $W_2^{(2)}$ , which are still B-DMCs. The symmetric capacity of  $W_2^{(1)}$  and  $W_2^{(2)}$  decreases and increases with respect to I(W), respectively. But their sum remains unchanged, that is, 2I(W).

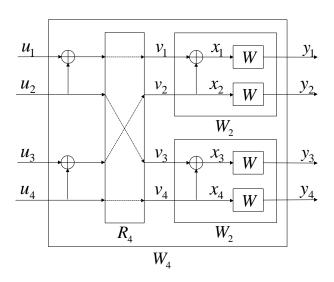

Figure 2.3 The channel  $W_4$  and its relation to  $W_2$  and W.

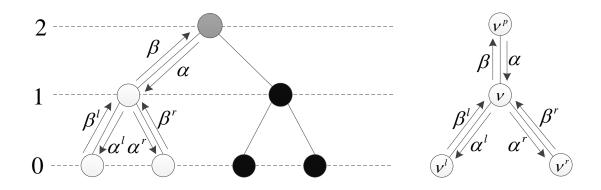

Since  $W_2^{(1)}$  and  $W_2^{(2)}$  are still B-DMCs, another step of channel transformation can be performed on  $W_2^{(1)}$  and  $W_2^{(2)}$ , respectively. Figure 2.3 shows the two-level channel transformation of four channel W, which executes  $\left(W_2^{(1)},W_2^{(1)}\right)\mapsto \left(W_4^{(1)},W_4^{(2)}\right)$  and  $\left(W_2^{(2)},W_2^{(2)}\right)\mapsto \left(W_4^{(3)},W_4^{(4)}\right)$ . Like this, if the one step channel transformation

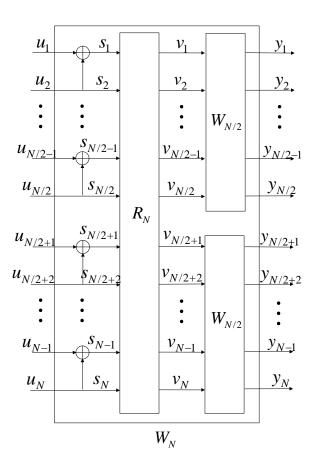

is performed recursively on  $N=2^n$  channel W, the recursive structure is shown in Figure 2.4, where permutation  $R_N$  carries out the operation  $v_1^N=R_N\cdot s_1^N=(s_1,s_3,\cdots,s_{N-1},s_2,s_4,\cdots,s_N)$ . The mapping between  $u_1^N$  and  $x_1^N$  is

$$x_1^N = u_1^N G_N, (2.21)$$

where  $G_N = B_N F^{\otimes n}$ .  $F = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$  and  $n = \log_2 N$ .  $F^{\otimes n}$  denotes the n-th Kronecker power of F.  $B_N$  is a bit-reversal permutation matrix, which can be calculated recursively by  $B_N = R_N \left( I_2 \otimes B_{N/2} \right)$  and  $B_2 = I_2$ .

Figure 2.4 Recursive construction of  $W_N$  from two copies of  $W_{N/2}$ .

N synthetic channel  $W_N^{(i)}$ ,  $i=1,2,\cdots,N$  can be obtained after channel transformation, with transition probabilities

$$W_N^{(i)}\left(y_1^N, u_1^{i-1}|u_i\right) = \sum_{u_{i+1}^N \in \mathcal{X}^{N-i}} \frac{1}{2^{N-1}} W_N\left(y_1^N|u_1^N\right),\tag{2.22}$$

where

2.2 Polar Codes

$$W_N(y_1^N|u_1^N) = \prod_{i=1}^N W(y_i|x_i).$$

(2.23)

These transition probabilities can be calculated recursively according to the recursive structure in Figure 2.4 as below.

$$W_{2N}^{(2i-1)}\left(y_{1}^{2N}, u_{1}^{2i-2} | u_{2i-1}\right) = \sum_{u_{2i}} \frac{1}{2} W_{N}^{(i)}\left(y_{1}^{N}, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2} | u_{2i-1} \oplus u_{2i}\right) \cdot W_{N}^{(i)}\left(y_{N+1}^{2N}, u_{1,e}^{2i-2} | u_{2i}\right),$$

$$(2.24)$$

$$W_{2N}^{(2i)}\left(y_{1}^{2N}, u_{1}^{2i-1}|u_{2i}\right) = \frac{1}{2}W_{N}^{(i)}\left(y_{1}^{N}, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2}|u_{2i-1} \oplus u_{2i}\right) \cdot W_{N}^{(i)}\left(y_{N+1}^{2N}, u_{1,e}^{2i-2}|u_{2i}\right), \quad (2.25)$$

where  $a_{1,e}^j$  ( $a_{1,o}^j$ ) denote the subvector with even (odd) indices ( $a_k$ :  $1 \le k \le j$ ; k even (odd)). After getting the transition probability of each synthetic channel, the symmetric capacity  $I\left(W_N^{(i)}\right)$  can be computed according to (2.15). The channel polarization theorem is then given in [36] as follows:

**Theorem 2.2.2.** For any B-DMC W, the channels  $\left\{W_N^{(i)}\right\}$  polarize in the sense that, for any fixed  $\delta \in (0,1)$ , as N goes to infinity through powers of two, the fraction of indices  $i \in \{1,\ldots,N\}$  for which  $I\left(W_N^{(i)}\right) \in (1-\delta,1]$  goes to  $I\left(W\right)$  and the fraction for which  $I\left(W_N^{(i)}\right) \in [0,\delta)$  goes to  $1-I\left(W\right)$ .

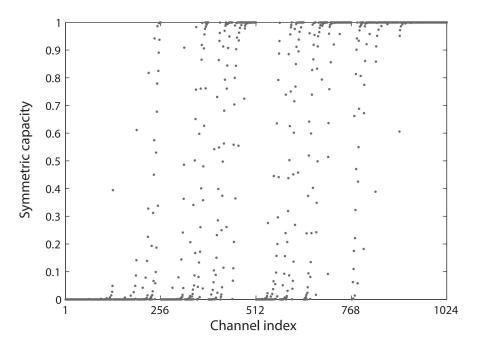

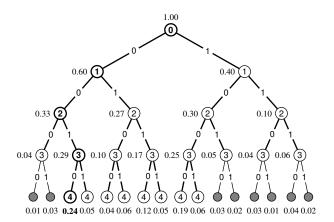

An example of the polarization effect for the case W is a binary erasure channel (BEC) with erasure probability  $\epsilon=0.5$  is shown in Figure 2.5. A B-DMC W is called a BEC if for each  $y\in\mathcal{Y}$ , either  $W\left(y|0\right)W\left(y|1\right)=0$  or  $W\left(y|0\right)=W\left(y|1\right)$ . In the latter case, y is said to be an erasure symbol. The sum of  $W\left(y|0\right)$  over all erasure symbols y is called the erasure probability  $\epsilon$  of the BEC. Note that  $I\left(W_N^{(i)}\right)$  can be calculated using the recursive relations which only valid for BECs.

$$I\left(W_{1}^{(1)}\right) = 1 - \epsilon,$$

$$I\left(W_{N}^{(2i-1)}\right) = I\left(W_{N/2}^{(i)}\right)^{2},$$

$$I\left(W_{N}^{(2i)}\right) = 2I\left(W_{N/2}^{(i)}\right) - I\left(W_{N/2}^{(i)}\right)^{2}.$$

(2.26)

Figure 2.5 Plot of  $I(W_N^{(i)})$  versus  $i = 1, ..., N = 2^{10}$  for a BEC with  $\epsilon = 0.5$ .

In Figure 2.5,  $I\left(W_N^{(i)}\right)$  is close to 0 for small i and close to 1 for large i. When  $N \to \infty$ , the fraction of indices i with  $I\left(W_N^{(i)}\right) = 0$  goes to  $1 - I\left(W\right) = \epsilon = 0.5$  and the fraction of indices i with  $I\left(W_N^{(i)}\right) = 1$  goes to  $I\left(W\right) = 1 - \epsilon = 0.5$ . We can intuitively think of using synthetic channel i with  $I\left(W_N^{(i)}\right)$  near 1 to transmit information data. This properly can be exploited to achieve reliable transmission. However, we should first find out how to determine the subset of indices i corresponding to synthetic channels with high reliability, which is an important computational problem whose solution will be given in the following subsection.

#### 2.2.2 Polar codes construction

In [36], the Bhattacharyya parameter is used to estimate the reliability of polarization channel. Given a B-DMC  $W: \mathcal{X} \to \mathcal{Y}$ , the Bhattacharyya parameter is defined as

$$Z(W) = \sum_{y \in \mathcal{Y}} \sqrt{W(y|0) W(y|1)}.$$

(2.27)

It is an upper bound on the probability of maximum-likelihood (ML) decision error when W is used only once to transmit a 0 or 1. The relationship between  $Z\left(W\right)$  and  $I\left(W\right)$  is shown in the proposition below.

2.2 Polar Codes

**Proposition 2.2.1.** For any B-DMC W, we have

$$I(W) \ge \log \frac{2}{1 + Z(W)},$$

$$I(W) \le \sqrt{1 - Z(W)^{2}}.$$

(2.28)

It is easy to see that I(W) = 1 iff Z(W) = 0, and I(W) = 0 iff Z(W) = 1. The Bhattacharyya parameter of the synthetic channels satisfy

$$Z\left(W_{2N}^{(2i-1)}\right) \le 2Z\left(W_{N}^{(i)}\right) - Z\left(W_{N}^{(i)}\right)^{2},$$

(2.29)

$$Z\left(W_{2N}^{(2i)}\right) = Z\left(W_N^{(i)}\right)^2,\tag{2.30}$$

with equality in (2.29) iff W is a BEC. With the help of (2.29) and (2.30), we can derive the below theorem.

**Theorem 2.2.3.** For any B-DMC W with I(W) > 0, and any fixed R < I(W), there exists a sequence of sets  $\mathbb{A}_N \subset \{1, \ldots, N\}$ ,  $N \in \{1, 2, \ldots, 2^n, \ldots\}$ , such that  $|\mathbb{A}_N| \ge NR$  and  $Z(W_N^{(i)}) \le O(N^{-5/4})$  for all  $i \in \mathbb{A}_N$ .

Theorem 4 inspires us to choose these synthetic channel with lower  $Z\left(W_N^{(i)}\right)$  to convey information. This idea leads to the definition of polar codes.

**Polar Codes**: Given a B-DMC W,  $u_1^N$  is the source block and it is encoded in the manner

$$x_1^N = u_1^N G_N, (2.31)$$

where  $G_N$  is the generator matrix of order N, defined above.  $u_i, i \in \mathbb{A}$  carry information bits and the rest are set to any fixed values. The information set  $\mathbb{A}$  is chosen as a K-element subset of  $\{1, \ldots, N\}$  such that  $Z\left(W_N^{(i)}\right) \leq Z\left(W_N^{(j)}\right)$  for all  $i \in \mathbb{A}$ ,  $j \in \mathbb{A}^c$ . Then we can obtain a mapping from source blocks  $u_{\mathbb{A}}$  to codeword blocks  $x_1^N$ . This mapping is called a polar code for W.

The following theorem shows that the polar codes achieve the symmetric capacity of any given B-DMC *W* under successive cancellation decoding. The details of successive cancellation decoding will be introduced in the next subsection.

**Theorem 2.2.4.** For any given B-DMC W and fixed R < I(W), block error probability for polar coding under successive cancellation decoding satisfies

$$P_e(N,R) = O(N^{-\frac{1}{4}}),$$

(2.32)

this also means that polar codes are Shannon capacity achieving if W is symmetric.

To get the information set  $\mathbb{A}$ , if B-DMC W is a BEC, the Bhattacharyya parameters of the polarized channels can be tracked by using the recursive calculation

in (2.29) and (2.30) with  $Z\left(W_1^{(1)}\right) = \epsilon$ . However, for channels other than BEC, the computational complexity grows exponentially with the code length and input alphabet size. To construct a polar code over an arbitrary symmetric B-DMC, Mori and Tanaka proposed the use of DE methods [77]. It is widely used in LDPC codes for tracing the PDF of LLRs at the variable and check nodes in the decoding graph, and is equally applicable to the polar codes design. Based on the calculated LLR PDFs, the error probabilities of all the polarized channels can be obtained. In practical implementation, the LLR PDFs should be quantized into q levels to keep an acceptable computational complexity. However, a typical value of q is  $10^5$ , thus causing a huge computational burden.

Tal and Vardy proposed an effective method to reduce computational complexity through appropriate approximation [78]. Two approximation methods, called upgrading and degrading quantization are introduced to transform the relevant channel into a new one with a smaller output alphabet. They give lower and upper bounds on  $Z\left(W_N^{(i)}\right)$  of polarized channel. The two bounds are found to be very close through analysis and numerical simulation, thus can be used as approximations of  $Z\left(W_N^{(i)}\right)$ . In this way, the construction complexity can be reduced dramatically compared to DE.

For binary input AWGN channels, an alternative method called GA can be applied in the construction of polar codes [79]. The GA has lower complexity than Tal and Vardy's method but yields almost the same precision when applied to binary input AWGN channels. It is a more attractive choice than other methods since AWGN channel is typically considered by coding theorists.

## 2.2.3 Polar encoding and decoding

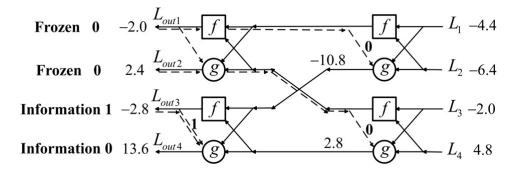

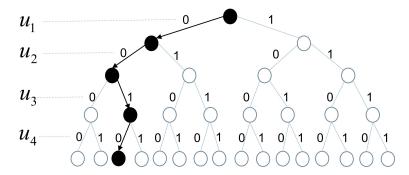

Figure 2.6 An example of polar encoding.