# A 0.20 mm<sup>2</sup> 3 nW signal acquisition IC for miniature sensor nodes in 65 nm CMOS

Citation for published version (APA):

Harpe, P. J. A., Gao, H., van Dommele, A. R., Cantatore, E., & van Roermund, A. H. M. (2016). A 0.20 mm<sup>2</sup> 3 nW signal acquisition IC for miniature sensor nodes in 65 nm CMOS. *IEEE Journal of Solid-State Circuits*, *51*(1), 240-248. https://doi.org/10.1109/JSSC.2015.2487270

Document license:

**TAVERNE**

DOI:

10.1109/JSSC.2015.2487270

Document status and date:

Published: 01/01/2016

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

# A 0.20 mm<sup>2</sup> 3 nW Signal Acquisition IC for Miniature Sensor Nodes in 65 nm CMOS

Pieter Harpe, Senior Member, IEEE, Hao Gao, Rainier van Dommele, Eugenio Cantatore, Senior Member, IEEE, and Arthur H. M. van Roermund, Senior Member, IEEE

Abstract—Miniature mm<sup>3</sup>-sized sensor nodes have a very tight power budget, in particular, when a long operational lifetime is required, which is the case, e.g., for implantable devices or unobtrusive IoT nodes. This paper presents a fully integrated signal acquisition IC for these emerging applications. It integrates an amplifier with 32 dB gain and 370 Hz bandwidth that includes positive feedback to enhance input impedance and dc offset compensation. The IC includes also a 10 bit 1 kS/s SAR ADC as well as a clock generator and voltage and current biasing circuits. The overall system achieves an input noise of 27 µV<sub>rms</sub>, consumes 3 nW from a 0.6 V supply, occupies 0.20 mm<sup>2</sup> in 65 nm CMOS, and has a single-wire data interface. The amplifier achieves an noiseefficiency factor (NEF) of 2.1 and the ADC has a figure-of-merit (FoM) of 1.5 f.J/conversion-step. Measurements confirm reliable operation for supplies from 0.50 to 0.70 V and temperatures in the range of 0–85  $^{\circ}$  C. As an application example, an ECG recording is successfully performed with the system while a 0.69 mm<sup>2</sup> photodiode array provides its power supply in indoor lighting conditions.

*Index Terms*—ADC, amplifier, analog front-end, CMOS, ECG, sensor, signal acquisition.

# I. INTRODUCTION

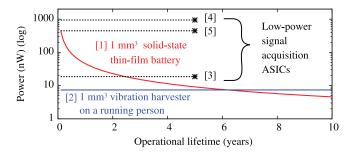

C IGNAL acquisition systems for emerging applications, such as implantable or unobtrusively wearable autonomous sensors, large sensor arrays, or wireless selfpowered sensors, require a minuscule form factor and sufficient operational lifetime. For instance, in case of implantable electronics, a lifetime of several years is demanded, while the smallest possible form factor will allow to reach more locations in the human body. The small size and weight inherently imply that the amount of energy available to supply the system will be limited. Thus, in order to achieve sufficient operational lifetime, the average power consumption has to be very low. Fig. 1 shows a few state-of-the-art examples of energy sources, when scaled to a size of 1 mm<sup>3</sup>. As can be seen, the power available from a state-of-the-art 1 mm<sup>3</sup> solid-state thin-film battery is limited to 4 nW for a 10 year lifetime [1], and a 1 mm<sup>3</sup> energy harvester attached to a running person delivers

Manuscript received April 30, 2015; revised September 01, 2015; accepted September 30, 2015. Date of publication October 26, 2015; date of current version December 30, 2015. This paper was approved by Guest Editor Jan Genoe. This work was supported by the Dutch Technology Foundation STW.

The authors are with the Mixed-Signal Microelectronics Group, Eindhoven University of Technology, P.O. Box 513, 5600MB Eindhoven, The Netherlands (e-mail: p.j.a.harpe@tue.nl).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2015.2487270

only 7.4 nW [2]. In other words, the power consumption budget for a multiyear operational lifetime is in the order of 1–10 nW/mm<sup>3</sup>. One of the critical tasks in these miniature systems is signal acquisition: signal conditioning and digitization of information from sensors. However, low-power signal acquisition systems that are presently available, for instance, as proposed in [3]–[5], have a power consumption that is still in the 20– 1000 nW range as shown in Fig. 1. Furthermore, the required circuits do not only need a low absolute power (within a 1–10 nW budget), they also need to maintain high power efficiency, i.e., deliver high performance given their power consumption. This is nontrivial, as the impact of fixed power dissipators such as biasing networks, clock generation, and leakage currents will start to become more pronounced at such low-power consumption levels. One approach to overcome this issue is to use more simplistic circuitry, for instance, by simplifying biasing networks or common-mode feedback (CMFB) networks. However, such an approach could lead to higher PVT sensitivity and lower reliability, as will be detailed later in Section III.

This work, which is an extended version of [6], presents a fully integrated signal acquisition IC including an amplifier and ADC, as well as voltage and current biasing and clock generation circuits. As a proof of concept, it shows that a low absolute power, a high power efficiency, and a PVT-robust design can be achieved at the same time. With 3 nW power consumption and state-of-the-art power efficiency, it can still ensure enough circuit reliability, precision, and bandwidth to enable practical applications.

This paper is organized as follows. Section II describes the design and optimization of the overall signal acquisition system, Section III presents the circuit-level implementations, followed by measurement results in Section IV. Finally, conclusions are drawn in Section V.

# II. SYSTEM DESIGN AND OPTIMIZATION

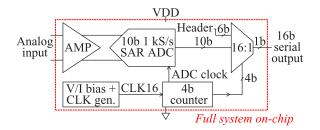

Fig. 2 presents the implemented system, which requires only a single supply voltage, has five external connections and no external components. It contains a differential amplifier, an SAR ADC, a serial data interface, a clock generator, and voltage and current biasing circuits. A reduced supply voltage is used to save power. Theoretically, more power can be saved at lower supply levels, but this comes at the cost of losing dynamic range, speed, and robustness. As a compromise, a nominal supply of 0.6 V was selected as it allows to use relatively conventional circuit implementations, provides sufficient performance and robustness, and also saves substantial power.

Fig. 1. State-of-the-art energy sources and signal acquisition ICs.

Fig. 2. Fully integrated signal acquisition system.

Typically, signal acquisition systems are optimized for a particular application. In this case, due to the very scarce energy resources that are available in an mm<sup>3</sup>-sized node, a feasibility calculation is performed first to investigate the potential performance given a power budget of 3 nW. First of all, considering that the amplifier and ADC are the most critical blocks, 1 nW is assigned to each of these circuits, leaving 1 nW for the remaining auxiliary circuits. Next, the dynamic range of the system is determined, which is related to the effective resolution or ENOB of the ADC. A higher dynamic range is desirable as it allows a better signal-to-noise-ratio (SNR), it can tolerate larger signal-strength variations, and it can tolerate larger interference signals such as motion artifacts without saturating the system. Typical low-power signal acquisition systems [3]–[5], [7] use ADCs with a resolution of 8, 9, 10, or 12 bit, while achieving an ENOB from 7.1 to 10.2 bit. To be in line with these existing systems, a 10 bit ADC with an expected ENOB of 9 bit is selected in this work. The noise of this ADC is determined by the quantization noise as well as the thermal noise of the circuitry. The quantization noise, equal to  $0.289V_{\rm LSB}$ , can be estimated as  $280~\mu V_{\rm rms}$  for this 10 bit ADC, assuming a differential full-scale range  $V_{\rm FS,ADC}$  of 1  $V_{\rm pp}$ . Including some budget for thermal noise, the total ADC noise is coarsely estimated as  $V_{n,ADC} = 400 \, \mu V_{rms}$ . Next, using a well-known figure-of-merit (FoM) for ADCs, the achievable performance can be predicted. The following FoM is used [8]:

$$FoM = \frac{P}{2^{ENOB} \cdot \min(f_s, 2ERBW)}$$

(1)

where P is the power consumption, ENOB is the effectivenumber-of-bits,  $f_s$  is the sample rate, and ERBW is the effective resolution bandwidth of the ADC. A survey of state-of-the-art ADCs [9] reveals that 10 bit ADCs can nowadays achieve an FoM in the order of 2 fJ/conversion-step. As the ERBW is not a limiting factor in this low-speed application, and an ENOB of 9 bit is required, this implies that a sample rate of 1 kS/s should be achievable within the 1 nW budget.

As a next step, the parameters of the amplifier are optimized. Considering that the ADC's sampling rate is set to 1 kS/s, it is logical to set the amplifier's bandwidth to a value slightly lower than the Nyquist frequency of  $\frac{1}{2}f_s$ , for instance, 400 Hz. Using the noise-efficiency factor (NEF) defined in [10], the amplifier performance can now be predicted

$$NEF = V_{n,amp} \sqrt{\frac{2 \cdot I_{total}}{\pi \cdot V_t \cdot 4kT \cdot BW}}$$

(2)

where  $V_{n,\rm amp}$  is the total input-referred noise (IRN),  $I_{\rm total}$  is the total current consumption,  $V_t$  is the thermal voltage, and BW is the bandwidth of the amplifier. Existing low-power amplifiers [3]–[5], [11] show that an NEF around 2 is achievable. With a bandwidth of 400 Hz and a current consumption budget of 1.7 nA at 0.6 V supply, this leads to a predicted IRN of  $V_{n,\rm amp}=25~\mu V_{\rm rms}$ .

The final parameter to decide is the gain of the amplifier, which will determine the overall IRN as well as the full-scale input range. The IRN of the system  $(V_{n,\mathrm{sys}})$  can be expressed as a combination of the amplifier noise  $(V_{n,\mathrm{amp}})$ , the ADC noise  $(V_{n,\mathrm{ADC}})$ , and the gain (A) of the amplifier

$$V_{n,\text{sys}}^2 = V_{n,\text{amp}}^2 + \frac{V_{n,\text{ADC}}^2}{A^2}.$$

(3)

At the same time, the peak-to-peak full-scale input range  $V_{\rm FS,in}$  is determined by the ADC's range divided by the amplifier gain

$$V_{\rm FS,in} = \frac{V_{\rm FS,ADC}}{A}.$$

(4)

Thus, on one hand, the gain A needs to be large enough to sufficiently suppress ADC noise (3), but on the other hand, it should be minimized to maximize the full-scale input range (4). As a compromise, the gain is set to  $A=40\times$ , leading to a predicted system with an overall IRN of  $V_{n,\rm sys}=27~\mu\rm V_{rms}$ , an input range  $V_{\rm FS,in}$  of 25 mV  $_{\rm pp}$ , a bandwidth of 400 Hz, and a power consumption of 2 nW for the core components.

As a result of the above analysis and optimization, it is demonstrated that it is feasible to develop a signal acquisition system within the assigned power budget. It should be noted that this system, in particular, in terms of IRN, cannot reach the same absolute level of performance as prior ASICs [3]–[5] due to the power constraints. Nonetheless, the envisioned performance enables extreme miniaturization of sensing nodes and is still sufficient for a variety of applications, such as ECG monitoring, physiological signal acquisition for implantable devices, or monitoring of environmental information.

#### III. CIRCUIT IMPLEMENTATION

Based on the system-level design described in Section II, this section will discuss the circuit-level implementation of the amplifier, the ADC, and the auxiliary circuits.

#### A. Amplifier

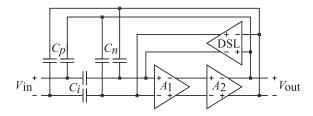

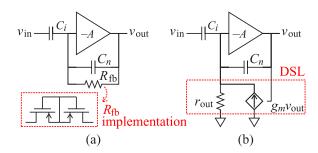

The ac-coupled amplifier is composed of a two-stage amplifier  $(A_1, A_2)$  and a dc servo loop (DSL), as shown in Fig. 3. The

Fig. 3. Overview of the capacitively coupled amplifier.

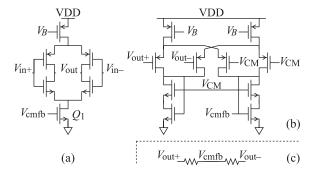

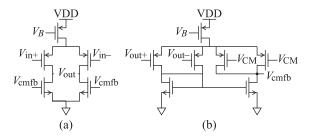

Fig. 4. Implementation of the (a) main amplifiers and their (b) active CMFB. Also shown is an (c) alternative CMFB topology.

capacitor ratio  $C_i/C_n=40~\mathrm{pF}/1~\mathrm{pF}$  sets the differential gain to  $40\times(32~\mathrm{dB})$  while capacitors  $C_p$  are used to increase the input impedance, as will be discussed later in detail. The DSL provides dc biasing to  $A_1$ , limits dc offset, and results in a high-pass corner frequency of the capacitively coupled amplifier. As the ac-coupled amplifier can only process ac information, the dc offsets of the amplifier stages and ADC are not calibrated or compensated. Their values are small enough to have no significant impact on the ac performance. To maintain stability,  $A_1$  is dimensioned for relatively low gain and high bandwidth, while  $A_2$  is dimensioned for high gain and low bandwidth. The latter can be achieved easily thanks to the large capacitive load already present at the second stage output node. In terms of noise, the first stage gain ( $\approx 20\times$ ) can still sufficiently suppress the noise of the second stage.

The transistor-level implementation of amplifiers  $A_1$  and  $A_2$ is shown in Fig. 4(a). Both amplifiers use the same topology but with different parameters. For best power efficiency, the input transistors are biased in weak inversion, and an inverter-based input pair is applied to double the  $g_m$ . Based on noise requirements, the bias current for  $A_1$  is set to 1 nA, while  $A_2$  uses 0.2 nA. This biasing current is determined by voltage  $V_B$ , which is set by a bias current  $I_{\text{amp}}$  (discussed in Section III-C) through current mirrors. As the amplifiers are differential, a CMFB is required. Either a passive or an active CMFB could be adopted. As a first solution, a simple passive structure is considered. This approach uses two resistors connected in series to the differential output nodes of the inverter-based amplifier [Fig. 4(c)]. The midpoint of these resistors determines the common-mode voltage and can directly drive the gate of the CMFB transistor  $Q_1$ . However, in this structure, the common-mode output voltage is directly related to the threshold voltage and overdrive voltage of  $Q_1$ :  $V_{\rm cm,out} = V_{\rm th} + V_{\rm ov}$ . While this solution

Fig. 5. DC biasing strategies. (a) Passive resistor network. (b) Active feedback.

can work well, it is dependent on PVT variations:  $V_{\rm th}$  can typically shift with more than 100 mV over process and temperature corners, leading to a similar shift in  $V_{\rm cm,out}$ . Considering the supply is only 0.6 V, this leads to a substantial loss of signal range. Further, when the supply voltage is changed,  $V_{\rm cm,out}$  will not track the midsupply level but remains at a fixed level set by  $Q_1$ . As a result, this implies that the output common-mode and hence the output swing reach an optimum for one particular supply only. Because of these drawbacks, this work implements active CMFB circuits as shown in Fig. 4(b), such that the  $V_{\rm cm,out}$  is correctly tuned to a  $V_{\rm CM}$  reference of  $\frac{1}{2}{\rm VDD}$ , irrespective of PVT variations.

The DSL amplifier implements three functions: first, the differential feedback reduces the amplifier's offset. Second, the CMFB of the DSL tunes the DSL's output common-mode voltage to  $\frac{1}{2}$ VDD. As this voltage is directly applied to the input of  $A_1$ , it thus indirectly provides biasing to the input pair of  $A_1$ . Third, the DSL sets the high-pass corner of the amplifier. Instead of using an active DSL, a passive circuit using only resistors could be used as well to implement exactly the same functionality; both these alternatives are shown in Fig. 5. As large resistor values are required in the passive solution [Fig. 5(a)], pseudoresistors using transistors are typically employed. In the active DSL solution [Fig. 5(b)], the DSL amplifier is modeled using a transconductance  $g_m$  and output resistance  $r_{\text{out}}$ . In the first case, the pole frequency is given by  $f_{\rm hp}=\frac{1}{2\pi R_{\rm fb}C_n}$ . As  $R_{\rm fb}$  is implemented with a pseudoresistor, its value can shift substantially over PVT variations (about 100× over a 0-85 °C temperature range according to simulations). This implies that the cutoff frequency cannot be defined accurately. Moreover, in case, the resistance is too large, it can lead to a substantial shift of the bias point of the amplifier due to voltage drop caused by gate leakage of the input pair of  $A_1$ . Because of the variability of the passive solution, this work proposes to use a DSL instead [Fig. 5(b)]. Now, the pole frequency is given by  $f_{\rm hp}=\frac{g_m}{2\pi C_n}.$  In weak inversion,  $g_m=\eta\frac{q}{kT}\cdot I_D$  is also temperature dependent but will show much less variation  $(\sim 25\%)$  than a pseudoresistor (100×). Moreover, the bias current scheme generating  $I_D$  can be designed to counteract the temperature coefficient of  $g_m$ . As the DSL provides more robust performance, this solution was adopted in this work. The actual DSL implementation is shown in Fig. 6(a), with its CMFB in Fig. 6(b). The most important challenge in the DSL design is to minimize its  $g_m$  to enable a low-frequency cutoff point. To do so, the amplifier does not use inverter-based inputs but uses a normal differential pair. Further, the bias current is tuned down

Fig. 6. Implementation of the (a) DSL amplifier and its (b) CMFB circuit.

to less than 2 pA and transistor lengths are increased to  $40 \mu m$ . The simulated  $g_m$  equals 20 pA/V, yielding an estimated  $f_{\rm hp}$  of 3 Hz.

Capacitors  $C_p$  (1 pF) create a positive feedback loop to increase the input impedance (Fig. 3). In the pass-band of the amplifier, the input will see  $C_i$  as well as  $C_p$  (assuming a singleended view for simplicity). The voltage across  $C_i$  is equal to the input voltage  $v_{\rm in}$ , as the input of  $A_1$  is a virtual ground. The voltage across  $C_p$  is equal to  $v_{\rm in}-v_{\rm out}=-39~v_{\rm in}.$  Thus, the effective input capacitance seen by the input is 40 - 39 = 1pF, rather than the 40 pF without positive feedback applied. At the lower and higher end of the amplifier's bandwidth, the impedance will gradually change due to impact from the DSL or from the reduced amplifier gain. For near-dc signals (below the cutoff frequency of the DSL),  $v_{\rm out}/v_{\rm in}$  approximates 0, and hence the input capacitance increases to  $C_i + C_p = 41$  pF. Above the amplifier's bandwidth, the open-loop gain will go to zero, resulting in a floating node at the input of  $A_1$  and  $v_{\rm out}/v_{\rm in}=0$  V. In this case, the input impedance is the series of  $C_i$  and  $C_n$ , in parallel to  $C_p$ , which is approximately 2 pF.

# B. ADC

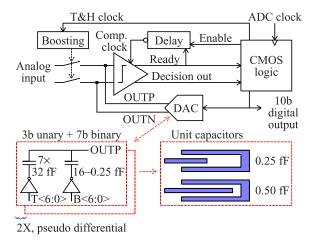

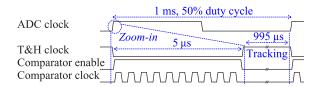

A low-power 10 bit 1 kS/s SAR ADC (Fig. 7) is implemented in this work. The differential analog input is first sampled on the top plates (nodes OUTP and OUTN) of the capacitor arrays that also implement the DAC functionality. During successive approximation, the DAC capacitively subtracts a voltage from the sampled voltage by means of charge redistribution, as in [12]. Therefore, the outputs OUTP and OUTN represent the difference between the sampled input voltage and the DACinduced voltage. This output signal is thus forwarded to the comparator to close the SAR loop. To avoid the need of an oversampled clock, a self-synchronized architecture is used, meaning that a single rising edge on the external 1 kHz ADC clock is sufficient to perform an AD conversion. Internal synchronization of the various SAR operations is achieved by creating a clock locally using an oscillation loop formed by the comparator and a delay element [13], [14]. On the rising edge of the ADC clock, this oscillation is enabled and initiates the SAR operation. When all 10 bits are resolved, the oscillation loop is disabled and the ADC returns to a sleep state while the T&H starts to track the next analog input. Clock boosting is used to achieve sufficient T&H linearity [15] by boosting the switch driving voltage to about 1 V. Despite the low VDD of 0.6 V, high- $V_t$  devices are used in the ADC to minimize leakage power. The dynamic comparator [16] is operating

Fig. 7. 10b asynchronous SAR ADC implementation, DAC implementation, and capacitor layout.

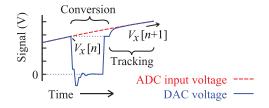

Fig. 8. Illustration of the ADC's input voltage and DAC voltage in time.

Fig. 9. Illustration of the analog-to-digital conversion process.

in subthreshold for best power efficiency. The 10b capacitive DAC uses a segmentation of three unary bits and seven binary bits to save power while improving DNL [14]. For simplicity, a single-ended view of the DAC is shown in Fig. 7, but the actual implementation uses two copies of this circuit. To save power, the LSB unit capacitor in the DAC is reduced to 0.25 fF, yielding an overall DAC capacitance of 300 fF (including parasitics), which is still sufficient for kT/C-noise requirements. In terms of mismatch, this small capacitor value is still expected to be sufficient based on previous experience, as discussed, for instance, in [12] and [14]. Hence, no calibration or trimming is applied. Ideally, each side of the DAC would be composed of  $2^{10} - 1 = 1023$  unit capacitors of 0.25 fF. To save chip area and reduce parasitics, the DAC is in reality composed of 511 units of 0.5 fF and a single unit of 0.25 fF. These small units are based on fringing capacitors, of which a layout sketch is shown in Fig. 7 [12], [17]. To increase capacitor density while reducing parasitics to the substrate, two high metal layers are used in parallel to implement these capacitors. Mostly thanks to the small DAC capacitors, the simulated power consumption of the ADC is approximately 1 nW at 1 kS/s. Further, as the ADC has no static biasing but uses purely dynamic circuits, this power scales linearly with the sampling rate.

Fig. 10. (a) Common-mode reference circuit. (b) Bias current generation.

Fig. 11. 16 kHz clock generation circuit.

Fig. 12. Die photo in 65 nm CMOS.

To save power on system level when connecting the amplifier to the ADC, the conversion process in Fig. 8 is considered. As can be seen, during the tracking period, the DAC voltage follows the ADC's input voltage. During the conversion phase, the DAC is disconnected from the input node and will successively approximate the sampled input voltage  $V_x[n]$ . Typical SAR ADCs discharge the DAC to 0 V after each conversion before the tracking of the next input signal  $V_x[n+1]$  starts. During the tracking phase, the equivalent DAC capacitance  $C_{\mathrm{DAC}}$  thus needs to be charged from 0 V to  $V_x[n+1]$  within the tracking time  $\tau_t$ . Assuming a slew-rate limited situation, this implies that the current  $I_{\mathrm{out}}$  drawn from the amplifier is given by

$$I_{\text{out}} = C_{\text{DAC}} \frac{V_x[n+1]}{\tau_t} \tag{5}$$

which thus depends on the DAC capacitance  $C_{\mathrm{DAC}}$ , the amplitude of the input signal  $V_x$  and the duration of the tracking

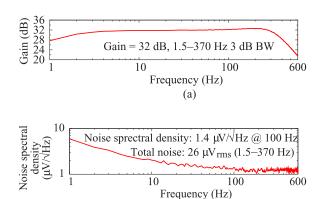

Fig. 13. Amplifier measurements. (a) Gain. (b) IRN.

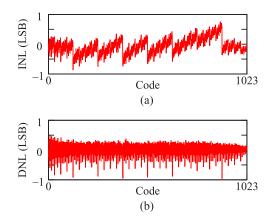

Fig. 14. Static ADC measurements. (a) INL. (b) DNL.

period  $\tau_t$ . To save power, first of all the DAC capacitance is minimized by using small unit capacitors, as detailed before. Second, the DAC in this particular ADC is not reset to 0 V after conversion, but it returns to the previously sampled voltage  $V_x[n]$  before starting to track the next voltage  $V_x[n+1]$ . Because of that, the current drawn from the amplifier is now given by

$$I_{\text{out}} = C_{\text{DAC}} \frac{V_x[n+1] - V_x[n]}{\tau_t} \tag{6}$$

which is dependent on the delta between consecutive input signals rather than their amplitude. Since in many biomedical applications, the highest amount of signal energy is concentrated at lower frequencies, and the power at higher frequencies is limited, the second alternative reduces the output current requirements for the amplifier. As a final step of power saving, the tracking time  $\tau_t$  is maximized by taking advantage of the asynchronous clocking scheme of the ADC and the speed available from modern CMOS processes. As illustrated in Fig. 9, the AD conversion is initiated on a rising edge of the ADC clock. As soon as the conversion is finished, which is approximately in 5  $\mu$ s, the ADC returns to tracking mode without waiting for the falling edge of the ADC clock. Since the total clock period is 1 ms, this results in a tracking phase which is 99.5% of the total clock period.

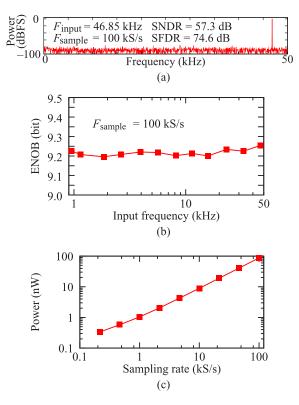

Fig. 15. Dynamic ADC measurements. (a) Single-tone output spectrum. (b) ENOB versus input frequency. (c) Power consumption versus sampling rate.

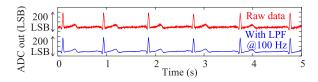

Fig. 16. Measured *in vivo* ECG using the complete signal acquisition system powered from a 0.69 mm<sup>2</sup> photodiode array.

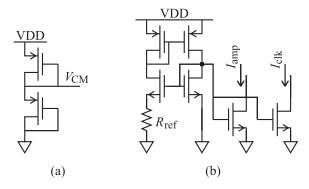

# C. Biasing Circuits, Clock Generation, and Serial Data Interface

This section describes the various auxiliary circuits that are needed to fully integrate the signal acquisition system. First of all, a common-mode reference  $V_{\rm CM}$  for the amplifier is created by two diode-connected PMOS devices in subthreshold mode [Fig. 10(a)], consuming only 20 pW. Further, Fig. 10(b) shows a standard bootstrapped current reference circuit which creates two bias currents: one for the amplifier stages  $(I_{\rm amp})$  and one for the clock generator  $(I_{\rm clk})$ . All transistors inside this reference circuit are biased in the subthreshold regime, allowing operation at supply voltages down to 0.5 V. A large  $R_{\rm ref}$  of  $40~{\rm M}\Omega$  is used to have reasonably stable operation over process corners, resulting in  $\pm 20\%$  variation of the generated reference currents while consuming 0.4 nW.

The serial data interface in Fig. 2 multiplexes 16 bit of data into a single-wire interface. Each 16 bit packet contains 10 bit of ADC data, preceded by a fixed code pattern of 6 bit. This header enables a receiving chip to correctly synchronize itself to the received packets, and thus to recover the clock frequency and ADC data. For multiplexing the data, the 16:1 MUX is

TABLE I SIMULATED POWER CONSUMPTION AT 0.6 V SUPPLY

| Component        | Power consumption |  |  |  |  |

|------------------|-------------------|--|--|--|--|

| Amplifier        | 1.05 nW           |  |  |  |  |

| A1 main stage    | 0.60 nW           |  |  |  |  |

| A1 CMFB stage    | 0.24 nW           |  |  |  |  |

| A2 main stage    | 0.12 nW           |  |  |  |  |

| A2 CMFB stage    | 0.06 nW           |  |  |  |  |

| DSL main stage   | 1 pW              |  |  |  |  |

| DSL CMFB stage   | 30 pW             |  |  |  |  |

| ADC              | 0.87 nW           |  |  |  |  |

| DAC              | 0.19 nW           |  |  |  |  |

| Т&Н              | 0.04 nW           |  |  |  |  |

| Comparator       | 0.50 nW           |  |  |  |  |

| Logic            | 0.14 nW           |  |  |  |  |

| Other components | 1.26 nW           |  |  |  |  |

| VCM bias         | 0.02 nW           |  |  |  |  |

| Current bias     | 0.40 nW           |  |  |  |  |

| Clock generation | 0.49 nW           |  |  |  |  |

| Serial interface | 0.35 nW           |  |  |  |  |

| Overall system   | 3.18 nW           |  |  |  |  |

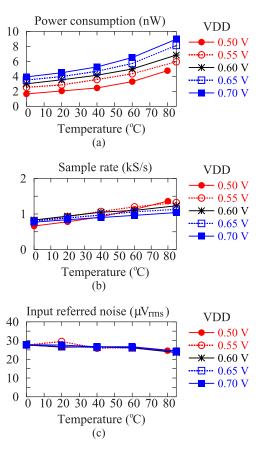

Fig. 17. Measurements as function of temperature and supply. (a) Overall power consumption. (b) ADC clock frequency. (c) Overall IRN.

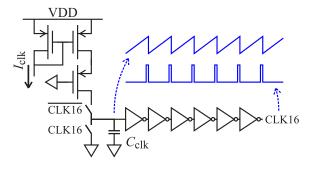

controlled by a 4 bit counter that runs at  $16\times$  the ADC sampling rate. Thus, a clock signal at 16 kHz is needed considering the ADC operates at 1 kS/s. To generate this clock, the previously generated reference current  $I_{\rm clk}$  is mirrored and integrated on a capacitor  $C_{\rm clk}$  of 10 fF, as shown in Fig. 11. A feedback loop resets  $C_{\rm clk}$  after a threshold voltage is reached, thus creating a

|           |                            | This work    | [3]   | [4]    | [5]       | [11]  | [1    | 4]   | [18]   |

|-----------|----------------------------|--------------|-------|--------|-----------|-------|-------|------|--------|

| System    | Process (nm)               | 65           | 65    | 180    | 350       | 180   | 65    |      | 40     |

|           | Area (mm²)                 | 0.20         | 0.6*  | 0.25 * | 1         | 0.25  | 0.076 |      | 0.0065 |

|           | VDD (V)                    | 0.6          | 0.6   | 0.45   | 1         | 1     | 0.6   |      | 0.45   |

|           | VT corner                  | 0.50-0.70 V  | N/A   | N/A    | N/A       | N/A   | N/A   |      | NI/A   |

|           | measurements               | 0–85 °C      |       |        |           |       |       |      | N/A    |

|           | Power (nW)                 | 3            | 18.6  | 940    | 445-895   | 266   | 72    | 97   | 84     |

| Amplifier | Power (nW)                 | 1.0          | 16.8  | 730    | 33–337    | 266   |       |      |        |

|           | BW min. (Hz)               | 1.5          | < 0.5 | 0.25   | 4.5 m-3.6 | <1    |       |      |        |

|           | BW max. (Hz)               | 370          | 250   | 10 k   | 31-292    | >500  |       |      |        |

|           | IRN (μV <sub>rms</sub> )   | 26           | 6.52  | 3.2    | 2.5       | 1.54  |       |      |        |

|           | Gain (dB)                  | 32           | 51-96 | 52     | 46-60     | 59 ## |       |      |        |

|           | CMRR (dB)                  | 60 at 100 Hz | 55    | 73     | 71        | 89    |       |      |        |

|           | PSRR (dB)                  | 63 at 100 Hz | 67    | 80     | 84        | 92    |       |      |        |

|           | NEF                        | 2.1          | 2.64  | 1.57   | 3.26      | 1.38  |       |      |        |

| ADC       | Power (nW)                 | 1.1/88 **    | 1.8   | 1350#  | 230       |       | 72    | 97   | 84     |

|           | Resolution (bit)           | 10           | 8     | 9      | 12        |       | 10    | 12   | 10     |

|           | ENOB (bit)                 | 9.2          | 7.14  | 8.27   | 10.2      |       | 9.4   | 10.1 | 8.95   |

|           | INL (LSB)                  | 0.87         | 1.8   | 1      | 1.4       |       | 0.48  | 1.90 | 0.44   |

|           | DNL (LSB)                  | 0.96         | 1.0   | 0.5    | 0.8       |       | 0.32  | 0.97 | 0.45   |

|           | F <sub>sample</sub> (kS/s) | 1.1/100 **   | 0.5   | 200#   | 1         |       | 40    | 40   | 200    |

|           | FoM (fJ/c.step)            | 1.7/1.5 **   | 25.5  | 22     | 196       |       | 2.7   | 2.2  | 0.85   |

TABLE II

PERFORMANCE SUMMARY AND COMPARISON

saw-tooth wave as illustrated. The saw-tooth results in a clock signal CLK16 of nominally 16 kHz. A chain of six inverters is used to create delay in the feedback loop to ensure a sufficiently long on-pulse for the generated clock. Also, the first inverter uses transistors with increased lengths to avoid short-circuit power loss due to the saw-tooth input signal. As shown in Fig. 2, CLK16 drives a 4 bit counter which controls the MUX. At the same time, the counter acts as a clock divider to generate a 1 kHz ADC clock.

# IV. MEASUREMENTS

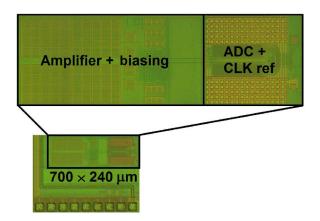

The signal acquisition system was implemented in a 65 nm CMOS technology and occupies a chip area of 0.20 mm² including supply decoupling capacitors but excluding the pads (Fig. 12). The relatively large size of the amplifier and biasing circuits is caused by the passive components, mostly the 40 pF input capacitors and the 40  $M\Omega$  reference resistor. In the following, stand-alone measurement of the amplifier and ADC will be shown first, followed by characterization of the full system. Unless stated otherwise, all measurements are performed at 0.6 V supply and room temperature.

#### A. Stand-Alone Amplifier and ADC Measurements

The measured amplifier shows a gain of 32 dB and a -3 dB bandwidth from 1.5 to 370 Hz [Fig. 13(a)]. Fig. 13(b) shows the IRN density, which is  $1.4 \ \mu V/\sqrt{\rm Hz}$  at 100 Hz. Integrated over the amplifier's bandwidth, this results in an integrated IRN level

of  $26~\mu V_{\rm rms}$ . With a power consumption of 1 nW at 0.6 V supply, this gives an NEF of 2.1. The measured CMRR and PSRR (at 100 Hz) of the amplifier are 60 and 63 dB, respectively.

The stand-alone ADC was characterized at 0.6 V supply. It operates at sampling rates up to 100 kS/s thanks to the  $\sim 5~\mu s$  conversion time. As shown in Fig. 14, it achieves an INL and DNL of 0.87 and 0.96 LSB, respectively. Fig. 15(a) shows a measured near-Nyquist spectrum when operating at the maximum speed of 100 kS/s. The achieved SNDR is 57.3 dB, giving an ENOB of 9.2 bit. This ENOB is maintained throughout the full bandwidth as can be seen in Fig. 15(b). Further, Fig. 15(c) confirms that the dynamic power consumption of the ADC scales linearly with the sampling rate down to a leakage level of 0.15 nW. At 100 kS/s, the power consumption is 87.8 nW, resulting in an FoM of 1.5 fJ/conversion-step.

# B. System Measurements

To provide an application example and to demonstrate the practical performance of the fully integrated system, the IC is used to perform an *in vivo* ECG recording. A three-electrode setup is used where two electrodes capture the ECG signal on the chest and a third electrode is used for grounding. Further, to demonstrate the low-power consumption and the ability to create miniature systems, the supply is directly provided by a 0.69 mm<sup>2</sup> photodiode array, composed of three TEMD7000X01 PIN photodiodes in series. In indoor fluorescent lighting conditions, a single TEMD7000X01 PIN photodiode was measured to have an open circuit voltage of only 0.2 V. Thus, by connecting three devices in series, a sufficiently high supply voltage can be generated for the IC. No power regulation

<sup>\*</sup>Estimated

<sup>\*\*</sup>Performance in integrated system and standalone at max sampling rate respectively.

<sup>#</sup>ADC performance per 10 channels.

<sup>##</sup>Open-loop.

is used, nor are external filters or capacitors applied. Fig. 16 displays the captured ADC data. Both the raw data without any processing are shown as well as the data after applying an LPF at 100 Hz in processing software.

At room temperature, the total measured power consumption of the system is 3 nW from a 0.6 V supply. A power breakdown, based on simulations, is shown in Table I. To verify the robustness of the system over supply and temperature corners, the power consumption, sampling rate, and IRN are measured in a 0–85 °C temperature range and a 0.5–0.7 V supply range. The power consumption [Fig. 17(a)] ranges from 2 up to 9 nW and shows a gradual increase with temperature. This is caused by the increase of leakage currents and the increase of the generated reference current. The latter effect directly increases the power consumption of the amplifier and also results in a proportionally higher clock frequency [Fig. 17(b)], thereby increasing the power consumption of the ADC. The IRN [Fig. 17(c)] of the full system (amplifier and ADC) is  $27 \mu V_{\rm rms}$  under nominal conditions. As the dominant IRN voltage is coming from the amplifier's input pair, it is proportional to  $kT/g_m$ . As  $g_m$  is proportional to the bias current  $I_B$  in the subthreshold mode, this implies that the IRN voltage is proportional to  $T/I_B$ . Normally, this implies that the noise will increase with temperature. However, as explained before, the generated bias current also increases with temperature T, thereby resulting in a relatively stable noise performance over VT variations.

Table II summarizes the performance of this work and gives a comparison to state-of-the-art low-power signal acquisition ICs [3]–[5], an amplifier [11], and ADCs [14], [18]. Compared to the other integrated systems, this work has the lowest power consumption, occupies the smallest chip area, and is the only low-power design verified over supply and temperature corners to validate robustness. Logically, due to fundamental noise-power tradeoffs, the sixfold power reduction comes at the cost of an increased IRN. However, the power efficiency figures of the proposed work (NEF = 2.1 for the amplifier and FoM = 1.5 fJ/conversion-step for the ADC) are well in line with state-of-the-art amplifiers and ADCs.

# V. CONCLUSION

This work demonstrated a fully integrated signal acquisition ASIC. With a chip area of  $0.20~\rm mm^2$  and a power consumption of 3 nW, it enables miniature, long-term sensing applications. The sixfold reduction in power consumption compared to prior art is achieved while providing adequate accuracy and speed to enable, e.g., biopotential sensing applications. At the same time, the IC offers a bandwidth, ADC speed, and ENOB well in line with alternative systems. Despite the low absolute power, state-of-the-art power efficiency in the amplifier (NEF = 2.1) and ADC (FoM =  $1.5~\rm fJ/conversion$ -step) is achieved. Measurements over supply and temperature corners confirm that, despite the extremely low-power consumption, the circuit shows reliable and predictable behavior.

# REFERENCES

- H. Nakazawa, K. Sano, T. Abe, M. Baba, and N. Kumagai, "Charge-discharge characteristics of all-solid-state thin-filmed lithium-ion batteries using amorphous Nb<sub>2</sub>O<sub>5</sub> negative electrodes," *J. Power Sources*, vol. 174, no. 2, pp. 838–842, Dec. 2007.

- [2] M. Wahbah, M. Alhawari, B. Mohammad, H. Saleh, and M. Ismail, "Characterization of human body-based thermal and vibration energy harvesting for wearable devices," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 4, no. 3, pp. 354–363, Sep. 2014.

- [3] Y.-P. Chen *et al.*, "An injectable 64 nW ECG mixed-signal SoC in 65 nm for arrhythmia monitoring," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 375–390, Jan. 2015.

- [4] D. Han, Y. Zheng, R. Rajkumar, G. Dawe, and M. Je, "A 0.45 V 100-channel neural-recording IC with sub-μW/channel consumption in 0.18 μm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2013, pp. 290–291.

- [5] X. Zou, X. Xu, L. Yao, and Y. Lian, "A 1-V 450-nW fully integrated programmable biomedical sensor interface chip," *IEEE J. Solid-State Circuits*, vol. 44, no. 4, pp. 1067–1077, Apr. 2009.

- [6] P. Harpe, H. Gao, R. van Dommele, E. Cantatore, and A. van Roermund, "A 3 nW signal-acquisition IC integrating an amplifier with 2.1 NEF and a 1.5 fJ/conv-step ADC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2015, pp. 382–383.

- [7] L. Yan et al., "A 680 nA fully integrated implantable ECG acquisition IC with analog feature extraction," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, 2014, pp. 418–419.

- [8] R. Walden, "Analog-to-digital converter survey and analysis," *IEEE J. Sel. Areas Commun.*, vol. 17, no. 4, pp. 539–550, Apr. 1999.

- [9] B. Murmann. (2015, Mar.). ADC performance survey 1997–2015

[Online]. Available: http://www.stanford.edu/~murmann/adcsurvey.html

- [10] M. Steyaert and W. Sansen, "A micropower low-noise monolithic instrumentation amplifier for medical purposes," *IEEE J. Solid-State Circuits*, vol. 22, no. 6, pp. 1163–1168, Dec. 1987.

- [11] Y.-P. Chen, D. Blaauw, and D. Sylvester, "A 266 nW multi-chopper amplifier with 1.38 noise efficiency factor for neural signal recording," in *Proc. IEEE Symp. VLSI Circuits Dig. Tech. Papers*, 2014, pp. 1–2.

- [12] P. Harpe et al., "A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios," IEEE J. Solid-State Circuits, vol. 46, no. 7, pp. 1585– 1595, Jul. 2011.

- [13] S.-W. Chen and R. W. Brodersen, "A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13μm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2669–2680, Dec. 2006.

- [14] P. Harpe, E. Cantatore, and A. van Roermund, "A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3011–3018, Dec. 2013.

- pp. 3011–3018, Dec. 2013.

[15] T. B. Cho and P. R. Gray, "A 10b, 20 Msample/s, 35 mW pipeline A/D converter," *IEEE J. Solid-State Circuits*, vol. 30, no. 3, pp. 166–172, Mar. 1905

- [16] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, and B. Nauta, "A 1.9 μW 4.4 fJ/conversion-step 10b 1 MS/s charge-redistribution ADC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2008, pp. 244–245.

- [17] J. Bach, "Capacitive array," US Patent 7 873 191, Jan. 2011.

- [18] H.-Y. Tai, Y.-S. Hu, H.-W. Chen, and H.-S. Chen, "A 0.85 fJ/conversion-step 10b 200 kS/s subranging SAR ADC in 40 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2014, pp. 196–197.

**Pieter Harpe** (SM'15) received the M.Sc. and Ph.D. degrees in electrical engineering from the Eindhoven University of Technology, Eindhoven, The Netherlands, in 2004 and 2010, respectively.

In 2008, he was a Researcher with Holst Centre/imec, Eindhoven, The Netherlands. Since then, he has been working on ultra low-power wireless transceivers, with a main focus on ADC research and design. In April 2011, he joined Eindhoven University of Technology as an Assistant Professor on low-power mixed-signal circuits. Since 2012, he is

a Co-organizer of the yearly workshop on Advances in Analog Circuit Design (AACD).

Dr. Harpe became Member of the Technical Program Committees of ISSCC and ESSCIRC, in 2013. He was the recipient of the VENI Grant from the Dutch Technology Foundation STW for research on multifunctional ADCs, in 2013.

Hao Gao received the B.Eng. degree from Southeast University, Nanjing, China, and the M.Sc. degree in electrical engineering from Delft University of Technology, Delft, The Netherlands, in 2008. Since then, he has been working toward the Ph.D. degree in electrical engineering at Eindhoven University of Technology, Eindhoven, The Netherlands.

In 2012, he had a European Marie Curie Researcher position with Catena Wireless Electronics (Catena Group, NXP Semiconductor), Stockholm, Sweden. Since 2014, he has been a Postdoctoral

Researcher with ELCA-Group, Delft University of Technology. His research interests include the ultra-low-power radio and wireless power transfer.

Mr. Gao was the recipient of the Philips Semiconductor Scholarship, Delft, The Netherlands, 2006. He was also the recipient of the Best Paper Reward at the WiSNet, the 2011 IEEE Radio Wireless Week, the US, and the corecipient of the High Quality Paper Award at ICICS 2011, Singapore.

**Rainier van Dommele** received the B.Eng. degree in electrical engineering from Fontys Hogeschool Eindhoven, Eindhoven, The Netherlands, in 2007.

In 2007, he was a Technician with the Radio Communications (ECR) Group, Eindhoven University of Technology, Eindhoven, The Netherlands. Since 2012, he has been a Technician with the Mixed-Signal Microelectronics (MsM) Group, Eindhoven University of Technology.

Eugenio Cantatore (M'98–SM'14) received the Master's and Ph.D. degrees in electrical engineering from Politecnico di Bari, Bari, Italy, in 1993 and 1997, respectively. From 1994 to 1999 he was first a Ph.D. student and then a fellow at the European Laboratory for Particle Physics (CERN) Geneva, Switzerland.

In 1999, he moved to Philips Research, Eindhoven, The Netherlands, as a Senior Scientist, and in 2007 joined Eindhoven University of Technology, Eindhoven, The Netherlands, where he is an

Associate Professor. He has authored or coauthored more than 130 papers in journals and conference proceedings, and 13 patents or patent applications. His research interests include the design and characterization of electronic circuits exploiting emerging technologies as well as the design of ultra-low-power microsystems for medical applications.

Dr. Cantatore is active in the Technical Program Committees of ESSDERC, ESSCIRC, and ISSCC, and has been member of the Executive Committee of ISSCC. Since 2013, he has been a Chair of the Technology Directions Subcommittee of ISSCC. He has been a fellow at the European Laboratory for Particle Physics (CERN) Geneva, Switzerland. In 2006, he was the recipient of the Beatrice Winner Award for Editorial Excellence from ISSCC and was nominated in the Scientific American top 50 list. He was also the recipient of the Philips Research Invention Award in 2007 and the Best Paper Award from ESSDERC in 2012.

**Arthur H. M. van Roermund** (SM'95) was born in Delft, The Netherlands, in 1951. He received the M.Sc. degree in EE from Delft University of Technology, Delft, The Netherlands, and the Ph.D. degree in applied sciences from K.U.Leuven, Leuven, Belgium, in 1975 and 1987, respectively.

From 1975 to 1992, he was with Philips Research Laboratories, Eindhoven, The Netherlands. From 1992 to 1999, he was a Full Professor with the EE Department, Delft University of Technology. In October 1999, he joined Eindhoven University of

Technology, Eindhoven, The Netherlands. Since then, he is a Chairman of the Mixed-signal Microelectronics Group, Technical University Eindhoven, Eindhoven, The Netherlands. He was a Director of Research with the EE Department, Delft University of Technology (2002–2012). He was a Coorganizer of the Yearly Workshop on Advanced Analog Circuit Design (AACD, 2001–2012). He has authored over 600 publications, 25 books, and is a Co-Editor of another 10 books.

Dr. van Roermund was a member of three international assessment panels: Politecnico di Milano, Milano, Italy, 2007; Aalto University, Espoo, Finland, 2009; KTH, Stockholm, Sweden, 2012. He was the recipient of the "Simon Stevin Meester" Award for his scientific and technological achievements in 2004.