# A reconfigurable mixed-time-criticality SDRAM controller

Citation for published version (APA):

Goossens, S. L. M. (2015). A reconfigurable mixed-time-criticality SDRAM controller. [Phd Thesis 1 (Research TU/e / Graduation TÙ/e), Electrical Engineering]. Technische Universiteit Eindhoven.

# Document status and date:

Published: 09/12/2015

# Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

# General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

# Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# A Reconfigurable Mixed-Time-Criticality SDRAM Controller

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 9 december 2015 om 16:00 uur

door

**Svennius Leonardus Maria Goossens**

geboren te Wouw

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. A.C.P.M. Backx 1<sup>e</sup> promotor: prof.dr. K.G.W. Goossens

copromotor: dr. K.B. Akesson

leden: Prof.Dr.-Ing. R. Ernst (Technische Universität Braunschweig)

prof.dr. K.L.M. Bertels (Technische Universiteit Delft)

prof.dr. H. Corporaal

dr.ir. R.J. Bril

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# A Reconfigurable Mixed-Time-Criticality SDRAM Controller

Sven Goossens

## Committee:

prof.dr. K.G.W. Goossens dr. K.B. Akesson prof.dr.ir. A.C.P.M. Backx Prof.Dr.-Ing. R. Ernst prof.dr. K.L.M. Bertels prof.dr. H. Corporaal dr.ir. R.J. Bril Eindhoven University of Technology, promotor

Eindhoven University of Technology, copromotor

Eindhoven University of Technology, chairman

Technische Universität Braunschweig

Technische Universiteit Delft

Eindhoven University of Technology

Eindhoven University of Technology

© Sven Goossens 2015. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Velociraptor skeleton cover image: (CC BY 2.0) Ben Townsend from Blacksburg, Virginia.

This thesis is typeset in Later than the sublime Text and built with SCons, contains figures created in LibreOffice Draw and graphs plotted using matplotlib, and is held together by Python-based duct-tape.

Printed by CPI Koninklijke Wöhrmann – The Netherlands.

A catalogue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-3976-5

Hofstadter's law: It always takes longer than you expect, even when you take into account Hofstadter's Law

- Douglas Hofstadter, Gödel, Escher, Bach, 1979

#### ACKNOWLEDGMENTS

This thesis did not appear out of thin air. In fact, its main ingredients are time, effort, and the support that I received from everyone that I will try to list here. Traditionally, a good place to start seems to be the promotor, and I see no reason to deviate from that trend. I would like to thank Prof. Kees Goossens, for being an organized, interested and very helpful promotor. Working together has always been a pleasant experience, and I think that the team-like atmosphere that he created within the CompSOC research group, both during and after office hours, might have been my greatest motivator during these past years. I am also extremely thankful to my copromotor, Dr. Benny Akesson, who possesses a seemingly endless supply of both energy and patience, which helped out a great deal in making this thesis what it is today. I appreciate his sense of humor, and the motivation and help he provided to improve the quality of my work.

I thank Prof. Rolf Ernst, Prof. Koen Bertels, Prof. Henk Corporaal and Dr. Reinder Bril for being a part of my Doctoral Committee, and for their time and effort in reviewing the manuscript. I would also like to thank Christian Weis and his team in Kaiserslautern for bringing an interesting set of practical problems that mixed well with the work done in the Memory Team in Eindhoven. I appreciated our collaborations.

Speaking of the Memory Team, I have to thank Karthik, Manil and Yonghui as the core members of the local SDRAM enthusiasts ensemble. I think every Ph.D. should have such a nice group of smart peers to bounce ideas back and forth with, and our discussions typically led to good insights and ways to move our work forward. I also thank the Memory Team alumni Tim and Jasper, who contributed a great deal to the foundations of this thesis. They were great to have around, and delivered a very nice piece of work, that I appreciate a lot more in hindsight, now that I realize how the average master student project ends up.

Working in the CompSOC team has been awesome. Since I cannot remember the exact Star-Trek-based classification system we made up, so I will just use an alphabetically ordered list: Anca, Andrew, Ashkan, Gabriela, Hadi, Juan, Martijn, Rasool, Reinier, Shubhendu, and those who I might have missed: Thanks for the all support and the fun things we have done over the past years.

One of the perks of being a Ph.D. student is the ability to travel around, and to see interesting places with interesting people. The highlight of this aspect was undoubtedly my internship at Sonics in Silicon Valley, where I was received with incredible amounts

of hospitality. It was an experience that I will never forget, and want to I sincerely thank the Milpitas team for that.

To make sure that this acknowledgment section does not overstay its welcome, I will speed it up now: Cedric, Gert-Jan, Maurice, Francesco: Fiuggi was excellent! (bottlesort, anyone?) Davit and Shakith: running around in Montreal with them made an already interesting ESWeek even better. Ralph, Sander, and my programming buddy Raymond: thanks for allowing me to ride along on the Computation train, it is hard work, but so much fun. Joost, Luc (x2), Marcel, Mar(c/k), and Roel: made "the coffee table" (and most notably the Friday afternoon version) an infamous tradition that is now passed on across the generations. And to Marja, Margot, Rian, and all the other ES group members I missed: I greatly value their support and the effort they put into making floor 3/4 the fun, functional and friendly place that it is.

Finally I thank my family and friends, for all the obvious reasons. Barend, Bas, Evert, Emil, JWN, Koen, Marijn, Niels and Rob: thanks for trucking along through at least the first 6+ years of my TU/e career: some of the older uploads might have faded away, but the memories and quotes live on!

# A Reconfigurable Mixed-Time-Criticality SDRAM Controller

Embedded systems process, move, and store data on behalf of the applications they run, and in doing so, inherit their requirements. Driven by cost and power constraints, there is a trend to integrate an increasing number and variety of applications within a single system. Applications have different time-criticalities: some have real-time constraints, and need certain worst-case performance guarantees from the system to assert that deadlines or throughput requirements are met. Others are satisfied with all the resources they can get, working according to a best-effort principle, where the user experience improves when the system provides more resources to them.

One of the commonly used data storage media for embedded systems is SDRAM. Multiple applications within a system typically share one SDRAM controller. Even though resource sharing reduces costs, it comes at a price: whenever applications share hardware, their timing behavior becomes interdependent. Some applications may not be tolerant to this interference, since it significantly increases the effort of verifying their behavior, or simply because a safety standard requires them to be isolated from others. *Predictable* and *composable* systems can be built to provide isolation of worst-case and actual-case performance to their applications, respectively, although this requires careful considerations when these systems are designed.

SDRAM technology progresses quickly, with new standards arriving almost on a yearly basis. Existing real-time SDRAM controllers lack the flexibility to effectively deal with this, since they are usually designed for one particular SDRAM device or generation. On a smaller timescale, they also lack the flexibility to adapt to applications that are dynamically started and stopped. Even though such applications only require resources in specific use-cases, existing controllers typically use a single configuration that necessarily has to account for the most challenging super-set of applications, leading to over-allocation. Finally, power consumption is not taken into account in the SDRAM command-scheduling algorithms these controllers use, even though most embedded systems have a limited power budget.

This thesis is about the design and performance analysis of an SDRAM controller that caters to both real-time and best-effort applications, and is hence a *mixed-time-criticality memory controller*. We *propose a novel reconfigurable memory controller architecture and corresponding worst-case performance analysis*. A prototype implementation of the controller in SystemC and synthesizable VHDL for an FPGA development board are used both as a proof of concept of the architecture template, and as a means to evaluate the remaining contributions.

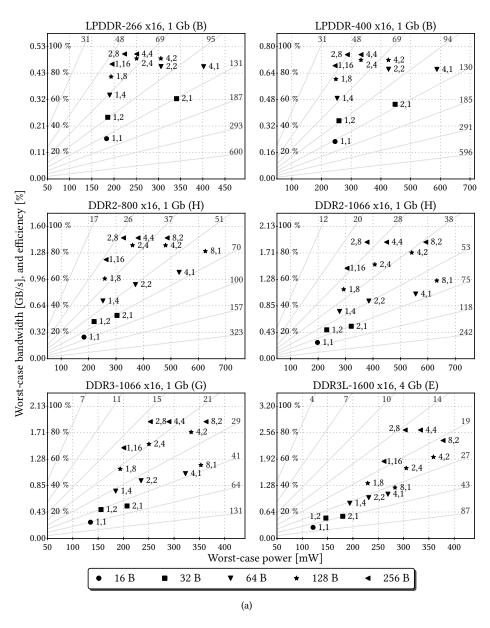

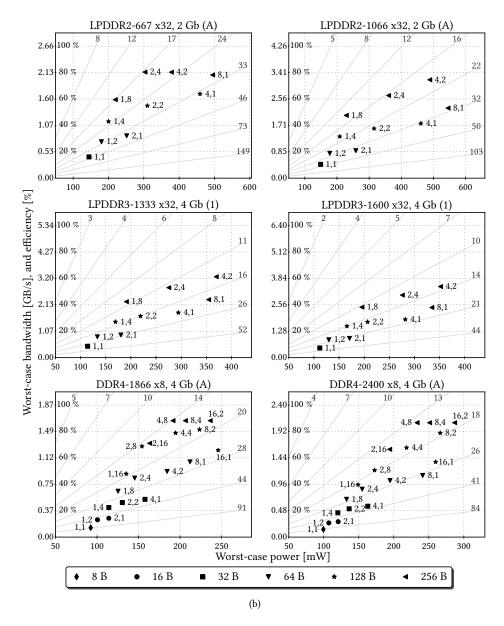

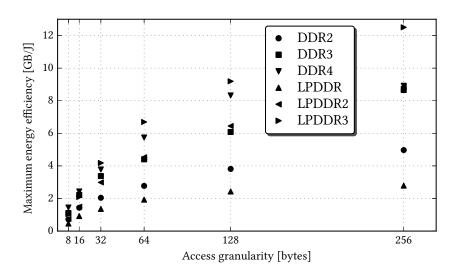

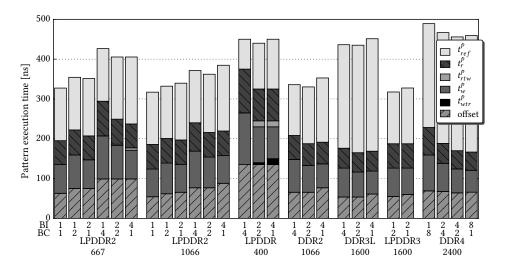

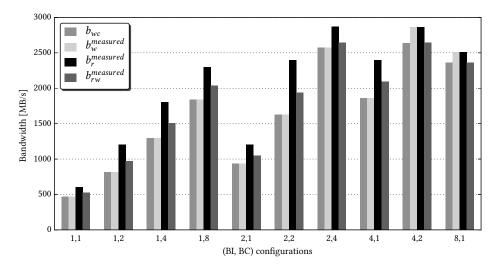

The command scheduler in the controller applies the concept of *memory patterns*, which are sequences of SDRAM commands that are statically computed at design time and dynamically scheduled at run time. We improve upon the state of the art by *exploring the entire memory pattern design space*, by varying the number of banks data is interleaved across, effectively changing the low-level memory map. We *show that a trade-off exists between worst-case bandwidth, power, and request execution time based on the selected memory map*, and evaluate it for twelve memories from six different SDRAM generations (LPDDR1/2/3, DDR2/3/4). The results quantify the controller's performance, and the observed trends can help a system designer in selecting a cost-efficient memory device and the associated memory-map operating point.

To create efficient memory patterns for the various considered memory generations, we propose an optimal ILP formulation and two fast heuristic versions. The first version generates near optimal results for most considered memory types. The second version is aware of bank-groups, a new architectural feature in DDR4, and can hence create shorter patterns for these memories. We additionally provide an algorithm to post-process memory patterns such that they deliver complete cycle-level isolation. This reduces the application verification costs with minimal impact on the worst-case performance.

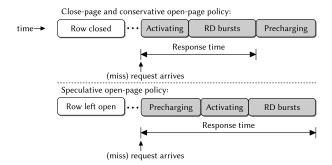

For best-effort applications, we introduce a *conservative open-page policy*, capable of partially exploiting locality of reference in the request stream the controller processes. *It improves average-case performance without compromising worst-case guarantees of real-time applications*. The policy can be combined with an alternative method to provide composability based on hardware delay blocks, enabling best-effort applications to benefit from the open-page policy, while real-time applications still receive cycle-level isolation. This scheme hence meets the needs of both application classes.

The proposed controller is *configurable at boot-time, and reconfigurable at run-time* on a per use-case basis, allowing arbiter settings and memory patterns to be customized to the active set of applications. Boot-time reconfiguration enables the use of different memories devices and generations from the same memory controller. The memory patterns can be customized to select different power / performance operating points (memory maps). For reconfiguration at run time as a result of a use-case switch, we *show* which conditions should be satisfied to maintain composable or predictable performance for running applications, while arbiter allocations are changed. This allows us to allocate arbiter budgets on a per use-case basis, instead of allocating for all use-cases at once, which increases the number of applications we can successfully map to the controller. We define, implement, and demonstrate how to implement these conditions for a TDM arbiter.

# CONTENTS

| 1 | INTRODUCTION                                            |                                                          |  |  |  |  |

|---|---------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

|   | 1.1                                                     | The SoC - SDRAM interface                                |  |  |  |  |

|   | 1.2                                                     | SDRAM Controllers                                        |  |  |  |  |

|   | 1.3                                                     | Cramming more applications onto (power-constrained) SoCs |  |  |  |  |

|   | 1.4                                                     | Performance                                              |  |  |  |  |

|   | 1.5                                                     | Requirements for SDRAM controllers in modern SoCs        |  |  |  |  |

|   | 1.6                                                     | Problem statement and contributions                      |  |  |  |  |

|   | 1.7                                                     | Thesis outline                                           |  |  |  |  |

| 2 | BACKGROUND AND TERMINOLOGY                              |                                                          |  |  |  |  |

|   | 2.1                                                     | SDRAM                                                    |  |  |  |  |

|   | 2.2                                                     | Pattern-based SDRAM controller                           |  |  |  |  |

|   | 2.3                                                     | Burst grouping                                           |  |  |  |  |

|   | 2.4                                                     | Refresh                                                  |  |  |  |  |

|   | 2.5                                                     | Latency-rate servers                                     |  |  |  |  |

| 3 | RECONFIGURABLE REAL-TIME MEMORY CONTROLLER ARCHITECTURE |                                                          |  |  |  |  |

|   | 3.1                                                     | Architecture template                                    |  |  |  |  |

|   | 3.2                                                     | Worst-case performance analysis                          |  |  |  |  |

|   | 3.3                                                     | CompSOC controller instance                              |  |  |  |  |

|   | 3.4                                                     | Evaluation                                               |  |  |  |  |

|   | 3.5                                                     | Conclusion                                               |  |  |  |  |

| 4 | MEMORY PATTERNS                                         |                                                          |  |  |  |  |

|   | 4.1                                                     | Generalized command scheduling rules                     |  |  |  |  |

|   | 4.2                                                     | Predictable patterns                                     |  |  |  |  |

|   | 4.3                                                     | Composable pattern conversion                            |  |  |  |  |

|   | 4.4                                                     | Evaluation                                               |  |  |  |  |

|   | 4.5                                                     | Conclusion                                               |  |  |  |  |

| 5 | POWER/PERFORMANCE TRADE-OFFS                            |                                                          |  |  |  |  |

|   | 5.1                                                     | Worst-case bandwidth, energy, and power metrics          |  |  |  |  |

|   | 5.2                                                     | Worst-case bandwidth / power trends                      |  |  |  |  |

|   | 5.3                                                     | Worst-case response time of an atom                      |  |  |  |  |

|   | 5.4                                                     | Evaluation                                               |  |  |  |  |

|   | 5 5                                                     | Conclusion                                               |  |  |  |  |

# X CONTENTS

| 6  | CONSERVATIVE OPEN-PAGE POLICY                                     | 104   |

|----|-------------------------------------------------------------------|-------|

|    | 6.1 Conservative open-page policy                                 | . 105 |

|    | 6.2 Impact on pattern-based controller                            | . 108 |

|    | 6.3 Using explicit precharge commands                             | . 110 |

|    | 6.4 Evaluation                                                    | . 113 |

|    | 6.5 Conclusion                                                    |       |

|    |                                                                   |       |

| 7  | RECONFIGURATION                                                   | 125   |

|    | 7.1 Reconfiguration options                                       | . 126 |

|    | 7.2 Performance guarantees during a use-case switch               |       |

|    | 7.3 Delay block / arbiter reconfiguration with persistent clients | . 129 |

|    | 7.4 Reconfigurable TDM arbiter                                    | . 130 |

|    | 7.5 Evaluation                                                    | . 140 |

|    | 7.6 Conclusion                                                    | . 145 |

|    |                                                                   |       |

| 8  | RELATED WORK                                                      | 146   |

|    | 8.1 SDRAM Controllers                                             |       |

|    | 8.2 SDRAM Performance overviews                                   |       |

|    | 8.3 Reconfiguration                                               | . 157 |

|    |                                                                   |       |

| 9  | CONCLUSIONS AND FUTURE WORK                                       | 159   |

|    | 9.1 Conclusions                                                   |       |

|    | 9.2 Future work                                                   | . 162 |

| DI | LIOGRAPHY                                                         | 164   |

| ы  | LIOURAI II I                                                      | 104   |

| A  | ILP PROBLEM FORMULATION                                           | 178   |

|    | A.1 High-level goal                                               | . 178 |

|    | A.2 Variables                                                     |       |

|    | A.3 Determining lower and upper bounds                            |       |

|    | A.4 Constraints                                                   |       |

|    | A.5 Objective function                                            |       |

|    | •                                                                 |       |

| В  | MEMORY SPECIFICATIONS                                             | 185   |

|    |                                                                   |       |

| C  | CODE LISTINGS                                                     | 188   |

| _  | A A A A A A A A A A A A A A A A A A A                             | 100   |

| D  | LIST OF ACRONYMS                                                  | 190   |

| Е  | LIST OF SYMBOLS                                                   | 193   |

| L  | EIGT OT STRIBOLS                                                  | 173   |

| F  | WORLDWIDE DRAM PRODUCTION                                         | 197   |

|    |                                                                   |       |

| G  | ABOUT THE AUTHOR                                                  | 198   |

|    |                                                                   |       |

| LI | T OF PUBLICATIONS                                                 | 199   |

# LIST OF FIGURES

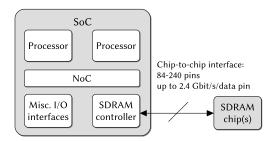

| Figure 1.1  | Typical SoC-SDRAM interface                                      | 2  |

|-------------|------------------------------------------------------------------|----|

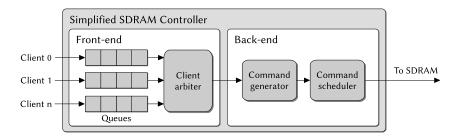

| Figure 1.2  | Simplified general memory controller architecture                | 3  |

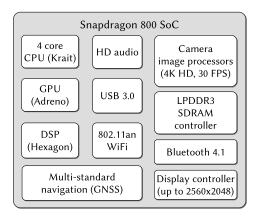

| Figure 1.3  | The Snapdragon 800 SoC [128]                                     | 5  |

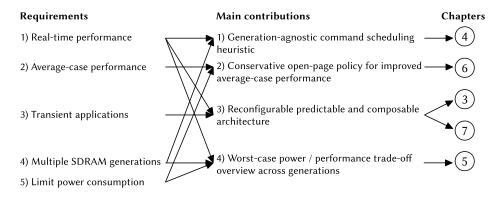

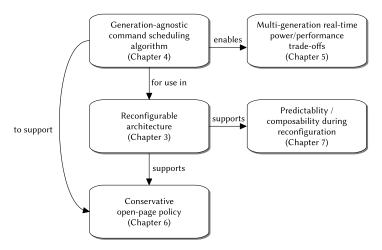

| Figure 1.4  | Mapping of requirements to contributions and chapters            | 12 |

| Figure 1.5  | Overview of chapters                                             | 13 |

| Figure 2.1  | Schematic view of the architecture of an SDRAM device            | 16 |

| Figure 2.2  | High-level SDRAM operation                                       | 17 |

| Figure 2.3  | Typical memory hierarchy for embedded SoCs and COTS systems.     | 20 |

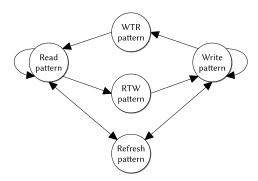

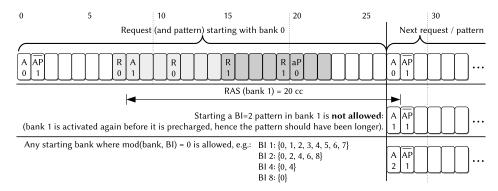

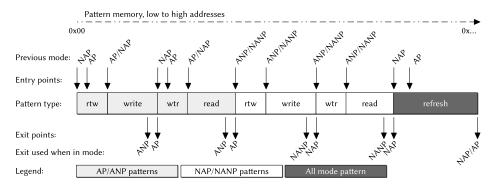

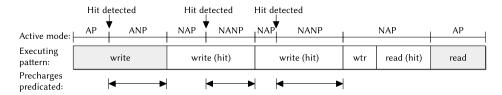

| Figure 2.4  | Allowed pattern sequences.                                       | 21 |

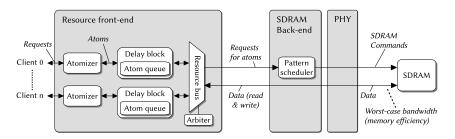

| Figure 2.5  | The general architecture of a pattern-based controller           | 23 |

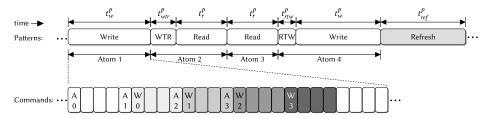

| Figure 2.6  | An example of the order in which patterns may be executed        | 24 |

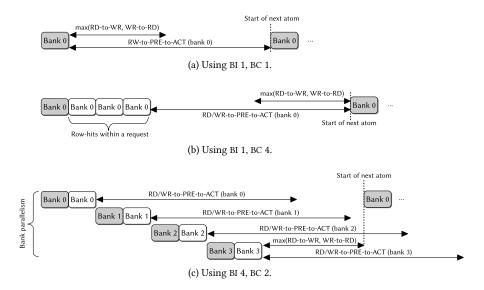

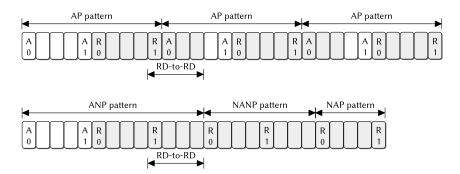

| Figure 2.7  | Examples of the effects of burst grouping                        | 26 |

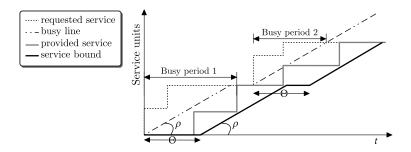

| Figure 2.8  | A $\mathcal{LR}$ server and its associated concepts              | 28 |

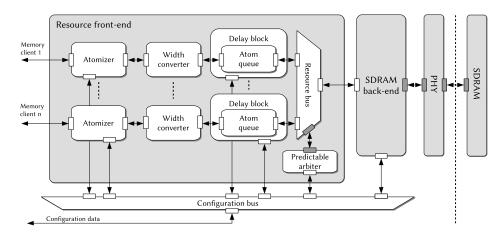

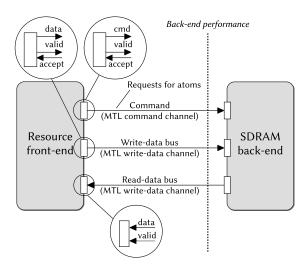

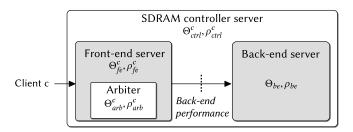

| Figure 3.1  | SDRAM controller architecture                                    | 31 |

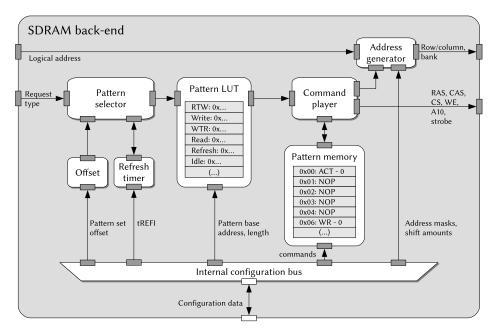

| Figure 3.2  | SDRAM controller back-end                                        | 33 |

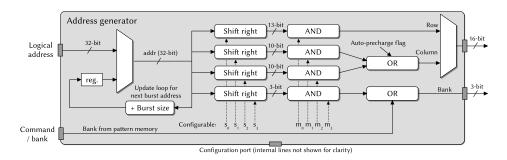

| Figure 3.3  | Address generator architecture                                   | 34 |

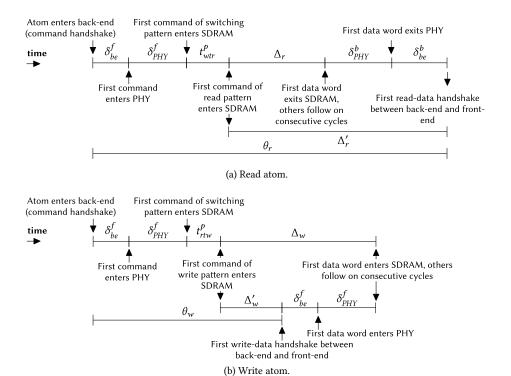

| Figure 3.4  | The interface characterized by the back-end performance          | 37 |

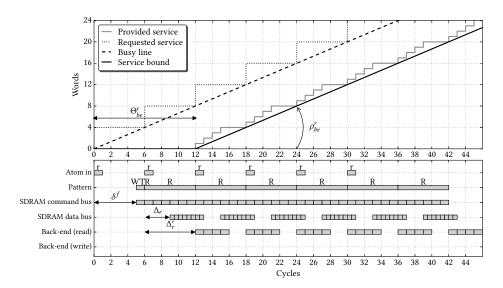

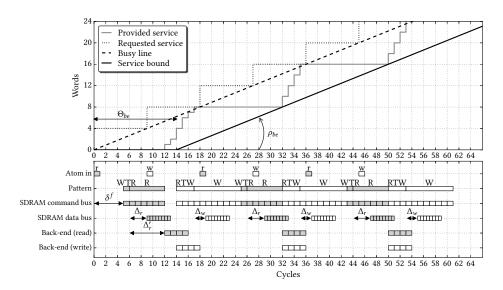

| Figure 3.6  | Worst-case back-end behavior for continuous reads                | 41 |

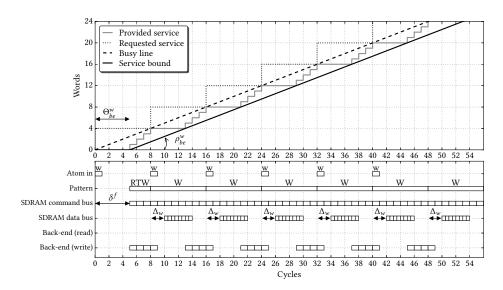

| Figure 3.7  | Worst-case back-end behavior for continuous writes               | 42 |

| Figure 3.8  | Worst-case back-end behavior for interleaved read / write atoms. | 43 |

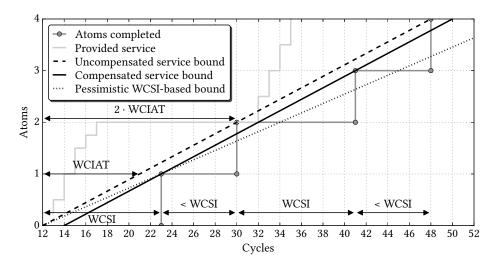

| Figure 3.9  | Demonstration of latency compensation for WCSI                   | 44 |

| Figure 3.10 | Front-end and back-end $\mathcal{LR}$ server concatenation       | 45 |

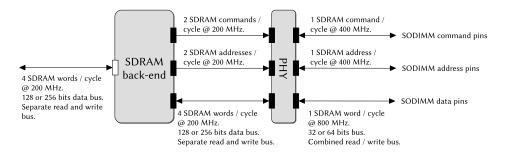

| Figure 3.11 | Typical clock frequencies and data bus widths for Raptor         | 48 |

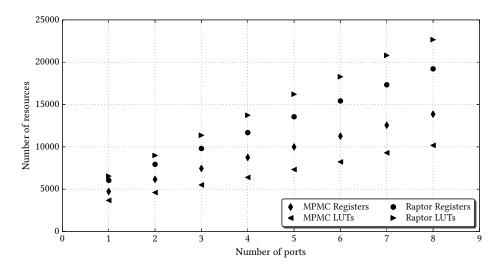

| Figure 3.12 | Resource usage of Raptor vs. MPMC                                | 50 |

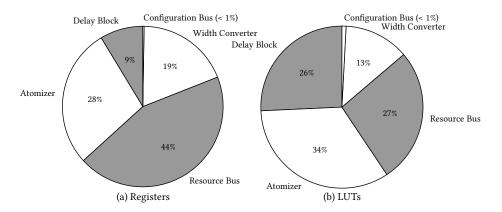

| Figure 3.13 | Front-end LUT and register usage break-down per port             | 52 |

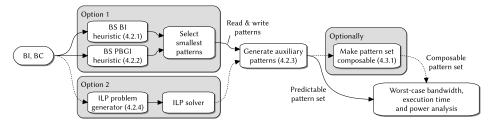

| Figure 4.1  | The pattern flow in this chapter                                 | 54 |

| Figure 4.2  | Constraint abstraction                                           | 56 |

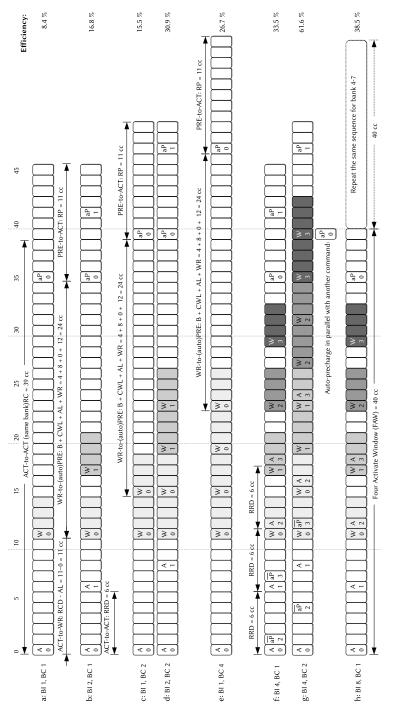

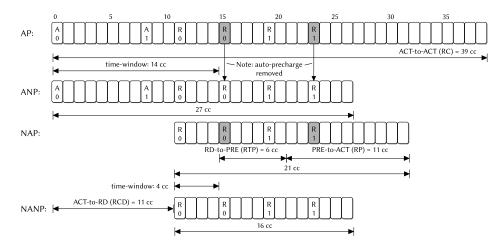

| Figure 4.3  | DDR3-1600 example schedules                                      | 59 |

| Figure 4.4  | A (BI 2, BC 2) read pattern for a DDR3-1066                      | 61 |

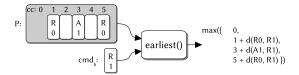

| Figure 4.5  | Example execution of the EARLIEST function                       | 62 |

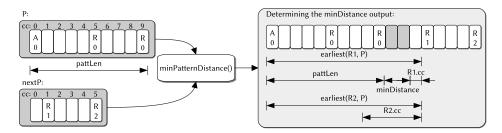

| Figure 4.6  | Example execution of the MINPATTERNDISTANCE function             | 62 |

| Figure 4.7  | (Partial) DDR4-1866 read pattern                                 | 65 |

| Figure 4.8  | Example of the ILP precedence constraints                        | 68 |

| Figure 4.9  | Memory map from logical to physical address                      | 70 |

| Figure 4.10 | Three memory map examples                                        | 71 |

| Figure 4.11 | Composable pattern generation example                            | 73 |

| Figure 4.12 | Exceptional non-optimal result for LPDDR3                        | 77 |

| Figure 4.13 | Write pattern lengths using BS BI, BS PBGI and ILP                    | 78  |

|-------------|-----------------------------------------------------------------------|-----|

| Figure 4.14 | Setup of the composability experiment                                 | 82  |

| Figure 4.15 | Timeline of events during the composability experiment                | 84  |

| Figure 4.16 | Difference in execution of MB1 compared to the baseline trace.        | 87  |

| Figure 5.1  | Worst-case bandwidth vs. worst-case power                             | 93  |

| Figure 5.2  | Maximum energy efficiency versus access granularity                   | 97  |

| Figure 5.3  | Request WCRT components                                               | 98  |

| Figure 5.4  | Worst-case and measured bandwidth                                     | 102 |

| Figure 6.1  | Response time of a hit versus a miss                                  | 105 |

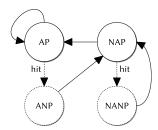

| Figure 6.2  | Read schedules in four different modes                                | 106 |

| Figure 6.3  | Allowed mode transitions                                              | 107 |

| Figure 6.4  | Mapping of patterns to the pattern memory                             | 108 |

| Figure 6.5  | Example of the relation between modes                                 | 109 |

| Figure 6.6  | Example where an ANP pattern is longer than an AP pattern             | 110 |

| Figure 6.7  | Patterns after converting auto-precharges to explicit precharges.     | 112 |

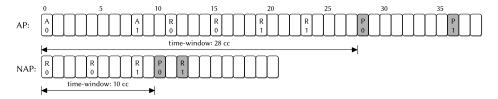

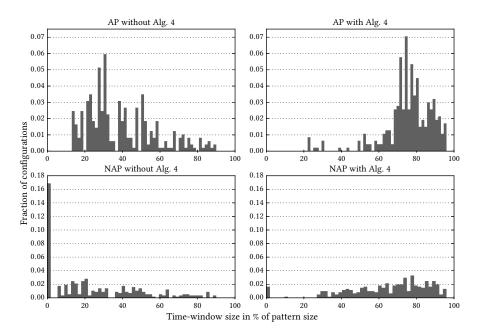

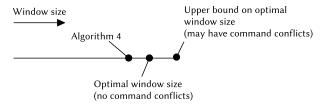

| Figure 6.8  | Relative time-window size histogram                                   | 115 |

| Figure 6.9  | Upper bound on the optimal window size                                | 115 |

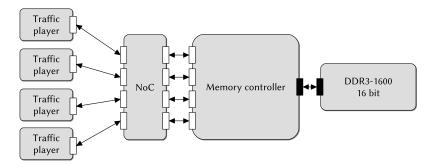

| Figure 6.10 | Setup of the conservative open-page experiments                       | 117 |

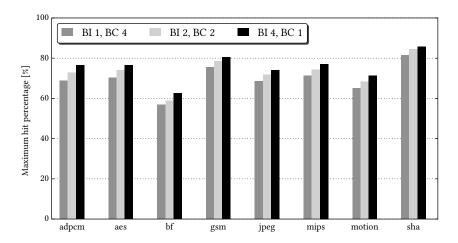

| Figure 6.11 | Available spatial locality per trace                                  | 118 |

| Figure 6.12 | Single-application experiment results                                 | 119 |

| Figure 6.13 | Multi-application experiment results                                  | 122 |

| Figure 7.1  | Reconfigurable components and their interdependencies                 | 126 |

| Figure 7.2  | Example burst placement after reconfiguration                         | 128 |

| Figure 7.3  | Client type hierarchy                                                 | 129 |

| Figure 7.4  | Potentially violated $\mathcal{LR}$ guarantees during reconfiguration | 132 |

| Figure 7.5  | Reconfigurable TDM arbiter architecture                               | 133 |

| Figure 7.6  | Splitting the reconfiguration in two steps                            | 134 |

| Figure 7.7  | 7 0 0                                                                 | 135 |

| Figure 7.8  | Setup showing predictable performance during reconfiguration.         | 140 |

| Figure 7.9  |                                                                       | 141 |

| Figure 7.10 | Slot allocation results                                               | 141 |

| Figure 7.11 | Response times with and without predictable reconfiguration.          | 142 |

| Figure 7.12 | 1                                                                     | 144 |

| Figure 7.13 | 1 1                                                                   | 144 |

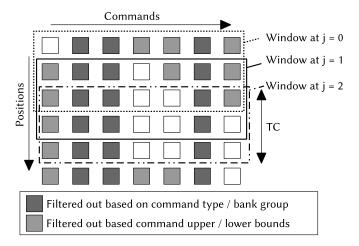

| Figure A.1  |                                                                       | 180 |

| Figure A.2  | Finding lower and upper bounds on the position of a command.          | 181 |

| Figure A.3  | Visualization of window-based constraints                             | 183 |

|             |                                                                       |     |

# LIST OF TABLES

| Table 2.1 | Approximate values of SDRAM timings relative to RC             | 19  |

|-----------|----------------------------------------------------------------|-----|

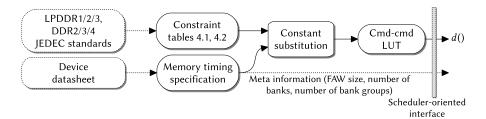

| Table 4.1 | Common constraints across SDRAM types (definition of $d()$ )   | 57  |

| Table 4.2 | SDRAM-type specific constraints                                | 57  |

| Table 4.3 | Memory specifications                                          | 76  |

| Table 4.4 | $e_{pc}$ (Equation (4.3)) for a range of SDRAM x16 devices     | 80  |

| Table 4.5 | The number of runs of a specific type that follow the gray (x) |     |

|           | or black plotted trace                                         | 86  |

| Table 5.1 | Raptor worst-case bandwidth $(b_{wc})$                         | 101 |

| Table 6.1 | Time-window sizes using the conservative open-page policy      | 114 |

| Table 6.2 | CHStone trace characteristics                                  | 116 |

| Table 6.3 | Pattern configuration influence on single application perfor-  |     |

|           | mance when using the conservative open-page policy             | 121 |

| Table 7.1 | Components we can reconfigure for persistent clients           | 130 |

| Table 8.1 | Related memory controllers                                     | 150 |

| Table B.1 | Memory device datasheets                                       | 185 |

| Table B.2 | Memory device timings in clock cycles                          | 186 |

| Table B.3 | $IDD\ [mA]\ /\ VDD\ [V]$ parameters for DRAMPower              | 187 |

|           |                                                                |     |

If you wish to make an apple pie from scratch, you must first invent the universe.

- Carl Sagan, Cosmos, 1980

1

## INTRODUCTION

The average human has a working memory capacity of seven digits, according to one of the most cited publications in psychology [102]. This means if you try to recite the series 3, 8, 5, 3, 2, 1, 1 after simply reading it once you will probably succeed, but repeating that trick with 4, 8, 1, 5, 1, 6, 2, 3, 4, 2 will likely fail. The literal translation of "working memory" to Dutch is "werkgeheugen," a word that is colloquially used to refer to the *Random-Access Memory (RAM)* in a computer system. The majority of the RAM in a computer is *Synchronous Dynamic Random-Access Memory (SDRAM)*, which is the center point of this thesis. Seven digits is approximately equal to 23 bits of information  $(7 \times_2 \log (10))$ , so in some sense, we all are the proud owners of 23 bits of brain-RAM, which is almost enough to store the word "bit" in standard 8-bit ASCII encoding in a computer.

Even though the 640 KB RAM that Bill Gates is rumored<sup>1</sup> to have said "ought to be enough for anybody" is already five orders of magnitude larger than the working memory of the brain, the world's hunger for memory has grown far beyond this number. Memory sizes in the order of gigabytes are now commonplace. The advances in memory capacity are part of a much larger trend, in which the number of transistors that can be manufactured for the same cost grows over time, due to the down-scaling of semiconductor circuits, as stated by *Moore's law* [103]. An equally important aspect of technology scaling is described by *Robert Dennard* [39], who notes that the power density of a chip remains constant, despite the scaling. The combination of Moore's law and Dennard scaling implied that the amount of potential functionality offered by a chip of constant size and with a constant power envelope grew almost exponentially over the past years, and even though we may have reached the tail-end of this trend [44, 69], we are still experiencing the benefits today.

In this chapter, we first look at the developments and trends that led to the current way of working with SDRAM in Section 1.1-1.4. We then identify the requirements on

<sup>1</sup> There are no reliable sources that confirm this quote.

Figure 1.1: Typical SoC-SDRAM interface.

a modern SDRAM controller in Section 1.5, and capture them in the problem statement in Section 1.6. Here, we also briefly discuss how our contributions address the raised issues. Finally, we link the contributions to the remaining chapters in Section 1.7.

#### 1.1 THE SOC - SDRAM INTERFACE

The ability of chips to harbor more and more transistors led to the integration of relatively powerful computing systems on a single chip, into what is called a *System-on-Chip (SoC)*. Their large computing capacity makes it possible to merge multiple distinct pieces of functionality onto a single SoC [65], as opposed to using a separate chip for each of them. The main advantage of doing this is cost reduction [93], which can be attributed to several forms of *resource sharing*. Most obviously, consolidating the functionality of multiple chips on a single SoC reduces the number of chips and the associated costs involved in their manufacturing, consisting of raw materials, masks, packaging, etc. Common circuit components, related to power distribution and clock generation may be shared. On-chip wires are less expensive in terms of area and power compared to wires that leave the silicon, also reducing the costs.

SDRAM has been largely left out of this integration trend, i.e. most modern SoCs connect to an external SDRAM chip. This can again be attributed to economic pressure which drives the development of *Dynamic Random-Access Memory (DRAM)* semiconductor technology in the direction of high-density and low-leakage chips. The design goal is to reduce the costs per bit and power consumption, while still satisfying capacity demands, contrary to logic-circuit technology which was mostly guided by speed requirements [95]. Uniting DRAM and logic in the same technology is not fundamentally impossible, but it is generally less cost effective than using separate chips.

The implication of separating the SoCs from the SDRAM is that a chip-to-chip interface has to be used to connect them, as shown in Figure 1.1. Interfaces (pins) that connect the SoC to external chips are relatively expensive. The *International Technology Roadmap for Semiconductors (ITRS)* [68] estimates the costs per pin as 0.21 (dollar) cents for an SDRAM chip, and as 0.20 and 1.21 cents per pin on a general low-end or high-performance SoC

Figure 1.2: Simplified general memory controller architecture.

package, respectively. Assuming these SoCs have a 84-pin and 240-pin memory interface, their total cost (at the SoC side) is approximately between 0.17 and 2.90 dollars per chip, respectively.

The number pins that can be spent on the SDRAM interface is limited by the size of the SoCs package, which additionally has to accommodate power-supply pins and all other external connections. This naturally creates a bottleneck at the interface, and the associated requirement to use the available SDRAM pins as efficiently as possible.

A complicating factor that is at play here is the so called *memory wall* problem [96, 149], which, in short, consists of the observation that the performance of logic grows faster than the performance of memory, such that memory performance eventually dominates the overall system performance. The memory wall exists for the same reason as the separation between the SoC and the DRAM, i.e. it is an implication of the different optimization goals that are applied to logic-circuit and DRAM technology. Even though 3D stacking promises to increase the number of connections between logic and memory [72, 150], improving the available bandwidth significantly, it does not seem likely that the drive for using the SDRAM interface efficiently will leave the picture.

Looking back at these developments helps to explain the status quo: we only have a relatively narrow interface by which the memory can be reached, shared by the entire SoC. Even though parallelism (in terms of the generation or consumption of data) may exist within both the SoC and SDRAM, we require a serializing component that controls what data is transported across the interface at a given time. The *SDRAM controller* fulfills this role, and is discussed in more detail in the next section.

### 1.2 SDRAM CONTROLLERS

An SDRAM controller is the interface for the SoC to the SDRAM devices. SDRAM controllers have one or more ports (on the SoC side), and each port is connected to a *memory client*. We define *clients* as the sources of memory traffic that are directly connected to the SDRAM controller. Clients generate read or write *requests* for the controller, which are queued until it is ready to execute them.

Figure 1.2 shows a simplified memory controller architecture. It is divided into a *front-end*, and a *back-end*. The front-end deals with the multi-ported nature of the controller, by deciding on the order in which requests from different clients are executed. It contains an (inter-client) *arbiter*, and *queues* for requests that are not executed immediately.

The back-end deals with the SDRAM protocol itself. Scheduled request are translated into *SDRAM commands* by a *command generator*. Once the commands are generated, they can be scheduled for execution on the SDRAM by the *command scheduler*. Although request-level arbitration and command-level scheduling are conceptually separate issues, they may be combined, depending on the controller implementation, although this naturally blurs the line between front-end and back-end.

Command scheduling is complex, since there are multiple timing constraints that have to be satisfied for each individual command to use the SDRAM correctly according to its specification. Each scheduling decision changes the memory state and thus the constraints that need to be taken into account for future decisions. Additionally, a scheduler may have to choose between multiple schedulable commands without a clear indication of the impact on performance and future scheduling options. This leads to a type of emergent behavior that is hard to predict, and thus memory performance is hard to bound in the general case; for many commercial controllers no analytical bounds can be provided. However, there are real-time memory controllers that do provide hard bounds on the time to serve all requests to assure client-level requirements are always satisfied, as will be discussed in Section 1.5.

In the next section, we will have a closer look at what the clients of a memory controller actually represent, and why they are growing in number.

# 1.3 CRAMMING MORE APPLICATIONS ONTO (POWER-CONSTRAINED) SOCS

Cost reduction through resource sharing is the main cause for the rise of the SoC, and their availability paved the way for a growing catalog of *applications* that use them. Applications might be purely software based, like those found in the app-store of the particular phone eco-system one subscribes to. However, we use "application" here in the broader sense of the word, and also include combinations of hardware and software that offer a certain chunk of functionality to the end user or to other applications through *sensors*, *actuators and communication links* [137].

It often possible to think of the clients of a memory controller as applications, although this does not always work. For example, an application may be distributed over multiple processors, each having its own connection to the controller, and hence *one* application might be represented by *multiple* clients. In our definition, applications cannot communicate or share data (if they do one of these things, they by definition are part of the same application).

The success of SoCs has enabled the use of high-performance multi-core architectures in consumer electronics, like mobile phones [128], tablets [12], wearables (smart

Figure 1.3: The Snapdragon 800 SoC [128].

watches, health trackers), home automation, and smart TVs [123], for example. Similarly, they find their way into cars, which contain a large number of *Electronic Control Units (ECUs)* [22], essentially SoCs with control applications. In all of these areas, we observe that the number of applications on a single SoC is increasing, as a logical consequence of growing SoC performance, the availability of the applications, and the drive towards cost reduction.

For example, consider mobile phones or tablets, which are simultaneously involved in handling a multitude of wireless protocols (like Wifi, Bluetooth, LTE, GPS and NFC), implemented in dedicated radio solutions or by using *Software-Defined Radio (SDR)* [116]. At the same time, they render graphics onto the screen, deal with encryption, while also running user apps and the underlying an operating system, all from the same SoC [93]. A high-end phone SoC is drawn in Figure 1.3, illustrating the various applications it supports. Wearables aspire towards the same feature set, although they are significantly more battery constrained. In general, battery capacity does not grow as quickly as the demand for processing power [138]. For mobile devices, the expected battery lifetime constrains the available power budget for the SoC and the SDRAM, and limiting power usage is hence an important design goal in this area.

One of the main challenges in the car industry is to merge the functionality of multiple ECUs, reducing costs in terms of materials, cabling and weight. Simultaneously, the trend towards (semi-) automated driving increases the required feature-set of cars. Automated driving heavily relies on sensing (vision, radar) and communication applications [46, 120, 142], for which custom SoCs are desired to effectively deal with all the required computation.

In conclusion, we see a growth of the number of applications per SoC across the board. A subset of those applications uses the SDRAM, and hence turn into clients of the memory controller. Unfortunately, the effects of sharing are not all positive, especially

when it involves a scarce resource like the SDRAM interface. In the next section, we discuss how applications are judged by their performance and why resource sharing can have a negative impact on it.

#### 1.4 PERFORMANCE

The evaluation of the success or failure of an application can be qualitative, but for the most part, it is quantified in terms of *performance*. Performance is an umbrella term describing the *rate* at which something of interest is produced or consumed, or the *amount of time* it takes to complete a specific operation [70]. Each instance of such rate or quantity of time is called a *performance metric*. For example, a video decoder's performance may be expressed as frames per second, or a control loop can process a specific number of input samples per millisecond. A *better or higher* performance almost universally refers to an *increase* of the rate or *reduction* of time, except when the quantity is consumed energy, in which case a smaller energy-time ratio is considered better.

Some performance metrics straight-forwardly apply to SDRAM controllers [131]. Bandwidth (bytes / second), response time (seconds / access) and power (joules / second) are the ones featured most prominently in this thesis. At first sight this might seem strange, since there are not many people who actually care how much bandwidth a certain application receives, or how much power the SDRAM consumes on its behalf. Instead, requirements are usually expressed at a higher level of abstraction, based on a specification of the functionality for user, e.g. "the video should play smoothly", or "the battery should last for at least 24 hours". Once refined in terms of performance metrics, requirements bound the allowed performance. Usually, requirements are one-sided (upper / lower) bounds, e.g. "at least 60 frames per second should be generated", or "at most 3 watts may be consumed." A guarantee bounds the actual performance. When the guaranteed performance equals or exceeds the required performance, then the requirement is satisfied.

# 1.4.1 Application requirements

A real-time application typically has a set of timing-related requirements it should satisfy [18, 131]. Such applications often have links to peripherals of the SoC, i.e. the interface to real world. For example, a SDR application might have to generate a response on the radio interface within a limited amount of time to correctly implement a communication protocol, or an adaptive cruise control system in a car might have to detect slowdowns of the surrounding traffic in time to avoid accidents.

The severity of the consequences of not meeting a deadline is usually expressed as a qualification on the real-time requirement, although the exact definitions vary. Using the definitions from [24, 131], we can distinguish *Hard real-time (HRT)* requirements and *Soft real-time requirements (SRT)*. HRT requirements relate to hard deadlines that can

not be missed without severe loss of functionality for the application's user. Sometimes such requirements are called *critical* or *safety critical*, in case the safety of the user is not guaranteed if the requirement is not satisfied. SRT requirements, on the other hand, may occasionally be missed, although this is still undesirable. In this thesis, we use *real-time* to refer to HRT, and we will not discuss SRT requirements. In the absence of real-time requirements, an application works on a *best-effort* basis.

Applications are not alone: instead, the increasing number of applications per SoC leads to an growing amount of interaction between them. This has an impact on the application's performance, and on how we deal with their requirements, as is discussed in the next sections.

# 1.4.2 Interference

An application that shares SoC resources is susceptible to *interference*, *i.e.* its (functional and temporal) behavior and that of other applications become interdependent. Only one application can use a shared resource at a time, leading to resource contention [104]. Other applications inevitably have to wait before they get access to the same resource, and hence experience *timing interference*. In an analogous manner, applications can experience *state interference*, which occurs when multiple applications change the state of a shared resource. As a straight-forward example, consider a memory in which one application overwrites the data of another application, changing its behavior in a potentially destructive manner.

Measures mitigating state interference for memory resources have been researched for quite some time [146], and solutions are available in the form of memory protection [13, 136] / management units [151] or data protection units. These modules effectively cordon off address ranges depending on the source of a memory access. Therefore, we focus on the timing aspect of interference in this thesis.

In most contexts, the word "interference" represents a negative effect, which is also the case here, since it changes the application's performance with respect to the case where there is no interference in an unpredictable way. In the following two sections, we describe two ways to qualify performance that are useful for real-time applications in the presence of interference.

# 1.4.3 Predictable performance

Predictability is a qualification of a performance metric of an application or hardware component [35] that (partially) specifies the assumptions that were made when this performance metric was derived. The predictable performance is a bound on all actual performances, assuming any possible initial condition, and including worst-case interference on shared resources without assumptions on the behavior of co-running applications [8]. When we refer to guaranteed or worst-case performance in this thesis, it is implied that

this performance is predictable. When a resource or methodology is predictable, then this means that predictable performance bounds can be derived for it or based on it.

Applications cannot communicate or share data (or else they would be part of the same application). If all resources an application uses provide predictable performance, then its worst-case performance is independent from other applications. The *verification* of the worst-case requirements of the application can then be done independently from other applications, i.e. it only has to consider the (predictable) hardware and the application itself. This reduces the complexity of this analysis compared to the non-predictable case, where all possible combinations of co-running applications also need to be factored in [121]. As such, it *enables incremental verification at a low relative cost, and reduces verification time.* Predictable performance enables model-based verification of requirements, using Dataflow [129], network calculus [34], or other traditional real-time approaches, for example. [53, 109, 118] outline what this process can entail.

# 1.4.4 Composable performance

Predictable performance is sufficient in cases where an application's verification is done based on a (formal) analysis of its worst-case requirements. However, there are cases where such an analysis is not possible, for example when a model of the application's timing behavior is not available. Such applications might be verified by simulation instead, essentially by executing them with a number of test inputs and assessing the results. Two issues complicate this work flow in multi-application environments: 1) the performance of tested applications can only be definitely assessed after they are integrated with their co-running applications, and 2) the performance in conjunction with *all possible combinations* of co-running applications has to be verified [86, 121]. If requirements are not satisfied, or if *any* application or the system setup is changed for other reasons, then the verification process has to be repeated, making the entire process circular [122].

These issues are avoided by systems offering composable performance, which means that the actual-case performance an application receives is not influenced by co-running applications [62, 115]. This definition is strict: intuitively it means that a deviation of a single cycle from the actual timing behavior the application expressed when running in isolation qualifies as being non-composable. Once an application receiving composable performance has been verified in isolation, it is guaranteed to also work correctly after integration, since its actual timing behavior during the verification is (exactly) the same as after integration. Composability is orthogonal to predictability, since it only implies independence of behavior, but by itself says nothing about the existence of worst-case bounds<sup>2</sup>.

<sup>2</sup> In practice, predictability is often used to provide composable performance [8].

# 1.5 REQUIREMENTS FOR SDRAM CONTROLLERS IN MODERN SOCS

In the previous sections, we discussed why the SDRAM is a scarce resource, and how it is shared amongst more and more applications with diverse requirements. We also discussed the complications interference introduces to the evaluation of real-time application performance. Based on these observations, we summarize the 5 main requirements on modern SDRAM controller in the context of this thesis as follows:

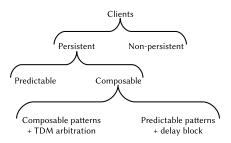

- Some applications have real-time requirements. To assure these requirements are met, the SDRAM controller must deliver predictable performance when the requirement verification is based on worst-case models, or composable performance, when the verification is based on simulation, or when a verification standard requires temporal isolation.

- 2. Some applications benefit from improved average-case (typical) performance, i.e. they can make use of all the resources the system can spare for them. Generally, an application's behavior or quality improves with additional resources, benefiting the user. Best-effort applications, i.e. applications without real-time requirements, generally fall within this category. Other examples include video decoding algorithms that support quality scaling [147], and user interfaces, for which higher responsiveness is generally better.

- 3. Applications are not active all the time. Instead, they can be transient, i.e. they only run in specific *use-cases*, in conjunction with a sub-set of the other applications the SoC supports. A memory controller should hence be able to efficiently deal with the changes in its set of clients.

- 4. SDRAM technology progresses quickly, and new generations are introduced every two to three years. An SDRAM controller architecture should hence be sufficiently flexible to handle the differences between the standards, such that it remains usable for a reasonable amount of time. The same requirement holds for the analysis on which its predictable performance guarantees are based. Ideally, a SoC should use the type of SDRAM that best fits its applications' requirements.

- 5. *The power budget is limited for (battery-powered) SoCs.* This requires a careful evaluation of how the SDRAM is used to minimize its power usage while still satisfying the remaining performance requirements.

Existing memory controllers come in a variety of forms, some of which are a better fit for these requirements than others. We distinguish three categories:

Real time, i.e. geared towards maximizing predictable performance. Real-time controllers are designed such that their guaranteed performance is maximal. The underlying assumption is that only the worst-case performance matters, and anything that cannot be guaranteed and analyzed is wasted effort.

- 2. Best effort, i.e. geared towards maximizing average-case (typical) performance. They are built according to the philosophy that mechanisms which positively impact the average performance are considered worthwhile, even if they negatively affect the worst case. They exploit knowledge that is only available at run time to make request-level or command-level scheduling decisions. As a result, they typically provide no useful analytical bounds on performance.

- 3. Mixed time-criticality<sup>3</sup>, i.e. balancing the needs of real-time and best-effort applications. Ideally, these controllers guarantee sufficient performance to satisfy the worst-case performance requirements, while maximizing the average-case performance for the applications.

When these descriptions are matched with the requirements we listed earlier, it is fairly obvious that best-effort controllers do not satisfy them, since they cannot guarantee (sufficient) performance to real-time applications. Complete isolation, as required for composability, is also practically impossible to achieve for these controllers, due to the complex interaction between the various average-case performance-improvement mechanisms, which inevitably leak state-information from one application to the other.

Real-time controllers, on the other hand, miss opportunities to improve the average-case performance that best-effort applications care about. It is hence not surprising that we consider a mixed-time-criticality controller the best fit for the requirements. Such a controller is built upon concepts that are known to be real-time analyzable, while selectively using techniques from best-effort controllers to improve the average case.

# 1.6 PROBLEM STATEMENT AND CONTRIBUTIONS

The high-level question we answer in this thesis is:

How should a mixed-time-criticality SDRAM controller be constructed that 1) provides predictable and composable performance to its real-time applications, both in terms of bandwidth, response time, and potentially within a limited power budget, while exploiting opportunities to improve the average-case performance for best-effort applications, 2) is flexible, both in terms of architecture and worst-case performance analysis, such that it can be used for the various available SDRAM generations, and allows for comparisons between them, and 3) retains these properties in the presence of transient applications, i.e. when it is used in multiple use-cases.

Existing works on real-time SDRAM controllers focus on providing predictable performance, and some extend this with composable performance. Mixed-time-criticality controllers improve average-case performance while retaining predictability. However, their scopes and capabilities are limited in certain areas. We highlight these issues in

<sup>3</sup> We focus on the diversity of timing requirements this thesis. In contrast, the broader term *mixed criticality* is typically used in works that deal with differences in certification requirements, including fault tolerance concerns, and varying degrees of pessimism in WCET estimations based on the required level of certainty [141].

the following sections, and connect them to the contributions in this thesis that address them. A graphical representation of the mapping of requirements from the previous section to contributions and chapters is shown in Figure 1.4. A detailed positioning of this thesis with respect to related work is given in Chapter 8.

# 1.6.1 Multi-generation power-aware command scheduling

The rapid development of SDRAM technology means multiple SDRAM generations are at a system designer's disposal at any given time. To select the right memory for a SoC that support real-time applications, worst-case performance bounds of the memories need to be available and comparable, to satisfy Requirements 1 and 4. Existing real-time controllers and command scheduling algorithms are limited to a single memory device, or one or two memory generations, and ignore the impact of the command scheduling algorithm on the SDRAM power usage, even though this is an important design constraint for (battery-powered) embedded systems [138], as identified by Requirement 5.

To address these issues, we provide an abstraction that allows us to write down an SDRAM command scheduling algorithm in a general fashion, i.e. without targeting one specific memory device or generation. Using this abstraction, we introduce a generation-agnostic command scheduling heuristic (Chapter 4). The schedules it produces allows us to bound the SDRAM's performance. The quality of the heuristic is evaluated through a comparison with optimal solutions generated by an Integer Linear Programming (ILP) formulation. We also provide a simple transformation for these schedules to turn the memory controller into a composable resource with negligible impact on the performance bounds.

The command scheduling heuristic is parameterized, such that worst-case performance in terms of bandwidth and response time can be traded against worst-case power, which is derived based on the power model of [31]. We apply the heuristic to twelve memory devices from six different memory generations, and plot this trade-off space, effectively providing an overview of worst-case power/performance trade-offs across generations (Chapter 5).

# 1.6.2 Improving average-case performance without affecting worst-case performance

Opportunities to improve (non-guaranteed) performance in real-time controllers are generally ignored, even though they could have a positive impact on both the application's performance and the power usage. Improving average-case performance and reducing power consumption is desirable, as mentioned in Requirements 2 and 5. Locality of reference influences how long it takes to read or write a unit of data. Memory controllers attempting to exploit locality across requests use an *open-page policy*, while those that do not use a *close-page policy* [119]. Open-page policies have only recently found their way into a few real-time and mixed time-criticality controllers, al-

Figure 1.4: Mapping of requirements to contributions and chapters.

though they require special measures (bank privatization, explained in Chapter 8) to avoid worst-case performance reduction.

In this thesis, we introduce a conservative open-page policy that improves the average-case performance without compromising on worst-case guarantees (Chapter 6). It exploits locality of reference to reduce the response time of requests, like any open-page policy would. However, it only deviates from how a close-page policy would act when the response time is guaranteed to be smaller while doing so.

# 1.6.3 Reconfigurable architecture

Existing controllers typically configure the behavior of the request-level arbiter and the command scheduler only once, when the SoC is booted. Therefore, this configuration has to cover all use-cases. Adapting the controller's behavior per use-case at run-time, to adapt to the arrival or departure of transient applications, is not considered, contradicting Requirement 3. If existing controllers would be reconfigured at run-time, they provide no bounds on performance to applications that remain active during these use-case transitions, which is unacceptable for real-time applications according to Requirement 1. Given how the number of applications per SoC is growing, it becomes paramount to specialize the controller configuration to the requirements of the active application set, in order to use the SDRAM in the most efficient manner.

To address this, we introduce a reconfigurable SDRAM controller architecture template (Chapter 3), and a proof-of-concept implementation, integrated in a predictable and composable SoC. The performance that is provided to each controller port is characterized by a worst-case analysis, and can be changed at run-time through reconfiguration. This allows for specialization of the controller on a per use-case basis, making it easier to swap transient applications in and out without having to (over) dimension for the most challenging super-set of requirements. The rules that have to be respected to retain

Figure 1.5: Overview of chapters.

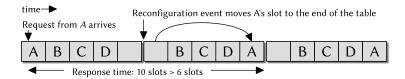

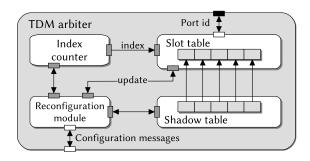

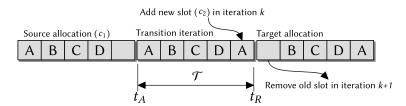

predictability or composability for (real-time) applications that are active during reconfiguration are discussed in Chapter 7. We demonstrate how to implement these rules for a *Time-Division Multiplexing (TDM)* arbiter, and prove that our reconfiguration protocols are safe.

### 1.7 THESIS OUTLINE

This remainder of this thesis is structured as follows. Chapter 2 introduces the necessary background information on SDRAM memories and SDRAM controllers. Chapter 3 shows the architecture template and the worst-case analysis of the memory controller we propose, and looks at one concrete instance of the template in more detail. Chapter 4 discusses how both predictable and composable configurations for the command scheduler in this memory controller can be generated. The used algorithms are transparently applicable to all contemporary SDRAM generations through the introduction of a simple abstraction layer. In Chapter 5, we provide an overview of the worst-case power and performance trade-offs in twelve memory devices in six different memory generations as a function of the different command scheduler parameters. Chapter 6 introduces a mechanism that improves average-case performance without sacrificing worst-case guarantees. Chapter 7 then shows when and how the various configurable components in the memory controller can be reconfigured without violating predictable or composable performance bounds. Figure 1.5 shows the relations between Chapter 3-7. Finally, Chapter 8 relates this thesis to the state of the art, and we end with conclusions and future work in Chapter 9.

Get your facts first, and then you can distort them as much as you please. — Mark Twain, From sea to sea: letters of travel, 1899

2

## BACKGROUND AND TERMINOLOGY

The purpose of this chapter is to set the stage on which the rest of this thesis plays out. Contrary to the remaining chapters, we try our best to not introduce novel ideas here. Instead, we describe the technology that we work with, in the form of the SDRAM chips that external companies produce for us (and the rest of the world) in Section 2.1.

The same SDRAM chips are used by everyone, so it is not surprising that most memory controllers, i.e. the interfaces that interact with these chips, have at least the same high-level structure, as introduced earlier in Section 1.2. For the sake of efficiency, the proverbial wheel tends to be invented only a few times before the interested community settles for a design that works in most cases. Further improvements are driven by the needs of specific application areas and the gradual evolution of the surrounding actors and requirements. This thesis focuses on the area of mixed-time-criticality systems, and uses an existing SDRAM controller for real-time systems, the *pattern-based controller* [3], as its starting point. The properties of this controller are introduced in Section 2.2.

Section 2.3 contains a brief introduction on burst grouping, which can be intuitively understood as a sort of batch processing. In the context of SDRAMs it means that groups of bursts that are relatively similar can be processed more quickly than those that are relatively different. Most memory controllers try to achieve some degree of burst grouping. We parameterize this concept, such that we can use it in later chapters to characterize the behavior of a memory command scheduler.

The advantage of not starting from scratch is that existing analysis methods are more or less applicable to the derived work, or at most require minor changes. Section 2.4 briefly introduces various existing approaches for dealing with *refresh*, which is a (mandatory) recurring operation required to retain data in an SDRAM. We end this chapter with Section 2.5, containing an introduction of the abstraction method on which the worst-case performance analysis in Chapter 3 is based.

#### 2.1 SDRAM

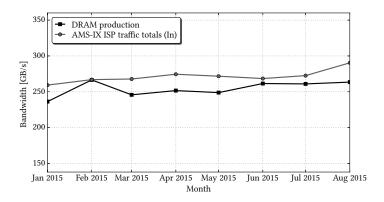

SDRAM is an extremely popular type of memory. DRAMExchange (a market analyst) reports that in February 2015 alone, 2.4 billion 2 gibibit (2<sup>30</sup>) equivalent units were produced worldwide [42], for a total *capacity* of 5.16 exabits. This amounts to a production rate of 267 GB/s<sup>1</sup>, a relatively modest "bandwidth" that about 100 combined contemporary *SDRAM devices* (single chips) could easily deliver, as we later show in Chapter 5.

SDRAM is volatile and used as temporary data storage, similarly to caches or *Static Random-Access Memory (SRAM)* memories. It only stores data as long as power is provided to it. In terms of area and power consumption it is cheaper than SRAM, since it requires only a single transistor-capacitor pair to store a bit. This efficiency makes it feasible to store gigabytes of data in SDRAM, while SRAM and caches are limited to capacities in the order of megabytes.

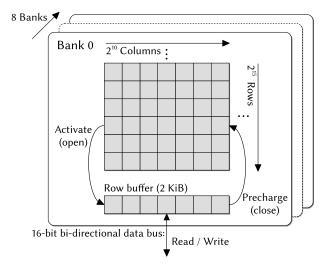

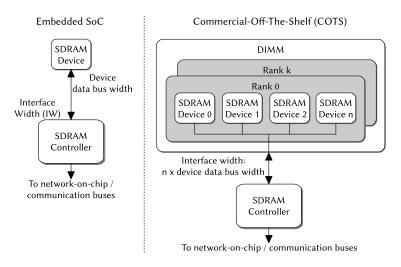

Many generations of SDRAM have been developed since it was invented by Robert Dennard in 1967 [38], but most of their characteristics are similar. SDRAM devices contain a hierarchically structured storage array [70]. A schematic view on a generic SDRAM architecture is shown in Figure 2.1. Each device consists of typically 8 or 16 banks that can work in parallel, but share a command, address, and data bus. Therefore, only one command can be sent to one bank at a time, but commands can take multiple cycles to complete, and the execution of commands on different banks can happen in a parallel (pipelined) fashion. A bank consists of a memory array, divided into rows, each row containing a certain number of columns. A column is as wide as the number of pins on the memory device's data bus, and hence only one bank may drive the data pins at a time. Typically, there are 2<sup>10</sup> or 2<sup>11</sup> columns per row, and about 2<sup>14</sup> to 2<sup>16</sup> rows per column, depending on the capacity of the device and its data bus width. SDRAMs with 4, 8, 16, and 32-bit data buses exist. The data bus is bidirectional, i.e. the same pins are used for both reading and writing. Some SDRAMs are Single Data Rate (SDR), transporting valid data on the rising clock edges only. However, all memory generations we consider in this thesis use a Double Data Rate (DDR), i.e. they transfer one data word (which is as wide as the data bus) on both the rising and the falling edge of the clock.

The name of an SDRAM device starts with its generation name, followed by its data rate in MHz, so for example DDR3-1600 refers to a DDR3 memory with a 800 MHz command clock frequency. In this thesis, we refer to the generation name as the *SDRAM type*. The width of the data bus is often indicated by a postfixed 'x' followed by the width in bits, e.g. an LPDDR2-1066x32 has a 32-bit data bus. The capacity of SDRAM devices is usually expressed in multiples of Mib (2<sup>20</sup> bits) or Gib (2<sup>30</sup> bits), although the 'i' is commonly dropped in datasheets. Bandwidths in this thesis use SI prefixes. For example, fully read-

<sup>2402·10&</sup>lt;sup>6</sup>·2·2<sup>30</sup>/8 bytes 2419·10<sup>6</sup>·2·2<sup>30</sup>/8 bytes Incidentally, this is only 0.15% less than the traffic flowing into the Amsterdam Internet Exchange (AMS-IX) in the same month [11] (645772 TB). The (live) construction of an SDRAM cache of a significant portion the Internet traffic was hence possible, although it might have been the last month this was feasible, given the growth trend of AMS-IX traffic. The power footprint of this Internet cache might be problematic though.

Figure 2.1: Schematic view on the architecture of an SDRAM device with the dimensions of a 512 MiB DDR3-1600 chip (see Appendix B).

ing a 512 MiB SDRAM with a bandwidth of 512 MB/s takes about 1.049 seconds (Gi is 7.3% larger than G).

### 2.1.1 SDRAM commands

An SDRAM can be instructed to perform certain actions by giving it *commands*. There are six main<sup>2</sup> SDRAM commands: 1) *Activate* (*ACT*), 2) *Read* (*RD*), 3) *Write* (*WR*), 4) *Precharge* (*PRE*), 5) *Refresh* (*REF*) and 6) *No operation* (*NOP*). The *command bus* of a DDR3 SDRAM consists of 4 wires: *row address strobe* (*RAS*), *column address strobe* (*CAS*), *chip select* (*CS*) and *write enable* (*WE*). The combination of these wires forms a (4-bit) command, which is clocked into the SDRAM. The other generations use a similar interface, although some reuse parts of the address bus as command wires. The commands work as follows:

- An ACT command opens a row in a bank, and makes it available for subsequent RD and WR commands by moving its content to the *row buffer* of the bank. An activate command is accompanied by the *address of the row* that should be opened.

- Each RD or WR command results in a *burst* of data, consisting of a range of columns from the active row. One burst occupies the data bus for multiple consecutive cycles. The number of words per RD or WR is called the *Burst Length (BL)*. Across contemporary memory generations the commonly supported value for BL is 8 [73–78]. The

<sup>2</sup> The remaining commands relate to power-down modes and setting up mode registers.

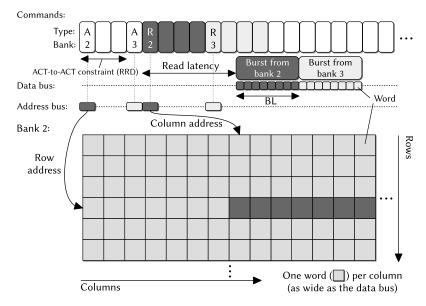

Figure 2.2: High-level SDRAM operation. The activation of bank 3 happens in parallel with the read command to bank 2. Data bursts of different banks are serialized, since the data bus is shared across banks. The two cycles between A2 and A3 are the result of the ACT-to-ACT timing constraint (RRD).

memory generations we consider all have a DDR, transporting data on both the rising and falling clock edge. Therefore, it takes only BL/2 clock cycles to transfer a burst. A RD or WR command is accompanied by the *address of the first column of the burst*, which generally must start at a multiple of the burst length. Data is available on the data bus after the associated *read or write latency* after the RD or WR has passed. The latencies for RD and WR commands may be different, but tend to be of the same order of magnitude (see Table 2.1).

- The PRE command closes a row, i.e. it stores the contents of the row buffer in the memory array, allowing for another row to be subsequently opened. Only one row per bank can be open at a time. An optional *auto-precharge* flag can be added to RD and WR commands, such that the associated row is closed as soon as the read or write is completed. A RD or WR with auto-precharge can be regarded as a regular RD or WR, followed by a PRE command from a timing perspective. The difference is that the precharge does not require the command bus. This frees a slot in the command schedule, which may be used for other commands.

- SDRAM is volatile, because the transistor-capacitor pairs it uses to store bits lose their charge over time. To avoid data loss, the memory must be *refreshed* periodically by

issuing a REF command. The required refresh command interval depends on the operating temperature and the memory size, and ranges between approximately 1  $\mu s$  and 10  $\mu s$  [73–78]. In this thesis, we assume the SDRAM always works within a fixed temperature range, and that the refresh interval is set to an appropriate (fixed) value.

• Finally, the NOP command does nothing. It is used to fill the time, e.g. while waiting for timing constraints (see Section 2.1.2) to be resolved. Some standards also support a *deselect (DES)* command that behaves similarly to a NOP, while others only have DES commands. We do not require a distinction between NOP and DES commands in this thesis, and always refer to unused command bus cycles as NOPs.

The scheduling of PRE and ACT commands is determined by the memory controllers' page policy. Memory controllers that leave a row open after a request is completed use an open-page policy, while those that close (precharge) it as soon as possible use a close-page policy [119]. A request that does not require an activate command, because the row it accesses is still open, is called a row hit or page hit. Requests that target a closed row are called a row miss or page miss. We return to discuss page-policies in Chapter 6.

The relation between the command, address and data bus is shown in Figure 2.2. In figures, we often show traces of commands as a series of rectangular blocks, like at the top of Figure 2.2 for example. Each block in this series represents a command. A block may contain a letter representing the command type, and a number, representing the bank to which the command is directed. We abbreviate ACT, PRE, RD and WR by A, P, R, and W, respectively, and encode NOPs as empty boxes.

# 2.1.2 Timings and timing constraints

Vendors of SDRAM devices characterize their memory chips by specifying their *timings*. Timings define the maximum time between internal operations in the memory, usually relating to the (analog) propagation delay between distinct components in the SDRAM. *Timing constraints* are built as mathematical expressions from these timings, and they define the minimum time between pairs of commands based on the state of the memory, which in turn is a consequence of earlier executed commands. An SDRAM controller has to satisfy all timing constraints to operate correctly. A detailed explanation of what each timing represents for a specific memory generation is found in the standards [73–78]. For the purpose of this thesis, these details are less important, since we mostly consider the SDRAM as a black box that we merely have to use according to its interface specification. Appendix B shows the numerical values associated with the timings of a range of SDRAM devices, while Chapter 4 provides a detailed view on the relation between timings and timing constraints. However, we will sometimes refer to timings before Chapter 4 to point out trends, and hence provide some early intuition on their

| Timing       | Related constraint            | Approximate value                 |  |

|--------------|-------------------------------|-----------------------------------|--|

| RC           | ACT-to-ACT, same bank         | 45 - 60 ns                        |  |

| RAS          | ACT-to-PRE, same bank         | 70% of RC, 35 ns                  |  |

| RCD          | ACT-to-RD/WR in the same bank | 30% of RC, 15 ns                  |  |

| RP           | PRE-to-ACT, same bank         | 30% of RC, 15 ns                  |  |

| RRD          | ACT-to-ACT, same device       | 25% - 30% of RC, 12.5 ns          |  |

| RFC          | REF-to-ACT, same device       | 1-5 times RC, depends on capacity |  |

| RL, WL or CL | RD/WR-to-data                 | 30% of RC, 15 ns                  |  |

| FAW          | Four Activate Window          | 85% of RC (50% for DDR4)          |  |

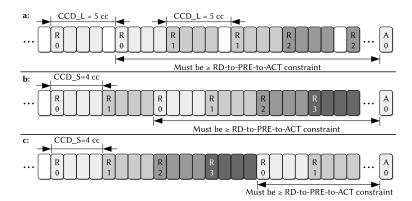

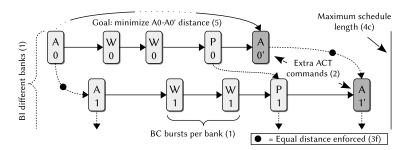

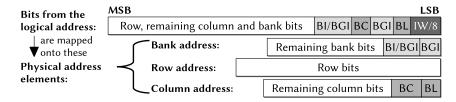

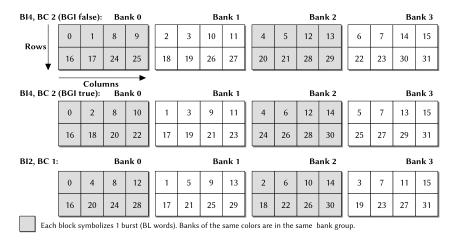

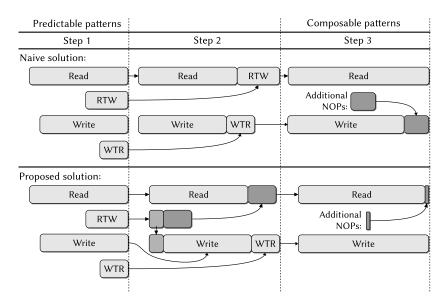

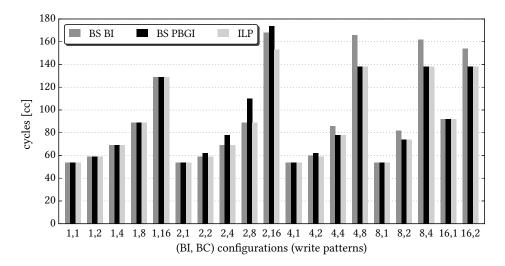

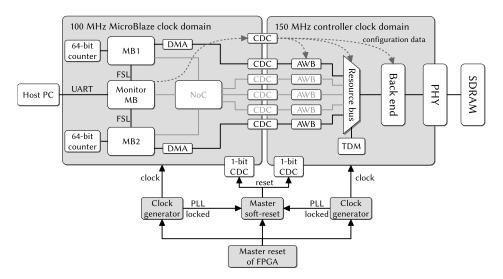

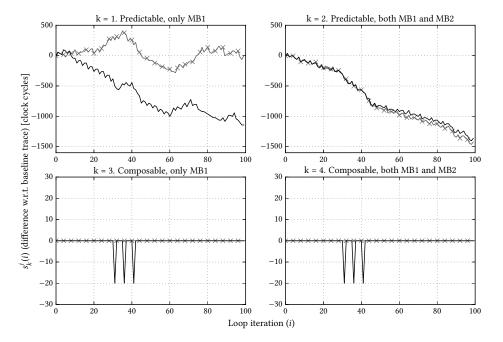

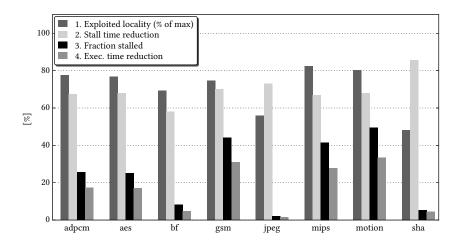

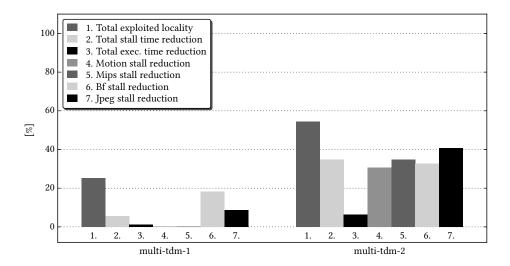

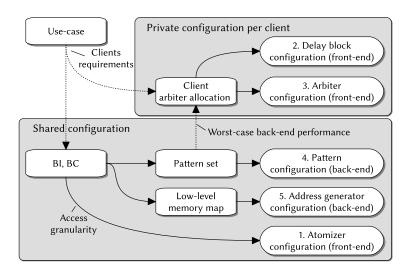

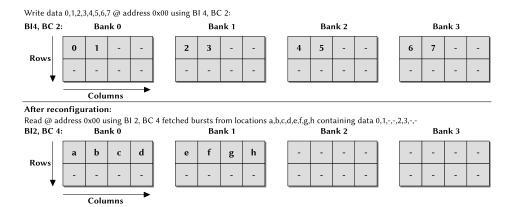

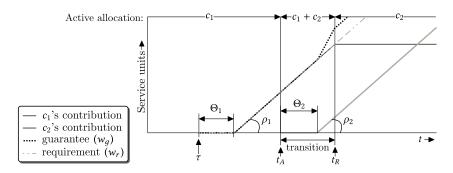

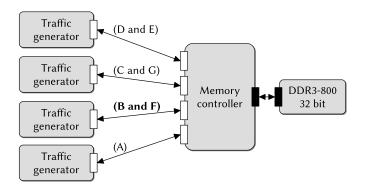

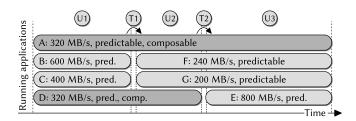

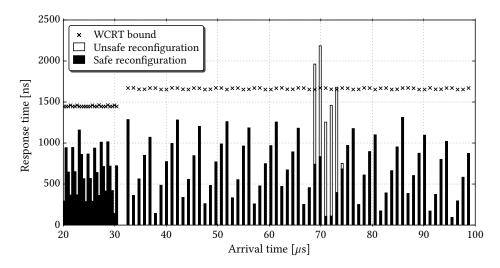

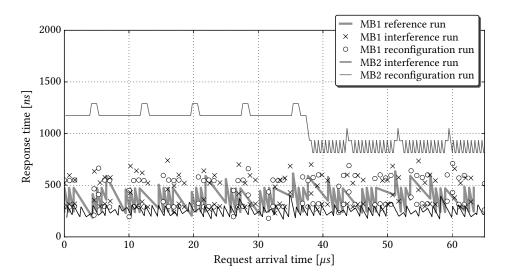

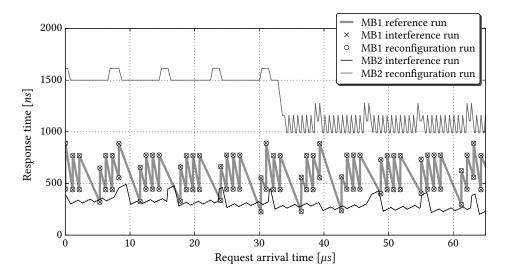

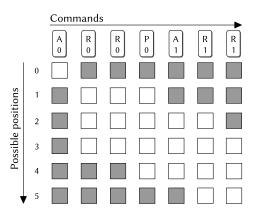

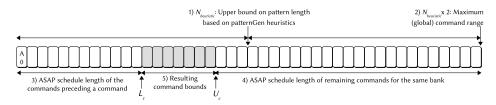

Table 2.1: Approximate values of SDRAM timings relative to RC.