# GADL : a gate array description language

*Citation for published version (APA):* Lippens, P. E. R., & Slenter, A. G. J. (1987). *GADL : a gate array description language.* (EUT report. E, Fac. of Electrical Engineering; Vol. 87-E-165). Technische Universiteit Eindhoven.

Document status and date: Published: 01/01/1987

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Eindhoven University of Technology Netherlands

Department of Electrical Engineering

# GADL: A Gate Array Description Language

by P.E.R. Lippens and A.G.J. Slenter

EUT Report 87-E-165 ISBN 90-6144-165-X ISSN 0167-9708

January 1987

Eindhoven University of Technology Research Reports EINDHOVEN UNIVERSITY OF TECHNOLOGY

> Department of Electrical Engineering Eindhoven The Netherlands

GADL A GATE ARRAY DESCRIPTION LANGUAGE

bу

P.E.R. Lippens and A.G.J. Slenter

EUT Report 87-E-165 ISBN 90-6144-165-X ISSN 0167-9708 Coden: TEUEDE

Eindhoven January 1987

| COOPERATIVE DEVELOPMENT OF AN INTEGRATED, HIERARCHICAL                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| AND MULTIVIEW VLSI-DESIGN SYSTEM WITH DISTRIBUTED                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| MANAGEMENT ON WORKSTATIONS.                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| (Multiview VLSI-design System ICD)                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| code: 991                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| DELIVERABLE                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Report on activities: 5.2.C : Cell generation schemes.<br>Developing or studying<br>cell architectures for<br>various CMOS families.<br>5.3.A : Generating layouts for<br>random logic.<br>5.3.B : Implementation of one<br>cell generation scheme<br>of some CMOS family.                  |  |  |  |  |  |  |  |  |  |

| CADL : A gate array description language.<br>Abstract:<br>This report describes a new way to map digital networks onto<br>rate array images                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| gate array images.<br>A language is defined to describe gate array images, design<br>rules for the wiring and arbitrary specified macros from<br>image dependent libraries. A data base is generated by<br>compliing the description of a gate array family in terms of<br>the above items. |  |  |  |  |  |  |  |  |  |

| Place and route software is automatically conditioned to<br>implement arbitrary specifications of a digital system in<br>terms of a netlist.<br>The performance of the system is demonstrated for various<br>practical situations.                                                          |  |  |  |  |  |  |  |  |  |

| deliverable code: WP 5, task: 5.2, activity: C;<br>task: 5.3, activities: A end B.                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| date: 23 - 12 - 1986                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| partner: Eindhoven University of Technology                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| authors: P.E.R. Lippens, A.G.J Slenter                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

This report was accepted as a M.Sc. Thesis of P.E.R. Lippens by Prof. Dr.-Ing. J.A.G. Jess, Automatic System Design Group, Department of Electrical Engineering, Eindhoven University of Technology. The work was performed in the time from November 1985 to December 1986 and was supervised by ir. A.G.J. Slenter.

CIP- GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Lippens, P.E.R.

GADL - a gate array description language / by P.E.R. Lippens and A.G.J. Slenter. -Eindhoven: University of Technology. - Fig., tab. - (Eindhoven University of Technology research reports / Department of Electrical Engineering, ISSN 0167-9708; 87-E-165) Met lit. opg., reg. ISBN 90-6144-165-X SISO 664.3 UDC 621.382:681.3.06 NUGI 832 Trefw.: elektronische schakelingen; computer aided design.

## CONTENTS

| 1. | INTRODUCTION                                            |    |  |  |  |  |  |  |  |  |  |  |  |

|----|---------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

| 2. | GATE ARRAY FEATURES                                     |    |  |  |  |  |  |  |  |  |  |  |  |

| 3. | SYSTEM OVERVIEW                                         |    |  |  |  |  |  |  |  |  |  |  |  |

| 4. | ROUTING DATA STRUCTURE 1                                |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.1 The position of wires, vias, wire blockades and via |    |  |  |  |  |  |  |  |  |  |  |  |

|    | blockades                                               | 11 |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.2 Design rules                                        | 12 |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.3 Leerouter cost function                             | 14 |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.4 Macro stamp information                             | 15 |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.5 Implementation considerations                       | 16 |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.6 Summary                                             | 19 |  |  |  |  |  |  |  |  |  |  |  |

| 5. | LIBRARY STRUCTURES                                      | 21 |  |  |  |  |  |  |  |  |  |  |  |

| 6. | THE GADL LANGUAGE                                       | 23 |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.1 Goals of GADL 23                                    |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.2 An outline of GADL 22                               |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.2.1 Image definition item 25                          |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.2.2 Range definition item 34                          |    |  |  |  |  |  |  |  |  |  |  |  |

| •  | 6.2.3 Design rule definition item 35                    |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.2.4 Cost function item 37                             |    |  |  |  |  |  |  |  |  |  |  |  |

| 7. | THE GADL COMPILER                                       | 39 |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.1 Image compilation                                   | 39 |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.1.1 Layer reduction 39                                |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.1.2 Data structure 40                                 |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.1.3 Routines 44                                       |    |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.2 Design rule compilation                             | 61 |  |  |  |  |  |  |  |  |  |  |  |

i

|    | 7.2.1       | Data structure 61                   |    |

|----|-------------|-------------------------------------|----|

|    | 7.2.2       | Routines 63                         |    |

|    | 7.3 Cost f  | unction compilation                 | 70 |

|    | 7.3.1       | Data structure 70                   |    |

|    | 7.3.2       | Routines 71                         |    |

| 8. | DIAGNOSTICS | AND PERFORMANCE                     | 72 |

| 9. | CONCLUSIONS | AND ACKNOWLEDGEMENT                 | 74 |

|    | Appendix A: | Vertex Data Structure               | 75 |

|    | Appendix B: | Syntax of GADL                      | 76 |

|    | Appendix C: | Algorithm Description Meta Language | 83 |

|    | Appendix D: | Ouput Formats                       | 86 |

|    | Appendix E: | Examples                            | 88 |

|    | REFERENCES. |                                     | 94 |

### LIST OF FIGURES

| Figure 1.  | Two typical gate array structures: a) island structure, |    |

|------------|---------------------------------------------------------|----|

|            | b) row structure                                        | 3  |

| Figure 2.  | Channel cells                                           | 4  |

| Figure 3.  | Gate cells                                              | 4  |

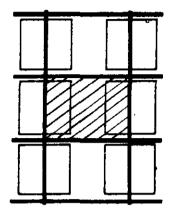

| Figure 4.  | Gridding of a gate array part                           | 5  |

| Figure 5.  | System overview                                         | 7  |

| Figure 6.  | Global cell choice                                      | 9  |

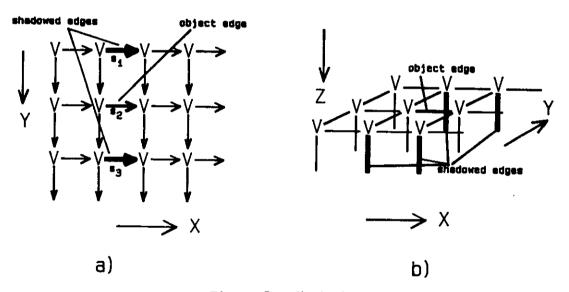

| Figure 7.  | Shadowing                                               | 13 |

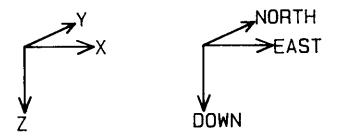

| Figure 8.  | Compass-card                                            | 16 |

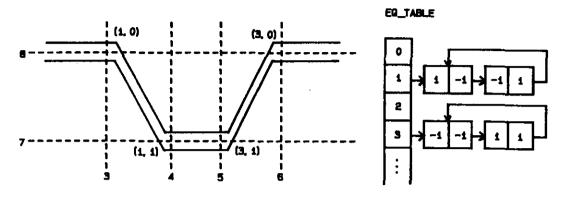

| Figure 9.  | Equivalent points                                       | 17 |

| Figure 10. | Design rule table                                       | 18 |

| Figure 11. | Cost table                                              | 19 |

| Figure 12. | Macro library structure                                 | 21 |

| Figure 13. | The directory structure                                 | 24 |

- v -

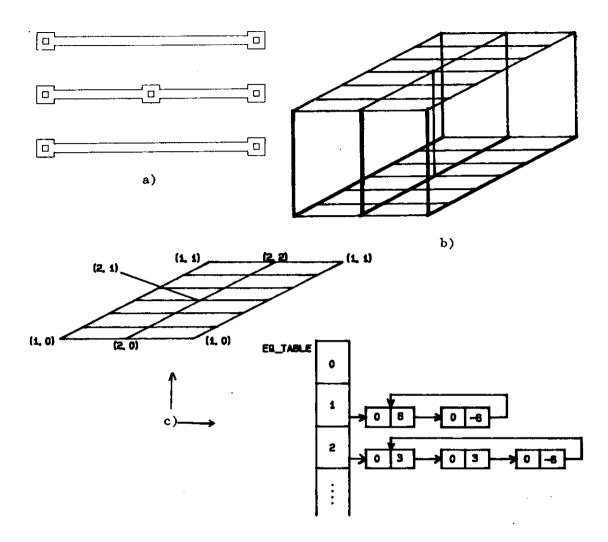

| Figure 1 |     | Layer reduction. a) geometry. b) grid model. c) reduced grid model | 40 |

|----------|-----|--------------------------------------------------------------------|----|

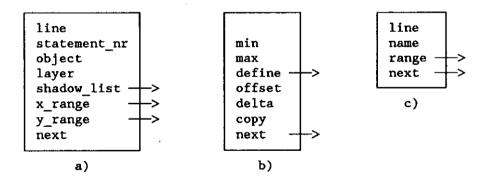

| Figure 1 | 5.  | Structures: a) MODULE b) MACRO                                     | 41 |

| Figure 1 | .6. | The EQ_ARRAY                                                       | 43 |

| Figure 1 | .7. | Coordinate lists                                                   | 45 |

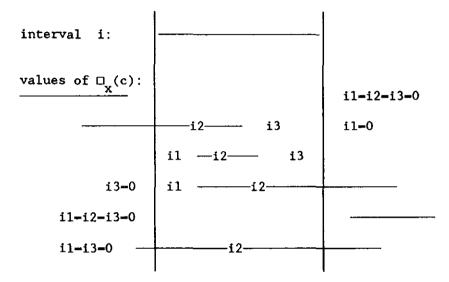

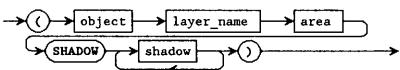

| Figure 1 | 18. | Structures: a) DRL_STATEMENT b) RANGE c) DEFINE                    | 61 |

| Figure 1 | 19. | Interval splitting                                                 | 68 |

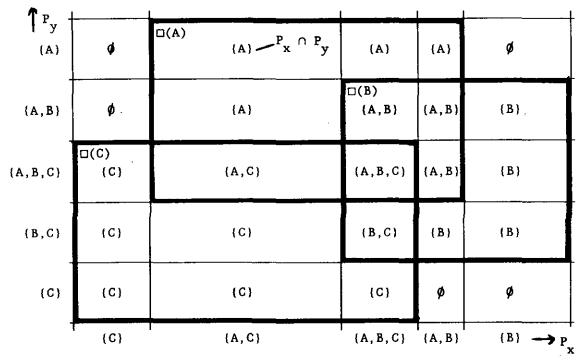

| Figure 2 | 20. | Result of first part of algorithm A2                               | 69 |

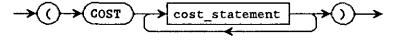

| Figure 2 | 21. | Structure COST_STATEMENT                                           | 70 |

| Figure 2 | 22. | Performance of the program                                         | 72 |

- vi -

- introduction -

#### 1. INTRODUCTION

Gate arrays, otherwise known as logic arrays or cellular arrays, are a type of programmable or semi-custom semiconductor components made possible by the rapid advances in integrated circuit design techniques and manufacturing technology. Where an electronic system may be implemented using TTL or CMOS logic, a gate array can typically replace twenty to fifty SSI/MSI packages and effect considerable cost, weight, size and power savings in the end equipment.

The concept of having a fixed base pattern of logic gates on a silicon integrated circuit (IC) which is then programmed or "wired up" by customised metal patterns is not new. It was first proposed in the mid-1960s and used by several companies where the development cost of custom IC design were not justified for the relative low volumes of each variant desired. It is this trade-off of development cost, unit cost and prototyping time that is addressed by the use of gate arrays and other types of programmable components, notably microprocessors. Such components are called semi-custom integrated circuits as they are part standard (the base diffusion) and part custom (usually the interconnect and contacts). The term semi-custom is not usually applied to microprocessors, which are personalised or programmed by the ROM program mask, although conceptually they too are semi-custom. Another class of semi-custom products are cell based designs where blocks of predesigned elements are drawn from a library, and a total design requiring unique masks for all processing levels, instead of just a few, is generated.

This report only regards the design automation of the interconnect masks of gate arrays. Gate arrays are designed in many technologies (TTL,  $I^2L$ , CMOS, NMOS). CAD systems for gate arrays have to face new problems caused by the rapid growing of the gate array market. The GAS gate array design system developed at the Eindhoven University of Technology claims to be very flexible with regard to the gate array type. It is designed for small and medium sized companies which have to deal with a large and pluriformly organised set of vendors and foundries, predominantly located in the US. To establish the flexibility an entry in the design system is

- introduction -

created, where structure and properties of a gate array can be described in a special for this purpose developed language: GADŁ (gate array description language). In GADL it is possible to describe the gate array structure, its design rules, the set of macro stamps and the properties of a cost function (used to guide the Leerouter) in an easy way. The main part of the report consists of a description of GADL (chapter 5) and a description of the GADL compiler (chapter 6).

#### 2. GATE ARRAY FEATURES

When we look at gate arrays, there are a few things they have in common. The most consist of a regular arrangement of basic cells (cellular array). Each cell can be personalised by metalisation to perform logic functions like NAND, OR, FLIPFLOP, etc.. These cells, usually referred to as function boxes, active areas etc., are separated by routing space, usually referred to as channels. Channels can be divided into basic cells called junction boxes, connection boxes or channel cells.

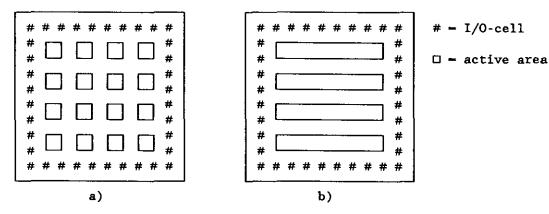

The area formed by regular repetition of function and junction boxes is called the core of a gate array. Around the core, a number of bonding pads and I/O-buffers is located. These I/O cells don't offer much space for routing and therefor are not interesting for us except the terminal positions. Figure 1 shows two typical gate array structures.

Let us now take a closer look at the junction and function boxes. A channel cell can vary in complexity from just some orthogonal tracks for intercellular connections to a more complex structure with prefabricated connection paths (cross unders or underpasses) with fixed or programmable contacts to the metal layer(s) above (figure 2). The gate cells of gate arrays are relatively more complex since many trade-offs have been made in these cell design. A gate cell consists of a number of discrete components with which one can build a set of useful functions in a

### - gate array features -

|       | [ |    | 0         |      |            |                  | o         |                     |           |              |     |                | 0         |                   |

|-------|---|----|-----------|------|------------|------------------|-----------|---------------------|-----------|--------------|-----|----------------|-----------|-------------------|

| 33    | 2 | 23 | $\Box$    | 12   | $^{\circ}$ | 15.5             | $\Box$    | 4.                  |           | $\mathbf{C}$ | r-  | 73.            | $\sim$    |                   |

| 1231  | 2 | 32 |           | 19   | n          | $\mathbb{C}^{n}$ | $\Box$    | $\mathcal{X}^{(i)}$ | $\square$ |              | i.  | 12             | $\square$ | $\mathcal{T}^{*}$ |

| 121   | 2 |    | 0         |      | 0          | $\sim$           | $\square$ |                     |           | 12           |     | 12             |           |                   |

|       |   |    |           | 12   |            |                  | ·         |                     |           |              |     | 3 <sup>1</sup> |           |                   |

| 1.1.1 | - |    | 0         | . Či | r 1        |                  | ?         | 1,-                 |           | .0           | ι., |                |           | 1.1               |

|       | - | 40 | <u>نا</u> |      |            |                  | -         | 4                   | i;        |              | l., | ं              |           |                   |

| 理道    | 3 | HI |           |      |            |                  | $\Box$    |                     |           |              |     |                | $\square$ |                   |

Figure 2. Channel cells.

|                                       | <u> </u>            |

|---------------------------------------|---------------------|

|                                       |                     |

| والمستحصيص الهجري والمستحصيص والمستحص |                     |

|                                       | <u>.</u>            |

|                                       | <u> </u>            |

|                                       | <b>-</b> , <b>U</b> |

|                                       | TI,                 |

|                                       |                     |

|                                       |                     |

|                                       | - <b>D</b> j        |

|                                       | T                   |

|                                       | 0                   |

Figure 3. Gate cells.

particular technology. These components enable the function to be built up to give the best compromise in terms of performance. The basic design will support the use of a number of cells to form a more complex function. A cell includes the active and passive components necessary to build any of the required functions with the greatest flexibility in programmability.

Depending on design philosophy, process technology, I/O capacities and, most importantly, routability of the gate array, gate cells may (and do) have quite different structures and properties. However, a gate cell always has to be:

- Programmable (intraconnectable)

- Interconnectable

- Repeatable

A few different gate cells are given in figure 3.

Although the gate arrays have different structures and are designed in different technologies, the following attributes the most have in common, even for those gate arrays which have not gate cells and routing channels explicitly:

- The intercellular connections can only be made vertically and/or horizontally on certain pre-defined tracks.

- When non-orthogonal wires are permitted in gate arrays, they are either provided by gate array foundries or routed manually.

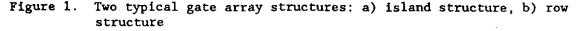

This observation leads to the conclusion that all, for routing interesting, features can be mapped onto a three dimensional grid. Figure 4 gives an example of the "gridding" of a part of a gate array.

Figure 4. Gridding of a gate array part.

Each coordinate in the third dimension represents a layer, where a layer corresponds (in general) with two physical masks: an interconnection mask

- gate array features -

and a contact (hole) mask.

The grid representation of gate arrays will serve as a basis for the routing data structure.

#### 3. SYSTEM OVERVIEW

÷.,

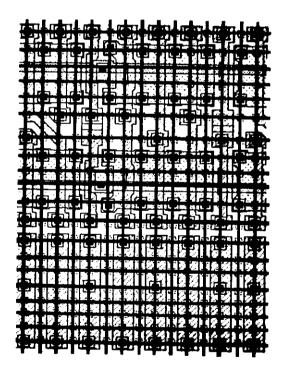

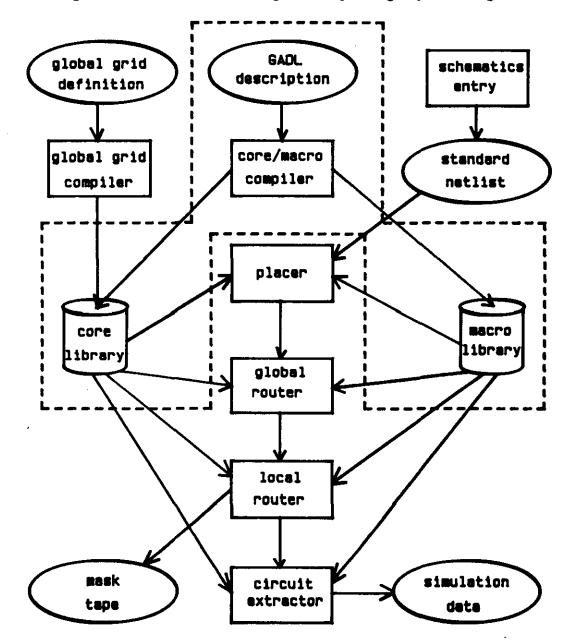

In figure 5 an overview of the gate array design system is given.

Figure 5. System overview.

First the gate array (structure, designrules, costs) and its macro stamps (structure, terminal positions, legal positions) have to be described in GADL and compiled to a datastructure suitable for the placement and routing programs. A macro is here regarded as a functional element (NAND, NOR, FLIPFLOP, etc.) while a macro stamp is one physical realisation of a functional element. The compilation has to be done just once for each gate array type. The data obtained from the *core/macro compiler* is stored in the *core library* (gate array core data) and in the *macro library* (macro stamp data).

Now netlists can be generated, either by hand (text) or by a schematics editor.

The *placer* takes care of the placement of macro stamps (when one macro has several physical realisations, the placer choses one stamp). The currently implemented placer works on the basis of simulated annealing (statistical cooling) <sup>[1]</sup>.

After the placement step, the gate array circuit is routed globally by the global router. The predicate "global" is assigned to this router because it operates on a global grid. This grid is usually much rougher than the fine grid proposed in chapter 2 and is defined by the global grid definition file. The global grid divides the gate array in global grid cells, where the cells correspond with "natural" routing space and the cell boundaries with "natural" routing blockades (usually power lines or active area). Figure 6 shows an example how a gate array could be divided in global cells.

A complete description of the global router is given by P. Nuijten <sup>[2]</sup>. With the information of the global router, the results of the placement, the gate array core grid and the contents of the macro library, the *local* router takes care of the final routing of the gate array circuit. For this purpose, an extended Leerouter is developed <sup>[3]</sup>.

In order to check the results (while developing the programs) and to simulate the circuit with regards to electrical performances (node capacities, cross coupling etc.) a *circuit extractor* will be developed.

- system overview -

Figure 6. Global cell choice.

This report regards the GADL language, the GADL compiler and the structure of the core and macro libraries (enclosed in dashed lines in figure 5).

- الفرائدة فالشار

and the second second

#### 4. ROUTING DATA STRUCTURE

The GADL compiler is developed in parallel with the program for local routing. Most of the data generated by the compiler is used by this router. The router operates on a universal data structure (universal with regards to the gate array type) which will be described here. This data structure is the target 'language' for the GADL compiler. As proposed in chapter 2, the information for routing can be mapped onto a three dimensional grid.

First of all, a few notions with regard to grids are stated. A grid G of size XSIZE \* YSIZE \* ZSIZE is a set of vertices (gridpoints)  $p_i$ :

$$G = \{ p_i = (x_i, y_i, z_i) \mid 0 \le x_i < XSIZE, 0 \le y_i < YSIZE, 0 \le z_i < ZSIZE \}.$$

$x_i$  represents the x-coordinate,  $y_i$  the y-coordinate and  $z_i$  the z coordinate of the vertex.

The distance  $D(p_1,p_2)$  between vertices  $p_1$  and  $p_2$  is defined as:

$$D(p_1, p_2) = |x_1 - x_2| + |y_1 - y_2| + |z_1 - z_2|.$$

$p_1$  and  $p_2$  are called neighbours if  $D(p_1, p_2) = 1$ . An *edge* is a pair of neighbour vertices, representing the gridline part between the vertices. The set E of edges is defined by:

$$E = \{ (p_1, p_2) \mid p_1 \in G, p_2 \in G, D(p_1, p_2) = 1 \}.$$

A path P in G is an ordered set of vertices:

$$P = \{ p_1, p_2, \dots, p_m \mid (p_i, p_{i+1}) \in S, 1 \le i < m \}.$$

so that,

$D(p_i, p_{i+1}) - 1, \qquad 1 \le i \le m.$

The path is said to be constructed of the edges  $(p_1, p_2)$ ,  $(p_2, p_3)$ , ...,  $(p_{m-2}, p_{m-1})$ ,  $(p_{m-1}, p_m)$ . A *layer* L<sub>1</sub> is a set of vertices defined by:

$L_1 = \{ (x_i, y_i, z_i) \in G \mid z_i = 1 \}.$

Our task now, is to assign those attributes to the vertices and edges so that the router can fulfil its task properly (without an unjustifiable amount of overhead). In this chapter, the information needed by the router is summarised.

#### 4.1 The position of wires, vias, wire blockades and via blockades

To map these properties onto the data structure, each edge is assigned a signal type. A signal type can have one of the three values: INITIAL, IMAGE or INHIBIT. A signal type initial indicates that the corresponding edge is free for routing (no blockade, no fixed wire or via). Likewise signal types of fixed and inhibit indicate an edge is occupied by a (pre-fabricated) wire or via, or blocked for routing respectively.

The router issues a fourth signal type: ROUTER, but this is beyond the scope of this report.

It will be obvious to the reader that in this way every wire being a path in G and every via that is positioned at a gridpoint can be modelled in the grid data structure. A careful choice of the positions of gridlines (which don't have to be equidistant) guarantees that a grid representation of each orthogonal wire and each via is possible. Non orthogonal wires however can not be transformed to a proper signal type setting of edges in the grid. Therefor the predicate equivalent point is introduced. In this context, two (or more) points are called (electrically) equivalent if there is a galvanic connection between these points and there is no way to model this connection in the grid representation. So a diagonal wire, that starts and ends at gridpoints, can be modelled by assigning an equivalent relation to these points. Care must be token that no other wire can cross the spanning orthogonal region of this diagonal

#### wire.

Generally each vertex has a set of equivalent vertices associated with it. It will be obvious that if  $p_2$  is an element of the equivalent vertex set of  $p_1$ ,  $p_1$  will be an element of the equivalent vertex set of  $p_2$ .

### 4.2 Design rules

Design rules are divided into numeric and structural rules. Structural rules tell something about preferred directions, not recommendable configurations etc.. They can be merged into the Leerout cost function and will not be discussed here.

In general numeric design rules take the form of a set of permissible geometries that can be used by the designer to make devices and interconnections within the resolution of the process and without violating the device physics required for their proper operations. They can be reduced to their simplest form: a set of geometrical constraints of the form of minimum allowable values for certain widths, separations, extensions and overlaps of geometrical elements. The length unit is usually in Lambda [4]

Gate array (numeric) design rules are quite different from the general ones. In gate arrays all the devices (transistors) are prediffused and only those processing steps involving the interconnections have to be carried out. Now, the width of wires and the size of via holes are process determined (and can be regarded sizeless) so the gate array design rules only concerns the minimum separations between interconnection layout elements (wires and via holes). The most basic design rules are already mentioned:

• All interconnections have to be made on gridlines

• All vias have to be made on crossing points of gridlines (gridpoints)

These rules are automatically provided by our way of modelling. Another consequence of the gridding process is that spacing rules can be described in terms of grid steps instead of Lambda. Because of the fact that gridlines don't have to be equidistant, and design rules are expressed in terms of grid steps, design rules are *position dependent*.

In our system, the design rules are modelled by the concept of shadowing. In general each edge in the grid shadows other edges in its surrounding area. If an edge  $s_1$  shadows an edge  $s_2$ , it means that if  $s_1$  is occupied (i.e. a wire or via runs along the edge),  $s_2$  should be free and vice versa.

In practice this means that, if the router decides to occupy edge s, all edges shadowed by s should be free. Up to now we have been able to model all numeric gate array design rules by this shadowing process.

For example, a horizontal edge can shadow horizontal edges on the adjacent horizontal gridlines (figure 7a).

Figure 7. Shadowing

This means that if the router decides to rout a wire along edge  $s_2$ , its shadowed edges (edge  $s_1$  and  $s_3$ ) have to be free i.e. not occupied by another net (figure 7a). Likewise a wire can shadow vias on adjacent gridlines (figure 7b).

It will be obvious that if  $s_1$  shadows  $s_2$ , then  $s_2$  will shadow  $s_1$ , so for every shadow relation a complementary relation exists.

#### 4.3 Leerouter cost function

The Leerouter is guided by a path cost function F. This function defines (for each edge s) the costs F(s) to extend the path along s. The costs F(P) of a path  $P = \{p_1, p_2, \dots, p_m\}$  is now defined as the sum of the costs of the edges the path is constructed of:

$$F(P) = \sum_{i=1}^{i-m-1} F((p_i, p_{i+1})).$$

The router tries to find a minimum cost path between the gridpoints it has to connect.

F has to be consistent to guarantee the proper operation of the router: [5]

#### Path consistency property:

Let F be a path cost function, P any minimum cost path from vertex A to vertex B, and Q any minimum cost path from B to C. If PQ is a minimum cost path from A to C through B, then F is called consistent with respect to P and Q. If F has this property for all choices of A, B, C, P and Q, then F is called consistent.

This implies that every path cost function F, where the costs to add an edge s to the path P are independent of the edges P is constructed of, is consistent.

Although the cost function could have any exotic shape and could be dependent on anything, we have to keep in mind that the router has to compute the function value every time it extends a path. Therefor we have restricted the properties of the function to the following simple form:

Suppose  $s = (p_1, p_2)$ , then F(s) is defined as:

$$F(s) = \begin{cases} c_{o} & \text{if } p_{1} \text{ or } p_{2} \text{ is occupied} \\ c_{n} & \text{if } p_{1} \text{ or } p_{2} \text{ is not occupied} \end{cases}$$

where  $c_0$  and  $c_n$  are predefined constant costs values. A vertex p is called occupied with respect to a rout R, if p is a start point of R. In spite of the fact that the above mentioned cost function form is very simple, and may be too simple in some cases, we have been able to model most of the desired costs in this form, while the 'computation' of the edge costs can be done by just testing the occupancy condition.

#### 4.4 Macro stamp information

For macro stamps some extra information has to be stored. First there are the positions of the terminals. The router has to know the exact position of the macro stamp terminals.

Second, the placer needs to know where the legal positions of the macro stamps are. A legal position of a macro stamp is some position in the gate array core, where the stamp performs its required function. For most gate array types the legal positions of macro stamps are sets of equidistant points.

Besides the terminals and legal positions we need to know the position of the internal wires of the macro stamps. Internal wires are those nets of a macro, which are not electrically equivalent to any terminal. These wires can not be used for routing and should be isolated. Isolation can not be performed during compilation because the internal wires can have connections to the 'outside' world. This implies that internal wires should be isolated during the design phase of the circuit. However, when the user specifies the positions of terminals and power lines, internal wires can be extracted automatically. Terminals and power lines are easier to discover than internal wires, so we will perform this automatic extraction.

Finally we need to know the equivalent terminals of a macro. Terminals are called equivalent if the nets connected to these terminals can be interchanged without changing the function of the macro. For example, the inputs A and B of a 2 input 'and-gate' can be interchanged, while the function will remain out - A.B. The router is not yet able to exploit this feature, while routing the circuit, but in future it will be.

#### 4.5 Implementation considerations

The in the previous sections proposed modelling of gate array features should be implemented in a form where we have an easy access to the proposed properties, and where the amount of required memory space is minimal.

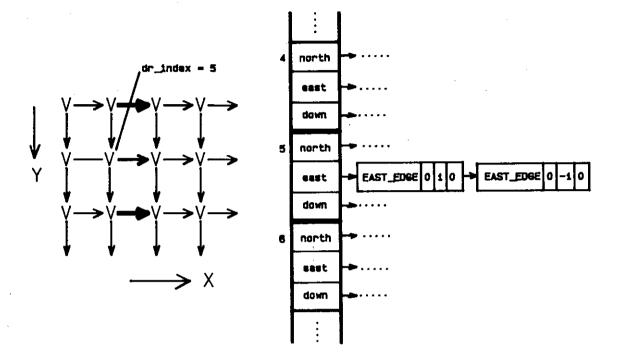

The grid is stored as a three dimensional array of vertices. This is a minimum because we need information about each vertex, so for each gridpoint data should be present. The edge descriptions are merged into the vertex records. Every gridpoint contains information about three edges: the edge in the north direction, the edge in the east direction and the edge in the down direction. The compass-card is given in figure 8.

Figure 8. Compass-card

What information has to be stored at each vertex ?

- The signal type of the associated edges. This means that in the vertex data structure minimal 6 bits have to be reserved for the signal types of the three corresponding edges.

- 2. Equivalent positions to the vertex. Equivalent relations are merged into the data structure by using a so called equivalence table. Each vertex has a equivalence index field and a equivalence offset field. The equivalence index is a pointer into the equivalence table. Each entry in the table represents a set of equivalent points. The equivalent points are stored cyclic as offsets to the next point in the set. The equivalence offset addresses a point in the cycle. Figure 9 shows the representation of two sets of equivalent gridpoints. This way of storage makes it possible to represent different sets of

(a, b) = eq\_index a, eq\_offset b.

Figure 9. Equivalent points

equivalent points, that have the same geometrical appearance, by just one table entry. Because of the repetitive structure of gate arrays, this means that the number of table entries is usually rather small, while the information stored at each vertex is minimal.

3. Shadowed edges of the associated edges. To store these properties, here again an external table, the design rule table, is used. Each vertex contains a design rule index, which is an entry in the design rule table. Every table entry contains three shadow lists. The first is the list of edges, shadowed by an east edge at the vertex. The second the list of edges, shadowed by a north edge and third the list of edges, shadowed by a down edge. A shadowed edge is fully determined by the position of the associated vertex and the direction of the edge (north, east or down). Therefor we store the shadowed edges as a relative position (relative to the position of the vertex in question) plus an indication about the direction of the edge. The direction indicators are: EAST\_EDGE, NORTH\_EDGE and DOWN\_EDGE. A shadowed edge can now be addressed by two attributes: (direction, rel position).

For example, if the east shadow list at some gridpoint contains the elements (EAST\_EDGE, (0,1,0)) and (EAST\_EDGE, (0,-1,0)), it means that an east edge at the vertex shadows horizontal edges on adjacent tracks (figure 10).

Figure 10. Design rule table.

Again because of the repetitive structure of gate arrays (and their design rules) the number of entries in the design rule table is quite small.

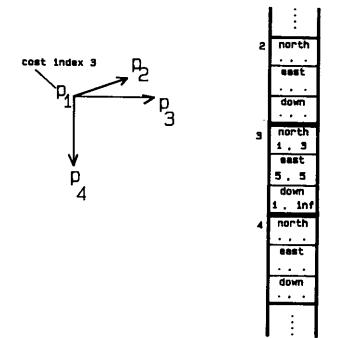

4. The costs to occupy each of the associated edges. As could be expected, here again we use an external table: the cost table. A vertex is assigned a cost index which represents an entry in the cost table. Every entry in the cost table contains six absolute cost values being the  $c_0$ 's and  $c_n$ 's of the associated (three) edges. If the router decides to occupy edge  $s - (p_1, p_2)$ , then dependent whether  $p_2$  is occupied with respect to the path currently expanded, the cost for this occupation is defined by the corresponding  $c_0$  or  $c_n$ . Figure 11 shows an example of cost definitions using a cost table.

Figure 11. Cost table

4.6 Summary

The for the compiler interesting datafields at each gridpoint (vertex) are:

- North signal type

- East signal type

- Down signal type

- Equivalence table index

- Equivalence table entry offset

- Design rule table index

- Cost table index

Besides this vertex data structure three tables are necessary:

- Equivalence table

- Design rule table

.

• Cost table

Macro stamps require some extra information:

- Terminal positions.

- Legal positions.

- Internal wire positions.

- Equivalent terminals

The definition of the vertex data structure is given in appendix A.

#### 5. LIBRARY STRUCTURES

In the previous section, the routing data structure was stipulated. The two libraries where the data is stored are described in this section. For the gate array core, the data is stored in a directory (gate array core library). In here, each item (grid, equivalence table, etc.) corresponds with a special file.

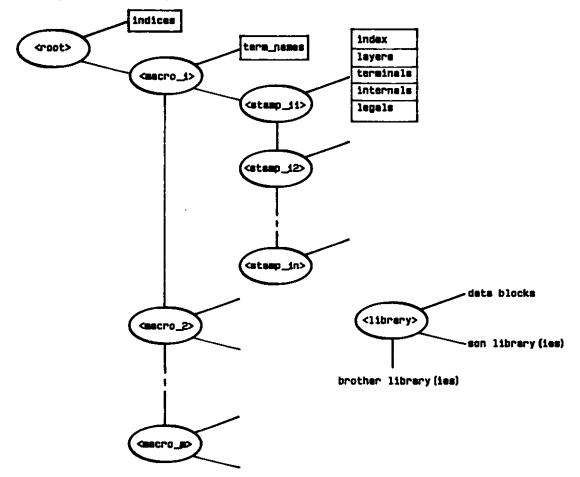

Figure 12. Macro library structure

Besides the gate array core data however, we need information about the macro stamps. Of course, here again a grid must be stored, but we also need information about the stamp's terminal positions, the position of internal wires (these can not be used for routing) and its legal positions (a macro stamp can not be mapped at every arbitrary place in the core, but has several predefined positions where the stamp performs its required behaviour). For this purpose a directory or directory tree could be used, but we have chosen (for sake of surveyability) for a separate macro library file. The file is a binary dump of the macro library structure given in figure 12. The used library access routines are extensively described in literature  $\begin{bmatrix} 6 \end{bmatrix}$ .

Now that we have defined the target language for the compiler, the source language (GADL) will be described.

#### 6. THE GADL LANGUAGE

#### 6.1 Goals of GADL

The objective of GADL is to describe the features of gate arrays, as mentioned in the previous sections, in an easy, compact and 'natural' way. The frame of GADL is a combination of the languages GADSL and GADRL, as proposed by Jichun Bu [7]. In these languages it is possible to describe the gate array core structure and its design rules. These languages are combined, adjusted and extended so that we can now describe the total gate array (inclusive macro stamps, design rules and cost function properties) in one uniform grammar.

Because of the repetitive structure of gate arrays the operation repetition is supported in GADL. Also transformations (mirror, rotation) on grid structures are legal operations. Besides the repetitive features, the language is hierarchical to an unlimited depth.

The combination of hierarchy and repetition makes it possible to describe most gate array cores in an extremely compact way (1 a 2 pages).

6.2 An outline of GADL

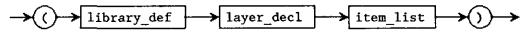

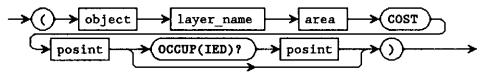

Each legal GADL sentence starts with a library definition followed by a layer declaration. Then an item list with all image- design rule- and cost function descriptions follows.

syntax:

<GADL\_sentence> ::= "(" <library\_def> <layer\_decl> <item list> ")".

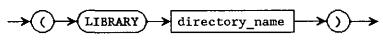

The library definition defines the location where the libraries should be stored.

syntax:

<library\_def> ::= "(" "LIBRARY" <dir\_name> ")".

semantics:

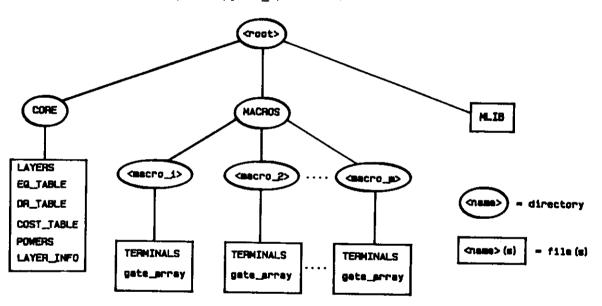

<dir\_name> is the name of a (UNIX) directory. In this directory a subdirectory CORE is created. In here, all gate array core information is stored (gate array core library). In <dir\_name> the file MLIB is created too. This file contains the information about the macro stamps (macro library). In the sub directory MACROS of <dir\_name>, for each macro, a directory <macro\_name> is generated, where the names of the macro's terminals and a file flag called gate\_array are stored. The sub directory MACROS is used by the schematics entry program: ESCHER. The directory structure is visualised in figure 13. example:

( LIBRARY /users/paul 1/TAL004 )

Figure 13. The directory structure

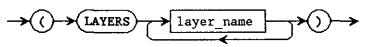

The layer declaration statement declares all layer names used in the GADL description.

syntax:

<layer\_decl> ::= "(" "LAYERS" {<layer\_name>}+ ")".

semantics:

The layer names have to be declared from the wafer upto the surface. *example*:

( LAYERS diffusion poly metall metal2 )

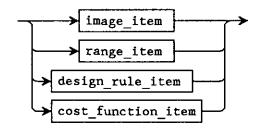

The <item\_list> is a list of items:

syntax:

<item\_list> ::= {<item>}+.

We distinguish four kinds of items:

- image definition item

- range definition item

- design rule definition item

- cost function definition item

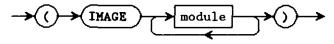

#### 6.2.1 Image definition item

The image definition item defines the geometrical appearance of the core or the macro stamps. These alternatives are mutually exclusive.

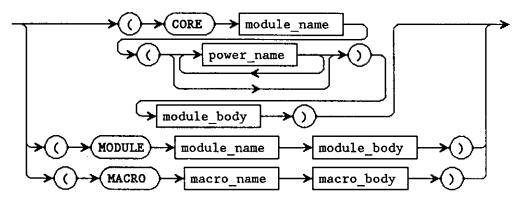

As mentioned in section 6.1 the structure description is hierarchical. The basic blocks are modules. A module can either be a simple module (type MODULE), a core module (type CORE) or a macro module (type MACRO). A simple module only describes geometry of a grid part. A core module defines the geometry of the total gate array core and a macro module defines the geometrical appearance of a macro (and its associated stamps). Simple modules can be called at certain positions in other modules. Of course, no recursion is allowed because an endless loop would be created.

Now the total image definition item is a list of modules. When a core module is defined, no macro modules are allowed. *syntax*:

<image\_definition> ::= "(" "IMAGE" {<module>}+ ")".

<module> ::= "(" "CORE" <name>

{<power\_name>}\*

<simple\_module\_body>

")"

| "(" "MODULE" <name> <simple\_module\_body> ")"

| "(" "MACRO" <name> <macro body> ")".

```

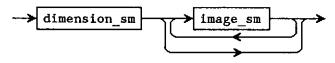

<simple_module_body> ::= <dimension_sm> {<image_statement>}*.

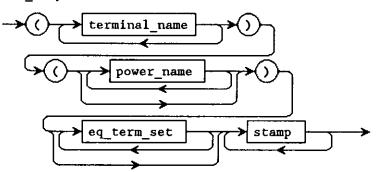

<macro_body> := "(" {<term_name>}* ")"

"(" {<power_name>}* ")"

{<eq_term_set>}*

{<stamp>}+.

```

semantics:

In the description of the core, the names of the power lines (and their positions) should be defined, because they are treated as special nets (if they don't appear in the netlist they should be isolated). The body of a simple module is just a dimension specification followed by a list of image statements. Some image statements are only meaningful and legal in macro stamp descriptions. For example the definition of a terminal in a simple module is meaningless and therefor not allowed.

The body of a macro consists of a list of terminal names, a list of power names, a list with equivalent terminal sets and a stamp list. The terminal names and power names of one macro are the same for all stamps. The positions of the terminals and the powers should be defined within the stamp body. The positions of the power lines are important when we want to determine the internal wires of a macro stamp. The equivalent terminal sets are identical for all stamps too.

syntax:

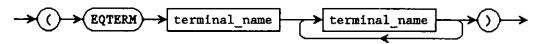

<eq\_term\_set> ::= "(" "EQTERM" <term\_name> { <term\_name>}+ ")".

example:

( EQTERM inl in2 in3 )

A stamp defines one physical realisation of a macro. Different stamps of one macro could have totally different geometric appearances, but they can also have the form of rotations or mirrors of one basic structure. In the latter case, it is advisable to define a simple module containing the basic structure, and call this module (with the proper transformations) in the macro stamp bodies.

syntax:

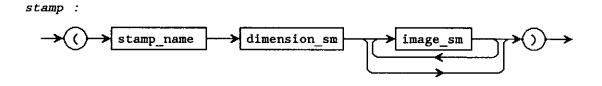

<stamp> ::- "(" <name>

<dimension\_sm>

- the GADL language -

{<image statement>}\* ")".

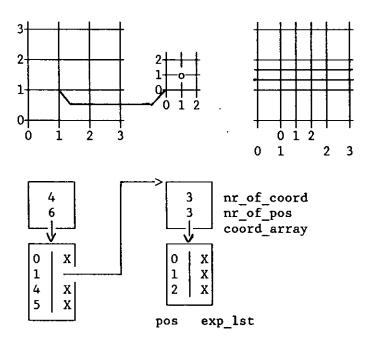

All image statements concern positions in grids. For ease of speech, first a few notions with regards to grids are stated. Each simple module, core module or macro stamp has its own *local grid*. The gridlines in this grid have to correspond with gridlines in the fine routing grid. However, sequential gridlines in the local grid can have many fine gridlines between them. Gridlines where no module is called are regarded as the gridlines of the fine routing grid. The gridpoints in the local grid are addressed by a *position*. A position is a pair of integers representing the x gridline and the y gridline in the local grid respectively. Note: the origin of the coordinate-system is  $(0 \ 0)$ .

Gridpoints in the fine grid are addressed by *coordinates*. It will be obvious to the reader that every position in the local grid corresponds with a coordinate in the fine grid.

The size of the local grid is defined by a <dimension\_sm>. syntax: <dimension\_sm> ::= "(" "DIMENSION" <x\_dim> <y\_dim> ")". semantics:

This statement defines the dimension of the module's local grid. <x\_dim> defines the number of y-axis-parallel gridlines. Likewise, <y\_dim> defines the number of x-axis-parallel lines. example:

( DIMENSION 14 12 )

Now we have to choose our set of image statements in such a way that all properties mentioned in chapter 4 can be described. We should also have the possibility to indicate the router freedom in the different layers to determine reducibility of layers (see section 7.1.1), and to make the description more compact.

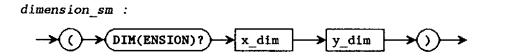

syntax:

- the GADL language -

| <wire\_sm>

| <nwire\_sm>

| <rwire\_sm>

| <via\_sm>

| <nvia\_sm>

| <pvia\_sm>

| <pvia\_sm>

| <equivalence\_sm>

| <terminal\_sm>

| <power\_sm>

| <legal\_sm>.

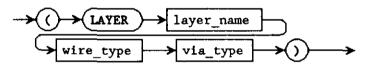

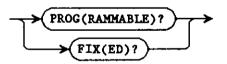

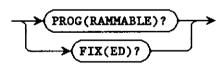

The <layer\_sm> specifies the default wire and via types. syntax:

<layer\_sm> ::= "(" "LAYER" <name> <wire\_type> <via\_type> ")"

semantics:

The wire and via types determine the degree of freedom for the router in the layer defined by <name>. <wire\_type> or <via\_type> can either be "FIX(ED)" or "PROG(RAMMABLE)". A type of FIX means that there is no freedom for the router to expand its paths in the layer. Likewise a type of PROG means that the router can create wires (or vias) in the corresponding layer. The layer type definition of the core module is used to determine the reducibility of layers. Layers with both via type and wire type set to FIXED offer no freedom for the router and can be reduced.

examples:

( LAYER diffusion FIXED FIXED )

( LAYER metal PROG FIX )

In the layer 'diffusion', the router can not create wires or vias (to the layer beneath). In the layer 'metal', wires can be generated, but vias are at (user defined) fixed positions.

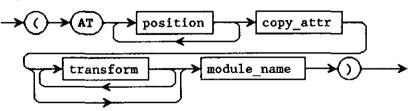

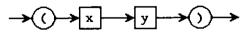

A <call\_sm> calls a simple module (optionally transformed) at a certain position in the local grid. syntax:

<call sm> ::- "(" "AT"

- the GADL language -

```

{<position>)+

[<copy_attr>]

{<transform>}*

<name> ")".

<position> ::= "(" <xpos> <ypos> ")".

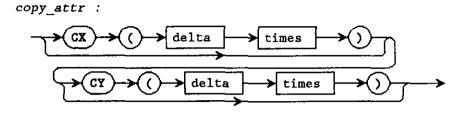

<copy_attr> ::= [ "CX" "(" <integer> <integer> ")" ]

[ "CY" "(" <integer> <integer> ")" ].

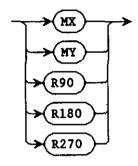

<transform> ::= "MX" | "MY" | "R90" | "R180" | "R270".

semantics:

```

This statement defines calls of simple module <name> at all local grid positions defined by {<position>}+ and <copy\_attr>. The size of the called module with respect to the local grid is always 1 \* 1. The defined positions are the points where the left under corner of the called module is mapped to.

The two integers in each copy attribute represent the delta- and timesvalue respectively. So CX(2 3) means: copy three times in the x direction with a delta of two. The <copy\_attr> operates on all positions of (<position>}+. If a module is called at position, let's say (x y), then between the local gridlines x and x+1 as many fine gridlines as required by the called module are inserted. The same holds for the y direction. The first gridline of the called module covers the local gridline of the calling module at the called position. Care must be token that all modules, called at coordinate x, require an equal number of gridlines to be inserted.

The transformation MX mirrors the called module in the x-axis, MY mirrors in the y-axis. R90 rotates the called module 90 degrees anti clock-wise. Transformation are executed 'from the <name> away'. example:

(AT  $(3 \ 3) CX(2 \ 2) CY(1 \ 3) MX R90 gate_cell$ ) Here, the module 'gate\_cell' is called (first rotated and then mirrored) at the positions (3 3), (5 3), (7 3), (3 4), (5 4), (7 4), (3 5), (5 5), (7 5), (3 6), (5 6) and (7 6). These are the positions where the left under corner of the (already transformed) module 'gate\_cell' is mapped to. Wire statements define the galvanic horizontal connections (horizontal means: situated in one layer).

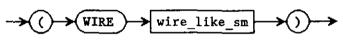

syntax:

<wire\_sm> ::= "(" "WIRE" <name>

{<coordinate>}+

[<copy\_attr>] ")".

<coordinate> ::= "(" <int> ["." <int>] <int> ["." <int>] ")".

semantics:

A wire is here regarded as a horizontal galvanic connection between gridpoints in the layer defined by <name>. The wire sequentially connects the gridpoints defined by their coordinates. When non-orthogonal wire-parts are defined, the spanning region of the wire part is blocked for routing, i.e. when the wire-part runs from  $(x1 \ y1)$  to  $(x2 \ y2)$ , the region formed by the cartesian product of (x1,x1+1, ..., x2) and (y1, y1+1, ..., y2) is blocked for routing (no wires can enter this region). The copy attribute operates on the total wire shape.

Coordinates defined in a wire statement are a little more complex than the positions defined in a call statement. Where the positions in a call statement only address positions in the local grid, in a wire statement it is possible to address coordinates in the fine grid. This is established by adding sub coordinates to the positions in the local grid. These sub coordinates define the number of fine gridlines that have to be added to the fine grid coordinate corresponding with local grid position. For example the coordinate (5.3 8.9) defines a coordinate obtained by stepping 3 fine gridlines in the x direction from the fine gridline corresponding with local gridline 5, and 9 gridlines in the y direction from the fine gridline corresponding with local gridline 8. This feature can be very useful to define powerlines (which are across the whole gate array) and to connect modules. Sub coordinates are only legal at positions where modules are called, and where the sub coordinate does not exceed the called module's fine dimension.

NOTE: The copy attribute only affects the local grid position. It is not legal to add sub coordinates to the copy attributes. examples:

```

(WIRE metall (0 0) (3 0) (3 4) CX(4 1))

```

(WIRE poly (0 8.1) (0.13 8.1) CX(2 1) )

The first statement defines two wires of equal shape. The second again defines two wires and shows the use of sub coordinates. One wire runs from  $(0 \ 8.1)$  to  $(0.13 \ 8.1)$ , the other from  $(2 \ 8.1)$  to  $(2.13 \ 8.1)$ .

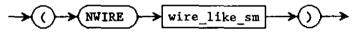

A nwire statement defines the position of wire blockades.

syntax:

<nwire\_sm> ::= "(" "NWIRE" <name>

(<coordinate>)+

<copy attr> ")".

semantics:

A nwire statement defines gridline parts that are blocked for routing. If a diagonal wire segment is detected, the spanning region is blocked as a whole. The same remarks as to wire statements apply to nwire statements.

example:

(NWIRE poly (3.4 0) (5 0) CY(2 3) )

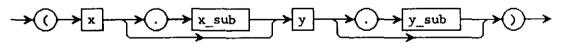

semantics:

A via statement defines vias (holes) from layer <namel> downto layer <name2>. If no <name2> is defined, a via to the underlying layer is assumed. The positions of the vias are defined by the coordinates and the <copy\_attr>. If two layer names are defined, it is necessary that <namel> is nearer to the surface of the wafer than <name2>. For the coordinates, the same as for the wire statement holds. example:

( VIA metal2.diffusion (0 0) (3.2 4.6) CX(2 1) )

( VIA poly (0 0) (0 5) (0 11) CX(2 10) )

```

- the GADL language -

```

32

```

It is advisable to define 'related' vias in just one statement in stead

of using a separate one for each individual via.

Nvia statements define the via blockades.

syntax:

<nvia sm> ::= "(" "NVIA" <name1> ["." <name2>]

{<coordinate>}+

<copy_attr> ")".

semantics:

At the defined positions, no via can be created by the router.

example:

( NVIA metal.poly (1 0) (1 5) CX(2 100) CY(20 8) )

Pvia statements define the positions of programmable vias.

syntax:

<pvia_sm> ::= "(" "PVIA" <name1> ["." <name2>]

{<coordinate>}+

<copy attr> ")".

semantics:

This statement is useful in cases where the layer via type is set to

FIXED and where at some pre-defined positions vias can be created. The

pvia statement defines those positions.

example:

( PVIA poly (1 0) (1 5) CX(2 100) CY(20 8) )

```

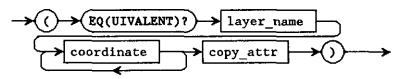

An equivalence statement defines a set of electrically equivalent points. syntax:

semantics:

~

An equivalent statement defines a set of electrically equivalent points in the layer <name>. The set is defined by the coordinate list. <copy\_attr> does not extend the set, but increases the number of sets. In fact it creates another set with the same shape but located elsewhere. *example*:

(EQ poly (3.1 0) (6.8 3.9) CX(5 1) CY(3 7))

semantics:

This statement is only meaningful and legal in a macro stamp body. <namel> is the name of the terminal. The name has to be declared in the terminal list of the macro module. <name2> defines the name of the layer, the coordinate(s) of the terminal are positioned. Only one coordinate of a terminal tree has to be defined. All galvanically connected coordinates are regarded as terminal positions. Usually the coordinate list exists of one coordinate. The defined layer should be not-reducible.

NOTE: A terminal position definition for each declared terminal should be present.

example:

( TERMINAL in2 metal (0 5.1) )

The power statement defines the position of power lines.

syntax:

<power sm> ::= "(" "POWER" <name1> <name2>

{<coordinate>}+ ")".

```

semantics:

```

All remarks concerning a terminal statement apply to a power statement. However, power position definitions are also allowed in the core module description.

example:

( POWER vdd metal (0.96) )

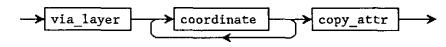

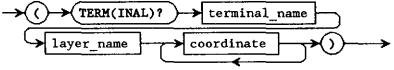

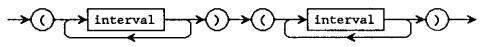

A legal statement defines the legal positions of a macro stamp. syntax:

```

<legal_sm> ::= "(" "LEGAL"

```

```

"(" <start> <delta> <end> ")"

"(" <start> <delta> <end> ")"

```

```

")".

```

<start> ::= <int>.

<delta> ::= <int>.

```

<end> ::= <int> | "END" ["-" <int>].

```

semantics:

Each legal statement defines a set of legal positions. The first <start>-<delta>-<end> sequence concerns the x-direction, the second the y-direction. <start> defines the first fine grid coordinate in the core grid. This position is repeated with delta <delta> until <end>. The legal position set is formed by the cartesian product of the x-direction coordinates and the y-direction coordinates. If <end>is "END", it means that the coordinates should be repeated until the size of the gate array core. <end> does not has to be: a multiple of <delta> plus <start>.

( LEGAL (0 20 200) (0 10 50) ) ( LEGAL (0 14 END) (0 8 END-1) )

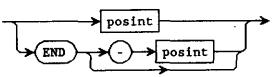

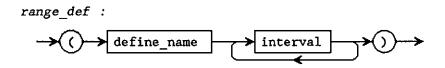

### 6.2.2 Range definition item

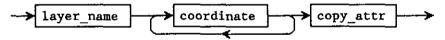

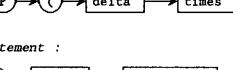

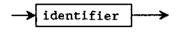

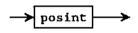

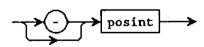

The range definition item defines ranges, and assigns names (identifiers) to them. These ranges may be used in the design rule and cost function part of the description.

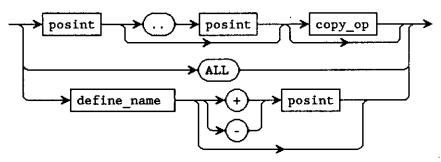

syntax:

semantics:

A range definition assigns  $\langle name \rangle$  to the range defined by the interval list. A range is a sequence of x (y) coordinates. An interval is a

closed sequence of coordinates (optionally copied) or a point to the definition of an earlier defined range (optionally offsetted). In the interval definition, just an <integerl> defines the coordinate with that value. <integerl> .. <integer2> defines a range from <integer\_1> upto and including <integer2>. Copy operators can be added to these intervals. "ALL" defines the total axis (x or y). Whether the x or y axis is meant should be clear from the context the range is called in. <name2> ("+"|"-") <integer3> defines a range obtained by adding (subtracting) <integer3> coordinates to each element of the range associated with <name>.

example:

( DEFINE

)

```

( vdd_x 19 CP(30 5) )

( poly_under_x 0 CP(2 94) vdd_x+2 vdd-2 )

( x_axis ALL )

( junction_x 10..29 CP(30 5) )

```

The first range defines a sequence 19, 49, ..., 169, the second a sequence 0, 2, ..., 188, 21, 51, ..., 171, 17, 47, ..., 167, the third a sequence 0..MAX and the last a sequence 10, 11, ..., 29, 40, ..., 59 etc..

Now, areas can be defined as the cartesian product of two ranges, where the first is the x coordinate range and the second the y coordinate range.

6.2.3 Design rule definition item

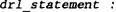

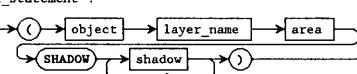

The design rule description knows no hierarchy because of the problems that would occur at the module's boundaries. As stated earlier, design rules are defined by the concept of shadowing. We define three kinds of objects: *HORWIRE*, *VERWIRE* and *VIA*. HORWIRE corresponds with an edge in the east direction, VERWIRE with an edge in the north direction and VIA with an edge in the down direction. With these three objects and area definitions it should be possible to model all of the design rules applying to a gate array type. The design rule part of the core description

A design rule statement says: When <object> is made in the area defined by the cartesian product of the two interval lists and the layer <name>, then it shadows the elements in the shadow list. A shadow element consists of the shadowed object, the layer name of the shadowed object and the position of the shadowed object relative to the position of the "make-object". <integerl> defines the delta-x and <integer2> the delta-y, so a shadow ( VIA metal -1 1 ) defines a shadowed via in layer metal (to the layer beneath) at the position obtained by adding -1 to the xcoordinate of the position of the object made and adding 1 to the ycoordinate. Every ("make-object", shadow) combination has its complement, i.e. if object A at (x,y) shadows object B at (x+dx, y+dy) then object B at (x,y) shadows object A at (x-dx,y-dy). These complements are generated automatically with respect to effects at the area boundaries. This means that the area defined in the input is not automatically copied to the complement relation, but shifted over the delta's as defined in the shadows.

example:

( DRL

```

( VERWIRE metal2 (in_gate) (ALL) SHADOW

( VIA metal2 -1 0 )

( VIA metal2 1 0 )

)

```

```

( VERWIRE metal2 (in_channel) (ALL) SHADOW

( VERWIRE metal2 -1 0 )

( VERWIRE metal2 1 0 )

)

( VERWIRE metal1 (in_channel) (ALL) SHADOW

( VIA metal2 -1 0 )

( VIA metal2 1 0 )

)

```

- the GADL language -

```

6.2.4 Cost function item

```

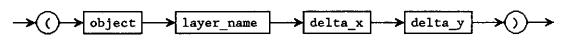

)

Here again, the cost function description knows no hierarchy because of boundary problems. The same objects: *HORWIRE*, *VERWIRE* and *VIA*. as in the design rule item are appropriate to describe the costs to occupy edges. It is also legal to use defined ranges (defined in the range definition item) in the cost function description.

```

syntax:

```

<costn> [ "OCCUP(IED)?" <costo> ]

```

<object> ::= "HORWIRE" | "VERWIRE" | "VIA".

```

")".

semantics:

A cost definition statement associates the identifier <name> with the cost value <cost>. A cost assignment says: The costs to occupy the edges defined by the layer <name>, the area defined by the interval lists and the direction defined by <object> are equal to <costn>, if one of the gridpoint defining the edge is not a start point of the route, and equal

```

to <costo> if so. <costo> and <costn> are either values (integers) iden-

tifiers (defined in a cost definition) or "INFINITE" to indicate a cost

value of infinite.

The costs of edges which are not set in the input default to the unit

cost 1 (costs have to be positive).

example:

( COST

( DEFINE function_box_cost 100 )

( DEFINE junction_box_cost 200 )

( HORWIRE metal (diffusion_x) (diffusion_y)

COST INFINITE OCCUPIED 1

)

( HORWIRE metal (function x) (function y)

COST function box cost

)

( VERWIRE metal (junction_x) (junction_y)

COST junction_box_cost

)

)

```

In appendix E an example of a gate array core description and some macro descriptions are included.

### 7. THE GADL COMPILER

In this chapter the algorithms and data structures used by the actual compiler are summarised. All routines operate on an internal data structures, independent of the input syntax. It is rather easy to redefine the input syntax (the features however have to be the same) without rewriting the compiler.

We distinguish three main parts in the compilation phase:

- Image compilation.

- Design rule compilation.

- Cost function compilation.

These parts are discussed separately.

## 7.1 Image compilation

Before we take a look at the internal data structure and the routines, the notion 'layer reduction' is introduced.

### 7.1.1 Layer reduction

In gate array technology some layers are provided by the foundry and offer no freedom for routing. It would be useless to regard these layers in our system because they only require storage space and don't contribute to the amount of information. These layers can be 'deleted' by the process of layer reduction. However, we can not just delete the layer(s) because they generally contain information about electrical equivalences in the layer above. When we discover that a layer can be reduced, all electrical equivalences obtained from the 'wire pattern' in the reducible layer have to be merged in the data structure of the upper layer. These electrical equivalences can be modelled in the same way as the equivalent relations discussed in section 4.5. For example: A fixed poly underpass under a routing channel of some CMOS gate array, with fixed metal poly

Figure 14. Layer reduction. a) geometry. b) grid model. c) reduced grid model.

vias can be modelled as shown in figure 14.

## 7.1.2 Data structure

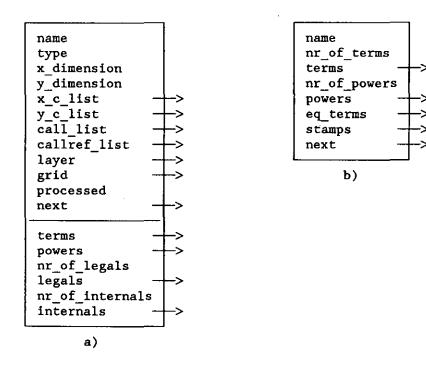

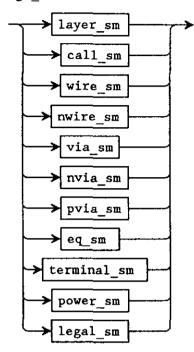

The input description statements are one to one projected to an internal data structure described in this paragraph. As the description is fully hierarchical, the data structure is too. The basic block is the module (figure 15a). The modules which are not a macro stamp are linked in a list called MODULES. The macros (figure 15b) are linked in a list called MACROS. The field 'stamps' of a macro is a list of modules, where each

Figure 15. Structures: a) MODULE b) MACRO

module represents a macro stamp. Now, each module structure corresponds with a module-, core- or macro stamp definition in the input description.

Besides these two lists there is an extra pointer called 'CORE\_MODULE' pointing to the module, describing the core of the gate array, and a list called 'LEAVES' containing all leaf cells. If a macro stamp is not calling any sub-module, the type will be 'MACRO\_STAMP', but it will be added to 'LEAVES'.

### Module structure description:

- 'name' is the name of the module as defined in the input.

- 'type' can either be MODULE\_CELL, CORE\_CELL, LEAF\_CELL, MACRO\_STAMP or NOT\_CONNECTED. MODULE\_CELL, CORE\_CELL and MACRO\_STAMP are self explanatory. A module is assigned the type LEAF\_CELL if it calls no other module. NOT\_CONNECTED means that the module is not called and is not a CORE\_CELL or MACRO\_STAMP.

- 'x\_dimension' and 'y\_dimension' define the size of the local grid.

'x\_dimension' is the number of y-axis parallel local gridlines, 'y dimension' the x-axis parallel gridlines.

- 'x\_c\_list' and 'y\_c\_list' are arrays of size x\_dimension and y\_dimension respectively. They are used during the expansion of the local grid to the fine grid (hierarchy processing) and are discussed in the description of the expansion routines.

- 'call\_list' is the list of called modules, inclusive the positions where the modules are called, and the effective transformations.

- 'callref\_list' is the list of all modules that call this one.

- 'layers' is an array of size NR\_OF\_LAYERS, where NR\_OF\_LAYERS is the number of layers declared in the input description. Each element of layers contains the (n)wires, the (np)vias, the equivalent relations and the default wire and via types (for that layer) as described in the input.

- 'grid' is a three dimensional array of type CVERTEX (appendix A). Initially this array is empty (filled with nulls) but will be filled during the compilation.

- 'processed' is a boolean to indicated that the module has been processed during some compilation phase. The initial value of 'processed' is FALSE.

- 'next' points to the next element of the list.

Beneath the line of figure 15a the extra data for macro stamps is summarised:

- 'terminals' is an array where the positions of the terminals are stored.

- 'powers' is an array where the positions of the power lines are stored (is also used in the CORE MODULE).

- 'nr\_of\_internals' is the number of internal wires of the stamp.

- 'internals' is a list of the positions of the internal wires.

- 'nr\_of\_legals' is the number of legal position sets of the stamp.

- 'legals' describes the legal position sets.

- the GADL compiler -

Macro structure description:

- 'name' is the name of the macro as defined in the input description.

- 'nr\_of\_terms' is the number of terminals of the macro.

- 'terms' is a list with the terminal names of the macro.

- 'nr\_of\_powers' is the number of powers defined for the macro.

- 'powers' is a list with the power names.

- 'eq\_terms' is a list of the equivalent terminal sets.

- 'stamps' is the list of all stamps. The elements in the list are of the type MODULE.

- 'next' points to the next macro in the list (MACROS).

Figure 16. The EQ ARRAY

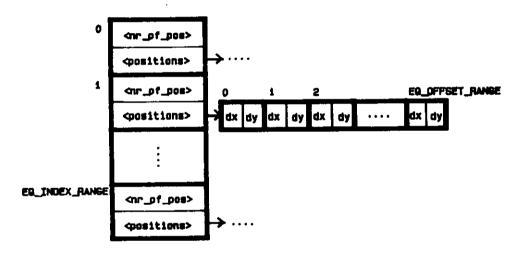

Besides these two structures we need a special array to store the equivalent relations: the EQ\_ARRAY (figure 16). The size of the array is EQ\_INDEX\_RANGE + 1, where EQ\_INDEX\_RANGE =  $2^{eq\_bits}$ -1. 'eq\_bits' is the number of bits reserved for the equivalence index in the VERTEX data structure (appendix A). Each entry in the array represents an equivalence set. The elements in the array contains two fields: 'nr\_of\_pos' and 'positions'. 'positions' is an array of size EQ\_OFFSET\_RANGE + 1, where EQ\_OFFSET\_RANGE =  $2^{offset\_bits}$ -1. The actively used number of elements in this array is 'nr\_of\_pos'. The equivalent positions in the array are stored as offsets to the first element of 'positions'.

### 7.1.3 Routines

The routines in the image compilation part can be divided in three sections:

- Grid expansion routines

- Grid filling routines

- Layer reduction routines

NOTE: The algorithms are described in terms of a meta-language, presented in appendix C.

### Grid expansion:

During grid expansion, the local grid is expanded to the fine grid. This means that between the gridlines of the local grid as many fine grids as required by the called modules are inserted. The grid expansion routines use the 'x\_c\_list' and 'y\_c\_list' fields of the modules. A 'c\_list' contains three fields: 'nr\_of\_pos', 'nr\_of\_coord' 'coord\_array'. and 'nr of pos' is the number of fine gridlines, 'nr of coord' is the number of local gridlines and 'coord\_array' is an array of size 'nr\_of\_coord' Each element in 'coord\_array' contains two fields: 'position' and 'expansion\_list'. 'position' is the position of the local gridline in the fine grid (relative to the origin of the module), and 'expansion\_list' is a pointer to the 'c\_list' of the module called at that coordinate. Figure 17 shows an example of how to interpret these lists. Expand\_grids is the routine that builds this part of the data structure.

- expand grids ()

synopsis:

void expand\_grids ()

description:

The objective of this routine is to define the fields in the 'c\_list's as described above.

algorithm:

BEGIN

Figure 17. Coordinate lists.

FOR all leafs DO

```

{ set processed flag in leaf

}

{ (they don't have to be expanded): }

leaf is processed;

ROF:

FOR all leafs DO

( expand (recursively) the axes )

{ of the calling modules

}

expand super axes of leaf;

ROF;

END;

subroutine:

void expand_super_axes ();

- expand_super_axes ()

synopsis:

void expand_super_axes ( module )

MODULE_PTR

module;

```

description:

```

- the GADL compiler -

```

```

This routine recursively checks whether the grids of the modules,

that

call <module>, can be expanded and expands them.

algorithm:

BEGIN

FOR all calling modules DO

IF calling module not yet processed THEN

IF all sub modules of calling module processed THEN

expand axes of calling module;

now calling module is processed;

expand super axes of calling module;

FI;

FI;

ROF:

END;

subroutines:

BOOLEAN sub_modules_processed ();

void

expand axes ();

void

expand_super_axes ();

- sub_modules_processed ()

synopsis:

BOOLEAN sub_modules_processed ( module )

MODULE PTR

module;

description:

Returns TRUE if all sub-modules of <module> are processed, i.e. if the

'processed' field of all sub-modules is TRUE. Else returns FALSE.

- expand_axes ()

synopsis:

void expand_axes ( module )

MODULE_PTR

module;

description:

Actually expands the axes of <module>.

algorithm:

```

46

```

47

- the GADL compiler -

BEGIN

FOR all called modules DO

IF at called position already expansion list THEN

IF expansion lists not equal THEN

error;

FI:

ELSE

set expansion list to c list of called module;

FI;

ROF;

update positions in c_list of module;

END;

subroutines:

BOOLEAN exp_lists_equal ();

void

update positions ();

- exp_lists_equal ()

synopsis:

void exp_lists_equal ( list1, list2 )

C LIST PTR

list1, list2;

description:

Returns TRUE if the lists <list1> and <list2> are equal concerning

number of gridlines. Else returns FALSE.

- update positions ()

synopsis:

void update_positions ( c_list )

C_LIST_PTR

c_list;

description:

Updates the position fields in the 'coord_array' of <c_list>.

Grid filling:

After the expansion of the grids, the filling can start.

```

```

48

- the GADL compiler -

- image_cmp ()

synopsis:

void image_cmp ()

description:

Compiles the description as defined by the statements in the input to a

proper signaltype and equivalence index and offset setting in the grid.

algorithm:

BEGIN

IF macros defined THEN

determine core pattern under macro stamps;

{ fill all grids: }

fill grids;

find internal wires of macros;

ELSE

IF core module defined THEN

fill grids; { fill all grids except the core grid }

fill core grid; ( fill the core grid )

FI;

FI:

END:

subroutines:

CVERTEX_PTR_3 read_image_grid ();

void

read_eq_table ();

void

read_pattern ();

void

free_grid ();

fill_grids ();

void

find internals ();

void

void

fill_core_grid ();

- fill_grids ()

synopsis:

void fill grids ()

description:

Fills the grids of all modules except the core module (special case)

```

```

according to the statements in the input definition.

algorithm:

BEGIN

{ processed field of the core module is set to TRUE }

{ to avoid grid filling during this routine:

}

all modules except core module not processed;

FOR all leafs DO

IF leaf not processed THEN

fill leaf layers;

now leaf is processed;

fill super modules (calling modules) of leaf;

FI;

ROF;

END;

subroutines:

CVERTEX_PTR_3 allocate_grid ();

void

fill_layer ();

void

fill super modules ();

- fill core grid ()

synopsis:

void fill_core_grid ()

description:

Fills the grid of the core module. The core module is processed

separately because in the grid of this module we can (generally) reduce

layers. The core module usually is the biggest of all and requires an

enormous amount of storage space. Therefor, we don't allocate the hole

grid but in first instance only one layer, the nearest to the wafer.

After the filling of that layer, for every other layer we check whether

the layer beneath can be reduced and merged into the current layer.

```

the layer beneath can be reduced and merged into the current layer. If so, the actual reduction takes place. The layer reduction routine returns whether a layer was really reducible. If it was, the space of the reduced layer is used for the layer above the current one. *algorithm*:

```

BEGIN

allocate bottom layer;

fill bottom layer;

FOR all other layers from wafer upto surface DO

IF no space for layer reserved THEN

allocate layer;

FI;

fill layer;

IF not a not-reducible layer detected THEN

IF layer under current one reducible THEN

reduce layer under current one;

IF really reduced THEN

reserve space of layer under current one for

layer above current one;

ELSE

not-reducible layer detected;

FI;

ELSE

not-reducible layer detected;

FI;

FI;

ROF;

END:

subroutines:

CVERTEX_PTR_3 allocate_layer ();

void

fill layer ();

BOOLEAN

reduce_layer ();

void

init_layer ();

- fill_layer ()

synopsis:

void fill_layer ( module, layer number )

MODULE PTR

module;

layer_number;

int

```

.

-----

```

description:

Fills layer <layer number> of <module>. The layers of all called

modules should be filled before this routine is called.

algorithm:

BEGIN

{ fill the grid with the grids of the called modules: }

fill calls;

( fill the grid with all other objects: )

fill the layer with the in the input defined wires

for the module;

fill nwires;

fill vias;

fill nvias;

fill pvias;

fill equivalences;

END;

subroutines:

void fill_wires ();

void fill_vias ();

void fill_equs ();

void fill_calls ();

- fill_super modules ()

synopsis:

void fill_super_module ( module )

MODULE_PTR