## GM: a gate matrix layout generator

Citation for published version (APA):

Lieshout, van, G. J. P., & Ginneken, van, L. P. P. P. (1987). *GM : a gate matrix layout generator.* (EUT report. E, Fac. of Electrical Engineering; Vol. 87-E-179). Technische Universiteit Eindhoven.

#### Document status and date:

Published: 01/01/1987

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Eindhoven University of Technology Netherlands

Faculty of Electrical Engineering

# GM: A Gate Matrix Layout Generator

by G.J.P. van Lieshout and L.P.P.P. van Ginneken

EUT Report 87-E-179 ISBN 90-6144-179-X September 1987

# EINDHOVEN UNIVERSITY OF TECHNOLOGY

Faculty of Electrical Engineering Eindhoven The Netherlands

ISSN 0167-9708

Coden: TEUEDE

A. A.

GM:

A gate matrix layout generator

by

G.J.P. van Lieshout

and

L.P.P.P. van Ginneken

EUT Report 87-E-179 ISBN 90-6144-179-X

> Eindhoven September 1987

# COOPERATIVE DEVELOPMENT OF AN INTEGRATED, HIERARCHICAL AND MULTIVIEW VLSI DESIGN SYSTEM WITH DISTRIBUTED MANAGEMENT ON WORK STATIONS.

(Multiview VLSI-design System ICD)

code: 991

#### DELIVERABLE

Report on activity: 5.3.D: Implement totally integrated cell generator and place- and route scheme.

title: GM: a gate matrix layout generator

Abstract: We present a gate matrix cell generator which can layout any nMOS circuit. The circuit is specified as a netlist of parametrizable transistors. The size of the transistors can be freely specified thereby giving the opportunity of optimizing parameters as power, speed and fanout. Also shape, pinout and design rules can be parametrized. The pinout can be determined while building the gate matrix structure, by simply extending certain gates or nets to the correct side. The design rule parameters can be satisfied by a simple two dimensional grid-based compaction algorithm. The horizontal connections are realized in the metal layer and are called the nets. The vertical connections are realized in poly silicon and are called the gates. We used a new two dimensional folding algorithm, to improve the layout density and to manipulate the shape of the cell. Two dimensional folding allows nets to be assigned to the same row, aswell as gates assigned to the same column. The area used for small logic examples is smaller on average (upto 40% smaller) than the area used by a pluri cell style random logic generator.

deliverable code:

WP 5, task: 5.3, activity D.

date:

21-08-1987

partner:

Eindhoven University of Technology

authors:

G.J.P. van Lieshout and L.P.P.P. van Ginneken

This report was accepted as a M.Sc. Thesis of G.J.P. van Lieshout by Prof. Dr.-Ing J.A.G. Jess, Automatic System Design Group, Faculty of Electrical Engineering, Eindhoven University of Technology. The work was performed in the period from 1 January 1987 to 27 August 1987 and was supervised by ir. L.P.P.P. van Ginneken.

CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Lieshout, G.J.P. van

CM: a gate matrix layout generator / by G.J.P. van Lieshout and L.P.P.P. van Ginneken. - Eindhoven: University of Technology, Faculty of Electrical Engineering. - Fig., tab. - (EUT report, ISSN 0167-9708; 87-E-179)

Met lit. opg., reg.

ISBN 90-6144-179-X

SISO 663.42 UDC 621.382:681.3.06 NUGI 832

Trefw.: elektronische schakelingen; computer aided design.

## CONTENTS

|     | Abstract                                                                                                                                                                                                                                                                                                                 | 1                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.  | General Introduction                                                                                                                                                                                                                                                                                                     | 2                                      |

| 2.  | The gate matrix layout style                                                                                                                                                                                                                                                                                             | 4<br>4<br>7                            |

| 3.  | Structure of a Gate Matrix Layout Generator                                                                                                                                                                                                                                                                              | 11                                     |

|     | Generating the gate matrix structure                                                                                                                                                                                                                                                                                     | 13                                     |

|     | The gate order                                                                                                                                                                                                                                                                                                           | 16<br>16<br>17                         |

| 6.  | Column folding 6.1 The folding problem 1 6.2 The folding problem 2 6.3 The folding algorithm                                                                                                                                                                                                                             | 21<br>23<br>25<br>27                   |

| 7.  | The Net placement                                                                                                                                                                                                                                                                                                        | 29                                     |

|     | Net placement with column folding                                                                                                                                                                                                                                                                                        | 31                                     |

|     | The final steps of the placement                                                                                                                                                                                                                                                                                         | 33<br>33<br>33<br>34                   |

| 10. | The power lines  10.1 The Power Matrix                                                                                                                                                                                                                                                                                   | 35<br>35<br>36                         |

| 11. | Compacting the layout                                                                                                                                                                                                                                                                                                    | 39                                     |

| 12. | Some results                                                                                                                                                                                                                                                                                                             | 41                                     |

| 13. | Suggestions for continuation                                                                                                                                                                                                                                                                                             | 43                                     |

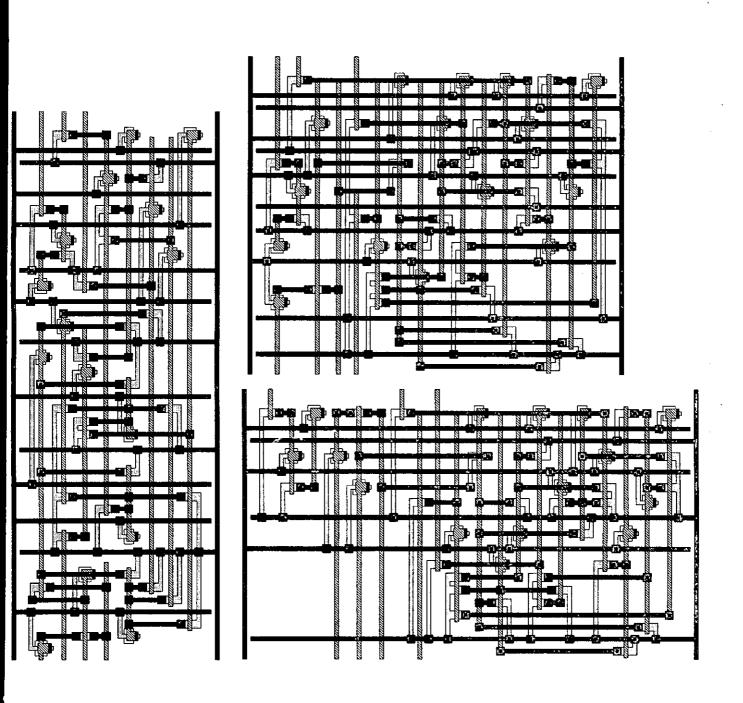

|     | Conclusions  Appendix 1: Literature  Appendix 2: Layout example (83 transistors)  Appendix 3: Larger layout example (180 transistors)  Appendix 4: An example of layout inefficien cy  Appendix 5: An example of shape flexibility  Appendix 6: Another example of shape flexibility  Appendix 7: Implementation details | 44<br>45<br>47<br>48<br>49<br>50<br>51 |

|     |                                                                                                                                                                                                                                                                                                                          | 52                                     |

### LIST OF FIGURES

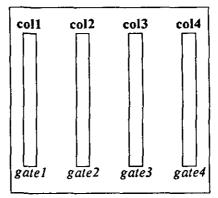

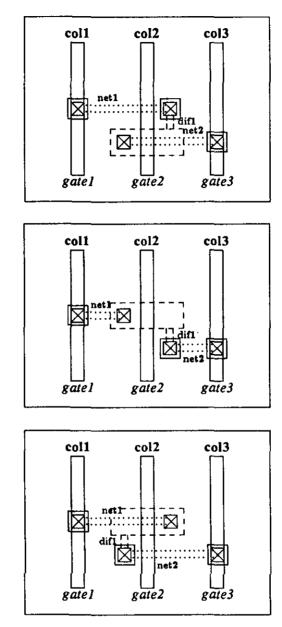

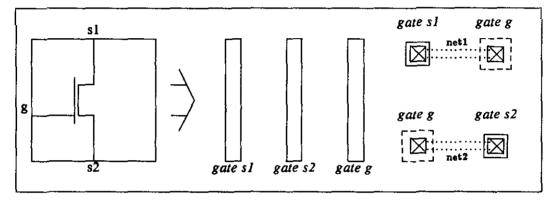

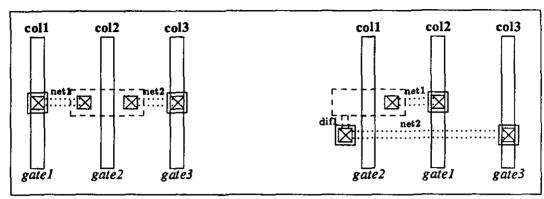

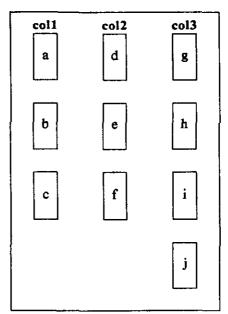

| Figure 1.  | Unfolded gates                                               | 4  |

|------------|--------------------------------------------------------------|----|

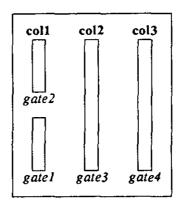

| Figure 2.  | Folded gates                                                 | 5  |

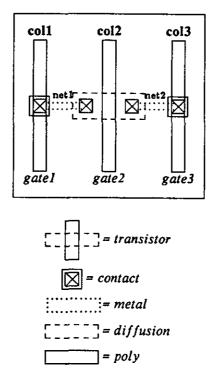

| Figure 3.  | Possible realization for a transistor                        | 5  |

| Figure 4.  | Four different implementations of a transistor               | 6  |

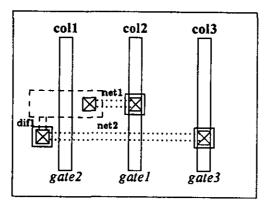

| Figure 5.  | Example of a gate situated in an outer column                | 7  |

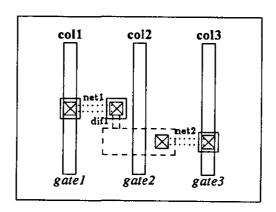

| Figure 6.  | Example of a net implemented in the diffusion layer          | 7  |

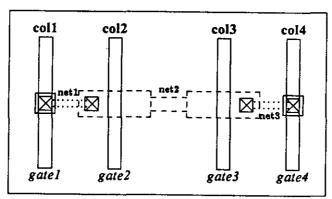

| Figure 7.  | Main Program Structure                                       | 11 |

| Figure 8.  | Transformation of a transistor into a layout structure       | 13 |

| Figure 9.  | Deleting a superfluous gate                                  | 13 |

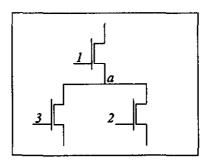

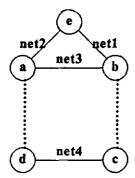

| Figure 10. | Circuit example                                              | 14 |

| Figure 11. | Illustration of the different gate groups                    | 18 |

| Figure 12. | Two realizations of a transistor                             | 19 |

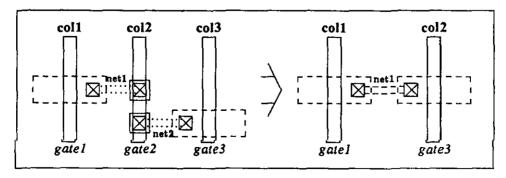

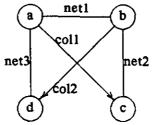

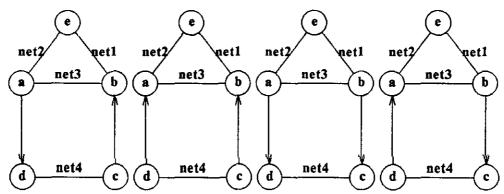

| Figure 13. | The $G_f$ old graph for the example                          | 22 |

| Figure 14. | Possible foldings for the example                            | 22 |

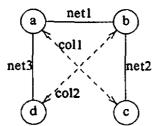

| Figure 15. | Example of a graph indicating a successful net placement     | 23 |

| Figure 16. | Example of unefficient folding                               | 24 |

| Figure 17. | G_fold with undirected edges                                 | 25 |

| Figure 18. | Possible realizations of fig.17                              | 25 |

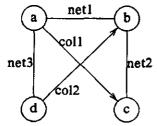

| Figure 19. | New $G_{fold}$                                               | 26 |

| Figure 20. | Example of a new G_fold graph                                | 26 |

| Figure 21. | Possible realizations of fig.19                              | 26 |

| Figure 22. | Acyclic new G_fold graph                                     | 27 |

| Figure 23. | Idea behind checking order for column folding                | 28 |

| Figure 24. | Example of a cross conflicts                                 | 39 |

| Figure 25. | Directions of design rule checking done by the row compactor | 40 |

#### Acknowledgements:

Before I start, I want to thank Lukas van Ginneken and Jos van Eijndhoven. Without their support and suggestions, I would never have come 80 far. I also want to thank Reinier van den Born, who made the laser jet layout pictures shown in the appendices.

There is one other group of people I should not forget. I want to thank all other students of the Automatic System Design group for never missing a single chance to delay my work.

#### Abstract

Lopez and Law introduced a new layout style in 1980: the gate matrix layout style. This matrix is made of intersecting rows and columns. Often, the columns are implemented in the polysilicon layer and the rows in both the metal and the diffusion layer; the transistors are situated on the intersections of rows and columns.

In this report, a gate matrix layout generator, GM, will be discussed. GM can generate layouts with any size of transistors; GM will always come up with a feasible result and GM allows the user to manipulate the shape of the final layout.

We will present the algorithms used in GM for signal ordering and folding and discuss the heuristics used for net placement. We will describe the addition of the power lines to the matrix and we will describe the compaction of the layout.

At the end, we will show some promising results generated by GM and compare them with layouts obtained from other layout generators.

#### 1. General Introduction

One of the current projects of the Automatic System Design group at the Eindhoven University deals with the application of the stepwise refinement technique in the layout design part of a silicon compiler.

The stepwise refinement technique was first described by Wirth [WIRT71] for programming purposes. Starting with a clear problem statement the problem is progressively redefined. Each decision should leave enough freedom to following stages to satisfy the constraints it created and at the same time rearrange the available data such that further meaningful decisions can be made in the next step.

The principles of stepwise refinement obviously apply to any complex design task based on a top-down strategy. It can also be used for layout generation [GINN84]. Say we want to generate a layout, consisting of several modules, defined as functional layout parts with a flexible shape. The size and shape of a module are constrained by the amount and type of circuitry that have to be accommodated into the module. These limitations can be found in the shape constraints.

Using the stepwise layout refinement technique, we start with the generation of a floorplan. First the modules are appointed to one out of two cells. Cells are collections of modules. They have a relative position; cell a can be situated to the right of cell b. The decision of which cell is suited for a module is primarily based on the resulting wiring length between the modules. Next, the modules within one cell are divided again, into smaller cells. This process continues until every cell contains only one module.

When the floorplan is complete, we know the relative position of every module; we know in what part of the layout it is going to be situated; we know the neighbouring modules; we know the topology of the layout. The exact shape of the layout is still unknown at this stage since we only have the shape constraints to work with. The geometrical details of the floorplan can now be determined.

We compute the shape constraints of all cells by adding the shape constraints of the different cells and modules it contains. This way, we will get the shape constraints for the total layout and are able to choose a certain shape for it. Then we work our way down again, specifying a shape for each cell and module.

The stepwise layout refinement technique is quite the contrary of other placement techniques. These work with totally specified modules, difficult to handle because of their inflexibility. In most cases, there is no possibility for adapting the modules to their environment. Using the stepwise layout refinement technique, the exact geometries of the modules are determined only after the generation of the floorplan.

If we want to exploit the benefits of this layout generation technique completely, we should be able to generate modules with the property of having very flexible shape constraints. In that case, the shapes of different modules can be well adapted to each other and cells containing several modules, can be made efficiently.

In recent years, a new layout style was introduced: the gate matrix layout style. Apart from being efficient, this style can be made to have the right shape flexibility.

To exploit the gate matrix layout style, a program, called GM, to generate gate matrix layouts has been developed. GM should generate the modules needed by the stepwise layout refinement technique. There were two demands set for GM:

- 1) The generated layout would have to be reasonably efficient.

- 2) The shape of the layout should be flexible.

Chapter 2 discusses the gate matrix layout style. The chapters 3 to 11 describe the

different techniques used in GM to generate a gate matrix layout. Results obtained with GM are shown in chapter 12, followed by some suggestions for continuation in chapter 13. Finally, some concluding remarks are made in chapter 14.

#### 2. The gate matrix layout style

The gate matrix layout style was introduced by Lopez and Law [LOLA80] in 1980. It can be regarded as a generalization of the earlier developed Weinberger layout style [WEIN67].

The gate matrix layout problem has received some attention in the past few years and various algorithms ([WING82], [WING83], [JTL183], [WIHU85], [DELA87]...) have been designed to automate the layout procedure. In this chapter I will introduce the gate matrix layout style and give a definition of the gate matrix problem (compare [WIHU85]).

#### 2.1 Introduction

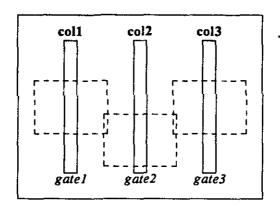

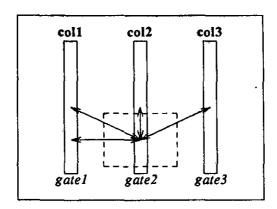

In the vertical direction of the gate matrix, the gates are situated in the different columns. If we only allow one gate in a single column, we get something like figure 1.

Figure 1. Unfolded gates

The gates will be implemented in the polysilicon layer. They will serve the dual role of transistor gates and interconnection.

There may be a gate for every *signal* present in the circuit or just for a distinct subset of all the signals. This depends on how we represent the circuit with the different gate matrix elements.

If we allow more than one gate into a single column, we could get the gate ordering shown in figure 2. Placing more than one gate into a single column is called *folding* (compare PLA folding).

Figure 2. Folded gates

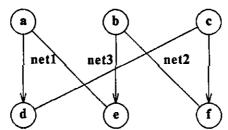

What we want to realize next, is a transistor. Figure 3 shows a possible gate matrix layout for a transistor. The gate of the transistor is situated in column 2. The drain and the source of the transistors are connected with gates 1 and 3 by two nets. Nets are usely implemented in the metal layer. What we call drain or source is unimportant for the whole transistor is symmetric.

Figure 3. Possible realization for a transistor

In the last figure, the nets were placed into the same row of the gate matrix. In that case, the transistor will always be placed in the same row also. We have to choose a position for the transistor if the two nets are situated in different rows. Look at figure 4; the resulting circuit is the same for all four. Only the position of the gate matrix elements near column 2 varies.

Figure 4. Four different implementations of a transistor

We use a diffusion run to get from one row to the other. This diffusion can be placed on either side of the transistor gate. If we allow no more than one diffusion run for every transistor, the transistor will have to be placed in one of the two rows containing a net.

Contrary to the situation of figure 3, in this case the layout is not completely specified after the net placement. The layout generator will have to decide upon where the diffusion runs and the transistors are going to be placed.

In the figures 3 and 4, the gate signal of the transistor was always situated in the middle column. An example of a gate signal in an outer column is shown in figure 5.

Figure 5. Example of a gate situated in an outer column

Not all nets are implemented in the metal layer. Figure 6 shows an example of a net ( net 2) implemented in the diffusion layer.

Figure 6. Example of a net implemented in the diffusion layer

We will gain some improvement of performance by implementing net 2 in the diffusion layer because of loosing two metal/diffusion contacts we would have had otherwise.

Having read this paragraph, the reader should have gained enough insight into the gate matrix layout style to understand the definition of the optimalization problem given in the next paragraph.

#### 2.2 Definition of the problem

One of the inputs for GM is a description of the circuit to be generated. The circuit is described on the transistor level. The transformation of this description into a layout can be divided into two separate problems:

- 1) First, we have to obtain a circuit description using gate matrix elements only.

- 2) Next, these elements have to be ordered efficiently.

Out of the first step, we get a description of the circuit using elements of the following sets:

$T = \{ t_i \mid 1 \le i \le number \ of \ transistors \} : set of transistors$   $G = \{ g_i \mid 1 \le i \le number \ of \ gates \} : set of gates$   $N = \{ n_i \mid 1 \le i \le number \ of \ nets \} : set of \ nets$

We also get information about the relations between these elements. This information can be found in the next Incidence matrix:

Define: Incidence matrix I[number of gates][number of nets]:

#### I[i][j] =

- -1: there is a connection between gate i and net j; no transistor is present.

- 0: there is no connection between gate i and net j.

- 1.. (number of transistors): on the intersection of gate i and net j a transistor is present with transistor number I[i][j].

Apart from this circuit description, there are two other inputs to the placement problem:

- 1) The structure of a gate matrix.

- 2) Details about the technology in which the layout is going to be generated.

#### ad 1)

The program has to know certain details about the structure of a gate matrix. In this description the following sets are defined:

$C = \{c_i \mid 1 \le i \le number \ of \ columns \ \}$ : set of columns of the gate matrix

$C' = \{ c'_i \mid 1 \le i \le number \ of \ C \ columns + 1 \}^1 : \text{ set of columns,}$ situated in between the polysilicon columns of C

$R = \{ r_i \mid 1 \le i \le number \ of \ rows \}$ ; set of rows of the gate matrix

ad 2)

While generating the gate matrix, we have to know details about the technology in which the gate matrix is going to be realized. It will specify facts like which layers are allowed to overlap or what the distance between two metal wirings should be to avoid short circuiting... This technology description is the third input.

One last gate matrix element has to be mentioned: the diffusion runs.

$D = \{ d_i \mid 1 \le i \le number \ of \ transistors \} : set \ of \ diffusion \ runs \ in \ the gate \ matrix$

Which transistors will cause a diffusion run is determined during the net placement.

The first column of C' is situated at the left of the first column of C; the last column of C' is situated at the right of C thus C' has one element more than C.

Knowing the three inputs for the placement problem, we are now able to define the placement problem. The gate matrix layout is completely specified if we have determined the next four functions:

1) The gate assignment function f assigns the different signals of the set G, to the columns:

$$f: G \longrightarrow C$$

2) The net assignment function h assigns nets to the rows of the gate matrix:

$$h: N \longrightarrow R$$

In the previous paragraph we discussed the problem of the diffusions. Consider a transistor whose drain and source are connected to nets m and n respectively. If h(n) <> h(m), there will be a vertical diffusion run between h(n) and h(m). For these diffusions, we define a third function:

3) The diffusion assignment function k assigns diffusion runs to the intercolumn area of the gate matrix:

$$k: D \rightarrow C'$$

One last function is needed to complete the description. We have to choose the positions of the different transistors.

4) The transistor assignment function *l* assigns transistors to the rows of the gate matrix.

$$l: T \rightarrow R$$

A generated layout is said to be realizable if all the diffusion runs defined by k are realizable without collisions. Say we have two diffusion runs: diffusion 1 from net  $dif1\_begin$  to net  $dif1\_end$ , and diffusion 2 from net  $dif2\_begin$  to  $dif2\_end$   $(h(difx\_begin) < h(difx\_end))$ . A collision occurs if:

If we take the "unfolded" approach, the optimal gate matrix layout problem can be stated as follows:

Given a set of transistors T together with the set of distinct gates G and the set of nets N, find functions f,h,k and I such that in the layout:

- 1) the number of rows is minimum.

- 2) the layout is realizable (no diffusion collisions).

The layout generator we developed is able to place more than one signal into a column. If we allow folding, the problem should be stated in a more general way:

Given a set of transistors T together with the set of distinct gates G and the set of nets N, find functions f,h,k and I such that in the layout:

- 1) the area used is minimum.

- 2) the layout is realizable (no diffusion collisions).

Most layout generators use a two-stage approach to the problem. First the function f is optimized and afterwards h is optimized. Some try to optimize the two functions in one stage [DEVA86]. I chose for the two-stage approach because it is generally not as time consuming as the second approach and because more literature is available about this approach.

However, the probability of choosing a function f' with a bad column order for the resulting h is probably smaller in the one-stage approach because of the closer relation between f and h.

If f and h are determined, it is quite easy to determine satisfying functions k and l, as long as they still exist. The functions f and h may disable the possibility of creating functions k and l causing no diffusion collisions. While determinating f and h, we will have to keep the realization of k and l in mind.

The purely on efficiency based problem descriptions given above, can be extended with several extra constraints e.g. a maximum width or height or some kind of aspect ratio. In the algorithms we will discuss, the user is able to manipulate the shape of the gate matrix during the determination of f.

#### 3. Structure of a Gate Matrix Layout Generator

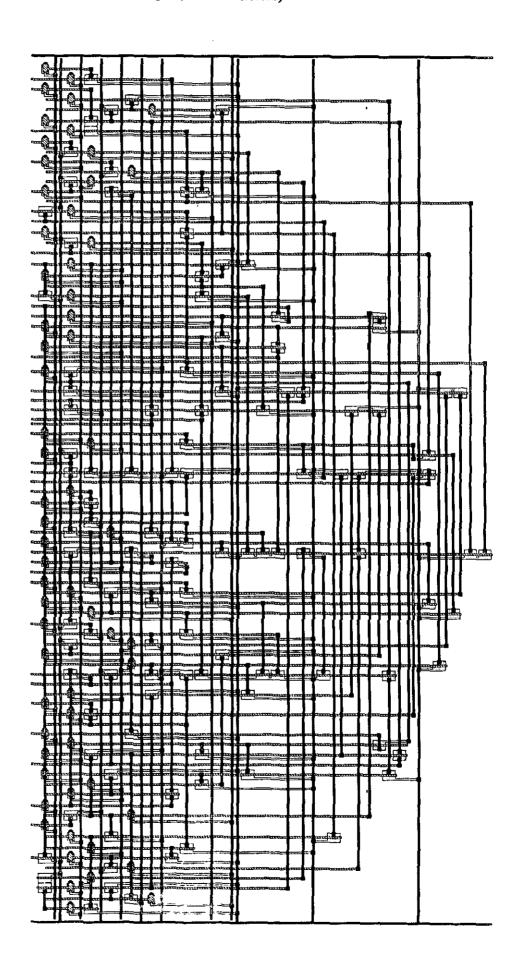

This chapter discusses the structure of our gate matrix layout generator GM. The layout generator is subdivided into several functional blocks. Figure 7 shows a diagram of these blocks.

Figure 7. Main Program Structure

- 1) We start with loading in the necessary data. The layout generator checks the data format of the input.

- 2) Block 2 generates a gate matrix structure for the circuit. It determines what signals are going to be represented by nets, what signals are going to be represented by gates, what extra nets have to be added for output signals etc. . Chapter 4 discusses this block in more detail.

- 3) If the two-stage approach for the optimization of the gate matrix is taken, the next step is the optimization of the function f. This is a very important part of the layout generator. A bad gate order can enlarge the layout area with a factor 2 or even more. Chapter 5 discusses different approaches to this problem. If we allow more than a single gate into one column, f becomes a bit more complicated. An extension of f for this purpose, is discussed in Chapter 6 on column folding.

- 4) The second stage of the two-stage approach is the optimization of the function h. We place the different nets into the rows of the gate matrix. Chapter 7 discusses the approach for net placement in an unfolded gate matrix and in chapter 8 this approach is expanded into one suitable for a gate matrix with folded gates.

- 5) Chapter 9 discusses the determination of k and l. If GM generated an unrealizable layout (a layout with diffusion collisions), it will have to start anew at block 2. This time, we would like to have an increased probability of generating a realizable layout. Chapter 9 also deals with these questions concerning the realizability of the layout.

- 6) For reasons to be explained in chapter 4, many gate matrix layout generators place the power lines after the complete placement of the signal containing part of the gate matrix. The "normal" gate matrix nets do not supply the power to the circuit. Chapter 10 shows how the positions of the power lines can be determined.

- 7) Moving towards the end, the final coordinates of every element of the gate matrix are determined. This "compaction step" is discussed in chapter 11.

- 8) The final step is the actual generation of the layout. This is more a matter of solid bookkeeping than of great algorithmic expertise. If all details about the gate matrix are exactly computed in the previous part, the gate matrix is uniquely described. In our implementation of GM, only the center coordinates of every gate matrix element arrive at block 8. The coordinates of the different element parts still have to be computed. Although this block is not really all that simple, it is not interesting enough for a detailed discussion.

#### 4. Generating the gate matrix structure

Before any optimization methods can be used, the circuit has to be represented by gate matrix elements. This gate matrix structure is generated in three stages:

The first stage deals with all the transistors. Every transistor has three connections with the outer world. We generate a single gate for every single signal.

One transistor will generate (at most) two nets, each net containing one half of the transistor. Thus, one transistor will result in the gate matrix elements given below:

Figure 8. Transformation of a transistor into a layout structure

In the final layout, the different components are able to realize a transistor as shown in chapter 2.

The second step has to remove some overhead produced in the first step. We can delete a gate out of a column if:

- -The gate is not used as a transistor gate.

- -The gate does not have to be connected to "the outside world".

- -The gate is connected with two nets.

The deletion is shown in figure 9.

Figure 9. Deleting a superfluous gate

As a result of this step, we now have nets connecting two transistors. No such

nets were generated by the first step.

The third step generates extra nets for output signals. If the user wants to have an output to the right or the left side of the gate matrix, an extra net is generated, connecting that specific gate and the right or left border of the gate matrix<sup>2</sup>.

Note that all the generated nets have exactly two terminals. They can be divided in 3 categories:

OT: nets with on one side a transistor piece and at the other side a poly/metal contact. These nets are generated in step 1.

TT: nets with a transistor piece on both sides. These nets are generated in the second step.

00: nets with on one side a poly/metal contact, and at the other side a terminal. These nets are generated in the third step.

The reader might wonder if there are not any "but's" for the gate matrix structure just generated. And indeed, there is one. Look at the following example:

Figure 10. Circuit example

Signal a will result in a gate placed in a column and three nets will leave from this column. Say, the gate representing signal a is placed into column 2, and the gates representing the transistor gates are placed into columns 1,5 and 6. The three nets leaving from column 2 are connected with columns 1,5 and 6 respectively. After the placement of the first two nets, signal a is already present as far as column 5. Generating the third net, this information is not used: not a net from 5 to 6 is generated but a net from 2 to 6. This disadvantage becomes particularly clear if we have signal connected to many other signals.

The caused disadvantage may seem bigger then it really is:

1) We can reduce the disadvantage by taking a different approach to some nets. Chapter 10 discusses the special approach we used for the power supply (a heavily connected "signal").

Note: Because of this special approach to the power supply, no nets resulting from connecting a transistor to the power supply will be found in the gate matrix structure. These connections are added to the

<sup>2.</sup> If the user wants to have a certain signal as an output to the bottom or top side of the gate matrix, we simply extend the gate to that specific border of the gate matrix.

gate matrix afterwards ( see chapter 10). A consequence of this approach is the fact that there is only one net present in the gate matrix structure, containing a transistor piece for a transistor connected to the power supply.

2) In a technology with only one metal layer, both sides of most transistors will have to be reached by nets placed in this metal layer. It will not be possible to continue a net, coming from one direction, into the other direction because a net is already present at the other side of the transistor.

Apart from the nets connected to the power supply, there is one other type of nets that will not be found in the gate matrix structure. In this case it concerns nets connecting a transistor gate with the source or drain of the same transistor. We remove these nets from the gate matrix structure and mark the transistor. In the layout, we will place a diffusion/poly contact to realize the connection.

At this stage, we have determined the gate matrix structure. Now we know the different elements of the gate matrix, which order can be optimized in the next parts of the layout generator.

#### 5. The gate order

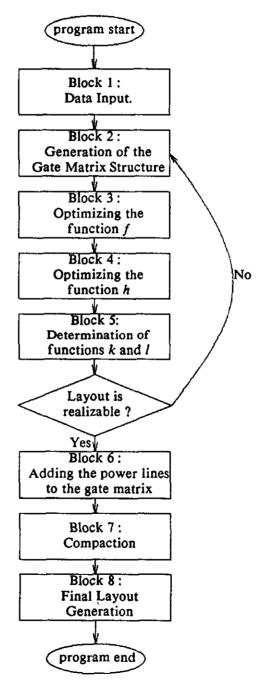

The first optimization problem is to determine the gate order in the columns. The order generated in the previous chapter (gate 1 into column 1, gate 2 into column 2 ...), does not have to be efficient at all. At first, only one gate is placed into a column. Placing more than one gate in a column is seen as a separate optimization problem which will be discussed in the next chapter.

We want to minimize the number of rows of the gate matrix, needed by the nets. Although not equal, this problem is highly correlated with the problem of finding a gate order resulting in a minimal total net length.

Probably because the importance of this problem, most of the literature on gate matrix layouts deals with this optimization problem. After a brief description of several possible solution methods, I will discuss the algorithms used in GM.

#### 5.1 Some ordering methods

Probably the most productive author on gate matrix layout generators is Omar Wing. Since the early eighties, he writes about this subject. He started with an approach to this linear gate array problem, similar to the one dimensional logic gate assignment introduced by [OHMO79]. First he generates a matrix containing all connections of nets and gates. Look at the next matrix<sup>3</sup>:

|      | gatel | gate2 | gate3 | gate4 |

|------|-------|-------|-------|-------|

| netl | 0     | 1     | 0     | 1     |

| net2 | 1     | 0     | 0     | 1     |

| net3 | 1     | 0     | 1     | 1     |

| net4 | 0     | 1     | 1     | 0     |

In this matrix, we can not see the net intervals clearly. The matrix does not show that net 1 is also positioned at col3. We can change this by filling up the matrix: substitute on every row, the 0's situated between 1's by 1's. Now the matrix becomes:

|      | gatel | gate2 | gate3 | gate4 |

|------|-------|-------|-------|-------|

| netl | 0     | 1     | 1     | 1     |

| net2 | 1     | 1     | 1     | 1     |

| net3 | 1     | 1     | 1     | 1     |

| net4 | 0     | 1     | l     | 0     |

This last matrix has the "consecutive 1's property": in every row the ones are grouped together.

If in one column of the matrix, two nets have 1, this means that if we would take the gate order of the columns in the matrix, those two nets would overlap at that particular column. The matrix is a representation for an interval graph [WIHU85]: the columns of the matrix are the vertices and there is an edge from vertex a to b if they have a 1 situated in the same column.

Nets which have a 1 positioned at the same column, form a clique in the interval

<sup>3.</sup> This matrix resembles the Incidence matrix of chapter 2. The matrix shown above can be obtained out of the Incidence matrix by substituting a one for every non zero element in I.

graph. The number of tracks needed in the final layout is equal to the largest clique number thus equal to the largest number of 1's positioned in a column. Now we can state the optimization problem:

Find a permutation of the columns such that if each row without the consecutive ones property is filled with ones, the largest number of ones positioned in any column is minimized.

Unfortunately, it is shown in [KAFU79] that this problem is NP-hard.

Omar Wing used several heuristics described in [WING82], [WING83] and [WIHU85] to find a reasonable result. Columns are placed one by one, at each stage trying to keep the number of necessary 0 to 1 substitutions as small as possible.

A some what different approach is used by [JTLI83]. He uses a different matrix to describe the problem but he also has to solve the problem of filling a matrix in order to get the consecutive ones property.

In [DEKR87], it is shown that there is a family of problems for which the ratio of the number of tracks, resulting from the two optimization methods described above, and the minimum number of tracks is unbounded.

Another approach is described by Leong [LEON86]. He used an algorithm based on simulated annealing. A temperature schedule, a cost function and several types of moves are described.

As mentioned in chapter 3, some optimization methods use a two dimensional placement to obtain the gate order and the gate folding in one step. In GENIE [DEVA86], Devadas and Newton use an algorithm again based on simulated annealing, to obtain a 2 dimensional order. Although the results shown look very promising, time complexity will become a problem for larger layouts. It would be nice to implement a two dimensional approach into GM in the near future and compare the results with the results obtained by the algorithm of paragraph 5.2.

The first algorithm I implemented, was the one described by Omar Wing in one of his more recent publications [WIHU86]. The gate order was based on the approximation algorithm described by Asano [ASAN82]. Some changes were made to this basic algorithm, for example Wing's algorithm uses the information about the size of the different components.

If we compare the results obtained by this algorithm, with the results from the algorithm we will discuss in the next paragraph, we have to decide in favor of the second algorithm. Wing only looks at the number of new nets he is introducing while placing a new gate. He does not take into account the number of finishing nets. We would need more time to determine the exact cause of the difference in performance between the two algorithms but at a first glance, this looks the main reason.

#### 5.2 A Kang based algorithm for gate ordering

The algorithm finally implemented in GM is based on an algorithm described by Kang [KANG83]. This linear ordering algorithm was already used for standard cell and gate array layout. The algorithm is given below:

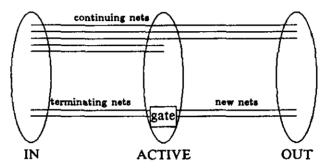

- 1) Read in the information about the circuit and put all the gates into OUT.

- 2) Select the most lightly connected gate from OUT. ( This first column is called the seed of the placement ).

- 3) Move the selected gate from OUT or ACTIVE to IN, and all gates connected to it from OUT to ACTIVE.

- 4) If ACTIVE is empty, go to 2. Otherwise select a gate from ACTIVE and go to 3.

- 5) Repeat 3-4 until OUT is empty.

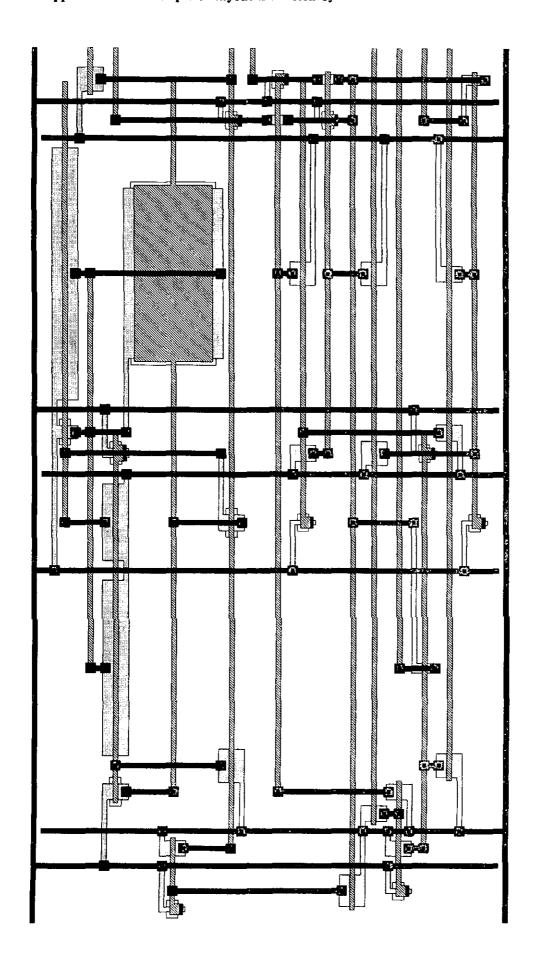

Figure 11 should illustrate the different groups. The gates in IN are already placed. The ones in ACTIVE are possible candidates for placement and the rest is situated in OUT.

Figure 11. Illustration of the different gate groups

The algorithm works very fast; O(col\*col). This is partly due to the fact that only gates situated in ACTIVE are candidates for placement, not all the unplaced gates. We could take the groups ACTIVE and OUT together; the algorithm becomes more simple and a better performance will be the result ( we remove an extra constraint ). It will increase the time usage of the algorithm.

In step 4 of the algorithm, a gate is chosen. Kang defines the *net gain*: the *net gain* is the number of new nets minus the number of terminating nets if a certain gate would be placed next.

The selection rules described by Kang are:

- 1) First, select a gate with minimum net gain.

- 2) For a tie, select one with larger number of terminating nets.

- 3) For a tie, select one with larger number of continuing nets<sup>4</sup>.

- 4) If tie again, select lighter one (least number of connected nets).

In figure 12, two realizations of a transistor are shown. It may be clear that we prefer the left situation. The right situation uses more diffusion space. Can we incorporate this fact into the selection rules?

The answer is Yes (of course): we do not want to place a gate functioning as a transistor gate, if both source and drain are not placed yet. A function, say two\_track(), should compute the number of these drain source conflicts for a certain gate, would this gate be placed next. If two\_track(gate1) > two\_track(gate2), we prefer gate2 to be placed instead of gate1.

The remaining difficulty is where this selection rule should be fitted into the old

<sup>4.</sup> I did not implement this selection rule because if two gates introduce the same number of terminating nets, they will always have the same number of continuing nets.

Figure 12. Two realizations of a transistor

selection rules. In GM, we choose to integrate it into the first selection rule, which becomes:

1) Select gate with Minimum net gain + two track(gate).

I would probably be wise if the weight of two\_track in this selection rule could be varied; one could think of an input variable specifying the weight of a gate source conflict in terms of an extra net gain. Two\_track() will add the input variable to his total for every gate source conflict a column placement would introduce.

#### 5.2.1 Seed selection

Step 2 of the Kang algorithm chooses the most lightly connected gate from OUT to start with. It may be clear that we do not want to start with a heavily connected gate, but does a lightly connected gate always result in an efficient placement?

I tested the placement algorithm using different seeds and found that the placement depends very strongly on the seed. In general, it is true that the best results are obtained starting with a relatively lightly connected seed. But, it is also true that the difference in total net length between two placements both starting with a 'most lightly connected seed', can be very large. In some examples, differences in total net length up to 30% were reached.

For this reason, we placed an extra option into GM. GM will then try out all most lightly connected seeds and continue with the one resulting in the smallest total net length.

Note: If the user has specified terminals at the left side of the gate matrix, we do not have the problem of choosing a seed. In that case the "column", connected with all nets realizing an output at the left side, will be the seed.

#### 5.2.2 Improving the result

We were still not satisfied with the result obtained. There should be some extra improvement possible. This time, the time complexity was of no importance; these extra steps should be optional. After some experimental work, the user could use these options to get a final result. Two strategies are implemented:

1) The first thing we did is, if the algorithm has decided what gate should be placed, an extra step decides whether this gate should be placed at the back of all the gates placed until now or in front of these gates. This decision is based on total net length.

2) We also thought of improving the result by performing swap operations; we started with trying to swap every gate with one of the adjacent columns and a considerable improvement of the total net length was obtained. Continuing this idea, we came up with the next swapping routine:

#### **BEGIN**

lastcol = number of columns.

Notice that the algorithm is purely based on net length and does not consider the diffusion size of the different transistors or the number of tracks the gate matrix is going to use. So in a way, we spoil the former result.

The swapping routine does not always result in a decreased number of tracks but, certainly for larger layout examples, the improvement was drastic. For a large unfolded gate matrix example, the number of tracks was reduced from 39 to 29.

We also tried to achieve improvement by using mirroring routines. We mirrored a certain number of adjacent columns. They proved very useful working at the traveling salesman problem. Nevertheless, probably due to the different connectivity structure of the problem<sup>5</sup>, the total net length resulting from these routines had a worse average and a larger spread than the results from the swapping routines.

<sup>5.</sup> In the traveling salesman problem every element is only connected to two other elements. If we mirror a certain group of adjacent elements, only two connections between this group and all other elements change. Mirroring a group of gates in the gate matrix will generally affect more than just two nets. It will also affect nets starting somewhere in the middle of the group and connected to elements outside the group.

#### 6. Column folding

What we have up till now, is a linear ordering of gates in the columns, every gate using a single column. If we want to fold different gates in one column, we will have to establish what columns are allowed to be folded.

There are a few reasons why two gates can not be folded into one column:

- -If two gates are in- or output gates at the same side (bottom or top) of the gate matrix, the gates can not be placed into one column.

- -If two gates are interconnected by a net, the two gates can not be placed into the same column ( the net would have to be folded ).

- -For reasons to be explained in the chapter on net placement with column folding, we do not want to fold gates connected to the same net path. A net path is a sequence of nets interconnected by diffusion runs.

We can generate a matrix FOLD using the facts stated above:

FOLD[gate1][gate2] = TRUE: if only one pair of gates of the gate matrix is going to be folded, it is allowed to fold the gates gate1 and gate2.

FOLD[gate1][gate2] = FALSE: otherwise.

Taking care of the matrix FOLD, does not guarantee that we will be able to place all nets into the gate matrix. This is due to the following fact:

Say gate a and b are placed in the same column and gate a is placed above gate b. All nets connected to gate a will have to be placed before any net connected to gate b can be placed. Only then we know the row in which gate b can start.

The following example might put things into a clearer perspective: We have 4 columns (a,b,c,d) and 3 nets (1,2,3). Their relations are given in the table below:

|   | а | b | C | đ |

|---|---|---|---|---|

| 1 | _ | _ |   | į |

| 2 |   | - | - |   |

| 3 |   |   |   |   |

Explanation of the figure: e.g. net 3 is connected to the gate a and the gate d. Recall that all the nets are two terminal nets.

Knowing the connections, we can generate the matrix FOLD:

<sup>6.</sup> The reader may wonder why the gate ordering and the gate folding are separated into two different parts of the layout generator. It is true indeed, that the resulting ordering would probably be better if the intergrated gate placement was used but then again this could be much more time consuming.

| FOLD |   |   |   |   |  |

|------|---|---|---|---|--|

|      | a | b | С | d |  |

| a    | 0 | 0 | 1 | 0 |  |

| b    | 0 | 0 | 0 | 1 |  |

| С    | 1 | 0 | 0 | 0 |  |

| d    | 0 | 1 | 0 | 0 |  |

Everything looks fine if we fold gates a and c into column 1, and gate b and d into column 2. But what happens if we start to place the nets:

First, we place net 1. So gate a has started in column 1 and gate b has started in column 2. Next, we want to place net 2. We can make a connection to gate a, but not to gate d because gate b is not placed completely yet. So we skip net 2 and try to place net 3. Again no luck; gate c can not be used because of the incomplete gate a. So there is no placeable net and the net placement will fail.

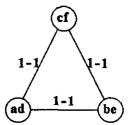

We can display the represent the situation by a graph G fold. G\_fold is made out of:

nodes: one for every gate.

labeled directed edges: a directed edge from node a to node b means that placement of nets connected to gate b can only occur after complete placement of all the nets connected to node a. The edge is labeled with the number of the column that caused it.

labeled undirected edges: an undirected edge from node a to node b indicates that the gates represented by the nodes are connected to the same net path. The placement of a net represented by an edge between node a and b depends on both nodes. The edge is labeled with the net number.

In figure 13, the G\_fold graph for the folding chosen above is shown.

Figure 13. The G\_fold graph for the example

The matrix FOLD excludes several gates from folding but does not guarantee successful placement if we fold gates which are allowed to be folded by FOLD. In figure 14, possible foldings are represented by dashed directed edges.

Figure 14. Possible foldings for the example

If we want to perform as many foldings as possible, we have to find a graph G\_fold with as many directed edges as possible and still describing a placement, guaranteed to succeed.

In the next two paragraphs, two possible approaches to this problem will be discussed. The approach discussed in 6.1 will be able to find the optimal G\_fold but is also very time consuming and for reasons to be explained in paragraph 6.1, the generated layout may still be very unefficient. Paragraph 6.2 describes a more simple approach, not as time consuming but then again also not as smart as the first approach.

#### 6.1 The folding problem 1

Take another look at figure 13. The reader may wonder how G\_fold displays a failing placement. It can be found using the next algorithm:

- 1) Label all the nodes with no incoming directed edges; these gates can be placed right away.

- 2) Label all nets connected to two labeled nodes.

- 3) Try to label the unlabeled nodes. A node may be labeled if all the connected undirected edges are labeled and if all the directed edges pointing at the node come from a labeled node.

- 4) If there are no edges or nodes labeled in the last two steps and not all nodes and edges are labeled yet, the folding indicated by the graph will result in a failing net placement.

If all edges and nodes are labeled, the folding indicated by the graph will result in a successful net placement. If not all edges and nodes are placed yet, goto step 2.

If we apply the algorithm to the example given in figure 13, we get:

- 1) label node a and b

- 2) label net 1

- 3) no new nodes labeled

- 4) goto 2

- 2) no new nets labeled

- 3) no new nodes labeled

- 4) --> failing net placement

If we apply the algorithm to the example given in figure 15, we get:

Figure 15. Example of a graph indicating a successful net placement

- 1) label a and d

- 2) label net 3

- 3) label node b

- 4) goto 2

- 2) label net 1

- 3) label node c

- 4) goto 2

- 2) label net 2

- 3) no new nodes labeled.

- 4) --> successful net placement.

What is the complexity of the search. Say the number of nodes is n and the number of edges is e. In the worst case, every time we apply step 2 and 3 only one additional node is labeled. This way, we cycle O(n) times through the loop. Rule 3 is the most time consuming step. Every time all unlabeled nodes have to be examined for possible labeling. A node can be connected to e edges at most so we will have to perform e comparing operations at most. Applying step 3 will thus cos t O(n + e). This results in a total complexity of O(n + e).

Having determined a search algorithm, we could try out all possible combinations of gate foldings and choose the one resulting in most foldings, still representing a successful net placement. This way, we will find the gate order with most foldings for sure. Apart from being very time consuming, there is another disadvantage to this method. Look at the configuration in the next figure:

Figure 16. Example of unefficient folding

If gates a and d only have connections with one gate from col 3, say gate j, and a and d are placed at the top of col 3, we would like gate j to be placed at the top of column 3 also. If gate j, like in the figure, is placed at the bottom of col3, gates a and d will become much longer than necessary.

We could avoid this situation by choosing the gate order in a column during the net placement. If we have placed gates a and d, nets from these gates will need gate j, and gate j will be placed at the top of col 3. The exact mechanism is described in chapter 8. As a consequence of this approach we can only determine what gate is going to be placed in what column during the folding. The order within a column is not determined yet. This approach is described in the next paragraph.

#### 6.2 The folding problem 2

If we do not know the ordering of the gates in a column, the directed edges in G\_fold become undirected edges. Look at fig 17.

Figure 17. G\_fold with undirected edges

This figure corresponds to the four possible orderings shown in figure 18:

Figure 18. Possible realizations of fig.17

If we want to be sure of a succeeding net placement, no possible gate ordering should result in a failing net placement. Out of the four possible realizations of fig 18, two result in a failing net placement, so the situation of figure 17 will have to be forbidden.

How can we find out if a folding is legal?

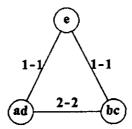

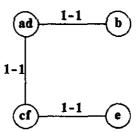

We will change the fold graph a bit. If gates are folded into the same column, we will represent those gates by one node. We also substitute edges connected to the same two

<sup>7.</sup> Note that if we forbid this situation, we also throw away two legal foldings.

nodes by one edge, at each node labeled with the number of gates the nets, the edge represents, are connected to. E.g. a new edge representing one old edge will be labeled with 1-1. An edge representing two nets, connected to different gates out of the same column, will be labeled with 2-2....

The graph of figure 17 now changes into the graph shown in figure 19.

Figure 19. New G fold

What kind of structures are forbidden in this new G\_fold graph. Having read the beginning of this chapter, it may be clear that we do not allow an edge with label 2-2 or higher between two nodes.

Another situation is shown in figure 20.

Figure 20. Example of a new G fold graph

The graph in figure 20 represents 8 possible foldings. One of them is shown in figure 21.

Figure 21. Possible realizations of fig.19

This folding will result in a failing net placement so we have to forbid the situation of figure 20. We could change it into figure 22.

In the new G\_fold graph, we have to check for loops between nodes containing more than one gate. It is easy to check for this property: for every subgroup of interconnected nodes containing more than one gate, the number of edges has to be one less than the number of nodes<sup>8</sup>.

<sup>8.</sup> Due to a lack of time, this 'cycle check' is not implemented in GM yet.

Figure 22. Acyclic new G fold graph

Resuming; the second approach is less time consuming but will forbid a number of foldings unnecessarily. It does have the advantage of giving the net placement the freedom of choosing the gate ordering. The second approach is implemented in GM.

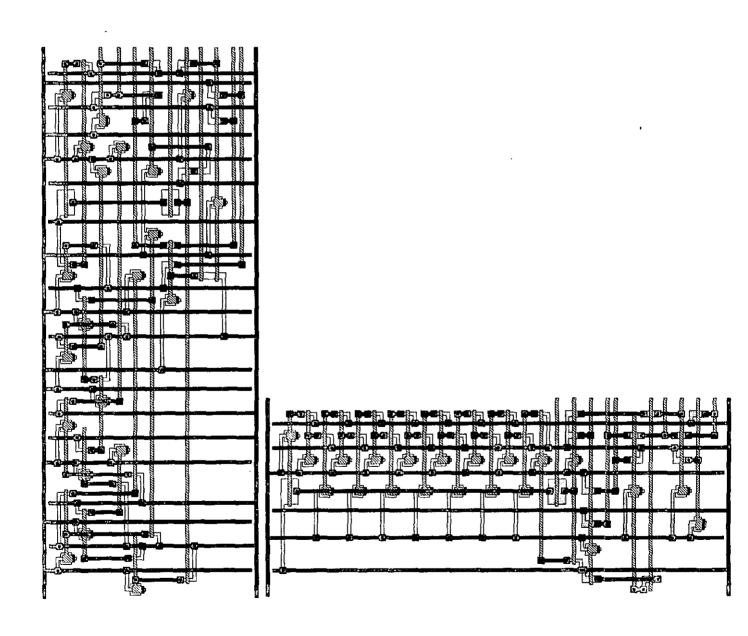

#### 6.3 The folding algorithm

Before we give the final folding algorithm, a few problems will have to be discussed.

Should we try to fold a certain gate with every other gate or just with a certain subgroup of the other gates?

Say we have a linear ordering of 20 gates coming from the gate optimization. The ordering is primarily based on the number of connections between the different gates. If we would fold gate 18 with gate 3 into column 3, the result would probably be poor. Signal 18 will be highly connected with gates near 18 (16,17,19,20). If we fold 18 and 3, many nets will have to go from the left side of the gate matrix (column 3), to the right side of the gate matrix (16,17,19,20). This would cost a lot of rows.

So we only want to try to fold gates with their "surrounding" gates. A solution may be to let the user specify this surrounding by an input variable BACK\_COL. BACK\_COL is the number of columns we go backwards during the folding, to see if folding is allowed.

Now another problem becomes evident. Let the gates 1,2 and 3 be placed into columns 1,2 and 3. If the user has specified that we are allowed to go 3 columns backwards for a folding attempt, gate 4 could be folded into columns 1,2 or 3. If all the foldings are legal, which one of them do we prefer?

One might think column 3 because if gate 5 is placed in column 4, and gate 4 and 5 are highly interconnected, the nets will stay short. If we use this "thought", we should work our way, checking for possible folding, form column 3 to column 2 to column 1.

In GM, we choose for the reverse order (1,2,3), because of the following consideration: Say, we fold gate 4 into column 3. Again I want to point at the fact that the linear ordering is primarily based on the interconnecting nets. So in the described situation, it is very likely for gate 5 to have an interconnection with gate 4 or 3. This will disable the folding of 5 into column 3. Maybe 5 can be folded into column 2. Then we are reversing the column order, which will cause difficulties at the left end.

The idea is shown in figure 23. Distance A, generated by checking for possible folding from the left to right to the left, is smaller than distance B, generated by checking for possible folding from the right to the left.

Figure 23. Idea behind checking order for column folding

I admit that the given evidence is not completely satisfying and further research could result in better folding. It might even be true that it is best to change the direction of the search depending on how much folding we want to have in our gate matrix (columns <--> rows).

One last consideration has to mentioned. If we, having taken all the facts mentioned above into account, are allowed to fold two gates, will we always want to fold them? If we have a layout which is unfolded realisable using 8 rows, and the folding of the gates a and b would result in using 15 rows just for these two gates, we probably do not want to execute the folding. We have to arm ourselves against such a mistake:

First we make an estimation of the number of rows we want the gate matrix to use. The user may specify ESTIMATION\_CO and the number of rows wanted, ESTimation\_NUMBer\_TRAcks, is determined by dividing the number of transistors in the gate matrix with the ESTIMATION\_CO. An estimation for the number of rows needed for a certain column, after folding another gate into that column, can be divided into 3 groups:

- T1: Number of nets connected to gates in the column before the latest folding.

- T2: Number of nets that cross the column.

- T3: Number of nets connected to the gate, candidate for folding.

Now, if (T1 + T2 + T3) <= ESTimation\_NUMBer\_TRAcks, we decide to fold the gate into the column.

The total folding algorithm is given below:

#### **BEGIN**

**END**

```

place gate 1 into column 1;

PLA_COUNT = 1;

FOR ( all gates )

FOR ( COL = PLA_COUNT - BACK_COL; COL <= PLA_COUNT; COL ++)

IF (the matrix FOLD allows the folding &&

T1 + T2 + T3 <= EST_NUMB_TRA &&

folding is allowed by new G_fold graph)

fold gate into column COL;

ELSE

{

PLA_COUNT = PLA_COUNT + 1;

place gate into column PLA_COUNT;

}

```

PLA\_COUNT = number of columns ( out of C ), containing gates.

#### 7. The Net placement

In step four of the total gate matrix realization the nets have to be placed in the rows of the gate matrix. I have chosen for a greedy routine, based on the left edge algorithm. If unconstrained left edge would be used, the realizability of the diffusions between the nets could not be guaranteed; diffusion collisions (contacts between diffusions of different transistors) might occur.

So alterations had to be made in the original left edge algorithm. In this chapter, several heuristics will be discussed. Heuristics, used during the placement in order to increase the probability that the generated layout is realizable.

We recall the division of the nets. In chapter 3, we defined three categories:

- 00) nets with a poly/metal contact at one side and a terminal at the other side (a net for an output signal).

- OT) nets with a transistor piece at one end, and a poly/metal contact at the other end.

- TT) nets with one transistor piece at each side.

In Chapter 4, it was explained that if we had two nets for the representation of every transistor, nets of the type TT will not exist. For a start we will only look at nets of the first three types.

#### Heuristic 1.

If a net of group OT is placed, always search for the other transistor part and place the two nets while checking for diffusion collisions.

If all nets of the gate matrix are in the first three groups, Heuristic 1 guarantees that the generated layout is realizable because during the placement of every single diffusion we check for a collision and all nets of one net path are placed at the same time. Problems arise if nets of category TT are present. In that case we may have more than one diffusion in a single net path. The placement of two nets with a realizable diffusion in between at the start of a net path, may disable a diffusion between t wo nets in another part of the net path. To avoid this situation, the following Heuristic should help:

#### Heuristic 2:

If a net of type TT is placed, and both connected transistors have a second half at another net, the net is placed in combination with one of the two nets containing the other transistor pieces. The third net is placed on a stack, and will be placed next.

Note that in this way, it can still not be guaranteed that the diffusion between the net of the type TT and the net on the stack is realizable. In order to lower the chance of a collision, another heuristic is used. Look at the next example:

| example 1<br>net | coli | col2 | col3 | col4     |

|------------------|------|------|------|----------|

| a)               | -    | _    | _    | T0       |

| b)               | T1:  | -    | -    | T0<br>T2 |

| c)               | T1:  | _    | -    | T3       |

| <b>d</b> )       |      | -    | -    | T2       |

## Syntax:

Tx -> a transistor

: -> a diffusion part

- -> a net part

. -> empty

Note: transistor T3 is a transistor connected to a power line thus only one transistor piece will be present among the nets.

Net a) was already placed and net b) has to be placed next. Net c) is placed at the same time and the diffusion of T1 will be realizable. Net d) is put on the stack and will be placed next. The diffusion of T2 cannot be placed because the transistors T0 and T3 block the way in both directions. A solution is brought by the next heuristic:

#### Heuristic 3:

Never place a net of type TT without having placed one of the other nets containing a transistor half first.9

Using this Heuristic, the placement of example 1 becomes:

| example 2<br>net     | coll       | col2        | col3 | col4                   |

|----------------------|------------|-------------|------|------------------------|

| a)<br>c)<br>b)<br>d) | T1:<br>T1: | -<br>-<br>- | -    | T0<br>T3<br>T2:<br>T2: |

Now no collision occurs for T1 or T2; both diffusions can be placed.

The heuristics explained above were implemented into GM. Very seldom a collision occurred and within 3 attempts all the layouts could be realized.

<sup>9.</sup> Note: this Heuristic does not apply to nets of type TT) with one of the transistors having only one transistor piece.

## 8. Net placement with column folding

The placement described so far, does not take any notice of column folding. How can we adapt the net placement to the column folding? From chapter 6, we know what gates have to be assigned to what columns, but we do not know the order of the gates within a certain column; we do not know which rows are going to be crossed by what gates.

In the horizontal direction we used a left edge algorithm. Why not use the same idea in the vertical direction as well. Start a gate in a columns and if the nets connected to this gate are placed, place another gate, out of the set of gates that have to be placed into that column, into the column; again place the nets connected to this column......

In the left edge algorithm we used for net placement in the unfolded gate matrix, it was always allowed to place a certain net. This is not true any more. How do we know whether we are allowed to place a net?

## First we define the array ACTIVE:

ACTIVE[col] = gat: in column col, the gate gat is said to be active if it is allowed to place nets in the gate matrix connected to this gate.

#### Several facts about ACTIVE can be stated:

Out of every column, only one gate can be active at the same time.

Starting the net placement, all the gates that have to be connected with the upper outside of the gate matrix are active because they will have to be the top gates of a column anyway.

A gate, not connected to the bottom side of the gate matrix, can be made active if no other gate folded to the same column is active. If the gate has to be connected to the bottom side of the gate matrix, every other gate folded to the same column has to be placed already: every other gate folded to that column has to be placed above the gate that has to be connected to the bottom side of the gate matrix.

A gate is made inactive if all the nets connected to the gate are placed.

In the columns of the power supply, situated at the left and right side of the gate matrix, the gates containing the power supply are always active.

Looking at ACTIVE, we know what gates we are allowed to use. What we want to know is what nets we are allowed to place. We need to know on what gates the placement of a certain net *depends*; what gates have to be ACTIVE if we want to place a certain net.

The placement of a net depends on the gates the net is connected to. If those gates are inactive, the net can not be placed. If we use the second Heuristic of the last paragraph, we will want to place the nets of a net path without having to place other nets in between, thus increasing the probability of generating a realizable layout.

If we state, the placement of a net depends on the gates connected to the net and on the gates connected to the same net path, we will always be able to place the nets of the net path as a whole. So we state:

A net depends on all the gates connected to the net path, the net is part of.

At this stage the reader should be able to understand why we did not want to fold gates connected to the same net path in the paragraph on column folding. We can not place net paths connected to more than one gate out of a column because the gates connected to the net path will never all be active at the same time.

In the table below, an example is shown:

|   | 1 | 2        | 3 | 4 | 5          | 6         |

|---|---|----------|---|---|------------|-----------|

| a | - | T1<br>T1 |   | • | <u>.</u> . | .         |

| b |   | TI       | - | - | T2         | ·i        |

| C |   |          | • |   | T2         | <u> j</u> |

Net a,b and c, all part of the same net path, all depend on the gates 1,2,4 and 5.

One last Heuristic is used during the net placement. It should assure that the gates in the columns do not use an unnecessary number of rows.

#### Heuristic 4:

Do not make any new gates active if there are still nets left, depending only on gates already active.

The net placement algorithm becomes:

#### **BEGIN**

**END**

The column folding determines whether the exit will be reached or not. If the folding was allowed by the new graph G\_fold, as discussed in the paragraph on column folding, the placement will never fail because of not finding any placeable net.

#### 9. The final steps of the placement

Having ordered the gates and placed the nets, all that remains to be done is the determination of the functions k and l. The next two paragraphs will discuss those functions. The last paragraph discusses what has to be done if an unrealizable layout is generated.

#### 9.1 The function l

The rules for the generation l are quite simple:

- If the two nets, containing a transistor piece of a certain transistor, are situated in the same row of the gate matrix, we also place the transistor in this row.

- If there is only one net containing a piece of a certain transistor, the transistor will be placed in the same row.

- The situation becomes a bit more complicated if we have two nets containing a transistor piece of a certain transistor and they are situated in different gate matrix rows. If we allow one diffusion run for each transistor, only the two rows containing one of the nets are candidates for the transistor placement.

The choice between those two rows is based on the width of the transistors. We choose that gate matrix row that contains the transistor with the largest width already.

#### 9.2 The function k

The function k has to be determined next. Look at the following example:

|   |   | coll |   | col2 | col3 | col4     |   | col5 |   |

|---|---|------|---|------|------|----------|---|------|---|

| 1 | _ | -    | _ | Tl   |      | t3       | _ | -    | - |

| 2 |   | •    |   | •    | T2 - | - T3     |   |      | ı |

| 3 | - | -    | - | tl   | •    | •        |   | T4   |   |

| 4 |   | •    |   | •    | t2 - | <b>-</b> | - | -    | - |

#### Syntax:

. = empty

- = net

tx = metal/diffusion contact for transistor x

Tx = transistor x.

We have to realize diffusions contacting Tx and tx. They can be placed in one of the columns from C', adjacent to the C column in which Tx and tx are placed. Working our way through the matrix from the left to the right, we will try to place each diffusion at the C' column at the left of the C column the transistor is placed in. If this is not possible, we will place the diffusion at the right side.

We will explain the determination of k using the example shown above. We start at the left side of the matrix, at the left of the first C column. We move from top to bottom and look at each row if a diffusion is needed. At the left of column 1, no diffusion has to be placed. At the left of column 2, we can place the diffusion for transistor 1 and at the left of column 3, the diffusion run for transistor 2 can be placed.

We have to be alert arriving at transistor 3. Transistors 2 and 3 will be connected by a

net implemented in the diffusion layer. Therefore, the diffusion of transistor two will have to be situated at the left of T2, and the diffusion of transistor three will have to be situated at the right of T3. In these cases, there is only one C' column available.

We continue to work our way through the columns until we have reached the last row in the last C' column. If by then, all diffusions are placed, we succeeded in generating a layout. If not, we failed and we will have to proceed as described in the next paragraph.

If it is possible to place the diffusions using the given functions f and h, this algorithm will find a diffusion placement. If the placement of diffusion a is disabled by diffusion b at the left C column, there was no alternative placement for diffusion b. If diffusion a cannot be placed in the right C column, this cannot be caused by a diffusion run, but must be the result of a transistor placement. In that case, the net placement is to blame.

### 9.3 Realizability of the layout

The layout generated will not always be realizable. If the layout is not realizable, we have to find out between which diffusions the collision takes place. At least one of the transistors connected to these diffusions is part of a net of the type TT. If that TT net did not exist, the collision would not take place. The TT nets were generated making the structure of the gate matrix. If a gate, connected with two nets of type 0T, was deleted, a net of type TT was born. If the gate is not deleted, the TT net is not generated.

The thing to do, if a collision occurs, is to find out which of the deleted gates was connected to the two nets now included in the TT net causing the collision. If, during the generation of the structure of the gate matrix, this gate is not deleted, the problem causing TT net will not be created and the same collision can not occur.

In the worst case, all the TT nets will be rejected in subsequent runs. Even in this case, the program will still be able to generate a realizable layout since the result of the algorithms discussed in the previous chapters is always realizable if no TT nets are present.

#### 10. The power lines

In chapter 4, the generation of the layout structure was discussed. It was mentioned that all the nets are two terminal nets. The disadvantages of this approach became clear dealing with signals having a lot of contacts. They were subdivided in so many non overlapping gate matrix nets, that the result could not be efficient any more. Signals with many terminals are e.g.:

- a clock signal in clocked logic

- power lines

Because of this effect power nets are treated differently from all other nets. It is not unusual to treat the power nets differently; in many articles discussing gate matrix layout generation, the power nets are situated in a different layer (extra metal layer), and are not really placed in the gate matrix.

In chapter 4 it was also mentioned that the signals connected to the power supply, are not represented by gate matrix nets. Only after the other nets are placed, these power nets are placed. The horizontal part of the power lines is placed in the metal layer, the vertical part in the diffusion layer. The metal part of the power lines can be situated between two tracks of the layout matrix we generated until now. We will call the tracks from the layout matrix made so far "signal tracks", while the possible situations for the power lines will be called "power tracks".

In this chapter, the determination of the position of the power lines will be discussed. First, a matrix POW\_MAT is generated, and using this matrix, the positions of the power lines are calculated.

## 10.1 The Power Matrix