## Technology mapping from boolean expressions to standard cells

#### Citation for published version (APA):

Berkelaar, M. R. C. M., & Theeuwen, J. F. M. (1987). Technology mapping from boolean expressions to standard cells. (EUT report. E, Fac. of Electrical Engineering; Vol. 87-E-174). Eindhoven University of Technology.

Document status and date: Published: 01/01/1987

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

## Eindhoven University of Technology Netherlands

Faculty of Electrical Engineering

# Technology Mapping from Boolean Expressions to Standard Cells

by M.R.C.M. Berkelaar and J.F.M. Theeuwen

EUT Report 87-E-174 ISBN 90-6144-174-9 June 1987 Eindhoven University of Technology Research Reports

EINDHOVEN UNIVERSITY OF TECHNOLOGY

Faculty of Electrical Engineering Eindhoven The Netherlands

ISSN 0167- 9708

i.

Coden. TEUEDE

#### TECHNOLOGY MAPPING

FROM BOOLEAN EXPRESSIONS TO STANDARD CELLS

by

M.R.C.M. Berkelaar and J.F.M. Theeuwen

EUT Report 87-E-174 ISBN 90-6144-174-9

> Eindhoven June 1987

### COOPERATIVE DEVELOPMENT OF AN INTEGRATED, HIERARCHICAL AND MULTIVIEW VLSI-DESIGN SYSTEM WITH DISTRIBUTED MANAGEMENT ON WORKSTATIONS. (Multiview VLSI-design System ICD) code: 991 DELIVERABLE Report on activity 5.2.D: Attempt to build optimisation routines into the logic editor such that the editor generates logic structures geared to the CMOS families found in activity 5.2.C. Abstract: In this report an approach is presented towards the problem of making a standard cells IC implementation from a previously optimised and decomposed set of boolean functions. The algorithms were implemented in Commonlisp. The library of standard cells should contain and-or-invert-gates up to a certain maximum size. Libraries of standard cells for NMOS or CMOS technologies usually do. This maximum size is a parameter to the algorithms, so the program can be used for different libraries of standard cells. The total problem is split up into two subproblems which are treated separately. First, functions which do not fit into standard gates directly, are split up in pieces small enough to fit. Second, the inverters, which are necessary between the gates in a technology with and-or-invert-gates, are removed if possible. Special attention is paid to the inverters on the critical path to speed up the circuit. Both problems are attacked in a partly heuristical and partly analytical way. The heuristical part limits the problem to a size small enough for an analytical approach, which then solves the limited problem completely optimal. Trial runs with international benchmark examples have shown that the approach shows good results deliverable code: WP 5, task: 5.2, activity: 5.2.D. 01 - 06 - 1987 dale partner: Eindhoven University of Technology author: M.R.C.M. Berkelaar, J.F.M. Theeuwen.

This report was accepted as a M.Sc. Thesis of M.R.C.M. Berkelaar by Prof.Dr.-Ing. J.A.G. Jess, Automatic System Design Group, Faculty of Electrical Engineering, Eindhoven University of Technology. The work was performed in the period from July 1987 to May 1987 and was supervised by Dr.ir. J.F.M. Theeuwen.

CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Berkelaar, M.R.C.M.

Technology mapping from Boolean expressions to standard cells / by M.R.C.M. Berkelaar and J.F.M. Theeuwen. - Eindhoven: University of Technology, Faculty of Electrical Engineering. - Fig. + (EUT report, ISSN 0167-9708; 87-E-174) Met lit, opg., reg. ISBN 90-6144-174-9 SISD 663.42 UDC 621.382:681.3.06 NUCI 832 Trefw.: elektronische schakelingen; computer aided design.

## - iii -

### CONTENTS

| :  | 1. AI | BSTRACT                                                | 1        |

|----|-------|--------------------------------------------------------|----------|

|    | 2. II | VTRODUCTION                                            | 2        |

|    | 2     | .1 A Short Overview                                    | 2        |

|    | 2     | .2 Some Definitions                                    | 2        |

|    | 3. TI | HE IMPLEMENTATION IN LISP                              | 4        |

| •  |       | .1 Introduction                                        | 4        |

|    | -     |                                                        | 4        |

|    | -     |                                                        | 5        |

|    | -     |                                                        |          |

|    | -     | .4 The Data-structure                                  | 6        |

|    | د     | .5 The Representation Of The Technology                | 7        |

| 4  | 4. TH | HE STEPS BEFORE AND AFTER THE TECHNOLOGY MAPPING       | 8        |

|    | 4     | .1 Introduction                                        | 8        |

|    | 4     |                                                        | 8        |

|    | 4     | •                                                      | 9        |

|    | 4     | O                                                      | 10       |

|    | 4     |                                                        | 10       |

|    |       |                                                        |          |

|    | 5. WI | EAK DIVISION                                           | 11       |

|    | 5.    | .1 Introduction                                        | 11       |

|    | 5.    | .2 The Approach                                        | 11       |

|    | 5.    |                                                        | 12       |

| 4  | 5. TH | HE ACTUAL MAPPING ONTO STANDARD CELLS                  | 15       |

|    |       |                                                        | 15       |

|    | -     |                                                        | 15       |

|    |       | •                                                      | 17       |

|    |       | • •                                                    |          |

|    |       | 0                                                      | 20       |

|    | 6.    | • •                                                    | 28       |

|    | 6     | .6 The Lisp Implementation 2                           | 29       |

| -  | 7. GI | ETTING RID OF THE INVERTERS AND CRITICAL PATH OPTIMIS- |          |

|    | II    | NG                                                     | 34       |

|    | 7     | .1 Introduction                                        | 34       |

|    | 7     |                                                        | 34       |

|    | -     |                                                        | 36       |

|    |       |                                                        | 36       |

|    |       |                                                        | 37       |

|    |       |                                                        | 39<br>39 |

|    |       | •                                                      |          |

|    | /     | .7 The Lisp Implementation 4                           | 40       |

| t  | B. C( | DNCLUSIONS                                             | 45       |

| 9  | 9. AI | PPENDIX                                                | 46       |

|    |       |                                                        | 46       |

| 1( | ). RE | SFERENCES                                              | 0        |

|    |       |                                                        |          |

i.

## LIST OF FIGURES

| Figure 1. | Graph of expression $a + b + c + d$                   | 15 |

|-----------|-------------------------------------------------------|----|

| Figure 2. | Graph of expression a.b.c.d                           | 16 |

| Figure 3. | Graph of expression a.b.c + d.e.(f + g).(h + i) + j.k | 16 |

| Figure 4. | DAG of gates                                          | 35 |

| Figure 5. | Optimised DAG                                         | 37 |

#### 1. ABSTRACT

In this report an approach is presented towards the problem of making a standard cells IC implementation from a previously optimised and decomposed set of boolean functions. The algorithms were implemented in Commonlisp.

The library of standard cells should contain and-or-invert-gates up to a certain maximum size. Libraries of standard cells for NMOS or CMOS technologies usually do. This maximum size is a parameter to the algorithms, so the program can be used for different libraries of standard cells.

The total problem is split up into two subproblems which are treated separately. First, functions which do not fit into standard gates directly, are split up in pieces small enough to fit. Second, the inverters, which are necessary between the gates in a technology with and-or-invert-gates, are removed if possible. Special attention is paid to the inverters on the critical path to speed up the circuit.

Both problems are attacked in a partly heuristical and partly analytical way. The heuristical part limits the problem to a size small enough for an analytical approach, which then solves the limited problem completely optimal.

Trial runs with international benchmark examples have shown that the approach shows good results.

#### 2. INTRODUCTION

#### 2.1 A Short Overview

Nowadays big efforts are made to generate the layout of (VLSI) integrated circuits automatically, or at least with a lot of computer support. In an ideal situation, the designer would feed some kind of functional description of the desired integrated circuit into the computer, push a button, and after a certain time the complete layout description, ready to go to the mask fabrication, would be produced. Currently, only some stages of the whole process are completely automatic. The designer still has to make a lot of choices at various points of this process.

This report treats some of the problems which arise in the this field of automatic generation of layout for integrated circuits. Specifically, we will describe some steps in the process from algebraic description of a piece of combinational logic to a so-called *standard cell implementation*. This process consists roughly of two steps, the first being *logical optimisation*, and the second *technology mapping*. This last step is the subject of this study.

#### 2.2 Some Definitions

Throughout this report a number of terms will be used with a specific meaning in this context. The logical inversion of <u>an express</u>ion will be denoted with a bar over the expression (i.e. expression). The meaning of the terms "literal", "operator", "expression" and "function" can be derived from the following description:

| <letter></letter>                    | ::= "a"   "b"   "z"   "A"   "B"   "Z"                                      |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| <digit></digit>                      | ::- "0"   "1"   "9"                                                        |  |  |  |  |

| <subscript></subscript>              | ::= { <digit>}+<br/>::= "-"</digit>                                        |  |  |  |  |

| <special></special>                  |                                                                            |  |  |  |  |

| <character></character>              | ::= <letter>   <digit>   <special></special></digit></letter>              |  |  |  |  |

| <variable></variable>                | ::= <letter> (<character>)* [<subscript>]</subscript></character></letter> |  |  |  |  |

| <literal></literal>                  | ::= <variable>   <variable></variable></variable>                          |  |  |  |  |

| <sum></sum>                          | ::= <literal>   {<product> "+"}+ <product></product></product></literal>   |  |  |  |  |

| <product></product>                  | ::= <literal>   {"(" <sum> ")" "."}+ "(" <sum> ")"</sum></sum></literal>   |  |  |  |  |

| <pre><expression></expression></pre> | ::= <product>   <sum></sum></product>                                      |  |  |  |  |

| <function></function>                | ::= <literal> "=" <expression></expression></literal>                      |  |  |  |  |

|                                      |                                                                            |  |  |  |  |

Furthermore the terms "cube" and "sum of cubes" are important and can

be defined like this:

<cube> ::= <literal> | <literal> "." <cube>

<sum of cubes> ::= <cube> | <cube> "+" <sum of cubes>

The last notion we have to define here is "subexpression". Only if an expression is not a single literal, it has so-called subexpressions. There are two possibilities:

- 1. The expression is a sum: the products which build the sum are the subexpressions.

- 2. The expression is a product: the sums which build the product are the subexpressions.

Boolean functions will be denoted according to the above syntax in the report, except in the sections called "The Lisp Implementation", which will describe the Lisp implementation of a specific part of the program. In those sections the representation will be as described in chapter 3, a prefix representation. This prefix representation is the exact image of the way the boolean functions are stored in the datastructure used by the program. The reader who is interested only in the ideas and algorithms and not in the Lisp implementation can skip these sections without missing essential information, and is not required to get acquainted with the prefix notation.

#### - 4 -

#### 3. THE IMPLEMENTATION IN LISP

#### 3.1 Introduction

First it has to be noticed that whenever we use the word Lisp in this report, we actually mean the Lisp dialect Commonlisp. For a complete description of this dialect lit. [4] can be referenced.

There are several reasons Lisp has been chosen to implement the algorithms for the technology mapping operation. The most important one is the possibility to make use of the Lisp standard data structure, the list. As will be shown in the next section, it is very easy to store boolean expressions, functions, and whole sets of functions in such a list. And, what is almost equally important, the implementation of operations on the boolean functions can be written as Lisp operations on lists in a very simple and clear-to-everybody way. No complicated types and structures have to be declared, no obscure pointer statements written, and no memory management done by the program; as would have been necessary when using pascal or C. All of this is hidden on the Lisp program level. And last but not least there is the beauty and simplicity of the basic Lisp structure, which makes it possible to write the Lisp functions in a very simple and beautiful way.

#### 3.2 The Representation Of Expressions And Functions

As "data-structure" we use the Lisp list structure. In the following table the representation of the structures we need is defined:

| boolean structure:                    |     | Lisp representation:                                      |

|---------------------------------------|-----|-----------------------------------------------------------|

|                                       |     |                                                           |

| <variable></variable>                 | ::= | Lisp symbol, symbol-name starting with letter             |

| <variable></variable>                 | ::= | Lisp symbol, symbol-name starting with "~"                |

| <literal></literal>                   | ::= | <variable>   <variable></variable></variable>             |

| <sum></sum>                           | ::= | <li>teral&gt;</li>                                        |

|                                       |     | "(" "+" <product> {<product>}+ ")"</product></product>    |

| <product></product>                   | ::- | <literal></literal>                                       |

|                                       |     | "(" "*" <sum> {<sum>}+ ")"</sum></sum>                    |

| <expression></expression>             | ::= | <sum>   <product></product></sum>                         |

| <function></function>                 | ::- | "(" "=" <literal> <expression> ")"</expression></literal> |

| <set-of-functions></set-of-functions> | ::- | "(" { <function>}+ ")"</function>                         |

The term "subexpression" is defined for the prefix notation in exactly the same way as for infix. If an expression is not just a single literal, it is built by an operator and a list of subexpressions. Again, there are two possibilities:

- 1. The expression is a sum: the products which build the sum are the subexpressions.

- 2. The expression is a product: the sums which build the product are the subexpressions.

An example of a correct set of functions in our Lisp notation:

(( = F1 (+ (\* a -b) (\* c d) e)) (= F2 (\* d e f (+ -a (\* -e -f)))))

In infix notation this set would be denoted as:

$F_1 = a.\overline{b} + c.d + e$  $F_2 = d.e.f.(\overline{a} + \overline{e}.\overline{f})$

As you can see we now denote boolean expressions and functions in a prefix notation. This is standard practice in Lisp expressions, and will prove very useful when we start writing Lisp functions which operate on boolean functions and expressions. It makes it for example especially easy to evaluate the boolean functions in the Lisp environment, although this is something we do not need during the technology mapping. It will however be useful in future extensions. Some practical examples can be found in the next section.

3.3 Some Basic Boolean Function Manipulation In Lisp

3.3.1 Logical inversion of a literal:

This is very simple: if the symbol-name of a literal starts with a "~", it has to be removed, otherwise a "~" has to be added to the front of the symbol-name.

In Lisp this may look like this:

(defun invert-literal (literal) (if (eq (subseq (symbol-name literal) 0 1) "~") (intern (subseq (symbol-name literal) 1)) ;; else (intern (concatenate 'string "~" (symbol-name literal))) ) )

3.3.2 Logical inversion of an expression:

Expressions can be inverted in a very simple way using the Morgan's rules, which (in a prefix notation) state that:

1.

$$(+ a_1 a_2 \dots a_n) = (+ a_1 a_2 \dots a_n)$$

, and:

2.  $(+ a_1 a_2 \dots a_n) = (+ a_1 a_2 \dots a_n)$

So all we have to do is change the operator from \* to + or vise versa, and invert each of the subexpressions a. All we have to watch out for is if the expression we get is a simple<sup>1</sup>literal, in which case our function *invert-literal* will do the job.

Implemented in Lisp this might look like this:

```

(defun invert-expr (expr)

(let (result)

(cond

;; is expr perhaps a single literal?

((symbolp expr)

(invert-literal expr))

;; expr is a list, a complex expression

(t

(setq result (if (eq '* (car expr))

'(+)

'(*)))

(dolist (sub-expr (cdr expr) (reverse result))

(setq result (cons (invert-expr sub-expr) result))

)

)

)

)

```

As you can see the implementation is very short and very clear. The above two functions only serve as an example to show the possibilities we get after choosing Lisp and the prefix notation for the implementation of the algorithms.

#### 3.4 The Data-structure

#### 3.4.1 The set of functions

In all of our Lisp functions we will assume that the set of functions is stored in the global variable *FUNCTION-LIST*. This is done according to the format defined in section 3.2.

Also available is the global variable FUN-NAME-LIST, which is a list with the names of the functions stored in FUNCTION-LIST, in exactly the right order. This list is used to facilitate referencing functions in FUNCTION-LIST. To make changes to FUNCTION-LIST the following functions are defined:

- (add-function-to-function-list <function>) Adds function <function> to the global function-list FUNCTION-LIST. It is added in front, and global variable FUN-NAME-LIST is updated.

- (replace-function-in-function-list <function> <literal>)

If a function with name <literal> is found in FUNCTION-LIST, it

is replaced by <function> and t is returned. FUN-NAME-LIST is

updated if necessary. In all other cases nil is returned.

- (remove-function-from-function-list <literal>) Removes the function with name <literal> from the global function-list FUNCTION-LIST. Returns t if successful, nil otherwise. Global variable FUN-NAME-LIST is updated.

Each of these Lisp functions have the obvious effect of making the desired changes to FUNCTION-LIST destructively. To safeguard the contents of FUNCTION-LIST, these are the only functions allowed to change it.

#### 3.5 The Representation Of The Technology

The technology is represented by a single integer called *gate-size*, which represents the maximum size of a standard cell in the library. This parameter is an argument of the Lisp functions which need it. See also section 6.2.

4. THE STEPS BEFORE AND AFTER THE TECHNOLOGY MAPPING

#### 4.1 Introduction

The whole process from the designer-specified description of a piece of combinational logic to the actual geometrical layout description of this piece of IC area is performed in a series of steps. We can describe them as follows:

- The designer specifies the functional description as a set of logical (= boolean) functions.

- 2. These functions are simplified as far as possible, which means that redundancies are removed.

- 3. The now nonredundant set of functions is decomposed to a certain degree, which means that subexpressions which occur more often than a users-specified minimum are replaced by a new variable, and the subexpression is added as a new function to the set of functions.

- Now the result of the previous step is mapped onto a certain technology (NMOS, CMOS), using some kind of structure (gate array, pla, standard cells, gate matrix...).

- 5. In case of gate arrays and standard cells placement and routing have to be performed as a last step.

Steps 1, 2, 3 and 5 will be looked at in this chapter. The mapping onto standard cells is described in the following chapters.

4.2 The Functional Description

The designer will have to specify a piece of combinational logic as a set of logical (boolean) equations.

With i inputs, j users-specified intermediate functions, and k outputs we get:

$$F_{1} = f(inp_{1} \dots inp_{i}, \overline{inp}_{1} \dots \overline{inp}_{i}, int_{1} \dots int_{j}, \overline{int}_{1} \dots \overline{int}_{j})$$

....

$$F_{k} = f(inp_{1} \dots inp_{i}, \overline{inp}_{1} \dots \overline{inp}_{i}, int_{1} \dots int_{j}, \overline{int}_{1} \dots \overline{int}_{j})$$

$$int_{1} = f(inp_{1} \dots inp_{i}, \overline{inp}_{1} \dots \overline{inp}_{i}, int_{2} \dots int_{j}, \overline{int}_{2} \dots \overline{int}_{j})$$

$$\dots$$

$$int_{j} = f(inp_{1} \dots inp_{i}, \overline{inp}_{1} \dots \overline{inp}_{i}, int_{1} \dots int_{j-1}, \overline{int}_{1} \dots \overline{int}_{j-1})$$

These functions have to be specified as sums of products.

The following small set of functions is provided as a realistic example. It is part of the benchmark set which is used for testing purposes all over the world, and known under the name of "alul". It does not contain intermediate functions.

Example:

$F_{1} = \overline{a} + e.\overline{l} + \overline{e}.\overline{k}$   $F_{2} = \overline{b} + \overline{l}.f + \overline{k}.\overline{f}$   $F_{3} = \overline{c} + \overline{l}.g + \overline{k}.\overline{g}$   $F_{4} = \overline{d} + \overline{l}.h + \overline{k}.\overline{h}$   $F_{5} = e.\overline{a}.\overline{i} + \overline{e}.\overline{a}.\overline{j}$   $F_{6} = f.\overline{b}.\overline{i} + \overline{f}.\overline{b}.\overline{j}$   $F_{7} = g.\overline{c}.\overline{i} + \overline{g}.\overline{c}.\overline{j}$   $F_{9} = h.\overline{d}.\overline{i}$

#### 4.3 Logical Simplification

The logical simplification at this moment is performed by the program  $log_{sim}$ , which removes only certain types of redundancy. Removed is cube containment, resulting in a minimum term prime implicant cover of all the functions.

To give an example of this simplification:

$F = a.b.c + a.b + c.d + c.\overline{d}$

will be reduced to:

F = a.b + c

because cube a.b.c is contained in <u>cube</u> a.b, which means that  $a.b \Rightarrow a.b + a.b.c$ , and because c.d + c.d can be written as c.(d + d), which is clearly logically equivalent to c.

For more information on this subject see lit. [1].

#### 4.4 Decomposition

The decomposition process performed on the set of functions can be guided by the designer with a number of parameters. He can choose a minimum size for subexpressions (measured in literals) to be substituted, and a minimum number of occurrences for them as well, all independently. Also a limit can be put to the logical depth of the resulting set of functions, measured in gate-delays. In this way the size and speed of the resulting circuit can be influenced. For an example of this influence the benchmark results in appendix A. can be referenced.

To give an example of this process, assuming no restrictions on the decomposition, we take the following set of functions:

$F_1 = a.b + c.d + e.f$  $F_2 = a.b + c.d + g.h$

The common term a.b + c.d will be found and substituted, after which the set of functions will become:

$F_{1} = subst + e.f$   $F_{2} = subst + g.h$ subst = a.b + c.d

It should be noted that this step introduces an extra level of logic, and therefore extra delay in the resulting circuit. Inputs a, b, c and d will have to propagate through two gates now before they reach an output. This means that decomposition will make the resulting circuit smaller, but it also makes it slower.

For more information on this subject see lit. [2] and [3].

#### 4.5 Placement And Routing

When the cells necessary to implement the combinational logic are found, they will have to be interconnected. This is called routing. In order to be able to do this with as little wiring as possible, the cells will have to be placed smartly, so the routing is preceded by a placement procedure. Only now the piece of combinational logic is implemented completely.

#### 5. WEAK DIVISION

#### 5.1 Introduction

As we have seen in chapter 3, the starting point of the technology mapping is a set of boolean functions in a sum of cubes format. This sum of cubes format is not very useful for us, because it often contains the same literal more than once. Because each literal which occurs in more than one cube will also mean that number of transistors in a standard cell in NMOS technology extra, or even twice that number of transistors in CMOS, reduction of these multiple occurrences will in the end reduce the necessary number of transistors, and therefore the occupied area on the chip. We will try to get rid of these multiple occurrences by using weak division.

Weak division will split up a function:

$$F = f(a_1 \dots a_n, \overline{a_1} \dots \overline{a_n})$$

in which a, occurs more than once, into:

$$F = a_i \cdot f(a_1 \dots a_{i-1}, a_{i+1} \dots a_n, \overline{a_1} \dots \overline{a_n}) + f(a_1 \dots a_{i-1}, a_{i+1} \dots a_n, \overline{a_1} \dots \overline{a_n})$$

which can also be written like:

F = term.cofactor + remainder

To give a simple example, weak division will change the sum of cubes format:

$$F = a.b + a.c$$

into a complicated expression format:

F = a.(b + c)

#### 5.2 The Approach

All functions from our initial set of functions are treated one by one. As they are expressed as sums of cubes, with each cube containing only literals, weak division upon them is relatively easy. The strategy chosen takes the literal occurring in the biggest number of cubes, and divides that one out. If there are more cubes with the same number of occurrences, the first one found is used. This process is then called recursively on the cofactor and the remainder, and is continued until all multiple occurrences are divided out. Example:

$F = a.b.c.d + a.b.\overline{e.f} + a.g.h + c.i.\overline{j} + i.\overline{j}.k.l$

will be divided in the following steps:

1.  $F = a.(b.c.d + b.e.f + g.h) + c.i.\overline{j} + i.\overline{j}.k.l$ 2.  $F = a.(b.(c.d + e.f) + g.h) + i.(c.\overline{j} + \overline{j}.k.l)$ 3.  $F = a.(b.(c.d + e.f) + g.h) + i.\overline{j}.(c + k.l)$

which can not be reduced further.

It is clear that after this step the functions are no longer sums of cubes, but complicated expressions with an undefined level of bracket nesting.

It is also clear that the strategy of starting with the most often occurring literal does not necessarily give the optimal result, the minimum number of literals. If we take the function:

F = a.b + a.c + a.d.e.f.g.h + d.e.f.g.h.i, containing 16 literals

then the result of our strategy will be:

F = a.(b + c + d.e.f.g.h) + d.e.f.g.h.i, containing 14 literals

whereas the best solution would be:

F = a.(b + c) + d.e.f.g.h.(a + i), containing 10 literals

It would therefore be recommendable to improve the strategy in the respect of choosing the right literal(s) to divide by. At the moment however it is not clear how to do this economically.

#### 5.3 The Lisp Implementation

If we assume the following Lisp functions to be defined:

- (get-most-freq-term <expression>) Returned is a list with the most frequent element in <expression> followed by the number of occurrences. For comparison #'equal is used. <expression> is scanned from left to right, so the leftmost element with the highest number of occurrences is found.

- (remove-l-elt <item> <sequence>) Returned is <sequence> with the first occurrence of <item> removed.

```

then we can write down the weak division algorithm in Lisp like this:

(defun dirty-simpl-by-div (expr)

(let ((divterm (get-most-freq-term expr))

remainder

cube

cofactor)

(cond

((= 1 (cadr divterm)); no term occurs more than once

expr)

(t ; there is something to divide

(setq divterm (car divterm))

(dolist (cube expr)

(cond

((operatorp cube)

nil)

;; is cube perhaps a single literal?

((symbolp cube)

(if (eq divterm cube)

(setq cofactor (cons '1 cofactor))

;; else

(setq remainder (cons cube remainder))))

;; is divterm in this cube?

((member divterm cube :test #'equal); yes, it is!

(if (> (length cube) 3); removing divterm will not

; change cube to single literal

(setq cofactor (cons (remove-1-elt divterm cube)

cofactor))

;; else, cube becomes single literal

(setq cofactor (cons (cadr (remove-l-elt divterm cube))

cofactor))))

;; divterm is not in this cube

(t

(setq remainder (cons cube remainder)))

)

)

```

```

- 13 -

```

```

;; format output

(if (null remainder)

(dirty-simpl-by-div (list '*

divterm

(dirty-simpl-by-div

(cons '+ cofactor))))

;; else

(dirty-simpl-by-div

(cons '+

(append remainder

(list

(list '*

divterm

(dirty-simpl-by-div

(cons '+ cofactor)))))))))

)

)

)

```

This Lisp function is called dirty-simpl-by-div because it sometimes produces "dirty" output like (\* a (\* b (+ ...))) instead of the correct notation (\* a b (+ ...)). This direct nesting of products is not allowed by the definition in section 3.2., and therefore has to be removed by a filtering function. This of course is the case in the total program.

#### 6. THE ACTUAL MAPPING ONTO STANDARD CELLS

#### 6.1 Introduction

At this stage of the process, we are left with a set of boolean functions of unknown structure and size. Many of these functions will be too complex to fit directly on one of the standard cells available in the current technology. Therefore a mapping operation will have to take place, which will split up the big functions into a set of smaller ones, each of which should have a direct counterpart in the set of standard cells. This mapping operation should be as optimal as possible in two respects: big functions should be split up in as few standard cells as possible, and the resulting multiple-level structure of these standard cells should be as fast as possible, i.e. the logical depth should be limited as far as possible.

## 6.2 The Library Of Standard Cells

For this program the library of standard cells should contain all and-or-invert gates up to a certain number of inputs for the and and the or. This maximum number of inputs must be equal for the and and the or gate, to make sure that for any gate of the library the dual gate does also exist. By dual gate we mean the gate with and changed to or and vice versa. The necessity of this requirement will become clear in the next chapter, when we will remove inverters by inverting functions. This maximum number of inputs is a parameter to the program and will henceforth be called gate-size.

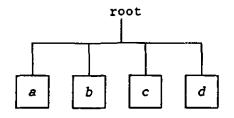

To give a formal definition of which gates are in the library for a given gate-size, we can denote an expression as a directed graph, with every literal forming a node and an or relation giving rise to two parallel edges, opposed to the and relation, which connects two nodes with an edge in series. This seems to be a bit complicated, but a few examples will soon clarify the situation. The expression a + b + c + d has a graph representation as follows:

#### leaves

Figure 1. Graph of expression a + b + c + d

The expression a.b.c.d has a graph representation like:

Figure 2. Graph of expression a.b.c.d

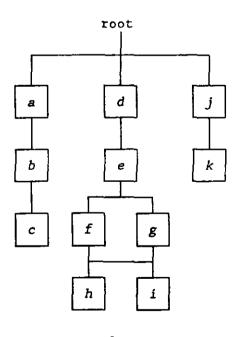

And the more complicated expression a.b.c + d.e.(f + g).(h + i) + j.k has a graph representation:

.

Figure 3. Graph of expression a.b.c + d.e.(f + g).(h + i) + j.k

In this last case the leaves are formed by the nodes c, h, i and k. The graph is directed in the sense that all edges connect downward or horizontally, but never upward. A horizontal part of an edge is therefore bidirectional.

Now the formal definition: A gate belongs to the library with parameter gate-size if and only if:

- 1. There is no path from root to any of the leaves which passes by more than gate-size nodes, and:

- 2. There is no horizontal cut in the graph which cuts more than gate-size edges.

Clearly all 3 above examples are part of all libraries with gate-size  $\geq 4$ .

So, if *gate-size* equals 3 (as it does in the technology currently used on the TUE), the following combined gates for example are in the library:

•

$$F = (a_1 + a_2 + a_3) \cdot (b_1 + b_2 + b_3) \cdot (c_1 + c_2 + c_3)$$

And of course all gates with the same form but missing one or more of the inputs.

•

$$F = \overline{a \cdot (b_1 + b_2) \cdot (c_1 + c_2) + d_1 \cdot d_2 \cdot d_3}$$

And the following gates for example are not included in the library:

•

$$F = \overline{a_1 + a_2 + a_3 + a_4}$$

•  $F = \overline{a.b.(c_1 + c_2) + (d_1 + d_2).e.f}$

Note that the fact that all standard cells have an inverted output will not bother us at this stage. We simply pretend they have straight outputs and add an extra inverter to each gate output later. In chapter 7 an approach to remove as many as possible of these inverters will be presented.

#### 6.3 The Approach

#### 6.3.1 Representation of a complicated function

The approach we use to split up the big functions is partly heuristical and partly analytical. The heuristical part consists of the following two limitations:

We use a so-called top-down approach, i.e. the function is attacked at its highest level, the output level. In this way we hope to get a situation where we map onto big, complicated standard cells near the output of the function, and get possibly smaller and simpler ones near the inputs. If we take for example the function:

F = a.b.c.d + e.f.g.h + i.j.k.l + m.n.o.p

and the library contains standard cells with a maximum gate-size of 3, then the top-down approach breaks down F into the set of functions:

```

F = a.b.subst_{1} + e.f.subst_{2} + subst_{3}

subst_{1} = c.d

subst_{2} = g.h

subst_{3} = i.j.subst_{4} + m.n.subst_{5}

subst_{4} = k.1

subst_{5} = o.p

```

The logical depth (- the biggest number of gates through which an input signal must propagate to reach an output) of the circuit represented by this set of functions is 3. The input signals which have a path of this length, are k, l, o and p.

The *bottom-up* approach however would result in the following set of functions:

$F = a.subst_{1} + subst_{5}$   $subst_{1} = b.c.d$   $subst_{2} = f.g.h$   $subst_{3} = j.k.1$   $subst_{4} = n.o.p$  $subst_{5} = e.subst_{2} + i.subst_{3} + m.subst_{4}$

The logical depth of this circuit is also 3, but now input signals f, g, h, j, k, l, n, o and p have a propagation path of this length.

The reason for this difference in number of input signals with the longest path is that the top-down approach results in bigger gates near the output, and smaller gates nearer to the inputs of the circuit. The bottom-up approach however tries to fit big gates near to the inputs, and near to the output only a small gate may be left. This certainly increases the number of inputs with maximum path length, and possibly in some situations even the logical depth. So we prefer the *top-down* approach here.

- 2. At each moment we limit our view of a certain expression to 1 level, which means we represent it like:

- $expr = subexpr_1 + subexpr_2 + \dots subexpr_n$ , or:  $expr = subexpr_1.subexpr_2.\dots subexpr_n$

whichever is appropriate, and solve the problem of mapping this expression on a tree of standard gates completely optimal, in an analytic way. If any of subexpr, is a complex expression itself, and not just a single literal, this process is continued recursively with these subexpressions until literals are found.

#### 6.3.2 Size restriction

To control this recursive process, the size an expression is allowed to have is represented by a pair of numbers (a, b), with a indicating the number of subexpressions the expression is allowed to have, and b how many sub-subexpressions each of the subexpressions will be allowed to have. Size restriction parameter a is always important at the current level, and b at the next level. In fact, at each level the second size restriction parameter is never used or changed, but only passed on as the first size restriction parameter for the next (lower) level. So, if gate-size equals 3, then at top level, when we enter a function, the size restriction will be (3, 3). Each of the subexpressions of the function will get a size restriction of (3, ...). The value of the second size restriction parameter for the subexpressions depends on what has happened with the expression on the current level, and will be important again for the possible sub-subexpressions, and so forth for every second level. In 6.4.2. this recursive process will be explained in more detail.

A more formal definition of size restriction can be formulated if we picture the expression as a graph, as defined in section 6.2. We must now distinguish two possibilities:

- Expression is a sum. The first size restriction parameter a now is equivalent to the maximum number of edges any horizontal cut in the graph may cut, and the second size restriction parameter b is equivalent to the maximum path length in the graph which is allowed.

- 2. Expression is a product. Now a limits the longest path and b the horizontal cut.

- 19 -

6.4 The Algorithm

6.4.1 The solution of the one level problem If we take the problem of mapping the expression:  $expr - subexpr_1 op \ subexpr_2 op \ \dots \ subexpr_n;$ op being either . or +

and the size restriction (a, b),

then we can calculate the exact structure of the tree of standardgates required to implement this expression. This solution of the one level problem will be optimal in two senses: we will use the minimal amount of standard cells to do it, and the logical depth of the solution will also be minimal. For this we only need the size restriction parameter *a*, telling us how many subexpressions we can leave in the expression, and the technology parameter gate-size, informing us on the maximum size of the potential substitution gates.

6.4.1.1 How does substitution on one level work?

If we see that an expression has more subexpressions than the first size restriction parameter a allows, then we have to limit this number of subexpressions somehow. What we do is to take away a number of subexpressions from the expression and substitute one literal for them instead. This literal has to be unique in the set of functions. To keep the set of functions equivalent to the originally user specified set, we have to add a new function to it, which defines the value of the newly chosen literal. So, if we substitute i subexpressions in an expression with originally n subexpressions, the process is as follows:

expr = subexpr, op subexpr, op ... subexpr

is transformed to the logically equivalent set of functions:

expr = subexpr op ... subexpr op subst subst = subexpr op ... subexprn

Now if n-i is still bigger than a, more of these substitutions will be necessary.

It is wise to take away exactly gate-size subexpressions per substitution, because then the newly formed functions will automatically be mapped to a standard cell which is as big as possible at least in one "dimension". All other possibilities have disadvantages:

• If we would take away less than gate-size subexpressions at a time, more substitutions would be necessary for every big expression, resulting in too many new functions and therefore in too

many standard cells in the resulting circuit. This is a waist of area.

- If we take away more than gate-size subexpressions per substitution, but not a multiple of gate-size, then the resulting substitution functions will have to be split up in their turn, before they fit in a standard cell. But this will then result in at least one function with less than gate-size subexpressions, again not optimal.

- Taking away a multiple of gate-size would be acceptable, but then these substitution functions would themselves have to be split into pieces with exactly gate-size subexpressions, so we might as well do this right away.

#### 6.4.1.2 The number of necessary substitutions

It is now easy to verify that the number of necessary substitutions for an expression with n subexpressions and a current size restriction (a, b) is:

nr-of-subst = ceiling((n - a)/(gate-size - 1))

Verification: we start with n subexpressions, of which a may be left in the end. So we have to get rid of n - a subexpressions. Each substitution takes away gate-size subexpressions, but adds the substitution variable as an extra subexpression to the expression. So the actual number of subexpressions removed per substitution equals gate-size - 1. We have to take the ceiling of the division, because even if one of the substitutions does not have to take away gate-size - 1 subexpressions completely, there still has to be a substitution for this smaller but excessive number of subexpressions.

#### 6.4.1.3 The one level substitution algorithm

Once we have found the number of substitutions, we have to start thinking about how these substitutions should be performed. To give an example of different possibilities for these substitutions we will consider the function:

F = a.b.c.d.e.f.g.h

We will take gate-size to be 3, and accordingly the size-restriction at top level will be (3, 3). This gives as the necessary number of substitutions ceiling((8-3)/(3-1)), which equals 3. Now there are a lot of possibilities to split up F using 3 substitutions, most of which do not have the minimal logical depth. To give a few examples:

subst<sub>1</sub> = f.g.h

subst<sub>2</sub> = c.d.e

subst<sub>3</sub> = subst<sub>1</sub>.subst<sub>2</sub>

$F = a.b.subst_2$

This solution gives us a logical depth in gates of 3. Let's look at another solution:

$subst_{1} - g.h$   $subst_{2} - e.f.subst_{1}$   $subst_{3} - c.d.subst_{2}$   $F - g.b.subst_{3}$

This solution gives us a logical depth of 4! Clearly the previous solution was better. But let's look at a third solution:

$subst_{1} = g.h$   $subst_{2} = d.e.f$   $subst_{3} = a.b.c$  $F = subst_{1}.subst_{2}.subst_{3}$

This one gives us a logical depth of only two, and seems to be the best solution possible.

6.4.1.4 The minimal logical depth

It is possible to calculate the minimum logical depth needed to map a function with n subexpressions, and given gate-size and size-restriction. If the first size-restriction parameter is a, then:

min-depth = ceiling( $gate-size_{\log n/a}$ ) + 1

This formula can also be verified quickly. With a depth of 1 we can handle a maximum of a subexpressions, with a depth of 2, a \* gate-size subexpressions, and with a depth of k, a \* gate-size<sup>k-1</sup> subexpressions. Clearly, the inversion of this formula results in the expression for the minimal depth.

This minimal depth can only be reached if we choose the right substitutions. The algorithm presented here will always find the optimal solution, without actually calculating it. To understand it, we have to switch to the prefix notation now. In this prefix notation, an expression can be represented by:

expr : (operator subexpr, ... subexpr,); n > gate-size

Because the operator is of no importance for the substitution operation, we will take only the list with the subexpressions  $(subexpr_1 \ldots subexpr_n)$ , and formulate the substitution operation on that list.

#### 6.4.1.5 The small gate

The first thing we have to worry about is that there is possibly one gate which does need less than gate-size inputs. This gate will always be one of the substitutes, because we will want the small gate to be one of the leaves of the tree of gates after the substitutions have taken place. The expression which tells us how many inputs this smaller gate will have is:

size-of-small-gate = remainder((n + nr-of-subst - a)/gate-size)

Verification: A total of  $n + nr \cdot of \cdot subst - a$  subexpressions have to be substituted into gates of size gate-size or smaller. Clearly we want as many substitutions as possible to have a size of gate-size. Then the one gate which can be smaller is of the above size. (If  $n + nr \cdot of \cdot subst - a$  is a multiple of gate-size, no small gate will be necessary).

6.4.1.6 The actual substitution

Now the substitutions are performed as follows:

- If size-of-small-gate > 0 substitute the small gate. Take away size-of-small-gate subexpressions from the end of the list, and add the substitution variable to the front of the list.

- 2. Now substitute all the other gates. Every substitution takes away the last gate-size subexpressions from the end of the list, and adds its substitution variable to the front of the list. This is continued until the list contains exactly a subexpressions, the number allowed by the size restriction.

The result of this algorithm is an optimal tree of gates. This can be proven as follows:

We start with a logical depth of 1 in the expression:

(operator subexpr, ... subexpr,)

Now, because we always take away subexpressions from the end of the list for each substitution, and add the substitution variables at the front, the logical depth connected to each subexpression of the list will always be decreasing in the direction of the list. This guarantees that we take away the subexpressions with the lowest possible logical depth. In this way the logical depth will be kept minimal.

#### 6.4.2 The complete mapping algorithm

We now know how to perform mapping on a one level expression. But of course most expressions are much more complicated. We will now discuss the problem of mapping such a complicated expression onto standard cells. We take the complicated expression

subexpr, op subexpr, ... op subexpr,

and a size restriction (a, b). Of course initially both a and b will be equal to gate-size. Each subexpr, is itself an expression of unknown size and structure. Now we distinguish two possibilities:

- 1. n > a: There has to be substitution at this level. Solve the one level problem and then map each of the *a* subexpressions left in the expression with size restriction (*b*, 1). Because all substitution functions are added to the set of functions, they will be mapped later as an independent function.

- 2.  $n \le a$ : No substitutions on this level. Map all n subexpressions subsequently now, the first subexpression with a size restriction (b, a-n+1). Of each subexpression after it has been mapped the size it actually needs is checked. The size an expression needs is also expressed as a pair of numbers, like the size restriction. This pair (x, y) has  $x \le b$  and  $y \le a-n+1$  of course, otherwise substitutions would have been done. Now y is important for us. The second subexpression gets size restriction (b, a-n+1-y+1), and the i-th subexpression, after the other subexpressions have returned an actual size of  $(x_1, y_1) \dots (x_{i-1}, y_{i-1})$ , a size restriction of:

$$(b, a-n+1 - \sum_{j=1}^{j-1} y_j + j-1).$$

So each subexpression gets a chance to expand on the "second level" as far as the situation up to now allows. If this space is not or not fully used up, the next subexpression gets the space which is left over.

The above algorithm requires something we have not yet discussed, the actual size an expression occupies. Its definition is simple: it is equal to the smallest size restriction necessary to get no substitutions with this expression. Therefore, if we picture expression as a graph, it is equal to:

- If expression is a sum, the pair (longest horizontal cut, longest path) of that graph, and

- If expression is a product, to the pair (longest path, longest horizontal cut).

To calculate it we use an equivalent recursive definition:

• An expression with only n literals occupies a space of (n, 1). So a single literal occupies a space of (1, 1). An expression with n subexpressions, each of which occupies a space of (x<sub>i</sub>, y<sub>i</sub>), occupies a total space of

n

( ∑ y<sub>i</sub>, max(x<sub>1</sub> ... x<sub>n</sub>))

i=1

i

This recursive definition also has its counterpart in graph theory:

- If we connect subgraphs in parallel, which is equivalent to making a sum out of (product-)subexpressions, then the longest horizontal cut of the total graph will be the sum of the longest cuts of the subgraphs, and the longest path in the graph will be equal to the maximum of the longests paths of the subgraphs.

- If expression is a product, then we connect the subgraphs in series. Now the longest horizontal cut of the resulting graph will be equal to the maximum of the horizontal cuts of the subgraphs, and the longest paths of the graph is equal to the sum of the longest paths of the subgraphs.

#### 6.4.3 A complete example

To illustrate the mapping algorithm, we will perform the mapping of a function step by step. To make the process reasonably interesting, we will assume a *gate-size* of 4. The function to be mapped is:

F = a.(b + c).(d + e.(g + h + i)).(j + k.(l + m)) + n.o.p.(q + r + s.(t + u))

It is clear that F is a sum, and consists of 2 subexpressions. To write down the steps the algorithm performs, we will make use of some formatting definitions. Each time we enter the mapping algorithm, we will write a line like "-entering: expression, size-restriction". The return value of the algorithm will be stated with "-returning: expression, actual-size". The recursive nesting will be shown by indenting the lines when we move down a level.

So, we enter the algorithm with the complete expression and a size restriction of (4, 4).

```

-entering: a.(b + c).(d + e.(g + h + i)).(j + k.(l + m))

+ n.o.p.(q + r + s.(t + u)), (4, 4).

expression is a sum with 2 subexpressions.

-entering: a.(b + c).(d + e.(g + h + i)).(j + k.(1 + m)), (4, 3).

expression is a product with 4 subexpressions.

-entering: a, (3, 1).

-returning: a, (1, 1).

-entering: b + c, (3, 1).

expression is a sum with 2 subexpressions

-entering: b, (1, 2).

-returning: b, (1, 1).

-entering: c, (1, 2).

-returning: c, (1, 1).

-returning: b + c, (2, 1).

-entering: d + e.(g + h + i), (3, 1).

expression is a sum with 2 subexpressions

-entering: d, (1, 2).

-returning: d, (1, 1).

\rightarrowentering: e.(g + h + i), (1, 2).

expression is a product with 2 subexpressions

n > a, so substitution has to be performed

the new function subst_1 = g + h + i is

formed

-returning: subst_1, (1, 1).

\negreturning: d + subst_1, (2, 1).

```

```

-entering: j + k.(1 + m), (3, 1).

expression is a sum with 2 subexpressions

-entering: j, (1, 2).

-returning: j, (1, 1).

\negentering: k.(1 + m), (1, 2).

expression is a product with 2 subexpressions

n > a, so substitution has to be performed

the new function subst_2 = k \cdot (1 + m) is

formed

-returning: subst<sub>2</sub>, (1, 1).

-returning: j + subst_2, (2, 1).

-returning: a.(b + c).(d + subst_1).(j + subst_2),

(4, 2).

-entering: n.o.p.(q + r + s.(t + u)), (4, 2).

expression is a product with 4 subexpressions

-entering: n, (2, 1).

-returning: n, (1, 1).

-entering: o, (2, 1).

-returning: o, (1, 1).

→entering: p, (2, 1).

-returning: p, (1, 1).

-entering: q + r + s.(t + u), (2, 1).

expression is a sum with 3 subexpressions

n > a, so substitution has to be performed

the new function subst_{2} = r + s.(t + u)

is formed

-returning: subst_3 + q, (2, 1).

-returning: n.o.p.(q + subst_3), (4, 2).

-returning: a.(b + c).(d + subst_1).(j + subst_2) + n.o.p.(q + subst_3),

(4, 4).

The result of this mapping operation is a set of 4 functions:

= a.(b + c).(d + subst_1).(j + subst_2) + n.o.p.(q + subst_3)

F

subst_1 = g + h + i

subst_2 = k.(1 + m)

subst_3 = r + s.(t + u)

```

#### 6.4.4 Possible future improvements to the algorithm

The main disadvantage of this algorithm is that the subexpressions of an expression are not investigated at all before determining how to substitute. It might well be useful to change this in future. Some kind of sorting operation on the subexpressions based upon their size could make the algorithm better.

#### 6.5 Optional Removal Of Equivalent Functions

#### 6.5.1 Introduction

If the decomposition previous to the technology mapping was not exhaustive, meaning that it was limited to subexpressions with a minimum size greater than 2, or a minimum amount greater than 2, then it is possible that some of the remaining equal subexpressions are found during our mapping operation. This will mean that there will be 2 or more functions in the set which are exactly the same. This also implies having two different gates on the chip doing exactly the same job. This is a waist of area, and therefore we will try to remove this redundancy.

Because this test is only necessary if the decomposition was limited, it is optional and can be switched on and off by the designer.

#### 6.5.2 The algorithm

Because testing for logical equivalence is a very time intensive operation, and because we know that the set of functions is freed as far as possible of redundancies, we will use a simpler algorithm instead. If we compare two functions, we will sort them uniquely, and then see if the results are subexpression by subexpression exactly equal. Only in that case we will declare them "equivalent" and remove one of them from the set of functions. Starting with leaf functions and working towards the outputs we test every function of the set (and its inverse) with every other function in this way, and remove the "equivalent" ones immediately. Of course all references to the removed functions are changed too. In this way we also find equivalences which occur only after another equivalence was removed.

#### 6.5.2.1 The sorting of expressions

Expressions are sorted with the relation expr<.  $(expr< expr_1 expr_2)$  returns t when:

In case both expr<sub>1</sub> and expr<sub>2</sub> are literals: if (string< expr<sub>1</sub> expr<sub>2</sub>) returns t (so they are put in alphabetical order).

- If one is a literal and the other is a complicated expression: the literal is considered expr< than the complicated expression. The complicated expression is sorted recursively.

- 3. When both are complicated expressions: The first subexpressions of the sorted (!) expressions are recursively compared with expr<.

Thus recursively sorted, all functions will have a unique representation.

#### 6.6 The Lisp Implementation

6.6.1 The mapping algorithm

The algorithm described in 6.4.2. is implemented in the Lisp function (implement-expr <gate-size> <expression> <size-restrl> <size-restr2>). The Lisp code follows the algorithm step by step and should not be difficult to understand.

```

(defun implement-expr (gate-size expr max-nr-of-subexprs

max-subexpr-length)

;; We need quite a lot of local variables, here they come:

(let* ((expr-length (l- (length expr)))

(current-operator (car expr))

(result-expr (list current-operator))

result-of-sub-impl

(max-incr-subexpr-length-used 1)

(total-incr-subexpr-width-used 0)

incr-subexpr-width-used

incr-subexpr-length-used

new-function-def

new-name

new-expr

subexprs-left

first-strip

nr-of-subst)

```

(cond

```

;; are there too many subexpressions?

((> expr-length max-nr-of-subexprs)

;; first we calculate how many substitutions will have

;;to be done, and how many subexpressions should be taken

;; away the first time ('first-strip')

(setq nr-of-subst

(ceiling (/ (- expr-length max-nr-of-subexprs))

(float (1- gate-size)))))

(setq first-strip

(rem (- (+ expr-length nr-of-subst)

max-nr-of-subexprs)

gate-size))

;; is there a gate with less than gate-size subexpressions?

(unless (zerop first-strip)

;; make new function out of last first-strip subexprs

(setq new-function-def

(cons current-operator

(nthcdr (1+ (- expr-length first-strip)) expr)))

;; update expr

(setq expr

(subseq expr 0 (1+ (- expr-length first-strip))))

;; get new name for substitution function

(setq new-name (intern (symbol-name (gensym))))

;; and add it to the front of expr

(setq expr (cons current-operator (cons new-name (cdr expr))))

(setq expr-length (1- (length expr)))

;; add new function to FUNCTION-LIST

(add-function-to-function-list (list equivalence

new-name

new-function-def))

```

)

```

;; now we start taking away 'gate-size' subexpressions at a

;; time until the expression is no longer too long. Substitution

;; is exactly the same as above

(while (> expr-length max-nr-of-subexprs)

(setq new-function-def

(cons current-operator

(nthcdr (l+ (- expr-length gate-size)) expr)))

(setq expr (subseq expr 0 (1+ (- expr-length gate-size))))

(setq new-name (intern (symbol-name (gensym))))

(setq expr (cons current-operator

(cons new-name (cdr expr))))

(setq expr-length (1+ (- expr-length gate-size)))

(add-function-to-function-list (list equivalence

new-name

new-function-def))

))

;; all substitutions ready, at most max-nr-of-subexprs now

(setq subexprs-left (length (cdr expr)))

(dolist (subexpr (cdr expr))

(setq subexprs-left (1- subexprs-left))

(cond

((symbolp subexpr); subexpr is a literal

(setq result-expr (cons subexpr result-expr))

(setq max-nr-of-subexprs (1- max-nr-of-subexprs))

(setq total-incr-subexpr-width-used

(l+ total-incr-subexpr-width-used)))

(t ; subexpr is a list, a complicated expression

(setq result-of-sub-impl (implement-expr subexpr

max-subexpr-length

(- max-nr-of-subexprs

subexprs-left)))

(setq new-expr (car result-of-sub-impl))

(setg incr-subexpr-length-used (cadr result-of-sub-impl))

(setq incr-subexpr-width-used (caddr result-of-sub-impl))

;; update Σ y,

(setq total-incr-subexpr-width-used

(+ incr-subexpr-width-used

total-incr-subexpr-width-used))

```

)

```

;; update \max(x_i)

(if (> incr-subexpr-length-used max-incr-subexpr-length-used)

(setq max-incr-subexpr-length-used

incr-subexpr-length-used)

)

(setq result-expr (cons new-expr result-expr))

(setq max-nr-of-subexprs

(- max-nr-of-subexprs incr-subexpr-width-used)))

)

)

;; Make return-value

(if (= 2 (length result-expr)); result-expr of form (sgnlx +)

(list (car result-expr)

total-incr-subexpr-width-used ; r y

max-incr-subexpr-length-used) ;max(x,)

(list (nreverse result-expr)

total-incr-subexpr-width-used ; \Sigma y_j

max-incr-subexpr-length-used) ; max(x_j)

)

)

```

)

- 32 -

6.6.2 The optional removal of equivalent functions

If we compare two functions, we sort them using the Lisp function (sort <sequence> <test>). After this they are compared with the Lisp function (equal <item1> <item2>). As test for (sort ...) we define the following function: (defun expr< (expr1 expr2)</pre> (cond ((and (symbolp exprl) (symbolp expr2)) (string< (symbol-name exprl) (symbol-name expr2)))</pre> ((symbolp exprl) ; But not expr2! (sort (cdr expr2) #'expr<)</pre> t) ((symbolp expr2) ; But not expr1! (sort (cdr exprl) #'expr<)</pre> nil) ;; Now both expr1 and expr2 are complicated expressions (t

)

To understand this function fully, we must bear in mind that the car of an expression is always an operator, and that (sort ...) sorts destructively. So we always sort the cdr of an expression only.

Two complicated expressions are sorted comparing only their first subexpressions. This is of course not unique for all expressions, because subexpressions like (+ a b c) and (+ a d e) could not be distinguished. But in our case, where redundancies are removed and literals which occur more than once are divided out, this situation never occurs.

#### 7. GETTING RID OF THE INVERTERS AND CRITICAL PATH OPTIMISING

### 7.1 Introduction

The situation now is that we have a set of logical functions, all broken down to a size small enough to have a standard cell in the library which can implement them. All of the functions represent and-or or or-and combined gates, or simple and or or gates. The problem is however, that the libraries of standard gates contain only and-invert, or-invert, and-or-invert and or-and-invert gates, because these are the most natural ones in the technology which is being used. This is the case for NMOS and CMOS for example.

This implies that every standard cell we use will have to be followed by an inverter to restore the function we actually need. This has several great disadvantages. First, the extra inverters enlarge the necessary area on the chip, something which is undesirable. Secondly, the whole circuit is slowed down considerably, if we take a unit gate delay, even to half the speed that we expected when we were only looking at the set of functions. So it is clear that we will have to try to improve this situation.

# 7.2 The Set Of Functions Represented As A Graph

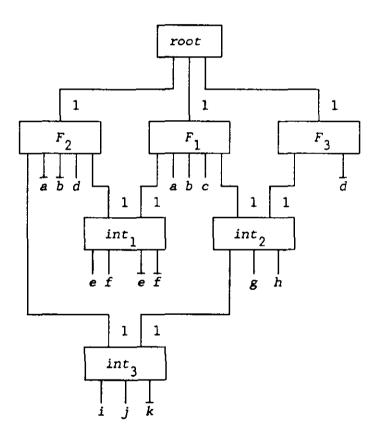

As we have seen in the previous chapter, a system of connected gates can be represented by a graph. Each gate becomes a node, and the relation "being an input of" creates an edge of the graph. If we introduce an extra node, which we call root, and declare all outputs of the circuit to be connected to root, then we have a directed a-cyclic graph (DAG) in which we can easily find these outputs. Each edge is directed in the sense that it points towards the outputs, and therefore follows the flow of the signals in the circuit. For reasons of simplicity we do not represent inverters as nodes in the DAG, but instead introduce two types of edges, one meaning "straight connection", and the other "connection through inverter". Associated with these two types of edges are numbers which indicate the delay in that connection, being 1 and 2 respectively. To give a small example we consider the following set of functions:

$$F_{1} = a.b + int_{1} + c.int_{2}$$

$$F_{2} = \overline{a.b} + d.int_{1} + int_{3}$$

$$F_{3} = \overline{d} + int_{2}$$

$$int_{1} = e.f + \overline{e.f}$$

$$int_{2} = g.\overline{h} + int_{2}$$

$$int_{3} = i.j + \overline{k}$$

i.

If we make a DAG out of this set directly we get the following result:

Figure 4. DAG of gates.

If we have a technology which requires extra inverters after each gate, we get exactly the same DAG, with the exception that the number next to each edge must be changed to "2".

# 7.3 The Delay In A Circuit

If we take a look at Fig. 4., it is clear that signals i, j and k have the longest way to travel before they reach an output. If we assume the normal situation with inverters following every output, and therefore all edges get a delay of 2, then, if we add up all delays on the path of *i*, *j* and *k*, we get 6. In fact, these signals determine the speed of the whole circuit. All other signals have a shorter way to the output. So it is clear that the speed of the whole circuit is determined by the longest path in the DAG, if we define path length as the sum of the delays as described by the type of edge. This longest path is therefore named the critical path. It is clear that if we want to influence the speed of a circuit we will have to do something about the delay on the critical path.

# 7.4 Inverting A Function In A DAG

If we consider the operation of inverting a function in the set of functions without changing the logical behaviour of the whole set, we can consider the Morgan's laws again. For reference, they were written down in section 3.3.2. With these we can see that a function is logically equivalent to its inversion with inverters added to both the output and all of the inputs.

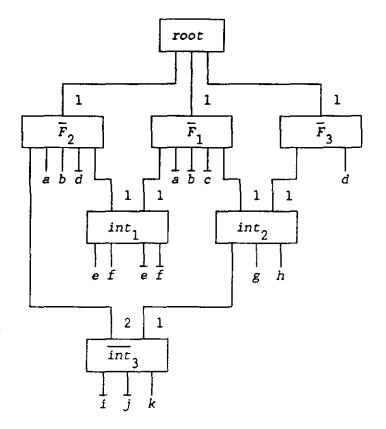

Now if we note also that two inverters in series add up to no inverter at all, we have found a way to manipulate inverters, without changing the logical behaviour of a circuit. If we face the situation, as we often do, that all functions are connected through inverters, then we can try to get rid of as many of them as possible by selectively inverting some functions in the set. In the example of section 7.2. it would be possible to get rid of most of them by inverting  $F_1$ ,  $F_2$ ,  $F_3$ and int<sub>2</sub>. The resulting set of functions then becomes:

$$\overline{F}_{1} = (\overline{a} + \overline{b}) \cdot \overline{int}_{1} \cdot (\overline{c} + \overline{int}_{2})$$

$$\overline{F}_{2} = (a + b) \cdot (d + \overline{int}_{1}) \cdot \overline{int}_{3}$$

$$\overline{F}_{3} = d \cdot \overline{int}_{2}$$

$$int_{1} = e \cdot f + \overline{e} \cdot \overline{f}$$

$$int_{2} = g \cdot \overline{h}$$

$$\overline{int}_{3} = (\overline{i} + \overline{j}) \cdot k$$

Figure 5. Optimised DAG.

The length of the longest path is now reduced to 3. In fact there are three paths with this length,  $int_3 \rightarrow F_2 \rightarrow root$ ,  $int_3 \rightarrow int_2 \rightarrow F_3 \rightarrow root$  and  $int_3 \rightarrow int_2 \rightarrow F_1 \rightarrow root$ . As you can see there is still an inverter left between  $int_3$  and  $F_2$ . Trying to remove it would however lengthen the critical path. It could be done by inverting either  $int_3$  or  $F_2$ , but in both cases other inverters are added to the circuit which only make the situation worse.

#### 7.5 Which Functions Must Be Inverted?

The answer to this question is by no means simple. It has been proven that to find the optimal solution, with the minimal number of inverters, is a N.P. complete problem. So finding this solution for big examples is probably not feasible. But then we must realise what goals we are really after. Mainly, we are interested in the speed of the circuit. But in section 7.3. we have seen that this speed is only determined by the critical path, and therefore by a few inverters only. On the other hand we still regard area as being important too. So the inverters in those parts of the circuit which are not on the critical path bother us as well.

To solve this situation the following strategy has been chosen:

- 1. At first we make a global run through all the functions in the set, and determine with the use of some simple heuristics whether or not to invert this function. At this stage we limit our view to the output and the inputs of the function and base our decision upon that view only. In this way we hope to get rid of most of the inverters, but we can not claim an optimal solution.

- 2. Secondly, we find out what the critical path is (or: paths are), and shorten this path (these paths) rigorously. In the simple case of straight paths this means that at most one inverter is left in each of them. This process is then repeated for the new critical path(s), until no progress is possible any more.

This approach will yield a result with few inverters in the whole circuit, if we choose the right heuristics for step 1. The speed of the whole circuit, determined by the delay on the critical path, should be (near) optimal. Yet the implementation in Lisp can be very fast.

7.5.1 The global optimising phase

All functions are considered for inversion only once, in an order which takes functions near the root first, and leaf functions last. They are inverted if:

- In case of leaf functions:

- if all input variables are inverted, OR

- if they do not have straight (= connected without inverter) parents AND more inverted variables as inputs than straight variables.

- In case of an intermediate or output function:

- if they have more children through inverters than straight children AND no straight parents.

The above strategy is simple and fast, and mainly based on common sense. Very probably it could still be improved, not enough experimenting has been done with it. It has however shown to give good results in many trial examples, very often even a result with the optimal critical path length. However, our main goal was minimising delay, and this problem will be attacked much more thoroughly in the next section.

# 7.5.2 Critical path optimising

The algorithm is as follows:

- 1. First, we have to determine the critical path(s). This is done with a standard longest path algorithm from lit. [5]. The path-length of root is equal to 0, and all other nodes get a path-length entry equal to the maximum of the path-length of its parents plus the delay determined by the type of edge that connects this parent. The leaf nodes with the longest path-length then determine the critical paths. The paths themselves are found by tracing backward from those leaf nodes. From the set of parents of a node on a critical path only those parents are on the path which have a path-length exactly equal to the local node's path-length minus the delay on the connecting edge.

- 2. After these paths have been found, they are shortened one by one. Starting at root all inverters are wiped off the path by making the necessary inversions of functions. Finding an inverter means invert the next function on the path. If the path forks, each branch is treated in this way. If there is reconvergent fanout on the path, which means that after forking several branches come together again, the rest of the path gets wiped more than once. When a leaf function is reached, the inverter in its output is removed unless the function has straight variables as inputs only.

- 3. Last, all path lengths are updated to the new situation. The new critical paths are determined. If these new critical paths are not shorter than the old ones were, stop. Otherwise go to step 2 and shorten the new critical paths.

# 7.6 Optional Resubstitution

# 7.6.1 Introduction

In some cases where speed is very important, it can be useful to try to turn back some of the kernel or cube substitutions done during the decomposition program. The implementation will have a few extra transistors, and therefore a larger area, but the trade-off between speed and area may be worth wile. This resubstitution can however only be possible if the minimum kernel-size or the minimal cube-size specified for the decomposition was smaller than or equal to gatesize, and even then it is not guaranteed to succeed. Because of this fact resubstitution is an option for the designer, who can determine beforehand whether it could be successful or not. The resubstitution is currently limited to the leaf functions of the critical paths only. Perhaps in future it could be extended to functions in other places of the critical path(s), but that will complicate matters considerably.

After the critical path optimisation stops, it is determined if it would be possible to resubstitute all of those leaf functions of the critical paths into their parents on the critical paths. Only if all of those resubstitutions are allowed by the gate-size restriction, the circuit can be speeded up. Even if only one should not be allowed, then there would still be a critical path left which keeps the circuit at the old speed. So all are resubstituted, or none.

After a successful resubstitution, the resulting new critical paths are determined, and critical path optimisation is started again. After this resubstitution is tried again, and the program keeps on resubstituting and optimising until the resubstitution fails. In appendix A. the number of successful resubstitution and optimising runs for the benchmark tests are recorded under "resubstitution level". Several times 3 consecutive runs were possible, speeding up the circuit considerably.

### 7.7 The Lisp Implementation

### 7.7.1 The representation of the DAG

To create the DAG of functions the following data-structure is defined. Each function-name is bound to a vector of length 11, and the definition of the contents of this vector are on position:

- 0: <expression> denoting the function definition.

- 1: a list of children which are connected straight.

- 2: a list of children which are connected through an inverter.

- 3: a list of parents which are connected straight.

- 4: a list of parents which are connected through an inverter.

- 5: an integer denoting the maximum path length from this function to root.

- 6: a list with all inputs of this function.

- 7: if this function is on (one of the) critical path(s), then a list of children which are also on the path and connected straight.

- 8: if this function is on (one of the) critical path(s), then a list of children which are also on the path and connected through an inverter.

- 9: if this function is on (one of the) critical path(s), then a list of parents which are also on the path and connected straight.

- 10: if this function is on (one of the) critical path(s), then a list of parents which are also on the path and connected through an inverter.

Of course at certain stages of the program not all of these items are specified. There is however a minimum set of specified items, set to the right value by the function (initialise-function-DAG). This functions sets items 0, 1, 2, 3, 4 and 6. The information for this is taken from global variable FUNCTION-LIST.